# DANIEL KOSLOPP DISTRIBUTED PROCESSING IN FPGA ACCELERATED CLOUD

Master of Science thesis

Examiner: Prof. Timo D. Hämäläinen Examiner and topic approved by the Faculty Council of the Faculty of Computing and Electrical Engineering on 29th August 2018

#### **ABSTRACT**

**DANIEL KOSLOPP**: Distributed Processing in FPGA Accelerated Cloud

Tampere University of Technology Master of Science thesis, 76 pages

December 2018

Master's Degree Programme in Information Technology

Major: Pervasive Systems

Examiner: Prof. Timo D. Hämäläinen

Keywords: Hardware Accelerator, FPGA, NFV, Cloud, SDN, Machine Learning

Motivated by the need of cost reduction, better energy efficiency and agile update and deployment of new services, telecommunication industry is moving towards virtualization, which lead to Network Function Virtualization (NFV) standard. NFV leverages cloud technologies to deploy network functions that are traditionally implemented using dedicated proprietary hardware. Still, the performance provided by current cloud infrastructure does not fulfill the requirements for demanding NFV's use cases. Thus, hardware acceleration should be deployed.

The hardware programmability of FPGAs allows them to adapt well to many type of workloads, placing them as good candidates to be used as hardware accelerators in virtualized environments. In this thesis, the CRUN framework is proposed to provide FPGA as hardware accelerator resources in cloud, abstracting the integration complexity while enabling sharable and scalable use of such devices.

CRUN architecture allow user's acceleration hardware to be accessed locally and through the datacenter's network. The latter provide flexible connectivity by following the Software-defined Networking (SDN) principles. The architecture enables the same sharable FPGA to be used simultaneously as a co-processor, a network accelerator or as a distributed accelerator in a scalable scenario over several FPGAs.

In its current development state, CRUN was leveraged for inference of a machine learning application composed of a fully connected neural network. The main performance target was to achieve ultra-low latency, less than  $40\mu$ s, for each inference at software level. Only CRUN fulfilled the requirement among the analyzed alternatives, where the architecture is capable of providing latency in the  $30\mu$ s range in average. For context, high-end General-Purpose Processor (GPP) and Graphics Processing Unit (GPU) provided latency values of  $798\mu$ s and  $1897\mu$ s respectively for the same application.

II

**PREFACE**

At first, I thank God for all the blessings in my life.

I would like to thank Nokia for all the support and working hours I had available to dedicate to this work. Also, I would like to express my gratitude to all my colleagues that are part of it: Anssi Örn, Kalle Holma, Pekka Jokela, Aki Kaihtela and Miika Jokinen.

Special big thanks to Jouni Markunmäki for the immeasurable technical guidance and support, Piia Saastamoinen for the careful review, Hannu Tulla for solving all possible problems with the laboratory and obrigado to Juho Tieaho for SDN development and the daily cooperation in any challenge.

I wish to thank Prof. Timo D. Hämäläinen for the opportunity to conduct my thesis under his supervision and all the assistance.

My most sincere thanks to my father Silvio Koslopp, my mother Maria Elisabeth G. Koslopp and my brother Denilson Koslopp, all of who have always supported me in all aspects and decisions in my life.

At last, my deepest gratitude, admiration and love to the greatest partner of my life, Talita Tobias Carneiro, for being my light and inspiration.

Tampere, 20.11.2018

Daniel Koslopp

# TABLE OF CONTENTS

| 1. | Introduc  | tion                                | 1  |

|----|-----------|-------------------------------------|----|

| 2. | Virtualiz | zation In Mobile Networks           | 4  |

|    | 2.1 Clo   | oud RAN                             | 4  |

|    | 2.2 Ne    | twork Function Virtualisation       | 7  |

|    | 2.2.1     | VNF Layer                           | 8  |

|    | 2.2.2     | NFVI                                | 9  |

|    | 2.2.3     | MANO                                | 10 |

|    | 2.3 Clo   | oud Computing                       | 11 |

|    | 2.3.1     | Virtualisation and Orchestration    | 12 |

|    | 2.3.2     | Deployment Modes of Cloud Computing | 14 |

|    | 2.3.3     | Service Models of Cloud Computing   | 15 |

|    | 2.4 Sof   | tware-defined Networking            | 16 |

|    | 2.4.1     | Data Plane                          | 17 |

|    | 2.4.2     | Control Plane                       | 18 |

|    | 2.4.3     | Management plane                    | 19 |

|    | 2.5 Clo   | oud Computing, NFV and SDN          | 20 |

| 3. | Hardwai   | re Acceleration in Cloud            | 24 |

|    | 3.1 Acc   | celerators                          | 24 |

|    | 3.1.1     | Workload Characteristics            | 25 |

|    | 3.1.2     | Connectivity Options                | 26 |

|    | 3.1.3     | Deployment Topologies               |    |

|    | 3.2 FP    | GAs in Cloud                        | 29 |

|    | 3.2.1     | Programming Languages               | 30 |

|    | 3.2.2     | Design Flow                         | 30 |

|    | 3.3 FP    | GA Virtualization                   | 31 |

|    | 3.3.1     | Sharing                             | 32 |

|    | 3.3.2     | Abstracting                         | 33 |

|     | 3.3.3     | Securing                               | 33 |

|-----|-----------|----------------------------------------|----|

|     | 3.3.4     | Scaling                                | 34 |

| 4.  | Related   | Work                                   | 35 |

|     | 4.1 Ha    | ardware Acceleration Only              | 35 |

|     | 4.2 Pa    | rtially Scalable Hardware Acceleration | 36 |

|     | 4.3 Fu    | lly Scalable Hardware Acceleration     | 37 |

|     | 4.4 Ha    | ardware Acceleration in NFV            | 39 |

| 5.  | Method    | ology                                  | 41 |

|     | 5.1 Ha    | ardware and Laboratory Setup           | 41 |

|     | 5.2 So    | ftware and Libraries                   | 42 |

|     | 5.3 Te    | st Cases                               | 43 |

| 6.  | CRUN .    | Architecture                           | 44 |

|     | 6.1 CF    | RUN FPGA's Hardware                    | 44 |

|     | 6.1.1     | Server and Datacenter                  | 44 |

|     | 6.1.2     | CRUN Shell                             | 46 |

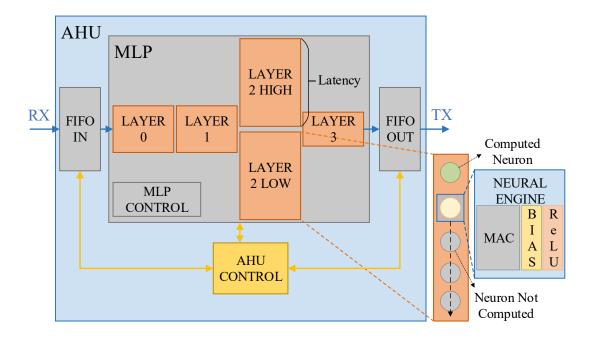

|     | 6.1.3     | Accelerator Hardware Unit              | 51 |

|     | 6.2 BF    | RO Management Software                 | 52 |

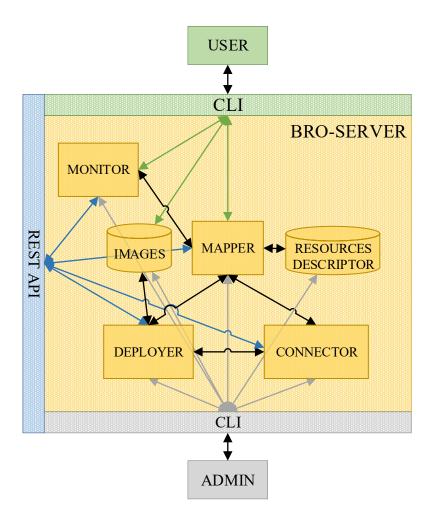

|     | 6.2.1     | BRO-SERVER                             | 52 |

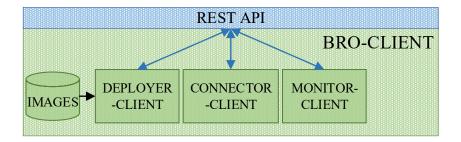

|     | 6.2.2     | BRO-CLIENT                             | 54 |

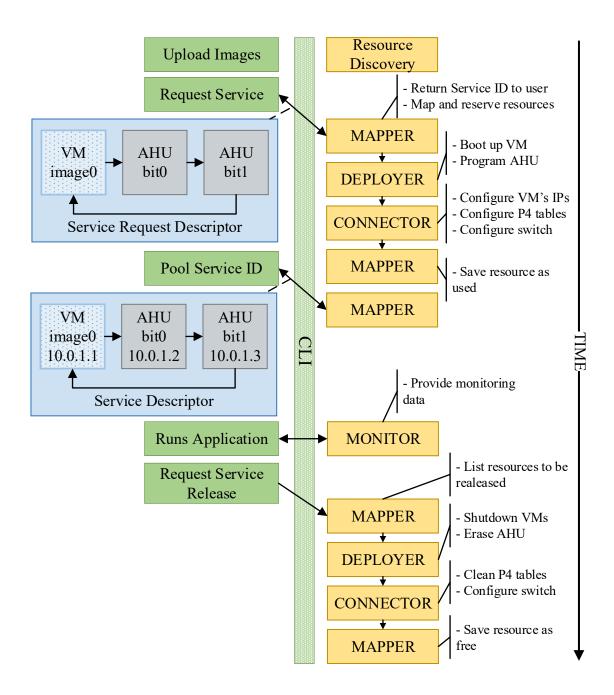

|     | 6.2.3     | BRO Usage                              | 55 |

| 7.  | Evaluat   | ion                                    | 58 |

|     | 7.1 De    | velopment State                        | 58 |

|     | 7.2 Ha    | ardware Metrics                        | 58 |

|     | 7.3 Tr    | ial                                    | 60 |

|     | 7.4 Ar    | nalysis                                | 64 |

|     | 7.4.1     | Hardware                               | 64 |

|     | 7.4.2     | Software                               | 65 |

| 8.  | Conclus   | ions                                   | 67 |

| Bil | bliograph | ıy                                     | 69 |

# LIST OF FIGURES

| 2.1 | Cloud RAN vs RAN                              | 5  |

|-----|-----------------------------------------------|----|

| 2.2 | Traditional network vs NFV                    | 8  |

| 2.3 | NFV architecture                              | 9  |

| 2.4 | NFV's main terminology                        | 11 |

| 2.5 | Virtua Machines vs Containers                 | 13 |

| 2.6 | Service models of cloud computing             | 15 |

| 2.7 | Software-defined Networking planes and layers | 17 |

| 2.8 | OpenFlow-enabled SDN devices                  | 18 |

| 2.9 | NFV, Cloud Computing and SDN                  | 21 |

| 3.1 | HWA attachement options                       | 26 |

| 3.2 | HWA deployment topologies                     | 28 |

| 5.1 | Main components, hardware and test cases      | 42 |

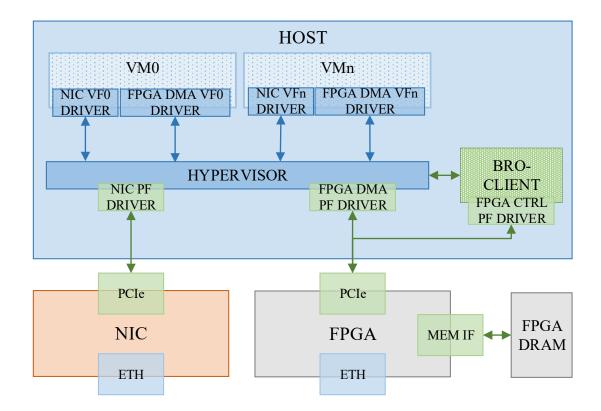

| 6.1 | Server architecture                           | 45 |

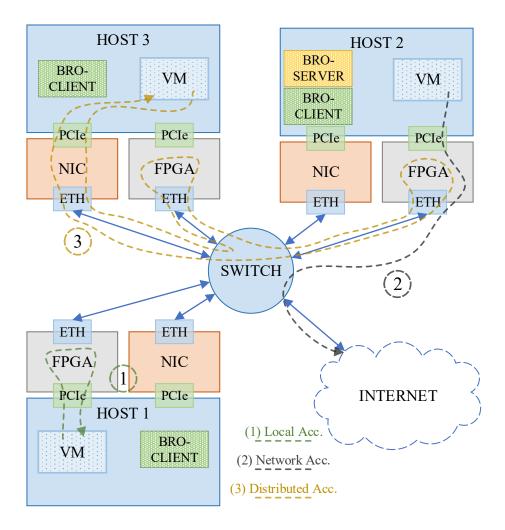

| 6.2 | Datacenter architecture                       | 46 |

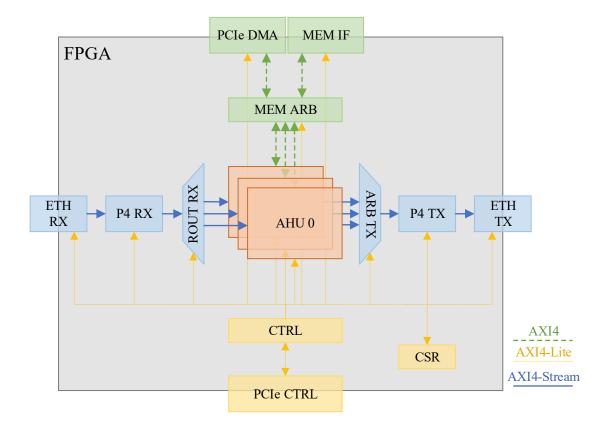

| 6.3 | FPGA architecture                             | 47 |

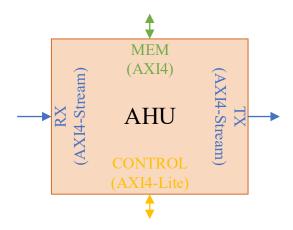

| 6.4 | AHU's interfaces                              | 51 |

| 6.5 | BRO-SERVER architecture                       | 53 |

| 6.6 | BRO-CLIENT architecture                       | 55 |

| 6.7 | BRO typical usage flow                        | 56 |

| 7.1 | MLP's AHU                                     | 61 |

| VI |

|----|

|    |

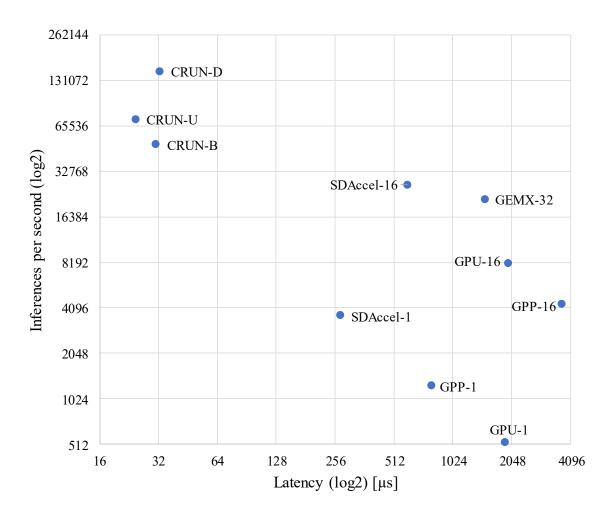

| 7.2 | Trial's inferences | per second v | s latency | results graph |  |  | 62 |

|-----|--------------------|--------------|-----------|---------------|--|--|----|

|-----|--------------------|--------------|-----------|---------------|--|--|----|

# LIST OF TABLES

| 2.1 | Cloud computing and Cloud RAN requirements                      | 7  |

|-----|-----------------------------------------------------------------|----|

| 7.1 | Shell's resource utilization                                    | 59 |

| 7.2 | Shell latencies per packet size at 10Gbps                       | 59 |

| 7.3 | Results for different implementations of the MLP neural network | 61 |

# LIST OF ABBREVIATIONS AND SYMBOLS

AHU Accelerator Hardware Unit

API Application Programming Interface

ASIC Application-Specific Integrated Circuit

AVG Average

BBU Baseband Unit

BS Base Station

CAPEX Capital Expenditure

CLI Command Line Interface

COTS Management and Orchestration

DMA Direct Memory Access

DPDK Data Plane Development Kit

DPI Deep Packet Inspection

EM Element Manager

ETSI European Telecommunications Standards Institute

FPGA Field-programmable gate array

GPP General Purpose Processor

GPU Graphical Processor Unit

HDL Hardware Description Language

HLS High Level Synthesis HWA Hardware Accelerator

IaaS Infrastructure-as-a-Service

ID Identification

IP Internet Protocol

ISG Industry Specification Group

IT Information technology

MANO Management and Orchestration

MAX Maximum MIN Minimum

MLP Multilayer Perceptron

NAT Network Address Translation NFV Network Function Virtualization

NFVI Network Function Virtualization Infrastructure NFVO Network Function Virtualization Orchestrator

NIC Network Interface Controller

NIST National Institute of Standards and Technology

NOS Network Operating System

N-PoP Network Point of Presence

OPEX Operating Expenses

OS Operating System

PaaS Platform-as-a-Service

PCIe Peripheral Component Interconnect Express

PF Physical Function

PNF Physical Network Functions

PR Partial Reconfiguration

PRR Partial Reconfigurable Region

RAN Radio Access Network

RRH Remote Radio Head

SaaS Software-as-a-Service

SDN Software-defined Networking

SFC Service Function Chain

SR-IOV Single Root I/O Virtualization

TCO Total Cost of Ownership

VF Virtual Function

VHDL VHSIC Hardware Description Language

VIM Virtual Infrastructure Manager

VM Virtual Machine

VNF Virtual Network Function

VNFC Virtual Network Function Component VNFM Virtual Network Function Manager

### 1. INTRODUCTION

For a long time, the telecommunications industry has relied on physical proprietary devices for providing services. This practice ossifies the infrastructure not allowing them to easily update or innovate services due to the specialized and manual work needed for it. Meanwhile, it also increases complexity to maintain the facilities [87].

The rapid increase of data traffic is well known worldwide [19] along with the diversity and insertion of new services. All this requires scale as well as constant and fast modifications on the underlying infrastructure, which tied to inflexible environments lead to high costs.

For this reason, telecommunication operators joined efforts and proposed virtualization and COTS (Commercial off-the-shelf) hardware as the key solution for enabling a rapidly evolving infrastructure, culminating on the establishment of the NFV (Network Function Virtualization) [22]. The core principle behind this move is the decoupling of the function from the physical equipment that runs it.

Concurrently, virtualization and COTS are also the key idea behind cloud computing, which has been evolving for some time. The benefits provided by this scheme, namely the possibility of offering infrastructure, platform and software as a service directly translates into efficient use, cost savings and flexibility [67].

Cloud providers are constantly improving their facilities for supporting a wide range of use cases. Consequently, more and more the usage of their services is spread over several segments of industry. The flexibility, scalability and usability constitute key elements for developing and deploying such a diversified scenario.

Just as common cloud applications, NFV covers a wide range of services and applications. This means that the requirements also vary considerably. Many NFV's use cases can be directly deployed in current cloud infrastructure. In fact, most of early trials and proofs of concept of NFV applications have used them.

Yet, more demanding NFV services have requirements that are not met by resources provided in common cloud, namely GPP (General Purpose Processors). Cloud RAN

1. Introduction 2

(Cloud Radio Access Network) is an example of such case, but even more straight forward use cases can face issues when executed in GPPs.

Motivated by the goal of supporting more applications and providing increased performance, which directly translate in added value and income, cloud providers have already started to introduce hardware acceleration in their infrastructure. Main common Hardware Accelerator (HWA) deployed is Graphical Processor Units (GPUs), which covers a range of applications but is not flexible and efficient enough for many of NFV's use cases. Similarly motivated by the limitations of current cloud systems, telecommunication operators and academia alike also have been researching and testing HWA solutions.

Recent efforts have been done for the deployment of FPGAs (Field-programmable Gate arrays) as HWA in cloud. This type of HWA adapts better for a wider range of workloads scenarios and use cases than GPUs and GPPs. Meaning that better performance and more energy efficiency may be obtained.

Still, FPGAs bring their own challenges for deployment in a virtualized environment, both for the provider and user. From the user perspective the development languages, such as VHDL (VHSIC Hardware Description Language) and Verilog, as well as tools and flows are significantly different from the ones software engineers are used to. Even when using currently available higher-level description languages the developer should have understanding of hardware design.

From the provider perspective, FPGAs insert heterogeneity in an already complex homogeneous system. This leads to difficulties in how to manage the resources and requires considerable changes in the software that orchestrate the infrastructure. Providers must implement a system that allow the FPGAs to be sharable, scalable and secure, while abstracting the hardware details when exposing the resources for development and deployment to the users.

This work presents a framework developed from the scratch for enabling the usage of FPGA as hardware accelerator in a cloud environment, motivated by NFV but not limited to it. The goal is to enable high performance and provide a scalable and flexible system while abstracting the complexity of managing and using it. There are some efforts available in academia with similar motivations as well as proprietary solutions in industry. Still the architectural details presented here are different, specially the usage of SDN (Software-defined Networking) to provide distribution of workloads over several accelerators.

The architecture developed is named CRUN. It provides abstraction of the connec-

1. Introduction 3

tivity and expose standard interfaces for the user. A scalable system is achieved and allows the distribution of processing over several accelerators. The software management system proposed virtualizes the FPGA as a resource in the cloud. Furthermore, a distributed ultra-low latency machine learning inference report of a trial that leverages CRUN is presented. The trial was developed by a third party.

The work also briefly explains the main associated subjects and their relation, such as NFV, SDN and cloud computing. Cloud RAN is presented and used as an example of the motivations behind this thesis. Moreover, hardware acceleration in cloud is briefly reviewed.

The rest of this thesis is structured as follows. Chapter 2 describes the main virtualization related concepts, such as cloud computing, NFV, SDN. Hardware acceleration and FPGAs in cloud are reviewed in Chapter 3. Chapter 4 discusses and review related efforts in the field. Chapter 5 presents the hardware equipment as well as software tools and libraries leveraged. Chapter 6 details the proposed architecture. Chapter 7 shows and discuss the results obtained from the architecture and its performance comparison provided by the trial. Finally, Chapter 8 presents the final considerations and prospects for future work.

# 2. VIRTUALIZATION IN MOBILE NETWORKS

In this chapter important concepts like Network Function Virtualization (NFV), Software-defined Networking (SDN) and cloud computing are presented along with how they relate with each other.

Even though there are several efforts for inserting hardware acceleration in common cloud, one can assume that the need is accentuated in the telecommunication industry due to its demanding requirements. Thus, first Cloud RAN is introduced, which is shown here as an example of the motivations for inserting FPGAs as hardware accelerator in cloud.

Cloud RAN demonstrates well the reasons behind virtualization trends in the telecommunication industry, namely the NFV, as well as the challenges it imposes in cloud computing technologies.

#### 2.1 Cloud RAN

The mobile traffic grow is well known, documented and experienced by the industry and users. Recent reports show an increase in global mobile traffic of 18-fold from 2011 (400 petabytes) to 2016 (7.2 exabytes) and forecast an 7-fold grow by 2021 (49 exabytes) [19]. On the other hand, average revenue per user does not compensate for the increase in Total Cost of Ownership (TCO) that traffic grow imposes in mobile operators [76, 13].

A simplified analysis of TCO can be break down to Capital Expenditure (CAPEX) and Operating Expenses (OPEX). CAPEX is related with costs for building the network infrastructure, while OPEX associates with operation and management of the network.

OPEX expense represents about 60% of TCO and is composed mainly by operation and maintenance, site rent and electricity. CAPEX cost examples are site acquisition, civil works, supplementary equipment as air conditioning and the actual hardware and software responsible for the wireless functionality. The latter is

2.1. Cloud RAN 5

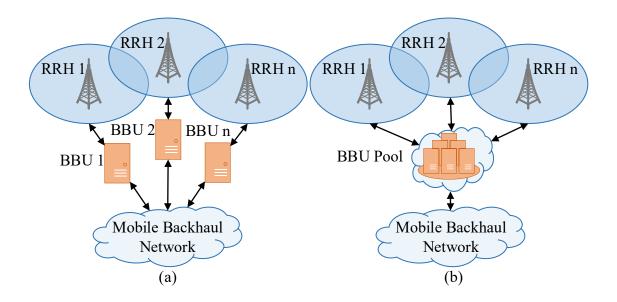

Figure 2.1 RAN (a) vs Cloud RAN (b). Adapted from [13].

what actually brings revenues and represents less than 50% of the CAPEX costs [15].

To support the afore mentioned growth, mobile operators have to improve their Radio Access Network (RAN) capacity, which architecture is traditionally designed to scale mostly with inclusion of more Base Stations (BSs). This solution quickly become prohibitively expensive and operators introduced the novel Cloud RAN [15].

Simply summarizing the RAN evolution, in the first wireless mobile architecture generations (1G and 2G) each network cell was a single Base Station consisting of an antenna located few meters away from a radio module. In the third generation (3G), the RAN is divided into Remote Radio Head (RRH), responsible for the analog to digital and vice-versa conversion, filter implementation and power amplification, and a Baseband Unit (BBU) that is mainly responsible for the signal processing tasks. In this configuration BBU could be located in more convenient and cost-efficient locations than beside RRH [13]. Finally, in the fourth generation (4G) and on the road for the fifth (5G), Cloud RAN is the evolution that leverages both wireless and IT (information technology) technologies by virtualising BBUs and sharing its storage and compute resources [62]. A high-level overview of the difference between traditional RAN architecture and Cloud RAN is shown in Figure 2.1.

The main benefits of Cloud RAN can be categorized as follow [76, 38]:

• Reduced Cost: Concentrating computation and sharing resources in a single

2.1. Cloud RAN

datacenter reduces OPEX by simplifying management, maintenance and operation. Also, the more efficient utilization of the equipment achieved through virtualization reduces CAPEX cost.

- Energy Efficiency: The number of individual BBUs are decreased and enables finer control for setting some BBU to low power and even turning it off. Also, there is no need to dimension several BBUs for the peak traffic of its location, since the dynamic loads of various locations may even out each other, i.e. some business area has high demand of traffic during day time, while house areas are mostly idle and vice-versa during night.

- Spectrum Utilization Efficiency: Centralization facilitates low latency sharing of information among BBUs, like base stations and user equipment link, traffic data and control services, which enables multiplexing more streams on the same channel with less mutual interference and consequently increasing capacity.

- Scalability: It becomes easier to add more resources or upgrade them to increase compute and storage capacity in the BBU. Also, RRH can be scaled to increase coverage and capacity faster and at lower cost since installation mainly requires the antenna and feeder systems.

Even tough Cloud RAN is a prime technology for enabling 5G mobile network [46], it does impose some challenges, such as [13]:

- High bandwidth, strict latency and jitter: the fronthaul transport network (between BBU and RRH) requirements may be 50 times larger than the backhaul (among BBUs and Mobile Backhaul Network)

- BBU Cooperation, Interconnection and Clustering: Sharing user data, scheduling and channel handling for interference control require BBU coordination, which in turn requires reliability and security mechanisms.

The challenges may be better understood from Table 2.1, which compares Cloud RAN requirements with common applications in cloud computing. One realizes that current cloud computing technology does not offer a ready made solution for telecommunication operators. Cloud RAN is an example of virtualization trends that motivated the foundation of the Network Function Virtualization standard.

In fact, Cloud RAN is one of the use cases covered by NFV [25, 87]. Hence, it is a narrower example of NFV's requirements since it varies for other use cases and can be even more demanding.

|                         | Cloud Computing         | Cloud RAN           |

|-------------------------|-------------------------|---------------------|

| Data rate               | Mbps range              | Gbps range          |

| Data profile            | Bursts and low activity | Constant stream     |

| Latency                 | Tens of ms              | Hundreds of $\mu$ s |

| $\operatorname{Jitter}$ | Tens of ms              | ns range            |

| Information Life time   | Long (content data)     | Extremely short     |

| Recovery time           | s range                 | ms range            |

| Number of clients       | Thousands to millions   | Tens to hundreds    |

Table 2.1 Cloud computing and Cloud RAN requirements. Adapted from [13].

#### 2.2 Network Function Virtualisation

The challenges of virtualization are not limited to mobile operators only but the whole telecommunication industry. To address it, seven world's leading telecommunication operators and the European Telecommunications Standards Institute (ETSI) founded in 2012 the Industry Specification Group (ISG) for Network Functions Virtualization (NFV) [22].

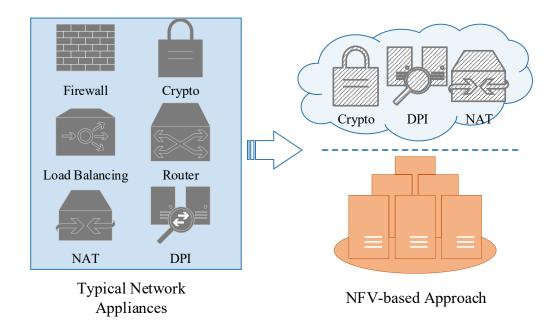

Broadening the scope from Cloud RAN and mobile operators to the telecommunication industry in general, networks traditionally contain several dedicated proprietary hardware to execute network functions, also referred as middle-boxes or Physical Network Functions (PNFs). Example of such middle-boxes are Network Address Translation (NAT), Firewall and Deep Packet Inspection (DPI).

The constant increase in diversity of services and demanding requirements is proportional to the number of PNFs in the network infrastructure. At the same rate, the complexity of deploying them rises due to the specialized and manual work needed for it. Also, incompatibility among middle-boxes is frequent as well as diagnosis of failures or misconfiguration is difficult. Furthermore, the fact that they are fixed in some physical and logical location and the inability to easily move or share them make the network inflexible and ossified. This issues directly translate in slow and costly process for a network provider to install, maintain or update any service [87].

NFV aims to change this scenario by standardizing how to leverage virtualization and change the way telecommunication operators infrastructure their network. Instead of deploying middle-boxes, they are implemented in Commercial-Off-The-Shelf (COTS) equipment in the form of Virtual Network Functions (VNFs) as shown in Figure 2.2 [30]. This effectively decouples hardware from software and brings flexibility for faster update and deployment of new services in the same hardware and enable dynamic scaling [51]. NFV target benefits such as improvement in energy efficiency, decreasing the equipment cost, faster update and deployment of new ser-

Figure 2.2 Traditional network functions in middle boxes are deployed as VNFs in COTS hardware. Adapted from [30].

vices, and provide a scalable and elastic ecosystem [87, 51].

Simply speaking, NFV is the cloudification of network functions. Throughout this work, traditional cloud computing is called common cloud, while NFV cloud refers to a cloud infrastructure used for deploying VNFs.

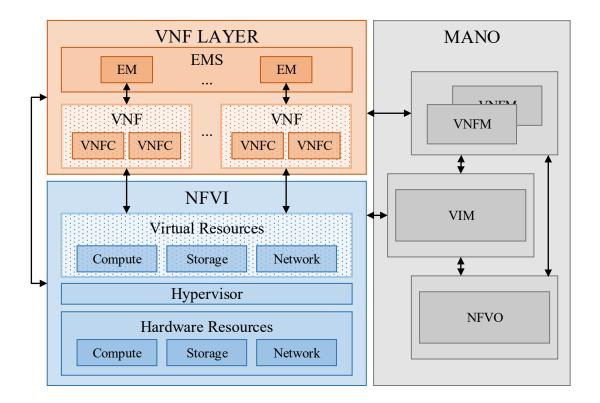

ETSI divides NFV architecture in three main layers: VNF Layer, Network Function Virtualization Infrastructure (NFVI) and Management and Orchestration (MANO) [23]. Figure 2.3 depicts this architecture.

# 2.2.1 VNF Layer

VNF is the virtual version of a PNF using virtual resources like Virtual Machines (VMs) in the NFV Infrastructure, providing the same functionalities of their physical counter-part. VNFs may be composed of one or several VNF components (VNFC). For example, one VNF can span several Virtual Machines, where each is one component, across multiple physical servers. The life cycle control of those components, such as instantiation and configuration, is the responsibility of Element Manager (EM). In the same context, one or more VNFs can be grouped to form a service [51].

Figure 2.3 NFV Architecture. Adapted from [87].

#### 2.2.2 NFVI

NFVI combines both hardware and software where the VNFs are deployed. In this layer hardware is decoupled from software [51].

The physical resources provide compute, storage and network functionalities from COTS equipment. Example of compute resources are x86 servers or hardware accelerators that can be applied for performance improvement. For storage, Direct Attached or Network Attached Storage servers can be used and for network standard switches are applied [87].

Those resources are then abstracted by a virtualization layer. Usually, virtual compute resources are exposed to the VNF layer as Virtual Machines using an hypervisor such Linux KVM [42], but container technology can also be used.

Virtual networking resources interconnect the virtual compute and storage nodes following the physical networking principles, but it must be aware that nodes may be located in the same host or not [31].

Following the same principle, virtual storage resources expose scalable and flexible pools of storage and also bring features such as backup and snapshots [87].

Software acceleration may be implemented in the virtual layer similarly to hardware accelerators in the physical layer, some common examples are Data Plane Development Kit (DPDK) and Single Root I/O Virtualization (SR-IOV) [40].

NFVI is not a complete solution for NFV and different service providers can and are building their own NFVI depending on their requirements [87].

#### 2.2.3 MANO

MANO is responsible of managing and orchestrate hardware and software resources and their life cycle in the NFVI layer. It also manages VNF instances, their placement and their life cycle. Furthermore, it includes database to store information of the VNFs and NFVI [51].

Due to such complex and wide scope MANO is further divided into three sub elements: NFV Orchestrator (NFVO), VNF Manager (VNFM) and Virtual Infrastructure Manager (VIM) as shown in Figure 2.3 [87].

NFVO chains and orchestrate multiple VNFs to provide services, it includes the responsibility of finding the optimal path and placement of the VNFs accordingly to the requirements. VNFM manages multiple instances of any type of VNF, including life cycle from instantiation to termination. Finally, VIM control and manages NFVI compute, storage and network resources [87].

ETSI presents a reference architecture for the MANO and it is known that NFVO, NFVM and VIM borders are blurry. Thus, many implementations of MANO may not be directly mapped to them [87]. Furthermore, the support for heterogeneity, i.e. hardware accelerators, is an open question still [51].

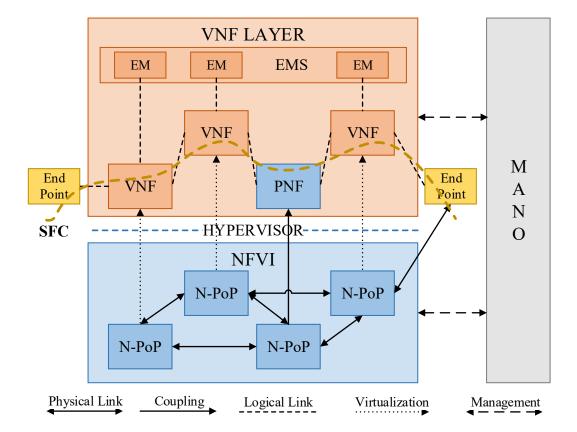

To summarize the NFV architecture, a visualization of the main terminology and how they are related can be seen in Figure 2.4. Virtualized network functions are referred in the standard as (VNF) and the Element Manager (EM) is responsible for controlling its life cycle. A NFV Infrastructure (NFVI) provides the necessary resources where VNFs are deployed. This deployment can be constituted of one or multiple VNFs connected to form a Service Function Chain (SFC). Due to strict requirements and high coupling of VNFs in a SFC, the location of those in the NFVI is important and are referred as Network Point of Presence (N-PoP). The control of resources and connection among VNFs in the NFVI is performed by the Management and Orchestration (MANO) element, which is further divided by the standard in Virtualized Infrastructure Manager (VIM), VNF Manager (VNFM) and NFV Orchestrator (NFVO) [87].

Figure 2.4 NFV's main terminology and their relations. Adapted from [87].

Note that a VNF can coexist with a PNF when forming a SFC, it is expected and especially important in the early implementation phase of NFV.

# 2.3 Cloud Computing

Cloud computing is a key technology in NFV. As many concepts on computer science, the idea behind cloud computing is not as new as it may seem. As early as 1961, Professor John McCarthy suggested the concept of utility computing, in which he envisioned computing as a public utility, just as the electricity and telephone system [1]. This early concept proposed that not only computing power, but specific applications would be sold in a utility-type business model in the future [66]. This idea was revitalized in the past two decades and resurfaced as cloud computing [1, 66].

There are many definitions for cloud computing, industry and academia alike have composed several meanings. According to the National Institute of Standards and Technology (NIST) cloud computing is "a model for enabling ubiquitous, convenient, on-demand network access to a shared pool of configurable computing resources (e.g.,

networks, servers, storage, applications, and services) that can be rapidly provisioned and released with minimal management effort or service provider interaction." [48, p. 2].

From the NIST definition one can point out five essential characteristics of cloud computing [67]:

- Scalability: Resources must scale up and down fast and as needed;

- Measurable services: Services must be controlled and monitored by cloud provider for billing, access control, resource optimization and other purposes;

- Automation: Tenants can use services on-demand without human interaction;

- Ubiquitous: Cloud is available over the network and can be easily accessed;

- Shared: Physical and virtual resources are assigned and reassigned on consumer demand who usually has no control of its exact location.

Computing is treated as utility in cloud. Thus, the user, also called tenant, pay for its usage as one pay for water and electricity, lowering costs since resources are essentially rented on demand [67]. This means a business paradigm shift in which third parties are contracted for delivering commodities of computing power, data storage and services to enterprises and customers [1].

Virtualization and cloud orchestration are key technologies enabling this paradigm shift and may be considered as one of the foundations of cloud computing [77, 6]. Furthermore, there are two important concepts within this context, the deployment mode and the service model of cloud computing. The next subsections briefly explain these terms.

#### 2.3.1 Virtualisation and Orchestration

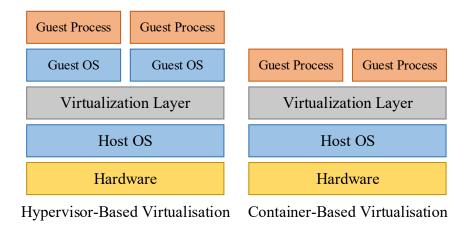

Virtualization is a technology used for running multiple independent virtual operating systems on a single computer [1], as such, the underlying physical resources are abstracted away by logical ones. The objectives of this abstraction are agility, flexibility and energy-efficient resource utilization [67], bringing further benefits such as hardware independence, availability, isolation and security [77]. There are two main techniques to achieve virtualization: hypervisor-based and container-based. Figure 2.5 compares them.

Figure 2.5 Virtual Machines vs Containers. Adapted from [77].

Most common form of virtualization is hypervisor-based, which inserts a software layer to provide abstraction of multiple virtual resources on top of a physical one (host). These virtual resources are called Virtual Machines (VMs). The hypervisor runs on host Operating System (OS) and provides an isolated execution environment to each VM allowing them to have their own OS, usually called guest OS. In practice it means that one host OS can execute multiple different guest OSs. Some well known hypervisors are Xen, VMware and KVM [77].

VMs impose overhead and degrade performance. A lightweight alternative is container-based virtualization. Containers are multiple isolated user-space instances that run directly in the physical machine at the OS level [77]. Containers do not provide the same level of isolation as VMs and may introduce security issues but have less footprint [87]. Docker [21] is probably the most well-known container platform.

To realize the full potential of a cloud, resource management is needed. Cloud orchestration controls and arranges the underlying hardware and hypervisors to provide users the required resources as efficient as possible. In practice the orchestrator controls the sharing of resources among several users. This is a complex task due to the need for scalability, heterogeneous resources and several constrain from the limited capacity [6]. OpenStack [58] is a widely used cloud orchestrator.

There are three main requirements for the cloud orchestrator [6]:

• Visibility: The system has to monitor all cloud resources and expose to user their availability, status, placement, cost and any other information required;

- Orchestration: The allocation must guarantee that user is provided with the agreed resource, such as bandwidth and latency, while coordination must ensure correct configuration and execution of the resources;

- Provisioning: Users and provider must coordinate sharing of statistics and resource utilization to optimize the system, using techniques such as autoscaling and failure recovery.

With proper orchestration and virtualization, a datacenter with its limited number of physical servers can be shared among several users, since one single host can execute many guests simultaneously [67].

# 2.3.2 Deployment Modes of Cloud Computing

There are four deployment modes as defined by NIST [48], categorized as below. This classification refers to the ownership of the cloud datacenter [61].

- Public Cloud: this category describes the environment own by a third party provider that exposes their services via the Internet [67, 61]. Resources are dynamically provisioned on a self-service basis in which the availability is done in a pay-as-you-go manner to the general public [61]. Famous examples are Microsoft's Azure [50], and Amazon AWS EC2 [4, 1].

- Private Cloud: the management of data and process is handled within the organization. In this sense, there are no restrictions as in public cloud services related to network bandwidth, security exposures and legal requirements. Some examples cited here are Amazon VPC and OpenStack [1].

- Community Cloud: is constituted by a group of organizations sharing the same interests, being specific security requirements an example. The group members share the access to the data and applications [67].

- Hybrid Cloud: is the combination of the Public and the Private Cloud modes, as such, an organization can run some applications on an internal cloud infrastructure while still running others in a Public Cloud. In this sense, the main advantage for a company is to benefit from scalable resources offered by third party service providers while being on control of specific applications or data [61]. Examples are RightScale and QTS [1].

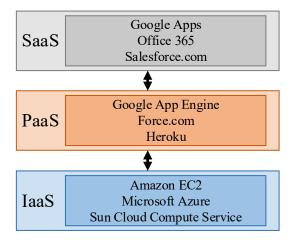

Figure 2.6 Service Models and the three layers. Adapted from [61].

The typical choice of telecommunication operators is the deployment of private clouds. Yet, this work is not limited to it since the main difference among the deployment modes is who owns and manages the cloud and not its infrastructure.

### 2.3.3 Service Models of Cloud Computing

With regard to the type of the service offered, the NIST definition specifies three distinct groups, as showed below [48]. These models are widely known "as a service". Figure 2.6 shows their correlation.

- Software-as-a-Service (SaaS): one or more providers owns the software, its delivery and remote management. They are offered in a pay-per-use manner. It constitutes the most visible service in this context, since the end consumer actually access and uses the software [61]. A single instance of the object code and the correspondent application database must be shared along common resources for supporting multiple customers in a simultaneously manner. Important examples are Salesforce.com and Oracle [1].

- Platform-as-a-Service (PaaS): these offerings are intended to software developers [61]. The key idea here is to provide developers with the systems and environments that they need, from an end-to-end life cycle perspective, comprising developing, testing, deploying, and hosting of applications [1]. In this sense, there is no need to worry about the underlying layer, which is the hardware infrastructure (IaaS), it means an easy to use environment for developing applications and services over the Internet [61]. Key examples are Google App Engine and Microsoft Azure [1].

• Infrastructure-as-a-Service (IaaS): as showed in Figure 2.6 this service model constitutes the lowest abstraction layer. It offers the computing resources directly, as processing power and storage in the format of a service over the Internet [61]. The provided infrastructure can be scaled up or down depending on the needs [67]. Usually IaaS is offered in a virtualized infrastructure, in which they are exposed to the upper layers through standardized interfaces as unified resources, where the user can create its own VMs, for example. As providers one may cite for processing Amazon Web Services with its Elastic Compute Cloud (EC2) and for storage Simple Storage Service (S3) [61].

The scope of this thesis is the IaaS level where the hardware accelerator is exposed to upper levels as a virtualized resource.

### 2.4 Software-defined Networking

In cloud computing, NFV and networks in general, switches and routers are key elements that enable flow of information around the world in the form of digital packets. Although highly pervasive, they are known to be complex and challenge to manage due to the usage of low-level and often vendor-specific languages. These characteristics lead to low flexibility, halt network evolution and increase costs [41].

Any update, new feature or change in the network functionality is complex since they need to be implemented directly into the network infrastructure [56]. A clear example of the problem is the transition from IPv4 to IPv6, which has taken more than a decade and is still ongoing, even though it is a protocol update only [41]. This environment, also so-called Internet "ossification", is attributed mainly to the tight coupling of data and control planes in the network devices [56].

Software-defined Networking (SDN) principle is exactly the separation between control and data planes [56]. SDN is still recent and growing at very fast pace, consequently its definitions may be fuzzy among literature. The objective of this work is not to debate over different views, as such, to avoid ambiguity the four pillars architecture definition provided by Kreutz at el. (2015) is used to identify the requirements of a SDN enabled device [41]:

- The control and data planes are decoupled;

- Forwarding decisions are flow based, instead of destination based;

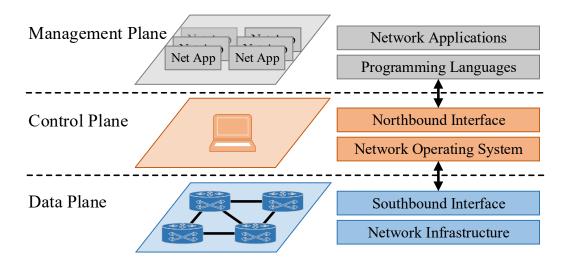

Figure 2.7 Software-defined Networking planes and layers. Adapted from [41]

- Control logic is moved to an external entity, called Network Operating System (NOS);

- The network is programmable through software applications running on top of the NOS.

Summarizing SDN architecture, the data plane is responsible for analyzing each packet and efficiently decide what to do with it, for example forward to some port or drop. The control plane is responsible for translating network policies, i.e. forward rules, so they are recognized by the data plane, which in turn will enforce the policy by processing the packet accordingly. On top of the control plane resides the management plane, which contains network applications that define the desired behavior of the network through some programming language that in turn abstracts away the actual implementation of the policies [41]. Figure 2.7 shows plane and layers views of SDN and next subsections go into more details.

# 2.4.1 Data Plane

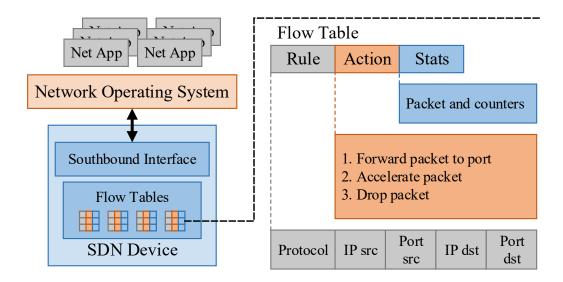

Data plane in SDN is simplified and composed basically from forward devices that leave all the intelligence to the control plane. These devices expose some standard interface called southbound [41]. There are multiple standards that can currently be used to fill the southbound interface layer, like OpenFlow, ForCES and POF [20]. Arguably, OpenFlow is the de-facto SDN standard and mostly widespread

Figure 2.8 OpenFlow-enabled SDN devices. Adapted from [41].

[41, 56]. Thus, it is described here how an OpenFlow-enabled device functions to better explain how the data plane actually works and is separated from the control plane.

Figure 2.8 shows the components of an OpenFlow-enabled device. In these equipment, header fields of incoming packets are matched against headers in the flow tables of the device. Depending on whether a match is found a specific action, i.e. forward or accelerate is taken, if a match is not found the device can be configured to drop the packet or forward it to the controller so the tables can be updated accordingly [20]. The tables can be pipelined and also include statistics field that can be fetched by the controller to visualize the network behavior. This functionality enables a device to be controlled to behave as a router, switch or even more complex roles as traffic shaper, load balancer, and other depending on what kind of actions it can execute on the packets [41].

Furthermore, depending on performance requirements no specialized hardware is needed and the forward device can be fully virtualized in COTS hardware [51].

#### 2.4.2 Control Plane

The SDN controller is frequently regarded as the operating system of the network, thus the name NOS, and in practice it abstracts away the application layer from the low level details of the hardware [20, 41, 56].

As traditional operating systems, NOS should provide essential services and common APIs (Application Programming Interfaces) to developers. Among essential services one can mention device management and discovery, shortest path, topology information, statistics, notification and security mechanisms. There are several controllers and platforms due to the number of competitors fighting to be at the forefront of SDN. Hence, there are no clear standard and they vary greatly in architecture and features [41]. The main aspects that differentiate them are:

- Centralized vs Distributed: Centralized controllers can provide enough performance for a dense data center but may suffer scalability issues and is a single point of failure, while distributed can scale better and be more resilient but are naturally more complex. [41]

- Packet vs Flow: Packet is the basic network unit but a per packet control may imply overhead, on the other hand, applications usually send many packets that can be grouped as a flow. [56]

- Reactive vs Proactive: In reactive control every time an unknown packet/flow arrives, it is forwarded to the controller to decide the action and update flow tables, this increases the delay of the first packet, which may or not be a problem. On the other hand, in proactive control new flows are kept in the data plane and the controller do not need to be consulted, usually.

OpenFlow and other southbound languages standardize the hardware interface, but it not necessarily makes the process of configuring them easy. Hence, they are usually compared to low-level language of x86 platforms such as assembly [20, 41]. More complex operations and orchestration of the network are realized in the management plane through applications [20]. Applications and NOS are connected by the northbound interface. Aligned with the controller diversity, no clear standard can be determined currently [20]. Furthermore, an east-west bound interface may be present, especially in distributed NOS architectures, since NOS interact with each other through it. However, these interfaces are usually private and incompatible among different controllers [20].

# 2.4.3 Management plane

Network applications reside in the management plane. Once more when comparing with x86 platforms, network applications are developed using high-level programming languages and also run on top of NOS. The main purpose of such high-level

languages are to abstract further the task of programming forwarding devices, assist software reusability and speed up development. Several high-level programming languages have been proposed, a comprehensive list and their approach can be found in [41].

As an example, a common network application is load balancing. One can imagine multiple workers executing the same heavy process in packets of a group of flows, the task of this application is to keep the load of the workers balanced so no flow is excessively delayed or dropped due to the limits of a single worker. Furthermore, it can be tuned to reduce power usage in periods of reduced load by directing all flows to a limited number of workers, allowing others to move to a low power state. To achieve this, the application must instruct the controller to install and update the forwarding rules and policies of the devices. [41]

In [41] it is provided detailed network application examples and references to them. Among a wide variety of use cases, SDN applications can usually be categorized as follow [41]:

- Traffic Engineering: Load balancing, energy aware routing, scheduling and Quality of service (QoS);

- Mobility and Wireless: RAN virtualization (Cloud RAN), interference management and programmable virtualised WLANs.

- Measurement and Monitoring: Active and passive measurements and monitoring of QoS parameters;

- Security and Dependability: Attack detection and mitigation, security flow rules privatization and fine-grained access control;

- Datacenter Networking: network utilization optimization, live network migration and workload prediction.

# 2.5 Cloud Computing, NFV and SDN

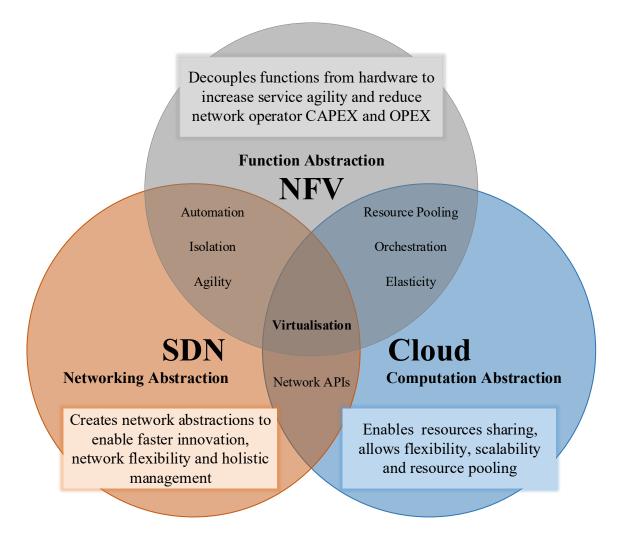

Cloud computing, NFV and SDN are enablers for a revolution in how networks are implemented and monetized, being NFV the one that unify them and which brings higher value for telecommunication operators [30]. In [51], they are classified as an abstraction of different resources, being compute for cloud computing, network for SDN and functions for NFV, as such, they are very related. NFV, for example,

Figure 2.9 NFV, Cloud Computing and SDN. Adapted from [51].

leverage cloud computing technologies to deploy VNFs while SDN may use the same technologies to implement one or multiple SDN controllers on demand [51]. Meanwhile, cloud computing may benefit from SDN applications and VNFs to automate and optimize datacenter's network [41]. Figure 2.9 summarize their relationship.

Additionally, NFV and SDN highly complement each other. For example, a SDN application, such as load balancing and monitoring, may be implemented as a VNF in a service chain. In this way SDN benefits from running in the NFVI while NFV can use SDN's features to automate complex service chains deployment [51]. Still, while very powerful when used together, NFV and SDN can be deployed independently of each other [87].

Moreover, the IaaS service model in cloud computing can be directly mapped to the NFVI layer in NFV's architecture, providing both physical and virtual resources.

Thus, most NFV early trials have been deployed using dedicated VMs in common cloud. Furthermore, VNFs and services can be compared with SaaS [51].

Yet, since NFV applications are mainly originated from telecommunication industry, they impose different requirements than commonly deployed cloud applications, such as high pressure on processing performance, harder network demands and stronger availability and reliability needs, as shown in Cloud RAN in Section 2.1 Consequently, NFV will most probably change considerably when compared with common cloud [51].

Although correlated, NFV and cloud are not the same. NFV focuses on function virtualization and open the scope to provision of services, while cloud focuses on resource virtualization [87]. NFV brings new challenges to the common cloud and intensifies the existing ones, such as:

- VNF performance

- Energy efficiency

- VNF deployment and placement

- VNF life cycle control and migration

- Service chaining

- Performance evaluation

- Policy enforcement

- Security, Reliability and Portability

This work concentrates mainly in the performance issue. More about the other items can be found in [87, 51, 31].

Performance requirements of applications should be guaranteed but it is an challenge even in non-virtualized hardware at high speeds [54]. Moreover, COTS are known to be weaker in terms of performance and reliability when compared to specialized hardware [87]. Packet processing, encryption and decryption are examples where GPPs perform poorly.

To address the question whether virtualized hardware can provide high and predictable performance while assuring portability, ETSI created the "NFV Performance & Portability Best Practises" specification [24]. This specification provides

recommendations of minimum features and requirements the hardware and hypervisor should support and also reports performance test results on NFV use cases. The results show that when using high-end servers and applying the recommendations, performance was consistent, predictable and portable as desired for the cases covered [51], showing that COTS hardware can support many applications requirements.

Yet, even though it is desired to have a virtualized environment composed of COTS hardware only [87], not all VNFs may achieve the performance requirements in this scenario as shown in [28]. Hence, studies show that hardware acceleration techniques will also be important in NFV [51]. Specialized hardware is against NFV's concept, nonetheless, in practice a trade-off among performance, cost and flexibility is needed [87, 51].

# 3. HARDWARE ACCELERATION IN CLOUD

In this chapter the main hardware accelerators used for cloud and how they are deployed are reviewed, along with the connectivity options and what type of workloads they best fit. The final section then go into details of why FPGAs should be leveraged for cloud acceleration, the requirements for doing so and how they are usually deployed.

#### 3.1 Accelerators

Unlike homogeneous systems composed of only General-Purpose Processors (GPP), heterogeneous systems introduce specialized hardware devices, also called Hardware Accelerators (HWAs), that are better suited for certain type of work. The motivation of such systems are performance and energy-efficiency requirements that may not be achieved with GPPs only systems in high demanding applications [29].

Some well-known HWAs currently used are Application-Specific Integrated Circuit (ASIC), Graphic Processing Units (GPUs) and Field-programmable Gate Array (FPGA) [57, 11].

GPUs are deployed mostly as co-processor and are widely used with General Purpose Processor (GPPs) to improve performance. Currently, most big players in cloud computing, such as Azure [5] and AWS [4], already offer scalable GPU-enabled instances in its infrastructure, providing on demand acceleration for application such as machine learning training and inference, streaming, gaming and video encoding.

ASICs are integrated circuits that offer unique features for specific applications, such as PNFs in NFV that are usually composed of such devices. On one hand, ASIC typically provides the highest performance and energy efficiency with smallest chip size. On the other hand, designing such devices that realize these advantages require considerably more development time. Also, each new feature or design error found after taping out of the chip requires a new set of masks for silicon fabrication as well as more time for a new tape out process. The ever increase complexity of designs aggravates it, since huge efforts and time in verification are needed to avoid errors.

3.1. Accelerators 25

This yields a very high cost which is only mitigated in applications that need high volumes of chips [88]. Furthermore, since ASICs have specific purpose, they provide very limited programmability [54].

FPGAs are COTS silicon devices that provide programmable digital circuits. Simply speaking, FPGAs contain several basic elements such as configurable logic blocks, registers and memory that are connected via programmable interconnects. This allows designers to develop custom hardware that takes most advantage of parallelism and data path of an application, in other words, the hardware can be configured at run time to best fit specific applications [43]. As with ASICs, FPGAs offer potential flexibility for many workloads [64], but with no fabrication process, faster development time and the ability to update or fix the design at any time by simply reprogramming the FPGA [26]. On the other hand, FPGAs do not match the performance of ASICs because of their internal structural overhead [39].

#### 3.1.1 Workload Characteristics

As mentioned before, GPPs are capable of providing sufficient performance for many applications but may not be enough in all use cases. These more demanding functions can be broadly classified in two types, Compute-intensive and Network-intensive [7]. They are mainly characterized by the amount of computation needed, latency and how dynamic is the data.

Compute-Intensive functions requires heavy computations and GPP resources in relatively static data. Example of such functions are big data, security, machine learning training and inference, media and games [7]. This type of workload can be further divided into responsive or not. Non-responsive Compute-Intensive workloads process huge chunks of data while latency can be on minutes to day's range. Examples of such applications are machine learning training and scientific calculations. Responsive ones on the other hand require relatively short latency values on moderate amount of data. Example of such application is non-real-time machine learning inference.

Both responsive and non-responsive Compute-Intensive applications can be accelerated using look-a-side model. In this type of acceleration data can be transferred from GPP's memory to accelerator using batches, a group of inputs, where the whole batch is processed and results are send back to GPP's memory. The size of the batches can then be adjusted to match the latency requirements.

Network-Intensive functions on the other hand process highly dynamic amount of

3.1. Accelerators 26

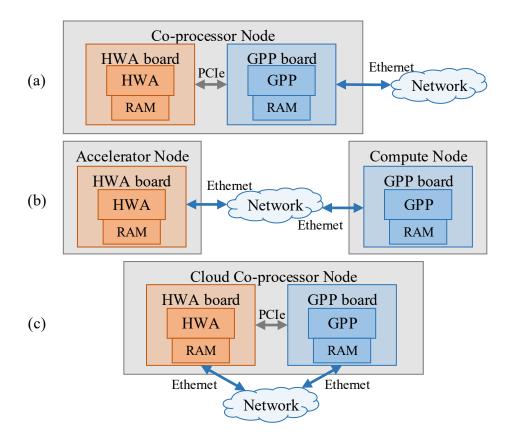

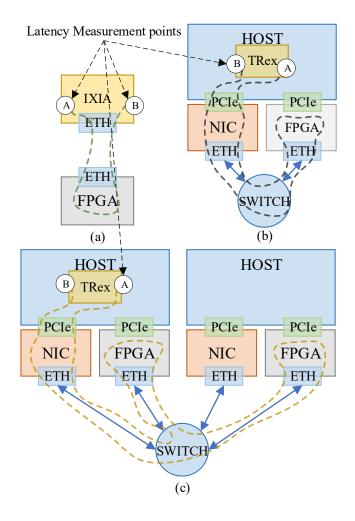

Figure 3.1 Hardware accelerator attachment options: (a) Tightly coupled; (b) Network attached; (c) Tightly coupled and network attached. Adapted from [39].

data with very short latency [7]. This type of function tends to exhaust memory bandwidth of GPPs architectures [55]. This workload is usually processed in a stream manner and examples of applications are NAT, load balancing, streaming video processing and machine learning inference with tight latency requirements.

Network-Intensive workloads are good candidates for in-line acceleration model. This type of acceleration processes the packets while they traverse through the accelerator.

# 3.1.2 Connectivity Options

One can point out three main options in how to connect HWA with GPPs as shown in Figure 3.1: Tightly coupled (a), Network connected (b) and combination of both (c) [39]. Figure 3.1 shows these options using PCIe (Peripheral Component Interconnect Express) and Ethernet as examples of interfaces.

3.1. Accelerators 27

The most prevalent type of accelerators systems are the ones composed of GPPs and co-processors [39], where the GPP offload compute intensive tasks to the co-processor that is tightly coupled to it [29]. Tightly coupled GPPs and HWA are usually connected to each other using some coherent memory mechanism or direct memory access (DMA) [10, 39]. The accelerator chip can be located in a daughter attached card, in the same board as the GPP or even in the same die [33, 73]. For GPUs and FPGAs the most common option is adding a daughtercard using PCIe [39, 73].

Tightly coupling accelerators with GPPs in the same board or die provide better latency values and can potentially easier DMA and coherence [64]. However, this approach suffer from scalability, resilience, size and power issues [73, 64]. They are expected to be used for very specific applications [73]. Using daughtercards and PCIe connectivity partially solves scalability since more chips and/or cards can be added, but if an application needs more devices than the number available it cannot be implemented. Also, if less are needed the system is over-provisioned [64]. In neither case tightly coupled accelerators scale across servers [10].

Network-only connect accelerators are directly hooked to the datacenter's network. Co-processing in this approach may not be efficient due to the higher response time and the need of constant communication with the host [39]. Thus, the accelerator has to work as standalone and capable to communicate with other resources over the network [73]. This approach increases scalability and flexibility compared with tightly attached option, since in this configuration accelerators can be accessed remotely, deployed independently of the number of hosts and allow user defined topologies [74].

Both previous options are good for some workloads but are not generic enough. A third and more flexible alternative is to provide both attachments, tight coupling and network connectivity [39]. This configuration covers more application scenarios, such as, local acceleration over the tight connection, network acceleration over the network connection and global acceleration using pool of remote HWA available from the network [11].

In more details, local HWA occurs when the accelerator works as a co-processor for the GPP and is ideal for Compute-Intensive tasks, as long as the local accelerator has enough capacity to handle it. Network acceleration are good for Network-Intensive workloads like processing incoming or leaving packets of the host. In the case where one accelerator is not enough for large-scale applications, network connectivity provide a pool of accelerators that can be used remotely to distribute the tasks [11].

3.1. Accelerators 28

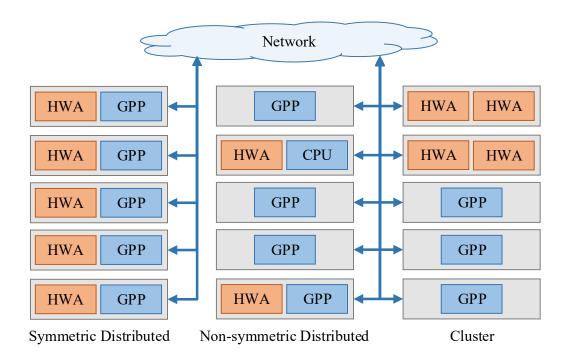

Figure 3.2 HWA deployment topologies alternatives.

### 3.1.3 Deployment Topologies

In [11], it is mentioned that there are basically two ways to introduce HWA in a datacenter: cluster and symmetrically distributed. This work goes further and also presents a third option, a non-symmetric distributed. Figure 3.2 shows these three deployment topologies.

Cluster of HWA break datacenter homogeneity and limits scalability [11]. Nevertheless, it minimizes disruption to the infrastructure and optimize hardware cost.

Non-symmetric distributed topology maintains optimized costs by providing flexible accelerator and server ratio while allowing the provider to introduce HWA continuously, in smaller steps as needed, to an already existing infrastructure. Also, it applies better than the cluster option for some workloads, i.e. local acceleration. However, the homogeneity is also broken, and management become more complex. For example, mapping some application requires details whether HWA is available in a specific node or not.

Symmetric distributed topology on one hand provide efficient scalability, easies the management, maintain the highly desirable homogeneity [11] and is generic enough for a wide range of workloads. On the other hand, in most cases it requires the

highest hardware investment and may result in underutilization.

Furthermore, the topology choice may be influenced by the physical restrictions in the infrastructure, such as, power limits for the accelerators, physical space, resilience and temperatures [11]. For example, a provider who wishes to insert HWA without buying new servers may have problems to go with the distributed options due to restrictions in its current servers.

#### 3.2 FPGAs in Cloud

The diversity of cloud workloads and its fast change rate is a challenge for HWA. It is highly desirable that any hardware inserted to the infrastructure can adapt to this during its lifetime, in other words, HWA needs programmability. This make FPGAs and GPUs preferable over ASICs whenever possible [11].

GPUs and FPGAs are both already deployed in cloud environments at reasonable scale [11]. GPUs architectures are efficient when processing images and video data, but since they are designed for its specific domain, they may not be so efficient or even decrease performance when processing different types of workload, such as signal processing and ciphering [43]. In fact, GPUs are not suited for tasks that do not contain a fair amount of well-structured data-level parallelism [29]. Furthermore, GPUs power and size requirements are bigger than FPGAs [11], which may make GPUs significantly less energy-efficient [37].

Providing FPGAs as resources in cloud infrastructure fills the gap among efficiency provided by ASICs and flexibility of GPPs [43]. As a matter of fact, AWS already provide FPGA as resources [4] while Azure currently offer it in preview mode for external users [50] and have worldwide deployment trials for its own purposes [64, 11]. An overview of developed HWA with FPGAs used for common cloud applications along with their main metrics is presented [35].

Additionally, resilience and reliability at hyper-scale is required when deploying FPGAs in cloud. Currently only Microsoft have such a high-volume system in production. They report only 0.03% of board failure in one month, all of them during the beginning of deployment, which is an acceptable level specially because the scale of datacenters provides sufficient redundancy [11]. The only restriction is that the management system should be able to detect and isolate problematic nodes.

The diverse range of workload types in NFV use cases [25] turn FPGA into even more promising candidate to be used as HWA in NFV systems. Yet, FPGAs do

come with their own differences and challenges when developing applications to run on it. One can classify these challenges in programming languages and design flow.

# 3.2.1 Programming Languages

Traditionally, applications for FPGAs are created using low level Hardware Description Language (HDL), such as VHDL or Verilog, this impose a challenge since it is a barrier for most software developers [69].

FPGA and system vendors have been putting high effort in the last years to reduce such a barrier by using well known high-level languages, such as C++, OpenCL and C, to abstract away hardware details. This abstraction is referred as High Level Synthesis (HLS) [35, 69]. Such abstraction usually results in reduced performance when compared with optimized HDL code, but for a wide range of designs, HLS tools can provide average performance around 90% when compared with optimized HDL [29]. Furthermore, usage of HLS facilitates code reuse and portability, even among different accelerators, i.e. the same OpenCL code can be deployed in FPGAs and GPUs [34].

Still, to obtain good results the developer should have understanding of hardware aspects [53], especially for I/O interfaces such as PCIe, Ethernet and off-chip DRAM [69]. This can be mitigated by frameworks that completely abstract the FPGA board and its I/O from the developer [69]. Some example of such frameworks from major vendors are Xilinx<sup>©</sup> SDAceel<sup>TM</sup> [81] and Intel<sup>®</sup> FPGA SDK For OpenCL<sup>TM</sup> [34].

Frameworks and pure HDL tools allow also another alternative to reduce the burden of developing HDL components. It is the use of Intellectual Property components designed by specialized developers, being third party entities or not. Making Intellectual Property components easily available and facilitating its integration by developers with no prior experience with HDL allow applications to leverage the better performance obtained by optimized HDL code seamlessly [35]. This approach works similarly as with software libraries, and as such, require usage of standard interfaces and is usually provided for tasks that are frequently required.

# 3.2.2 Design Flow

FPGAs also require a completely different design flow and set of tools than the ones software engineers are used to for compiling the applications. Instead of a set of instructions, the end result of a FPGA "compiler" is a binary file that mainly

describe the internal connectivity of the basic elements inside the device. This binary file, also called bitstream, is then loaded into the FPGA to implement the desired circuit and functionality [26].

The flow to obtain such bitstream is composed of a chain of automated tools that know the details of the available elements and their possible connections in the device target and translate the HDL descriptor accordingly [39].

One can simply describe the flow chain as follows: First, if the design is developed using HLS languages, it is translated to HDL. A synthesis step then take place where the HDL functionality is mapped to the basic elements available in the device. Then in the placement phase, the tool chooses among the elements which one to be used based on its location in the silicon floor. Later, in the routing phase the tool explores the best possible routes to connect the mapped elements. Finally, a time analysis take place, this phase checks each existing path among the elements and verify if they meet time requirements, in other words, it check if the desired clock frequency can be used, ensuring that the hardware functions as expected.

In practice, each step search among a wide range of possibilities and choose optimal configurations with the goal of reaching requested time constrains, while keeping the number of elements (area) and power consumption as low as possible. Due to the wide range of possibilities, designers can constrain the tools to look for solution that optimize time, performance or energy consumption. The whole flow is a heavy and complex process, as such, compiling a design can take from minutes to several hours for each of the steps depending on the complexity [39].

### 3.3 FPGA Virtualization

Besides challenges from the developer point of view, providing FPGAs as HWA resources in cloud is no simple task for the infrastructure provider either. There are at least four essential requirements that need to be addressed [14]:

- 1. Sharable: As with all resources in cloud, FPGAs should be sharable among multiple tenants and applications in order to maximize resource utilization.

- 2. Abstracted: FPGAs must be exposed to tenants as a pool of resources that can easily be requested, allocated and deallocated. Programmability of the FGPAs must be exposed to tenants, similar as with GPPs and GPUs, in other words, FPGAs should not be considered as an ASIC, but a programmable one.

- 3. Secure: FPGAs should provide proper isolation when multiple tenants and applications are sharing the same resource and one cannot impact the other on purpose or not.

- 4. Scalable: To not limit applications to resources of a single FPGA at most, tenants should be able to easily scale applications among multiple FPGAs and create their own topology.

Furthermore, to increase productivity, it is highly desirable to expose APIs for controlling the FPGA as well as interfacing application logic and board-level functions while supporting resilience and debugging [64].

In the following it is discussed how those essential requirements are or can be provided.

# 3.3.1 Sharing

The fact that GPPs applications are a set of instructions allow the same core to execute several applications from multiple users, in practice, the virtualization takes place by sharing the same resource by time slicing and scheduling the instructions from each application accordingly. Even though the synthesis time required by FPGA's design can be mitigated by creating the bitstream beforehand, the process to program an FPGA is still too slow to allow multiple applications and users to share the same area of the device in a time slice manner, limiting its scalability [64].

To allow more applications and users one could simply deploy multiple FPGAs for that, but it easily become costly, consuming more power and wasting resources when not needed. Partial Reconfiguration (PR) is a key enabler for sharing FPGAs and can be used to allow multiple applications to run on the same FPGA by dividing the device's area, instead of time slicing [64].

PR is a technique where only part of the FPGA is reconfigured during run-time instead of the whole device. Beforehand a specific area is reserved to be static, this region is never reconfigured during run-time and usually contain all the management circuitry and communication interfaces, such as PCIe and Ethernet. The remaining area of the device can be divided into multiple Partial Reconfigurable Regions (PRR) that can be reconfigured during run-time without interfering in others PRR [26].

## 3.3.2 Abstracting

Infrastructure level of abstraction for FPGAs can be achieved by exposing them as a resource in a cloud management system such as OpenStack [58]. Following the cloud nomenclature, in its core this functionality is provided by a hypervisor that allows users to implement and execute their guest Operating System. In the FPGA context, the hypervisor is a set of hardware (shell) and software (manager) components that allows user to program and run their own hardware design [39, 8].

In the hardware side, abstraction is achieved by utilizing a static area that is programmed during start-up and not accessible by the user, the shell. The shell abstracts away all the board connectivity, such as PCIe and Ethernet, while providing common standard interfaces, such as AMBA [3, 2], to the user's hardware, in this work called Accelerator Hardware Unit (AHU). This release the heavy burden of system integration from the user and makes the design reusable among different devices and boards as long as the shell remains compatible, speeding up development and increasing portability [64]. Furthermore, the shell communicates with the manager, providing status and debugging information while receiving global or user-specific configurations commands.

Multiple flavors of HWA can be exposed to users via the manager. It could be for example the whole FPGA or part of it, in both cases PR can be leverage to provide abstraction [39], allowing fine grain selection of resources. Once a resource is selected, the desired acceleration functionality is programed into the FPGA with a compatible bitstream image previously uploaded to the manager, i.e. using *glance* service in OpenStack [8].

# 3.3.3 Securing

From the security point of view, the infrastructure must guarantee that users cannot propositionally crash other's applications or the system. Also, it must provide complete data isolation [14].

The former requirement can be provided by a robust hypervisor that ensure security access in the manager level [39] and that utilize PR. With Partial Reconfiguration users can only affect their own region in the FPGA and the shell must be designed so that it is able to detect faulty AHU and prevent it to affect others [14].

Data isolation for tightly coupled connections can be solved using DMA. The hypervisor supervises all DMA operations and allow only legal and correct ones, thus

users can only access the memory regions they are allowed to [14]. For network connected devices, common network security approaches can be used while the hypervisor must ensure that the users can only receive and generate packets from and with addresses which they are allowed.

### 3.3.4 Scaling

FPGA attached through tightly coupled connections have scalability limited to a single server [10]. Hence, to enable truly scalable FPGAs and allow global acceleration [11], at least network connectivity is needed. The hypervisor should allow the user to request as many FPGAs as the design requires, which could be from couple to thousands of devices [10].

Furthermore, it is needed to allow the user to easily create its own topologies for network connection when requesting multiple FPGAs. Integrating SDN capabilities into the manager and shell allow the user to create extremely flexible and scalable architectures that enable powerful solutions.

Besides the four essential requirements above, another is compatibility. It addresses the issue that design flows, tools and libraries for developing FPGAs applications are still very dependent on the vendors and devices. A framework that provide common ecosystem and seamlessly migration among devices versions and vendors available should be exposed. Contrary to [14], here scalability requirement was promoted as essential in place of compatibility. This is done so because this work concentrates on the IaaS layer of the cloud environment. One could argue, but here it is assumed that compatibility could be better addressed in a higher level of abstraction, similar with the PaaS in common cloud, while the four essential requirements must be addressed already in the infrastructure layer.

### 4. RELATED WORK

In this chapter closely related works are reviewed, this means that the list is reduced to efforts that focus on FPGAs and in at least one of the subjects: HWA virtualization or abstraction; Scaling HWA; HWA for NFV or SDN;

They are divided in four sections: Hardware acceleration only contains efforts that do not provide scalability; Partially scalable hardware acceleration reviews works that have some level of scalability; Fully scalable hardware acceleration provides review of efforts that allow deployment of scalable hardware acceleration in the range of thousands or more; Finally, Hardware acceleration in NFV provides review of related works that focus on it.

# 4.1 Hardware Acceleration Only

Even though this work focusses on enabling FPGA in a cloud environment for distributed acceleration of NFV systems, FPGAs are currently mainly used for acceleration of specific applications. It is worth to mention some available solutions that focus on this area.

IBM's Coherent Accelerator Processor Interface (CAPI) [75] enables acceleration of Compute-Intensive applications on POWER8 processors by simplifying the complexity of programming the I/O system. The system connects GPP and FPGA through PCIe and provide coherent memory between them, allowing the application to share its memory space with the hardware accelerator and transfer data through simple memory access commands.