# ALEKSI TERVO OPTIMIZING TRANSPORT-TRIGGERED ARCHITECTURES FOR FIELD-PROGRAMMABLE GATE ARRAYS

Master's thesis

Examiner: D.Sc. Pekka Jääskeläinen

The examiner and topic of the thesis were approved on 15 August 2018

#### **ABSTRACT**

**ALEKSI TERVO**: Optimizing Transport-Triggered Architectures for Field-Programmable

Gate Arrays

Tampere University of Technology Master of Science Thesis, 53 pages

Major: Embedded Systems

Examiner: D.Sc. Pekka Jääskeläinen

Keywords: transport triggered architectures, field programmable gate arrays,

parallelism

With the growing importance of energy efficiency, heterogeneous computing has become more popular in recent years. Field-programmable gate array (FPGA) devices are no exception: offering highly parallel execution at low power, they are an option worth considering for many tasks, and increasingly more available for users through cloud computing services.

While FPGA devices offer a lower barrier to entry to logic design than integrated circuit design, they are still difficult to design for compared with instruction set processors. While tools exist for translating a high-level language description of an algorithm into an FPGA design, they still require expertise most software designers do not have.

One way around this problem is building soft processors onto the programmable logic as a programmability layer for sofware designers. Transport-triggered architectures (TTAs) are a promising avenue of research in this area for their simple implementation and inherently parallel programming model.

This thesis presents FPGA-centric optimizations for transport-triggered architectures and evaluation of these optimizations through synthesis. Together, these optimizations yielded between 20 and 30 percent reduction in logic utilization in the tested architectures while having little effect on the clock frequency. Additionally, the scalability of TTAs for more parallel workloads is evaluated with various configurations of a TTA vector processor as well as a convolutional neural network processor case study.

## TIIVISTELMÄ

**ALEKSI TERVO**: Siirtoliipaistujen prosessorien optimointi ohjelmoitavalle logiikalle

Tampereen teknillinen yliopisto

Diplomityö, 53 sivua

Sähkötekniikan diplomi-insinöörin tutkinto-ohjelma

Pääaine: Sulautetut järjestelmät Tarkastaja: TkT Pekka Jääskeläinen

Avainsanat: siirtoliipaistut prosessoriarkkitehtuurit, ohjelmoitava logiikka, rinnakkai-

suus

Energiatehokkuuden tärkeyden kasvaessa heterogeeniset laskenta-alustat ovat kasvattaneet suosiotaan. Ohjelmoitavat logiikkapiirit eivät ole tästä poikkeus: erittäin rinnakkainen suoritus matalalla energiakulutuksella tekee ohjelmoitavista logiikkapiireistä varteenotettavan vaihtoehdon moniin käyttötarkoituksiin, ja käyttäjille koko ajan helpommin saatavissa pilvipalveluiden kautta.

Vaikka näille laitteille suunnittelu on helpompaa kuin perinteisille sulautetuille logiikkapiireille, suunnitteluprosessi vaatii erikoistietämystä verratuuna käskykantasuorittimien ohjelmointiin. Työkalut, joilla voidaan kääntää korkean tason ohjelmointikielellä kuvattu algoritmi ohjelmoitavalle logiikkapiirille, käyttävät samoja kieliä kuin käskykantasuorittimille ohjelmointi, mutta nämäkin vaativat suunnittelijalta syvällistä ymmärrystä siitä, miten algoritmi kuvautuu logiikkapiiritoteutukseksi.

Yksi tapa kiertää tämä ongelma on rakentaa ohjelmoitavalle logiikalle käskykantasuoritin, jota ohjelmoijat voivat käyttää toteuttaakseen halutun algoritmin. Siirtoliipaisut suoritinarkkitehtuurit ovat lupaava tutkimussuunta tällä alalla niiden yksinkertaisen toteutuksen ja rinnakkaisen ohjelmointimallin takia.

Tässä diplomityössä esitellään siirtoliipaistujen suorittimien toteutusta ohjelmoitaville logiikkapiireille parantavia muutoksia, sekä näiden muutosten arviointeja synteesitulosten kautta. Näiden muutosten yhteisvaikutus näkyy pääasiallisesti prosessorien koossa: eri arkkitehtuurien koko pieneni 20-30 prosenttia, ilman suurta muutosta kellotaajuudessa. Tämän lisäksi siirtoliipaistujen suorittimien skaalautuvuutta rinnakkaisille algoritmeille tutkitaan siirtoliipaistujen vektorisuorittimien sekä syväooppimiseen suunnitellun suorittimen näkökulmasta.

#### **PREFACE**

The work for this thesis was done at the laboratory of Pervasive Computing at Tampere University of Technology with funding from the HSA Foundation, as well as the ALMARVI and FitOptiVis projects.

I would like to thank Dr. Pekka Jääskeläinen for giving me a chance to work on interesting projects and the valuable learning opportunities that have come with that work, as well as his guidance and support regarding this thesis. I would also like to thank my coworkers, present and former, for a positive work environment and a helpful attitude. Finally, I would like to thank my friends and family for supporting me throughout my life and studies and during the writing of this thesis.

In Tampere, Finland, on 15 November 2018

Aleksi Tervo

# **CONTENTS**

| INTR | CODUCTION                                                                                                                                                           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PRO  | CESSOR ARCHITECTURES                                                                                                                                                | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 2.1  | Instruction Scheduling                                                                                                                                              | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 2.2  | Parallel Organizations                                                                                                                                              | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 2.3  |                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 2.4  | Application-Specific Tailoring                                                                                                                                      | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| TRA  | NSPORT-TRIGGERED ARCHITECTURES                                                                                                                                      | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 3.1  | From VLIW to TTA                                                                                                                                                    | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 3.2  | From Scalar OTA to TTA                                                                                                                                              | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 3.3  | TTA-Based Co-Design Environment                                                                                                                                     | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|      | 3.3.1 TTA Template                                                                                                                                                  | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|      | 3.3.2 Hardware Generation                                                                                                                                           | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| FIEL | D PROGRAMMABLE GATE ARRAYS                                                                                                                                          | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 4.1  | Architecture                                                                                                                                                        | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|      | 4.1.1 Logic and Arithmetic                                                                                                                                          | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|      | 4.1.2 Routing Resources                                                                                                                                             | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|      | 4.1.3 Storage Elements                                                                                                                                              | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|      | 4.1.4 Reset                                                                                                                                                         | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 4.2  | Designing for FPGAs                                                                                                                                                 | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 4.3  | Comparison to ASIC                                                                                                                                                  | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| IMPL | LEMENTED OPTIMIZATIONS                                                                                                                                              | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 5.1  | Instruction Fetch and Decode                                                                                                                                        | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 5.2  | Interconnection Network                                                                                                                                             | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 5.3  | Memory Organization                                                                                                                                                 | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 5.4  | Arithmetic Logic Units                                                                                                                                              | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| EVAI | LUATION                                                                                                                                                             | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 6.1  | Multiplexers on FPGA                                                                                                                                                | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 6.2  | TTA Suboptimizations                                                                                                                                                | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|      | 6.2.1 Reset Regime                                                                                                                                                  | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|      | 6.2.2 Interconnection Network                                                                                                                                       | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 6.3  | Total Effect of Optimizations                                                                                                                                       | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 6.4  | Parallel Execution on TTAs                                                                                                                                          | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 6.5  | Convolutional Neural Network Case Study                                                                                                                             | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| RELA | ATED WORK                                                                                                                                                           | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| FUTU | URE WORK                                                                                                                                                            | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| CON  | CLUSIONS                                                                                                                                                            | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|      |                                                                                                                                                                     | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|      | PROC<br>2.1<br>2.2<br>2.3<br>2.4<br>TRAI<br>3.1<br>3.2<br>3.3<br>FIEL<br>4.1<br>4.2<br>4.3<br>IMPL<br>5.1<br>5.2<br>5.3<br>5.4<br>EVAI<br>6.1<br>6.2<br>FUTU<br>CON | 2.2       Parallel Organizations         2.3       Memory Organization         2.4       Application-Specific Tailoring         TRANSPORT-TRIGGERED ARCHITECTURES         3.1       From VLIW to TTA         3.2       From Scalar OTA to TTA         3.3       TTA-Based Co-Design Environment         3.3.1       TTA Template         3.3.2       Hardware Generation         FIELD PROGRAMMABLE GATE ARRAYS         4.1       Architecture         4.1.1       Logic and Arithmetic         4.1.2       Routing Resources         4.1.3       Storage Elements         4.1.4       Reset         4.2       Designing for FPGAs         4.3       Comparison to ASIC         IMPLEMENTED OPTIMIZATIONS         5.1       Instruction Fetch and Decode         5.2       Interconnection Network         5.3       Memory Organization         5.4       Arithmetic Logic Units         EVALUATION       6.1         6.2       TTA Suboptimizations         6.2.1       Reset Regime         6.2.2       Interconnection Network         6.3       Total Effect of Optimizations         6.4       Parallel Execut |  |  |  |

# **LIST OF FIGURES**

| Figure 3.1. | A simplified VLIW architecture and possible operation encoding          | 10 |

|-------------|-------------------------------------------------------------------------|----|

| Figure 3.2. | Exposed-datapath VLIW                                                   | 11 |

| Figure 3.3. | VLIW-connected TTA and possible instruction encoding                    | 12 |

| Figure 3.4. | An example of a TTA design                                              | 12 |

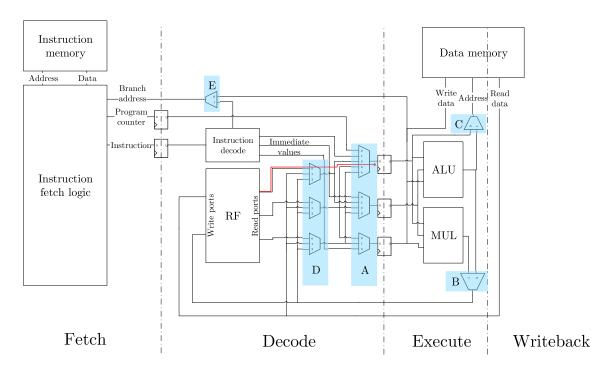

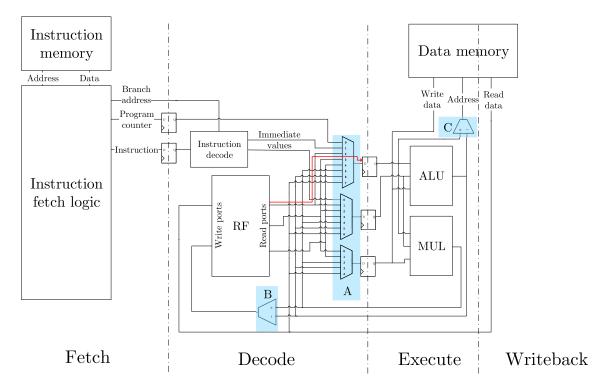

| Figure 3.5. | A scalar OTA design with a four-stage pipeline and data forward-        |    |

|             | ing [73], with the critical path through multiplexers' datapath marked  |    |

|             | with a red arrow. Most control signals have been omitted for clarity    | 13 |

| Figure 3.6. | Modified four-stage scalar OTA pipeline, with the critical path through |    |

|             | multiplexers marked with a red arrow                                    | 14 |

| Figure 3.7. | A TTA architecture with the connectivity of a four-stage scalar OTA     |    |

|             | pipeline with bypassing                                                 |    |

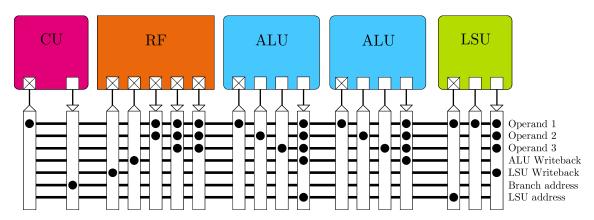

| Figure 3.8. | And-or interconnect network                                             | 17 |

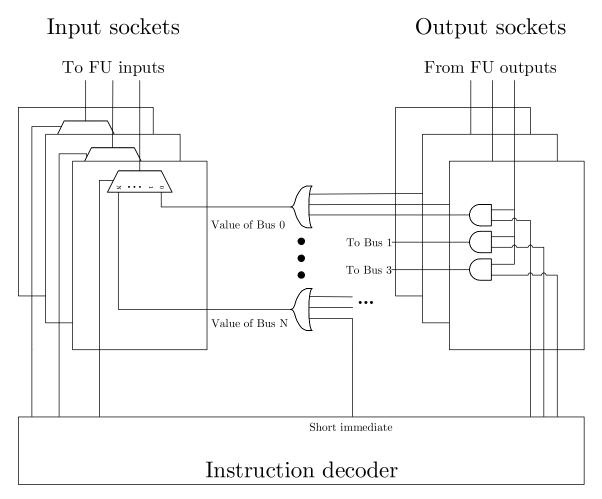

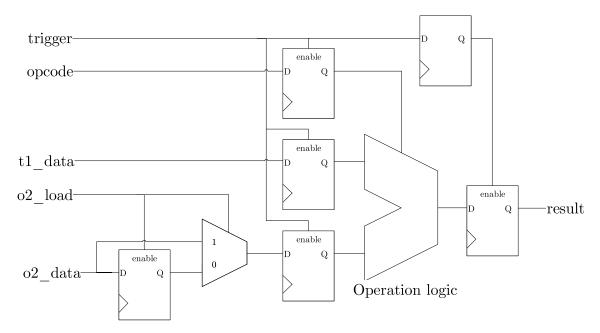

| Figure 3.9. | A possible implementation of semi virtual-time latching                 | 18 |

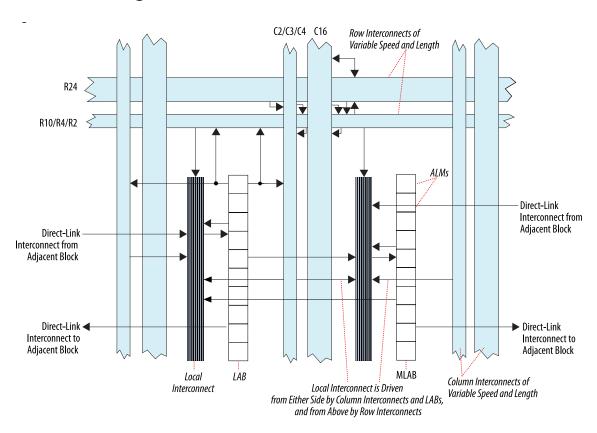

| Figure 4.1. | A high-level description of the routing resources in Intel Stratix 10   |    |

|             | devices [36]                                                            | 21 |

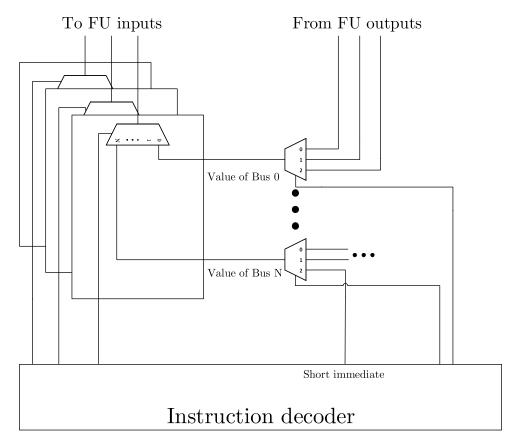

| Figure 5.1. | Multiplexer-based interconnection network                               | 26 |

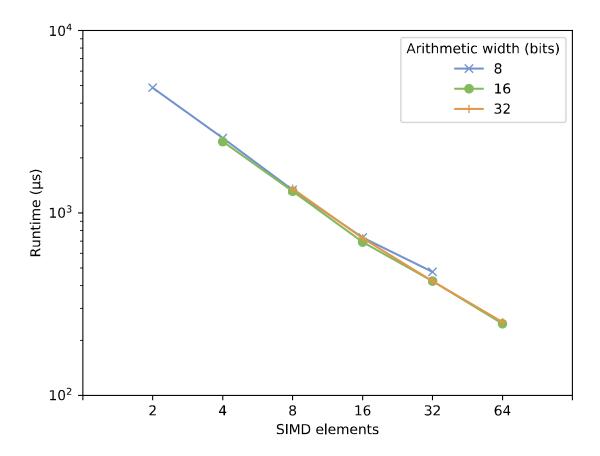

| Figure 6.1. | Total runtimes of the vector architectures.                             | 36 |

#### LIST OF ABBREVIATIONS

ALU Arithmetic-Logic Unit

ASIC Application-Specific Integrated Circuit

CNN Convolutional Neural Network

FF Flip-Flop

FPGA Field Programmable Gate Array

FU Function Unit CU Control Unit

HLS High-Level Synthesis

IC Interconnection Network

IP Intellectual Property

LSU Load-Store Unit

LUT Look-Up Table

NRE Non-Recurring Engineering

PC Program Counter

PE Processing Element

RAM Random Access Memory

RF Register File

RISC Reduced Instruction Set Computer

RTL Register-Transfer Level

SIMD Single Instruction Multiple Data

SRAM Static Random Access Memory

SVTL Semi Virtual-Time Latching

TTA Transport Triggered Architecture

VLIW Very Long Instruction Word

# 1. INTRODUCTION

Field-programmable gate array (FPGA) devices offer a low barrier to entry to logic design compared with application-specific integrated circuit (ASIC) design. They are more suitable for low volume production and prototyping, since they have lower non-recurring engineering (NRE) costs and can be updated in order to fix erroneous behavior in the design [81]. Cloud service providers, such as Amazon Web Services [3] and Huawei [23], have recently added servers with FPGA devices to their offering, further aiding the wider adoption of FPGAs.

FPGAs, however, do not remove the engineering difficulty of developing the logic circuit in the first place. While register-transfer level (RTL) design entry is done with a programming language, the paradigm of traditional hardware description languages is likely to be unfamiliar to software developers. Furthermore, the RTL approach is low-level and requires the designer to understand what kind of logic is inferred from the code they have written, and how this affects the performance and resource consumption of the synthesis result [74, pp. 5-11]. This is even more important in FPGA designs, as the routing resources and logic primitives are less flexible than their ASIC counterparts. The required skills are a rarity: According to a 2017 survey, software engineers outnumber computer hardware engineers 17 to 1 in the United States [69].

High-level synthesis (HLS) is one approach to improve the accessibility of hardware design for software engineers. Here, design entry is done in a high-level language such as C or C++ that is familiar to software programmers and operates at a higher level of abstraction than RTL design. However, HLS tools do not eliminate the need for hardware expertise: Better results can be achieved with an understanding how the algorithms map to the low-level implementation. [44]

Processors are another way to shift design effort from hardware engineers to software designers. They can be used either to manage the control logic for fixed-function hardware, or as primary processing elements in and of themselves. However, a programmability layer introduces inefficiencies in power, performance and utilization compared with fixed-function logic. This overhead can be reduced by tailoring the processor for the application at hand [25], but the high NRE costs of ASIC production mean processors implemented with these technologies have to be more flexible. Soft processors, i.e., processors implemented on FPGA fabric, can be customized more aggressively, as the device can be reprogrammed with a different processor if the application changes. Programming these processors will be more similar to the software programmer's existing experience, and they will not only use familiar languages, but use them in a familiar manner.

1. Introduction 2

Transport-triggered architectures (TTA) have shown promise in the field of soft processors. Compared with a traditional operation-triggered architecture, TTA has a simpler implementation, leading to lower logic requirements and higher frequency. Furthermore, the instruction encoding describes explicit parallelism without requiring complex decoding logic. [37]

This thesis describes FPGA-specific optimizations for TTAs and extends previous work by exploring the TTA design space, focusing on different parallel programming models and their scalability on FPGAs. Chapter 2 presents an overview of common processor architectures and their approaches for high performance are reviewed. This is followed by an in-depth examination of the TTA paradigm in Chapter 3 followed by an overview of the toolset used in this thesis to aid the architectural exploration of TTAs. Chapter 4 begins with a description of the structure of modern FPGA devices, followed by an overview of the design methods targeting FPGAs and a comparison to ASIC technologies. In Chapter 5, the details of TTA soft processor implementations are discussed. Different implementations of the components of TTAs and guidelines for high-performance FPGA designs are presented here. These implementations are evaluated in Chapter 6. In addition to a comparison of the individual component implementations, parallel function unit configurations are examined, and a case study involving a TTA optimized for convolutional neural network execution is presented. Chapter 7 presents related work and compares the existing approaches to the work presented in this thesis. The thesis finishes with a discussion of what has been achieved in it and an examination of possible future research avenues in Chapter 9.

# 2. PROCESSOR ARCHITECTURES

There are a wide variety of processor architectures, with different use cases and different approaches on fulfilling their design goals. Understanding popular processor design ideas is clearly beneficial when designing similar processors, and while the processor architecture approaches presented here have originated from and seen most use in traditional operation-triggered architectures, many of these approaches can be applied to TTA design as well.

This chapter presents the basics of processor architectures and common ways to to achieving high performance. This is divided into instruction scheduling, ways to parallelize computation at a processor architecture level, and memory hierarchies. Finally, we cover the principles of application-specific processor design.

# 2.1 Instruction Scheduling

Dynamic instruction scheduling can be used to mask long instruction latencies, and increase the performance particularly with heavily branching code. It is used extensively in modern general-purpose processors, and allows for speculative execution of conditional branches, executing multiple instructions from one thread in parallel, and managing high-latency instructions by executing the following instructions while it completes, as long as the data dependencies between operations are satisfied. However, the required scheduling logic can be very costly. Indeed, this is the main disadvantage of a hardware-heavy scheduling approach [26, p. 222].

Even without dynamic scheduling, pipelined processor architectures require hazard detection and resolution logic to detect and avoid pipeline hazards, such as an instruction reading a value from the register file (RF) before the correct value has been written there by the previous instruction. Exposed datapath architectures alleviate the logic requirements by moving the work of resolving pipeline hazards to the compiler. By allowing direct control of the datapath and requiring the compiler to resolve some or all of the control logic for it, the hardware implementation can be simplified.

In addition to TTAs, which will be covered more thoroughly in this chapter, various exposed datapath architectures have been proposed, with a large variance in organization and scale. Some architectures use one-dimensional [82] or two-dimensional [7, 9, 54, 79, 80] arrays of small processing elements (PEs) with a software-controlled interconnect between them, while others have an organization resembling very long instruction word (VLIW) processors, with multiple PEs controlled by one instruction [80].

There are drawbacks to exposing the datapath at the architectural level. Most directly, since more of the implementation is described by the architecture, it cannot be changed radically

to accommodate e.g. out-of-order execution. New versions of exposed datapath processors are more likely to break compatibility with their predecessors. This is undesirable in systems where a longer lifespan is a key concern, especially those with closed-source software developed for them.

Relying on static scheduling by the compiler limits the optimizations to the opportunities the compiler can guarantee. For example, if a function accesses two pointers simultaneously, reading from one and writing to the other, the compiler cannot necessarily resolve if the two pointers are equivalent. In this case, the two memory accesses have to be kept in the same order as they are specified in the program. It is possible for the compiler to produce code that checks during execution whether the accesses overlap, and choose between two versions of the code based on that, but this increases the resulting code size. A hardware-based dynamic scheduler can look at the two accesses when they are ready to be scheduled, and issue them accordingly based on whether or not they conflict.

Dynamic latencies can also be an issue. In order to resolve data dependencies between operations, the compiler needs to make some assumptions on how many clock cycles it takes for an operation to produce a result. However, certain operations, most commonly cached memory accesses, may take a nondeterministic amount of time. Some of this can be hidden by the architectural description of the processor, by assigning these operations a latency equal to the maximum latency of the operation. This negates the performance gain of a potentially shorter operation, such as a cache hit, and may introduce no-operation instructions into the instruction stream, thus raising the instruction memory size requirements.

Alternatively, the execution of other PEs can be halted while the operation result is being produced, either when the PE should produce the result, or when the result would be read by another instruction. This approach can improve performance when the longer latency executions happen less often and does not require inserting nonfunctional operations into the instruction stream, but requires more communication between PEs.

# 2.2 Parallel Organizations

A simple approach to improving performance is to connect multiple processors together, usually by sharing some or all of the memory space between individual processors. Each processor executes independently and communicates through the shared memory space. While multiprocessor systems give a theoretically linear increase in performance and logic utilization, communication between processors limits their performance in practice.

Another way to parallelize an application is to run multiple threads simultaneously on one processor. Even without additional resources for the execution of operations, switching between threads can mask long operation latencies. *Barrel threading* is a specific multithreading approach where the active thread is switched every cycle in a constant order. This is simple to implement in hardware, and can be used to reduce data forwarding

between processor pipeline stages. For example, in a four-thread barrel threaded processor, each thread is only active every four cycles, so there is no need to pass data from one pipeline stage to the three pipeline stages preceding it, as they are executing different threads. Furthermore, the RF can be split into four parts, one for each thread. These RFs can be further simplified, as it might be possible to use the same port for two or more accesses in different pipeline stages through time multiplexing.

Exposing parallelism explicitly in the instruction encoding can be a more resource-efficient way to increase performance. This is especially popular for application-specific processors, where binary compatibility between processors is not as important. Like traditional superscalar processors, VLIW processors have multiple PEs in parallel, capable of executing different sets of instructions. Instead of the instruction scheduler extracting parallelism from an inherently serial instruction stream, VLIW machines have an instruction that specifies operations separately for each PE. In order to simplify the control logic between many PEs even further, VLIW processors are statically scheduled, with architecturally visible fixed latencies for all operations. As a result, the burden of resolving the hazard falls on the compiler instead of the hardware, simplifying the logic implementation. [26, p. 194]

A VLIW processor usually has a very complex RF. Traditionally, PEs have two operand ports and one result port. In order to execute, for example, a four-lane VLIW instruction in parallel, the PEs will read eight operands from the RF and store four results to it. Any memory structure with eight read ports and four write ports is very complex, but there are approaches to reduce the port count of the RF blocks. Most commonly, a complex RF can be partitioned into multiple simpler ones, e.g. an RF with four write and eight read ports can be split into two RFs with two write and four read ports each. While the register files still have the same number of total read and write ports and can therefore be used with four PEs with full utilization, this creates additional constraints for the compiler. For example, it cannot schedule an instruction that tells all four PEs to write to the same RF partition. The performance impact can be reduced with a register allocation scheme that takes the partitioning into account.

Single Instruction Multiple Data (SIMD) is another way to expose parallelism to the programmer. They processors execute the same instruction across multiple elements, similar to vector arithmetic. This execution model allows the PEs to perform work largely decoupled from each other. Communication between PEs is still necessary, but this is often done through memory rather than the register file, or by specialized instructions that transfer data between vector elements. However, programming SIMD processors can be more difficult: Even when the algorithm can be executed in vector operations, assembly level programming may be needed to utilize it [91]. On the other hand, compilers attempt to vectorize programs automatically when the processor can use those operations, and libraries with vectorized implementations of common algorithms are available.

Another way to increase the flexibility of parallel processing is the Single Instruction

Multiple Thread (SIMT) execution model, most often seen in graphics processing units [26, p. 288]. Here, multiple threads are executed simultaneously as a *warp*, usually in parallel on multiple PEs. The execution is more restricted than a multicore processor, however, as traditionally only one instruction can be issued at once. This means that when threads in a warp take different paths from a branch instruction, i.e., *diverge*, the SIMT processor will execute both paths serially, allowing execution on some of the threads while keeping the other threads idle. Lower divergence means more active threads on average and a greater performance.

The two main challenges with SIMT architectures are memory accesses and warp scheduling. When executing a memory operation during completely convergent execution, all threads issue one load. Handling many memory accesses serially is very slow, so parallelizing the accesses is preferred. However, multiport memory structures are expensive to implement, so this is usually done by a series of wide memory accesses.

Because the processing elements run different threads, simultaneous memory accesses do not necessarily have any relation to each other. In the worst case scenario, all active threads issue a load to addresses so far apart from each other that any wide memory access can only hit at most one of the requested memory locations. Some of these difficulties can be alleviated by a combination of caches and thread- or warp-local scratchpad memory, and by switching execution to another set of active threads or to another warp entirely while the memory accesses are done in the background. However, the best performance can only be reached by using an algorithm where simultaneous memory accesses to land next to each other.

The traditional approach to keeping track of warp execution is stack-based. Whenever warp execution diverges, the scheduler pushes a divergence token onto the stack. This contains information about which threads did not take the branch, and the program counter (PC) from where to continue executing those threads. This information will be used to return active status to those threads once threads that took the branch reach an instruction with a bit that signifies the end of the branch, i.e., the point where the originally diverged execution should resynchronize. Once the newly active threads reach the same instruction, the warp resynchronizes and continues execution. [18].

This method of warp scheduling is incompatible with the way mutexes are used to synchronize between threads in general purpose processors. If a thread tries to acquire a lock that is held by a different thread, it cannot progress forward until the thread unlock the mutex. If the thread holding the lock is in the same warp, it will not progress until the active threads reach a synchronization point. This results in a deadlock.

One way to handle warp scheduling that avoids this problem is to have each thread hold its own state, i.e., program counter and stack [68, p. 27]. The scheduler chooses one of the program counters to issue an instruction, and threads that have a program counter that matches what has been issued activate. Some logic is still needed to choose a PC such that

divergent threads converge as soon as possible in order to reach a good performance. At its simplest, this method can be the thread that has the smallest stack pointer, or in the case of a tie, the smallest program counter [17]. This approach can also be used in a system where the scheduler can issue more than one instruction at a time [16].

It should be noted that the different approaches to parallelization do not necessarily exclude one another, and many combinations are complementary to the strengths of individual approaches. For example, it is possible to design a processor with a VLIW programming model that also has SIMD instructions, or a SIMT processor that uses a combination of parallel PEs and barrel threading to execute a warp.

## 2.3 Memory Organization

Memory organization is an important part of a processor system. In terms of performance, larger memories are slower to access than smaller ones. The main memory is often on a separate integrated circuit from the processor, introducing additional latency in the driving circuitry, and through the increased capacitance of the longer wires. In terms of power consumption, faster memories are more power-hungry, which encourages reducing the size of fast memories places an upper limit on how fast you can make the main memory.

Cache hierarchies are often used in general purpose processors in order to have tiers of small but fast memories close to the processors, backed up by a large but slow memory off-chip. When a cache receives a memory access request for the first time, it will forward it to the next level in the hierarchy. The response can be stored in the cache, possibly replacing an old value, so that an access to the same memory address can be fulfilled without accessing the higher levels in the hierarchy.

Another option is to have a non-uniform memory structure, where a portion of the memory is faster to access from a particular processor, or by having a separate address space for a local scratchpad. Unlike caches, this requires explicit software control and may as a result increase programmer effort.

# 2.4 Application-Specific Tailoring

When a processor is designed with a particular application in mind, rather than as a general-purpose processor, the design should take that into account in all of its parts. The approaches presented above may suit one application better than another, and it is important to understand the application, for example, in terms of how well it can utilize a SIMD organization, or how much memory is needed to contain the working data set at any time. For example, many image processing algorithms can be parallelized easily, as they essentially perform one operation on every pixel of an image, while some encryption algorithms may depend on the value of the previous iteration, leading to serial execution.

The instruction set provides another way of tailoring the processor. Most simply, the designer can start with a general-purpose instruction set and remove the operations that

are not being used by the application. Alternatively, instructions can be added depending on the needs of the application. These can be constrained versions of general-purpose instructions, a common combination of instructions, or a custom instruction that is simple to implement in hardware but does not map well to software, such as specific bit-level transformations that may require many bitwise shift and logic operations in software, but only need a handful of logic gates and wires for the hardware implementation.

# 3. TRANSPORT-TRIGGERED ARCHITECTURES

Transport-triggered architectures are a mostly unexplored avenue in soft processor architectures. However, they have many features that make for a simple and efficient implementation on FPGAs, and initial work [37] has shown them to be competitive with vendor-supplied soft processor templates.

This chapter first presents the TTA paradigm, along with transformations from two common processor architectures into an equivalent TTA and comparisons between the approaches. Lastly, this chapter will cover the TTA-Based Co-Design Environment (TCE), specifically the configuration parameters of its TTA template and the default implementation of the TTAs that can be described by this template.

#### 3.1 From VLIW to TTA

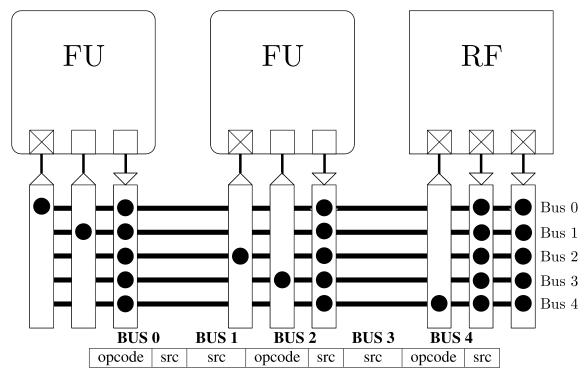

The TTA paradigm is often seen as an extension of VLIW architectures, and there are a number of similarities: Both are statically-scheduled processors which typically feature explicit parallelism by dividing the instruction word into independent partitions. Indeed, Corporaal [19, pp. 81-102] demonstrated how to transform a generic VLIW machine into a TTA, a process which will be revisited here.

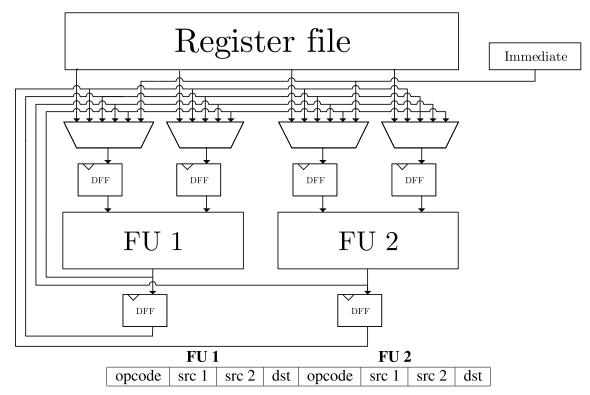

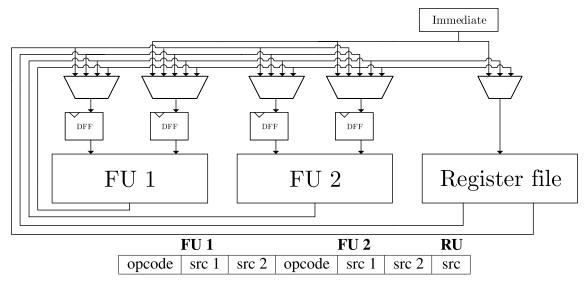

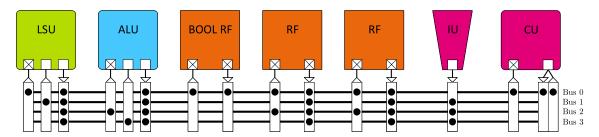

The VLIW machine in Figure 3.1 exemplifies VLIW design. The instruction word is divided into multiple smaller instructions which execute independently on separate function units (FU). Operations have architecturally-visible latencies and some of the work of resolving hazards is moved to the compiler. The main downside of VLIW implementations, especially on FPGAs, is the register file, which is needed for the FUs to communicate with each other. Assuming a typical FU with two inputs and one output, the RF requires three ports for each FU.