# TIMO PALDANIUS ANALOGUE PREDISTORTION OF RF BIPOLAR JUNCTION TRANSISTORS USING A LOGARITHMIC AMPLIFIER

Master of Science Thesis

Examiners: University Lecturer Olli-Pekka Lunden, Lecturer Jari Kangas Examiners and topic approved on 28 February 2018

ii

## ABSTRACT

**TIMO PALDANIUS**: Analogue Predistortion of RF Bipolar Junction Transistors Using a Logarithmic Amplifier Tampere University of technology Master of Science Thesis, 61 pages, 14 Appendix pages September 2018 Master's Degree Programme in Electrical Engineering Major: Electronics Examiners: University Lecturer Olli-Pekka Lunden, Lecturer Jari Kangas

Keywords: amplifier, analogue predistortion, bipolar junction transistor, exponential, intermodulation, linear, linearization, logarithmic amplifier, nonlinear

A proof of concept study is conducted in the thesis, a new analogue predistortion linearization scheme for bipolar junction transistors is implemented and tested. Output current and voltage of a bipolar junction transistors exponentially depends on the input voltage, thus the output is distorted exponentially. We study whether a bipolar junction transistor can be linearized by cascading a logarithmic amplifier in front of the bipolar junction transistor amplifier. Logarithmic function is the inverse of the exponential function. Consequently, these two functions should cancel each other, rendering the system's output linearly dependent on the input. To verify this, the scheme is implemented in practice and measured. The measurement results confirm the viability of the scheme, the output third-order intermodulation products are suppressed by 20 dB. The proposed linearization scheme is low cost and complexity and inherently broadbanded.

## TIIVISTELMÄ

TIMO PALDANIUS: Radiotaajuisen bipolaaritransistorin analoginen esivääristys logaritmisella vahvistimella Tampereen teknillinen yliopisto Diplomityö, 61 sivua, 14 liitesivua Syyskuu 2018 Sähkötekniikan diplomi-insinöörin tutkinto-ohjelma Pääaine: Elektroniikka Tarkastajat: Yliopistonlehtori Olli-Pekka Lunden, Lehtori Jari Kangas

Avainsanat: analoginen esivääristys, bipolaaritransistori, epälineaarinen, exponentiaalinen, keskinäismodulaatiosärö, lineaarinen, logaritminen vahvistin, vahvistin

Tämä opinnäytetyö on soveltuvuusselvitys, jossa toteutetaan ja testataan uusi analoginen esivääristyslinearisointimenetelmä. Bipolaaritransistorien ulostulo on exponentiaalisesti riippuvainen sisäänmenosta, joten bipolaaritransistorilla toteutetun vahvistimen ulostulossa luonnostaan esiintyy exponentiaalista säröytymistä. Ongelman korjaamiseksi vahvistimen eteen kytketään kaskadiin logaritminen vahvistin, sillä logaritmifunktio on eksponenttifunktion vastakohta. Teoriassa logaritmisen ja exponentiaalisen säröytymisen pitäisi kumota toisensa, minkä seurauksesta systeemin ulostulo riippuu lineaarisesti sisäänmenosta. Työssä tehdään käytännön toteutus, jolla menetelmän toimivuus ia Mittaustulokset käytännöllisyys todennetaan. varmentavat menetelmän toimivuuden; ulostulon kolmannen kertaluvun leikkauspiste on parantunut 10 kolmannen kertaluvun keskinäismodulaatiosärö-signaalit dB:llä. Lisäksi vaimenevat 20 dB:llä. Esitelty linearisointimenelmä on yksinkertainen ja kustannustehokas. Sen lisäksi työssä esitelty menetelmä on luonnostaan laajakaistainen.

### PREFACE

First, I would like to thank the TUT electronics club TELOK and its members, especially Markus Ristiniemi and Teemu Salminen. The printed circuit board manufacturing process and the soldering (and sometimes desoldering) equipment at TELOK proved to be invaluable for the practical thesis work. Helpful advice on how to improve my layout designs, board manufacturing and soldering were also provided by members of TELOK. I would also like to acknowledge my examiners Jari Kangas and Olli-Pekka Lunden as they were almost always readily available for conferring about thesis related issues. Lastly, I would also like to thank my brother Antti for helping improve my soldering and desoldering skills that were absolutely necessary for the success of the thesis.

# CONTENTS

| 1.  | INTR             | RODUCT     | ΓΙΟΝ                                                        | 1           |

|-----|------------------|------------|-------------------------------------------------------------|-------------|

| 2.  | BAC              | BACKGROUND |                                                             |             |

|     | 2.1 Linearity    |            | ty                                                          | 3           |

|     | 2.2              | Conseq     | puences of nonlinearity                                     | 5           |

|     | 2.3 RF amplifier |            | plifier linearization methods                               | 9           |

|     |                  | 2.3.1      | Power back-off                                              | 9           |

|     |                  | 2.3.2      | Feedforward linearization                                   | 10          |

|     |                  | 2.3.3      | Cartesian feedback loop                                     | 11          |

|     | 2.4              | Predist    | ortion                                                      | 12          |

|     |                  | 2.4.1      | Digital predistortion                                       | 12          |

|     |                  | 2.4.2      | Analogue predistortion                                      | 13          |

|     | 2.5              | Analog     | gue predistortion Implementations                           | 13          |

|     |                  | 2.5.1      | A wideband analog predistortion power amplifier with m      | ulti-branch |

|     |                  | nonline    | ear path for memory-effect compensation                     | 13          |

|     |                  | 2.5.2      | Analog pre-distortion circuit for radio over fiber transmis | sion 14     |

|     |                  | 2.5.3      | An E-BAND analog predistorter and power amplifier MM        | IIC chipset |

|     |                  |            |                                                             | 15          |

| 3.  | PREI             | DISTOR     | TION SCHEME                                                 | 17          |

|     | 3.1              | Ebers-N    | Moll model                                                  | 17          |

|     | 3.2              | Logarit    | thmic amplifier                                             | 21          |

|     | 3.3              | RF BJ      | T amplifier linearization using an analogue predistortion l | ogarithmic  |

|     | amp              | lifier     |                                                             | 24          |

| 4.  | VER              | IFICATI    | ON                                                          | 27          |

|     | 4.1              | Implen     | nentation                                                   | 27          |

|     | 4.2              | Side pr    | ojects                                                      |             |

|     |                  | 4.2.1      | Wilkinson Power Divider                                     |             |

|     |                  | 4.2.2      | Impedance transformer                                       | 37          |

|     |                  | 4.2.3      | Measurement setup                                           | 39          |

|     | 4.3              | Measu      | rements and simulations                                     | 40          |

|     |                  | 4.3.1      | Intermodulation measurements                                | 40          |

|     |                  | 4.3.2      | Gain measurements                                           | 44          |

|     |                  | 4.3.3      | Stability                                                   | 47          |

|     |                  | 4.3.4      | Impedance measurements                                      | 48          |

|     |                  | 4.3.5      | Simulation results                                          | 49          |

| 5.  | DISC             | USSION     | ۸                                                           | 52          |

|     | 5.1              | Practic    | al work                                                     |             |

|     | 5.2              | Assess     | ment                                                        | 54          |

|     | 5.3              | Future     | work                                                        | 56          |

| 6.  | CON              | CLUSIO     | DN                                                          | 57          |

| DEI | FEREN            | ICES       |                                                             | 59          |

| APPENDIX 1: DIODE-CONNECTED TRANSISTOR SIMULATIONS | 62 |

|----------------------------------------------------|----|

| APPENDIX 2: LAYOUT MATERIAL                        | 64 |

| APPENDIX 3: WILKINSON POWER DIVIDER LAYOUT         | 67 |

| APPENDIX 4: IMPEDANCE TRANSFORMER LAYOUT           | 70 |

| APPENDIX 5: SIMULATION CIRCUITS                    | 72 |

# LIST OF FIGURES

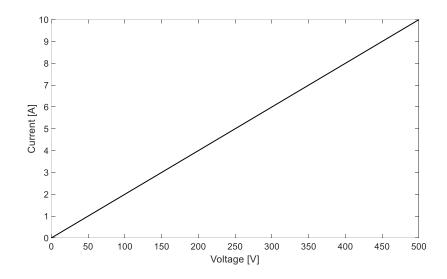

| Figure 1. Current through a 50 $\Omega$ linear resistor as a function of voltage    | 4  |

|-------------------------------------------------------------------------------------|----|

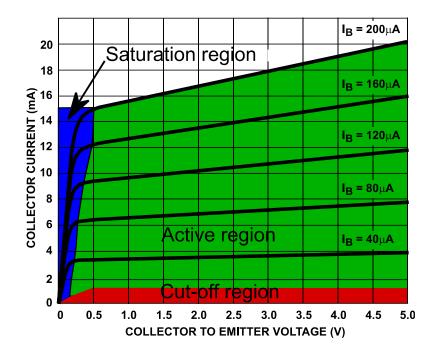

| Figure 2. HFA3134 BJT characteristics curve. Modified from [12]                     | 5  |

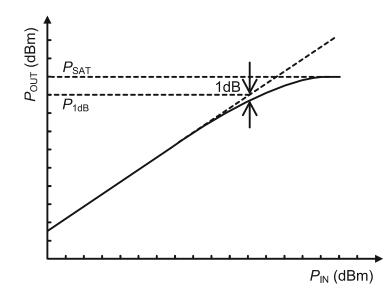

| Figure 3. Gain compression. [14]                                                    | 6  |

| Table 1. Intermodulation products for the first five orders. [15, 16]               | 6  |

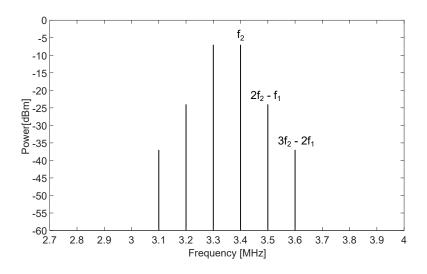

| Figure 4. Intermodulation measurement results for a nonlinear low power             |    |

| amplifier                                                                           | 7  |

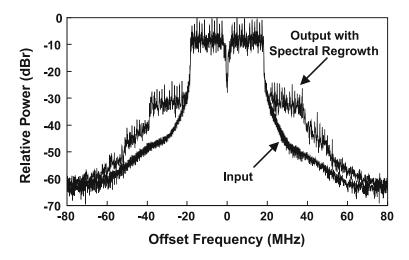

| Figure 5. Spectral regrowth. [14]                                                   | 7  |

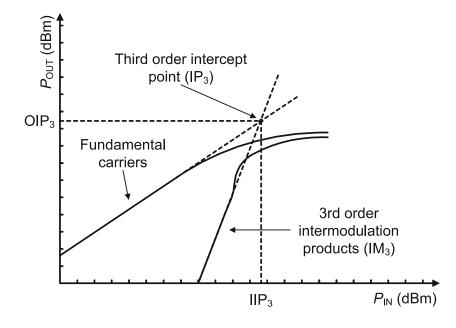

| Figure 6. Third order intercept point (IP <sub>3</sub> ). Modified from [14]        | 8  |

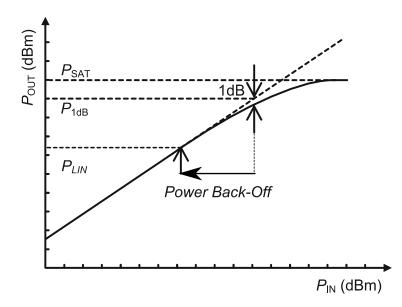

| Figure 7. Power Back-off for RF amplifier. Modified from [14]                       | 9  |

| Figure 8. Two tone intermodulation with feedforward linearization. [3]              | 10 |

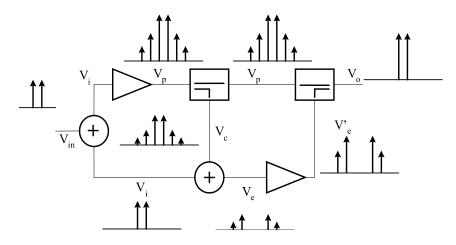

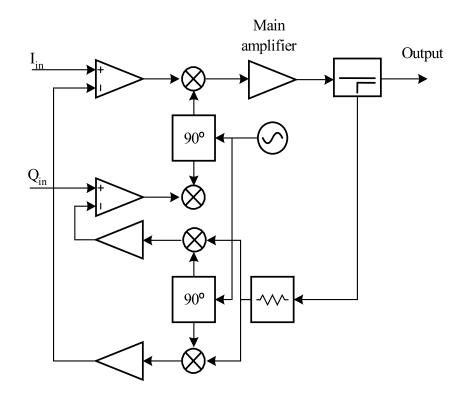

| Figure 9. Simplified Cartesian Loop architecture. [3]                               | 11 |

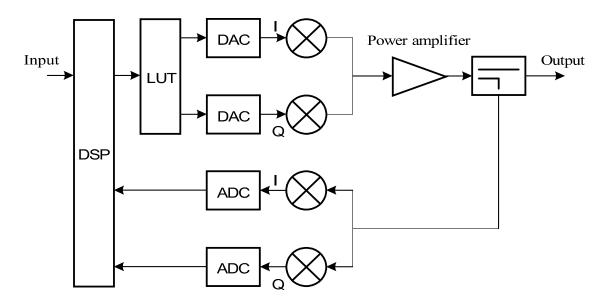

| Figure 10. Digital baseband adaptive predistortion. Modified from [3]               | 12 |

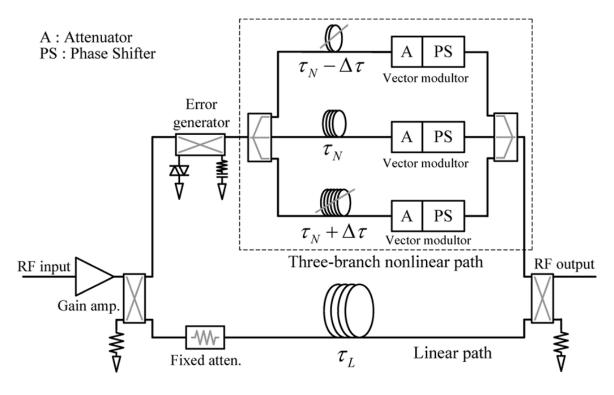

| Figure 11. Multi-branch analogue predistortion schematic. [20]                      | 14 |

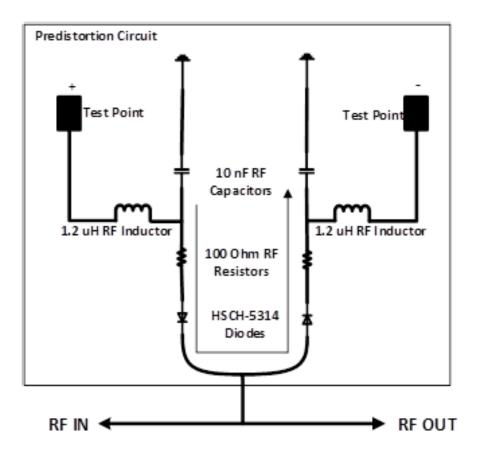

| Figure 12. Predistortion circuit for radio over fiber systems. [21]                 | 15 |

| Figure 13. E-Band analogue predistorter schematic. [22]                             | 16 |

| Figure 14. Thesis predistortion scheme                                              | 17 |

| Figure 15. npn BJT consist of n and p-type semiconductor materials                  | 17 |

| Figure 16. NPN BJT Ebers-Moll model. Modified from [23]                             | 18 |

| Figure 17. Reduced Ebers-Moll model for forward biased operation. Modified          |    |

| from [23]                                                                           | 19 |

| Figure 18. A negative logarithmic amplifier.                                        | 21 |

| Figure 19. Positive logarithmic amplifier                                           | 22 |

| Figure 20. Proposed predistortion scheme of a BJT RF amplifier. [5]                 | 24 |

| Figure 21. The final implementation of the predistortion scheme.                    | 27 |

| Figure 22. Simulated gain S21 and stability factor $\mu$ (Mu) for a diode-connected |    |

| transistor. The circuit amplifies from 4.2 GHz to 5.85 GHz. If $\mu$ is             |    |

| below 1, then the circuit is potentially unstable                                   | 29 |

| Figure 23. Simulated gain and stability factor Mu for a stabilized diode-connected  |    |

| transistor circuit                                                                  | 30 |

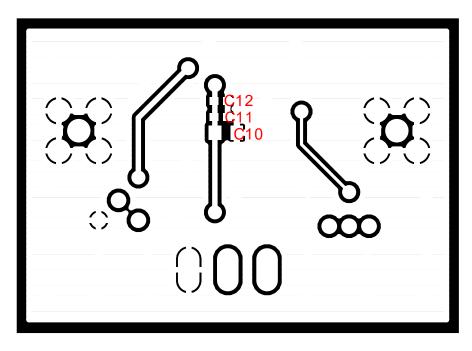

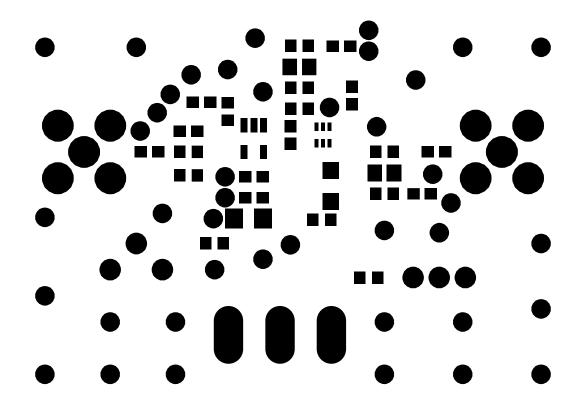

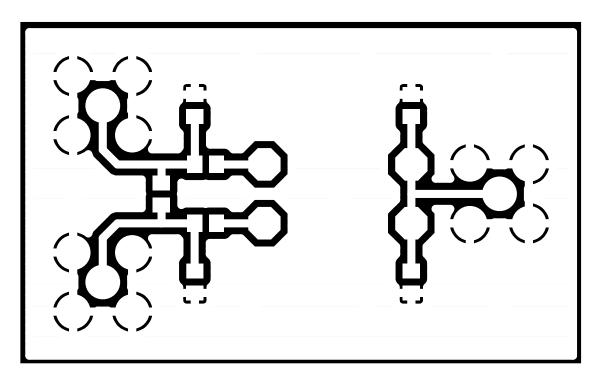

| Figure 24. Top copper layer. The layout is a negative: white is copper and black    |    |

| is the exposed FR4 substrate. Note, the layouts in the figures are                  |    |

| not to actual scale                                                                 | 31 |

| Figure 25. Bottom copper layer.                                                     | 31 |

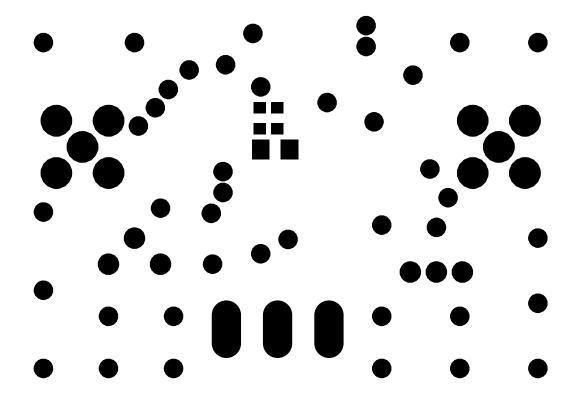

| Figure 26. Top layer of the implementation.                                         |    |

| Figure 27. Bottom layer of the implementation.                                      | 32 |

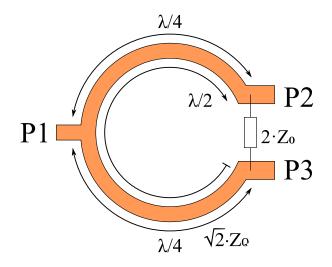

| Figure 28. Wilkinson Power Divider architecture based on microstrip lines. Ports    |    |

| <i>P2 and P3 are the input ports and P1 is the output port when the</i>             |    |

| divider is operated as power combiner. The wavelength is denoted                    |    |

| by $\lambda$ and the characteristic impedance by $Z_0$ . [30]                       |    |

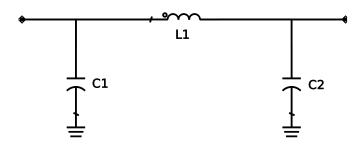

| Figure 29. Lumped element model for a short transmission line.                      | 34 |

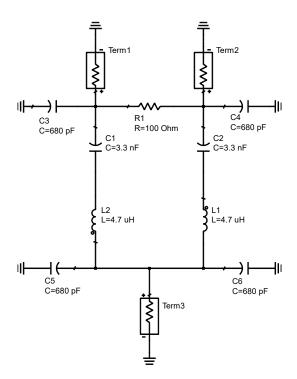

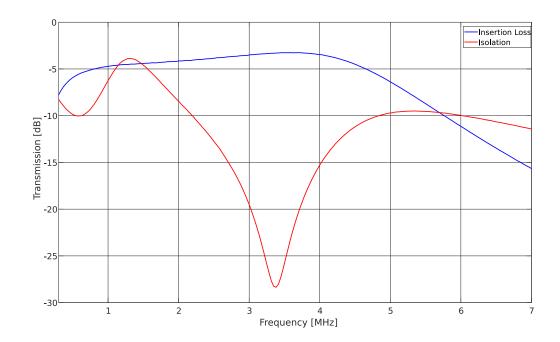

| Figure 30. Wilkinson Power Divider for 3 MHz.                                                    | 35 |

|--------------------------------------------------------------------------------------------------|----|

| Figure 31. Measured Insertion loss and isolation for the Wilkinson Power                         |    |

| Divider                                                                                          | 35 |

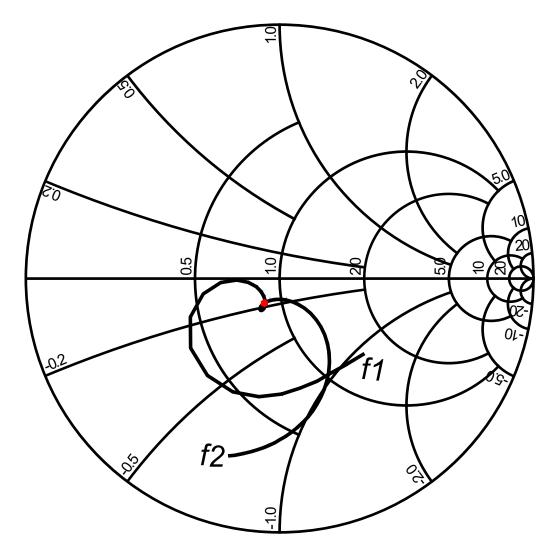

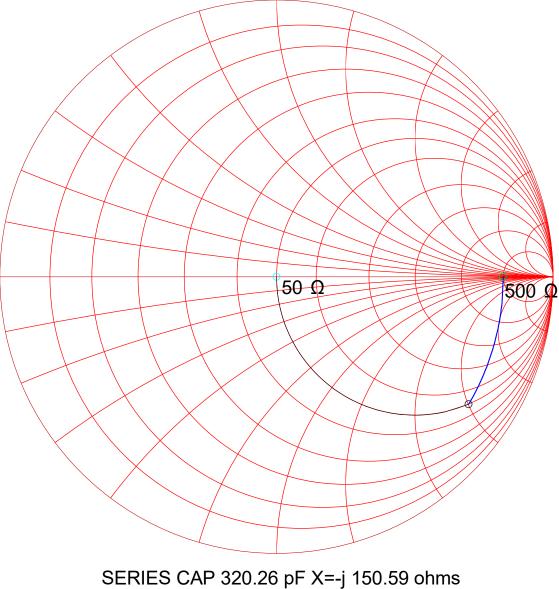

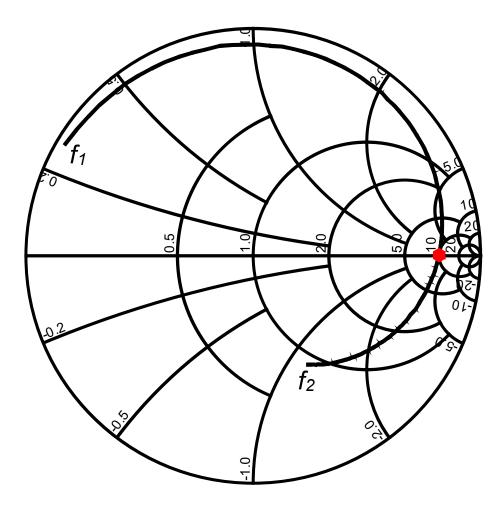

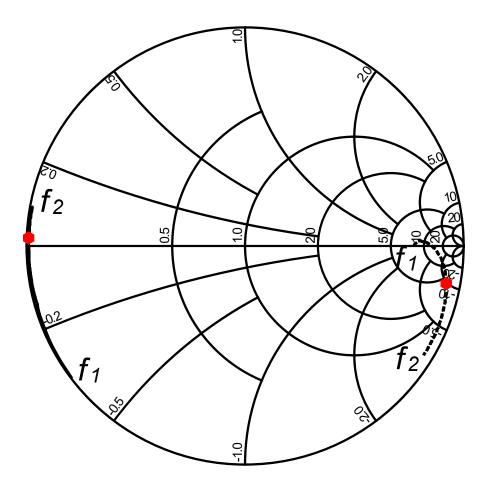

| Figure 32. Wilkinson Power Divider impedance, measured impedance at 3.3 MHz                      |    |

| is $Z = Z0(0.870 - j0.171)$ . Note, the impedance is normalized. A                               |    |

| red dot in the chart marks the impedance at 3.3 MHz. The                                         |    |

| frequency sweep was from $f1 = 300 \text{ kHz}$ to $f2 = 7 \text{ MHz}$ . The                    |    |

| graph start and end frequencies are marked shown in the plot                                     | 36 |

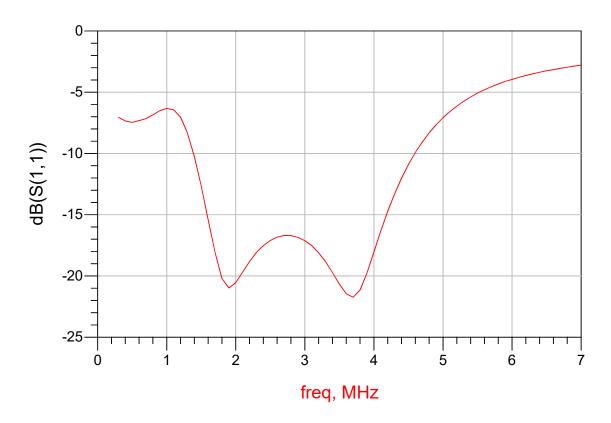

| Figure 33. Return loss (S11) for the Wilkinson Power Divider                                     |    |

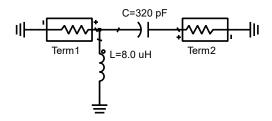

| <i>Figure 34. Schematic for the impedance transformer. The component values in the</i>           |    |

| schematic are for a matching circuit that operates at 3.3 MHz                                    | 37 |

| <i>Figure 35. Determining the capacitance and inductance for the impedance</i>                   |    |

| transformer with Smith's chart                                                                   | 38 |

| Figure 36. Measured impedance from $f1 = 300 \text{ kHz}$ to $f2 = 7 \text{ MHz}$ . 500 $\Omega$ |    |

| impedance is marked with a red dot                                                               | 30 |

| -                                                                                                | 39 |

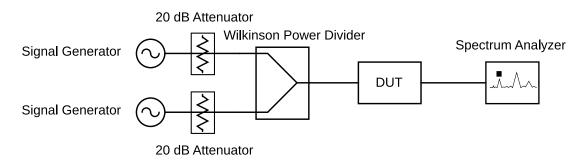

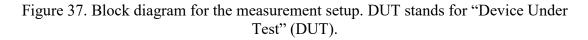

| Figure 37. Block diagram for the measurement setup. DUT stands for "Device                       | 20 |

| Under Test" (DUT).                                                                               | 39 |

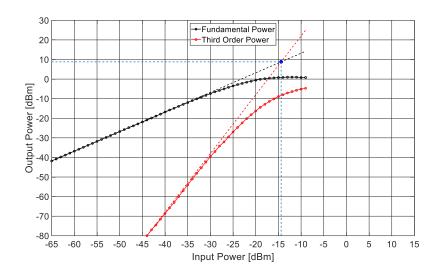

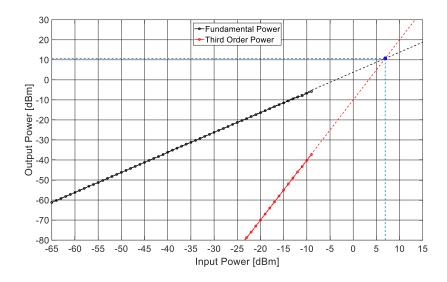

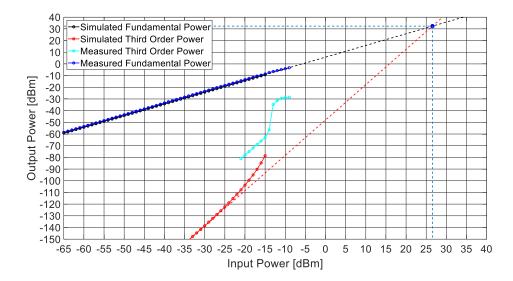

| Figure 38. Reference amplifier measurement results with $IC = 5 \text{ mA}$ . Each dot in        |    |

| the graph represents a single measurement point. The black dots                                  |    |

| are for the fundamental power and the red dots are for the third                                 |    |

| order intermodulation products. The frequencies for the third order                              |    |

| power were measured to be 3.2 MHz and 3.5 MHz. The noise floor                                   |    |

| was at -80 dBm. OIP3 and IIP3 are shown by the blue dot and the                                  |    |

| blue dashed lines                                                                                | 41 |

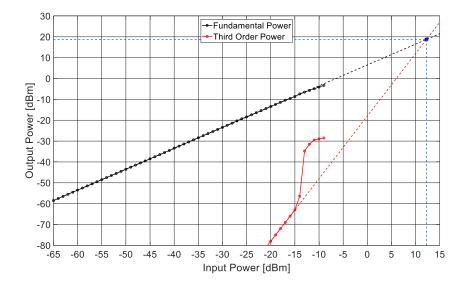

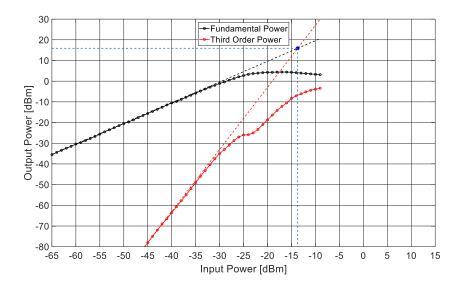

| Figure 39. Intermodulation measurement results for the linearized amplifier with                 |    |

| collector currents being 5mA.                                                                    | 41 |

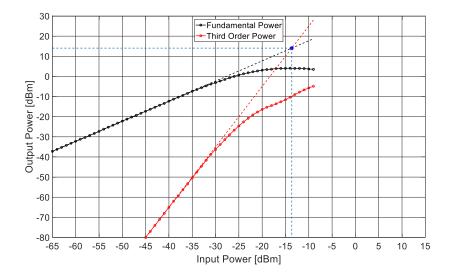

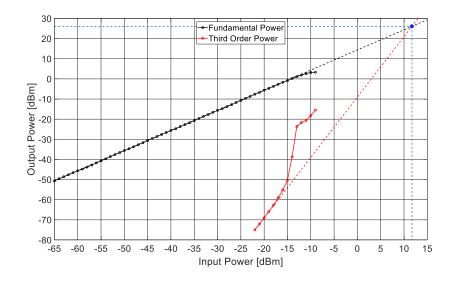

| Figure 40. Intermodulation measurement results for the reference amplifier with                  |    |

| collector current of 10mA                                                                        | 42 |

| Figure 41. Results for the reference amplifier with 20 dB attenuator at the input                | 43 |

| Figure 42. Intermodulation measurement results for the reference amplifier with                  |    |

| the impedance transformer connected. Note, the collector current is                              |    |

| 5 mA                                                                                             | 43 |

| Figure 43. Linearized amplifier with the impedance transformer                                   |    |

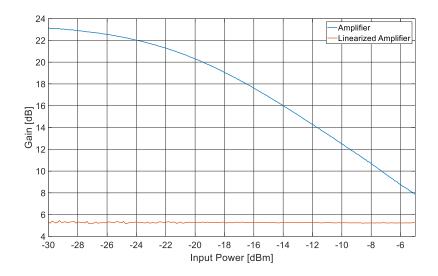

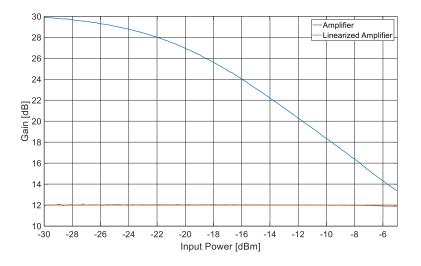

| <i>Figure 44. VNA input power sweep for the reference amplifier and the linearized</i>           |    |

| amplifier.                                                                                       | 45 |

| <i>Figure 45. Gain versus input power plot for the reference amplifier and the</i>               | 10 |

| linearized amplifier with the impedance converter connected                                      | 15 |

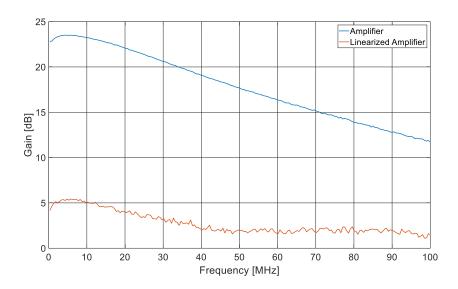

| Figure 46. Frequency sweep gain measurement results with standard 50 $\Omega$ load               | 75 |

| impedance                                                                                        | 46 |

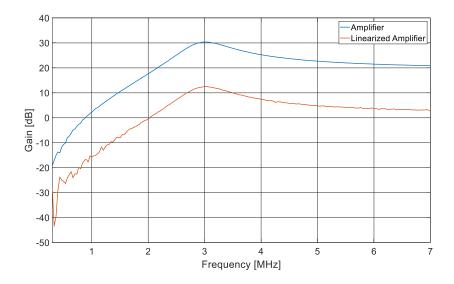

| Figure 47. Frequency sweep with impedance transforming. Note, the frequency                      |    |

| sweep was only conducted up to 7 MHz                                                             | 46 |

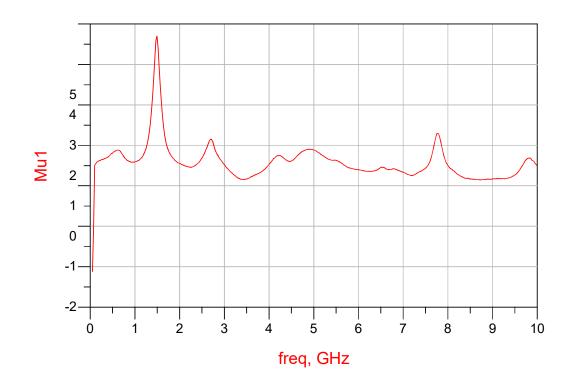

| Figure 48. Stability factor Mu for the linearized amplifier.                                     | 47 |

| Figure 49. Impedance measurement results from $f1 = 300 \text{ kHz}$ to $f2 = 7 \text{ MHz}$ |    |

|----------------------------------------------------------------------------------------------|----|

| for the linearized amplifier. The input impedance is marked a solid                          |    |

| line and the output impedance with a dashed line. The impedance                              |    |

| values at 3.3 MHz are marked with red dots. At 3.3 MHz the input                             |    |

| impedance is $ZIN = Z0(0.005 + j0.019)$ and the output                                       |    |

| impedance $ZOUT = Z03.438 - j9.573$ .                                                        | 48 |

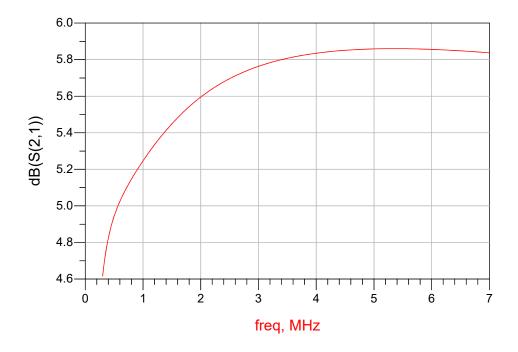

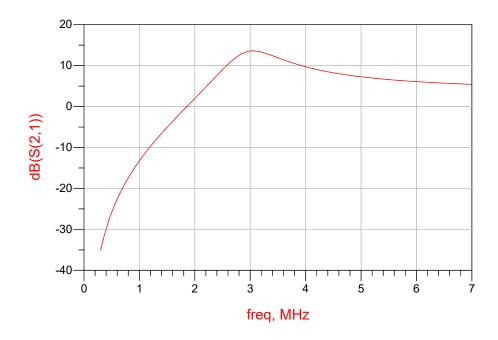

| Figure 50. S21 simulation for the linearized amplifier with 50 $\Omega$ load                 |    |

| Figure 51. S21 simulation with 500 $\Omega$ load                                             |    |

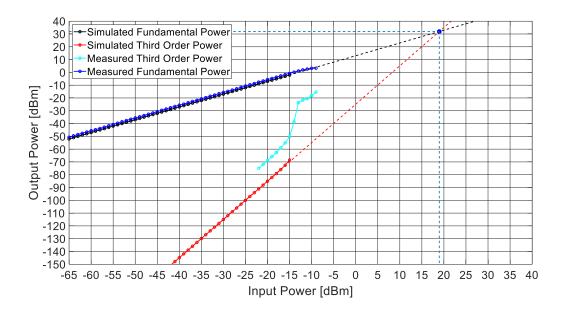

| Figure 52. Intermodulation simulation and measurement results with 50 $\Omega$ load.         |    |

| Note, linear extrapolation has not been included for the                                     |    |

| measurement results.                                                                         | 50 |

| Figure 53. Intermodulation simulation and measurement results with 500 $\Omega$ load         | 51 |

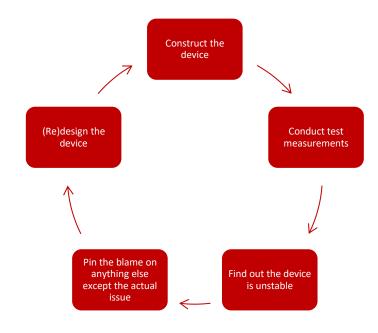

| Figure 54. The vicious cycle.                                                                |    |

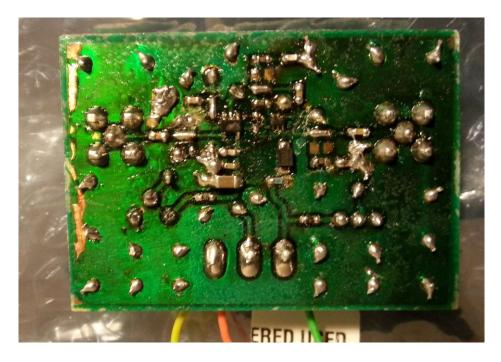

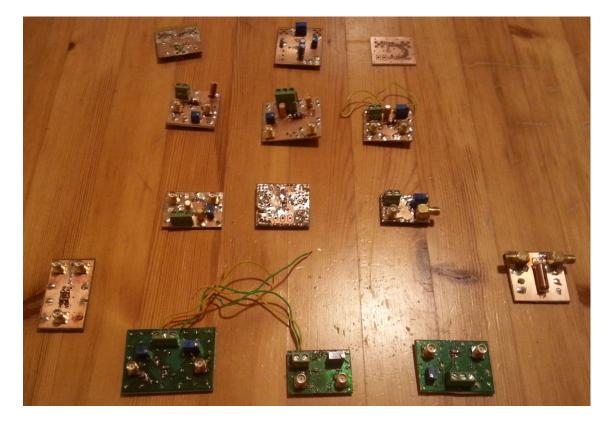

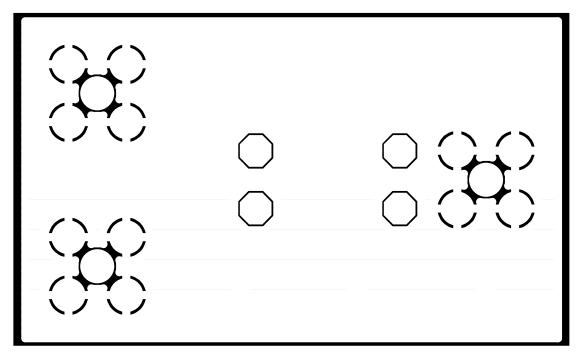

| Figure 55. Boards made during the thesis work. Note, some of the boards have                 |    |

| been salvaged for components                                                                 | 54 |

| Table 2. Measurement and simulation results. Ref stands for the reference                    |    |

| amplifier, Lin. for the linearized amplifier and Imp. for the                                |    |

| impedance transformer. Load impedance is 50 $\Omega$ and the current is                      |    |

| 5 mA unless otherwise stated. Note, IM3 to Carrier at 50 $\Omega$ is                         |    |

| measured when the fundamental output power is -10 dBm and with                               |    |

| 500 $\Omega$ load when the power is -5 dBm                                                   | 55 |

| Table 3. Cost breakdown of the linearized amplifier. [34]                                    | 55 |

| Figure 56. Unstable diode-connected transistor simulation schematic                          | 62 |

| Figure 57. Simulation schematic for the stabilized diode-connected transistor                | 63 |

| Figure 58. Linearized amplifier schematic in EAGLE.                                          | 65 |

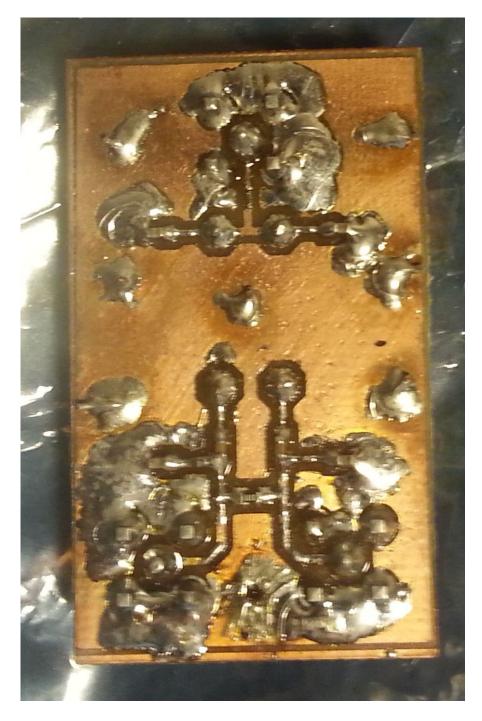

| Figure 59. Top layer solder mask with drill holes included                                   | 66 |

| Figure 60. Bottom layer solder mask with drill holes included                                | 66 |

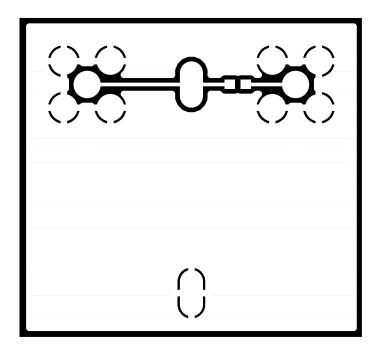

| Figure 61. Wilkinson Power Divider top layer                                                 | 67 |

| Figure 62. Wilkinson Power Divider bottom layer                                              | 67 |

| Figure 63. Picture of the top layer                                                          | 68 |

| Figure 64. Picture of the bottom layer                                                       | 69 |

| Figure 65. Impedance transformer top copper layer                                            | 70 |

| Figure 66. Impedance transformer bottom copper layer                                         | 70 |

| Figure 67. Impedance converter top layer                                                     | 71 |

| Figure 68. Impedance converter bottom layer                                                  | 71 |

| Figure 69. S21 simulation schematic with 50 $\Omega$ load                                    |    |

| Figure 70. S21 simulation schematic with 500 $\Omega$ load                                   |    |

| Figure 71. Intermodulation simulation schematic with 50 $\Omega$ load                        | 74 |

| Figure 72. Intermodulation simulation schematic with 500 $\Omega$ load                       | 75 |

# LIST OF SYMBOLS AND ABBREVIATIONS

| ADS              | Advanced Design System                                               |

|------------------|----------------------------------------------------------------------|

| BJT              | Bipolar junction transistor                                          |

| DSP              | Digital signal processor                                             |

| DUT              | Device under test                                                    |

| IIP <sub>3</sub> | Third order input intercept point                                    |

| IP <sub>3</sub>  | Third order intercept point                                          |

| IM3              | Third order intermodulation                                          |

| IM5              | Fifth order intermodulation                                          |

| LUT              | Lookup table                                                         |

| KCL              | Kirchhoff's current law                                              |

| OIP <sub>3</sub> | Third order intermodulation output intercept point                   |

| RF               | Radio frequency                                                      |

| SPICE            | Simulation program with IC emphasis                                  |

| VNA              | Vector network analyzer                                              |

|                  |                                                                      |

| $A_F$            | current-controlled current source coefficient for the forward biased |

| 111              | source                                                               |

| $A_R$            | current-controlled current source coefficient for the reverse biased |

|                  | source                                                               |

| β                | DC current gain                                                      |

| B                | Bipolar junction transistor base                                     |

| BC               | Bipolar junction transistor base-collector interface                 |

| BE               | Bipolar junction transistor base-emitter interface                   |

| C                | Bipolar junction transistor collector                                |

| Ē                | Bipolar junction transistor emitter                                  |

| $\frac{1}{f}$    | Frequency                                                            |

| $G_T$            | Transducer power gain                                                |

| I                | Current                                                              |

| $I_B$            | Base current                                                         |

| $I_C$            | Collector current                                                    |

| $I_E$            | Emitter current                                                      |

| $I_F$            | Forward current                                                      |

| $i_L$            | Load current                                                         |

| $\overline{I_R}$ | Reverse current                                                      |

| k                | Boltzmann constant                                                   |

| q                | Elementary charge                                                    |

| $P_{1dB}$        | 1-dB compression point for power                                     |

| $P_{avg}$        | Available power                                                      |

| $P_L$            | Load power                                                           |

| P <sub>sat</sub> | Output saturation power                                              |

| R                | Resistance                                                           |

| Т                | Temperature                                                          |

| V                | Voltage                                                              |

| $V_{BE}$         | Base-emitter voltage                                                 |

| $V_{CC}$         | Positive supply voltage                                              |

| $V_{CE}$         | Collector-emitter voltage                                            |

| $V_{EE}$         | Negative supply voltage                                              |

| $V_D$            | Voltage over a diode                                                 |

| $V_{ON}$  | Diode turn-on voltage     |

|-----------|---------------------------|

| Vout      | Output voltage            |

| $V_{REF}$ | Reference voltage         |

| $V_T$     | Thermal voltage           |

| Ζ         | Impedance                 |

| $Z_0$     | Characteristics impedance |

| λ         | Wavelength                |

# 1. INTRODUCTION

Amplifiers are crucial part of everyday electronics; for instance, consumer wireless communication systems could not function without amplification. Generally, amplifiers are designed to be linear, meaning they produce an output signal that is an amplified reproduction of the waveform at the input. However, the waveform can be inadvertently altered due to nonlinear behavior of the amplifier. Consequently, a multitude of linearization techniques have been developed for correcting nonlinear behavior. [1, 2]

Each linearization method is a trade-off between the efficacy, bandwidth, adaptability, efficiency, the added complexity, and cost. Linearization methods can be divided into two subcategories, to analogue and digital linearization methods. Perhaps the best adaptability is offered by digital linearization methods as sensors combined with microprocessor enable autonomous and instantaneous control. This allows the system to adapt to changing operation conditions such as device and ambient temperatures and dropping battery voltages. Analogue linearization methods offer a varied range of advantages and disadvantages depending on the technique. Feedforward linearization offers superior linearity and theoretically limitless bandwidth at the cost of efficiency and complexity; the technique is one of the most challenging linearization techniques to implement [3]. Cartesian feedback is a more adaptable and simpler to implement but it suffers from limited bandwidth and slightly reduced linearity when compared to the feedforward linearization. If simplicity is the deciding factor, then analogue predistortion is perhaps the best choice. [4]

Predistortion is a linearization method where the signal is distorted prior to feeding to the amplifier. Amplifiers usually distort in an identifiable manner, allowing the identification of the nonlinear characteristics. If the input were to be an inverse function of the distortion, then the two distortions would effectively cancel each other out. The system output would now be linearly dependent on the input. [3]

This thesis is a part of proof of concept study where a new analogue predistortion scheme for a radio frequency (RF) bipolar junction transistor (BJT) is presented. A BJT RF amplifier is linearized by cascading a logarithmic amplifier with the BJT RF amplifier input. The logarithmic amplifier consists of a transistor connected in negative feedback with an operational amplifier. A matched pair transistor is used, the first transistor is used in the logarithmic amplifier and the second one in the BJT RF amplifier. The best degree of linearity is achieved when the transistors are identical as possible [5]. Logarithm is the inverse function of the exponential dependence experienced by the BJT, thus the distortions are canceled out. Consequently, the amplifier output should be linearly dependent on the input. The objective of the thesis is to verify the effectiveness and the viability of the linearization method by implementing the linearization scheme for a simple BJT amplifier. Prior works related to the study include a bachelor's thesis titled "High-frequency logarithmic amplifier for predistortion (in Finnish) [6]" by Olli Hytönen and at the moment of writing this thesis an unpublished scientific article "Linearization of BJT's with Logarithmic Predistortion [5]" by Olli-Pekka Lunden. Parts of the thesis heavily rely on these two works. The results obtained in this thesis will be used in the article.

First, the thesis discussed the background including linearity and other contemporary linearization methods. Next, the source of nonlinearity in BJTs is studied and the linearization scheme for the thesis is presented. The linearization scheme implementation, measurement and simulation results are examined and presented. Additionally, side projects undertaken during the thesis are briefly discussed. Lastly, practical work done during the thesis is reviewed and an assessment of the success of the thesis and possible future work is provided.

# 2. BACKGROUND

Before discussing RF amplifier linearization, we must understand the fundamentals of linearity and distortion. We will examine a couple of established linearization techniques, but predistortion will be studied more thoroughly, since it is the main topic of the thesis. Implementations of analogue predistortion will be presented alongside the underlying theory.

### 2.1 Linearity

In electronics linearity is often a desirable feature. By definition, a function is linear if it is homogeneous and additive. For instance, Ohm's law satisfies these conditions. The voltage V over a resistor is dependent on the resistance R and the current I flowing through the resistor as shown by Ohm's law

$$V = RI. \tag{1}$$

We can present voltage as a function of current by assuming the resistance to be a constant

$$V(I) = RI. (2)$$

Voltage is now expressed as a function of current. Scaling the current with an arbitrary factor a we get obtain the following function

$$V(aI) = R(aI) = aRI = aV(I).$$

(3)

This satisfies the homogeneity condition, as scaling the current with factor *a* directly scales the voltage with the same factor. A sum of two currents,  $I_1 + I_2$  flowing to a resistor results in the subsequent formula

$$V(I_1 + I_2) = R(I_1 + I_2) = RI_1 + RI_2 = V(I_1) + V(I_2).$$

(4)

Additivity is clearly observed in (4). As a consequence of satisfying these conditions, linear functions adhere to the superposition principle. If a function is linear, then a plot of the function is a straight line that passes through the origin. We fall back on Ohm's law again to demonstrate this. Let us choose an arbitrary fixes resistance value of 50  $\Omega$  and plot the current as a function of voltage. [7]

Figure 1. Current through a 50  $\Omega$  linear resistor as a function of voltage.

With a fixed arbitrary resistance value, the resulting plot of (2) is straight line as shown in Figure 1. The same applies for other linear approximations, when the relationship between different quantities is plotted, the resulting graph is always a straight line.

Generally, these factors make linearity a desirable feature in electronics. Linear systems enjoy a high degree of predictability due to output being directly related to input. In addition, nonlinear distortion is absent in linear systems. But the reality is more complicated, most, if not all systems exhibit nonlinear behavior to a certain degree. Once again, let us utilize a resistor and Ohm's law as an example. Earlier we claimed the resistance R is a constant. However, when current flows through a resistor, it heats up and a change in resistance is observed. Therefore, voltage over a resistive element is not only dependent on current and a constant resistance as Ohm's law dictates. Nonetheless, in most cases temperature has a negligible effect on the resistance and thus the Ohm's law is accurate enough linear approximation of reality. [7]

Linear systems are not wholly exempt from distortion, but first we must define distortion before we delve into this. Distortion is described as "the act of twisting or altering something out of its true, natural, or original state" [8]. Let us consider a two-port amplifier as an example, where one port is the input and the other is the output. If the waveform of the output is not a replica of the waveform present at the input, then the signal is distorted. Distortion itself is divided into two categories, nonlinear distortion and linear distortion. Linear systems are susceptible to the latter, as the output can be linearly dependent on the input and distorted at the same time. For instance, if a square wave input were applied, then the waveform might experience linear change due to linear filtering [9]. Nonlinear distortion is more varied, since all waveform deformations that are not linearly dependent on the input are included in this category. Additionally, nonlinear distortion can generate new frequency content. In the next chapter we will examine nonlinearity and its effects, especially intermodulation distortion. [10]

#### 2.2 Consequences of nonlinearity

Systems that inherently exhibit strong nonlinear behavior do not have an accurate linear approximation for the entirety of the operation range. This type of system is called a non-linear system. To illustrate how nonlinear behavior might look like, we will examine a DC characteristics of a BJT shown in Figure 2. [11]

Figure 2. HFA3134 BJT characteristics curve. Modified from [12].

The relationship between current and voltage is now more complicated. There are three distinct regions in the Figure. In each region the relationship between collector current  $I_C$  and collector to emitter voltage  $V_{CE}$  is different. The regions are highlighted in the Figure: cut-off region is highlighted with red, active region is highlighted with green and the blue highlights saturation region. In the cut-off region the current remains at zero despite the voltage. The opposite applies for the saturation region, depending on the base current  $I_B$ , a small increase in  $V_{CE}$  results in huge increase in  $I_C$ . Nonetheless, the curves appear to be linear in certain areas. If only a limited part of the operation range is examined, then the device seems to exhibit linear behavior, hence linear approximation is viable in these regions. However, the prior example was limited in scope and depth. A whole host of different nonlinearities manifest, when other variable dependencies considered. Depending on the system, the consequences of nonlinear behavior vary. [13]

Distortion may cause loss of data or otherwise degrade the overall performance. To illustrate this point, we will examine amplifiers and a few common types of nonlinearities afflicting them. Ideally an amplifier should provide a constant gain regardless of the input power. However, at higher input power levels, the device is pushed into nonlinear region. Consequently, the output is distorted. This phenomenon is known as gain compression. Figure 3 illustrates this behavior. [14]

Figure 3. Gain compression. [14]

The dashed line is the ideal gain and the solid line is the actual gain. The maximum output power achieved by the amplifier is expressed by output saturation power  $P_{SAT}$  that is determined from the point where the gain plateaus. Another parameter shown in the graph is the 1-dB compression point  $P_{1dB}$ . The parameter is used as figure of merit to describe the linearity of the device. The point itself is given by the location in the graph where the difference between the extrapolated ideal gain and the actual gain is 1 dB. Operating past  $P_{1dB}$  decreases gain and introduces distortion. [14]

Intermodulation distortion is a consequence of nonlinearity. This occurs when there are two or more frequencies present at the input of a nonlinear device. The two frequencies  $f_1$  and  $f_2$  mix and create intermodulation products with different frequencies. The product frequencies are  $|Nf_1 + Mf_2|$ , where N and M are positive or negative integers, including zero. The order of an intermodulation product is defined as |N| + |M|. The odd order products are especially detrimental if the frequencies are within a range where the amplifier provides a constant gain. Intermodulation orders and their respective products are compiled up to the fifth order in table 1. Note, the table does not contain all the products for each order. [15]

Table 1. Intermodulation products for the first five orders. [15, 16]

| Order                 | Intermodul                 | Comments                        |                    |

|-----------------------|----------------------------|---------------------------------|--------------------|

| 1 <sup>st</sup> Order | $f_1$                      | $f_2$                           | Fundamental        |

| 2 <sup>nd</sup> Order | $f_1 + f_2$                | $f_2 - f_1$                     | Sum and difference |

| 3 <sup>rd</sup> Order | $2f_1 - f_2 = 2f_2 - f_2$  | $1  2f_1 + f_2  2f_2 + f_1$     | Primary concern    |

| 4 <sup>th</sup> Order | $2f_2 + 2f_1$              | $2f_2 - 2f_1$                   | Not of concern     |

| 5 <sup>th</sup> Order | $3f_1 - 2f_2  3f_2 - 2f_3$ | $f_1  3f_1 + 2f_2  3f_2 + 2f_2$ | Secondary concern  |

The bolded products in the table are of interest as they are close to the fundamental frequencies. Consequently, filtering the undesired response is difficult. As an example, we study how intermodulation affects a certain nonlinear low power amplifier through two-tone intermodulation test results shown in Figure 4. [14]

Figure 4. Intermodulation measurement results for a nonlinear low power amplifier.

Input frequencies are 3.3 MHz and 3.4 MHz. The intermodulation products are found evenly spaced at both sides of the input frequencies. The distance between the fundamental frequency and the closest third order intermodulation distortion (IM3) peak is only 100 kHz. The fifth order intermodulation distortion (IM5) products are farther away, the distance being 200 kHz. Filtering the distortion would be difficult and costly as a highly selective bandpass filter is required. If the device is to operate at multiple frequencies, then filtering might not be feasible or cost-effective. The additional frequency content generated by intermodulation is detrimental to device operation [14]. Spectral regrowth is a consequence of intermodulation; the phenomena is illustrated in Figure 5.

Figure 5. Spectral regrowth. [14]

The intermodulation products are interfering with the adjacent channels, reducing signal quality or in worst case, completely blocking the channel. Additionally, modulation may be affected by spectral regrowth, potentially resulting in loss of information. The relationship between input power and third order intermodulation products are shown in Figure 6. [14]

Figure 6. Third order intercept point (IP<sub>3</sub>). Modified from [14].

IM3 becomes visible, when the device operates in the compression regime. Increasing input power beyond the 1-dB compression point results in accelerated growth of IM3. The slope of IM3 is 3:1 whereas fundamental carriers have a slope of 1:1. Therefore, after a certain point IM3 could be expected surpass the fundamental carrier. However, the distortion power plateaus due to compression before it surpasses the fundamental carrier. Nonetheless, a theoretical intercept point can be determined by performing linear extrapolation for both curves. The point where the extrapolated lines cross is called the third order intercept point IP<sub>3</sub>. Similarly to P<sub>1dB</sub>, IP<sub>3</sub> is also a measure of linearity. [14]

Accurate predicting of intermodulation distortion in amplifiers can prove challenging as they do not always adhere to static characteristics. Amplifiers also have dynamic characteristics that affect distortion, causing deviation from static models. The past device states influence the device behavior; the effects ranging from changes in distortion phase and amplitude to shift in frequency. This type of dynamic deviation is known as the memory effect. Self-heating and nonconstant impedances are common sources of memory effects [17]. [18]

#### 2.3 RF amplifier linearization methods

Linearization itself is defined as a process for making a system more linear. Theoretically this should help mitigate nonlinear distortion [4]. We will study a couple of commonplace linearization techniques for RF amplifiers, including power back-off, feedforward, Cartesian Feedback and predistortion. The feasibility of a linearization method depends on the application. Wireless devices usually require high efficiency due to limited battery life [19]. On the other hand, linearity is crucial in base stations [19]. Increased linearity usually comes at a price; usually in form of decreased efficiency and increased complexity and cost [17].

It is crucial that we understand what efficiency means in the context of the thesis, before we can evaluate different linearization methods. Efficiency  $\eta$  is defined as the ratio of output RF power P<sub>OUT</sub> and the DC power P<sub>DC</sub> drawn by an amplifier

$$\eta = \frac{P_{OUT}}{P_{DC}}.$$

(5)

The more DC power is converted to RF power, the higher the efficiency. Linearization usually decreases efficiency as more power is required for the linearization process. [17]

#### 2.3.1 Power back-off

An attentive reader might have inferred that external linearization circuitry might not always be an absolute necessity. What if the operation point is moved from the saturation regime to the linear region. This method is termed power back-off and it ranks as one of the most rudimentary linearization processes. The concept of power back-off is illustrated in Figure 7. [4]

Figure 7. Power Back-off for RF amplifier. Modified from [14].

The operation point is moved from the nonlinear compression regime to a point in the curve where the behavior is still linear. The point is marked as  $P_{LIN}$  in the graph. The device now operates in more linear fashion. Another option to achieve the same result is by using a more expensive high-power amplifier. The main advantage is that external linearization circuitry is not needed. Nonetheless, power back-off is not always feasible. The amplifier is underutilized and hence the power efficiency is low. Employing this technique in wireless applications would mean considerably shorter battery life. Therefore, external linearization circuits are required if both, high degree of linearity and power efficiency are desired. [4]

#### 2.3.2 Feedforward linearization

Feedforward linearization offers a high degree of linearity regardless of the frequency and bandwidth. The technique is based on signal splitting and coupling. A simplified feedforward linearization architecture for a RF amplifier is shown in Figure 8. [3]

Figure 8. Two tone intermodulation with feedforward linearization. [3]

The scheme consists of two loops. A waveform that only contains the intermodulation distortion components generated by the amplifier is created in the first loop. In the second loop, the waveform is scaled and subtracted from the amplifier output, cancelling out the distortion. By utilizing feedforward linearization, it is possible to negate all the nonlinear effects. In addition, the architecture is open loop, hence the scheme is unconditionally stable regardless of frequency and bandwidth. However, feedforward linearization suffers from two significant drawbacks. The total power consumption is effectively doubled by the additional amplifier. The scheme is complex and difficult to implement. Figure 8 does not include the necessary gain and phase adjustment blocks. The linearization fails if the distortion waveform and the amplifier output are out of phase or have different power levels. Realtime phase and gain adjustments are necessary, since they are affected by changes in operating conditions. [3]

#### 2.3.3 Cartesian feedback loop

While feedback linearization is simple and effective, it has flaws that make it unsuitable for RF application. Stability and reduction in bandwidth are major issues due to the delays introduced by the feedback loop [3]. Hence, Cartesian Feedback Loop has been developed. The issues with bandwidth and frequency are circumvented by downconverting the signals in the loop. There are two separate indirect feedback loops, one for the in-phase (I) and another for the quadrature (Q) component of the signal. A simplified Cartesian Feedback Loop scheme is shown in Figure 9. [4]

Figure 9. Simplified Cartesian Loop architecture. [3]

The feedback signal is demodulated by an I/Q demodulator, splitting the distorted signal into in-phase I' and quadrature Q' components. The input is split to I and Q signals that are fed alongside I' and Q' components from the feedback loops into differential amplifiers. The signals are compared and amplified by the differential amplifiers, resulting in amplified error signals. These signals upconverted and are fed back to the main loop, forcing a linear response. Despite the improved stability and bandwidth, Cartesian Feedback is still limited to narrowband applications. Nonetheless, Cartesian feedback is more straightforward and power efficient when compared to feedforward linearization. [4]

## 2.4 Predistortion

Predistortion is a linearization technique where the amplifier input is distorted so that the amplifier distortion is cancelled. This can be achieved by cascading a distorter that produces an inverse function of the distortion with the distorting amplifier. However, you need to know the distortion function before implementing a predistortion scheme, thus a model for the amplifier is required. Fortunately, finding the relationship between the amplifier input and output is enough to construct a black box behavioral model for the amplifier. [19]

Predistortion is intrinsically an open-loop linearization technique, allowing wider operating bandwidth. The method is not inherently adaptable as environmental effects and component aging are not considered. At the cost of simplicity, adaptability can be improved by employing feedback loops; this is known as dynamic or adaptive predistortion. Predistortion is divided into two main categories: analogue predistortion and digital predistortion. [19]

## 2.4.1 Digital predistortion

Digital predistortion is usually more suitable for adaptive control. Consequently, digital predistortion implementations able to cope with changes in the response better than their analogue counterparts. The inclusion of a digital signal processor (DSP) allows simultaneous implementation of multiple linearization methods. For example, digital predistortion can be coupled with Cartesian Feedback, further improving linearity. This is known as digital baseband adaptive predistortion. The architecture is shown in Figure 10. [3, 9]

Figure 10. Digital baseband adaptive predistortion. Modified from [3].

The input is converted from analogue to digital and fed to the DSP alongside the feedback signal, enabling error correction. This mitigates the adverse effects on linearization introduced by component aging and environmental factors. The predistortion element is in the lookup table (LUT) contains a behavior model for the amplifier. The I and Q parts of the signal are converted back to analogue and fed to the amplifier. The DSP can also be utilized to deal with possible memory effects. The bandwidth and the operation frequency are limited by the Cartesian Loop and DSP. Nonetheless, baseband distortion techniques are viable in wideband applications. Digital baseband predistortion is often low cost, more easily implemented and has a higher power efficiency when compared to feedforward linearization. [3, 9]

## 2.4.2 Analogue predistortion

Excluding power back-off, analogue predistortion is currently perhaps the simplest linearization technique. For instance, a series diode and a parallel capacitor constitute a rudimentary predistorter [19]. Unfortunately, not every analogue predistortion scheme readily lend themselves to adaptive control. Additionally, analogue predistortion is much more application specific. Nonetheless, analogue predistortion is still, to this date, a viable approach for linearization. Bandwidth and power are practically only limited by the analogue components. Consequently, analogue predistortion is suitable for wide bandwidth and high-power applications. Furthermore, analogue predistortion generally has a low cost and complexity of implementation. [3, 9]

## 2.5 Analogue predistortion Implementations

The design of an analogue predistortion scheme varies greatly depending on the application. Consequently, analogue predistortion implementations are diverse. To illustrate this point, we will go through three different proposed and implemented analogue predistortion schemes.

## 2.5.1 A wideband analog predistortion power amplifier with multi-branch nonlinear path for memory-effect compensation

Normally amplifiers are designed to exhibit the least possible amount of memory effects. However, when an amplifier operates with wideband signals, mitigating memory effects becomes a difficult task. Conventional analogue predistorters are not able to cancel distortion effectively due to memory effects that occur with wideband signals. Therefore, the authors of the article [20] have proposed and implemented an analogue predistortion scheme that is able to compensate for memory effects. A proposed analogue predistortion scheme is shown in Figure 11. [20]

Figure 11. Multi-branch analogue predistortion schematic. [20]

There are two main paths in the scheme, a linear path and a nonlinear path that is splits into three branches. The two additional paths help mitigate memory effects. Both, the linear and nonlinear paths have a delay line to compensate for possible phase differences. Further amplitude and phase adjustments are done with an attenuator and a phase shifter. The memory effect compensating paths have additional variable  $\Delta \tau$  in the delay line. The variable is used to either to shorten to lengthen the delay experienced in the path. By controlling the variable, the memory effects can be compensated for. It is possible to improve the design and thus the linearity by adding additional nonlinear paths with different relation to  $\Delta \tau$ .[20]

## 2.5.2 Analog pre-distortion circuit for radio over fiber transmission

Compared to the last analogue predistortion example, the linearization method proposed in this article [21] is substantially less complex. The scheme is meant for radio over fiber systems and is designed to suppress third and fifth order intermodulation distortion. Broadband Schottky diodes function as the distorting elements; they are located in two separate branches in an anti-parallel configuration. A schematic for the scheme is shown in Figure 12. [21]

Figure 12. Predistortion circuit for radio over fiber systems. [21]

The even order distortions generated by the Schottky diodes are almost completely suppressed thanks to the push-pull configuration. Series resistors in conjunction with a DC power supply bias the current that passes through the diodes. The power supply is connected to the test points, only one power supply is required for operation. The inductors and capacitors in the circuit function as a bias tee, so the DC bias does not interfere with the RF signal and vice versa. A power divider splits the RF input signal into the both branches. This linearization scheme is simple and has low power consumption and cost implementation. [21]

## 2.5.3 An E-BAND analog predistorter and power amplifier MMIC chipset

This predistortion scheme [22] meant for high frequency and wide bandwidth applications; the circuit is only designed to suppress IM3. The design consists of two branches: a linear branch and a nonlinear branch. A class C error amplifier functions as the distorter. The schematic for the predistorter is shown in Figure 13.[22]

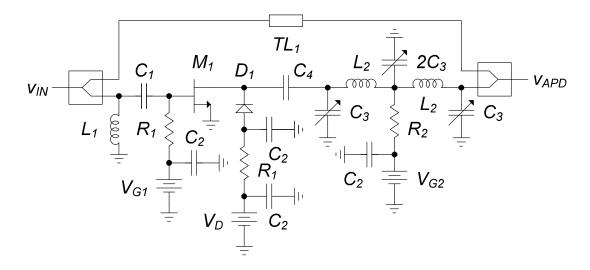

Figure 13. E-Band analogue predistorter schematic. [22]

The input and output both have an integrated Wilkinson power divider, for splitting the signal at the input and for combining at the output. Due to the high operating frequency, the dividers are realized with quarter wave transformer transmission lines. The linear path consists only of a transmission line to match the delays. To further ensure a matched delay, a variable delay line is included in the nonlinear path. The variable delay line is made of pi-section transmission lines constituting of varactors  $C_3$  and inductors  $L_2$ . The phase in the delay line is controlled by  $V_{G2}$ . The third order predistortion coefficient is controlled by the error amplifier transistor gate bias  $V_{G1}$ . By adjusting  $V_{G1}$  and  $V_{G2}$  it is possible to adapt to outside factors such as changes in environmental temperature. However, it must be done manually due to the open-loop structure of the scheme. [22]

# 3. PREDISTORTION SCHEME

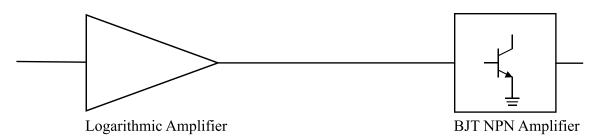

In the thesis, a logarithmic amplifier is used to linearize a BJT RF amplifier. The linearization technique is simple, the predistorter is cascaded with the amplifier. The scheme is shown in Figure 14.

Figure 14. Thesis predistortion scheme.

It is critical to understand the source of nonlinearity in BJTs, before the predistortion scheme is discussed. Furthermore, understanding of logarithmic amplifiers is required. Therefore, Ebers-Moll model and logarithmic amplifier are examined first.

#### 3.1 Ebers-Moll model

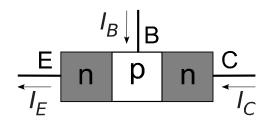

Inside a BJT, there are two pn-junctions that effectively behave as diodes. The junctions are formed in between the three terminals, base B, collector C and emitter E. A simplified npn BJT is shown in Figure 15. Current directions are also shown in the figure: collector current is  $I_C$ , base current is  $I_B$  and emitter current is  $I_E$ . [23]

Figure 15. npn BJT consist of n and p-type semiconductor materials.

The pn-junctions are formed at the base-emitter (BE) and base-collector (BC) interfaces. As an electronic device, diode is nonlinear by nature. The current-voltage relationship in a pn-junction follows the Shockley-equation [13]. The current  $I_F$  flowing through the base-emitter pn-junction diode is expressed as the product of the reverse saturation current  $I_{SF}$  and an exponential function involving the voltage over the diode  $V_D$ , thermal voltage  $V_T$  and the ideality factor n

$$I_F = I_{SF}(e^{\frac{V_D}{nV_T}} - 1).$$

(6)

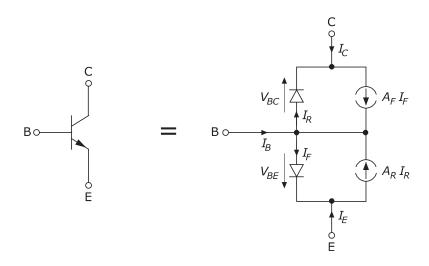

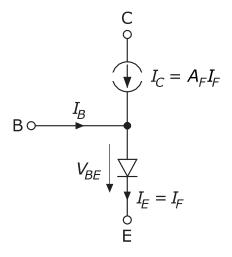

BJTs experience exponential dependence between voltage and current due to the pn-junctions as shown by (6). Ebers-Moll model describes a BJT as a circuit model. The model consists of two diodes that are connected back to back. The diodes represent base-emitter (BE) and base-collector (BC) pn-junctions. The base current is modelled by two currentcontrolled current sources and the currents  $I_R$  and  $I_F$ . One of the sources models the forward-biased operation and another one models the reverse-biased operation. The sources also have their own respective controlling coefficients,  $A_F$  for forward current  $I_F$  and  $A_R$ for the reverse current  $I_R$ . Ebers-Moll model for a npn BJT is shown in Figure 16. [23]

Figure 16. NPN BJT Ebers-Moll model. Modified from [23].

The currents can be expressed with the help of (6) and Kirchhoff's Current Law (KCL). The reverse current can be determined with (6) when applied to BC pn-junction

$$I_R = I_{SR} \left( e^{\frac{V_{BC}}{nV_T}} - 1 \right). \tag{7}$$

The forward current has similar relationship with the BE pn-junction

$$I_F = I_{SF} (e^{\frac{V_{BE}}{nV_T}} - 1).$$

(8)

With KCL and equation (6) the collector and emitter currents are expressed as follows

$$I_{C} = A_{F}I_{SF}\left(e^{\frac{V_{BE}}{nV_{T}}} - 1\right) - I_{SR}\left(e^{\frac{V_{BC}}{nV_{T}}} - 1\right) = A_{F}I_{F} - I_{R}$$

(9)

$$I_E = A_R I_{SR} \left( e^{\frac{V_{BC}}{nV_T}} - 1 \right) - I_{SF} \left( e^{\frac{V_{BE}}{nV_T}} - 1 \right) = A_R I_R - I_F.$$

(10)

In forwards biased mode the current flows to the emitter, whereas in the reverse-biased mode, the current flows to the collector. Since in the thesis we are using the BJT as an amplifier, the device operates in forward-biased mode. In this mode  $V_{\text{BE}} > 0$  and  $V_{BC} < 0$ .

Diodes have a turn-on voltage  $V_{ON}$  that is usually in range of 0.7V; if this voltage is not exceeded, then the junction is not conducting. Consequently, in the forward-biased mode the BE pn-junction conducts, while practically no current flows through the BC pn-junction

$$I_R \approx I_{SR} \approx 0. \tag{11}$$

This reduces the model to the state shown in Figure 17. [13, 23]

Figure 17. Reduced Ebers-Moll model for forward biased operation. Modified from [23].

Analyzing currents and voltages is now easier as we can ignore the BC pn-junction and the reverse biased source. However, this model only applies when the transistor is operating in the active region (Figure 2). The equations are simplified to

$$I_C = A_F I_{SF} \left( e^{\frac{V_{BE}}{nV_T}} - 1 \right) = A_F I_F \tag{12}$$

$$I_E = I_{SF} \left( e^{\frac{V_{BE}}{nV_T}} - 1 \right) = I_F.$$

$$\tag{13}$$

The current-controlled current source coefficient for the forward biased source  $A_F$  is the ratio of the collector and emitter currents

$$A_F = \frac{I_C}{I_E}.$$

(14)

The emitter current in this mode of operation is the sum of the currents flowing through the base and collector

$$I_E = I_B + I_C. ag{15}$$

The two base and collector currents are related by the DC current gain  $\beta$  that is typically in the range of hundreds

$$I_C = \beta I_B. \tag{16}$$

The relationship between  $A_F$  and  $\beta$  derived with the help of (14), (15) and (16), by first solving  $I_E$  from (14)

$$I_E = \frac{I_C}{A_F}.$$

(17)

Next,  $I_E$  is related to  $A_F$  and  $I_C$  by using (15) and (17)

$$I_B = I_E - I_C = \frac{I_C}{A_F} - I_C = \frac{I_C - A_F I_C}{A_F} = I_C \frac{(1 - A_F)}{A_F}.$$

(18)

Finally, we can relate  $\beta$  to  $A_F$  by substituting (18) to (16) and by solving  $\beta$

$$\beta = \frac{I_C}{I_B} = \frac{I_C}{I_C \frac{(1-A_F)}{A_F}} = \frac{A_F}{1-A_F}.$$

(19)

In forward operation  $A_F$  is a constant, since  $I_E$  is the sum of  $I_B$  and  $I_C$ ,  $A_F$  is slightly smaller than 1. Additionally,  $\beta \gg 1$ , hence

$$I_C \gg I_B. \tag{20}$$

When (20) holds true, a gross simplification is possible in terms of emitter current:

$$I_E = I_{SF} \left( e^{\frac{V_{BE}}{nV_T}} - 1 \right) \approx I_C$$

(21)

These simplifications make the analysis of a BJT considerably simpler. The exponential dependence is still present despite the simplifications. However, the model only applies when the device operates in the active region. With low DC operating point and high signal level, the instantaneous operation point swings out of the active region, rendering the model inaccurate. [23]

#### 3.2 Logarithmic amplifier

Logarithmic amplifier is a nonlinear device by design; the amplifier output relates to the input logarithmically. First, we are going to examine a negative logarithmic amplifier and afterwards, a positive logarithmic amplifier. A component that exhibits logarithmic behavior is required. Conveniently, a pn-junction exhibits logarithmic behavior when examined in terms of junction voltage:

$$\frac{I_F}{I_{SF}} = e^{\frac{V_D}{nV_T}} - 1 \tag{22}$$

By rearranging the terms and taking a logarithm of each side we can solve the voltage over the junction

$$\ln(\frac{I_F}{I_{SF}} + 1) = \ln(e^{\frac{V_D}{nV_T}}).$$

(23)

The above equations ultimately simplifies to

$$V_D = nV_T \ln\left(\frac{I_F}{I_{SF}} + 1\right). \tag{24}$$

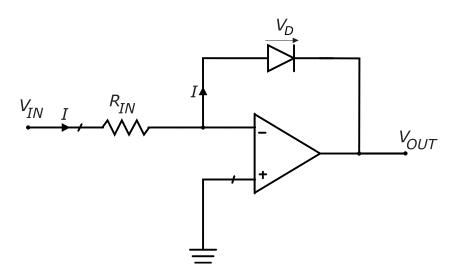

A logarithmic amplifier can consist of an operational amplifier and a diode that is connected as negative feedback element. The circuit is shown in Figure 18. [24]

Figure 18. A negative logarithmic amplifier.

The operational amplifier attempts to keep the potential difference between the positive and negative inputs at zero, thus a virtual ground forms at the negative input. We can assume that practically all input current flows through the feedback loop as operational amplifiers have high input impedance, often in range of megaohms. Only a negligible amount of current leaks through the negative input. The anode is at greater potential than the cathode, hence the operational amplifier drives an output voltage  $V_{\text{OUT}}$ . Due to the

virtual ground, the amplifier drives equal but opposite voltage to the voltage over the diode  $V_D$

$$V_{OUT} = -V_D. (25)$$

$V_D$  can be determined with (24) and KCL. Conveniently, the current is the same through the resistor and the diode. Subsequently, Ohm's law can be applied to (24) in addition to (25)

$$V_{OUT} = -nV_T \ln\left(\frac{V_{IN}}{R_{IN}I_{SF}} + 1\right).$$

<sup>(26)</sup>

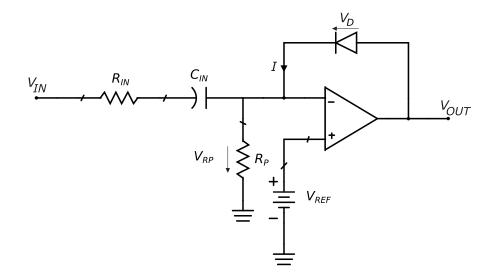

The circuit can be converted into a positive logarithmic amplifier [6]. [24]

Figure 19. Positive logarithmic amplifier.

Three new components have been incorporated to the design, a DC-block capacitor  $C_{IN}$ , a reference DC-voltage source  $V_{REF}$  and a resistor  $R_P$ . Additionally, the cathode is now connected to the negative input and the anode to the output. Due to these changes, the direction of the current is now different than in Figure 18. The operational amplifier attempts to keep the potential difference between the inputs at zero. Consequently, the amplifier drives a DC-voltage equal to the reference voltage  $V_{REF}$  at the negative input.

$$V_{REF} = V_{+} = V_{-}.$$

(27)

The reference voltage sets the operating point of the logarithmic amplifier. All the DCcurrent flows through  $R_P$ ; as no DC-current passes through  $C_{IN}$  and the operational amplifier. Subsequently, the voltage  $V_{RP}$  over  $R_P$  is also equal to the reference voltage

$$V_{RP} = V_{REF}.$$

(28)

The AC-current flows through the input resistance  $R_{IN}$  and the diode, influencing the operating point set by  $V_{REF}$ . The input AC-current is equal but opposite to the diode current

$$I_{IN} = \frac{V_{IN} - V_{REF}}{R_{IN}} = -I_F$$

(29)

By utilizing KCL, we can determine the output voltage

$$V_{OUT} = V_D + V_{REF}.$$

(30)

Substituting (24) and (29) to (30) confirms the positive logarithmic dependence

$$V_{OUT} = nV_T \ln\left(\frac{I_F}{I_{SF}}\right) + V_{REF} = nV_T \ln\left(\frac{V_{REF} - V_{IN}}{R_{IN}I_{SF}} + 1\right) + V_{REF}.$$

(31)

However, the logarithm is finite and real only if the term  $\frac{V_{REF}-V_{IN}}{R_{IN}I_{SF}}$  is greater than -1. Otherwise, the operational amplifier will saturate to supply voltage due to the logarithmic function approaching negative infinite. Consequently, the output is severely distorted. This can be avoided by increasing  $V_{REF}$  as this only occurs when the negative AC-voltage is exceeds the DC voltage. [6]

The diode in the logarithmic amplifier can be replaced with a transistor. Diode has a limited logarithmic dependence; ohmic resistance and temperature dependence are of concern, more so than with a transistor unless a costly "log diode" is used [24]. The logarithmic dependence may not be accurate with great input voltage variations, for instance if the input varies from picovolts to millivolts. A change in the temperature influences the thermal voltage  $V_T$ , affecting the response of the amplifier.  $V_T$  is product of the Boltzmann constant k and the temperature T divided by the elementary charge q

$$V_T = \frac{kT}{q}.$$

(32)

The reverse saturation current is also affected by the ambient and device temperatures. Transistors suffer from these issues to a lesser extent. Being three port devices, a wider array of configurations are available; allowing more specialized logarithmic amplifier implementations. As an additional benefit, transistors lend themselves more readily to different temperature compensation circuits. However, transistors are capable of amplifying signals. Consequently, stability issues may arise. In addition, compared to diodes, transistors are not as robust. At higher signal levels, a transistor might get damaged or destroyed. [6]

## 3.3 RF BJT amplifier linearization using an analogue predistortion logarithmic amplifier

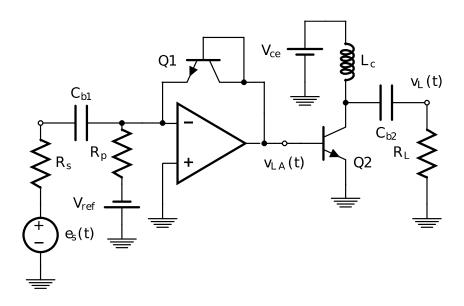

The initial proposed linearization scheme is shown in Figure 20. The logarithmic amplifier is similar to the one in Figure 19, the main differences being the diode-connected transistor, the location of the reference source. Now, the positive input is grounded, and the reference source is connected to the negative input through resistor  $R_P$ . [5]

Figure 20. Proposed predistortion scheme of a BJT RF amplifier. [5]

A matched pair transistor is used [25], meaning the transistors Q1 and Q2 are almost identical. Therefore, the circuit analysis is simplified as the ideality factors and the reverse saturation currents assumed equal

$$n_1 = n_2 \tag{33}$$

$$I_{SF1} = I_{SF2}. (34)$$

The DC-current gain is also in the range of 60-250 [25] , hence the gross simplification in (21) is viable. [5]

Since the positive input is connected directly to ground, a virtual ground is formed at the negative input. We can utilize (24) to determine the base-emitter voltage for Q1. The emitter current in the equation below follows the relation shown in (21)

$$V_{BE1} = n_1 V_T \ln\left(\frac{i_{E1}}{I_{SF1}} + 1\right).$$

(35)

The operational amplifier output is directly connected to the base of the second transistor Q2. Due to the virtual ground we can assume that the base-emitter voltages are equal

$$V_{BE1} = V_{BE2}. (36)$$

The DC-currents flowing through the transistors are determined by the reference voltage and the resistor  $R_P$

$$I_{E1} = I_{C1} = I_{C2} = \frac{V_{ref}}{R_p}.$$

(37)

From (37) it becomes apparent that this linearization scheme at least doubles the current consumption, as the currents through both the transistors are equal. In addition, the operational amplifier draws quiescent current. [5]

If the BJT amplifier transistor Q2 operates in the active region, in the configuration shown in Figure 20, then the collector current can be expressed with the help of (21), (35) and (36). The earlier simplifications (33) and (34) also greatly assist with the current analysis

$$i_{c2} = I_{SF2} \left( e^{\frac{V_{BE2}}{n_2 V_T}} - 1 \right)$$

(38)

$$= I_{SF2} \left( e^{\frac{n_1 V_T \ln(\frac{i_E}{I_{SF1}} + 1)}{n_2 V_T}} - 1 \right)$$

(39)

$$= I_{SF2} \left( \frac{i_E}{I_{SF1}} + 1 - 1 \right)$$

(40)

$$=i_{E1}.$$

(41)

Only AC-current flows to the load due to the decoupling capacitor at the BJT amplifier output. Consequently, the load current is completely compromised of AC-current. Due to the RF choke inductor, the load current  $i_L$  is the negative of the collector current.

$$i_L = -i_{c2} = -i_{E1} \tag{42}$$

Q1 current AC-component is the same as the system input current due to the AC-current having no other viable path; the potentials at both ends of  $R_P$  are at constant value and the input impedance of the operational amplifier is typically in range of megaohms. The input AC-current flows through the resistor R<sub>s</sub>, no DC-current flows through the resistor due

to the decoupling capacitor at the input. Therefore, the input current can be written with the help of Ohm's law

$$i_{IN} = \frac{e_s}{R_s} = -i_{E1}.$$

(43)

Now the load voltage is

$$v_L = R_L * - \left(-\frac{e_s}{R_s}\right) = \left(\frac{R_L}{R_s}\right) e_s.$$

(44)

The gain of the linearized amplifier can be estimated by determining the transducer power gain  $G_T$ . The transducer gain in decibels is the ten times the logarithm of the ratio of the load power  $P_L$  and available power than can be drawn from the source  $P_{avg}$ :

$$G_T = 10 \log\left(\frac{P_L}{P_{avg}}\right) dB.$$

(45)

The load power can be obtained by applying (44) to the power equation:

$$P_L = V_L^2 / R_L = \frac{e_s^2 R_L}{R_s^2}$$

(46)

The available power is square of the absolute value of the input voltage divided by four times the real part of the source impedance

$$P_{avg} = \frac{e_s^2}{4R_s}.$$

(47)

Now we can determine the transducer gain as

$$G_T = 10 \log \left(\frac{\frac{e_s^2 R_L}{R_s^2}}{\frac{e_s^2}{4R_s}}\right) dB = 10 \log \left(\frac{4R_L}{R_s}\right) dB.$$

(48)

The transducer gain is only affected by the load and source impedances. Other parameters such as transistor or operational amplifier parameters have no apparent effect on the gain. In a 50  $\Omega$  system  $R_s = R_L = 50 \Omega$ , resulting in gain of  $G_T = 6$  dB. With a different load impedance  $R_L = 500 \Omega$ , the gain is  $G_T = 16$  dB.

# 4. VERIFICATION

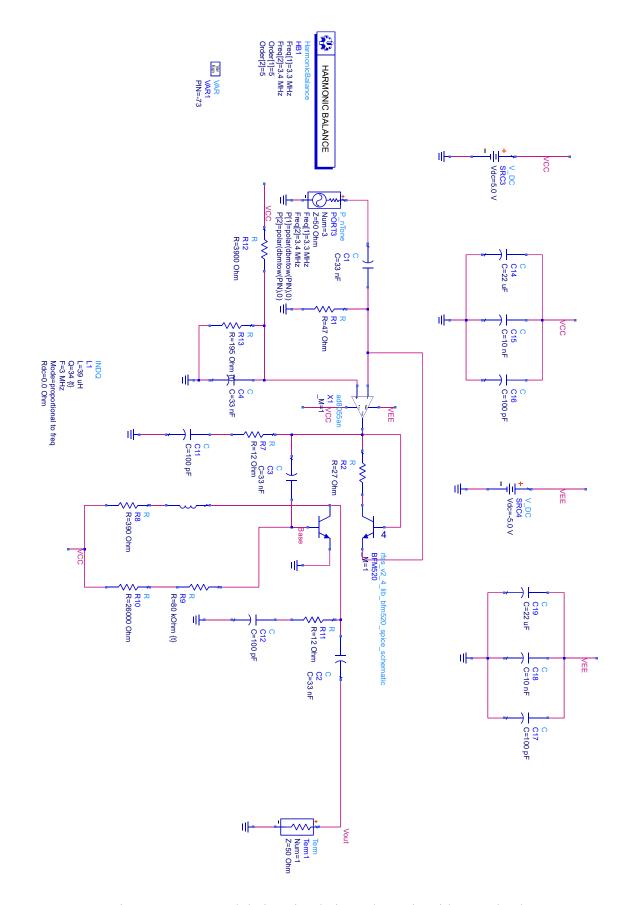

The system was implemented, and intermodulation measurements were conducted to verify the viability of the scheme. Target specifications were as follows: the system was to operate at 3 MHz, the current through both the transistors was chosen to be 5 mA, and the circuit was to be unconditionally stable. Additional side projects were also undertaken to facilitate the intermodulation measurements and measuring with different load impedances.

### 4.1 Implementation

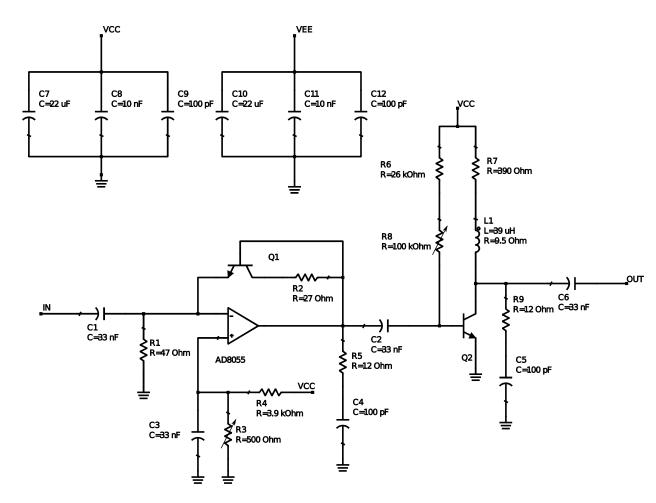

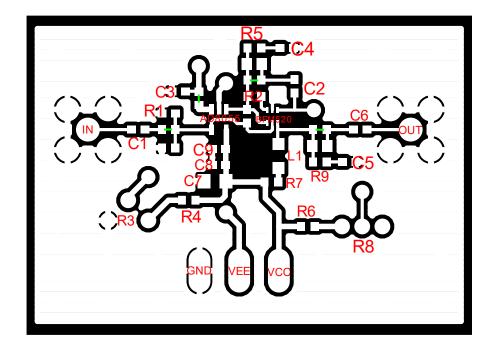

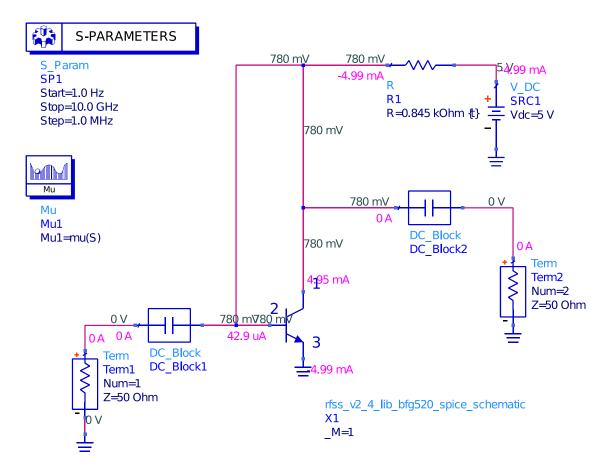

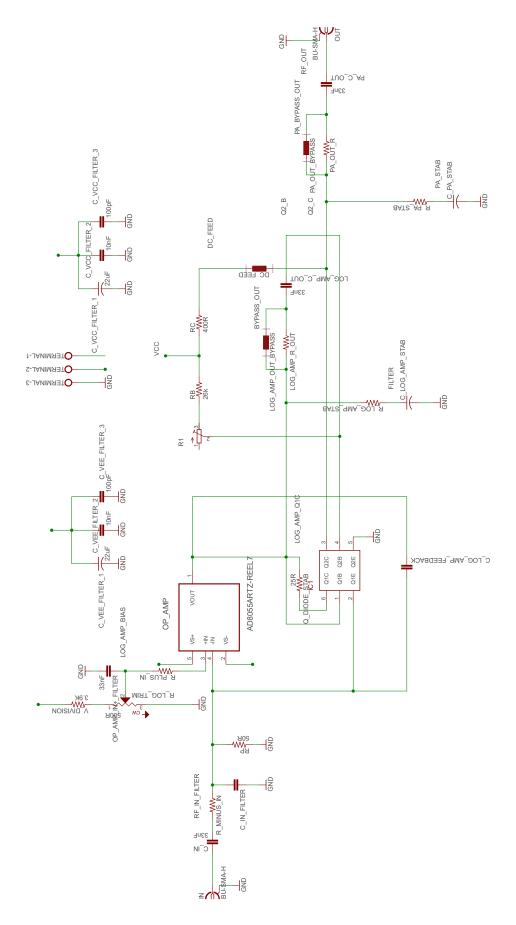

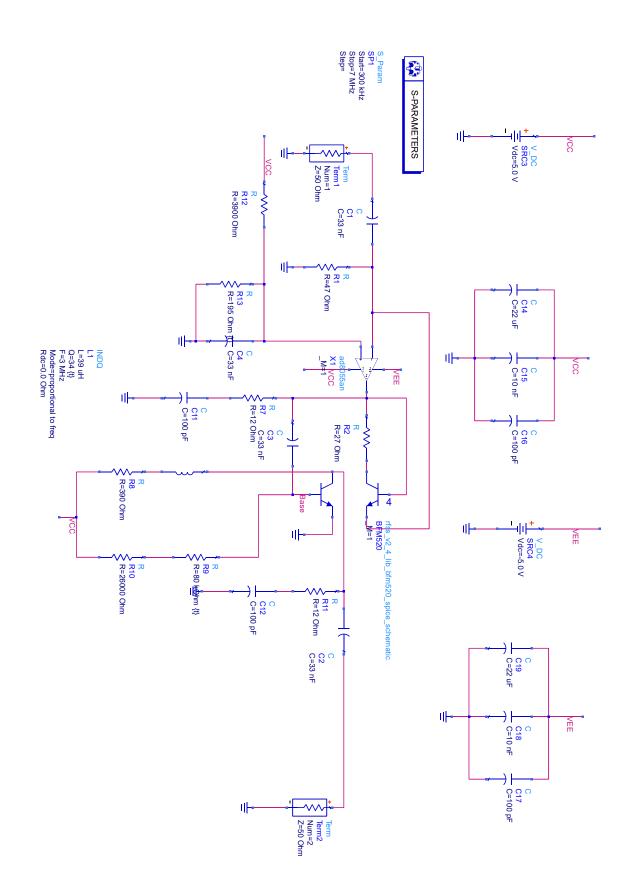

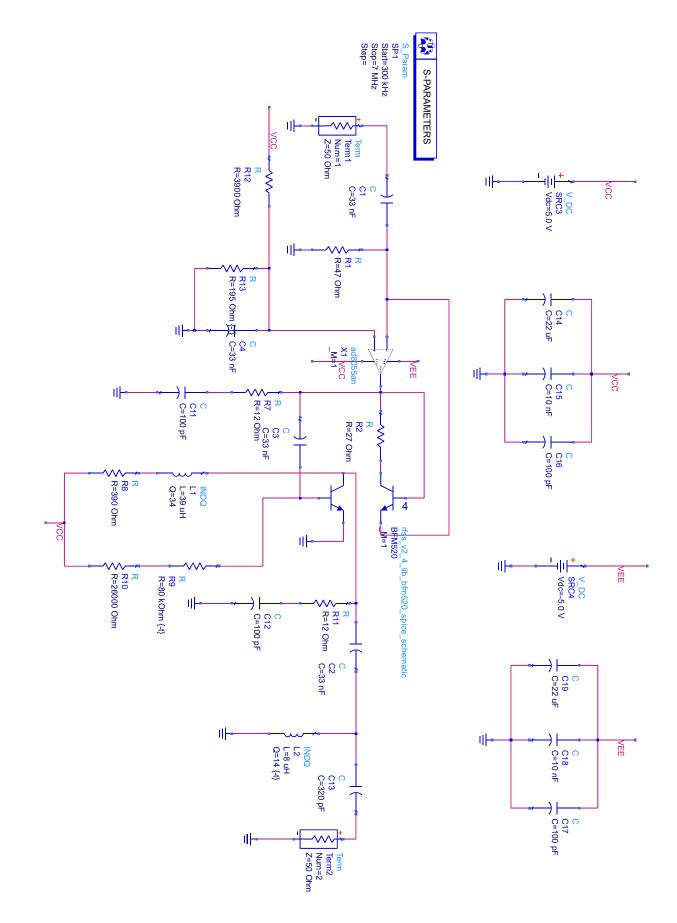

For the implementation, BFM520 [25] was chosen as the matched pair transistor and AD8055 [26] as the operational amplifier. However, changes had to be made to the original design. The final design is shown in Figure 21.

Figure 21. The final implementation of the predistortion scheme.

There are three major differences between the final and the initial designs. The BJT and logarithmic amplifier are DC-decoupled with capacitor C2, hence both amplifiers have

their own separate biasing circuitry. This approach was chosen because even though the transistors are a matched pair, they are not completely identical. Separate biasing circuitry can alleviate the situation. Furthermore, during the initial tests, it was observed that Q2 would draw current in order of hundreds of milliamps with certain logarithmic amplifier bias conditions. Absolute maximum DC collector current rating for BFM520 is 70 mA [25]. Stabilization circuitry has been incorporated to the design. Lastly, the reference source is replaced with a voltage divider circuit and moved to the positive input of the operational amplifier. Fortunately, the AC-operation is not affected as the amplifiers are DC-decoupled, thus (44) still holds true.

The operational amplifier uses dual side supply, +5 V positive supply voltage VCC and -5 V negative supply voltage VEE. Capacitors C7 – C9 filter the ripple voltage in VCC and C10 – C12 are used for VEE. For convenience, the reference voltage is supplied by a voltage divider instead of a DC-voltage source. The voltage is controlled by variable resistor *R3*

$$V_{ref} = \left(\frac{R3}{R3 + R4}\right) V_{CC}.$$

(49)

*R4* is a fixed value resistor with a resistance of 3.9 k $\Omega$ , *R3* ranges from 0  $\Omega$  to 500  $\Omega$ . The minimum reference voltage is 0 V and the maximum is 568 mV. Consequently, *I<sub>C</sub>* can range from 0 mA to 12 mA. The collector currents were chosen to be 5 mA, hence according to (37) *V*<sub>ref</sub> biased to 235 mV. For the BJT RF amplified, the Collector-emitter voltage was chosen as 3 V. *R7* biases the collector current, *R6* and *R8* bias the base current. *R8* is a variable resistor with resistance ranging from 0  $\Omega$  to 100 k $\Omega$ , allowing making changes to bias conditions on the fly. However, if the resistance *R8* is too low, then AC-current could flow to the power supply. Therefore, a fixed value 26 k $\Omega$  resistor *R6* is included. The collector resistor *R7* is only 390  $\Omega$ , thus an inductor is required at the collector. The required value for *R7* was determined with Ohm's law. *V<sub>CE</sub>* is 3 V, this leaves 2 V over the *R7* and the current through it is 5 mA:  $R7 = \frac{2 V}{5 \text{ mA}} = 400 \Omega$ . Closest available resistance value was 390  $\Omega$ . The DC-current gain for BFM520 ranges from 60 to 250, for calculations it was estimated that  $\beta$  is 120 and the *V<sub>BE</sub>* is 0.8 V [25]. These estimates were based on prior test measurements. With Ohm's law, KCL and (14) the we can determine the total base resistance *R6 + R8 (R<sub>B</sub>)* as follows

$$R_B = \frac{(V_{CC} - V_{BE})}{\frac{I_C}{\beta}} = \frac{\beta(V_{CC} - V_{BE})}{I_C} = \frac{120(5 \text{ V} - 0.8 \text{ V})}{5 \text{ mA}} = 100.8 \text{ k}\Omega,$$

(50)

therefore, *R8* should be set to 74.8 k  $\Omega$ .

Stabilization circuitry is incorporated to both the amplifiers. Resistor *R9* and a capacitor *C5* is introduced between Q2 collector and the ground. Identical circuitry is also introduced between the ground and the logarithmic amplifier output. Due to the capacitors, the circuitry does not affect the DC-biasing. Capacitance values are sufficiently low, so that the effect on the fundamental frequency is minimal. At 100 pF, the impedance of the stabilization circuitry approximately 3 k $\Omega$  is for a 3 MHz RF signal. The circuits help eliminate higher frequency spurious oscillations.

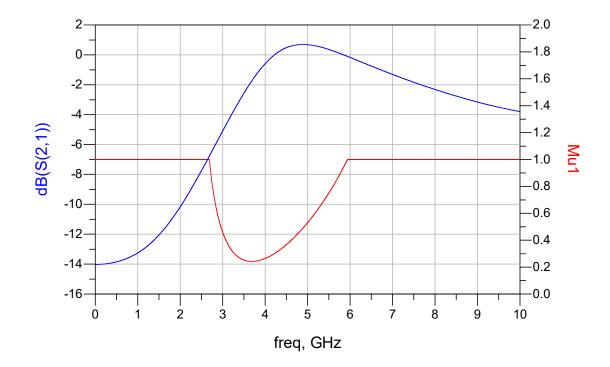

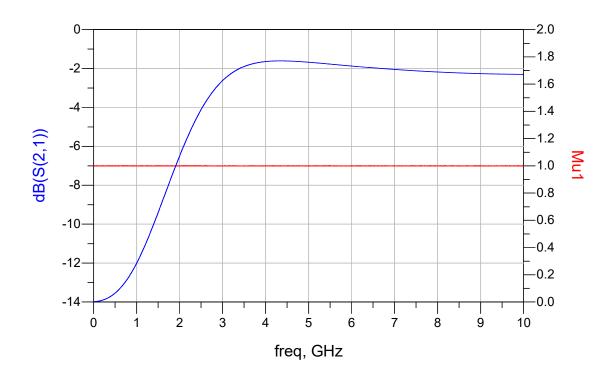

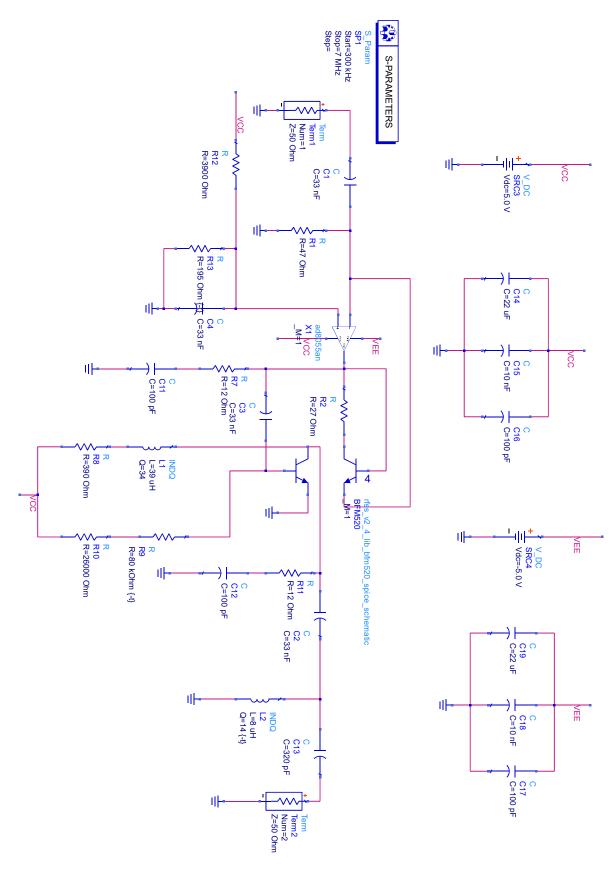

Despite the efforts to stabilize the circuit against high frequency spurious oscillations, the system persistently suffered from oscillation in the frequency range of 3 GHz – 7 GHz. During the thesis work, we found that a diode-connected transistor can have negative resistance when the transsusceptance is high. Consequently, at higher frequencies, the diode-connected transistor can be unstable. This is contrary to what is claimed in literature; according to [24] diode-connected transistors can not produce gain, thus stability is always achieved. Simulations with Advanced Design System 2017 (ADS) [27] were utilized to confirm the findings. The simulation circuits are found in APPENDIX 1. Figure 22 shows that the transistor can oscillate at higher frequencies.

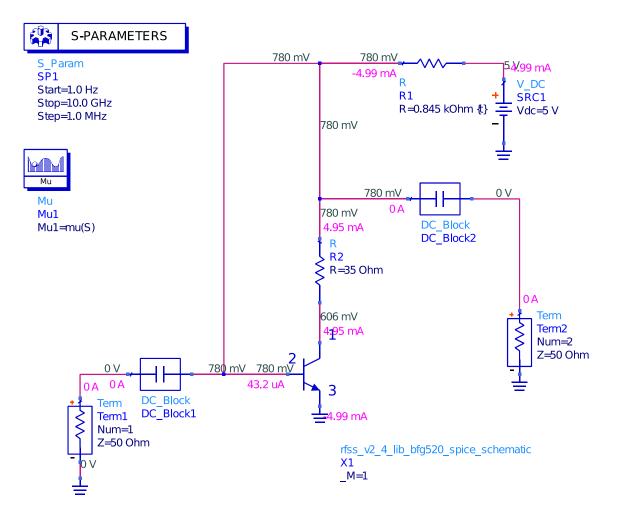

Figure 22. Simulated gain S21 and stability factor  $\mu$  (Mu) for a diode-connected transistor. The circuit amplifies from 4.2 GHz to 5.85 GHz. If  $\mu$  is below 1, then the circuit is potentially unstable.

As the frequency increases, the transistor attenuates less. At certain frequencies the transistor even amplifies the signal. To remedy the stability issue with minimal effect on the performance, 27  $\Omega$  resistor *R2* was connected in series with the collector. The simulation results for the stabilized diode-connected transistor are shown in Figure 23.

Figure 23. Simulated gain and stability factor Mu for a stabilized diode-connected transistor circuit.

The stability factor now remains at 1 regardless of the gain. In addition, the gain now does not exceed 0 dB, meaning that the transistor attenuates at all frequencies. Simulations at higher frequencies is unnecessary, since the transition frequency for BFM520 is at 9 GHz [25].