#### PETTERI LIIKKANEN

## SIGNAL INTEGRITY ENHANCEMENTS FOR AUTOMATED LPDDR4 MEMORY TESTING SYSTEM

Master of Science thesis

The examiner and topic of the thesis was approved by the Council of the Faculty of Computing and Electrical Engineering on 28 March 2018

#### **ABSTRACT**

PETTERI LIIKKANEN: Signal Integrity Enhancements for Automated LPDDR4

Memory Testing System

Tampere University of technology Master of Science Thesis, 66 pages

March 2018

Master's Degree Program in Electrical Engineering

Major: Electronics

Examiner: Professor Karri Palovuori

Keywords: LPDDR4, PoP, memory testing, ATE, signal Integrity, mobile device

Designing a smart phone requires plenty of testing, tweaking and verification to offer flawlessly functioning high-end products for the customers. Fine-tuning and verifying the memory interface between the application processor and memory, is one important area, which ensures the reliable operation of the device over different operating conditions. Automated testing process reduces the amount of manual measurements, and speeds up the development cycle of the product.

However, because of the rising bandwidth (BW) of memories, the signal integrity (SI) properties of the currently used memory testing system have begun to interfere with the device under test (DUT) by causing stability issues. Also, the measured waveforms have not been corresponding to the expected results with the latest memory modules with high data rates and clock speeds. This master's thesis combines the previous experience and research about the topic, and introduces some new techniques to improve the measurement quality and to minimize the measurement system's impact to signal properties of DUT.

The final goal is to upgrade the previously used automated memory testing system with newly developed techniques to allow good measurement quality with 4<sup>th</sup> generation low power double data rate (LPDDR4) memories. In the future, the implemented system is meant to be compatible also with upcoming LPDDR memory generations, with very slight modifications.

With implemented memory testing system, there was no more previously mentioned stability issues and measured waveforms matched well to simulations. So at the end, the system performed as expected. There was couple of observations done during the designing and testing process which could improve the system marginally even further but they were not mandatory in terms of system's operation, and could be implemented easily to next revisions of breakout *printed wiring boards* (PWB) for memories with different *ball grid array* (BGA) pinouts.

#### TIIVISTELMÄ

PETTERI LIIKKANEN: Signal Integrity Enhancements for Automated LPDDR4

Memory Testing System

Tampereen teknillinen yliopisto

Diplomityö, 66 sivua

Maaliskuu 2018

Sähkötekniikan diplomi-insinöörin tutkinto-ohjelma

Pääaine: Elektroniikka

Tarkastaja: professori Karri Palovuori

Avainsanat: LPDDR4, PoP, muistintestaus, automatisoitu mittaus, signaali,

mobiililaite

Älypuhelimen suunnittelu vaatii paljon testausta, virittelyä ja varmennusta moitteettomasti toimivien tuotteiden tarjoamiseksi asiakkaille. Prosessorin ja keskusmuistin välisen dataväylän hienosäätö ja varmennus on yksi tärkeä alue, joka varmistaa laitteen luotettavan toiminnan erilaisissa käyttöolosuhteissa. Automatisoitu testausprosessi vähentää manuaalisesti tehtävien mittausten määrää ja nopeuttaa tuotteen kehityssykliä.

Muistien kaistanleveyden kasvaessa nykyisen muistintestausjärjestelmän signaalin häiritä eheysominaisuudet ovat alkaneet testattavaa laitetta. aiheuttaen staabiliusongelmia. Myöskään viimeisimmistä, korkeilla kellotaajuuksilla datanopeuksilla toimivista muistimoduuleista mitatut aaltomuodot eivät ole vastanneet odotettuja tuloksia. Tämä diplomityö yhdistää aikaisempia kokemuksia ja tutkimusta aiheesta, ja esittelee joitakin uusia tekniikoita mittauslaadun ja mittausjärjestelmän mittaustulosta vääristävän vaikutuksen minimoimiseksi.

Lopullisena tavoitteena on parantaa aiemmin käytettyä muistintestausjärjestelmää käyttäen uusia kehitettyjä tekniikoita, jotka mahdollistavat hyvän mittauslaadun LPDDR4 muisteilla. Toteutetun järjestelmän on tarkoitus olla yhteensopiva tulevien LPDDR muistisukupolvien kanssa erittäin vähäisin muutoksin.

Toteutetun muistintestausjärjestelmän kanssa aiemmin mainittuja stabiiliusongelmia ei ollut ja mitatut aaltomuodot vastasivat hyvin simulointeja. Lopuksi järjestelmä toimi kuten oli odotettu. Suunnittelu- ja testausprosessin aikana tehtiin joitakin havaintoja, joilla järjestelmää voitaisiin parantaa edelleen marginaalisesti. Parannukset eivät kuitenkaan olleet pakollisia järjestelmän toiminnan kannalta, ja ne voidaan toteuttaa helposti seuraavien piirilevyversioiden yhteydessä piireille, joilla on erilainen BGA pinnijärjestys.

#### **PREFACE**

This Master's thesis extends the previously made research with automated mobile phone's memory measurement systems and allows the top quality measurements to continue with new LPDDR4 memories with high memory BW. The work has been done for the Baseband team in Microsoft Mobile Oy in Tampere.

I would like to thank my supervisors Jouni Karinen, Sunil John and Tomi Mäkinen from Microsoft Mobile. Also, I want to thank, Joonas Möykkynen, Markku Alkki, Lauri Nissinen, Mika Jäsberg, Markku Koistinen and Henri Eskola for valuable comments, guidance and assistance during the design process. Also the comments from Riku Ranta and Gary Horning helped a lot during the finalization process of this thesis work.

A lot of people from different teams from sites in Tampere and Salo were involved in this project without forgetting the support from my family. Everyone, involved in this project, would not fit into this page, so thank you to all, equally!

"To invent, you need a good imagination and a pile of junk"

- Thomas Edison (1847-1931)

Vaasa, 18.03.2018 Petteri Liikkanen

Karitie 14D 27 65230 Vaasa +358503449552

## **CONTENTS**

| 1. | INTF                   | 1                                           |    |  |

|----|------------------------|---------------------------------------------|----|--|

| 2. | THEORETICAL BACKGROUND |                                             |    |  |

|    | 2.1                    | Signal integrity                            | 7  |  |

|    | 2.2                    | Power integrity                             | 16 |  |

| 3. | CHA                    | RACTERIZATION OF THE PREVIOUS SYSTEM        | 19 |  |

| 4. | DES                    | 26                                          |    |  |

|    | 4.1                    | Signal integrity and timing measurement BoB | 26 |  |

|    | 4.2                    | Current consumption measurement BoB         | 32 |  |

| 5. |                        | T-PROCESSING                                |    |  |

| 6. | PRO                    | 38                                          |    |  |

|    | 6.1                    | Probing system                              | 40 |  |

|    | 6.2                    | Mechanical considerations                   | 42 |  |

|    | 6.3                    | Board on Board design                       | 43 |  |

|    |                        | The final implementation                    |    |  |

| 7. | RES                    | ULTS                                        | 52 |  |

| 8. | CONCLUSIONS            |                                             |    |  |

#### LIST OF SYMBOLS AND ABBREVIATIONS

#### **ABBREVIATIONS**

AC Alternating current

ADC analog-to-digital converter

AFR Automatic Fixture Removal

BGA Ball Grid Array

BoB Breakout board

BW Bandwidth

CSP Chip-Scale Package

DC Direct Current

Dk Dielectric constant

DRAM Dynamic Random Access Memory

DUT Device Under Test

FR4 Flame Resistant PWB material with type 4 epoxy resin

FV3 PWB structure with stacked and filled any layer microvias

GND Ground

GPIB General Purpose Interface Bus

HDI High Density Interconnect

HW Hardware

IBIS Input / Output Buffer Information Specification

IC Integrated Circuit

LFSR linear feedback shift register

LNA Low-Noise Amplifier

MEMS Microelectromechanical Systems

LPDDR Low Power Double Data Rate

NPTH Non-Plated Through Hole

ODT On-die termination

PDN Power Delivery Network

PI Power integrity

PoP Package-On-Package

PWB Printed Wiring Board

RCCu Resin-Coated Copper

RF Radio Frequency

SI Signal Integrity

SMA SubMiniature version A

SMD Surface Mount Device

SNR Signal to Noise Ratio

S-parameter Scattering parameter

SP6T Single-Pole Six-Throw

SPDT Single Pole Double Thro

SPDT Single-Pole Double-Throw VNA Vector Network Analyzer

#### **SYMBOLS**

$\beta$  Propagation constant  $\Gamma$  Reflection coefficient

$\delta_s$  Skin depth

$\varepsilon_r$  Relative permittivity

$\mu_0$  Permeability of vacuum

$\sigma$  Conductivity loss

b Height of substrate between two ground layers

c Speed of lightG Conductance

l Length

RL Return Loss

VF Velocity Factor

$W_e$  Effective width of conductor

Z Impedance

## 1. INTRODUCTION

Performance and features of mobile phones have developed rapidly, while the size requirements are getting tighter because customers want thinner devices with good battery life and durability. These requirements set the size limit for the actual mobile phone's *printed wiring board* (PWB) and the amount and size of components that can be utilized. Two main approaches to implement memory into mobile device is to use a separate memory *integrated circuit* (IC), which communicates with processor via signal traces of the mainboard. The second, and more common approach in high-end devices is to use a *package-on-package* (PoP) stacked *application processor* (AP) and *low power double data rate* (LPDDR) memory. This thesis work presents the memory testing system for 4<sup>th</sup> generation low power double data rate (LPDDR4) memories but the same technique could be utilized also with different LPDDR generations and memory interface techniques with minor modifications.

**Table 1** Clock frequency and core voltage comparison in different LPDDR generations. [1, p.5]

|                  | LPDDR | LPDDR2 | LPDDR3 | LPDDR4 |

|------------------|-------|--------|--------|--------|

| Approx. year     | 2005  | 2010   | 2013   | 2015   |

| IO data rate     | 400   | 1066   | 1866   | 3200+  |

| (Mbps / pin)     |       |        |        |        |

| Clock frequency  | 200   | 533    | 933    | 1600+  |

| (MHz)            |       |        |        |        |

| Core voltage (V) | 1.8   | 1.2    | 1.2    | 1.1    |

Memories are getting faster, but the physical size and pin count of the memory *chip-scale* packages (CSP) are still limited due to the size requirements of the mobile devices. This obviously means that the data pins of the memory must have higher data rates, or the width of the data bus needs to grow to increase the total data *bandwidth* (BW) of the memory. Table 1 presents the rapidly increasing memory data BW and other key specifications of LPDDR memory generations.

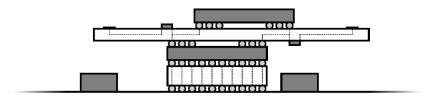

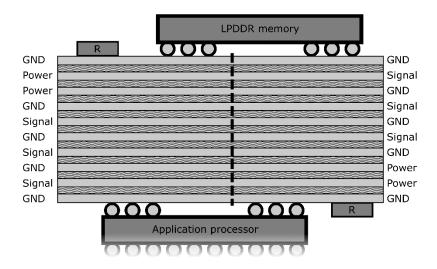

Figure 1 Side view of PWB with PoP stacked AP and LPDDR4 memory and passive components.

1. Introduction 2

Logically, the state of the single data pin can be '1' or '0'. However, due to physical properties of electricity, the transition from one logical state to another cannot be infinitely fast. The transition time, also called rise and fall time, sets the maximum limit to the highest usable data rate for a single data line. The PoP stacked AP and *dynamic random access memory* (DRAM) are reflow soldered directly to each other in the final product, as presented in Figure 1, so *signal integrity* (SI) issues related to *hardware* (HW) design are managed by IC manufacturers. However, bus transceiver and timing parameters are configurable by software [2], and the verification of software parameters is done by the manufacturer of the end product. Also, current consumption measurements are done to achieve the best possible voltage regulation characteristics and battery life of the product.

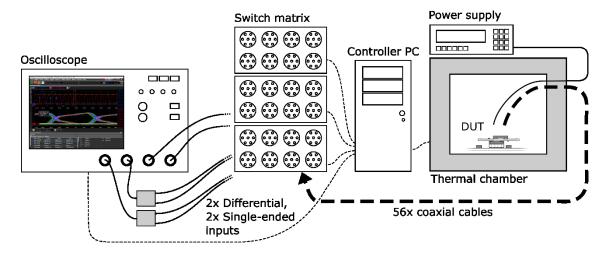

Measuring all the needed signals manually would be very time-consuming and unpractical. Previously signals have been measured by an automated, computer controlled setup which includes oscilloscope, switch matrix and PWB attached multi-position probes [4]. The currently used setup has been developed originally for LPDDR3 and lower speed grade LPDDR4 memories. However, lately the increasing clock speeds have introduced a new problem – the measurement setup interferes with the *device under test* (DUT) so much that the device becomes unstable, or even unable to power the device up at all. It also means that the measured signal is not the same as it would be without the measurement system.

The goal of this master's thesis is to characterize the bottlenecks in the currently used automated memory testing system and introduce some new techniques to improve measured signal quality and the operation of the DUT itself. Among the other things, this thesis work introduces a new probing technique, which extends the actual probing point closer to the wanted measurement node by utilizing a carefully impedance controlled transmission line and by removing the need for an external oscilloscope probe with high input impedance. The design is improved further by introducing a new *breakout board* (BoB) component placement topology which allows the measurement system to be more invisible for the DUT. The new BoB design takes the current measurement capability to a separate BoB, which has a newly presented memory activity probing system that utilizes capacitive coupling. The interference between DUT and measurement system in a capacitively coupled probing system is negligible and the SI is very good.

The first part of this master's thesis presents the background theory behind the newly designed improvements to the measurement system. After that, the old system is characterized in chapter three, and new design improvements, based on the previously made observations, are presented in the fourth chapter. Chapter five introduces digital post-processing techniques to improve the measurement results further. The implemented measurement system is presented in chapter six, and the performance measurements are compared to the previously used system in chapter seven. Finally, chapter eight concludes this master's thesis.

## 2. THEORETICAL BACKGROUND

While the utilized frequency BW increases, transmission line theory plays a more and more significant role in any design related to data signals between the receiving and transmitting end. In high BW applications, like the memory testing system presented in this master's thesis, even minor non-idealities can affect the signal's properties quite radically. This chapter presents briefly the background theory behind the techniques, used in this LPDDR4 memory testing system.

Complex digital systems, like the memory interface between the AP and DRAM includes more than a hundred signals, in which SI must be well implemented to allow fast data transfers reliably. Basically, the DRAM interface includes parallel data signals and clock, or strobe signals, which initiate the data transfer. The total throughput of the memory interface can be increased by adding the bit width of the bus or by rising the clock frequency. However, the size and SI properties of the IC package limits the maximum reasonable amount of parallel data signals, so also the clock speeds are getting constantly higher. Single LPDDR4 CSP also includes multiple ICs, which operate in parallel. By knowing the IC and driver configuration, the amount of the measured signal can be reduced to allow a simpler measurement setup with higher measurement quality. At minimum, only one of the signals in same signal group with similar drivers and driver configurations is needed and the other signals in the same group can be expected to be similar enough with each other.

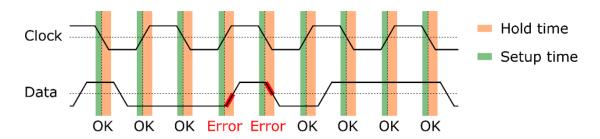

Figure 2 Illustrative figure of setup and hold time requirements regarding to typical clock and data signals in DDR system.

In simple terms, we can inspect every measured data – clock or strobe signal pair to get all the needed information. Figure 2 shows the relation between the data and strobe signals. The data signal must stay in its state at least for a specified setup time before the edge of the clock signal occurs and the data is read. Also, the signal must stay in its state at least for a specified hold time after the data strobe occurs to prove reliable data transfer. There are defined voltage threshold values for high and low status, and the transition must be fast enough to achieve the needed voltage value after the hold time but before the beginning of the setup time of the following bit. This requirement creates a relation

between the strobe signal and the data signal. If the state of the signal alters too slowly, the setup and hold time requirements are not met, and if the phase offset between these two signals is not configured properly, the system may violate the setup or hold time requirements. The competition in mobile device markets is intense and manufacturers are pushing the IC's to operate as fast as possible, and the previously explained timing tolerances are very strict. [5, p.510]

$$V(t) = V_{offset} + \frac{4}{\pi} \sum_{n=1}^{\infty} \frac{V_{ampl} \cdot \sin(2\pi(2n-1) \cdot t \cdot f)}{2n-1}$$

(1)

Based on the Fourier's series theorem, an ideal square wave is composed of an infinite amount of sine waves with different amplitudes and frequencies, which can be extracted from Formula 1 [6, p. 17]. Frequency of nth harmonic component can be calculated by (2n-1)f,  $n \in \mathbb{N}^+$ , and the amplitude of each frequency component by  $\frac{4}{\pi} \frac{A}{(2n-1)}$ ,  $n \in \mathbb{N}^+$ . One frequency component forms only a sine wave at the frequency to signal's base frequency. If more frequency components are included, the resulting sum signal begins to look more like a square wave, depending on the amount of utilized frequency components. Mathematically it is possible to generate an ideal square wave but in a real electronic system, the width of the usable BW and frequency components depends on the properties of components and transmission line.

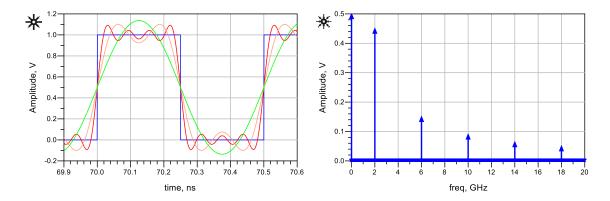

**Figure 3** Ideal square wave and its harmonic frequency components in 20 GHz range. Also non-ideal square waves presented with 1, 2 and 4 frequency components included.

As stated, a signal's voltage value cannot alter infinitely fast from one level to another. It would need a transmitter with infinite BW. Figure 3 presents the ideal square wave and the corresponding frequency domain response. As can be seen, the signal transition becomes faster when there are more frequency components included.

**Figure 4** Frequency BW utilization comparison with ideal LFSR source and same signal with limited transition speed. The brown trace presents the amplitude ratio between the ideal and non-ideal frequency components.

Figure 4 brings the previously presented theory closer to real-world digital high-speed applications. While the first Fourier's series example had only a continuous, repeating square wave signal, the frequency spectrum would correspond quite well to continuous clock signals. However, in data signals, the time interval between level transitions will vary in discrete time steps because the data might have more than one logical one or zero in a row. Figure 4 illustrates the ideal data signal with infinitely fast rise and fall times, generated with *linear feedback shift register* (LFSR) algorithm, and another signal, which looks a lot more like a real measured signal from a high speed digital system with the signal's transition speed limited by the circuit's physical properties. Instead of utilizing infinite frequency BW, the BW of the example signal in Figure 4 signal is only approximately 3.2 GHz, as the marker at -3 dB point indicates.

$$BW = \frac{0.35}{t_{ns}} \tag{2}$$

Based on the previous explanation, the needed system's BW and rise and fall time have a relation. As Figure 4 presents, the measured rise time from 10 % to 90 % is 110 ps. Now we can use the relation [7, p.3], presented in Formula 2, to estimate the needed BW, which would be 3.2 GHz in this case. The calculated value matches the observed –3 dB point in frequency domain plot in Figure 4.

In conclusion, the measurement system must have a frequency BW wide enough to be able to capture all the needed frequency content from the inspected system. Generally, the BW of the measurement system must have a certain margin compared to the BW requirements of the DUT itself. If the signal's transition time would be out of the specification by being too fast, the measurement system must have high enough BW to be able to detect the problem. Also, the measurement system is intended to be usable in the future, with higher speed DUT's without major upgrades, so it must be taken into account in the design process.

According to Agilent's application note [8], a good rule of thumb is to have a measurement system with a BW of five times the clock frequency of a DUT. This estimation is quite rough because the estimation does not involve the signal's transition time. More precise BW value can be calculated by determining the previously mentioned fastest signal's transition speed and multiplying the BW by the factor, defined by the oscilloscope's low-pass filter's roll-off characteristics and the required measurement accuracy. For example, an oscilloscope with maximally flat frequency response and required accuracy of 3 % would induce a 6.4 GHz needed BW if the signal's fastest transition speed would be the same as in the previous example case, 110 ps. The measurement system, presented in this thesis, has an oscilloscope with four channels and analog BW of 16 GHz [9]. According to the previous example, 16 GHz maximally-flat analog BW with an accuracy of 3 % would allow signals with 44 ps, 10 – 90 % transition time.

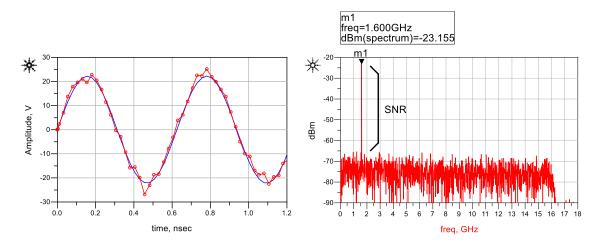

**Figure 5** Blue: ideal 1.6 GHz sine wave, red: 1.6 GHz sine wave with 1.8 mV<sub>RMS</sub> summed white noise. The oscilloscope's 40 GS/s sampling rate presented in red, noisy waveform. SNR can be calculated from the frequency domain presentation. Also the noise power reducing effect of the limited 16 GHz measurement BW can be seen from the frequency domain presentation.

Another important specification of the oscilloscope, is the sampling rate, which is illustrated in Figure 5. Defined by Nyquist's sampling theorem, the well-known factor of the oscilloscope's minimum sampling rate is two times the required BW. However, digital signals have also higher frequency components than the base frequency, so having just the sampling rate of two times of the clock frequency of the DUT would cause pre-shoot, over-shoot and varying edge speeds to the measurement results. According to Agilent's application note, an oscilloscope sampling rate of 4-8 times the measured clock frequency would induce accurate measurement results. [10] The oscilloscope, used in this master's thesis, has 40 GS/s sampling rate per channel when all four channels are utilized [9]. According to previously mentioned numbers, the sampling rate of the oscilloscope would be usable with digital signals up to 5-10 GHz clock rates.

A good measurement does not disturb the DUT by much. The measurement system, presented in this thesis work, implies the power division between the signal's receiver and the measurement system by using a surface mount device (SMD) resistor, which is placed in series with the measurement node. Too high of a resistance value would attenuate the signal too much between the DUT and the oscilloscope and too low of a value would disturb the DUT by taking a significant amount of power from the signal trace to the measurement node. The RMS noise floor of the oscilloscope used, is 0.35 mV<sub>rms</sub> at 10 mV/div setting and 16 GHz frequency BW [9]. An oscilloscope with good noise characteristics allows the usage of high resistance series resistors, while still maintaining adequate signal-to-noise ratio (SNR). The effect of the oscilloscope's noise level is presented in Figure 5, which also presents the effect of limited measurement BW. SNR can be calculated by knowing the total powers of fundamental signal and noise. If total power levels are not known, they can be calculated by dividing the frequency spectrum into bins and dividing the total power of signal bins with noise bins, excluding direct current (DC) offset and harmonic components [11]. This implies that if the measured signal does not utilize the full BW of the oscilloscope, it can be limited manually to remove extra noise content from the frequency spectrum.

## 2.1 Signal integrity

Good SI consists of many different aspects, which must be taken into account in the SI critical design. To inspect SI related issues, signal paths must be modelled as transmission lines with defined characteristic impedance, attenuation, propagation speed and other factors, like crosstalk to nearby signals. Analyzing the signal path starts by modelling the transmission line. A simple transmission line can be inspected analytically with relative ease but there are also powerful, computer aided tools to analyze transmission lines and the characteristics of a complex system of transmission lines. However, to understand the essence of the established problem or to make appropriate design solutions, the theory behind the curtain must be understood. [12]

Especially, the measurement system for SI critical design cannot have poor SI characteristics because then there would be uncertainty, if the perceived problem is caused by the DUT or the measurement system. Also, the timings or drive strengths cannot be fine-tuned reliably if the signal characteristics in a real product would not be very close to measured results.

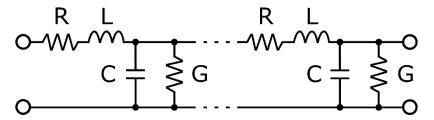

Figure 6 Equivalent circuit for lossy transmission line model.

The transmission line can be modelled as a series of equivalent circuits, presented in Figure 6. The model consists of an infinite amount of equivalent circuits, whose parameters are defined by the physical properties of the transmission line. There are different abstraction levels to inspect transmission lines. The basic model includes only a series inductance, caused by the conductor itself, and the parasitic capacitance of the return path. Also the lossy model can be used. It includes the parasitic series resistance of the conductor, and the parasitic conductance of insulator material. [13, p.48-51] Of course, the computer aided simulation tools do the lossy analysis with ease, but in analytic inspection, the latter two have often been omitted from the analysis for simplicity. In some cases, if the materials are far from ideal, or the transmission line is long, the lossy transmission line analysis must be used to get accurate results.

Every transmission line has its own characteristic impedance. In high speed signaling we are often interested in the transition points where two different transmission lines connect to each other. For example, connectors, vias or solder joints of IC's pins can cause impedance discontinuities. Also, the load impedance in the end of transmission path should be matched to the characteristic impedance of the transmission line. If the two impedances are different, part of the signal power reflects back to the opposite direction from the transition point. Most of the SI issues in high speed designs are typically a consequence of reflections, caused by impedance mismatches. For example, overshoot, undershoot, ringing and rise-time degradation are typical phenomenon, caused by reflections [12].

$$\Gamma = \frac{Z_L - Z_O}{Z_L + Z_O} \tag{3}$$

$$RL_{dB} = 20 \log_{10}|\Gamma| \tag{4}$$

Return loss is a commonly used parameter to inspect the amount of power which is reflected from the merge point of two transmission lines, or from the end termination point of the transmission line. Formulas 3 and 4 present the reflection coefficient, which depends purely on the differences in two impedances. By using Formula 4, the same issue can be presented in decibels. For example, a return loss of 6 dB would mean that only 75 % of the power goes through the transition point, and 25 % of the power is reflected to another direction. If the reflected signal bounces again from another discontinuity in the transmission line, it starts to oscillate between these two points and causes visible ringing in the measured waveform [12].

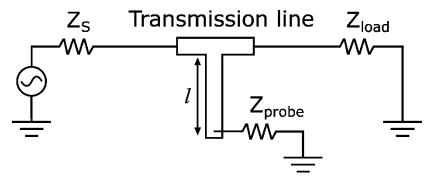

**Figure** 7 Simplified transmission line model of signal path between the signal transmitter and receiver with an extra branch of transmission line, which have equivalent resistance of oscilloscope probe, connected to it.

The main problem, observed in causing SI problems in the previous measurement system is presented more practically in the next chapter. To understand the root cause, we can simplify the measurement system according to Figure 7. There is a signal source, which could be for example an AP, transmitting data to the DRAM. There is a series resistor  $Z_s$ , which corresponds to the output impedance of the transmitting AP. The signal goes through the bond wires, *ball grid array* (BGA) balls and interposer PWB, which is modelled as a single transmission line. At the end, there is  $Z_{load}$ , which is the input impedance of the receiving DRAM IC. The measurement node is presented as an extra branch of the transmission line with a length of l, and then there is  $Z_{probe}$ , which presents the input impedance of the oscilloscope's probe.

At DC, the extra open-ended stub would not make any noticeable difference, but related to the previously presented transmission line theory, the reflection coefficient of an open-ended stub is 1, which means that the signal reflects completely from the open end of the transmission line.

As electricity has a finite propagation speed, the effect of the stub depends on the length of it and the frequency of the signal. At the crossing point, the signal coming from the source, and the signal which is reflected from the open-ended stub, will sum together, and the summed wave continues towards the end termination of the transmission line. If l is short and the frequency is low, then the reflected signal would be closely at the same phase at the crossing point, as the signal coming from the source, and the stub does not make any noticeable difference. On the other hand, if the wavelength of the signal would be four times the length of the stub, then the reflected signal would have exactly a  $180^{\circ}$  phase shift on the crossing point. The sum of these two is zero, so the open ended stub appears as a short circuit. [14]

$$Z_{in} = \left| Z_{load} \parallel Z_{tline} \cdot \frac{Z_{probe} + j Z_{tline} \cdot tan(\beta L)}{Z_{tline} + j Z_{probe} \cdot tan(\beta L)} \right|, \qquad \beta L = \frac{2\pi \cdot f \cdot l}{VF \cdot c} \quad (5)$$

The characteristic impedance of the system is close to 50  $\Omega$ , so in the ideal case  $Z_{load}$  and  $Z_{tline}$  would be 50  $\Omega$ . The input impedance of the oscilloscope probe,  $Z_{probe}$ , varies over the frequency range. At DC, it is close to 25 k $\Omega$  but in 1 – 2 GHz frequencies, we can assume it to be close to 300  $\Omega$  [15]. By placing the values into Formula 5, we will notice that the oscilloscope probe with high input impedance does not affect the input impedance calculation by much, so in this case, the  $Z_{probe}$  can be omitted completely to simplify the formula. Then the stub should be assumed as open-ended. The velocity factor of the PWB trace is close to 0.5 and the length from AP – DRAM interconnection to the oscilloscope probe is 25 – 30 mm.

$$Z_{in} = |Z_{load}|| -j Z_{tline} \cdot \cot(\beta L)|$$

$$= \left(\left|\frac{1}{Z_{load}} + \frac{1}{j Z_{tline} \cdot \cot(\beta L)}\right|\right)^{-1}$$

(6)

Formula 6 describes basically the same situation, as previously presented in Figure 7 and Formula 5, but the effect of probe's impedance is omitted. The equation becomes much simpler but as stated, the difference is not significant. For accurate calculations, it should be noted that the impedance of the oscilloscope probe is not purely resistive, and also the reactive component should be noted. All in all, for accurate results, the most convenient way is to use simulator tools, which utilize all needed parameters with ease.

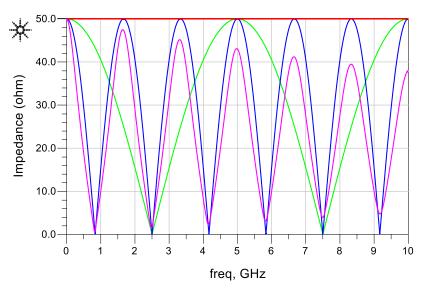

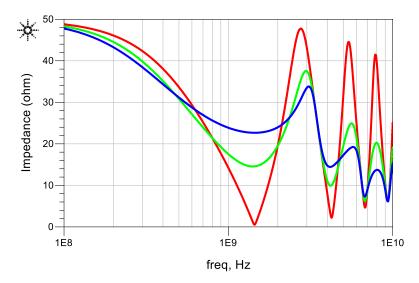

**Figure 8** Impedance seen by the signal source with various stub configurations. Red: ideal 50  $\Omega$  transmission line, Green: stub added with 0.1 ns electrical delay, Blue: stub added with 0.3ns electrical delay, Magenta: stub added as realistic transmission line with lossy PWB simulation and 43 mm length.

Figure 8 illustrates the simulated impedance curves, which could be also calculated by using Formula 6. There is one transmission line without the stub. As expected, it is at the 50  $\Omega$  mark over the frequency range because nothing disturbs the characteristic impedance of an ideal transmission line with proper terminations. Two of the traces are

simulated with the stub at 0.1 ns and 0.3 ns one-way electrical delays. One trace is simulated with the same configuration as the other simulation with a 0.3 ns stub, but the transmission line is done by using non-ideal, lossy PWB materials, which should correspond quite well to the characteristics of the PWB stackup, used in the implemented device. Now we can see that analytical solution gives good estimation, especially in the lower end of frequency range, but as the frequency increases, the real-world non-idealities begin to cause variations, which are taken into account with relative ease in simulation

**Figure 9** Cross section of PWB layer stack with two stripline signal routes and microvia ground fences.

software, if compared to analytical solution.

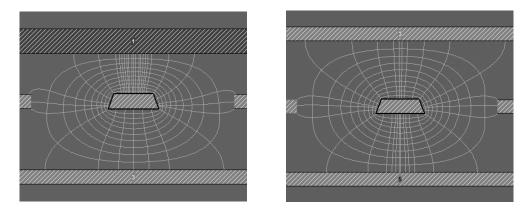

As stated earlier, the LPDDR memories have more than 100 signal routes which should be routed between the two IC's, and a portion of them are also routed to the measurement connector matrices, through the series resistor. The PWB should also have plenty of space for large ground and power planes. The chosen PWB stackup had ten layers, which should be enough for the BoB interposer. The stripline topology, presented in Figure 9, is the only practical way of implementing impedance critical signal paths when there are a large amount of impedance critical signal paths to route. All transmission lines are buried between two ground planes with coplanar ground planes and microvia fences. This arrangement forms a rectangular, grounded shield around the center conductor, which can also be perceived as a rectangular coaxial cable in the PWB. [16]

$$Z_0 = \frac{30\,\pi}{\sqrt{\varepsilon_r}} \, \frac{b}{W_e + 0.441b} \tag{7}$$

By using Formula 7 to get the characteristic impedance of a stripline, we will notice that compared to typical 10-layer *high density interconnect* (HDI) PWB layer dimensions, the dielectric material has to be quite thick or the trace width quite narrow to get the 50  $\Omega$  matched stripline [13, p.142]. Also, decreasing the *dielectric constant* (Dk) value of the dielectric material or reducing the copper thickness increases the characteristic impedance value of a stripline. These are well known drawbacks of microstrip transmission lines. However, by using a decent quality PWB manufacturer, tight requirements are met quite well and the impedance match will be close to the required 50  $\Omega$ . When calculating the characteristic impedance of a stripline, also the manufacturing tolerances of the PWB

manufacturer should be noted because even small variations can change the value of the characteristic impedance considerably. Many PWB manufacturers offer also an additional service for impedance matching, which could be used in impedance critical designs. By using this, the manufacturer measures the transmission lines after the boards are produced, and fine tunes the parameters so, that all the impedance critical transmission lines fit into the specified margins.

When designing the construction parameters of the previously presented stripline, the maximum allowed path loss should be noted. At low frequencies, the resistance of the copper trace will be the main attenuating factor. The obvious way to decrease the attenuation, is to increase the cross section area of the signal trace by using thicker copper or wider traces. However, at high frequencies, the current tends to flow through the surface of the conductor. This is called skin effect. The depth of effective thickness of current route depends on the frequency. The benefit, obtained by increasing the copper thickness might be very small in some cases, if the frequency is high enough. The effect of the used dielectric material typically does not matter in low frequency applications but the rapidly changing electrical field begins to rotate the dipoles in the dielectric material, and due to the friction, part of the signal's power transfers into heat. [17]

$$\delta_s = \sqrt{\frac{1}{\pi f \mu_0 \sigma}} \tag{8}$$

By using Formula 8, we can calculate the skin depth of the material. Copper's conductivity loss is  $5.813 \cdot 10^7 \frac{s}{m}$  [13, p.719], so the skin depth at 100 MHz is approximately 6.6 µm. The result means that even the thinnest widely available copper layer thickness will not cause significant extra attenuation to the signal with similar BW, used in LPDDR4 memories. Of course a thicker PWB trace increases the conductor's skin area but the extra benefit is not very significant after a certain limit, defined by the skin depth. The extra copper thickness would be beneficial in power traces, because the frequency range of the specified *power delivery network* (PDN) impedance is much lower than the frequency range of data signals. Ideally, the layer could be combined so that the PWB includes thicker copper layers for power planes and thinner signal traces, which are needed in this project, based on simulations.

The layered structure of the PWB stack will not allow a perfect ground shield around the signal trace but the gap between two layers can be filled with vias, as presented in Figure 9. Via fences minimizes the parallel-plate mode, caused by the potential difference between the surrounding ground layers, and also enhances the isolation between two striplines, placed side by side on the same layer. Via fences are easy to implement in the PWB with HDI FV3 buildup technology, which allows placing a microvia between any two layers without affecting to other layers. To keep the characteristic impedance of the stripline high enough, the coplanar grounds should not be too close to the center

conductor. The preferable width of the slot around the center conductor is at least three times, and preferably 5 times the width of the center conductor. Too large of a distance will affect the electrical performance of the stripline by allowing pseudo rectangular waveguide modes, which have a cut-off frequency of  $c/(2 \cdot w)$ , where w is the total width of the slot around the center conductor. [16]

Another rule of thumb, considering the density of metallized vias in the via fence, is that the separation should be smaller than  $1/8^{th}$  of the minimum wavelength, for which the stripline is designed to. This keeps the signal from leaking to neighbor transmission lines and the potential differences over two ground planes stays low enough. [16]

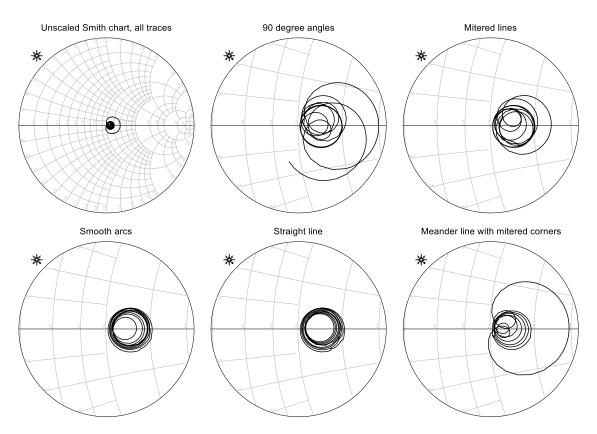

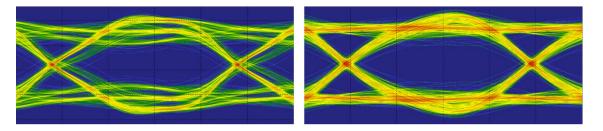

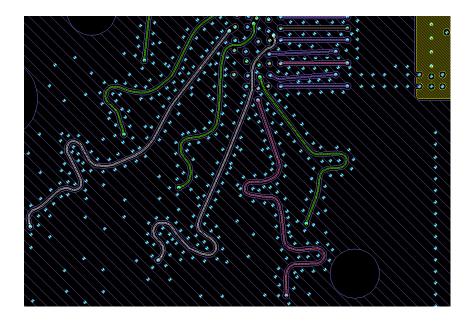

Figure 10 Simulated PWB length matching structures: straight line, smooth arcs, mitered lines, lines with 90 degree angles and meander line with mitered corners.

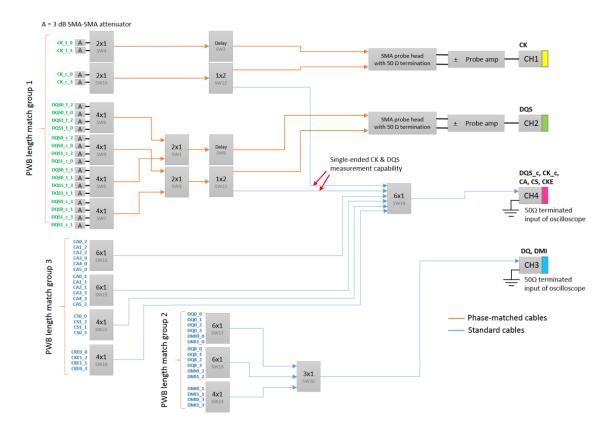

One part of the verification process, is to inspect the software configurable timing skew between the clock and data signals [2]. As electricity has finite propagation speed, it is important to note that the length of two different measurement paths are the same, so the measurement setup does not distract the original timing skew. Although the differences in the electrical delay of measurement paths will be characterized and compensated in post-processing, in the final measurement setup, there are three separate length matching groups in the PWB. When the length of the signal trace is defined, the next revisions of BoB interposers for different products are easier to make, and there will be no need to do new post-processing files, as the differences in length are equal in every BoB designs. When defining the length of the traces in same length matching group, the length is typically defined by the longest path, which will be routed as directly as possible. Other PWB traces in same group are lengthened to have that exact same length. Shorter distances are routed typically by doing curved PWB traces to increase the length. Figure 10 presents some techniques for increasing the length of the PWB trace.

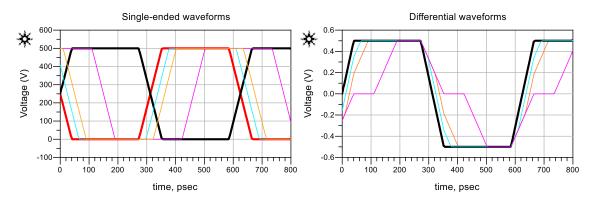

**Figure 11** Effect of timing skew in differential signals. Red – Black signal pair with zero timing skew induces black differential waveform on the right side. The cyan signal has a 25 ps timing skew, orange 50 ps and magenta 150 ps timing skew. The base frequency of the signal is 1.6 GHz which corresponds to real memory interface clock rates.

However, only the timing skew of single-ended signals can be fully compensated in post-processing. Differential signals are more challenging because the signal is converted into single-ended before it can be measured with oscilloscope. Differential measurement paths can be compensated only if both of the signal paths in the differential pair are exactly the same. Figure 11 presents the effect of timing skew between the signals of the differential pair, when the signal is converted single-ended. This explains, why the measurement setup has 5 ps length matched coaxial cables in the differential pairs.

The shape of the previously presented length matching PWB structures does matter at high frequencies. The characteristic impedance of a transmission line is defined by the ratio of the capacitive and inductive properties of the trace. Tight corners will change the ratio slightly, and will cause impedance mismatches, which reflects a fraction of the signal to the opposite direction.

**Figure 12** Corresponding Smith chart **Γ**-plane presentations for PWB traces with mm electrical length, presented in Figure 10. Frequency sweep from 0.5 GHz to 80 GHz.

To analyze the effect of PWB routing and length matching technique's effect on the system's performance, a couple of different types of PWB trace length matching structures, presented in Figure 10, were simulated. Simulations were done by using a similar PWB stackup, materials and dimensions to produce a transmission line which corresponds to the real product, which is built along this thesis work. The electrical length of every stripline was 8.1 mm. Figure 12 presents the result. There were no major differences in the frequency band from 0 to 30 GHz, but extending the simulation frequency to 80 GHz, illustrates the best technique in terms of SI. A PWB trace with smooth arcs takes quite lot of PWB area, but the performance is very close to a straight PWB trace without corners. The next best option would be the trace with mitered corners. A tightly meandering trace with mitered lines is very space efficient, but the performance is not as good as with previously mentioned techniques. The worst option is a trace with 90 degree corners, which is obviously against all general PWB routing rules. The maximum usable frequency range of every technique depends on multiple factors and should be considered case by case. A very narrow trace width, which will be used in the PWB design of the SI BoB, is not very sensitive for tight corners. All in all, there is no significant impact to system performance with the utilized frequency BW and PWB routing properties. However, traces with smooth corners were used in the system that was built because by using more space efficient options, there would not have been any significant benefits. [16]

## 2.2 Power integrity

Good SI alone cannot ensure flawless operation of the device. Also, *power integrity* (PI) issues need to be considered. LPDDR4 memories do not consume a significant amount of power but this does not mean that there would not be PI challenges. Generally speaking, PI design can be divided into two parts – DC and *alternating current* (AC) analysis [18].

DC analysis inspects the voltage drop between the power supply and the analyzed device when the current stays constant. When the electrical current, properties of the metals used and the temperature are known, it is possible to calculate the voltage drop over the specified PDN. Low power mobile memories do not cause a significant DC voltage drop over multiple parallel supply voltage pins which are connected to uniform power planes, but at DC, the majority of the voltage loss is caused by the current shunt resistor which is used to measure the current of a specific voltage rail.

$$Z_{target} = \frac{V_{tolerance}}{I_{transient}} \tag{8}$$

Formula 8 can be used to calculate the best resistance value for the current shunt resistor. The resistance value should be as high as possible to provide a measurable amount of voltage loss over the current range of interest. When the maximum allowed voltage drop and the maximum peak current of the DUT are known, the maximum resistance value for the current shunt resistor can be calculated easily by using Ohm's law. The resistance of the PDN itself must be subtracted from the calculated value because the shunt resistor and the resistance of PDN are effectively connected in series. However, a simple DC analysis is not enough in practice, which might have very rapid and intense current peaks although the total average current consumption would be low.

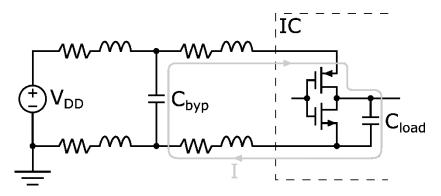

AC analysis inspects the noise suppression characteristics of the PDN. With digital logic, like LPDDR memories, this is a very important issue to characterize properly. Every conductor inside the IC or on the PWB has a non-zero parasitic capacitance value. When the digital logic state toggles, the transistors pulls the conductor to *ground* (GND) or to the supply voltage. To change the voltage level fast enough, the current flow through the transistor must be high enough to charge the parasitic load capacitance. In digital IC's, voltage transitions occur in discrete time intervals and typically a vast amount of transitions occur simultaneously. This causes very significant, rapid current spikes, which causes switching noise to voltage supply rails. [19]

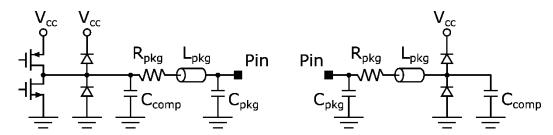

**Figure 13** PDN of IC, and the path of current when the IC is driving the signal from '0' state to '1'.

At high frequencies, also the inductance of supply current loops needs to be characterized. The voltage regulator typically provides the transient response at low frequencies but at high frequencies, transient current is taken from bypass capacitors, which are located right next to the supply voltage pins of the IC. Figure 13 illustrates the previously mentioned push – pull transistor configuration, which toggles the state of signal to one or zero by charging or discharging the parasitic load capacitance. The current, required to charge  $C_{load}$ , is taken from the bypass capacitor. To minimize the current loop area and parasitic resistance, the bypass capacitor is placed always as close to the IC as possible. [19]

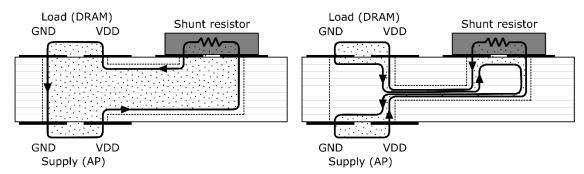

**Figure 14** PWB's cross section from bad and good current measurement systems. The dotted area represents the current loop area, which should be minimized. On the left side there are top & bottom BGA pads for GND and supply voltage, and on the right side is the current shunt resistor.

Regarding to the design process of the current consumption measurement BoB and its tight voltage rail impedance requirements, also the PWB layer stackup design affects BoB's electrical performance. Large overlapping power and ground plane layers generate parasitic capacitance, which is good in power supply applications. The capacitance is not large but it is close to the IC and gives a very good transient response at high frequencies, which would be otherwise degraded by the parasitic inductance between the IC and the bypass capacitor. Also the power plane and the current's return path should be as close to each other as possible to minimize the inductance of the current loop, presented in Figure 14.

All in all, in complex digital systems, the power delivery network can be quite challenging to analyze, so the math is done often with the aid of PI simulation tools. In many cases, good PI needs a lot of PWB area and bypass capacitors. This may compromise the SI of data signals or the price of the product. Component manufacturers define specifications for their IC's, which must be met in the end product. Typically, a good product design aims certain impedance targets, however surpassing these targets by a large amount is not beneficial because of the extra cost incurred and lack of added value to the product. Bearing that in mind, the PDN of the measured DUT is already made to match the minimum requirements with a certain safety margin, so the extra interposer BoB between the AP and DRAM IC must have a very well designed PI to still meet the original PDN impedance requirements.

# 3. CHARACTERIZATION OF THE PREVIOUS SYSTEM

The existing system needs to be characterized carefully before starting to design the upgrades, which will extend the system's capabilities to measure the current high-end mobile devices and upcoming products. Good and well-functioning areas will be preserved and only the mandatory parts are upgraded to save effort and expenses. This chapter introduces the issues which need to be considered in order to extend the SI properties of the automated memory testing system.

In the beginning, the previous testing system was measured and simulated to detect the causes of the DUT's stability related issues, limited measurement BW and other SI issues. In general terms, the most significant issue was caused by the impedance match of the high impedance probes and the IC. Also, part of the issues were caused by the limited PWB area.

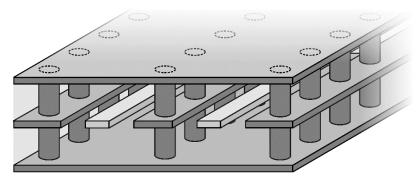

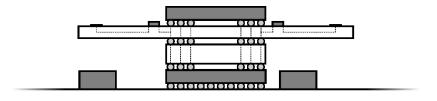

Figure 15 Cross section of the previously used memory testing system interposer stack.

As the Figure 15 shows, the AP is reflow soldered directly on the mainboard. On top of it, there is an interposer construction, which includes the riser board and the BoB. Riser board allows the required spacing between the BoB and the mainboard, so the passive components, next to the AP, will not come in contact with the BoB. At the top of the stack, there is the LPDDR memory IC.

The previous measurement system was capable of measuring almost every possible signal between the LPDDR memory and AP. There was also a current measurement capability embedded into the same BoB. The reason for that was primarily to maintain the compatibility between the existing measurement system, which connects to the interposer structure. Note that, the measurement system could not be fully compatible with the previous versions. In any case, it was also considered, if there would be any signals that does not have to be measured now, or in the future. By collaborating with memory specialists, there appeared to be a possibility to reduce a significant amount of the measured signals without notably compromising the coverage of memory verification measurement results. A reduced signal count leaves more PWB area for more ideal signal routing.

When considering the operation of a mobile device in general level, typically the memory interface have one of the highest frequency BW in the device. Any extra length in memory signal paths would eventually distort the signal, depending on the SI properties of the transmission line. Previously, the riser board had been reworked between the AP and DRAM because the removal of AP is not necessary when attaching the interposer construction on top of it. Also, the DRAM IC has typically less BGA balls with a larger pitch than the AP, so the BGA reballing needs less effort and reworking success is more probable. However, the riser board begins to distort the signal more when the utilized frequency BW increases. Based on the simulations, the riser is placed between the mainboard and the AP in the new design. The memory testing prototype device is dedicated only for memory testing, so it does not matter if the riser board slightly distorts non-memory signals, as long as it does not cause instability.

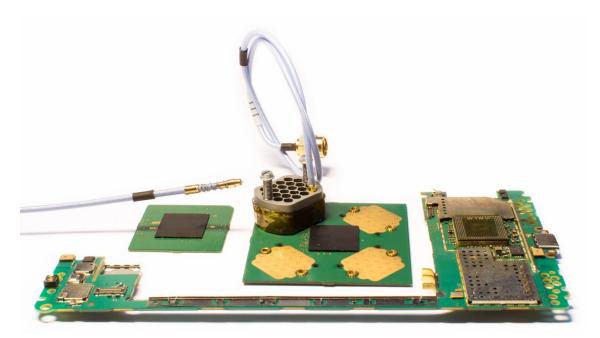

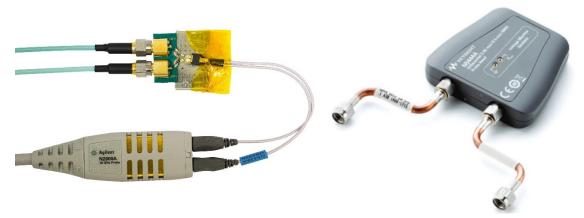

**Figure 16** Agilent N2887A Probing matrix connected to the previous version of the LPDDR4 measurement BoB.

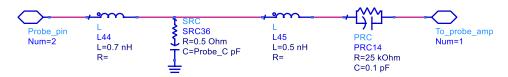

The previous background theory chapter introduced the problem caused by the combination of an extra branch of transmission line and the probe head with a high input impedance, connected to the system. The previously used Agilent's Soft touch probe head, presented in Figure 16, includes multiple probing tips, encapsulated into a small and handy connector, which allows a solderless attachment to the BoB. To inspect the system-level characteristics of the previous measurement setup, the equivalent model of one Soft touch's pin was made based on the measured electrical properties presented in product's datasheet [15].

**Figure 17** Equivalent circuit for a single probing pin of the Agilent N2887A Soft touch probe head.

Figure 17 presents the single-ended equivalent circuit of the Agilent N2887A Soft touch probe head. The model is based partly on the parasitic properties and the impedance plot, presented in product's datasheet [15] and partly experimentally tuned regarding to the probe's physical structure. At DC, the parasitic inductance and capacitance does not affect to the informed 25 k $\Omega$  input impedance of the probe, so there must be a 25 k $\Omega$  series resistor. The typical differential input equivalent capacitance was told to be 350 fF, which means that the single-ended equivalent load capacitance should be approximately twice that amount. Inductors L44 and L45 presents the parasitic inductances, caused by the wires and pins of the probe head. The first rough approximation was done by estimating the length of the wires and pins in the probe head and by using the rough rule of thumb – 10 mm of wire causes the inductance of 10 nH [20, p.238]. The fine tuning of the model's unknown parasitic properties was done so, that the simulated input impedance trace matches to the one, presented in the product's datasheet.

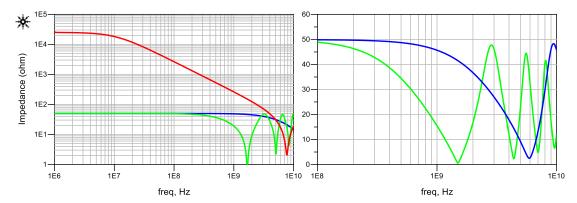

Figure 18 Impedance, seen by the signal source. On the left side, the red trace is the case where only the Agilent N2887A Soft touch probe head would be connected. In the green trace, there would be 21 mm open-ended PWB stub connected in parallel with a 50  $\Omega$  load impedance. The blue trace is the same case but with 5 mm open-ended PWB trace. Figure on the right side presents same cases but now the probe head is connected to the end of the mentioned open-ended PWB traces.

Figure 18 shows the simulated input impedance curve of the probe head only. It matches well to the one, presented in the product's datasheet [15]. However, the impedance values are halved, if compared to the differentially measured values. Figure 18 also presents the effect of the open-ended PWB branch, which is combined with the probe head. On the left side, there is just the open-ended PWB branches, simulated at different lengths. On the right side of the Figure 18 there is the same case, but the equivalent circuit of the probe head is connected to the end of the PWB branch. Although the input impedance of

the probe head begins to decrease at higher frequencies, the effect of the added probe head does not change the impedance, seen by the transmitting end by much. The obtained result corresponds well to the theory, explained in the previous chapter.

Some of the older BoB revisions had a direct PWB traces, going from the via between the AP and DRAM IC to the pads of the probing matrix connection, which are located on the sides of the BoB. In the newer models, there are series resistors added next to the LPDDR IC. Resistors were added after finding out that the newer memory models with the higher clock speeds did not operate reliably anymore. Resistors isolate the unterminated PWB trace from the signal source so, that the signal quality remains good enough for the correct operation of the device.

**Figure 19** Impedance seen by the signal source when the measurement node includes a 3 mm transmission line, a series resistor and a 18mm transmission line, going from the series resistor to the equivalent circuit of the Soft touch probe head. Red: 0  $\Omega$ , green: 22  $\Omega$ , blue: 47  $\Omega$

Figure 19 presents the simulated case, where there is a 3 mm PWB trace, going from the AP – DRAM interconnection to the series resistor and a 18 mm PWB trace, going from the series resistor to the measurement pads on the edge of the PWB. As can be seen, the series resistor with a higher resistance maintains the impedance, seen by the signal source, closer to ideal 50  $\Omega$  over the frequency range. In contrast, the higher series resistance value degrades the measurement quality.

However, the clock speeds with the latest LPDDR4 memories have increased to the point, where the system did not operate at designed clock speeds anymore even if the series resistors would be desoldered completely. Also, the crosstalk has become a problem lately because the higher frequency components couple more easily on to close by PWB traces.

To inspect the crosstalk performance, the BoB PWB layout was imported into the field-solver simulation software, which finds out the crosstalk parameters between the signal

traces. Based on the earlier experience, there have been a significant differences between the simulated and measured absolute crosstalk values, although the relative values have been in line with each other.

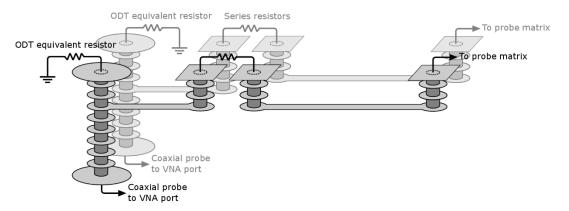

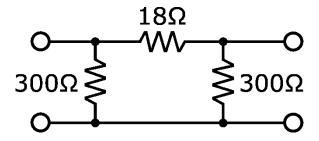

**Figure 20** Illustration of the crosstalk measurement setup and the inner construction of the PWB.

Due to the above-mentioned factors, the crosstalk was measured by using a *vector network analyzer* (VNA) and a miniature solder-in coaxial probes, connected to the BGA pads of the PWB. To minimize the crosstalk, caused by the measurement system itself in relation to the crosstalk, caused by the close by PWB traces, the measured signal pair was chosen based on the worst case simulation. Also the equivalent *on-die termination* (ODT) resistors were soldered on the PWB regarding to the Figure 20.

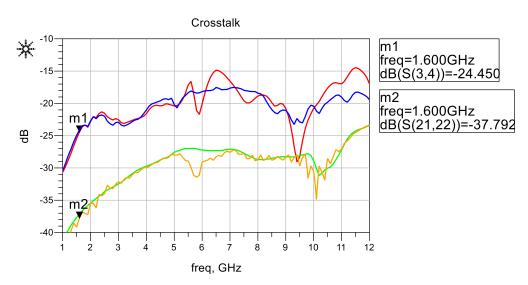

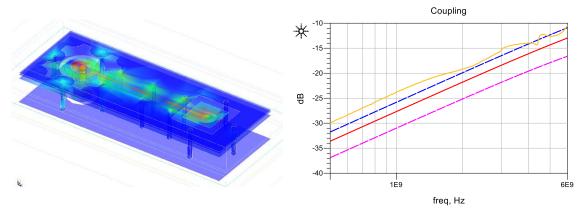

**Figure 21** Worst-case crosstalk performance, measured with the VNA. Blue: previous BoB, probing system disconnected. Red: previous BoB, probing system connected. Green: newly designed BoB, probing system disconnected. Orange: newly designed BoB, probing system connected.

The measurement was done with the probe head connected and disconnected. Figure 21 presents the measured crosstalk values from the BoB, designed along this thesis work. For comparison, there is a measurement done from one of the previous LPDDR4 BoB

revisions. Regarding to the VNA measured results and observations during the earlier memory testing measurements, the crosstalk performance of the previous LPDDR4 measurement BoB was quite poor. Figure 21 presents the improvement in worst case crosstalk performance, which is 13.3 dB at 1.6 GHz.

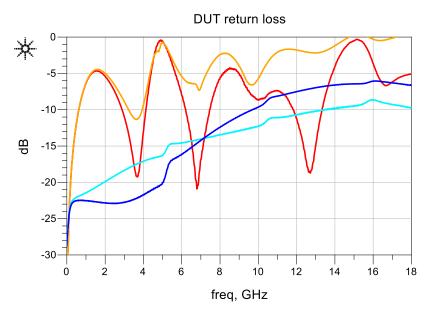

**Figure 22** Return loss traces. VNA's port connected to the BGA pad of the mentioned signal sources. Equivalent ODT resistor connected to the BGA pad of the receiving end. Orange: previous system & DRAM transmits. Red: previous system & AP transmits. Cyan: new system & AP transmits. Blue: new system & DRAM transmits.

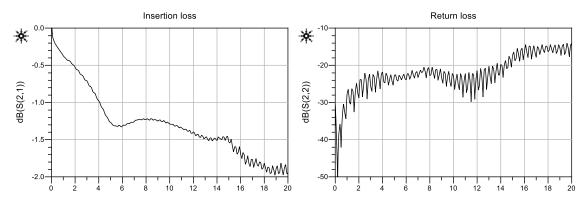

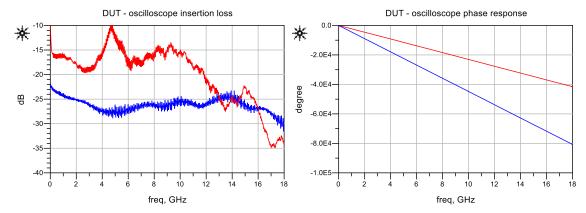

Using the same VNA measurement setup than with the above mentioned crosstalk measurements, also the improvement in return loss characteristics were inspected. The issue with signal reflections in the previous BoB designs, is clearly visible in Figure 22. The length of the improperly terminated transmission line stub defines the density of notches in frequency domain. Longer, the denser. The plot also explains, why the DUT has become unstable with the latest high speed memories. The return loss of 5 dB at 1.3 GHz would denote that approximately 30 % of the transmitted power would reflect instead of going through the system. The new BoB design does not have that same issue, caused by the open-ended PWB stub, so there is a significant improvement in return loss characteristics. During the measurements, the miniature solder-in coaxial probe measurement technique was also noted to be relatively inaccurate in higher than approximately 5 GHz frequencies.

In conclusion, most of the upgrades over the previous measurement system was done into BoB design and to the probing matrix, connected to the BoB. The RF performance of the other components in the system were already at good level. The existing computer controlled switch matrix is built by using a high grade *radio frequency* (RF) relays with an 18 GHz BW [21], and the performance characteristics of them does not limit the measurement quality significantly with current memory clock rates, nor the clock rates

that are expected in the near future with LPDDR5 memories. Also, the oscilloscope's 16 GHz analog BW and 40 GSa/s sample rate from four channels simultaneously [9] is good enough for the LPDDR4 and LPDDR5 measurements.

## 4. DESIGN IMPROVEMENTS

Based on the previously made research about the predecessor measurement system, there were areas, which have worked well and should not be modified, and areas which need upgrades to allow the higher measurement BW, needed by the LPDDR4 memories. This chapter presents the design improvements made over the previous system.

## 4.1 Signal integrity and timing measurement BoB

As stated in the previous chapter, the electrical performance of the system was limited notably by the combination of the effectively open-ended PWB stub and the Agilent N2887A probe head. Even though it would have been possible to terminate the PWB stub which goes from the probing point to the pads of the probing matrix, the limits of the Soft touch based probing system were already reached in terms of electrical performance.

Since the whole switch matrix system already had a characteristic impedance of  $50 \Omega$ , the apparent choice was to extend the  $50 \Omega$  transmission line as close to the probing point as possible. To not to attenuate the signal between the AP and the DRAM IC considerably, the power division must be done so that the probing system loads the DUT as marginally as possible. Still, the signal should be strong enough at the oscilloscope's end to achieve measurement results with an acceptable SNR.

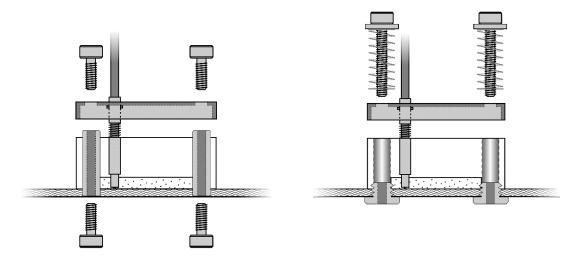

Figure 23 Cross section view of the newly designed memory testing system interposer stack.

The previous BoB design, presented in Figure 15, minimizes the length between the AP and the LPDDR IC, and the length of the extra branch to the SMD resistors is electrically quite long. Microsoft's previous internal research have shown that the previous design topology began to cause SI issues with the high-end LPDDR4 memories because of the earlier mentioned reflections, caused by the extra PWB branch. One option would have been to place a very small, 01005 sized SMD resistors between the PWB and the IC. However, resistors with the length of 0.01" and the width of 0.005" would have been quite unpractical in terms of rework and soldering. The new design, presented in Figure 23, increases the length between the AP and the LPDDR memory IC marginally, but the additional length is not a problem because the transmission line is always terminated from the receivers end, so the extra length will not increase the reflections significantly. The

new design also allows the usage of a 0201 sized resistor, which can be hand-soldered with relative ease. In the new design, the extra stub from the signal trace, between the AP and the LPDDR IC, to the series resistor has only the length of the via stack, which is approximately 0.5 mm. Also the usage of embedded resistors was investigated but the size and the high manufacturing price opted them out.

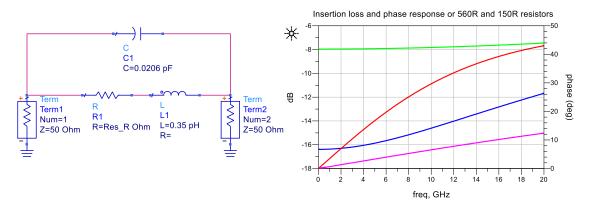

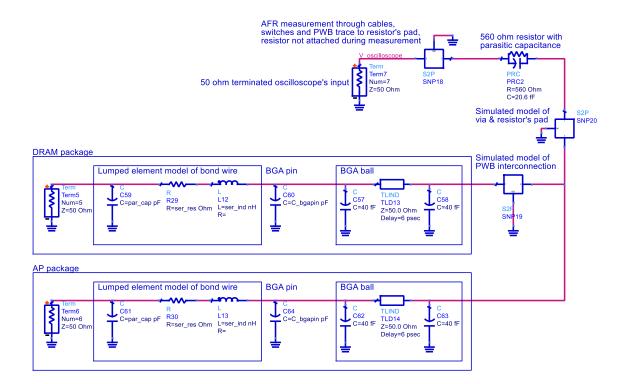

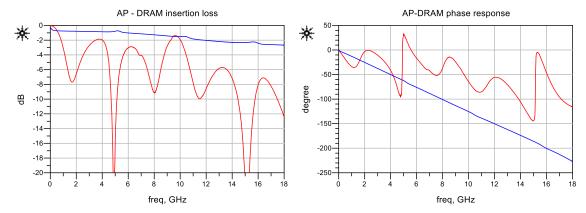

**Figure 24** Simulation of a 0201 sized SMD resistor with the parasitic components included. Blue trace presents the insertion loss of a 560  $\Omega$  resistor and the red trace is the phase response of that. The green trace is the insertion loss for a 150  $\Omega$  resistor and the magenta trace is the corresponding phase response.

The physical size of the resistor also affects the system's performance. Typically small resistors are more ideal. Regarding to Vishay's research [22], the parasitic properties of the 0201 SMD resistors are already at relatively good level. As the parasitic properties of the resistors are mainly caused by the physical dimensions and the construction style, the values for the simulated 560  $\Omega$  and 150  $\Omega$  resistors were taken directly from the Vishay's technical note. There are small variations between the products of different manufacturers and the different resistor series, but the parasitic values were tested and there was no significant difference observed in the measured waveforms, if the value of the parasitic capacitance or inductance was changed slightly to a greater or a smaller value in the postprocessing function, which will be described more in depth in the next chapter. The effect of the resistor's series inductance in the waveform data, was unobservable small, but the effect of the 560  $\Omega$  resistor's 20.6 fF parasitic capacitance was seen in the measured waveforms when the parasitic properties of the resistor was included into the postprocessing function. The simulation, presented in Figure 24, also shows that the 120  $\Omega$ resistor appears to be more ideal over the frequency range. This is because the resistive component is more dominant in relation to the parasitic components, if compared to the 560  $\Omega$  resistor.

As stated in the previous chapter, the long, unterminated branch of the transmission line will cause notable reflections in high BW applications. Generally, the transmission line is perceived as electrically long if the signal propagates from its source to the end of the transmission line and reflects back to the source faster than the signals transition time. In a electrically short, unterminated transmission line, the possible effects caused by the

signal reflection is nominated by the rising or falling edge of the signal. The generally used rule of thumb is that if the propagation delay of the transmission line is longer than 1/6<sup>th</sup> of the signals transition time, a termination is needed. [23]

$$l = \frac{t \cdot VF \cdot c}{6} \tag{9}$$

According to Formula 9, the application with the transition time of 100 ps and VF of 0.5 would need a termination if the length of the transmission line is longer than 2.5 mm. Although if the interconnections between the two PoP stacked CSP's are shorter than that, the bond wires in the CSP packages increase the total length from IC's die to die well over the calculated length, and a termination is needed.

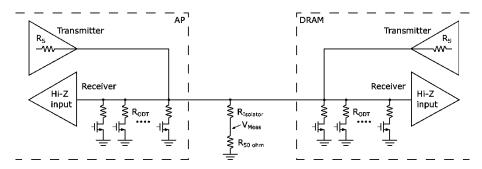

**Figure 25** Illustration about the total impedance, formed by the parallel connection of the ODT and the measurement node.

Typically the termination point of the transmission line is placed physically as close to the end of the transmission line as possible to minimize reflections. In LPDDR4 memories, the termination is implemented on the silicon chip. As the Figure 25 presents, the impedance of the ODT can be set in discrete steps by switching the transistors accordingly. Active logic also allows the ODT to be turned off on the transmitting end, so it does not attenuate the signal unnecessarily. By modifying the software defined parameters, the ODT impedance can be set to match the transmission line's impedance as closely, as the discrete impedance steps allows. [2]

Figure 25 shows also the obligatory drawback of the measurement system. The series connection of the resistor on the PWB and the oscilloscope's 50  $\Omega$  input impedance is connected in parallel with the ODT impedance of the receiving IC. When using the measurement system for finding the best possible ODT value, the effect of the parallel connected measurement branch must be taken into account. A high series resistance in the measurement node reduces the effect of the measurement setup but the tradeoff must be done so that the series resistance is still low enough to achieve an adequate SNR.

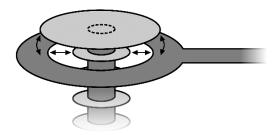

The previously used Agilent Soft touch probing system was very good in terms of usability because the spring loaded probing heads took a direct contact to the pads on the PWB without soldering required. To maintain the fast and easy connectivity, the probing matrix was replaced with a multi-positioned RF connector with the characteristic

impedance of 50  $\Omega$ . However, the only option found, which met the demanding requirements in terms of electrical performance, size, amount of positions and availability, had some disadvantages that needed mechanical modifications, which are presented more in depth in chapter 6.

To inspect the timing attributes reliably between two or more signals, the PWB traces in the BoB needs to be length matched, so the measured timing skew is exactly the same as it is between the AP and the DRAM IC. The previous BoB's have had every trace length matched with each other. This increases the crosstalk because there is no space to add ground fills between every signal, due to the large length matching structures. On the new design, the length matching is divided into three groups so, that every signal which goes to the same oscilloscope channel, through the switch matrix, is lengthened similarly. This way, the signal mapping to the connector's positions can be arranged to allow reasonably sized length matching structures and good SI properties in the PWB layout. Because of the difference in propagation delay between the length matching groups, the timing skew is compensated in the digital post-processing of the measurement data.

Based on the previous research [4, p.74], also the concept design about the completely new switch matrix was investigated during this master's thesis. It would have been implemented by using the microelectromechanical systems (MEMS) switches. This would have allowed shorter coaxial cables than the separate rack-mounted switch units. However, the crosstalk would have been a problem with the MEMS switches because they are physically small, and the isolation between the two signal paths would not have been sufficient enough for this kind of measurement setup and performance requirements. The system's performance was estimated also with the GaAs transistor switches, which would have allowed a very good crosstalk performance, but the GaAs switches, with the electrical performance high enough, were very costly and the attenuation was not low enough for this application. Also, most of the MEMS or the transistor based switches had a single-pole double-throw (SPDT) topology, so for example, multiplexing eight signals would have needed seven switch components, while the rack-mounted switching units with multiple single-pole six-throw (SP6T) Narda RF relays [21] are able to multiplex six signals with one relay component. So in the end, the rack-mounted switches with good quality cables still offers the best performance without the extra effort of designing and implementing a completely new switching system and its control software.

The temperature tolerance of the system is one important aspect. All parts, close to the interposer construction, should tolerate a wide range of operating temperatures, because the DUT will be tested in different operating conditions in a temperature controlled chamber. This basically prevents the usage of active components, like signal amplifiers, close to the DUT, because the electrical characteristics of them typically depend significantly on the operating temperature [5]. Also the electrical characteristics of the passive components varies over the temperature range, but the variation in the cables, connectors or SMD resistor's characteristics is insignificant in terms of this application.

The SI verification process of the LPDDR IC includes many different measurements. Previously, the same BoB has been used for the SI measurements and also every voltage rail had its own shunt resistor for the current consumption measurements. Both of the mentioned measurements have their own requirements. Current measurements do not need information about the data bytes but only if there is data traffic ongoing or not. The current consumption measurement board should operate at the maximum clock speeds, so the current reading corresponds to realistic use cases. Signal integrity measurements do not necessarily need all the signals to be routed out because part of them are very close to identical with each other, and only one of them needs to be measured. Also, the SI measurements should run at full clock speeds to inspect the eye diagrams and waveforms in most critical scenarios in terms of timing and SI. Of course, soldering two separate boards for the SI and the current consumption measurements needs more effort and resources, but at this point, it seems like a good compromise to be done.

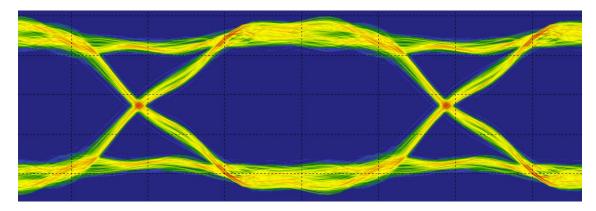

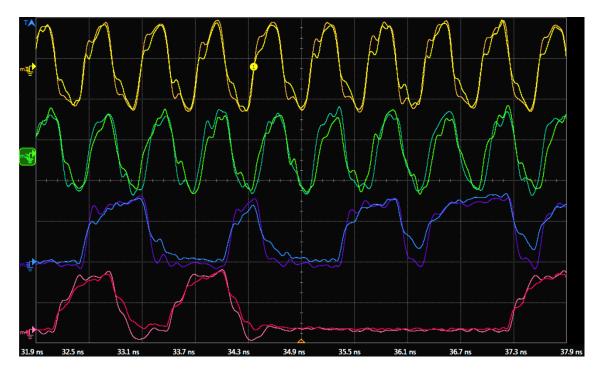

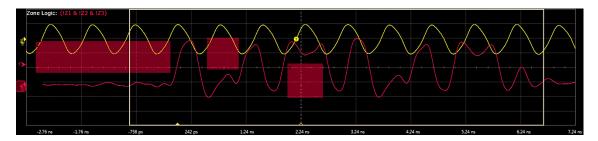

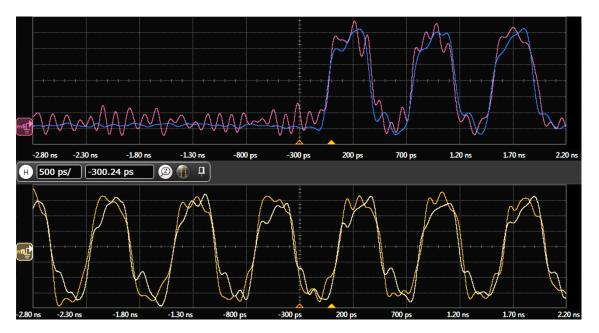

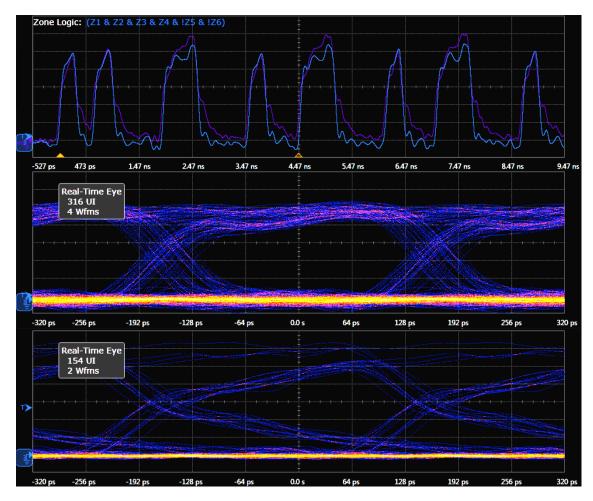

The eye diagram measurements and simulations are an important and very useful way to inspect the system's response to the periodic, arbitrary data signals. The simulated transmitter sends, for example, LFSR randomized data values to the signal path, and the receiver plots them on top of each other with color grading and infinite persistence. The eye-shaped area between the transitions should not have any overlapping traces because then the data might be read incorrectly. The minimum acceptable width and height of the eye-pattern is also specified for the receiver IC.

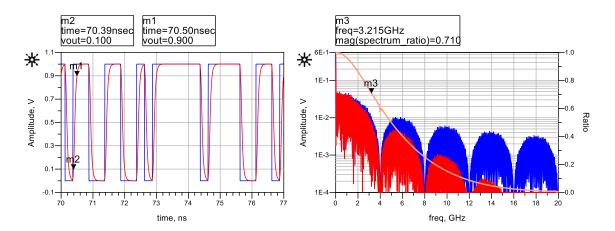

**Figure 26** An eye diagram seen by the DRAM in a simulated, unmodified PoP stack when the AP transmits.

Figure 26 presents the simulated ideal case where the AP and DRAM are connected directly to each other without the interposer stack or the measurement system attached. The shape of the eye diagram varies depending on the pin and software configurable transceiver parameters but it does not matter in this case, as long as, every comparable simulation uses the same pin and transceiver settings. When the interposer stack is included into simulation, ideally, the IC's received eye diagram, should not change from the ideal simulation case, and also the eye diagram, seen by the measurement instrument, should look similar. If the received and measured signal would look similar to ideal simulation without the interposer stack attached, it would mean that the measurement

system is totally invisible to the DUT and the signal would not be distorted between the DUT and the oscilloscope. However, this kind of measurement system is practically impossible to implement because there must be at least a power division between the DUT and the measurement node, which affects to the amplitude of the waveform. If only a small fraction of the power is captured to the measurement node, the amplitude degradation will be insignificant.

**Figure 27** A simulation of the previous measurement system with the Soft touch probe head connected. Left: the eye diagram observed by the DRAM IC when the AP transmits. Right: Same setup, the eye diagram seen by the oscilloscope.

Figure 27 presents the simulated case with the previous measurement system connected. As stated, the practically open-ended PWB stub distorts the signal quite much between the AP and DRAM. Also the waveform in the oscilloscope's end looks closer to a sine wave because the system's BW is not enough for capturing the highest frequency components when the DUT is operating at maximum 3.2 Gb/s data rates.

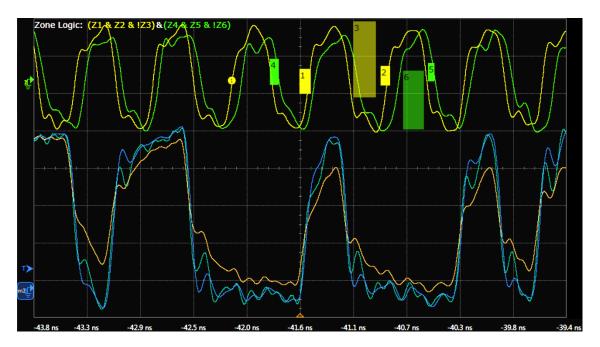

**Figure 28** A simulation of the new measurement system with the connector matrix connected. Left: the eye diagram observed by the DRAM IC. Right: same setup, the eye diagram seen by the oscilloscope when the AP transmits.

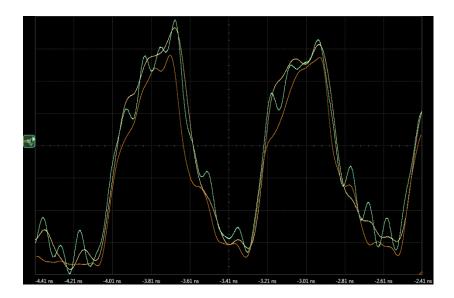

The same simulation was done with the simulation model of the new system. As can be observed from the Figure 28, the eye diagram does not look exactly similar to the ideal reference simulation, without the interposer attached, but the eye-pattern seen by the DRAM has not shrank much because of the interposer stack. Also, the measured eye-pattern does not differ significantly from the ideal case. Of course, long coaxial cables and the switch setup attenuates high frequency components more, so the transition appears to be slightly slower with the new measurement setup, if compared to the ideal simulation case. All in all, the eye diagrams of the newly designed system seems good, and the minor distortion and transition speed degradation, caused by the measurement setup, can be mostly compensated in post-processing, which is explained in the next chapter.

#### 4.2 Current consumption measurement BoB

The current consumption of the DRAM IC varies significantly depending on the amount of data traffic and the used clock speed. To allow the best possible SI in the signal traces, they are routed directly from the top side BGA pads to the bottom side of the PWB. There is only a microvia stack between the two BGA pads. However, the current consumption measurement requires an information about the memory's activity. By placing a direct PWB branch, which would go from the clock or the data strobe trace to the probing point, would impair the SI, and possibly cause stability issues at the highest clock frequencies. To get the current consumption measurement results with respect to the amount of data transfers and active memory channels, the setup still needs those probing points for activity monitoring.

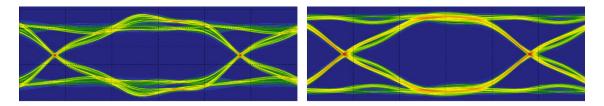

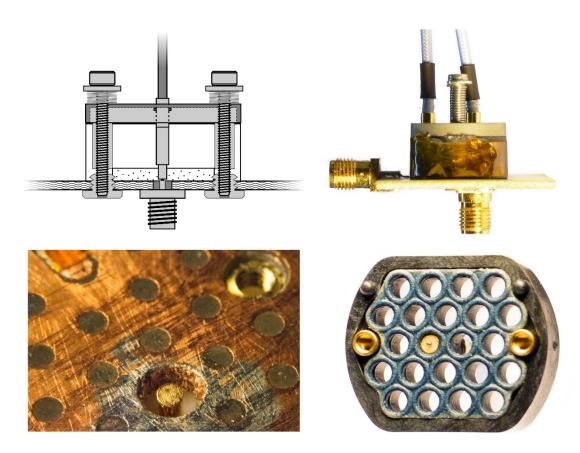

**Figure 29** A BGA pad and a microvia stack which connects it to the corresponding BGA pad through the PWB. The ring-shaped trace acts a coupler which takes a very minor part of the signal to the test pad to identify if there is a data transfer going on or not.

The crosstalk is typically unwanted property between the two PWB traces but this newly designed testing technique makes use of it. By placing a ring shaped PWB trace under the BGA pad, a very small fraction of the high speed signal couples to it because of the common capacitance between the two copper traces. The ring shaped coupler trace, presented in Figure 29, is connected to a test pad, which can be measured with an oscilloscope.