# ARTO OINONEN IMPLEMENTATION OF SYSTEMVERILOG AND UVM TRAINING

Master of Science Thesis

Examiners:

Professor Timo D. Hämäläinen and Doctor Teemu Laukkarinen Examiner and topic approved by the Council of the Faculty of Computing and Electrical Engineering on 9th December 2015

#### **ABSTRACT**

**ARTO OINONEN**: Implementation of SystemVerilog and UVM Training

Tampere University of Technology Master of Science Thesis, 72 pages January 2017

Master's Degree Programme in Electrical Engineering

Major: Embedded Systems

Examiner: Prof. Timo D. Hämäläinen, Dr. Teemu Laukkarinen

Keywords: SystemVerilog, UVM, verification, education

Integrated circuits have become more complex every year and their verification has become more time-consuming. Therefore, effective education of new verification engineers is important for industry. This thesis covers planning of an efficient exercise package for education of verification engineers. The exercises cover key principles of SystemVerilog language and Universal Verification Methodology (UVM). The object of the exercise package is that a person with programming experience but no previous experience of system design or verification should be able to digest the most important concepts in five training days and be able to perform verification tasks using UVM after the training.

The planned exercise package was divided into four exercises on SystemVerilog language and seven exercises on UVM, which cover the methods the designer can use to aid in verification process and the basic principles of UVM methodology. The exercises were implemented as independent work so that the assistant was present to help solving problems and to answer questions. The planning of the exercises adapted to the needs of the participants on different levels so that every student was able to learn the most important concepts and additional more advanced tasks were provided for faster students. The advanced tasks did not introduce new crucial concepts, but deepened the understanding of the concepts used in the mandatory exercises.

The exercises were used as a part of digital design and verification education, where the participants had a programming background. The completion of learning objectives was metered by a time usage survey and a feedback form. Based on the results the learning objectives were fulfilled and every student was able to comprehend the concepts. The students were contented with the content and the structure of the exercises.

# TIIVISTELMÄ

ARTO OINONEN: SystemVerilog- ja UVM-harjoitusten toteutus

Tampereen teknillinen yliopisto

Diplomityö, 72 sivua Tammikuu 2017

Sähkötekniikan diplomi-insinöörin tutkinto-ohjelma

Pääaine: Sulautetut järjestelmät

Tarkastajat: Prof. Timo D. Hämäläinen, TkT Teemu Laukkarinen

Avainsanat: SystemVerilog, UVM, varmennus, verifiointi, koulutus

Integroitujen piirien koko on kasvanut jatkuvasti ja suunnittelun varmennukseen käytetty aika on entistä suurempi osa projektin kokonaiskestoa. Siksi on tärkeää kouluttaa uusia varmennuksen osaajia mahdollisimman tehokkaasti yritysten tarpeisiin. Tämä diplomityö kuvaa tehokkaan varmennusharjoituspaketin suunnitteluprosessia. Harjoituksissa käydään läpi SystemVerilog-kielen sekä UVM-varmennusmenetelmän keskeisimmät ominaisuudet. Harjoitusten tavoitteena on, että työntekijä, jolla on ohjelmointitaustaa mutta ei aiempaa suunnittelu- tai varmennuskokemusta, pystyy sisäistämään tärkeimmän sisällön viiden koulutuspäivän aikana ja työskentelemään koulutuksen jälkeen varmennustehtävissä käyttäen UVM-menetelmää.

Harjoituspaketti on jaettu neljään SystemVerilog- ja seitsemään UVM-harjoitukseen, joissa esitellään käytännöt joita suunnittelija voi tehdä varmennuksen kannalta sekä UVM-menetelmän perustoiminnot. Harjoitukset suunniteltiin itsenäisesti tehtäväksi niin että assistentti on paikalla avustamassa ongelmatilanteissa sekä vastaamassa kysymyksiin. Harjoitukset mukailevat opiskelijoiden erilaisia lähtötasoja niin että jokainen ehtii oppia perusasiat mutta nopeimmille opiskelijoille on syventäviä lisätehtäviä. Lisätehtävät eivät esittele uusia tärkeitä asioita vaan syventävät perusharjoituksissa hankittua tietoa.

Harjoituksia käytettiin osana Digitaalisuunnittelu ja varmennus –opintokokonaisuutta, minkä osallistujilla oli enimmäkseen ohjelmointitausta. Oppimistavoitteiden saavuttamista tarkkailtiin ajankäyttö- ja palautelomakkeiden avulla. Tuloksien perusteella oppimistavoitteet saavutettiin hyvin ja koulutukseen osallistujat olivat tyytyväisiä harjoitusten sisältöön sekä rakenteeseen.

iii

PREFACE

This Master of Science Thesis was done for the Department of Pervasive Computing at Tampere University of Technology as a part of a digital design and verification education

arranged by Edutech during fall 2015. The education team was full of great people and

experts on their fields and I was privileged to be part of it.

The exercise package that was built in this thesis was designed as independent work, but

the UVM exercises were partly based on OVM exercises designed by Ville Yli-Mäyry for a previous verification course arranged by the Department of Pervasive Computing at

Tampere University of Technology.

I would like to thank professor Timo D. Hämäläinen, Dr. Teemu Laukkarinen and Taru

Hakanen for all the support and for giving me this opportunity. I also want to thank Ville

Yli-Mäyry for the basis of the UVM exercises.

The UVM video lectures on Verification Academy were of invaluable help when learning

UVM. I extend special thanks to Tom Fitzpatrick for the video lectures and Dave Rich

for active online help on multiple forums.

My deepest gratitude to my family and friends for all the support and for pushing me

forward.

Tampere, 22.12.2016

Arto Oinonen

# **CONTENTS**

| 1. | INTRODUCTION |                                          |                                                     |    |  |  |

|----|--------------|------------------------------------------|-----------------------------------------------------|----|--|--|

|    | 1.1          | Backgr                                   | ound of verification methodologies                  | 2  |  |  |

|    | 1.2          | Motivation, methods, and scope of thesis |                                                     |    |  |  |

|    | 1.3          | -                                        |                                                     |    |  |  |

| 2. | SYST         | STEMVERILOG                              |                                                     |    |  |  |

|    | 2.1          | SystemVerilog for design                 |                                                     |    |  |  |

|    | 2.2          | SystemVerilog for verification           |                                                     |    |  |  |

| 3. | UNIV         | NIVERSAL VERIFICATION METHODOLOGY (UVM)  |                                                     |    |  |  |

|    | 3.1          | .1 UVM building blocks                   |                                                     |    |  |  |

|    |              | 3.1.1                                    | Objects and components                              | 18 |  |  |

|    |              | 3.1.2                                    | Macros and methods                                  | 21 |  |  |

|    | 3.2          | UVM a                                    | rchitecture                                         | 24 |  |  |

|    |              | 3.2.1                                    | UVM Environment                                     | 24 |  |  |

|    |              | 3.2.2                                    | UVM Tests                                           |    |  |  |

| 4. | REQ          | EQUIREMENTS AND METHODS FOR THE TRAINING |                                                     |    |  |  |

|    | 4.1          | _                                        | ements and student background                       |    |  |  |

|    | 4.2          | Tools u                                  | ised in the exercises                               | 29 |  |  |

|    | 4.3          | Structure of exercises                   |                                                     |    |  |  |

| 5. | SYST         | SYSTEMVERILOG EXERCISES                  |                                                     |    |  |  |

|    | 5.1          | Learning objectives                      |                                                     |    |  |  |

|    | 5.2          | Structu                                  | re                                                  |    |  |  |

|    |              | 5.2.1                                    | Exercise 1: Introduction to SystemVerilog           |    |  |  |

|    |              | 5.2.2                                    | Exercise 2: Decrypter module                        |    |  |  |

|    |              | 5.2.3                                    | Exercise 3: Assertions and testbenches              |    |  |  |

|    |              | 5.2.4                                    | Exercise 4: Bus connectivity                        |    |  |  |

| 6. |              | M EXERCISES4                             |                                                     |    |  |  |

|    |              |                                          | ng objectives                                       |    |  |  |

|    | 6.2          |                                          | ures and UVM concepts used in the exercises         |    |  |  |

|    | 6.3          |                                          | re                                                  |    |  |  |

|    |              | 6.3.1                                    | Exercise 1: Introduction to UVM                     |    |  |  |

|    |              | 6.3.2                                    | Exercise 2: Creating classes                        |    |  |  |

|    |              | 6.3.3                                    | Exercise 3: Subscribers and analysis ports          |    |  |  |

|    |              | 6.3.4                                    | Exercise 4: Automatic checking and randomized input |    |  |  |

|    |              | 6.3.5                                    | Exercise 5: Verifying FIFO blocks                   |    |  |  |

|    |              | 6.3.6                                    | Exercise 6: Verifying the decrypter                 |    |  |  |

|    |              | 6.3.7                                    | Exercise 7: Integration level testbench             |    |  |  |

| 7. |              | TRAINING SESSIONS AND RESULTS            |                                                     |    |  |  |

|    | 7.1          | Learning outcomes6                       |                                                     |    |  |  |

|    | 7.2          |                                          |                                                     |    |  |  |

|    | 7.3          | Problems faced                           |                                                     |    |  |  |

| 8. | CONCLUSIONS | .72 | 2 |

|----|-------------|-----|---|

|----|-------------|-----|---|

# **LIST OF FIGURES**

| Figure 1.  | Design and verification gaps                                       | 1  |  |

|------------|--------------------------------------------------------------------|----|--|

| Figure 2.  | ASIC Project time spent on verification, as found in the Wilson    |    |  |

|            | Research Group study in 2014. [12]                                 | 2  |  |

| Figure 3.  | The evolution of verification methodologies. [8]                   | 3  |  |

| Figure 4.  | The ASIC design size trends in 2014. [12]                          |    |  |

| Figure 5.  | ASIC/IC testbench methodology adoption trends. [11]                | 17 |  |

| Figure 6.  | UVM base class hierarchy. [3]                                      | 19 |  |

| Figure 7.  | UVM component class hierarchy. [3]                                 | 19 |  |

| Figure 8.  | Port – export – implementation connection. [3]                     |    |  |

| Figure 9.  | UVM Phases. [5]                                                    |    |  |

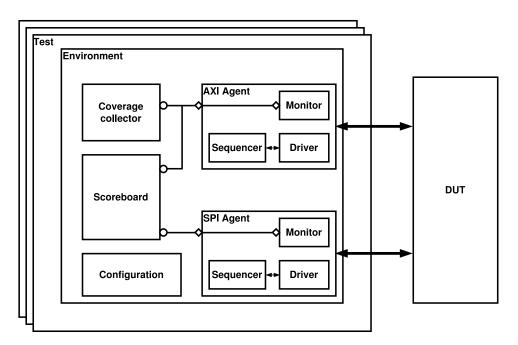

| Figure 10. | A complete block level testbench. [5]                              | 24 |  |

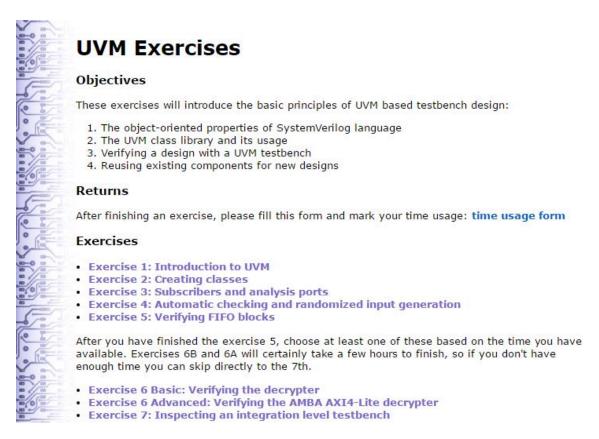

| Figure 11. | The UVM exercise index page                                        | 30 |  |

| Figure 12. | An example of an exercise page. 1 describes a bullet with the      |    |  |

|            | concrete task and 2 is body text containing the motivation for the |    |  |

|            | task. 3 is an example of a code block                              | 31 |  |

| Figure 13. | An information block example                                       | 32 |  |

| Figure 14. | The complete encrypt-decrypt system. [20]                          | 37 |  |

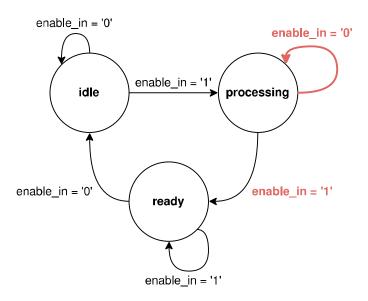

| Figure 15. | A state diagram for the decrypter module                           |    |  |

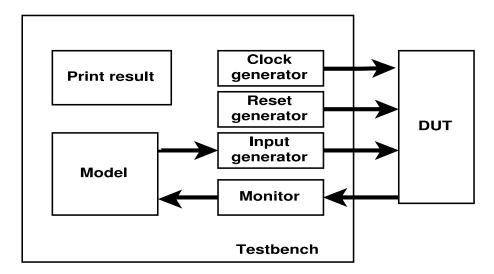

| Figure 16. | Block diagram of the testbench for the decrypter module            | 40 |  |

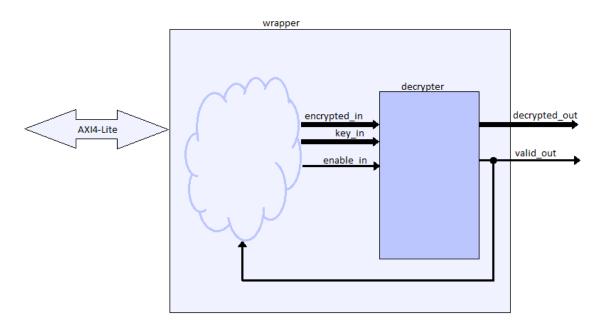

| Figure 17. | AXI wrapper                                                        | 41 |  |

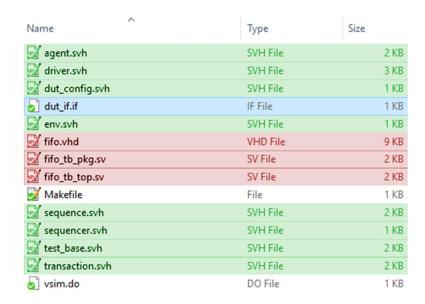

| Figure 18. | Testbench folder layout                                            | 45 |  |

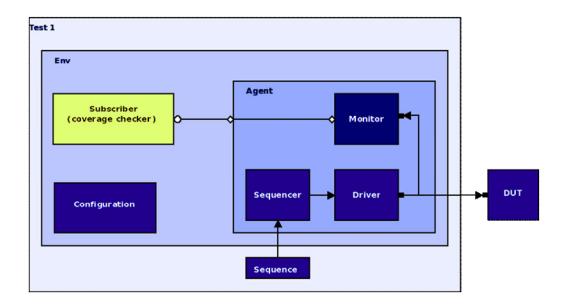

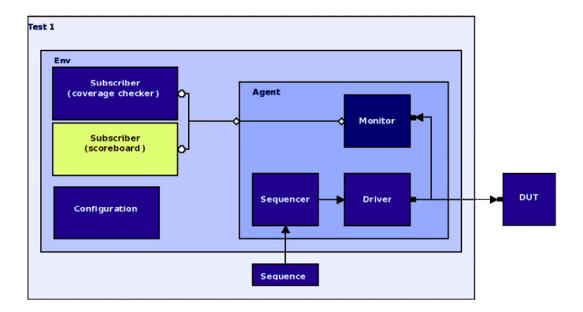

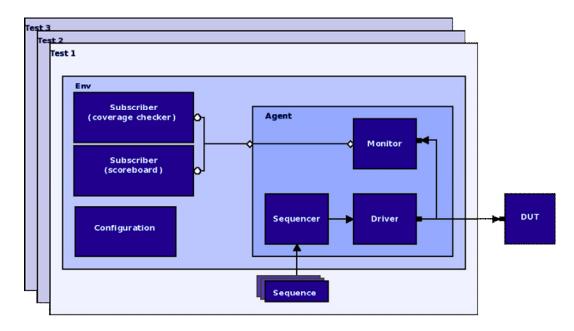

| Figure 19. | The final testbench after finishing exercise 5                     | 46 |  |

| Figure 20. | The base testbench delivered to the student                        | 48 |  |

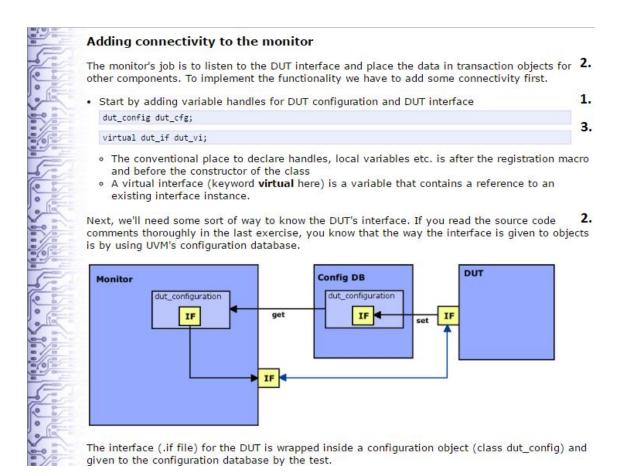

| Figure 21. | Testbench with the monitor attached                                | 50 |  |

| Figure 22. | Delivering DUT interface to monitor                                | 51 |  |

| Figure 23. | Coverage collector added to the testbench                          | 54 |  |

| Figure 24. | Scoreboard added to the testbench                                  | 58 |  |

| Figure 25. | The final UVM testbench                                            | 60 |  |

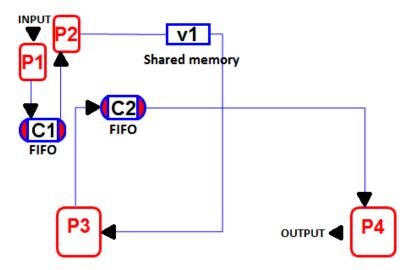

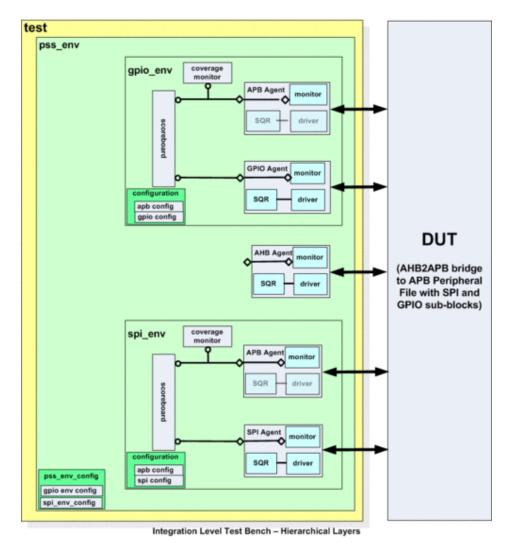

| Figure 26. | The integration level testbench. [18]                              | 63 |  |

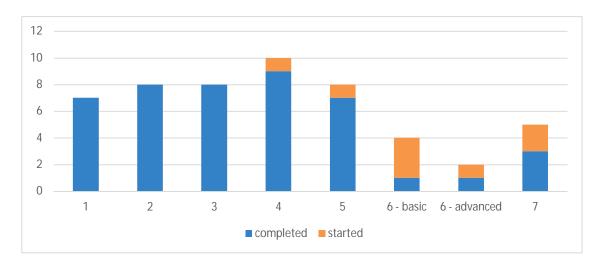

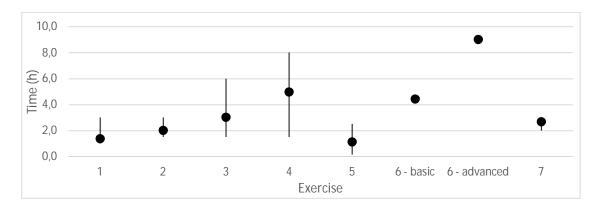

| Figure 27. | Completion of each exercise                                        | 66 |  |

| Figure 28. | Time usage in each UVM exercise                                    | 66 |  |

## LIST OF SYMBOLS AND ABBREVIATIONS

AMBA Advanced Microcontroller Bus Architecture

AXI Advanced Extensible Interface

ASIC Application Specific Integrated Circuit

DUT Design under test

EDA Electronic design automation

eRM e Reference Manual FIFO First in, first out IC Integrated Circuit IP Intellectual property

OVM Open Verification Methodology PCI Peripheral Component Interconnect

RAL Register Abstraction Layer

RVM Reference Verification Methodology UVM Universal Verification Methodology

USB Universal Serial Bus

VHDL Very High Speed IC Hardware Description Language

VMM Verification Methodology Manual

XOR Exclusive or operation

# 1. INTRODUCTION

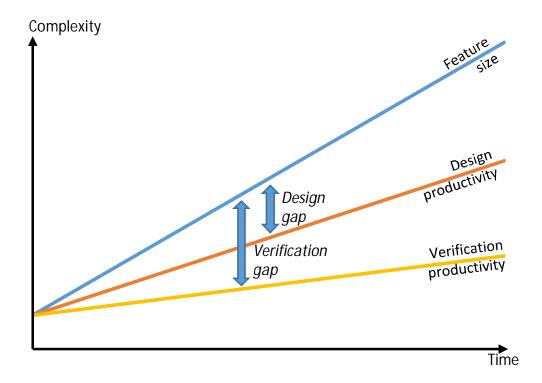

The transistor revolution has brought complex digital systems as an integral part of everyday life where the applications of integrated circuits (ICs) vary from simple toys to mainframe datacenters. As the Moore's law has dictated, the number of transistors in integrated circuits has doubled approximately every two years, which has consequently increased the complexity of ICs. The increase in design complexity creates a burden on design and verification engineers so that the design effort needed for a project exceeds maximum productivity. A rendition of so-called design and verification gaps that portray the difference between effort and productivity is shown in Figure 1. The feature size that follows the Moore's law depicts the design effort needed for completing a complex project.

Figure 1. Design and verification gaps.

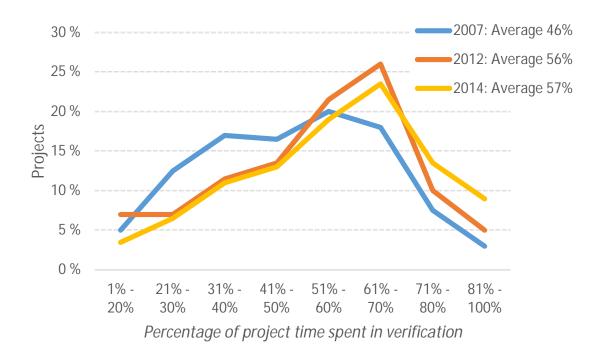

Increasing design reuse has decreased the design gap, but reuse in verification has not been as mature, so the trend is that the growth of the design gap will slow down but the verification gap will continue growing, as found in study done by Wilson Research Group in 2014 [12]. They found out that the percentage of application specific integrated circuit (ASIC) project time spent in verification has been growing rapidly as shown in Figure 2. Notably, the amount of projects where verification covers over 70% of the project time has been growing every time the study has been made.

Figure 2. ASIC project time spent on verification, as found in the Wilson Research Group study in 2014. [12]

# 1.1 Background of verification methodologies

Verification is a process that examines if all the aspects of the design follow the specification correctly [9]. Verification can be *functional* or *formal*. The difference is that functional verification runs a simulation of the design under test (DUT) in a *testbench* that feeds the design test input and checks its output, when formal verification proves the correct functionality with a mathematical model. *Validation* is another procedure in design functionality checking. Validation is used to ensure that the design meets the functional requirements and the needs of the customer.

Traditionally systems were first designed using hardware description languages such as VHDL and Verilog and then functionally verified using testbenches written in the same languages [19]. However, the hardware description languages were not designed to be effective in verification purposes and the system complexity quickly outgrew the verification capabilities of the language. Writing complex tests for large systems would be more effective with languages that function on higher levels of abstraction.

Specific *verification languages*, such as e and Vera, were created as an answer to the problem [10]. They were closer to traditional high-level programming languages and introduced for example object-oriented properties, complex assertions, coverage metering and constrained randomization to aid verification engineers. The problems with these languages were that learning a completely new language for verification meant a lot of unproductive work and the large set of languages might have prevented design engineers

from doing also verification. In addition, some of the languages were tied to specific software tools produced by the developer of the language and were not supported in other tools. The worst-case situation was that a company had to use multiple verification languages with accompanying tools to verify different parts of the design.

Verification languages are powerful and versatile tools but writing verification environments from scratch every time for new tests is not effective. Some parts of the code in existing systems can be reused, but there are no standard procedures built into the languages and therefore components written by different verification engineers may not be compatible. Companies can have internal guidelines, but the procedures used in one company may not be compatible with the guidelines of the subcontractor or the verification IP vendor. To ease the reuse and to provide a common system for testbench design, *verification methodologies* have been introduced. Simply put the verification methodologies are guidelines of functional partitioning of the testbench so that most of the components can be reused in different test configurations. In addition, the methodologies could provide methods, macros and control of the simulation procedure.

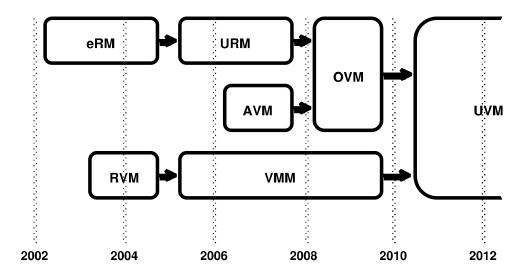

All the three design tool market leaders - Cadence, Synopsys and Mentor Graphics - had multiple competing methodologies written in different languages [8]. A hierarchy of the evolution of some of the methodologies is shown in Figure 3. E Reuse Methodology was first introduced in 2002 and it was followed by competing OpenVera Reference Verification Methodology (RVM) developed by Synopsys and Advanced Verification Methodology (AVM) by Mentor Graphics. New methodologies were later introduced that were built on the previous methodologies.

Figure 3. The evolution of verification methodologies. [8]

The diversity in languages, methodologies and tools created a need for universal industry standards. Accellera Systems Initiative was created as a consortium of EDA companies

for the task. The basis for a new standard language was a combination of Verilog hardware description language and OpenVera that was donated to Accellera. The result was *SystemVerilog* that was standardized in 2005 as an extension to Verilog [19]. A plan for a new standard methodology was introduced by Accellera in 2009 with a proposed name *Universal Verification Methodology (UVM)* [6]. It was built on the SystemVerilog language combining the previous methodologies OVM and VMM. SystemVerilog and UVM have since evolved and their usage in the industry has been constantly growing [11].

## 1.2 Motivation, methods, and scope of thesis

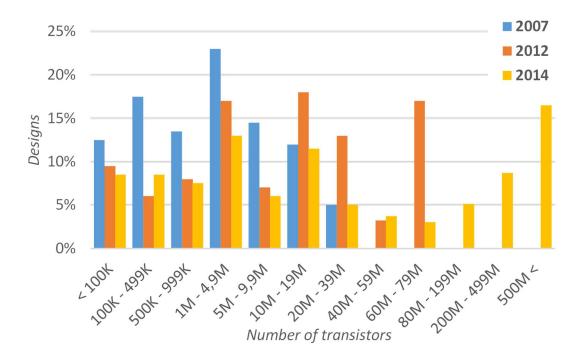

The trend in design sizes were observed in the Wilson Research Group study in 2014 to follow the Moore's law, as shown in the Figure 4 [12]. The majority of design sizes in 2014 were still on the same scales as in 2007, but the amount of designs on the highest border of the spectrum has been growing at the same time as the border has been moved to cover designs that are more complex.

Figure 4. The ASIC design size trends in 2014. [12]

As the design sizes trend to increase, efficient usage of verification methodologies would have a strong impact on verification productivity and shorten the time to market. The integration of verification methodologies as a valuable part of design projects requires education of verification engineers who master the concepts, because the methodologies are complex collections of precisely defined rules and principles that would take a long time to adopt from large reference manuals. An education that follows the standardized guidelines would ensure that the work done by different verification engineers is compatible.

Especially the companies starting to adopt UVM, but also those that have already integrated UVM and orientate new verification engineers, would benefit from a short and effective training. A specifically tailored education would cover all the target areas the company finds the most important and produce quickly new verification engineers that are ready to start implementing verification environments. An efficient education should also include lots of hand-on training that simulates the real verification tasks so the students can apply their knowledge to real-world problems and learn new principles at the same time.

This thesis presents the planning and implementation of an exercise package that can be used in an efficient verification education. The objective is to create an efficient exercise package that introduces the key concepts of SystemVerilog language and Universal Verification Methodology on a compact schedule. After finishing the exercises, a student with no previous verification or design background should understand the reasons for the amount of work done on verification and validation and be able to perform verification work using the current standard language and methodology.

The exercises were made as a part of a specifically tailored digital design and verification education that was ordered by a company. The aim of the education was to introduce employees with a programming background into hardware design and verification concepts and reeducate them to perform verification work using UVM.

The requirements for the verification module made by the customer dictated that the participants should understand the basic principles of verification, master the key mechanisms and syntax of SystemVerilog in the verification perspective and be able to use the UVM class library so that he can produce a working test environment.

The underlying theory of SystemVerilog and UVM is introduced on a level that would be required for understanding the scope of the exercises. The planned contents of each exercise is portrayed precisely, so that this thesis would help new assistants responsible for the same exercises to understand the concepts and the reasons for the used methods. Solutions for the exercises are not provided, so this thesis alone would not be sufficient for orientation material.

The planned exercise projects are tested by implementing them in the classroom as part of the education module. The metered results are the time usage in each exercise and a feedback form that was returned by the students after the education. Another interesting meter would be to follow if the participants in the education were placed later to perform verification tasks in the company and their later opinions on how the education prepared them for the tasks. This could have been monitored with a survey one year later after the education, but such a survey has not been done.

Pedagogy would be an important factor in education design to ensure that the selected teaching methods would best serve the learning process. Pedagogy was left out of the

scope of this thesis, but the planning of teaching methods follows subjective experiences of well-designed exercises during previous study work.

## 1.3 Outline of thesis

The thesis is divided into seven parts. Chapter 2 introduces the SystemVerilog language considering both the design and verification perspectives of the language. The purpose of the chapter is to provide an overview of the basics of the language and to explain the details of the concepts that are used in the following chapters. The most important concepts that would be emphasized in the exercises are outlined. Chapter 3 outlines the basic principles of Universal Verification Methodology on a level that was needed in this thesis and drafts a plan, how the principles are introduced to the student when planning the exercises. Small examples of advanced concepts are also introduced to widen the perspective and to introduce the possibilities that integrating UVM in verification process offers.

Chapter 4 explains the preliminary requirements for the training and introduces the selected teaching methods. It also provides information of the practical arrangements, such as the development environment and the tools used in the training. Chapters 5 and 6 explain the contents of the exercise instructions. Chapter 5 describes the SystemVerilog exercises and chapter 6 concentrates on the UVM portion of the training. A large number of code examples in these chapters are provided to offer a deeper understanding of the theory in Chapters 2 and 3.

Chapter 7 reviews the results of the training. The completion of the learning objectives was monitored with a time usage survey and a feedback form that are analyzed in the chapter. The chapter also explains the problems that were faced during the exercise sessions and offers improvement suggestions if a similar education is arranged later. Finally, Chapter 8 concludes this thesis.

# 2. SYSTEMVERILOG

SystemVerilog is a unified hardware description, specification and verification language that was first described in the standard IEEE 1800-2005 and most recently updated in 2012. It started as a set of extensions for the Verilog design language described in standard IEEE 1364-2005, but the two standards were merged into a single language in 2009 [15, 16]. The purpose of the original SystemVerilog extensions was to provide verification engineers with tools on higher abstraction level to improve productivity, readability and reusability. They also provided design specification methods such as new data types, packages, extended port declarations and interfaces [13, 14].

Because the two standard have been merged, this thesis does not differentiate the Verilog language from the SystemVerilog extensions, but describes the design and verification properties of the unified language following the IEEE 1800-2009 standard. Therefore, not all the code examples are fully compatible with the older Verilog standard. There are a few common Verilog design principles that are still used but upon which SystemVerilog has made improvements, so they have been considered to be worth explaining.

Understanding the basic SystemVerilog principles is mandatory for completing the exercises in the education module. This chapter introduces extracts from the language standard that explain the basic concepts that are used in the SystemVerilog and UVM exercises. The most important parts of the basic concepts are selected to form the learning objectives for the education.

# 2.1 SystemVerilog for design

The focus of the training module is on verification, but before inspecting the high-level verification properties of the SystemVerilog language it is beneficial to know the design-oriented side of the language, because the high-level verification language was originally an extension to the Verilog hardware description language. A verification engineer will also encounter designs to be tested written in SystemVerilog and knowing the design principles of the language will enable him to find and correct the bugs in the design. This section introduces the most basic design concepts of SystemVerilog that would be used in the SystemVerilog exercises with code examples.

The SystemVerilog design hierarchy consists of *modules* that are the basic building blocks [15]. Modules represent design units that have input and output ports and logic combining them. Modules communicate with each other usually through the input and output ports. Program 1 describes the declaration of a simple module that performs a bitwise and operation for signals a and b.

```

module simple_and (input wire a, b, output y);

assign y = a & b;

endmodule: simple_and

```

#### **Program 1.** Module declaration.

The module declaration in the Program 1 is started with the module header and ended with keyword endmodul e. The module header describes the *ports* and gives the module a specific *name* to differentiate it from other modules. The input and output port declarations in the header include the port directions and data types. If the data type is omitted, as is the case for the output signal y, it will be implicitly declared by the compiler. An *assign* primitive is used to set the output value and to form the logic between the ports.

The module header in Program 1 where the port directions are listed follows the *ANSI* type declaration of SystemVerilog. The ANSI type declaration is not supported in the Verilog language and the traditional way is to declare only the data types in the header and the directions on the first lines after the declaration. The ANSI method is advised to be used, because it reduces unwanted repetition.

Modules can be instantiated inside each other to create design hierarchy, as shown in Program 2. In the example a top-level module, that has no input or output ports itself, creates an instance of the simple\_and module that was described in Program 1. Internal variables in1, in2 and out1 are connected to the ports of the instantiated module.

```

module top; // module with no ports

logic in1, in2; // variable declarations

wire out1; // net declaration

// module instance

simple_and u1 (

.a(in1),

.b(in2),

.y(out1));

endmodule: top

```

#### **Program 2.** Module instantiation.

Modules were chosen to be an integral part of the learning objectives, as they are the basis for every SystemVerilog design. The first thing the student should learn in the exercises should be to declare a module using the ANSI type declaration but he should know of the existence of non-ANSI type declaration as well. He should also be able to instantiate modules to create hierarchical designs.

*Procedural statements* describe behavioral code, where programming statements, for example if-else, case or for loop structures, can be used to describe the functionality. The statements usually contain a *sequential block* delimited by keywords begin and end, where the statements are executed sequentially in the given order so that all the statements

inside the procedure act syntactically like a single assignment. There are two basic types of procedures: *initial* and *always*. Initial procedures run only once and they are usually used for variable initialization. Always procedures describe combinational or sequential logic that is run triggered by events in the sensitivity list. The sensitivity list is declared using the character @.

SystemVerilog introduces separate *always\_comb* and *always\_ff* procedures that specifically state the designer intention. The benefit of using these new procedures is that the compiler should generate a warning, if the desired function is not achieved. An always\_comb procedure has an inferred sensitivity list so that it is run every time any of the signals used in the procedure change. An always\_ff procedure always generates sequential logic and the sensitivity list should contain clock and reset signals. Simple examples of always\_comb and always\_ff procedures are shown in Program 3. The always\_comb procedure describes a 2-to-1 multiplexer. The output signal y is connected to the a or b input depending on the selection signal sel. The always\_ff procedure is set to run on every rising edge of the clock signal when the asynchronous reset is set high and update the d input value to q output. On the falling edge of the reset signal, the output is set to 0, where it stays until the reset is set high.

```

// An always_comb procedure describing combinational logic

always_comb begin // procedural block

if (sel) y = a; // procedural statement

else y = b;

end

// An always_ff procedure describing a D flip-flop

always_ff @(posedge clock iff reset_n == 1 or negedge reset_n) begin

q <= reset_n ? d : 0;

end</pre>

```

#### **Program 3.** Procedure example. [15]

The learning objectives should include procedures and sequential blocks near the beginning of the SystemVerilog exercises. Because most of design work uses synchronous logic, the exercises should concentrate on the always\_ff procedure, but also introduce initial and combinational procedures.

The data types in SystemVerilog are divided to *nets* and *variables*. Nets represent physical connections and do not store data. Therefore, they cannot be used in procedural statements. The most common net type is *wire*, which is a 4-state type. 4-state types can have values '1', '0', 'X' or 'Z', where 'X' represents an unknown logic value and 'Z' is a high-impedance state. 2-state data types also exist. They can have only values 0 and 1, but they are not synthesizable and are meant to be used in simulation to reduce overhead.

Variables can store data and can be written in procedural statements unlike nets. The most common variable type is *logic*, which is a 4-state type. In Verilog, the basic variable type was *reg*, but it has been renamed to logic to avoid confusion, as the name reg can be

perceived to imply a hardware register. The reg data type still exists in SystemVerilog, but the use of logic is preferred.

Variables and nets can be declared as *arrays* in either *packed* or *unpacked* structure, as shown in Program 4. A packed array declaration has the dimensions declared before the name. Packed arrays always represent a contiguous set of bits. A one-dimensional packed array is often referred to as vector, in which every element can be conveniently accessed. Multidimensional arrays are also supported. There are data types, for example integer, that are already packed arrays of predefined widths and therefore they cannot be declared as packed arrays.

Unpacked arrays can be used to declare multiple similar signals that are not required to be contiguous, for example if the signals are connected to different components. The declaration has the array dimensions after the name. Any data type can be used as unpacked arrays. The statement on the second line of Program 4 declares an 8-element unpacked array vectors that contains 32-bit vector values.

```

logic [31:0] vector1; // a 32-bit wide unpacked array of type logic

logic [31:0] vectors [7:0]; // packed array of 8 32-bit unpacked arrays

```

### **Program 4.** Packed and unpacked array declarations.

The most important data types are logic and wire and their usage should be part of the training. Packed arrays should also be emphasized and only mentioning the existence unpacked arrays would be sufficient. The exercises should concentrate on the current SystemVerilog syntax, so the data type logic is preferred over the older reg type. 2-state data types would require less attention in the SystemVerilog exercises as they are a more abstract concept, but their usage would be introduced in the UVM exercises.

To enhance reusability modules can be *parameterized*. The list of module parameters is declared in the module header between the module name and the port list using the character # as shown in Program 5. The example shows the header of an adder module, in which the widths of the input and output data signals are set using the data\_width\_g parameter.

**Program 5.** Parameterized module header.

Defining array widths is an important design concept in terms of reusability, because then the same component can be used in different systems that incorporate different data widths. Therefore, parameters should be introduced in the first SystemVerilog design exercises. More advanced parameters would not be needed in the SystemVerilog part of the training.

*Interfaces* is a concept introduced in SystemVerilog that enhances design reuse by encapsulating the communication between design blocks. An introduction to interfaces was requested by the customer, and their usage would be deeper explained in the UVM exercises.

For example, in a large design where multiple components connect to the same complex data bus, the bus signals can be declared only once in the interface construct and then the modules can be declared to use the interface. An example of a memory interface is shown in Program 6. The interface block describes all the signals and two *modports* for master and slave components. The modports are used to set the signal directions. Interfaces can be parameterized as well.

```

interface mem_bus(input logic clk); // Interface header

// Signals in the interface

logic read, write;

logic [7:0] addr, wdata;

logic [7:0] rdata;

// Modports set the signal directions

modport master (input rdata, output read, write, addr, wdata);

modport slave (input read, write, addr, wdata, output rdata);

endinterface: simple_bus

module memory(mem_bus.slave bus0);

endmodul e

// Connect the modules on top level

module top;

mem_bus bus0();

memory 12(.bus0(bus0));

endmodul e

```

## **Program 6.** Interface example.

Assertions were an important part of the learning expectations for the SystemVerilog exercises and they should require a separate exercise. They ensure the behavior of the system and are used to validate the design. SystemVerilog has an advanced assertion language built in to allow complex assertions that could monitor the execution during multiple clock cycles. Assertions can be declared using keywords assert and assume. Assert assertions specify obligations for the design that must always hold and assume assertions are used to specify assumptions for the environment, for example the format of the input data that formal verification tools could use to generate test input. Assertions can also be used to provide functional coverage data.

SystemVerilog assertions can be either *immediate* or *concurrent*. Immediate assertions are checked every time the statement line is run following the simulation event semantics. They are intended to be used in simulation. Concurrent assertions are always active based on clock semantics and use sampled variable values. They can be used to describe behavior that spans over time, for example to check signal values during multiple clock cycles. The concurrent assertions can also be used in formal verification tools in addition to event-based simulation.

Program 7 introduces an example of an immediate assertion that can be used in simulation. The assertion checks on every rising edge of the clock that logical or operation of signals req1 and req2 is always true. If the assertion fails, the simulator will print an error message including the current simulation time, as specified in the else branch. If the else condition is not specified, the default procedure is to use an error print.

```

time t;

always @(posedge clk)

if (state == REQ)

assert (req1 || req2)

else begin

t = $time;

#5 $error("assert failed at time %0t",t);

end

```

**Program 7.** An immediate assertion. [15]

Program 8 shows an example of concurrent assertions. This assertion ensures that every time the enable\_in signal has a rising edge, the signal valid has to be set to 1 after two clock cycles. The assertion is tied to the rising edge of the clock signal, but disabled if the system is in reset. Concurrent assertion can be very complex and used to validate correct signal behavior over long time.

**Program 8.** A concurrent assertion.

# 2.2 SystemVerilog for verification

A significant difference between Verilog and SystemVerilog is the support for object-oriented programming for verification purposes on a higher abstraction level. The vast language reference is not completely explained in this section, but only the basic object-oriented properties that are needed for understanding the structure of UVM. The learning objectives for the exercises required that the object-oriented properties should be covered in the exercises and this section provides an overview of the required concepts. The concepts would be introduced to the student in UVM exercises.

The object-oriented properties in SystemVerilog follow object-oriented programming guidelines very closely, so the structure is familiar for designers who have programming experience in C++, Java or other object-oriented languages [19]. The main benefit in object-oriented testbench design is that the designer can declare complex data types and combine them with routines that use the data. Instead of toggling bits in the DUT directly, those routines can be used to perform even complex transactions without considering the state of every bit on every clock cycle.

The basic building block for a high-level testbench in SystemVerilog is *class*. The class encapsulates *data* and *routines* together in a single block of code. A class declaration for a simple transaction packet is shown in Program 9. The class BusTran contains variables for an address vector and a data array and it has two routines: one that prints the address in the packet and one that calculates a cyclic redundancy check of the data to the variable crc.

```

class BusTran;

bit [31:0] addr, crc, data[8];

function void display;

$display("BusTran: %h", addr);

endfunction : display

function void calc_crc;

crc = addr ^ data.xor;

endfunction : calc_crc

endclass : BusTran

```

**Program 9.** A simple class declaration. [19]

Routines can be either *tasks* or *functions* [15]. The example in Program 9 uses functions with the return type of void. The difference between tasks and functions is that the functions can have input and output values and are processed without blocking the simulation time – in the simulation perspective they return their value immediately. Tasks do not return a value, but can block the simulation time during execution, so tasks have a concept of time. Tasks can incorporate delays to bind the processing to a certain moment of time, a signal value or to another event.

Classes are instantiated as *objects*. An object has a type and a name and the instantiation is done by first creating a variable of the type of the class to hold an object *handle* and after that the object is created and assigned to the variable using the function new that is called a *constructor*. An example instantiation is shown in Program 10. The object creation in SystemVerilog reminds of C++ or Java, but the memory allocation and deallocation of C++ is not needed. Object construction is simple and garbage collection is performed automatically.

```

class Packet;

integer command;

function new();

command = IDLE;

endfunction

endclass

...

Packet p; // declare a variable of class Packet

p = new; // initialize variable to a new allocated object

// of the class Packet

```

#### **Program 10.** Class instantiation. [15]

New classes can be derived from base classes using the *extends* keyword [15]. The declared properties and methods in the base class can be accessed using the keyword super, or overridden by declaring new methods. Program 11 shows an example, where the class Li nkedPacket is derived from the Packet class described in Program 10. The Li nkedPacket class is a special form of the class Packet, which introduces a new method get\_next that returns an object of the type Li nkedPacket. As the Li nkedPacket is extended from the Packet class, every Li nkedPacket object is a legal Packet object. A Li nkedPacket object handle can be assigned to a variable of type Packet.

```

class LinkedPacket extends Packet;

LinkedPacket next;

function LinkedPacket get_next();

get_next = next;

endfunction

endclass

```

### **Program 11.** Class inheritance. [15]

Class declarations in SystemVerilog, including routines and inheritance, will be introduced to the student in the UVM exercises and therefore they will not require a separate exercise in the SystemVerilog part of the training. The syntax of SystemVerilog for verification is not emphasized as the motive for any UVM exercises, but it will still be listed as one of the important learning objectives that the student will learn on the side when he is getting familiar with UVM.

SystemVerilog has also introduced new block statements in addition to the sequential blocks that are delimited by the begin and end keywords [15]. There is also a *parallel block* that is delimited by keywords fork and join. All the statements in the block are processed concurrently, so the code in Program 12, that sets the value of the variable r after certain clock cycle delays, finishes 200 clock cycles after entering the block. A similar sequential block would process the assignments one at the time, so the processing time would be 500 clock cycles when all the delays are added together. If the execution does not have to wait for all the forked statements to finish, additional join keywords

j oi n\_none and j oi n\_any can be used to change the behavior. As functions do not have a concept of time, the usage of parallel blocks in the functions is limited.

```

fork

#50 r = 'h35;

#100 r = 'hE2;

#150 r = 'h00;

#200 r = 'hF7;

join

```

**Program 12.** An example of a parallel block [15].

Parallel blocks are not important for the education because they would not be required for the designs in the exercises. Therefore, they will be omitted from the exercise instructions. Using parallel blocks in a UVM testbench would allow more complex testbench designs, but finding them out is left for the student himself. If the student declares a need for parallel processing in his testbench, the assistant can hint the usage during exercise sessions.

# 3. UNIVERSAL VERIFICATION METHODOLOGY (UVM)

Unified Verification Methodology (UVM) is a class library written in SystemVerilog. It is developed and standardized by Accellera, which is a consortium of EDA tool vendors and users including Synopsys, Mentor Graphics, Cadence, AMD, Intel, ARM and other companies [2]. Accellera released a press release in July 2015 where it was announced that UVM will be submitted as IEEE standard IEEE 1800.2 and the work is currently in progress [1].

The purpose of UVM was to combine the principles of several verification methodologies, mainly OVM and VMM, into a single standard methodology to be used across the field. The Accelera verification IP technical subcommittee declared in a release on January 2010 that the methodology will "enable users to deploy an efficient, reusable, and interoperable SystemVerilog verification environment." [6]

Mentor Graphics commissioned the Wilson Research Group Functional Verification Study in 2016 on the state and trends of verification on ASIC/IC market [11]. According to Harry Foster from Mentor Graphics, the studies performed every second year were "world-wide, double-blind, functional verification studies, covering all electronic industry market segments. To our knowledge, the 2014 and 2016 studies are two of the largest functional verification study ever conducted."

The adoption trends found in the study for various ASIC/IC testbench methodologies built using class libraries are shown in Figure 5. Based on the study, UVM is already widely used in the industry and its popularity has been rising at the cost of older methodologies every time the study has been conducted. According to the results, over 70% of the participants already used UVM and the trend was that in 2017 the number would be higher. It should be noted that selection of multiple verification methodologies was possible in the study, so companies that have only started adopting UVM but mainly use other methodologies might be visible in the numbers. [11]

Figure 5. ASIC/IC testbench methodology adoption trends. [11]

This chapter provides an overview of the UVM concepts that have been described in the learning objectives for the exercises. The concepts are analyzed so that the most important content forms the basis for the training material and less relevant information can either be omitted, mentioned as a curiosity or used in more advanced exercises.

The code examples given are very abstract and the more precise usage of the UVM macros, methods and components is described in Chapter 6, which covers the contents of the UVM exercises. The first five exercises in Chapter 6 contain the steps needed for building a complete UVM testbench with code examples.

# 3.1 UVM building blocks

The structure of a UVM testbench consists of small and relatively simple components that are built hierarchically. The tests that contain information of how the DUT should be tested is separated from the environment that describes how the DUT should be connected to the testbench.

The benefit of dividing the testbench into small components is simplifying the testbench design and reuse. Reuse can be horizontal and vertical, so in addition to reusing components in new testbenches, the verification environments for single blocks can be integrated together to form subsystems that can be integrated further to implement system level testing.

Since the UVM testbench is built from dynamic objects, that do not exist in memory before they are created, a static component is needed for launching the simulation [5]. The static component in UVM is a top level SystemVerilog module that includes pin connections to the DUT and starts the test, which then configures the environment and runs a sequence of transactions to the DUT.

The student should be instructed to declare his own components in the UVM exercises and he should gain an understanding of how to reuse his own components. Both the horizontal and vertical reuse should be explained in advanced tasks. The existence and function of the top-level module should be explained, but writing such a module would not be the most important part in UVM to be mastered by the student.

The UVM testbench file hierarchy uses SystemVerilog *packages*. Packages are constructs that combine related declarations and definitions together in a common namespace that is a single compilation unit for the simulator. To access the namespace and the underlying definitions the package must be imported. The usage of packages allows the testbench developer to organize the code and ensure consistent references to types and classes.

A package file should contain all the related class declaration files [5]. For a simple UVM testbench a single package could contain all the definitions, but in a large system level testbench the declarations could be divided between multiple packages so that there is a separate package for every bus interface and a number of packages for different types of test sequences that contain all the declarations for running different tests. Instead of declaring all the classes directly in the package file, the coding guidelines by Mentor Graphics state that every class declaration should be in a separate file and all the declaration files are included in the package using a SystemVerilog include directive. The include directive instructs the compiler to insert the entire contents of a source file inside another file in place of the directive. The package should only contain the include directives for class declaration files.

The approved use of include macros and import directives should be explained to the student to ensure that the focus in reusability is emphasized from beginning. The testbenches in the exercises would be simple so that the whole hierarchy can be declared in one package, but in a more advanced additional exercise, multiple sublevel packages could be introduced.

# 3.1.1 Objects and components

Object is the basic building block in a UVM testbench and all the objects are extended from the uvm\_obj ect base class [3]. The primary role of the uvm\_obj ect base class is to define the common methods for basic operations, for example create and print, that are used for every object. It also defines instance identification interfaces, for example name and unique id. The most basic objects are data packages sent to the DUT that are instantiated as sequences of packages to generate test input.

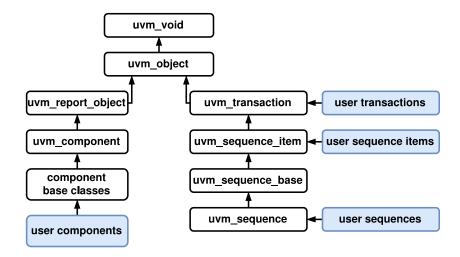

A hierarchy tree of the most basic UVM classes is introduced in the Figure 6. The base class uvm\_obj ect is supplemented with a reporting interface to form a uvm\_report\_obj ect class. The class uvm\_report\_obj ect is extended further into uvm\_component class that introduces a concept of hierarchy and properties needed for creation and connection of

components. The uvm\_component class is further extended to the base classes of the components that are implementable by the user as shown in the figure. On the other branch uvm\_obj ect is extended into transactions and sequence items that form a sequence of items that are delivered to the DUT. The highlighted classes can be created by the user.

Figure 6. UVM base class hierarchy. [3]

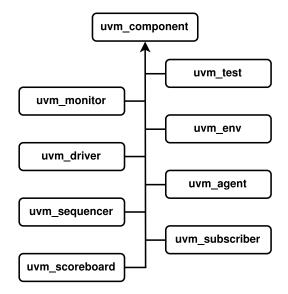

All the component base classes are derived from the uvm\_component that contains all the common properties making the base classes of the separate components relatively simple [3]. A hierarchy tree of the common UVM components is shown in Figure 7. Deriving every component from the matching base class allows the testbench designer to distinguish components from each other and ensures that the components will benefit from all the features built into the base class. Some component base classes, for example uvm\_monitor, are just empty shells that do not add any additional features to those derived from the uvm\_component, but functionality may be added in the future UVM versions.

Figure 7. UVM component class hierarchy. [3]

The complicated class inheritance system allows the user to write simple implementations of components, because the core functionality is built into the base class. The user can extend his own class implementations as well enhancing reusability. When the user-defined components are simple, they require less rewriting when used in other testbenches. The selection of correct base classes for the student's own objects and components should be emphasized in the exercises. After the training, the student should be familiar with the class inheritance hierarchy of the most common classes in UVM so that he would know the difference between the object and component base classes. He would also see in practice in advanced tasks, what are the changes that are mandatory for the components when a UVM testbench is converted for testing a different design.

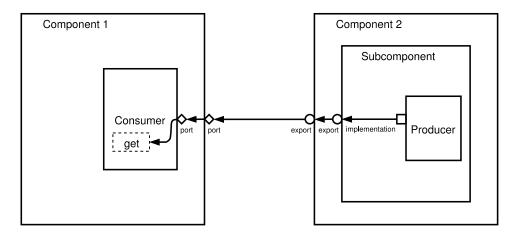

The components can communicate with each other by delivering transaction level modeling (TLM) transaction objects or by reading and writing the UVM configuration system. The TLM transactions are delivered via channels between ports and exports that are introduced in components and then connected to each other. A port is instantiated in components that initiate transaction requests. The ports are connected to implementations in components that implement the initiated methods. Exports are channel items that forward an implementation to be connected by the port.

Figure 8 describes a block diagram in which the consumer instantiated inside the component 1 wishes to get data from the producer that is instantiated in subcomponent inside component 2. To create the connection, the implementation of the producer is connected to the port of the consumer via ports and exports on higher levels. When the consumer calls the get procedure, the data flows in the direction of the arrows. The implementation is marked with a square  $(\Box)$  in the picture. The diamonds  $(\diamondsuit)$  are ports and the circles  $(\circ)$  are the exports.

*Figure 8.* Port – export – implementation connection. [3]

The usage of ports and exports should be explained to the student. He would see in practice how the initiator calls the transfer functions of the implemented port and how the functions are declared in the components including the export. He would also declare ports and exports himself.

#### 3.1.2 Macros and methods

UVM includes *macros* that provide users a shorthand notation for SystemVerilog constructs. The macros can define object behavior and interaction with the internal UVM mechanisms and assist in reporting. Macros are defined beginning with the grave accent character (`), which should not be confused with the apostrophe (').

All the reporting in UVM should be done using *reporting macros*, because they handle the filtering of unneeded messages to reduce processing overhead [3]. The reporting macros also automatically provide file names and line numbers in the prints done by the testbench and ensures that the user does not accidentally prevent printing of warning and error messages by setting a verbose level. Examples of reporting macros are shown in Program 13. The parameters for the macros are the message identification, INF01 and WARN1 in the program, and the message to be printed [5]. The uvm\_i nfo macro can also include a level of verbosity for filtering of the messages. A sformatf method is used to format the info message using the syntax similar to printf function in the C language. There are also similar macros for errors and fatal errors.

```

`uvm_info("INF01", $sformatf ("data: %0d", data), UVM_LOW)

`uvm_warning("WARN1", "This is a warning")

```

#### **Program 13.** Examples of UVM reporting macros.

Other important macros are the *factory registration macros* [5]. The *factory* is a class internal to the UVM mechanisms, which takes care of creating UVM objects and components and maintains a list of every instantiation done in the testbench. All the objects and components should be registered to the factory by performing a factory registration macro:

```

`uvm_component_utils(my_class)

```

There are separate registration macros for objects and components. The purpose of the registration macro is to help the factory to keep a record of every object and component in the testbench. The classes can be later substituted with another compatible class by using the factory without changing the underlying component hierarchy code. In addition to the registration macro, the class instantiation should be done using a special factory method instead of calling the constructor function directly. The factory method will call the constructor function of the classes, but also performs additional procedures that are mandatory for the function of the UVM factory. The syntax for the factory method for instantiating an imaginary class comp is following:

```

comp_h = comp::type_id::create("comp_h", this);

```

The factory registration macro should be introduced to the student when he is instructed to declare his first class to ensure the correct structure of the testbench from the beginning.

Reporting macros should be introduced so that the uvm\_info would be explained first and the knowledge would be deepened later by providing the more severe alternatives.

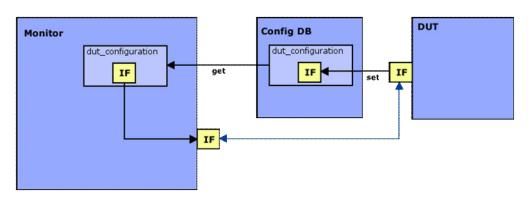

Another important internal mechanism of UVM is the *configuration database*. The configuration database stores variables to be read in the components to allow communication across the testbench during runtime. In addition to the variable name and value, a scope is set that dictates the hierarchical path to the component using the value. The configuration database can be written and read by every component by using functions set and get. Usage of the configuration database enhances efficient reuse by making the components in the testbench more configurable.

The configuration database would be used in the exercises to deliver a pointer to the DUT interface from the top-level module to the testbench components that communicate with the DUT. More advanced exercises could also mention other configuration for the testbench, but the delivering of the virtual interface would be enough to show the function of the database.

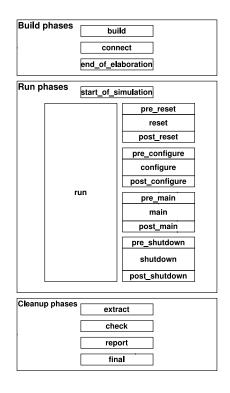

The simulation of UVM is divided into *phases*. The sequence of the UVM phases is shown in Figure 9. There are 21 simulation phases in total and they can be divided into three categories. In the beginning of the simulation the build time phases construct the test environment by building components using the factory, form the connections between the TLM channels and configure all the components using the configuration database. The build time phases do not consume simulation time.

Figure 9. UVM Phases. [5]

After the test environment has been constructed, the run-time phases are started and the simulation time is consumed. The run-time phases carry out the actual simulation where the test case is run for the DUT. After the test has been stopped, simulation time is not consumed anymore and cleanup phases collect the results of the test case and report them.

The functionality of components in every simulation phase is configured by providing specific phase methods in the class declarations. Not all the 21 simulation phase methods have to be declared in every class declaration, but only the methods where the component should have user-specified activity. The high number of phases allows a common understanding on what should happen in each phase of the simulation when verifying complex designs, even when the components are developed by different engineers.

An example of the usual phase methods for an imaginary class is shown in Program 14. The build phase method creates components that are lower in the hierarchy by using the factory instantiation method. The connect phase function follows the build phase and performs the connections between the components created in the build phase. On run phase, an imaginary data object is created and commanded to start execution. The run phase consumes time during simulation, so the type of the phase method is task. All the phase tasks have to use specified method names and be parameterized by the UVM phase as in the example. [5]

```

function void build_phase(uvm_phase phase);

// create two components of type comp

comp1_h = comp::type_id::create("comp1_h", this);

comp2_h = comp::type_id::create("comp2_h", this);

endfunction: build_phase

function void connect_phase(uvm_phase phase);

// Call the connect method to connect the implementation to export

Comp1_h. conn_imp. connect(comp2_h. conn_exp);

endfunction: build_phase

task run_phase(uvm_phase phase);

...

// create a object of type obj and call its start method

obj_h = obj_type::type_id::create("obj_h");

obj_h.start(...);

...

endtask: run_phase

```

**Program 14.** Examples of phase methods.

The exercises should focus on the most important build, connect and run phases, because these phases implement the basic methods of UVM. The instructions could mention that there are more phases as well, but the testbenches to be designed in the exercises would not require declaring methods for them.

## 3.2 UVM architecture

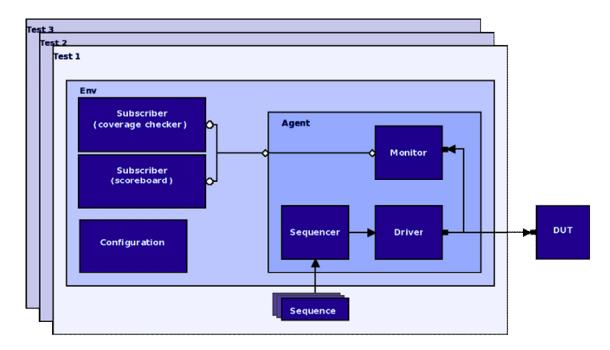

The architecture of a UVM testbench consists of user-defined components extending base classes in the UVM library [5]. Every component has a name and a parent in the testbench hierarchy and they are instantiated in the build phase by using the UVM factory in a top to bottom order. An example of a block level UVM testbench is introduced in the Figure 10. The example in the figure contains an UVM environment that is used in multiple tests. The example environment contains agents for interfacing the two bus interfaces and components for test coverage monitoring and the functional checking of the DUT.

*Figure 10.* A complete block level testbench. [5]

The UVM architecture will be an important learning objective in the exercises. The student should be able to distinguish between the test and the environment. He should know the most common UVM components on a level that he should be able to declare a simple UVM testbench himself using a correct hierarchy.

#### 3.2.1 UVM Environment

The *environment* is the component that describes the physical architecture of the testbench [4]. It instantiates all the components hierarchically and one environment can contain multiple sublevel environments. On system level testbenches there could be one top-level environment that instantiates multiple environments for each block of the design. The same block level environments cold be used for block level testing before integration. The method of building a system level testbench from block level environments is often referred to as *vertical reuse*.

The environment contains one or more *agents*, which communicate with the DUT, and *subscribers*, which use the data provided by the agents. An agent is a component that instantiates the components that manage the stimulus flow, feed the input data to the DUT and monitor the signals that move between the testbench and the DUT. If the DUT communicates with multiple interfaces, there is usually one agent per interface. An agent could have an active or passive role set by the configuration database: an active agent provides stimulation data for the DUT and a passive one only monitors the transfers.

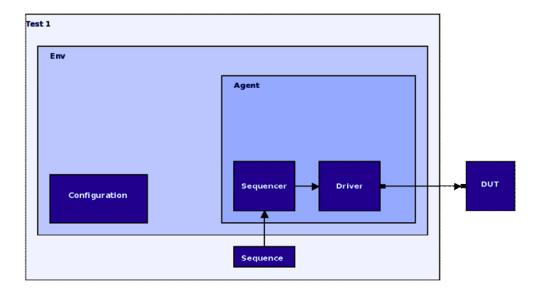

The first testbench to be designed by the student would be simple and contain only one environment that has one agent. The passive and active roles of the agent could be introduced, but not emphasized in the beginning. More advanced tasks could introduce the usage of multiple agents. The student should know after the exercises what the role of the agent is and what components it includes.

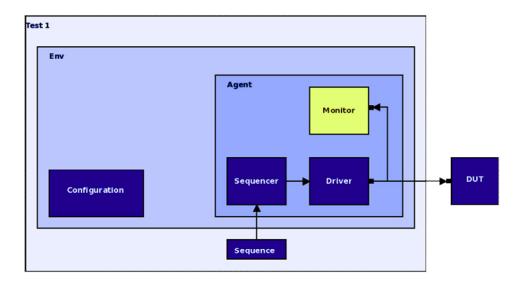

The usual components instantiated within the agent are *sequencer*, *driver* and *monitor*. The *sequencer* is an arbiter that reads sequence objects from a list and controls the sequence flow. The sequences are delivered as TLM transactions. The *driver* receives the TLM transactions from the sequencer and drives them to the DUT. Thus, the driver transforms the abstract transaction level sequences into pin-level activity in the DUT.

*Monitor* is a component that follows the activity in the DUT interface and samples it. The pin-level activity in the DUT is converted into TLM transactions and sent out for analysis. The monitor includes an analysis port that delivers TLM data further into the testbench. In a passive agent, the sequencer and the driver are turned off and only the monitor is active.

The data sent out by the monitor is analyzed by the subscribers that implement analysis exports, which connect to the analysis port in the monitor. The subscribers usually reside outside the agent in the environment, but can be instantiated in the agent as well in more complex designs. The subscribers answer to the questions "How does the DUT perform?" and "How much have we tested so far?" [4]

Coverage collector is a subscriber that gathers functional coverage data [5]. It samples all the transactions sent by the monitor and uses the data to increment counters in *cover-groups*. Covergroups specify the signals and conditions that are to be monitored as *cover-points*. The counter values for each coverpoint represent real-time functional coverage data of situations that have and have not been tested.

Scoreboard is the UVM component that determines if the DUT functions properly. It specifies a reference model and compares the output produced by the DUT to the reference. In simple designs the reference the model and comparator can be declared in a single component, but it is also possible to use separate components or even use an outside model of the DUT as the reference. [5]

The exercises should include a coverage collector and a scoreboard, because they are components that use the data provided by the monitor and implement the testbench functionality that answers the questions "Have we tested enough?" and "Does the DUT perform correctly?" The student should examine test coverage data provided by the coverage collector he has declared and verify the functionality of the DUT by comparing its output to a functional model.

### 3.2.2 UVM Tests

Test is the top-level component of a UVM testbench [4]. The test controls the building and configuration of the test environment, selects the stimulus sequence to be used in the test and controls the simulation process. There can be multiple tests using the same environment but different sequences and configuration. It is common to declare a base test class that instantiates the environment and does the necessary configuration, and then extend tests from it to cover different test cases for the DUT.

Sequences are lists of objects that are delivered to the sequencer in the agent [5]. The sequencer processes the list item by item. The sequences can be layered on top of each other to provide means of describing the complex transactions that include multiple layers such as USB 3.0 or PCI express. A higher-level sequence can control the transactions on a higher abstraction level and command the lower level sequences that work closer to the hardware.

Variables in sequences can set to be *randomized* to allow randomized testing. *Constraints* can be set to limit the randomization to include a specific value range or to set distributions so that a signal can be for example set high 95% of the time, but low for the rest. The concept is used in constraint random testing that was part of the learning requirements.

The simulation run is controlled by an *objection* mechanism [4]. In the start of the run phase the test raises objection and the simulation runs until all the objections have been dropped. This way a component can inform the testbench that it is not ready yet for stopping the simulation by raising another objection.

If there are multiple tests, the top-level module of the testbench specifies the test to be run by declaring the test name as a parameter for the run\_test method:

```

run_test ("test_base");

```

The test name can also be given as a parameter to the simulator, if the parameter is not provided for the run\_test method. In terms of reusability, the better way to start the specific test would be to omit the test name from the top-level module and declare it when starting the simulation using the UVM\_TESTNAME flag. That would allow the user the run different tests without modifying the code.

A base test and sequence should be provided ready for the student, so the first exercises could concentrate on the UVM environment. Later exercises, when the environment is ready, should include multiple tests that use a constraint-randomized sequence extended by the student from the provided classes. The student should also encounter the usage of objections. Layered sequences are more advanced UVM concepts and they will not be introduced in the exercises.

The original learning requirements made by the customer also dictated that the UVM register abstraction layer (RAL) should be introduced. The RAL provides a way of controlling the contents of the registers in the DUT and introduces a convenience layer to the register and memory locations. As it was later agreed in a meeting that the RAL should only be covered on a lecture basis, the deeper function of the RAL is not covered in this thesis.

# 4. REQUIREMENTS AND METHODS FOR THE TRAINING

The verification training module was split into ten days, of which five were lecture days and five were used in exercises. Two of the exercise days were for SystemVerilog and three for UVM. The schedule for the verification education module is shown in Table 1. The first four days of the module were lectures, after which there was a second part of six days with mostly exercises and one lecture day in between about UVM. All the lectures were held at the customer's premises and the exercise days were in the computer classroom TC221 at Tampere University of Technology.

Day Theme 15.9.2015 Lecture: Verification - Principles & methodologies (1) 16.9.2015 | Lecture: Verification - Principles & methodologies (2) 28.9.2015 | Lecture: Verification – Systemverilog (1) 29.9.2015 Lecture: Verification – Systemyerilog (2) 5.10.2015 Exercises: Verification - Systemverilog (1) 6.10.2015 Exercises: Verification – Systemverilog (2) 22.10.2015 Lecture: Verification - UVM 23.10.2015 Exercises: Verification – UVM (1) 29.10.2015 Exercises: Verification – UVM (2) 30.10.2015 Exercises: Verification – UVM (3)

**Table 1.** The schedule of the verification module.

# 4.1 Requirements and student background

According to the requirements for the module, the student should know the following concepts:

- 1. DUT

- 2. Testbench

- 3. Functional simulation

- 4. Coverage

- 5. Coverage driven verification

- 6. Directed test

- 7. Constraint random test

- 8. Assertions

- 9. Assertion based formal verification

He will also master the key mechanisms and syntax of the SystemVerilog language in the verification perspective and the UVM class library so that he can produce a working test

environment using UVM. The requirements covered both the lectures and exercises. The requirements for the content of the exercises were redefined in meetings with the customer and the final learning objectives are explained in the chapters 5 and 6 that cover the planning of the exercises.

The participants in the education were professionals in information technology and telecommunications with experience of programming and software development. Some had former hardware design experience as well and some participated in the digital design education module. It was dictated by the customer that because verification is programming by nature, the module should be introduced to the students so that they were essentially learning a new programming language.

### 4.2 Tools used in the exercises

The exercises were designed to be run using the Mentor Graphics Modelsim simulation tool. Modelsim was chosen, because it is created by a major vendor and therefore a common tool in the industry. Modelsim also has the UVM library included, so there was no need to compile it. Mentor Graphics has also a more advanced QuestaSim verification tool available, but it was decided that it would offer no real benefit in this case and the essential usage of Modelsim is completely similar.

Instead of running the Modelsim directly on the class workstations running Windows 7, a Linux virtual machine was decided as a platform. The Linux environment allows the use of make automation tool that eases the compiling and running of the simulations because a multitude of parameters are needed for UVM simulations. Using a virtual machine also allows a diverse set of text editors – the students had a choice of common tools from both the Windows and Linux environments including Notepad++, Emacs, Gedit and vi.

The Linux Modelsim packages already available on the department network drive limited the selection of the operating system into Red Hat Enterprise Linux or its derivatives. Centos Linux 6 was selected, because it is a free community-driven alternative to Red Hat Enterprise Linux and the installation packages were compatible with it. There was also a newer Centos 7 version available, but the more traditional Gnome 2 user interface of Centos 6 was more appropriate for usage in class compared to the Gnome 3 in CentOS 7, and it was already proven to work on other courses on the department in which a virtual machine has been utilized.

The students had no access to any network drives because of their temporary guest accounts. Therefore, every student was given a USB memory for storing his or her data between exercise sessions. The virtual machine was reset every night to ensure similar experience between workstations and the students were advised to either use a temporary folder on the Windows host machine that would be shared for the virtual machine, or alternatively access the USB memory directly from the virtual machine for data storage.

### 4.3 Structure of exercises