# LETICIA TRINIDAD VALDERAS RODRÍGUEZ A COMPILER FRAMEWORK FOR A COARSE-GRAINED RE-CONFIGURABLE ARRAY

Master of Science Thesis

Examiners: Prof. Jari Nurmi Dr. Waqar Hussain Examiners and topic approved by the Faculty Council of the Faculty of Computing and Electrical Engineering on 6th May 2015

ii

### ABSTRACT

LETICIA TRINIDAD VALDERAS RODRÍGUEZ: A Compiler Framework for a Coarse-Grained Reconfigurable Array Tampere University of Technology Master of Science Thesis, 55 pages June 2015 Master's Degree Programme in Information Technology Major: Electronics Engineering Examiner: Prof. Jari Nurmi Dr. Waqar Hussain

Keywords: Compiler, CGRA, MVM, RPN, Place and Route, SCREMA, COFFEE RISC, CREMA

The number of transistors on a chip is increasing with time giving rise to multiple design challenges. In this context, reconfigurable architectures have emerged to provide high flexibility, less power/energy consumption yet while delivering high performance levels. The success of an embedded architecture depends on powerful compiler support. Current studies are focused on developing compilers to reduce the designer's effort by introducing many automation related features. In this thesis work, a compiler framework is presented for a scalable Coarse-Grained Reconfigurable Array (CGRA) called SCREMA.

The compiler framework presented in this thesis replaces the exiting GUI compiler with an added feature of automatic placement and routing. The compiler receives a Reverse Polish Notation (RPN) description of the target algorithm by the user. It extracts the computational information from the RPN description and performs placement and routing over the CGRA template. The first configuration stream generated by the compiler is the main processing context. Furthermore, if additional configuration patterns have to be designed, the compiler framework gives the possibility to implement them in two different design paradigms: a preprocessing context and a canonical context. Preprocessing context is used to align the data into a CGRA to facilitate post-processing. Canonical context allows the user to perform additions in sum-of-products related algorithms.

The compiler framework has been tested by implementing real integer Matrix-Vector Multiplication (MVM) algorithms. Specifically, the tested MVM orders are 4<sup>th</sup>, 8<sup>th</sup>, 16<sup>th</sup> and 32<sup>nd</sup> on the CGRA sizes of 4x4, 4x8, 4x16 and 4x32 PEs, respectively. All the implementation are based on the RPN description of 4<sup>th</sup>-order MVM. Other than implementing 4<sup>th</sup>-order MVM, the rest of tested MVM algorithms need preprocessing and canonical contexts to be designed and implemented. The user effort which was needed to Place and Route (P&R) an algorithm manually on SCREMA is now reduced by using this compiler framework as it provides an automatic P&R mechanism.

### PREFACE

The work presented in this thesis is conducted at the Department of Electronics and Communications Engineering, Tampere University of Technology, Finland.

I am deeply grateful to Dr. Waqar Hussain for proposing this interesting subject and for his consistent support, guidance and motivation during the implementation of this work. Sincere acknowledgement goes also to Prof. Jari Nurmi for accepting me and supervising this thesis. I thank M. Sc. Sajjad Nouri for helping me from the beginning to the end of this project.

I would like to express my deepest gratitude to my parents, Maria Josefa and Asterio for their constant support, patience and love. Without their strength and effort, I had not come until here. Special thanks to my sister and friend, Rebeca, for listening to me and providing me her advices. I thank to the rest of my family for believing in my possibilities and encouraging me in my whole life.

I would like to thank my best friends, Saez, Laura, Dakas, Castro, Andy y Pedro for their time, friendship, advices and support. I am also grateful to my Rolix girls, Conchi and Maria for all the relaxed days that have helped me to continue fighting to be here.

I am also thankful to my high school friends, Leti, Mire and Sara, for still remembering all the good days we had at Lázaro Cardenas.

I cannot forget to Noemí, Alex, Inés, Fer, Lamas, Lallana, Merino, Ana, Olalla, Sandra, Dani Martinez, Serrano, Lucas, Sergio, Cristobal, Pablo, Velasco, Carazov, Nacho, Ramirez, Lalo, Antonio, Maria, Marta, Ainara, Carlos Lopez, Carlos Martinez and Luis for their company during the last six years at Universidad Politécnica de Madrid, Spain.

Finally, I thank to my new family and friends, Tano, Diane, Victor, David, Pedro, Sergi, Charlotte, Sebastian, Alejandro, Alba, Romain, Ursules, Pedro Juan, Edu, Carmen, Laura, Enrico Manuzzato, Enrico Mosconi, Maxime and Pedro portugués.

Tampere, June 2015 Leticia Trinidad Valderas Rodríguez

iii

# TABLE OF CONTENTS

| INTR | RODUCTION                                                                                                                                          | 1                 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| LITE | RATURE REVIEW                                                                                                                                      | 3                 |

| 2.1  | CoDe-X Compiler                                                                                                                                    | 3                 |

| 2.2  | DIL compiler                                                                                                                                       | 3                 |

| 2.3  | DRESC Compiler                                                                                                                                     | 4                 |

| 2.4  | RaPiD-C Compiler                                                                                                                                   | 5                 |

| 2.5  | XPP-VC Compiler                                                                                                                                    | 5                 |

| THE  | COFFEE RISC PROCESSOR                                                                                                                              | 7                 |

| THE  | SCALABLE CGRA TEMPLATE                                                                                                                             | 11                |

| 4.1  | The existing GUI-based Compiler                                                                                                                    | 12                |

|      | 4.1.1 CGRA Parameter File                                                                                                                          | 13                |

|      | 4.1.2 Configuration Header Files                                                                                                                   | 18                |

| DESI | GN AND IMPLEMENTATION OF AUTOMATIC COMPILER                                                                                                        | 20                |

| 5.1  | Reverse Polish Notation                                                                                                                            | 20                |

| 5.2  | Matrix-Vector Multiplication                                                                                                                       | 20                |

| 5.3  | Top-level module                                                                                                                                   | 21                |

| 5.4  | Information Processing                                                                                                                             | 24                |

| 5.5  | Context Implementation                                                                                                                             | 29                |

| 5.6  | Mask Delivery                                                                                                                                      |                   |

| TEST | FING AND EVALUATION                                                                                                                                | 43                |

| 6.1  | 4 <sup>th</sup> -Order MVM                                                                                                                         | 43                |

| 6.2  | 8 <sup>th</sup> -Order MVM                                                                                                                         | 46                |

| 6.3  | 16 <sup>th</sup> -Order MVM                                                                                                                        | 51                |

| 6.4  | 32 <sup>nd</sup> -Order MVM                                                                                                                        | 51                |

| CON  | CLUSIONS                                                                                                                                           | 53                |

| 7.1  | Future work                                                                                                                                        | 54                |

|      | LITE<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>THE<br>4.1<br>DESI<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>TEST<br>6.1<br>6.2<br>6.3<br>6.4<br>CON | LITERATURE REVIEW |

# LIST OF FIGURES

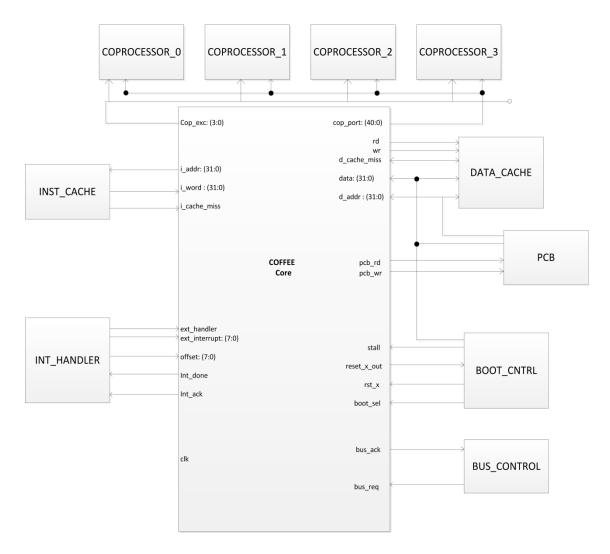

| Figure 3.1 Interfacing the COFFEE RISC core [12]                                 | 8  |

|----------------------------------------------------------------------------------|----|

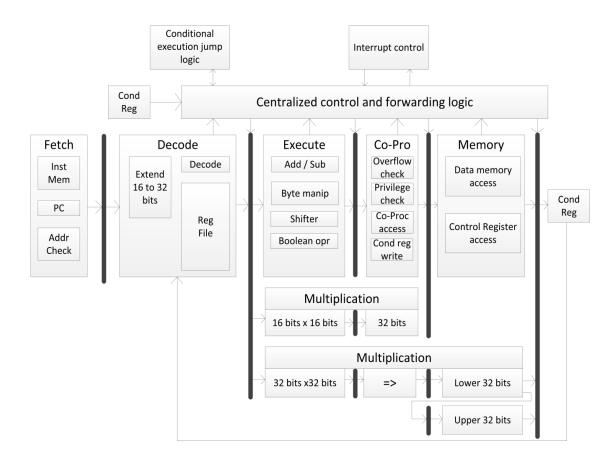

| Figure 3.2 COFFEE RISC Core pipeline [12]                                        | 9  |

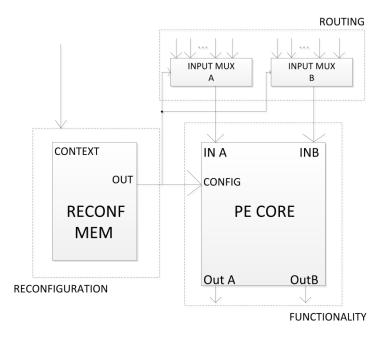

| Figure 4.1 Design blocks defined at compile-time using a set of parameters [6]   | 12 |

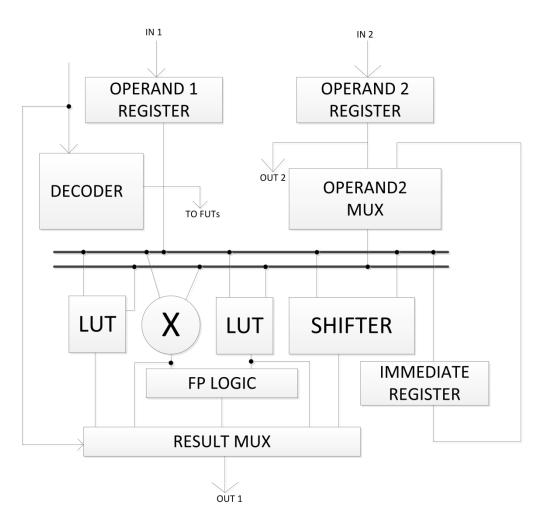

| Figure 4.2 PE Core Template [6]                                                  | 13 |

| Figure 4.3 Graphical User Interface to design new context                        | 14 |

| Figure 4.4 Binary fields in the configuration words                              | 19 |

| Figure 5.1 Compiler Dataflow                                                     | 21 |

| Figure 5.2 Elements of SCREMA template                                           | 22 |

| Figure 5.3 Example of the information process for MVM algorithm                  | 24 |

| Figure 5.4 Enumeration of the memory banks and the PE of the first row           | 26 |

| Figure 5.5 First step of information function                                    | 27 |

| Figure 5.6 Different arrays which save information related to the operations and |    |

| operands                                                                         | 27 |

| Figure 5.7 Third step of schedule function where the operands are placed in the  |    |

| local input memory                                                               | 27 |

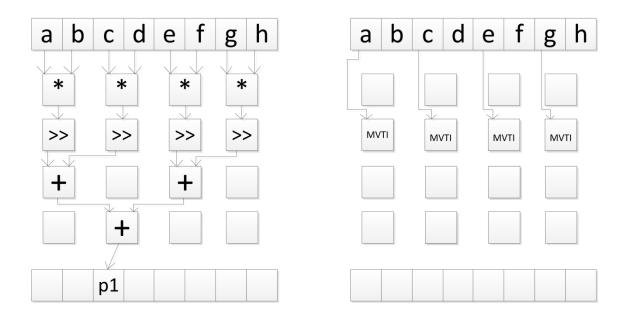

| Figure 5.8 First step in the processing function for MVM algorithm               | 29 |

| Figure 5.9 Second step in the processing function for MVM algorithm              | 29 |

| Figure 5.10 Implementation of second addition when MVM is processed              | 29 |

| Figure 5.11Explanation of the calculation of the best PE                         | 31 |

| Figure 5.12 The identifier number for each PE                                    | 33 |

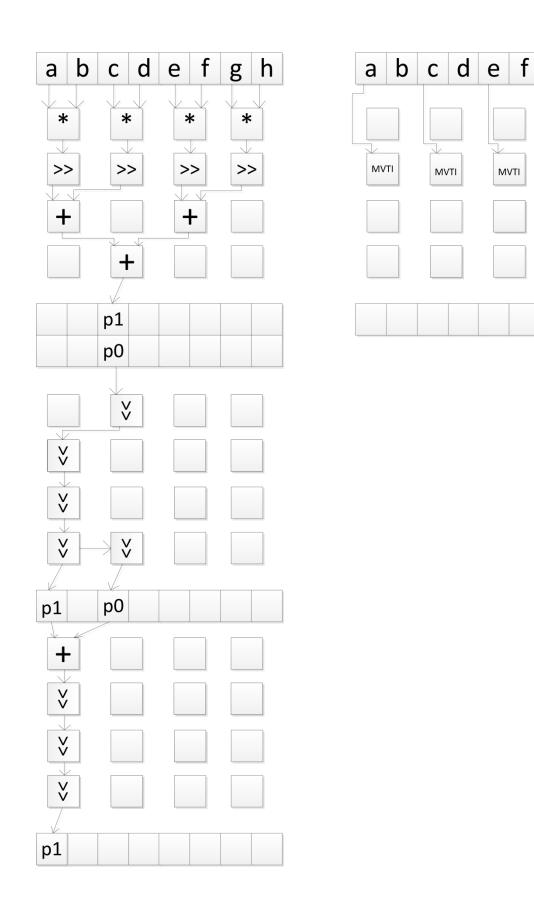

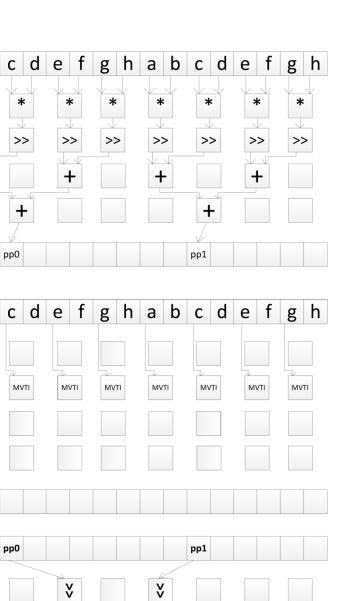

| Figure 5.13 Implementation of the mainContext function using MVM for a 4x8       |    |

| PE CGRA                                                                          | 36 |

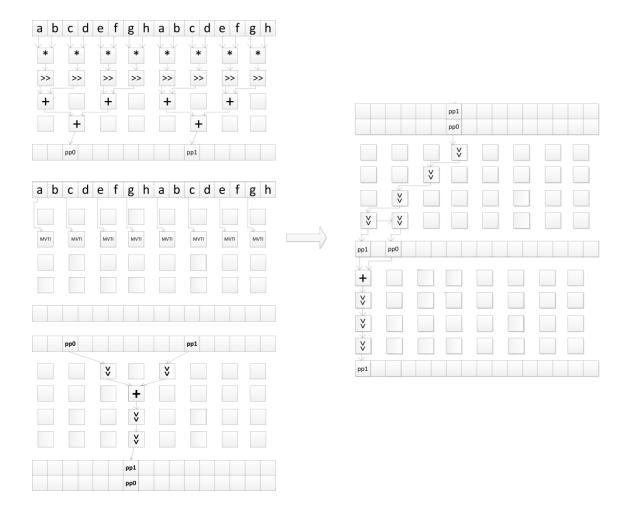

| Figure 5.14 Implementation of canonical context in a 4x8 PE CGRA using a 4x4     |    |

| PE CGRA template                                                                 | 37 |

| Figure 5.15 Example of pre-processing context                                    | 38 |

| Figure 5.16 Example of a matrix generated with parameters function and the       |    |

| different kinds of data                                                          | 39 |

| Figure 5.17 Example of a matrix generated with mask function and the different   |    |

| kinds of data                                                                    |    |

| Figure 6.1 The two context of 4 <sup>th</sup> –Order MVM in 4x4 PE CGRA          | 44 |

| Figure 6.2 Terminal results of 4 <sup>th</sup> Order MVM in 4x4 CGRA             |    |

| Figure 6.3 Terminal results of 4 <sup>th</sup> Order MVM in 4x8 CGRA             |    |

| Figure 6.4 The contexts of 8 <sup>th</sup> –Order MVM in 4x4 PE CGRA             | 47 |

| Figure 6.5 Terminal results of 8 <sup>th</sup> – Order MVM in 4x4 PE CGRA        |    |

| Figure 6.6 The context of 8 <sup>th</sup> -order MVM in 4x8 PE CGRA              |    |

| Figure 6.7 The context of 16 <sup>th</sup> -order MVM in 4x8 PE CGRA             | 50 |

## LIST OF TABLES

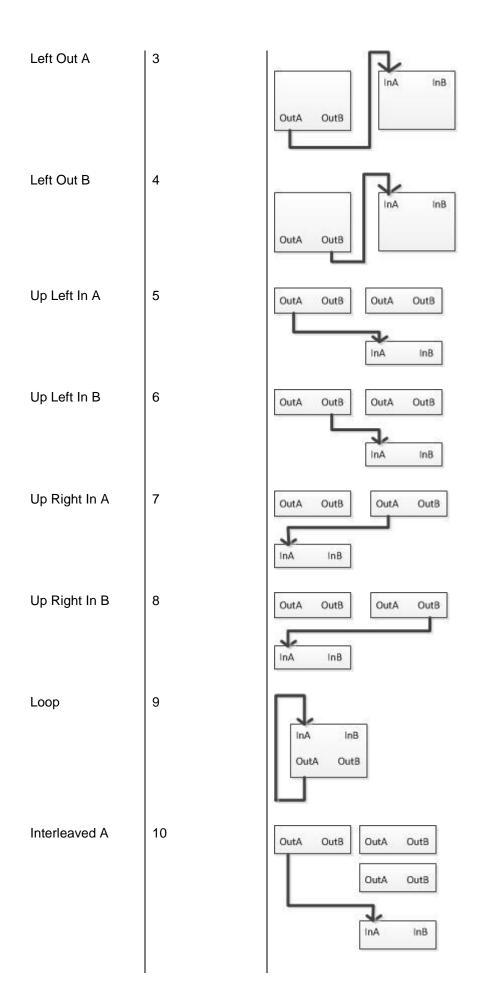

| Table 4.1 Interconnections between PEs in CREMA [6]                           | 15 |

|-------------------------------------------------------------------------------|----|

| Table 4.2 Possible functionalities of each PE with their related identifier   | 17 |

| Table 5.1 Different connection cases considering one operand is in the memory |    |

| and the PE is in the first row                                                | 34 |

| Table 5.2 Different connections considering that one operand is not in the    |    |

| memory and the PE is in the third row                                         | 34 |

| Table 5.3 Different data saved into contextPE array                           | 41 |

|                                                                               |    |

## LIST OF SYMBOLS AND ABBREVIATIONS

| ADRES    | Architecture for Dynamically Reconfigurable Embedded System          |

|----------|----------------------------------------------------------------------|

| ALE-X    | Arithmetic and Logic Expressions for Xputers                         |

| ASIC     | Application-Specific Integrated Circuit                              |

| BP       | Bank Position                                                        |

| CCB      | Core Configuration Block                                             |

| CGRA     | Coarse-Grained reconfigurable architectures                          |

| CISC     | Complex Instruction Set Computer                                     |

| DIL      | Data-flow Intermediate Language                                      |

| DPSS     | Data-Path Synthesis                                                  |

| DRESC    | Dynamically Reconfigurable Embedded System Compiler                  |

| DSP      | Digital Signal Processing                                            |

| FireTool | FIeld programming and REconfiguration management Tool                |

| FPGA     | Field Programmable Gate Array                                        |

| FU       | Functional Unit                                                      |

| GP-REG   | General Purpose REGisters                                            |

| MOVTI    | MOVe To Immediate                                                    |

| MVM      | Matrix-Vector Multiplication                                         |

| NML      | Native Mapping Languag                                               |

| NPL      | Native Mapping Language                                              |

| NRE      | Non-Recurring Engineering                                            |

| NRE      | Non-Recurring Engineering                                            |

| PCB      | Peripheral Control Block1                                            |

| PE       | Processing Element                                                   |

| PEP      | PE Position                                                          |

| rDPA     | Data-Path Array                                                      |

| RF       | Register Files                                                       |

| RISC     | Reduced Instruction Set Computer                                     |

| RPN      | Reverse Polish Notation                                              |

| SCREMA   | Scalable Coarse-Grain Reconfigurable Array with Mapping Adaptiveness |

| VLIW     | Very Long Instruction Word                                           |

| XPP      | eXtreme Processing Platform                                          |

|          |                                                                      |

## 1. INTRODUCTION

Currently, the use of embedded systems and applications has been continuously increasing at the exponential pace. Applications such as streaming audio/video, image processing and interactive services demand high performance and use of sophisticated algorithms. This demand is shadowed by the tradeoff between constraints and performance. Constraints include design costs, time-to-market, non-recurring engineering (NRE) costs, etc., whereas efficiency can be related to performance, power dissipation and some other high level metrics, e.g., W/Hz. [1]. The two most used approaches for implementation are software running on a general purpose processor and hardware in the form of Application-Specific Integrated Circuit (ASIC) [2]. General Purpose Processors (GPPs) are characterized to be flexible enough to perform various applications. However, it does not provide fast execution time and high performance. ASICs are designed for a specific application, consuming less power and providing a high performance as they are custom-tailored. Reconfigurable architectures take the advantages of the two mentioned approaches and provide high performance for various applications along with flexibility. They can be classified in three groups according to their level of granularity: Fine-grained, Middle-grained and Coarse-grained. Fine-Grained reconfigurable architectures consist of functional units interconnected by a programmable network. These functional units implement low-level bit-oriented logic functions [3]. Field Programmable Gate Array (FPGA) belongs to such reconfigurable systems. Middle-Grained consists of configurable cells with a granularity level of equal to or less than 8bits. They are mostly found integrated with microprocessor cores [3]. Coarse-Grained Reconfigurable Arrays (CGRAs) are composed of an array of functional units and storage resources. The functional units are designed to execute word-level or subword-level operations like additions and subtractions [1]. These reconfigurable architectures provide a drastic reduction of configuration memory and configuration time, as well as a diminution of the placement and routing problem. For that reason, various platforms using template-based CGRA have been designed; very popular since the last decade [1]. It should be noticed that the architectural specifications, computational model and designed tools diverge from one CGRA to another.

One of the first CGRA was Xputer architecture [3]. It consists of a reconfigurable Data-Path Array (rDPA) organized as a uniform two-dimensional array of ALUs. Another CGRA is RaPiD composed of a three integer ALUs, multipliers, six general-purpose datapath registers and three RAM blocks [4], whereas PiPeRench [3] is composed of reconfigurable pipelines stages called hardware stripes. Each of these hardware stripes has an array of Processing Elements (PEs) with registers and ALUs. Architecture for Dynamically Reconfigurable Embedded System (ADRES) is another CGRA. It consists of two major components, a Very Long Instruction Word (VLIW) processor and a reconfigurable array [1]. Another CGRA is BUTTER [5], which is 4x8 matrix of PEs with a 32-bit datapath. It works with general purpose Reduced Instruction Set Computer (RISC) processor. Since CGRAs contain high computational parallelism and throughput, they occupy an area of few million gates. In this context, a Scalable Coarse-Grained Reconfigurable Array with Mapping Adaptiveness (SCREMA) template was developed to generate applications-specific accelerators for optimal resource utilization was providing scalability [6]. Using SCREMA, the user can instantiate only those resources that are required by a specific set of applications.

One of the most important challenges of designing a reconfigurable architecture is related to its programing and compilation. Programming CGRAs are highly dependent on the structure and the granularity. In an ideal CGRA compiler, the user does not program in complex low-level programming. Compilation environments for reconfigurable systems span from manual placement and routing (P&R) tools to automatic design flow from high-level programming languages, such as C.

The target of this research work is to design and implement a compiler framework for SCREMA, to replace the existing manual P&R Graphical User Interface (GUI) tool. Such tool would be time consuming for the user if the size of the CGRA is extra large and there is large amount of computational information. The implemented compiler will automatically place and route the operations over the matrix of PEs and generate output configuration packages needed to create the SCREMA template. The input source is a Reverse Polish Notation (RPN) file with the description of the target algorithm. From this file, the main processing context will be created by the compiler. The compiler framework implements two important dataflow graphs to perform a broad range of sum-of-products related algorithms. The compiler framework has been tested and evaluated specifically for integer Matrix-Vector Multiplication (MVM) algorithms.

This thesis work is organized as follows. Chapter 2 discusses some of the related CGRA compiler frameworks. The architecture of platform which is composed of a RISC core and a CGRA is explained in Chapters 3 and 4, respectively. The design and implementation of the compiler is explained in Chapter 5 and the results from the Matrix Vector Multiplication are discussed in Chapter 6. In Chapter 7, conclusions and future work are presented.

# 2. LITERATURE REVIEW

Compiler environments of CGARs differ by the approach used for technology mapping, placement and routing. The characteristics of each compiler depend on the constraints and specifications of the reconfigurable architecture. The primary works regarding compiler design can be found for FPGA. In this case, compilers analyze a hardware descriptive text, i.e, VHDL or Verilog, and synthesize it for the FPGA device. In case of CGRAs, the compilers use only high-level programming languages, e.g., C. The following examples are the most important and relevant academic work for CGRA compilers.

#### 2.1 CoDe-X Compiler

CoDe-X compiler is used to map a C-like code, called X-C, into Xputer hardware [7]. Xputer is one of the first CGRA. It consists of two-dimensional array of arithmetic and logic reconfigurable units. There are three kinds of interconnections between them [3]: nearest neighbors, row/column back-buses and one global bus. The architecture is characterized for providing high area effectiveness. The input source for the compiler is X-C. The input program is divided by using the compiler which applies a number of loop parallelization transformations. In the next step, the compiler creates a description for each division using Arithmetic and Logic Expressions for Xputers (ALE-X) which will be synthesized using a Data-Path SyntheSis (DPSS). ALE-X can be generated automatically from the input code or it can be made manually. DPSS generates an assembler file for the configuration of the target architecture. Moreover, DPSS has a data scheduler which is responsible for organizing the operation to be mapped in the architecture. Finally, after scheduling and with the help of a mapper, placement and routing is performed. Furthermore, the array configurations and corresponding controllers are also generated.

#### 2.2 DIL compiler

DIL compiler has been designed to map the input source to PipeRench architecture [8]. In this case, the compiler uses a Data-flow Intermediate Language (DIL) as an input source. The compiler is responsible for scheduling, placement and routing.

PipeRench is a template-based, pipelined reconfigurable architecture since it consists of virtual pipeline stages implemented as hardware stripes [9]. There can be several programmable PEs that can be found in each stripe. Each PE is composed of a number of ALUs, pass registers and several control logic units. Each ALU has three inputs; two

inputs for data and the other one is used as control input. Three types of connections can be found inside this reconfigurable architecture. One of them is between two stripes, the other one is between a stripe and some of their PEs, and the last connection is passregister interconnect, where each register can transfer information to the other registers [9].

DIL [3] is a hardware independent high-level language which is also similar to Silage [10] and behavioral Verilog. It can be used to describe the algorithms for reconfigurable architectures. DIL has the C-operators and allows the programmer to manipulate arbitrary the width of integer values to guarantee that no information loss happens due to the overflow or type-conversions.

The first step is reading the specification of the target architecture. Then, the function and module techniques are performed in the input source to facilitate further analysis. During the synthesis process, the compiler constructs a graph whose structure is hierarchical acyclic and the nodes represents operations, I/O ports and delay-registers. After generating the graph, the compiler performs placement and routing over the graph, to generate the virtual hardware stripes [3]. In those processes, the compiler uses a deterministic linear-time greedy algorithm based on list scheduling [3]. This compiler has excellent compilation speeds and produces optimal hardware utilization.

### 2.3 DRESC Compiler

Dynamically Reconfigurable Embedded System Compiler (DRESC) [1] is a compiler designed for ADRES. This compiler maps the intensive loops parts of the C program to the reconfigurable architecture while the rest of the code is executed by VLIW processor. An intermediate representation is used to implement the scheduling process, and then, a novel modulo scheduling algorithm is employed to perform a combination of scheduling, placement and routing.

ADRES is composed of a VLIW processor and a reconfigurable array. The reconfigurable array consists of two dimensional array of functional units (FUs) which are responsible for executing a set of operation. The storage elements are Register Files (RFs) and memories blocks. Each FU can perform fixed-point operations. ADRES template is defined using an XML-based architecture specification language which is generated by DRESC compiler [3].

DRESC compiler accepts a C language program as input source. The first step is identifying the loops which will be mapped into the two dimensional array of FUs. Then, an intermediate representation is generated using a VLIW compiler framework called IM-PACT. The representation is called *Lcode* and it is used to execute the scheduling process. A novel modulo scheduling algorithm is developed by the program and the architecture representation as input sources. It is a software pipelining technique which attempts to schedule an iteration of a loop and determine which of the FUs will perform each operation. Finally, the placed and scheduled operations are implemented [1]. The objective of this compiler is to provide high-performance using all the family of ADRES architectures

### 2.4 RaPiD-C Compiler

RaPiD [4] architecture is a reconfigurable pipelined datapath architecture that uses RaPiD-C compiler to map a high-level hardware description. This compiler needs RaPiD-C, as a C software language to implement an application over the reconfigurable system. It also requires the user collaboration to specific parallelism, data movement and data partitioning across the multiple elements of the RaPiD architecture [3]. The compiler process is composed of four steps [4]: netlist generation, dynamic control extraction, instruction stream/decoder generation and I/O address generation.

RaPiD [4] is a coarse-grained field-programmable architecture that enables pipelined computational structures to be built from an array of arithmetic units, registers and memories. It consists of functional units such as ALUs, multipliers, General Purpose REGisters (GP-REGs) and RAMs. The large numbers of functional units are spread across a field-programmable segmented bus structure.

The application description is given in RaPiD-C language, which consists of multiple loops, one for each stage of the application. The programmer has to design the code paying attention to the architecture characteristics, for instance, to the number of functional units and the available memory. From the RaPiD-C language, specific operations are assigned to a specific stage at a specific time. One operation is performed by each pipeline stage in each cycle [4].

During the netlist generation process, the compiler instantiates registers for variables, ALUs for adds (and also other operations), multipliers for multiplication and multiplexers for *if-then-else* statements [4]. Once the netlist is generated, the compiler executes dynamic control extraction process. All the multiplexers are gathered in a lager multiplexer, depending on the size of the reconfigurable architecture. The compiler also realizes the same operation for the functional units. The compiler then extracts the address and instructions generated to control transfers values between stages [3]. The compiler is specifically designed for RaPiD, however it can be used in different technologies such as FPGAs or ASICs.

### 2.5 XPP-VC Compiler

The eXtreme Processing Platform (XPP) [10] uses XPP-VC compiler to map a C code into the reconfigurable architecture. The compiler flow consists of a preprocessing and a

dependence analysis of the input code followed by a temporal partitioning of each task, Native Mapping Language (NPL) generation and the final placement and routing.

The XPP technology is provided with development tool suite consisting of a placer, a router, a simulator and a visualizer [10]. The architecture is characterized by twodimensional array of PEs, internal memories and interconnection resources. The PEs executes arithmetic and logic operations, comparisons and special operations as counters. It should be noted that the output of each PE can be considered as the input source of another PE.

The input source of the compiler is a C code without structures, floating-point data, pointers, irregular control flow, recursive and system calls [10]. The user can provide a file where the parameters of the architecture and the external memories are defined. A preprocessing step is required by the compiler to transform the code into a program which facilitates the next steps. In the temporal partitioning, the code is divided into tasks that will be transformed to a Native Mapping Language (NML) reconfiguration code. After that, the NML module is placed and routed over the architecture. Finally, the configuration data and the binary codes are generated.

# 3. THE COFFEE RISC PROCESSOR

The compiler framework presented in this thesis work generates CGRA accelerators using SCREMA template in order to work with COFFEE RISC processor in a processor/co-processor model. COFFEE and SCREMA generated accelerators interact with each other using a network of switched interconnections that provide dedicated connections for fast communication [11].

COFFEE RISC Core [12] is a general-purpose processor which was designed for setting up embedded systems with a motivation to accelerate the tasks related to telecommunication and multimedia applications. There are different types of processor cores which can be classified depending on the instruction types: Reduced Instruction Set Computer (RISC), Complex Instruction Set Computer (CISC) and Digital Signal Processing (DSP). RISC and CISC are used to implement general purpose operations. However, DSP is a core to execute digital signal processing kernels where large numbers of mathematical operations have to be performed quickly. The difference between RISC and CISC is basically the type of instructions. CISC executes complex instructions such as an arithmetic operation load from memory. Nevertheless, RISC only accesses to the memory if load or store operations are called. The target of RISC is to perform the instructions using fewer cycles per instruction. COFFEE RISC Core was designed by following the RISC philosophy to executing one instruction per cycle. It uses delay branching with efficient hardware which consists of finding instructions to be placed in delay slots [12]. The length of a RISC instruction is fixed. RISC instructions contain all needed information without requiring any access to the memory. Only load and store instructions access the memory.

The COFFEE RISC Core instruction set architecture incorporates the most common instructions of a typical RISC core. It has flexibility in its instruction-set which allows coprocessor support. A hardware support is also placed to give the opportunity to execute DSP instructions. There are 14 arithmetic instructions, 10-bit field manipulation instructions, six boolean operation, eight conditional branches, four other jumps and six shift instructions [12]. In addition, COFFEE RISC is characterized by implementing real-time operating systems which can be achieved by dividing its mode into user register set and supervisor register set.

Figure 3.1 Interfacing the COFFEE RISC core [12]

The COFFEE RISC Core can be called load-store machine since memory operands are saved into registers before any operation [12]. The same occurs with the result of each operation where the value is saved into a register. To avoid excessive memory traffic, a large general-purpose register bank is used. This register is divided in two parts, one part for the user mode and the other for the supervisor mode. Moreover, COFFEE RISC offers the opportunity to configure it. For that reason, an internal memory mapped configuration register bank called Core Configuration Block (CCB) is provided. A Peripheral Control Block (PCB) was designed to configure and communicate with the peripheral devices.

The COFFEE RISC core is 32-bit Harvard architecture, where data and instruction memory can be distinguished from their interfaces. As it can be seen from the interface of COFFEE RISC Core in Figure 3.1, the memories are interconnected and they allow accessing them with different memory addressing schemes. The access time to the

Figure 3.2 COFFEE RISC Core pipeline [12]

memory may be reconfigurable using CCB. The PCB module is included to the COF-FEE RISC Core's data bus interface.

The COFFEE RISC Core can support four coprocessor interfaces that are attached as memory interface along with the maximum register bank size of 32 bits [12]. Such coprocessors can interrupt the core by an exception signal. COFFEE RISC core also provides an internal interrupt and eight different kinds of external interrupts. Those external interruptions can be from twelve sources if the coprocessor interfaces are not used.

As it can be seen in Figure 3.2, the COFFEE RISC Core has six stage pipelines with a maximum throughput of one instruction per cycle. The first pipeline stage is called fetch, where one instruction is fetched from the instruction memory depending on the pointer of the program counter. The address is checked by the *Addr Chek* block. During the decode stage, the instruction is identified and processed for the following stages. In the third pipeline staged, called execute, the arithmetic and logic operations are performed. Some operations like multiplication need to be executed in two pipeline stages. For that reason, co-processor stage is provided. After that, if load or store operations are required, they can be executed in the data memory stage. Finally, in the last stage, the final data will be written in the destination register of the register file.

The COFFEE RISC Core is a VHDL description which can be portable between technologies. For this reason, it has been synthesized for 90 nm low-power ASIC technologies, considering low supply voltage of 0.95V, high temperature of 125 degree centigrade and variations to guarantee high manufacturing processes. The highest frequency found was 150 MHz [12].

In addition, it was synthesized and P&R on ALTERA EP2S130F1020C4 and Xilinx XC4VLX160FF1148-11 devices, with different timing constraints. The results show the difference between the two technologies, in such a way that Altera targets higher density and higher operating frequencies, while Xilinx has less power dissipation [12].

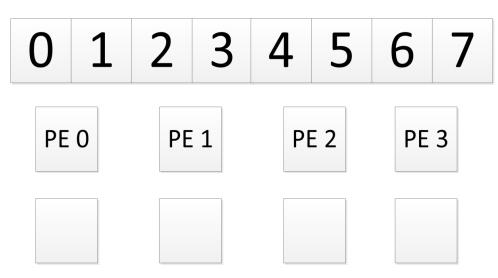

The software development tools are designed at Tampere University of Technology, Finland for COFFEE RISC Core. Several template-based CGRAs have been developed to work with COFFEE RISC Core, e.g., CREMA, AVATAR and SCREMA. CREMA is a 4x8 matrix of PEs. AVATAR consists of 4x16 matrix of PEs while SCREMA is a scalable CGRA to instantiate different sizes of CGRAs chosen by the user. SCREMA platform will be explained in details in the next chapter.

# 4. THE SCALABLE CGRA TEMPLATE

SCREMA is a Scalable Coarse-Grained REconfigurable Array with Mapping Adaptiveness [6]. SCREMA was designed to be scalable in both the number of PE rows and columns to meet the specific performance requirements of an algorithm. SCREMA is equipped with 32-bit local memories. The mapping adaptiveness consists of tailoring the array to specific application requirements [6]. A CGRA is composed of a matrix of interconnected PEs. The functionality and the routing among PEs can be modified by using the runtime reconfigurability feature of CGRAs. Every PE supports a fixed set of operations and different interconnections. Specifically, each PE can perform 32-bit integer or floating point operation in IEEE-754 format [11]. In general, interconnections can be classified into local, interleaved and global interconnection. A reconfiguration pattern, called context, specifies the operation to be implemented in each PE, as well as the interconnection. Each application consists of one or more reconfiguration patterns. For each context, several reconfiguration words are generated. They are stored into the reconfigurable memory of each PE that enables fast switching between contexts. Such mechanism permits the modification of the functionality and routing which can be performed in one Clock-Cycle (CC) [6].

The CGRA design is realized using a VHDL template which can be generated using FIeld programming and REconfiguration management Tool (FireTool). Using Firetool, the user can instantiate manually the functionality and the routing among PEs for each context. It generates two different files. The first one is a VHDL package based on the template size. The second one is a set of C header files that contain the operations and interconnections need to be selected for each context. The content of this thesis is to provide an automatic approach to generate both files, without using Firetool.

The elements that can be found inside the VHDL package are related to the routing of PEs, the PE functionality and the reconfiguration infrastructure. Figure 4.1 shows the last three components.

Each PE has two inputs and two outputs. The data of each input is taken from a multiplexer. Each multiplexer is connected to the possible data sources. The selection bits, defined in the VHDL file will indicate which connection has to be performed by the PE for each context. Moreover, in the VHDL package, the size of such multiplexer is defined which depends on the number of input sources. For example, if in one application, one PE is always connected to the same input source, then the multiplexer must not be used. However, if one PE needs four different connections, a 4-to-2 multiplexer has to be instantiated.

Figure 4.1 Design blocks defined at compile-time using a set of parameters [6]

The architecture of the PE is in most part compile-time configurable [6]. The different elements of the PE core can be seen in Figure 4.2. The configuration of each element can be found in the VHDL package. The components can be divided in two groups: functional blocks and reconfigurable control blocks. Functional blocks comprise integer functional units, such as adder, multiplier, shifter and a memory for LUT logic function implementation, immediate register and a floating point block. The VHDL file indicates which blocks have to be instantiated for each context. Reconfigurable control block consists of a decoder and the output multiplexer. The size of these two elements depends on the number of operation to be performed by each PE.

The configuration words are inserted into the array of PEs using pipelined infrastructure [13]. Such process consists of injecting the reconfigurable patterns into the array to be propagated along the horizontal and vertical directions.

### 4.1 The existing GUI-based Compiler

FireTool is the manual graphical tool used to design the different reconfiguration patterns for the CGRA. This tool consists of several windows. In the first one, the user is asked to introduce information about the size of the CGRA, the project name and the directory where the information will be saved. In the second window, the user is allowed to design a new context or to modify an existing one. The buttons to generate the VHDL package and the C header files are also found in the second window.

Figure 4.2 PE Core Template [6]

Regarding the design of a context, a user must perform the placement and routing manually by using the graphical interface shown in Figure 4.3. It consists of an array of PEs where the users are allowed to select the functionality and the interconnection of each PE input. The user can also activate the use of the immediate register for shift operation.

After configuring one context, the VHDL package and the C header files can be generated. Once the new reconfiguration pattern is designed, both of the files (VHDL, C headers) will be updated. The characteristics of each file are explained in detail in the following subsections.

### 4.1.1 CGRA Parameter File

It is a VHDL file which is based on the CGRA template configuration. It defines the architecture of each configuration pattern, i.e., the routing among PEs, the PEs functionality and the reconfiguration infrastructure. The file consists of several parameters. The description of the most important parameters is presented below:

| rray Cell 0: Row 0            | Array Cell 1: Row 0            | Array Cell 2: Row 0            | Array Cell 3: Row 0            | Array Cell 4: Row 0            | Array Cell 5: Row 0            | Array Cell 6: Row 0            | Array Cell 7: Row 0            |

|-------------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|

| Input A                       | Input A                        | Input A                        | Input A                        | Input A                        | Input A                        | Input A                        | Input A                        |

| Disconnected 🗸                | Disconnected 👻                 | Disconnected 👻                 | Disconnected 🗸 🗸               | Disconnected 👻                 | Disconnected 👻                 | Disconnected 👻                 | Disconnected •                 |

| (nput B                       | Input B                        | Input B                        | Input B                        | Input B                        | Input B                        | Input B                        | Input B                        |

| Disconnected 🗸                | Disconnected 👻                 | Disconnected 🗸                 | Disconnected •                 |

| Operation 🕅 IMM               | Operation IMM                  | Operation 🗐 IMM                | Operation 🕅 IMM                | Operation 🕅 IMM                | Operation 🔲 IMM                | Operation 🕅 IMM                | Operation 🕅 IMM                |

| NOP 👻                         | NOP 👻                          | NOP 👻                          | NOP 👻                          | NOP 👻                          | NOP 👻                          | NOP 👻                          | NOP                            |

| Conf. from Up A               | Conf. from Up A                | Conf. from Up A                | Conf. from Up A                | Conf. from Up A                | Conf. from Up A                | Conf. from Up A                | Conf. from Up A                |

| ray Cell 0: Row 1             | Array Cell 1: Row 1            | Array Cell 2: Row 1            | Array Cell 3: Row 1            | Array Cell 4: Row 1            | Array Cell 5: Row 1            | Array Cell 6: Row 1            | Array Cell 7: Row 1            |

| input A                       | Input A                        | Input A                        | Input A                        | Input A                        | Input A                        | Input A                        | Input A                        |

| Disconnected 👻                | Disconnected +                 | Disconnected 🗸                 | Disconnected +                 | Disconnected +                 | Disconnected +                 | Disconnected 👻                 | Disconnected •                 |

| Input B                       | Input B                        | Input B                        | Input B                        | Input B                        | Input B                        | Input B                        | Input B                        |

| Disconnected 👻                | Disconnected 👻                 | Disconnected 👻                 | Disconnected -                 | Disconnected 👻                 | Disconnected 👻                 | Disconnected 👻                 | Disconnected                   |

| Operation 🕅 IMM               | Operation 🕅 IMM                | Operation 🕅 IMM                | Operation 🕅 IMM                | Operation 🕅 IMM                | Operation 🔲 IMM                | Operation 🕅 IMM                | Operation 🕅 IMM                |

| NOP 👻                         | NOP 👻                          | NOP 👻                          | NOP 👻                          | NOP 👻                          | NOP 👻                          | NOP 👻                          | NOP                            |

| Conf. from Up A               | Conf. from Up A                | Conf. from Up A                | Conf. from Up A                | Conf. from Up A                | Conf. from Up A                | Conf. from Up A                | Conf. from Up A                |

| rray Cell 0: Row 2<br>Input A | Array Cell 1: Row 2<br>Input A | Array Cell 2: Row 2<br>Input A | Array Cell 3: Row 2<br>Input A | Array Cell 4: Row 2<br>Input A | Array Cell 5: Row 2<br>Input A | Array Cell 6: Row 2<br>Input A | Array Cell 7: Row 2<br>Input A |

| Disconnected -                | Disconnected -                 | Disconnected -                 | Disconnected                   | Disconnected                   | Disconnected                   | Disconnected +                 | Disconnected                   |

| Input B                       | Input B                        | Input B                        | Input B                        | Input B                        | Input B                        | Input B                        | Input B                        |

| Disconnected -                | Disconnected -                 | Disconnected -                 | Disconnected -                 | Disconnected                   | Disconnected -                 | Disconnected -                 | Disconnected                   |

| Operation IMM                 | Operation IMM                  | Operation IMM                  | Operation IMM                  | Operation IMM                  | Operation IMM                  | Operation IMM                  | Operation IMM                  |

| NOP +                         | NOP +                          | NOP +                          | NOP •                          | NOP •                          | NOP +                          | NOP +                          | NOP                            |

| Conf. from Up A               | Conf. from Up A                | Conf. from Up A                | Conf. from Up A                | Conf. from Up A                | Conf. from Up A                | Conf. from Up A                | Conf. from Up A                |

| ray Cell 0: Row 3             | Array Cell 1: Row 3            | Array Cell 2: Row 3            | Array Cell 3: Row 3            | Array Cell 4: Row 3            | Array Cell 5: Row 3            | Array Cell 6: Row 3            | Array Cell 7: Row 3            |

| input A                       | Input A                        | Input A                        | Input A                        | Input A                        | Input A                        | Input A                        | Input A                        |

| Disconnected 👻                | Disconnected -                 | Disconnected +                 | Disconnected -                 | Disconnected 👻                 | Disconnected 👻                 | Disconnected 👻                 | Disconnected                   |

| nput B                        | Input B                        |

| Disconnected 👻                | Disconnected +                 | Disconnected -                 | Disconnected -                 | Disconnected 👻                 | Disconnected +                 | Disconnected +                 | Disconnected                   |

| Operation 🕅 IMM               | Operation IMM                  | Operation 🔲 IMM                | Operation 🕅 IMM                | Operation 🕅 IMM                | Operation 🕅 IMM                | Operation 🕅 IMM                | Operation IMM                  |

| NOP 👻                         | NOP 👻                          | NOP 👻                          | NOP 👻                          | NOP 👻                          | NOP 👻                          | NOP 👻                          | NOP                            |

| Conf. from Up A               | Conf. from Up A                | Conf. from Up A                | Conf. from Up A                | Conf. from Up A                | Conf. from Up A                | Conf. from Up A                | Conf. from Up A                |

Figure 4.3 Graphical User Interface to design a context

- *crema\_cfg\_ic\_depth\_A* → This parameter represent a matrix of the same size as the size of the CGRA. Each position represents one PE. As it was mentioned in the Section 4, a PE has two inputs and in each of them, one multiplexer is implemented to select the input source. In this matrix, the select line information of the multiplexer of the input A is saved.

- *crema\_cfg\_ic\_depth\_B* → Its description is same as *crema\_cfg\_ic\_depth\_A* except that each position of this matrix saves the selection bit of the multiplexer of the input B.

- crema\_cfg\_width → The size of this matrix is the same as the size of the CGRA. This parameter is a matrix of integers that represents the selection bit of the output multiplexer. In this case, the size of the multiplexer depends on the number of operations that have to be performed by a PE.

- *crema\_sel\_width* → Each integer in the matrix is related to the output of the PE. The integers select the multiplexed output of the PEs. The specific value of the integer depends on the number of functions that a PE processes.

- $crema\_mux\_mask\_A \rightarrow$  This large constant matrix is composed of several smaller matrices. The value of these smaller matrices is equal to the number of PE rows in the CGRA that means if there are four PE rows in the CGRA there will be four groups of small matrices. Every small matrix has to be of the same size. A non-zero column of these small matrices represent an interconnection with another PE.

All stored information in these small matrices corresponds with the connection identifier (See Table 4.1) for the input A of the PE. As it can be seen in Table

4.1, each connection is represented by a number. This means that if the input source of one PE is in the output A of another PE, the connection would be Up In A and is represented by '1'.

- $crema_mux_mask_B \rightarrow$  This large matrix also consists of several smaller matrices, as in the previous case of  $crema_mux_mask_A$ . The unique difference is that the connection identifier for the input B can be stored in each position.

- *crema\_cell\_mask* → The dimension of this group of matrices is the same as in the last two cases. As it can be seen in Table 4.2 that an operation to be performed by a PE has an identifier. The operation identifier can be stored in each position of this group of matrices.

- *crema\_add* → The dimension of this matrix is equal to the size of the CGRA. The binary information saved in each position will indicate if the PE has to perform an addition operation.

- *crema\_sub* → The characteristics of this matrix are the same as in the last case. However, the only difference is binary information in the matrix which indicates if a subtraction has to be performed by each PE.

- *crema\_mul*  $\rightarrow$  Each position of this matrix indicates if the PE has performed a multiplication. The size of the matrix is the same as the size of the CGRA.

- *crema\_shifter*  $\rightarrow$  In case, if a shift operation has to be performed by a PE, a binary parameter 'true' will be stored in each position of the matrix.

- *crema\_ram* → In this case, each position of the matrix will be will represent a RAM related operation.

- *crema\_imm* → The characteristics of this matrix are the same as the others, but with a difference that it will indicate if the immediate register has been used by the PE.

- $crema\_confup \rightarrow$  This matrix indicates if the configuration of the above PE has been used for the reference PE. The dimension is the same as the CGRA.

- *crema\_word\_width\_int* → It indicates the word width of each PE which is equal to 32 bits.

| Interconnections | Interconnections identifier | Representation |

|------------------|-----------------------------|----------------|

| Disconnected     | 0                           |                |

| Up In A          | 1                           | OutA OutB      |

| Un In B          | 2                           | OutA OutB      |

Table 4.1 Interconnections between PEs in CREMA [6]

Table 4.2 Possible functionalities of each PE with their related identifier

| Functionality | Functionality<br>identifier |

|---------------|-----------------------------|

| NOP           | 0                           |

| ADD           | 1                           |

| SUB           | 2                           |

| MUL           | 3                           |

| ADDS          | 4                           |

| SUBS    | 5  |

|---------|----|

| MULS    | 6  |

| SHIFT   | 7  |

| LOAD    | 8  |

| STORE   | 9  |

| MOVTI   | 10 |

| DELAY   | 11 |

| UNREGFT | 12 |

### 4.1.2 Configuration Header Files

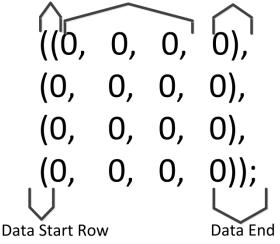

Header files contain different configuration words for each context. Each configuration file consists of several configuration arrays. The number of configuration arrays is the same as the total number of contexts needed to be implemented for an application.

The configuration words are represented by eight hexadecimal digits and each number keeps the information related to the routing and the functionality of each PE. The first two digits save the PE identifier. Starting from the last significant bit side, the first hexadecimal digit saves information about the interconnection of the input A. The information related to the interconnection of the input B is saved in the next digit. The next hexadecimal number is reserved to store the information about the functionality. If the PE uses the immediate register, one digit is needed to show in which context the immediate register has been used. Generating such configuration words is explained in the following example.

Figure 4.4 depicts the example, where the configuration words can be seen and are represented in binary numbers for each context. It can be seen that each group of bits represent several other routing and operation parameters, as it was mentioned earlier. The number of bits for the groups called inA, inB and Oper depends on amount of interconnections and different functions to be performed by each PE, respectively.

Suppose that first PE will receive the input sources from three different PEs, both for input A and input B. To represent three options, two bits are needed. Hence, the selection bits for each multiplexer will be equal to two. If a PE is supposed to receive data from only one input source then only one bit would be required. Two bits representing the routing field inA and inB are shown on the right side of Figure 4.4 as the selection bits of the multiplexer for each input. Each input source is listed depending on the order it was used. If one input source is used again in another context, it is codified with the same number. If we look at Figure 4.4, it is supposed that input A uses the input source numbered as zero both in the first and fourth context. The same occurs for input B in the third and fourth context, but in this case the input source is numbered as three.

| First Context  | ÷ | 0 0 0 0 0 0 0 0 1 0<br>PE Number | 1 1 0 0 0 0 0 0 0<br>Imm Oper InB InA |

|----------------|---|----------------------------------|---------------------------------------|

| Second Context | → | 0 0 0 0 0 0 0 0 1 0<br>PE Number | 1 0 0 1 0 1 0 1<br>Imm Oper InB InA   |

| Third Context  | → | 000000010<br>PE Number           | 1 0 1 0 1 0 1 0<br>Imm Oper InB InA   |

| Fourth Context | ÷ | 0 0 0 0 0 0 0 0 1 0<br>PE Number | 1 0 1 1 1 0 0 0<br>Imm Oper InB InA   |

Figure 4.4 Binary fields in the configuration words

Then, assume that PE performs four different operations. In this case, the number of selection bits for the decoder is equal to two since there are four different possibilities. Each operation will also be represented by two bits called Oper (See Figure 4.4). The bits for the decoder are also listed depending on the order they are used.

Finally, if a PE needs the use of the immediate register then the bit called imm is used. If the immediate register is not instantiated then the imm bit is not written in the configuration word. To know in which context the immediate register is needed, imm bit will be 1. As it can be seen in Figure 4.4, the immediate register was only needed in the first context.

# 5. DESIGN AND IMPLEMENTATION OF AUTO-MATIC COMPILER

The compiler framework replaces the existing GUI tool with an added feature of automatic placement and routing. The input source of the compiler is a Reverse Polish Notation (RPN) file. Such file is analyzed to extract the computational information and to generate the main processing context. The user has the possibility of implementing additional configuration patterns. Two different design paradigms are provided: preprocessing context and canonical context.

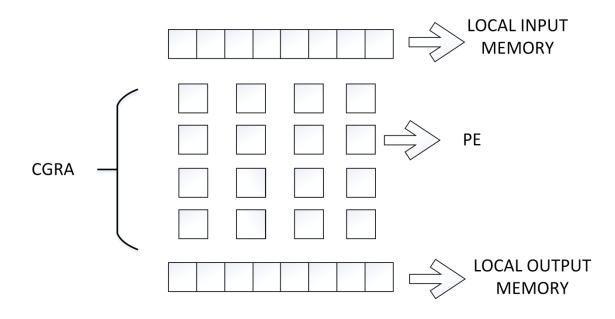

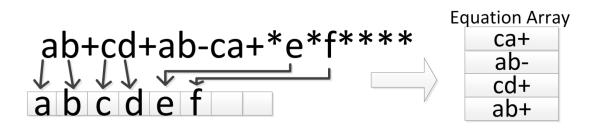

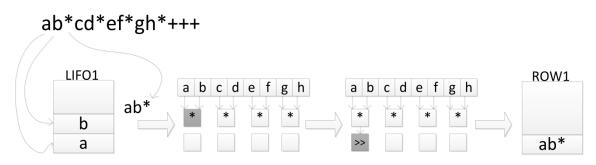

#### 5.1 Reverse Polish Notation

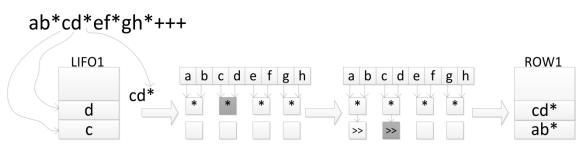

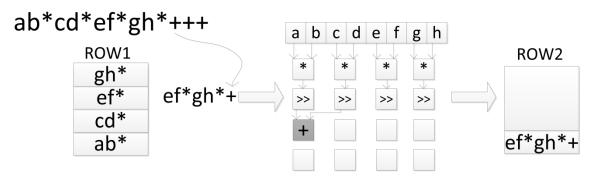

The input source for the compiler is a RPN sequence related to the equations to be mapped on the CGRA. RPN is a mathematical notation where each operator is placed after their operands. This means that instead of writing a+b in general, the RPN is written as ab+. Such notation was invented by Burks, Warren and Wright [14]. At the beginning of 1960 it was reinvented by Friedrich L. Bauer and Edsger Dijkstra [14]. They reinvented it to reduce the memory access time in the computers and to provide higher performance. RPN is frequently used in computer science, e.g., in Unix pipelines and in concatenative programming languages based on stacks. A Last-In-First-Out (LIFO) is needed to process the RPN information. The algorithm followed to process the RPN information consists of distinguishing between operands and operators. The operands are store into one LIFO. If one operator is identified, the program pulls the last two stored operands from the LIFO, produces the operation and pushes the result into the same LIFO. This algorithm is followed by the compiler as it will be explained later.

#### 5.2 Matrix-Vector Multiplication

The compiler has been tested by Matrix Vector Multiplication (MVM). An N<sup>th</sup> order matrix consists of N scalar products between each row of an NxN matrix and a vector. This process is just the multiplication between one element in the row of the matrix and another element of the vector which are in the same position. Once all multiplications have been made, the addition of all results is required. Eq. 5.1 represents an example of  $4^{th}$  order MVM. The result of each row of 4x4 matrix and the vector can be observed in Eq. 5.2.

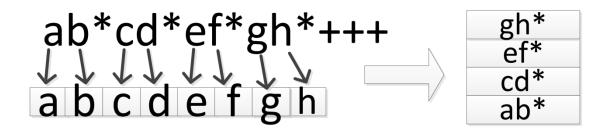

Figure 5.1 Compiler Dataflow

$$\begin{pmatrix} a_{11} & a_{12} & a_{13} & a_{14} \\ a_{21} & a_{22} & a_{23} & a_{24} \\ a_{31} & a_{32} & a_{33} & a_{34} \\ a_{41} & a_{42} & a_{43} & a_{44} \end{pmatrix} x \begin{pmatrix} b_1 \\ b_2 \\ b_3 \\ b_4 \end{pmatrix} = \begin{pmatrix} p_1 \\ p_2 \\ p_3 \\ p_3 \end{pmatrix}$$

$$p_1 = (a_{11} \times b_1) + (a_{12} \times b_2) + (a_{13} \times b_3) + (a_{14} \times b_4)$$

$$p_2 = (a_{21} \times b_1) + (a_{22} \times b_2) + (a_{23} \times b_3) + (a_{24} \times b_4)$$

$$p_3 = (a_{31} \times b_1) + (a_{32} \times b_2) + (a_{33} \times b_3) + (a_{34} \times b_4)$$

$$p_4 = (a_{41} \times b_1) + (a_{42} \times b_2) + (a_{43} \times b_3) + (a_{44} \times b_4)$$

$$(5.2)$$

In order to implement this algorithm on SCREMA template, the RPN sequence of only p1 is sufficient as p1, p2, p3 and p4 are all identical.

#### 5.3 Top-level module

Compiler design consists of three main steps: information processing, context implementation and mask delivery. The Figure 5.1 depicts the compiler dataflow. During the information processing, the RPN file is analyzed to place the operands inside the local input memory of the CGRA optimizing resources. Within the context implementation stage, the different contexts are designed. The main processing context is designed from the RPN file. The rest of contexts are implemented by two different design paradigms (pre-processing and canonical context). Finally, the VHDL package and C header files are generated in the mask delivery step.

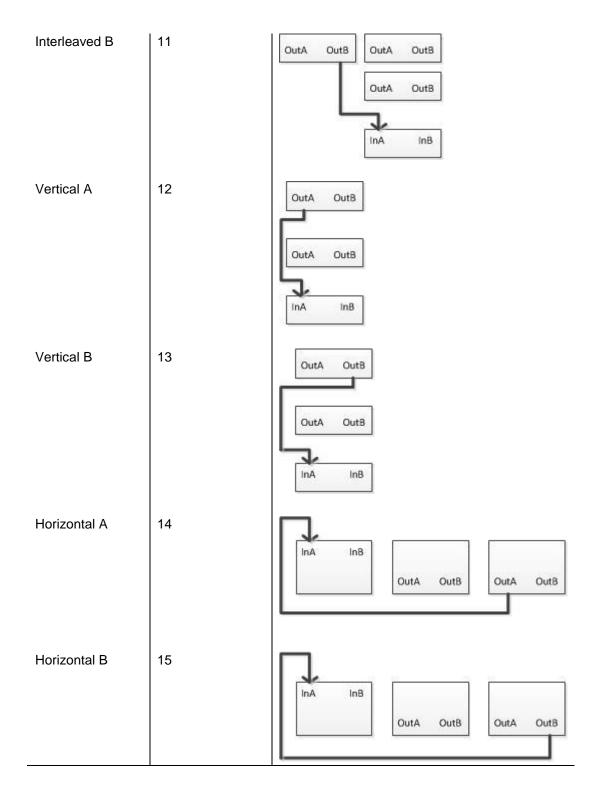

Figure 5.2 Elements of SCREMA template

To design the compiler, the SCREMA template has been virtualized. In Figure 5.2, it can be seen the virtualized elements of SCREMA template: the local input memory, the local output memory and the PEs.

The design of the compiler consists of several functions which will be explained below. The main function is responsible for saving the initial information provided by the user which is in the RPN file, i.e., the project name and the size of the desired CGRA. The main program also initializes the global variables, executes the rest of the functions and interacts with the user to design new contexts.

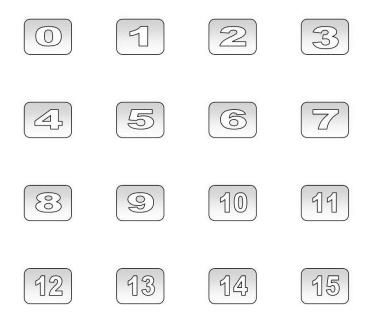

As it was mentioned before, the main function needs to declare all the global variables. Such variables define the virtualized parts of the CGRA (PEs and local memories), the VHDL matrices (See Section 4.1.1), LIFOs and their pointers. The VHDL matrices are represented as arrays. Two CGRA are created: a CGRA template and the CGRA to be instantiated. The CGRA template is generated from the RPN file. The template design might be replicated to obtain the CGRA to be instantiated. The template CGRA can instantiate at maximum sixteen columns of PEs and any number of PE rows based on the user input. In the design of compiler, a PE is defined as structure, as it can be seen in the description below. It consists of two strings, *inA* and *inB*. The connection identifier for each input is saved in these strings, respectively. The operation identifier is saved in the string called *operation*. The information about the equation executed by the PE is saved in the *info* string. *ConnnectedPE* indicates if that PE has been connected to other PEs or to the output memory. The PE information for each context is stored in the *con*-

*text* array. This array is needed to generate the C header file. Finally, *pointerContext* is defined to indicate in how many contexts the PE have been used.

| 1 | <pre>typedef struct PE {</pre> |                                                     |

|---|--------------------------------|-----------------------------------------------------|

| 2 | char inA[3];                   | <pre>//save the connection identifier for InA</pre> |

| 3 | char inB[3];                   | <pre>//save the connection identifier for InB</pre> |

| 4 | <pre>char operation[3];</pre>  | <pre>//save the operation identifier</pre>          |

| 5 | char info[100];                | <pre>//store information about the operation</pre>  |

| 6 | <pre>int connectedPE;</pre>    |                                                     |

| 7 | <pre>int context[8][9];</pre>  | <pre>//save the values of this PE</pre>             |

| 8 | <pre>int pointerContext;</pre> |                                                     |

| 9 | }PE;                           |                                                     |

|   |                                |                                                     |

**Program 5.1** PE structure declaration

Both of the input and output local memories of the CGRA are defined in the main function. The information that will be used by the PEs is saved into the input memory while the results of the operations to be performed by the CGRA are saved into the output memory. The size of both memories is two times the number of PE columns of the CGRA that is being targeted by the compiler.

As it was discussed in section 5.1, the RPN algorithm is based on the use of LIFOs. The compiler needs five of them to process the information. The compiler reads the RPN file character by character. When one operand is identified, it is saved into a LIFO called LIFO1. The compiler repeats the same process until it reads an operator. In that case, the compiler extracts the two last operands from LIFO1 and it searches for the ideal PE to place the operation to be performed. If the PE is in the first row of the CGRA, the result is saved into the LIFO called ROW0. The same occurs with the rest of the results of the other rows. They will be saved inside of their respective LIFOs. They are called ROW1, ROW2 and ROW3, respectively. Every LIFO has its own pointer to know the position for pushing or pulling the data, and also indicates how many values can be stored in them.

Finally, the number of context is initialized in the main function. This parameter is needed to know which context is being designed at each moment since that information is required once the C header file is generated by the compiler.

Inside the main function, several files can be seen. They are required to read the RPN file and to generate the VHDL package and the also C header file. In particular, *file1* is for saving the RPN file, *file2* for creating the VHDL file and *file3* for generating the C header file.

Some functions are executed by the main program: *initialization*, *information*, *processing*, *mainContext*, *draw*, *header*, *preprocessing* and *canonical*. The VHDL matrices are initialized by the *initialization* function. This function is needed to be able to modify those matrices in other functions. The required information for that function is the size

Figure 5.3 Example of the information processing for MVM algorithm.

of the CGRA and the VHDL file since the dimensions of the matrices depend on the size of the CGRA. Information function is used to extract the relevant information of RPN file and to place the operands inside the input memory. Information function needs the CGRA template dimensions, the RPN file and the number of operations to be performed by the CGRA. Processing function is responsible for reading the RPN file and performing the placement and routing in the CGRA template where the size of the CGRA template and the RPN file will be required. MainContext function replicates the CGRA designed in *processing* function depending on the size of the desired CGRA. As it can been understood, this function requires the dimension of both CGRA template and the CGRA to be instantiated. Draw is the function for generating the VHDL package. It reads the data from the VHDL matrices and creates the corresponding file. Header function is responsible for generating the C header file. This function will read the data from the *context* array of each PE and design the configuration stream. The input parameters of this function are the size of the final CGRA, the C header file and the project name. Two design paradigms are provided: pre-processing and canonical contexts. Preprocessing and canonical function will design these two contexts, respectively.

#### 5.4 Information Processing

In information processing module, the compiler places automatically the pair of operands in the input memory. It also performs the placement and routing for the first row of the CGRA template. Information processing module consists of *information* and *schedule* functions

*Information* function collects the important data from the RPN file to optimize the process of placing the operands in the local input memory of the CGRA. In this case, the compiler keeps an image of the local input and output memory to perform placement and routing. The compiler needs to know which operations will require the two operands from the local input memory of the CGRA. Within this step, the compiler will know if there is enough space in the local input memory to place the operands. Otherwise, the compiler will indicate a constraint.

First, the compiler places the operands in the local input memory of the CGRA. If two operations use the same operand, it is placed in the local input memory only once. The order to place the operands is the order in which they are written in the RPN sequence. The compiler then reads again the RPN file and searches for the operations which are required to take both operands from the input memory.

In Figure 5.3, the mentioned process can be seen. The RPN sequence is related to the MVM algorithm. The sequence consists of a few addition and multiplication operations. First, the compiler places all the operands in the input local memory of the CGRA. The operations that have both operands in the input memory are saved into the *equation* array which can be seen on the right side of Figure 5.3. As it can be noticed, this function would not be needed in the case of MVM since the compiler might just read character by character and place the operands in the input memory. However, this solutions was implemented to design a more efficient and general compiler.

This function needs the size of the CGRA, the number of total operations and the RPN file. The dimensions of the CGRA are required to know if the operands would be placed inside the local input memory and are also used for executing the next *schedule* function. The number of total operations is needed to create the mentioned *equation* array. Finally, the RPN file is required to read each character and to identify which of those are operands or operators.

*Schedule* is another function inside the information processing module. Basically, this function calculates which operand is the most used in the global equation. Such operand is placed inside the local input memory of the CGRA depending on how many times it is required in the global equation. The compiler then searches for the other operands (called neighbors) needed to perform the operation. The compiler places them together in the local input memory of the CGRA. *Route* function is executed to make a connection between each PE and each memory bank of the local input memory of the CGRA.

The parameters inside this function represent the dimension of the CGRA template, the number of operations which require both operands in the memory, the number of operands which are needed to implement the last operations and the mentioned *equation* array.

Inside *schedule* two different structures can be found. The first one, shown in Program 5.2 and is called *data*. It saves information about each operand, i.e., how many times it is required in the equation, the number of the other operands that are used with it (called neighbors) and the name of these operands. The operations and information that says if that operation has been analyzed are saved in the second structure (See Program 5.3).

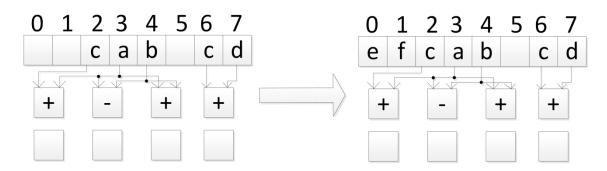

Figure 5.4 Enumeration of the memory banks and the PE of the first row

Once these structures are defined, the *schedule* function starts to fill them with *equation* array that is provided by *information* function.

| 1 | <pre>typedef struct data{</pre>       |                                     |

|---|---------------------------------------|-------------------------------------|

| 2 | char name;                            | //name of the operand               |

| 3 | int times;                            | <pre>//how many times is used</pre> |

| 4 | int neighbour;                        | //how many neighbors has            |

| 5 | char neighborName[numCharacter        | ]; //saved the name of the neigh-   |

|   | bors                                  |                                     |

| 6 | }data;                                |                                     |

|   | <b>Program 5.2</b> Definition of      | f data structure                    |

| 1 | <pre>typedef struct operations{</pre> |                                     |

| 2 | char e[1][4]; //save the equa         | ations                              |

| 3 | <pre>int used; //indicates if '</pre> | that operation has been used by PE  |

| 4 | <pre>}operations;</pre>               |                                     |

#### Program 5.3 Definition of operation structure

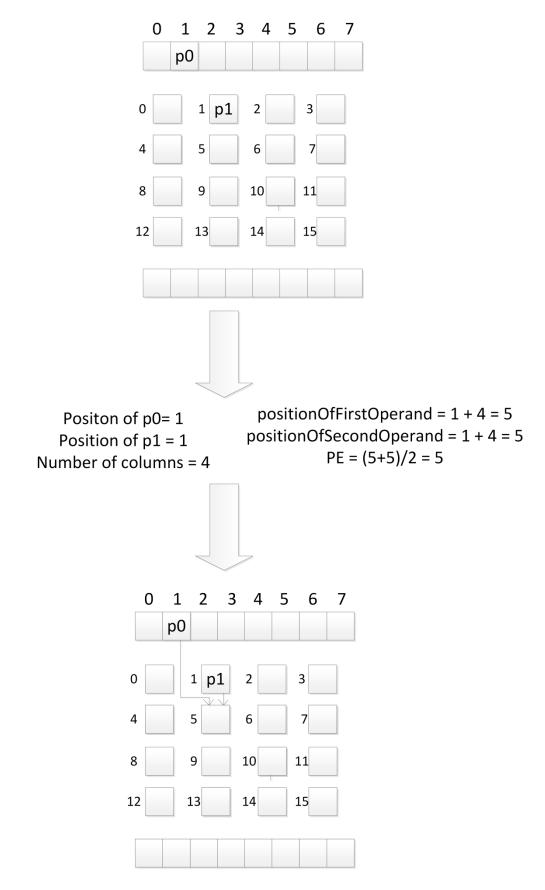

Before going in more detail about how this function works, it is needed to explain the considerations that have been taken in account during the design. Due to the constraints in the hardware structure provided by SCREMA, each PE of the first row can only take the information from Left Up In A, Left Up In B, Up In A, Up In B, Right Up In A, Right Up In B (See Table 4.1). Hence, this fact limits the space where to put the operands inside the local input memory of the CGRA.

If we look at the numeration provided in Figure 5.4, it can be seen that if one operand is placed in the memory bank number one, it can be used only for PE 0 and PE 1. However, if the same operand is placed in the position number three of the local input memory of the CGRA, it may be used for more number of PEs. The operand which is most used for operation is placed by the compiler, so that the maximum number of PEs can use it.

Figure 5.5 First step of information function

|     |       |        |          | Equation Al | ay  |

|-----|-------|--------|----------|-------------|-----|

| Opr | Times | N.Neib | Neighbor | Equations   | use |

| а   | 3     | 2      | bc       | ca+         | 0   |

| b   | 2     | 1      | а        | ab-         | 0   |

| С   | 2     | 2      | a d      | cd+         | 0   |

| d   | 1     | 1      | С        | ab+         | 0   |

Figure 5.6 Different arrays which save information related to the operations and operands

*Figure 5.7* Third step of schedule function where the operands are placed in the local input memory.

If the operand is required three or more times, it will be placed in the memory bank number three since in that position more PEs may use it, as it was mentioned and considering the case if the size of the CGRA is 4x4 PEs. If that operand is just needed twice or once, it will be placed in the memory bank number one.

Once the most frequently used operand is placed, the compiler looks for the other operands to place the operator in the PEs. First of all, the compiler searches operation that includes the most frequently used operand. Then it looks for a place inside the local input memory of the CGRA to place the second operand of same equation. The compiler then places the operation in the nearest PE. *Route* function is executed to place the

**Equation Array**

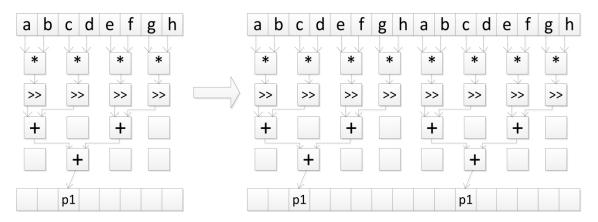

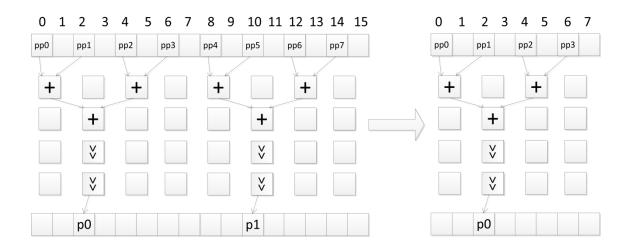

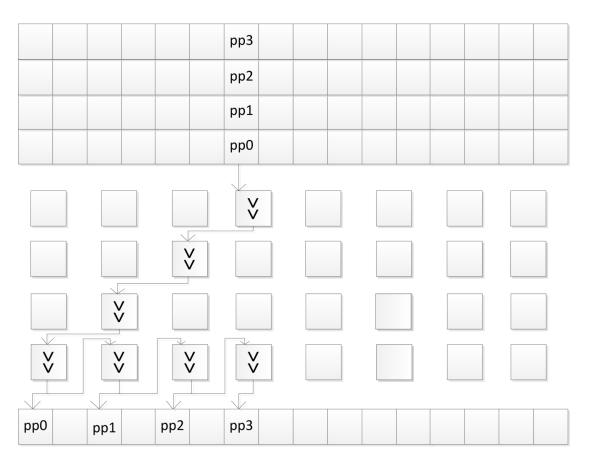

equation in the PE and to implement the interconnections. If all the PEs are occupied, the compiler stops and indicates accordingly. Once that operation is placed, the PE is marked as used. When all the operands have been put inside the local input memory of the CGRA, the *schedule* function searches if there are other operations without having been placed in the CGRA. The compiler places the operands of these operations following the same steps. At the end it checks if all the operands are placed in the input local data memory of the CGRA.