## FAIZAN UL HAQ LOW POWER SWITCHED CAPACITOR DC-DC CONVERTERS FOR LOW POWER TRANSCEIVER APPLICATIONS

Masters of Science Thesis

Examiners: Professor Nikolay T. Tchamov, Svetozar Broussev Examiners and subjects were approved in the Faculty of Computing and Electrical Engineering Council meeting on 05-10-2011

#### PREFACE

This work has been done at the RF-ASIC Laboratory of Institute of Communications Engineering, TUT. The atmosphere of interaction and innovation of all teams at this location has a major influence on this work and will be a guiding experience for my future. I sincerely acknowledge how much I owe to all my colleagues and friends for their support, friendly challenges and fruitful competition.

I would like to thank Professor Nikolay Tchamov for giving me the opportunity to work in his research group and develop this design. I would also like to thank Svetozar Broussev and other team members of RF-ASIC department for their helpful advices during the design process.

Last but not least, my parents and friends have been a great source of motivation for me during this whole time. I would like to thank them with kindest regards possible.

Tampere, December 2011

Faizan ul haq Insinöörinkatu 60 D, 305 33720 Tampere FINLAND Tel. +358 44 3048911

## ABSTRACT

TAMPERE UNIVERSITY OF TECHNOLOGY Master's Degree Programme in Radio Frequency Electronics **UL HAQ, FAIZAN**: Low power Switched Capacitor (SC) DC-DC Converters for wireless transceiver applications Masters of Science Thesis, 72 pages February 2012 Major: Radio Frequency Electronics Examiners: Professor Nikolay T. Tchamov, Svetozar Broussev Keywords: DC-DC converter, Switched capacitor (SC),Digital Capacitance Modulation (DCM), Pulse Frequency Modulation (PFM), Metal Oxide Metal (MOM), Metal Oxide Semiconductor (MOS)

DC-DC converters, also known as switching voltage regulators, are one of the main components of a power management unit. Their main role is to provide a constant, smooth output voltage to power the electronic devices. Recent miniaturization trend of electronics circuitry has led to the need for smaller and high-efficient DC-DC converters in current and future applications.

This thesis presents a Switched Capacitor (SC) based DC-DC converter, which can directly operate at input voltage of 4.2V on 45nm CMOS process. Currently, most of the DC-DC converters on 45nm are not able to operate at such high voltages. Moreover, SC architecture has resulted in smaller size of converter compared with LC type DC-DC converters.

The design uses three SC topologies, which include two novel SC topologies of 2/5 and 2/7. Devices break down conditions have been overcome by implementing some of the MOS switches in cascoded structures. The converter structure uses eight phase interleaving approach to reduce output ripple to as low as 25mV level.

In addition to the main SC structure, a four-stage differential ring oscillator is designed for providing quadrature clock signals to the SC topologies. Clock generator can be enabled/disabled from outside the chip, through an enable (EN) pin. For instance, the EN pin can be used for regulating the output voltage in Pulse Frequency Modulation (PFM) feedback approach.

## TIIVISTELMÄ

TAMPEREEN TEKNILLINEN YLIOPISTO Radiotaajuuselektroniikan koulutusohjelma **UL HAQ, FAIZAN**: Low power Switched Capacitor (SC) DC-DC Converters for wireless transceiver applications Diplomityö, 72 sivua Helmikuu 2012 Pääaine: Radiotaajuuselektroniikka Tarkastajat: Professori Nikolay T. Tchamov, Svetozar Broussev Avainsanat: Tasajännitemuunnin, Kytketty kondensaattori, Digitaalinen kapasitanssimodulaatio, Pulssitaajuusmodulaatio, Metal Oxide Metal (MOM), Metal Oxide Semiconductor (MOS)

Tasajännitemuuttaja, eli hakkuriteholähde, on keskeinen komponentti tehon hallinta yksikössä. Sen tehtävänä on tuottaa vakio käyttöjännite elektroniselle laitteelle. Elektroniikan miniatyrisoinnin johdosta nykyisiin ja tuleviin laitteisiin tarvitaan pienikokoisia ja korkean hyötysuhteen tasajännitemuuttajia.

Tässä diplomityössä esitellään kytketty kondensaattori (switched capacitor, SC) periaatteella toteutettu tasajännitemuuttaja, joka kestää 4.2V sisäänmenojännitteen 45nm CMOS prosessissa. Suurin osa nykyisistä 45nm prosessilla toteutetuista tasajännitemuuttajista eivät pysty toimimaan näin korkeilla sisäänmenojänniteillä. SC rakenteen ansiosta suunniteltu piiri on kooltaan pienempi kuin LC tyyppiset tasajännitemuuttajat.

Suunniteltu piiri muodostuu kolmesta SC topologiasta, mukaanlukien uudet 2/5 ja 2/7 topologiat. Transistorien rikkoutumisen estämiseksi osa MOS kytkimistä on toteutettu kaskodi raknteena. Muuntimessa on käytetty kahdeksaa lomitettua vaihetta, joilla ulostulojännitteen vaihojännite osan amplitudi saadaan tiputettua jopa 25 mV:iin.

SC piirien lisäksi suunniteltiin differentiaalinen rengasoskillaattori tuottamaan kvadratuuri kello signaalit eri SC topologioille. Kellogeneraattori voidaan kytkeä päälle tai pois piirin ulkopuolelta käyttäen enable (EN) pinniä. EN pinniä voidaan käyttää esimerkiksi säädettäessä ulostulojännitettä pulssitaajuusmodulaatio (pulse frequency modulation, PFM) menetelmällä.

## CONTENTS

| TI | VIST                        | ELMÄ                      |                                              | 2  |

|----|-----------------------------|---------------------------|----------------------------------------------|----|

|    |                             |                           |                                              |    |

| TE |                             |                           | SYMBOLS                                      |    |

| 1  | INTRODUCTION                |                           |                                              |    |

|    | 1.1                         |                           | ground                                       |    |

|    | 1.2                         | Classi                    | ification of DC-DC converters                |    |

|    |                             | 1.2.1                     | Linear Regulators                            |    |

|    |                             | 1.2.2                     | 0.8                                          |    |

|    | 1.3                         |                           | of-the-art DC-DC converters                  |    |

|    | 1.4                         | U                         | n targets                                    |    |

| 2  | ON                          |                           | SWITCHED-CAPACITOR (SC) DC-DC converters     |    |

|    | 2.1                         | Impor                     | rtance of SC converters                      | 15 |

|    | 2.2                         |                           | operation of SC converter                    |    |

|    | 2.3                         | Loss 1                    | mechanisms in SC converters                  | 16 |

|    |                             | 2.3.1                     | Linear Efficiency Loss                       |    |

|    |                             | 2.3.2                     | Bottom Plate Capacitance Loss                |    |

|    |                             | 2.3.3                     | Gate Drive Loss                              |    |

|    | 2.4 Power delivery analysis |                           |                                              |    |

|    | 2.5 Output ripple           |                           | ıt ripple                                    |    |

|    | 2.6 Control schemes         |                           |                                              |    |

|    |                             | 2.6.1                     | Pulse Frequency Modulation (PFM)             |    |

|    |                             | 2.6.2                     | Pulse Width Modulation (PWM)                 |    |

|    |                             | 2.6.3                     | Digital Capacitance Modulation (DCM)         |    |

|    |                             | 2.6.4                     | Quasi Switched-Capacitor (QSC) configuration |    |

|    | 2.7 Implementation issues   |                           |                                              |    |

|    |                             | 2.7.1                     | MOS transistor switch implementation         |    |

|    |                             | 2.7.2                     | Integrated capacitor implementation issues   |    |

| 3  | Inte                        | grated                    | Implementation of SC DC-DC converter         |    |

|    | 3.1                         | Propo                     | osed Design                                  |    |

|    |                             | 3.1.1                     | Feedback Control Unit                        |    |

|    |                             | 3.1.2                     | 8-Phase Quadrature Clock Generator           |    |

|    |                             | 3.1.3                     | Topology Selector                            |    |

|    |                             | 3.1.4                     | Bias Voltage Generator                       |    |

|    | 3.2                         | 3.2 Topology Selection    |                                              |    |

|    | 3.3                         | 3.3 Switch Implementation |                                              |    |

|    | 3.4                         | .4 Capacitor Selection    |                                              |    |

|    | 3.5                         | Drive                     | r Design                                     | 40 |

|    | 3.6                         | Ripple                    | e Reduction                                  | 41 |

|    | 3.7                         | Clock                     | Generator Design                             | 41 |

|     | 3.8 Level Shifter Design          | .43 |

|-----|-----------------------------------|-----|

|     | 3.9 Simulation results            | .46 |

| 4   | MEASUREMENT SETUP                 | .54 |

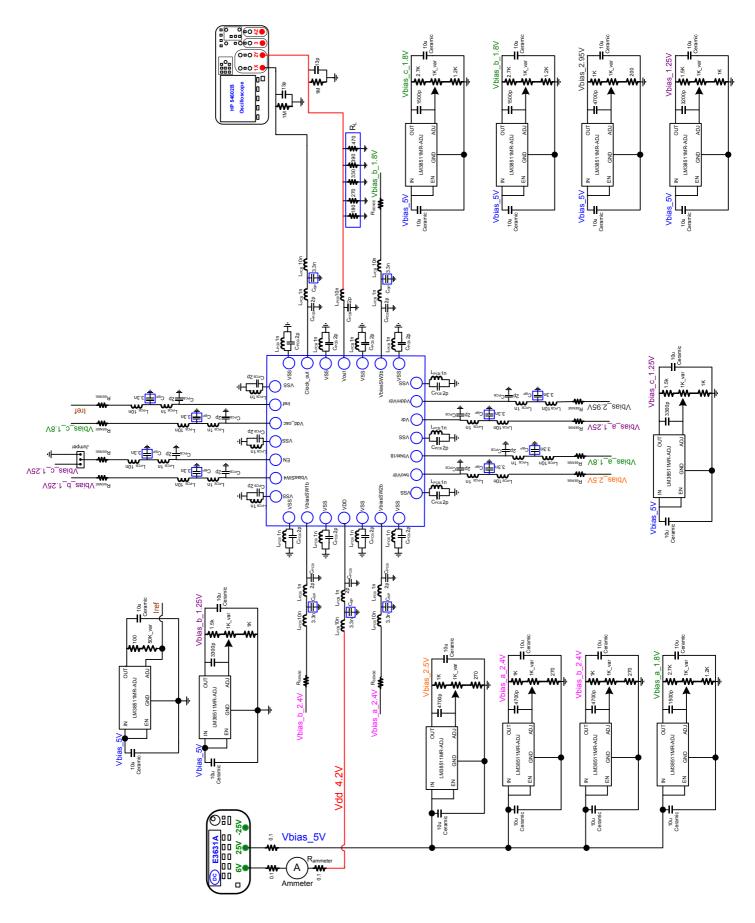

|     | 4.1 Load Resistor Calculations    | .54 |

|     | 4.2 LM38511 Resistor Calculations | .55 |

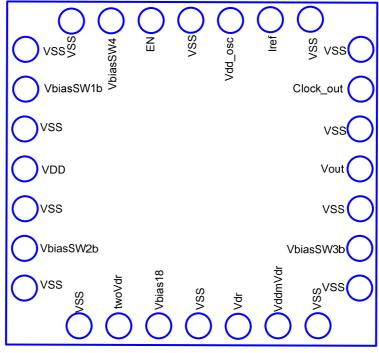

|     | 4.3 PIN Description               | .57 |

|     | 4.4 Electrical Characteristics    |     |

| 5   | LAYOUT DESIGN                     | .60 |

| 6   | CONCLUSION AND FUTURE WORK        | .65 |

| REF | ERENCES                           | .67 |

|     |                                   |     |

## FIGURES

| Figure 1-1. Use of DC-DC converters in portable electronic circuits                 | 9     |

|-------------------------------------------------------------------------------------|-------|

| Figure 1-2. Classification of DC-DC converters [5]                                  | 11    |

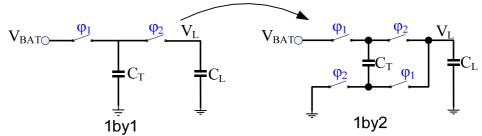

| Figure 2-1. A 1:1 SC converter topology                                             | 15    |

| Figure 2-2. Some common SC converter topologies a) 1by1 b) 1by2 c) 2by3 d)          |       |

| e)1by3 [1]                                                                          |       |

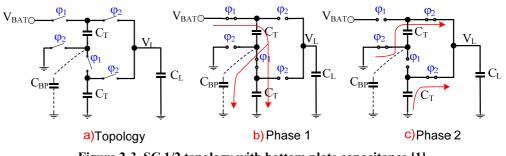

| Figure 2-3. SC 1/2 topology with bottom plate capacitance [1]                       | 19    |

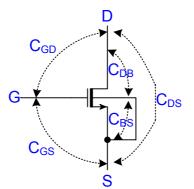

| Figure 2-4. MOS transistor parasitic capacitances                                   | 19    |

| Figure 2-5. SC converter structure improvement for higher output current            |       |

| Figure 2-6. Improved gain setting of SC topologies a) 1by1 b) 1by2 c) 1by3 d) 2by   | y3 e) |

| 3by4 [1]                                                                            | 22    |

| Figure 2-7. Basic 1/3 SC topology [25]                                              | 23    |

| Figure 2-8. (a) Voltage Waveforms without interleaving (b) Voltage waveforms        | with  |

| interleaving [25]                                                                   |       |

| Figure 2-9. Pulse Frequency Modulation                                              | 24    |

| Figure 3-1. Proposed SC DC-DC converter block diagram                               | 30    |

| Figure 3-2. One example for DCM Feedback Algorithm                                  | 30    |

| Figure 3-3. Theoretical linear efficiency versus Input voltage                      | 32    |

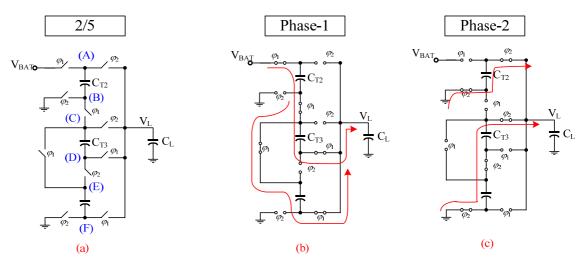

| Figure 3-4. Proposed SC topologies for required design a) 1by3 b) 2/5 c) 2/7 d) Com | bined |

|                                                                                     | 33    |

| Figure 3-5. Working operation of 2/7 topology a) 2/7 topology b) phase 1 operation  | on b) |

| phase 2 operation                                                                   | 34    |

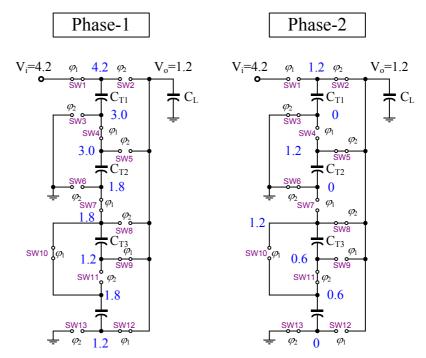

| Figure 3-6. Working operation of 1/3 topology, a) 1/3 topology b) phase 1 operation | on b) |

| phase 2 operation                                                                   | 34    |

| Figure 3-7. Working operation of 2/5 topology, a) 2/5 topology b) phase 1 operation | on b) |

| phase 2 operation                                                                   | 34    |

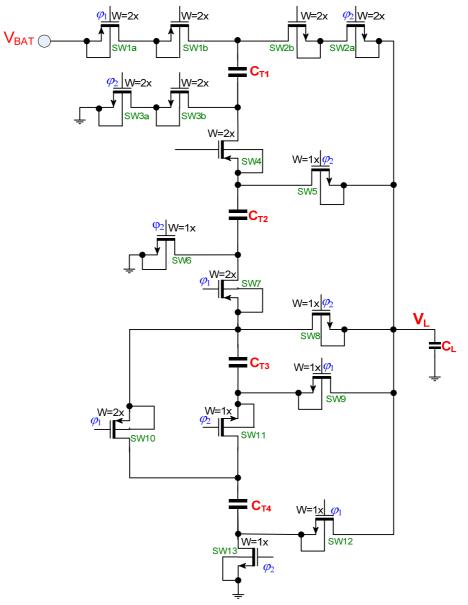

| Figure 3-8. Maximum voltage conditions for 2/7 topology                             | 36    |

| Figure 3-9. MOS implementation of 2/7 topology                                      | 37    |

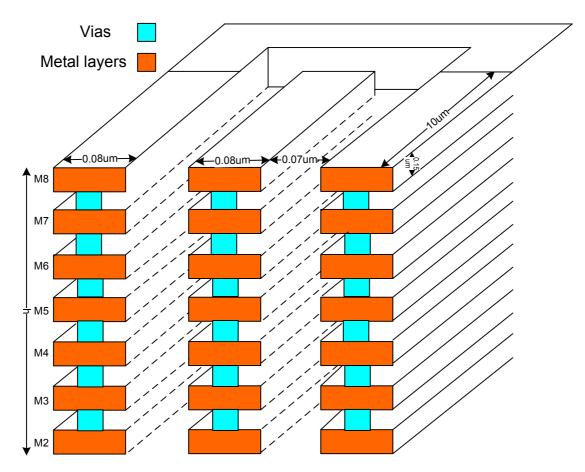

| Figure 3-10. Metal Insulator Metal (MOM) capacitor physical structure               | 38    |

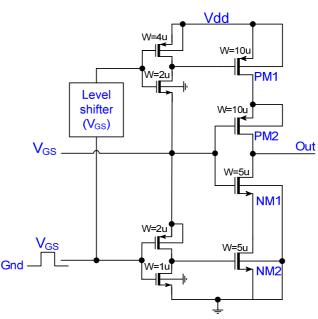

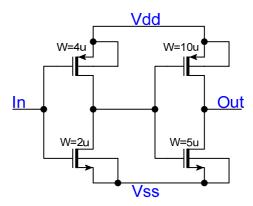

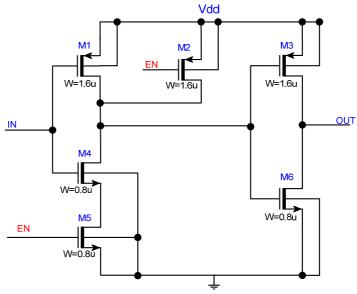

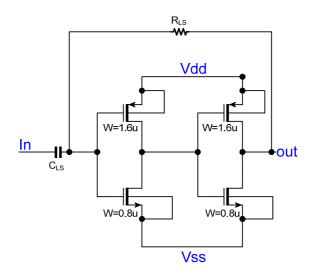

| Figure 3-11. Cascoded buffer design for clock voltages above breakdown limit [32]   | 41    |

| Figure 3-12. Buffer driver design                                                   | 41    |

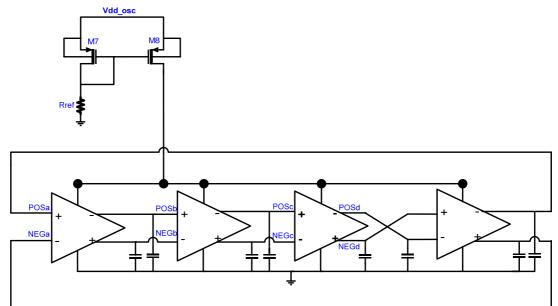

| Figure 3-13. Four Stage Differential Ring Oscillator for Clock generation [33]      | 42    |

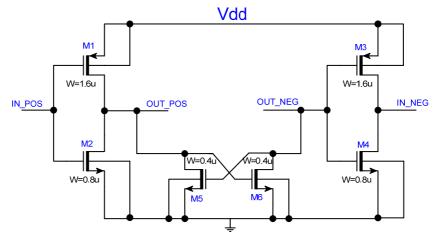

| Figure 3-14. Single stage of differential ring oscillator                           | 43    |

| Figure 3-15. AND Gate implementation                                                | 43    |

| Figure 3-16. Level shifter design [34]                                              | 44    |

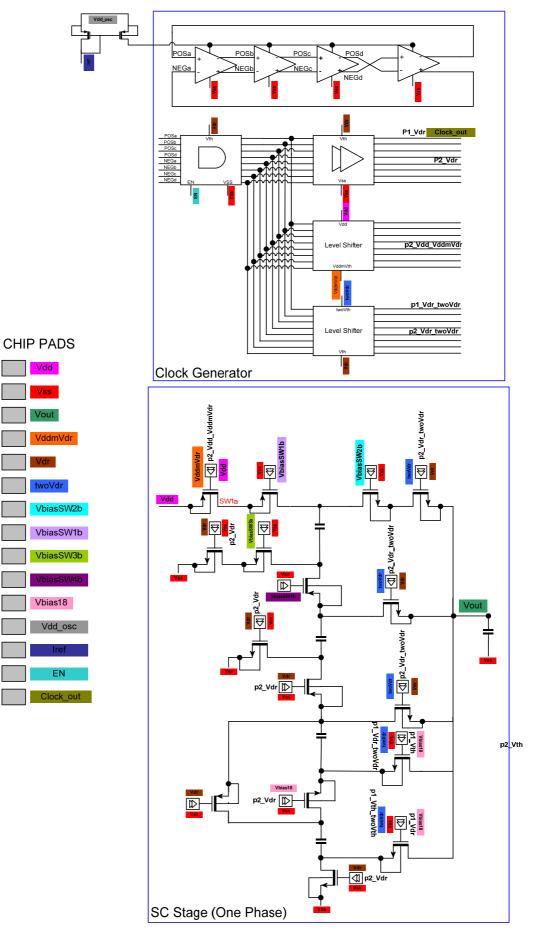

| Figure 3-17. Overall circuit diagram                                                | 45    |

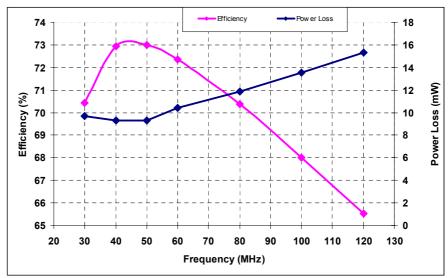

| Figure 3-18. Frequency versus Efficieny and Power loss                              | 46    |

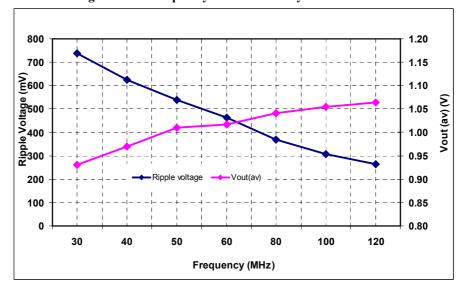

| Figure 3-19. Frequency versus Ripple voltage and Vout (av)                          | 46    |

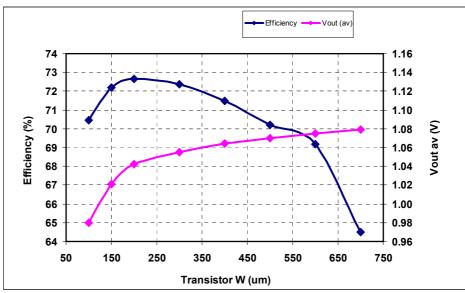

| Figure 3-20. Transistor width versus. Efficiency and Average output voltage         | 47    |

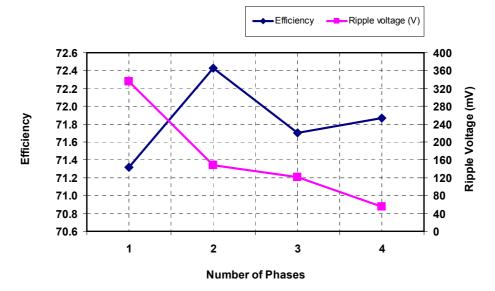

| Figure 3-21. Interleaving effect on output ripple                                   | 48    |

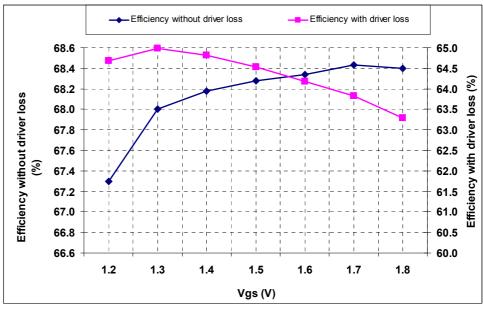

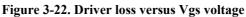

| Figure 3-22. Driver loss versus Vgs voltage                                         | 49    |

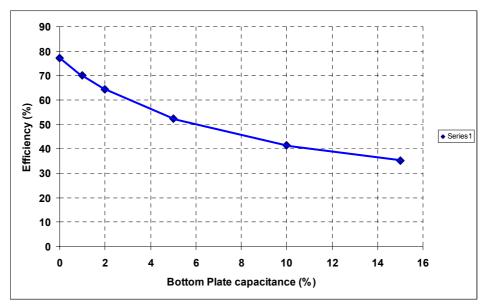

| Figure 3-23. Bottom Plate capacitance effect on Efficiency                          | 49    |

## 1. Introduction

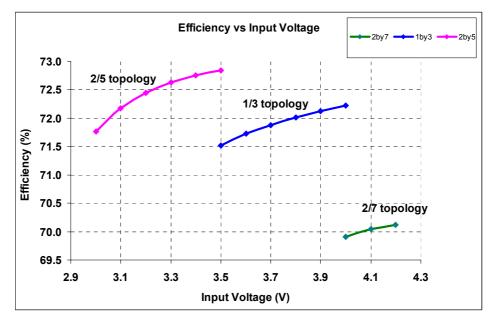

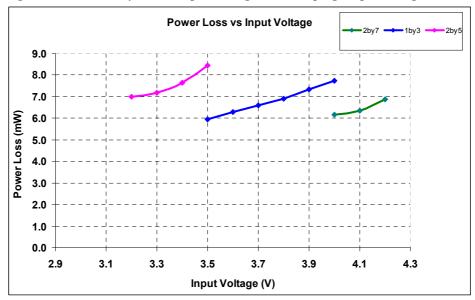

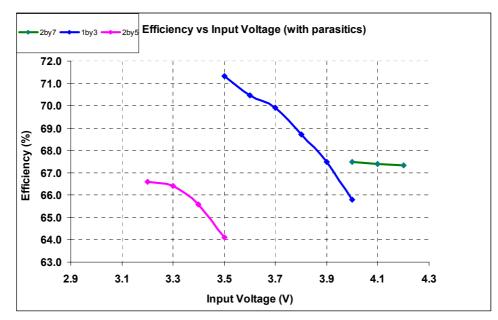

| Figure 3-24. Simulated Open loop Efficiency versus Input Voltage                   | 50 |

|------------------------------------------------------------------------------------|----|

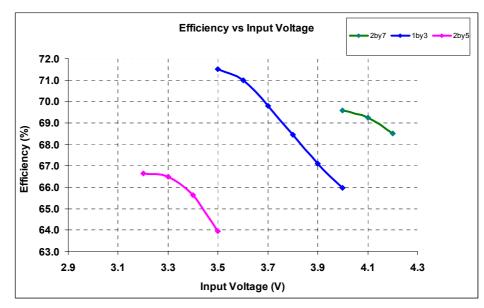

| Figure 3-25. Efficiency versus Input Voltage while keeping output voltage constant | 51 |

| Figure 3-26. Power Loss versus Efficiency while keeping output voltage constant    | 51 |

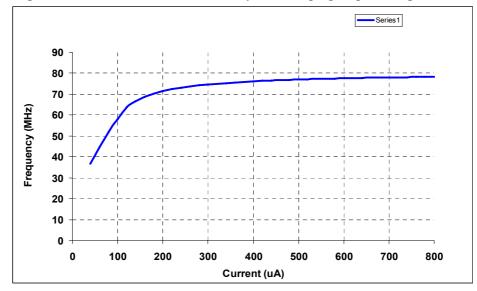

| Figure 3-27. Ring oscillator tuning curve                                          | 51 |

| Figure 3-28. Efficiency versus Input Voltage for final circuit                     | 52 |

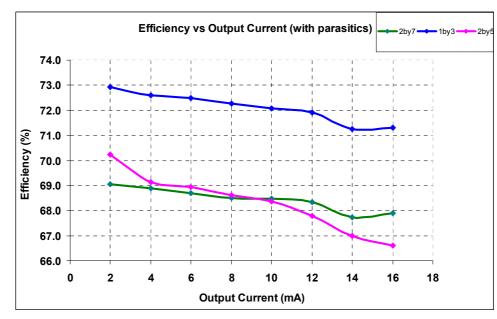

| Figure 3-29. efficiency versus Load current for final design                       | 53 |

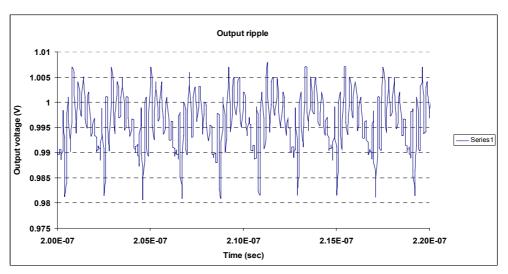

| Figure 3-30. Output ripple characteristics of final design                         | 53 |

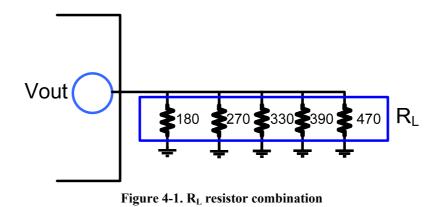

| Figure 4-1. R <sub>L</sub> resistor combination                                    | 55 |

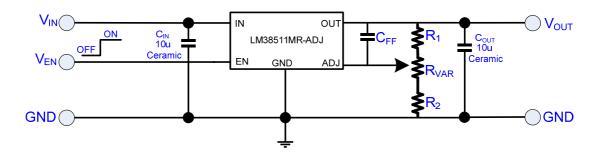

| Figure 4-2. LP38511-ADJ circuit diagram [37]                                       | 55 |

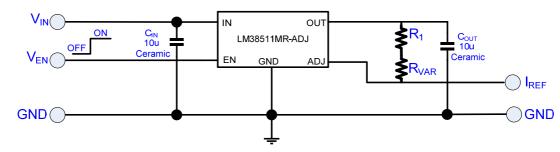

| Figure 4-3. LM38511MR-ADJ as reference current source                              | 56 |

| Figure 4-4. SC converter pin diagram                                               | 57 |

| Figure 4-5. SC DC-DC converter measurement setup                                   | 59 |

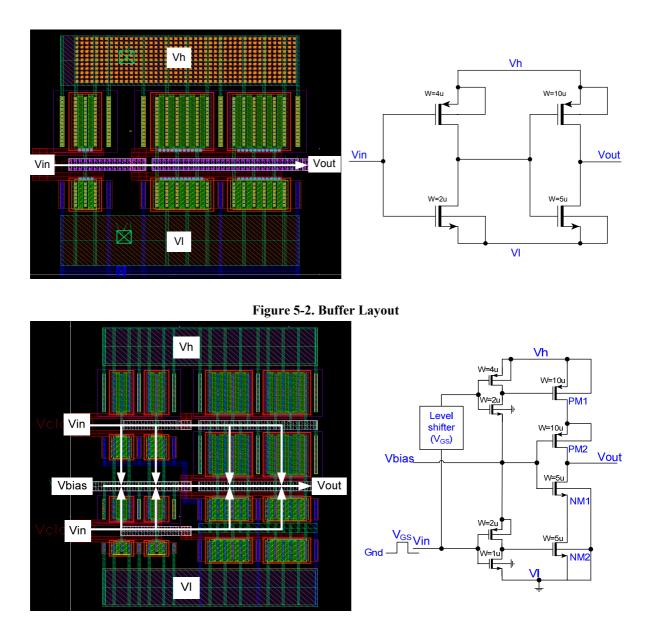

| Figure 5-1. Initial Layout Proposal                                                | 61 |

| Figure 5-2. Buffer Layout                                                          | 62 |

| Figure 5-3. Cascoded buffer layout                                                 | 62 |

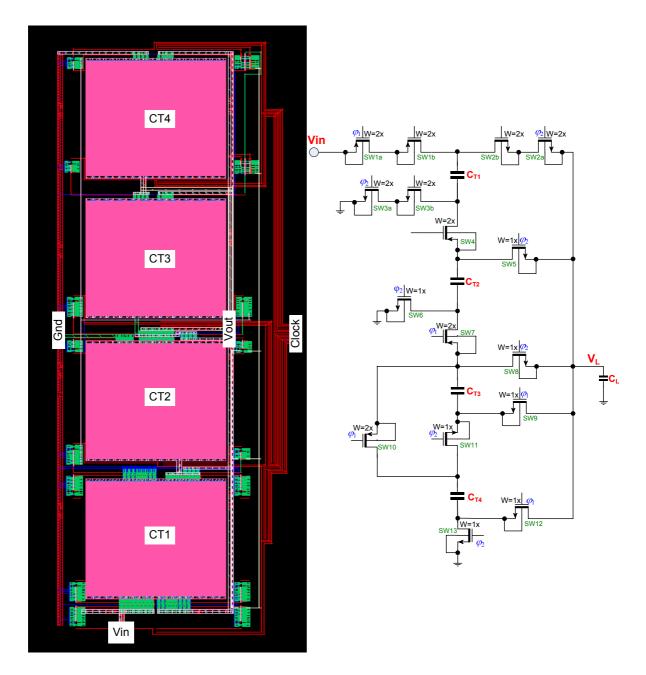

| Figure 5-4. Layout of one phase of SC converter                                    | 63 |

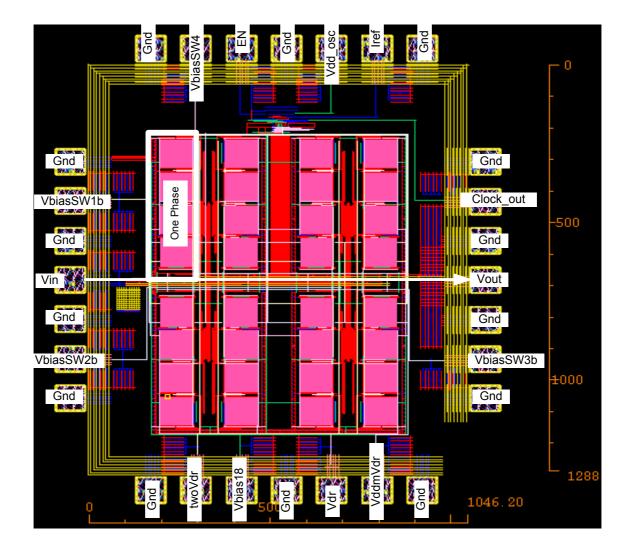

| Figure 5-5. Overall Layout                                                         | 64 |

|                                                                                    |    |

## **TERMS AND SYMBOLS**

| Symbols |                                  |

|---------|----------------------------------|

| SC      | Switched Capacitor               |

| DC-DC   | Direct Current to Direct Current |

| DVS     | Dynamic Voltage Scaling          |

| IC      | Integrated Circuit               |

| EMI     | Electromagnetic Interference     |

| SMC     | Switching Mode Converters        |

| U-DVS   | Ultra Dynamic Voltage Scaling    |

| PFM     | Pulse Frequency Modulation       |

| PWM     | Pulse Width Modulation           |

| DCM     | Digital Capacitance Modulation   |

| MOS     | Metal Oxide Semiconductor        |

| MIM     | Metal Insulator Metal            |

| MOM     | Metal Oxide Metal                |

|         |                                  |

# **1** INTRODUCTION

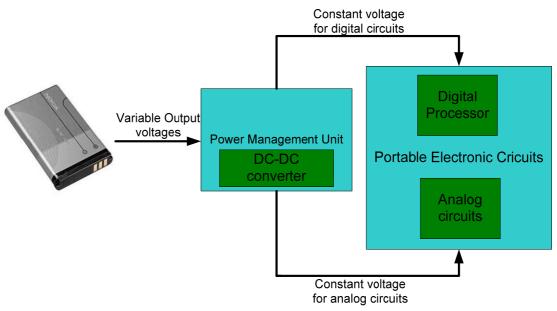

Recent advances in the portable electronics industry have led to the development of more compact and higher performance electronic systems. Currently, these devices are powered through portable batteries, such as Li-Ion battery. One of the main performance drawbacks of these batteries is their variable output voltage. As most of the portable electronic devices operate at a fixed power supply voltage; using the output voltage of these batteries directly as a power supply can change the performance level of the electronic blocks. Therefore, there is an imperative need for a power management electronics circuit between the battery output and the electronics circuit's supply input, see Figure 1-1. The main purpose of the power management unit is to take widely varying voltage from the battery, and to convert it to a fixed output voltage, that is suitable for the operation of electronics circuits.

DC-DC converters, also known as switching voltage regulators, are one of the main components of the power management unit. Their main role is to provide a constant, smooth output voltage to power electronic devices. Recent advances in electronics have made it possible to integrate digital and analog electronics circuits into a single silicon chip, also known as mixed-signal Integrated Circuits (IC's). For example, consider the case of mixed-signal IC's in a mobile handset. The processor present in the IC normally operates on 1V while the analog circuitry may require higher voltages to operate, see Figure 1-1. In addition to these different voltage requirements, increased demand for speed and smaller portable electronic devices has made the design of a power management system even more challenging. This thesis deals with the importance and the technological requirements imposed on the design of DC-DC converters. Moreover, a design of state-of-the-art Switched Capacitor (SC) DC-DC converter has been presented with necessary performance results. Chapter 1 deals with the different types of DC-DC converters while Chapter 2 details Switched Capacitor (SC) converters, which in the integrated electronics domain, are one of the important type of DC-DC converters. The explanation continues in Chapter 3, where a design of state-of-the-art DC-DC converter is presented with necessary simulation results. Then, chapter 4 explains the necessary procedure for practical measurement of proposed DC-DC converter. At the end chapter 5 deals with the layout and chapter 6 concludes the topic with comparison of designed circuit with other published designs.

#### 1. Introduction

Figure 1-1. Use of DC-DC converters in portable electronic circuits

## 1.1 Background

Portable-electronic circuits today, ranging from cell phones, laptops, pagers, wireless sets etc, operate on batteries as their power source. One of the most commonly used batteries for portable-electronics circuits are Li-Ion. The nominal output voltage of a Li-ion battery is 3.6V. However, during operation, the output voltage of these batteries can vary widely from 4.2V to 2.6V [30],[1]. This varying output voltage makes the Li-Ion battery unsuitable for the current integrated circuits due to their requirement for a constant DC supply voltage at different power domains. Therefore, designing a DC-DC converter, which can provide regulated DC output voltage at varying battery input voltages, has become imperative. Furthermore, the constant increase in circuit complexity, their smaller size and higher speeds have given rise to greater challenges in DC-DC converter design. A state-of-the-art DC-DC converter for today's portable integrated applications should possess the following characteristics:

- 1. High power efficiency

- 2. Small size ( $\sim 1 \text{ mm}^2$  or smaller).

- 3. No off-chip components (or small amount).

- 4. Higher current delivering ability

- 5. Wider input voltage range (should be directly able to operate with current batteries such as Li-ion having input voltage range 4.2-2.6V)

- 6. Low output voltage ripple (10-50mV or smaller)

In order to reduce power consumption, the present trend in digital integrated circuits is the use of Dynamic Voltage Scaling (DVS). In DVS, supply voltage of a digital circuit is lowered to reduce the power consumption of the circuit. According to [1] supply voltage has got a quadratic relationship with power consumption. i.e.:.

$$P_{CONSUMED} \propto (V_{SUPPLY})^2 \tag{1.1}$$

However, decreasing the supply voltage comes at the cost of circuit operating speed. As digital circuits are not operating all the time at higher speeds, voltage scaling can be done in times of lower speed operations, thereby reducing the power consumption. Thus DC-DC converters should provide scalable output voltages for DVS.

These factors pose various design challenges on DC-DC converter design for portable electronics applications. Various design methods are adopted to meet the above performance parameters. These different design approaches have led to the division of DC-DC converters into two main types, i.e. Linear and Switching converters. The next section deals with these main classifications of DC-DC converters in detail.

## 1.2 Classification of DC-DC converters

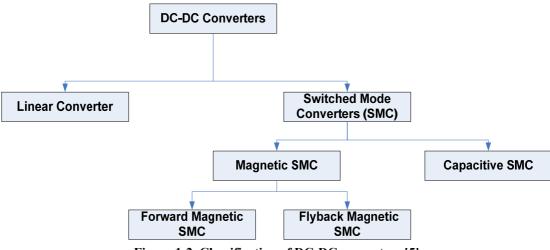

Based on their circuit operation, DC-DC converters are divided into two main types: Linear and Switching DC-DC converters. Furthermore, switched DC-DC converters have a more general classification of Buck and Boost converters. Buck converters provide an output voltage lower than the input voltage, while in Boost converters output voltage is higher than their input voltage. Figure 1-2 shows the main divisions of DC-DC converters.

Following text explains briefly different types of DC-DC converters.

### 1.2.1 Linear Regulators

Due to their simple design and smaller size, linear regulators are employed in a large number of applications. Linear regulators regulate the output voltage by changing the resistance of the active transistor [2]. As the output current is taken entirely from the input source through a controlled transistor resistance, the maximum efficiency of the linear regulator is limited to the ratio of the output voltage to the input voltage ( $V_L/V_{BAT}$ ). This efficiency limitation becomes quite critical when the difference between the battery and output voltage, also called the dropout voltage, is quite large. As a result, the use of linear regulators is only efficient for lower dropout voltages.

Figure 1-2. Classification of DC-DC converters [5]

## 1.2.2 Switching Regulators

The main transistor in switching regulators has either an 'on' or 'off' condition. This provides intermittent bursts of energy at the output. This working principle is different from that of the linear regulators, where the transistor operates in the active region all the time. As the transistors remain in saturation or cutoff region most of the time, switching regulators provide a much higher level of efficiency than linear regulators, which theoretically can go up to 100%. However, switching regulators are much more complex to design than linear regulators. They also generate Electromagnetic Interference (EMI) problems due to their switching action. On the basis of their main energy transfer components, switching regulators are further divided into Switched Capacitor (SC) converters and Magnetic switching mode converters.

Magnetic switching regulators consist of an inductor to smooth out the output ripples, which exist due to the switching operation of the regulator. Theoretically, these regulators are able to provide 100% efficiency, but the main problem with these regulators is their bigger size, which makes them unsuitable for integrated applications. Recent works [3],[4] have been able to design these regulators using monolithic inductors, but the space taken up by these regulators is still quite large. Magnetic regulators are further divided into Forward and Fly-back regulators. In Forward regulators, the energy goes from the input through the magnetic components and then to the load simultaneously. Fly-back regulators, on the other hand, first store energy from the input in the magnetic components and later release it to the load [5].

If the energy transfer component in switching converter is a capacitor rather than an inductor, resulting converters are categorized as Switched Capacitor (SC) DC-DC converters. More elaborated explanation of SC converters will be dealt in chapter 2. Here a brief summary for advantages/disadvantages of different DC-DC converter types is presented in Table 1.

| Converter Types               | Advantages                                                                                                                                                                                                                                                                 | Disadvantages                                                                                                                                                                                                                                                                                     |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Linear converters             | <ul> <li>High Efficiency for low<br/>dropout voltages</li> <li>Lower output ripples (practi-<br/>cally no ripples)</li> <li>Smaller size, ease of integra-<br/>tion</li> <li>Simple design</li> <li>Less EMI</li> </ul>                                                    | <ul> <li>Poor Efficiency for high<br/>dropout voltages</li> <li>Can provide only output<br/>voltages lower than input<br/>voltage</li> </ul>                                                                                                                                                      |

| Magnetic switching converters | Very high efficiency                                                                                                                                                                                                                                                       | <ul> <li>More complex design</li> <li>Not easily integrated</li> <li>Bigger size</li> <li>EMI problem</li> </ul>                                                                                                                                                                                  |

| SC converters                 | <ul> <li>Ease of integration</li> <li>Higher efficiency than linear regulators with large dropout voltage (same for LC)</li> <li>Smaller size compared to magnetic switching regulators</li> <li>Can provide higher or opposite polarity voltages (same for LC)</li> </ul> | <ul> <li>Only discrete number of<br/>output voltages are possible<br/>at peak efficiency. Scalable<br/>output voltage generation is<br/>difficult to obtain.</li> <li>Lower output current than<br/>Magnetic regulators</li> <li>Less efficient than Magnetic<br/>switching regulators</li> </ul> |

Table 1 Advantages/disadvantages of different DC-DC converter types

## 1.3 State-of-the-art DC-DC converters

Due to increased demand of small-sized and highly-efficient portable electronic systems, design requirements for DC-DC converters are becoming more and more challenging. Up till now, magnetic switching converters have offered the best possible efficiency but the bigger size and electromagnetic interference (EMI) generated by these regulators make them unsuitable for future miniature electronic systems. Therefore, emphasize of converter design is shifting towards Switched Capacitor (SC) DC-DC converters for future miniature applications.

SC DC-DC converters not only provide smaller size than magnetic switching converters, but they are also comparable and even superior to magnetic converters in terms of efficiency at low power levels. In addition, SC technology can have less EMI if operated with a single switching frequency clock. These evident benefits have led to increased research in the field of SC DC-DC converters. However, like all other design approaches, SC converters have some design limitations. Few of these are listed below:

- It is estimated that the current Li-Ion batteries will dominate the industry for atleast five to ten more years [30]. Output voltage of these Li-ion batteries vary from 4.2-2.6V [1]. This voltage poses a design problem in advanced silicon processes, as these voltages are much higher than voltage breakdown of the process. Because of this limitation, most of the current SC DC-DC converters operate at a lower input voltage generated by off-chip switching regulator.

- 2. SC converters have only discrete number of output voltages at peak efficiency i.e. scalable output voltage generation with equally high efficiency is difficult to obtain.

- 3. Integrated capacitors posses high value of bottom plate capacitance associated between bottom plate capacitor and substrate. If the capacitors are implemented with bottom plate connected to some other potential than ground a huge amount of power loss occurs during circuit operation due to charging and discharging of bottom plate capacitance.

- 4. Large currents require bigger capacitors in the design. This makes the size and losses associated with these capacitors quite big. Special silicon processes are required to produce high-density and linear integrated capacitors.

Recent works have tried to overcome these design limitations by introducing various novel techniques. References [7],[8] are examples of small size, fully integrated DC-DC converters in 45nm technology, while works [9],[10], provide scalable voltage conversion as well. For higher current designs, [11] is able to deliver 200mA of output current with an active area of only 0.37mm<sup>2</sup> in 32nm technology.

In the domain of magnetic switching converters, references [3],[4] are examples of designs with fully monolithic inductors. The sizes occupied by these converters are 3.76mm<sup>2</sup> and 1.592mm<sup>2</sup> respectively.

From the above discussion it is evident that state of the art monolithic SC DC-DC converter at the time of writing this thesis should possess the following properties:

- 1. Should directly operate from Li-ion battery.

- 2. Should provide a lower output voltage in range of 1-0.8V for near-future 32 and 28nm silicon processes.

- 3. Should provide scalable output voltage.

- 4. Should be fully integrated.

- 5. Should be as small as possible in size ( $\sim 1$  mm<sup>2</sup> or smaller).

- 6. Should possess efficiency comparable to the magnetic converters.

## 1.4 Design targets

Based on above discussion, design targets for this thesis have been presented in the Table 2. Due to the increased circuit complexity, this thesis focuses on the analysis and design of the power stage of DC-DC converter only. More importantly, power stage is the most crucial converter element in determining efficiency and output ripple. Therefore, a proper design of power stage ensures that the circuit will work properly in closed loop operation. Full closed loop operation of DC-DC converter requires feedback circuitry as well, design of which however, is left for future research.

|                | 8 1         |

|----------------|-------------|

| Input Voltage  | 3.2-4.2V    |

| Output Voltage | 0.9-1V      |

| Output Ripple  | 40mVp-p max |

| Output Current | 0-100mA     |

| Efficiency     | 60-80%      |

Table 2 SC DC-DC converter design specifications

# 2 ON CHIP SWITCHED-CAPACITOR (SC) DC-DC CONVERTERS

### 2.1 Importance of SC converters

The ever-growing increase in the demand for smaller and battery-efficient integrated circuits, have resulted in the need for a power management unit. In this context, switched capacitor converters, which are one of the main components of a power management unit, offer high potential for integration and smaller size. Although SC circuits tend to be less efficient than contemporary inductor-based switching converters, recent advances have developed various methods to reduce the loss mechanisms associated with SC designs.

Judging by current trends in the integrated circuit industry, it is logical to assume that SC converters will become an essential part of power management units in integrated circuits. In the text to follow, basic operation of SC converter will be explained. Loss mechanisms associated with SC converters will be elaborated. The discussion will continue with the efficiency and load current analysis of common SC converter topologies and at the end various control schemes adopted in SC converters together with implementation issues will be addressed. This theoretical knowledge will form a basis for the design of state of the art dc-dc converter in Chapter 3.

### 2.2 Basic operation of SC converter

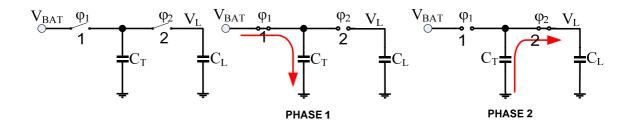

Consider the circuit shown in Figure 2-1, consisting of only switches and capacitors. The switches in the circuit are operated by two distinct non-overlapping clock signals,  $\varphi_1$  and  $\varphi_2$ , so that the switches turn on when the clock signal is high.

Figure 2-1. A 1:1 SC converter topology

During  $\varphi_1$ , the battery voltage starts charging the charge-transfer capacitor  $C_T$  through switch 1. The charging time depends on the on-resistance of the switch and a small amount of voltage is dropped across the switch-on resistance. Similarly, during  $\varphi_2$ switch 1 turns off, switch 2 turns on, and  $C_T$  discharges into the load capacitor  $C_L$ through switch 2. If the switch on-resistance is assumed to be negligible, then the output voltage at no-load condition (V<sub>NL</sub>) will be equal to the input battery voltage. Because of this, the SC converter topology shown in Figure 2-1 is called 1:1 SC topology.

In practice, SC converters always have some load attached with them. Moreover, switch on-resistance Ron is not negligible. Due to these load and switch on-resistances, output voltage  $V_L$  of the SC converter drops below the no-load output voltage  $V_{NL}$ . The difference between the  $V_{NL}$  and  $V_L$  is known as dropout voltage and is given by  $\Delta V = V_{NL}$ - $V_L$ . It has been observed that  $V_L$  is mainly dependent on output current, switching frequency, and the charge transfer capacitor's value. The value of  $V_L$  is important in determining the linear efficiency related with the SC converter given by [1].

$$\eta_{LIN} = \frac{V_L}{V_{NL}} \tag{2.1}$$

Equation (2.1) implies that a smaller value for  $V_L$  will result in a loss in efficiency, and thus it is not possible to use a single SC converter topology in a power-efficient way, if multiple output voltages are desired.

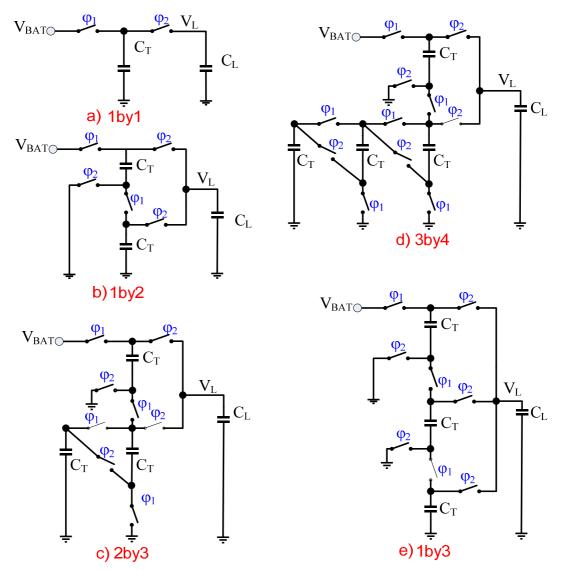

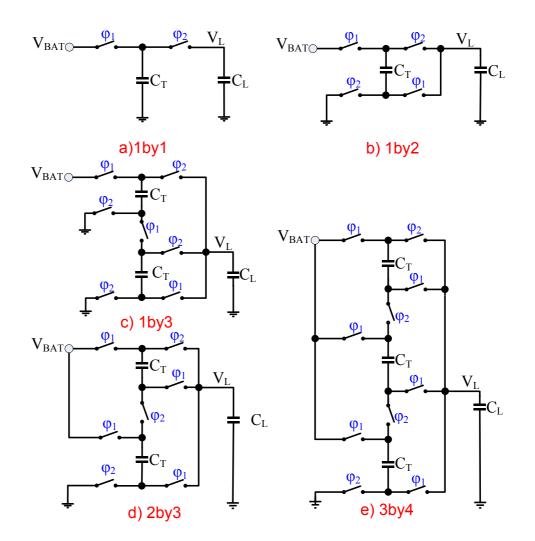

The limitation imposed on the linear efficiency by SC converters demands the need for separate SC converter topologies whose output voltages are quite near to their no-load voltages. Recent developments of SC converter topologies are able to produce no-load voltages of 1, 1/2, 1/3, 2/3, 3/4, 1/4, 2/5 and 3/5 of battery voltages, etc [1], [6]. Other topologies can also be made by changing the configuration of the SC structure. Therefore, if scalable output voltages are required, various topologies need to be switched in the main circuit, so that the overall dropout voltage always remains low. Figure 2-2 shows some common topologies of SC converters.

### 2.3 Loss mechanisms in SC converters

Various loss mechanisms exist in SC converters due to which power efficiency of SC is greatly suffered. Most important of these loss mechanisms are explained below:

#### 2.3.1 Linear Efficiency Loss

In all SC converter topologies, maximum power efficiency is limited by equation (2.1), where  $V_L$  is the output voltage of DC-DC converter, and  $V_{NL}$  is the output voltage at no

load condition. This efficiency loss due to topology structure is known as linear efficiency loss. The reason for linear efficiency loss is due to charging and discharging of energy-transfer capacitors, where the charge-transfer currents cause power losses dissipated mainly in the capacitor series resistance ( $R_{ESR}$ ) and the switch on resistance  $R_{ON}$  [15].

It has been observed that  $V_L$  is mainly dependent on output current, switching frequency and charge-transfer capacitors value. A lower value of  $V_L$  will result in lower efficiency, which is one of the major drawbacks of SC converters. As a result, in order to obtain similar efficiency for large range of output voltages, multiple topologies are required so that  $V_L$  is always quite close to  $V_{NL}$  [9].

Figure 2-2. Some common SC converter topologies a) 1by1 b) 1by2 c) 2by3 d) 3by4 e)1by3 [1]

The above statement can also be expressed in terms of dropout voltage, which is given as  $\Delta V = V_{NL}$ . For the same switching frequency and charging capacitor values, smaller dropout voltage will result in higher efficiency but lesser output current. Thus, if a certain topology is unable to provide required output current at certain dropout voltage, a higher  $V_{NL}$  topology is used. Use of higher  $V_{NL}$  will result a drop in efficiency but load current requirements will be met [9].

As the maximum efficiency can be achieved only with minimum possible drop out voltage; switching frequency, charging capacitor size and switch conductance must be increased to reduce dropout voltage value.

#### 2.3.2 Bottom Plate Capacitance Loss

In SC converters, parasitic capacitances exist from the bottom plate of the charge transfer capacitors to ground. The bottom plate capacitance can be up to 5-20% of the total charge-transfer capacitance and constitute a major role in SC circuits transfer functions [1]. In gate-oxide implementation of capacitors with N-well as a bottom plate, the parasitic arise due to reverse-biased diode capacitance of N-well, p-substrate junction [1]. If  $C_{BP}$  represent the bottom plate capacitance of the charge transfer capacitance  $C_{T}$ , then

$$C_{BP} = \alpha.C_T \tag{2.2}$$

Where  $\alpha$  is a constant and can be from 5-20% for on-chip capacitors oxide capacitors [1].

The power loss associated with bottom plate capacitance is given as [28]:

$$P_{bp} = f_{sw} \sum_{i} C_{bp,i} V_{bp,i}^{2}$$

(2.3)

Where  $f_{sw}$  is switching frequency,  $C_{bp}$  is bottom plate capacitance and  $V_{bp}$  is the maximum voltage swing across bottom plate capacitance.

Consider a SC converter topology shown in Figure 2-3. The circuit operates in two distinct and non-overlapping phases  $\varphi_1$  and  $\varphi_2$ . In phase 1, switches connected with  $\varphi_1$  turn on, charging the two charge transfer capacitors C<sub>T</sub> at half of battery voltage V<sub>BAT</sub>.

Figure 2-3. SC 1/2 topology with bottom plate capacitance [1]

In this phase the switches connected to  $\varphi_2$  are open. Similarly, in phase 2 switches connected to  $\varphi_2$  turn on, charging the output capacitor C<sub>L</sub> through the charge-transfer capacitors C<sub>T</sub>. The process repeats in next cycle.

Bottom plate capacitance associated with upper charge-transfer capacitor  $C_T$  also gets charged to  $V_{BAT}/2$  during  $\varphi_1$ . During  $\varphi_2$ , this bottom plate capacitance gets connected to the ground terminal and useful energy stored in the  $C_{BP}$  capacitor is wasted. If the bottom plate capacitance is big enough, then this energy loss can result in notable efficiency degradation [1].

#### 2.3.3 Gate Drive Loss

When a transistor is switched on in SC converters, parasitic capacitances associated with the transistor switches get abruptly discharged to zero [17]. Power consumed in this process is given by [27].

$$P_{sw} = f_{sw} \cdot \sum_{i} C_{MOS,i} \cdot V_{i}^{2}$$

(2.4)

Where  $C_{MOS}$  represents any of the MOS transistor capacitances e.g.  $C_{gs}$ ,  $C_{gd}$ ,  $C_{sb}$ , and  $C_{db}$  etc, while  $V_i$  represents the maximum voltage swing across these capacitors (see Figure 2-4). Overall switching loss  $P_{sw}$  will then be the sum of the power losses of all these capacitors  $C_{gs}$ ,  $C_{gd}$ ,  $C_{sb}$ , and  $C_{db}$ .

Figure 2-4. MOS transistor parasitic capacitances

Increasing the width of the transistor is associated with bigger transistor parasitic capacitances and will eventually increase the gate drive loss. On the other hand, bigger transistor width results in smaller  $R_{ON}$ , which will decrease the conduction loss. Hence, there is an optimum width of the transistor at which efficiency is maximum.

Overall efficiency equation of the SC converter will then include all the above mentioned losses, and it is given by:

$$\eta = \frac{P_o}{P_o + P_{SW} + P_{bp} + P_{Cntrl}}$$

(2.5)

Here  $P_o$  is total output power,  $P_{sw}$  is switching power loss,  $P_{bp}$  is bottom plate capacitance power loss and  $P_{cntrl}$  is the control circuitry power loss.

#### 2.4 Power delivery analysis

Consider SC converter 1/2 topology shown in Figure 2-3. For analysis purpose we will consider that the bottom plate capacitance is negligible. In phase 1, switches connected with  $\varphi_1$  turn on, charging the two charge transfer capacitors C<sub>T</sub> at half of battery voltage V<sub>BAT</sub>. Energy extracted from the battery during  $\varphi_1$  is given by [9]:

$$E_{BAT} = C_T \cdot V_{BAT} \cdot \Delta V \tag{2.6}$$

Where  $\Delta V$  is given by  $\Delta V = V_{NL} - V_{L}$ .

During  $\varphi_2$  charge transfer capacitors C<sub>T</sub> get connected to the load and transfer a charge twice than the charge gained in  $\varphi_1$ . Hence the energy delivered to the load in is given by [9]:

$$E_{L} = 2.C_{T} V_{L} \Delta V \qquad (2.7)$$

Linear efficiency of the SC converter is given by:

$$\eta_{LIN} = \frac{E_L}{E_{BAT}} = \frac{2.C_T.V_L\Delta V}{C_T.V_{BAT}.\Delta V} = \frac{V_L}{V_{BAT}/2}$$

(2.8)

As  $V_{BAT}$  / 2=V<sub>NL</sub> so

$$\eta_{LIN} = \frac{E_L}{E_{BAT}} = \frac{V_L}{V_{NL}} = \frac{V_{NL} - \Delta V}{V_{NL}} = \left(1 - \frac{\Delta V}{V_{NL}}\right)$$

(2.9)

The power delivered to the load is given by [9]:

$$P_{o} = \frac{E_{L}}{t_{s}} = E_{L} \cdot f_{s} = 2.C_{T} \cdot V_{L} \cdot \Delta V \cdot f_{s} = E_{BAT} \cdot f_{s} \cdot \eta_{LIN}$$

(2.10)

Where  $f_s$  is switching frequency of converter and  $t_s$  is the switching period.

It can be seen from Equation (2.10) that the power delivered to the load can be increased by increasing the switching frequency and/or the charge-transfer capacitor value. Moreover, increasing  $\Delta V$  will cause increase in the amount of power delivered to the load, but it will result in decreased linear efficiency. Therefore, if a topology is unable to provide enough power at the output, a higher topology should be used having higher  $\Delta V$  to meet the load requirements [9].

Reference [1] reports improvement in conventional SC converter topologies shown in Figure 2-2. The improved topologies possess higher current delivering ability. In conventional SC converter topologies, battery voltage has no direct connection with the load. During  $\varphi_1$ , charging capacitors get charged from the battery voltage with no connection to the load, while in  $\varphi_2$  load capacitor is charged to V<sub>L</sub> by the charging capacitors. This conventional process can be improved, for more output current, by providing a path from battery voltage to load during both charging phases  $\varphi_1$  and  $\varphi_2$ . For clear understanding consider a conventional 1:1 SC converter topology shown in Figure 2-5 [1].

The topology can be improved for delivering more output current by connecting the ground terminal of bottom most charge transfer capacitor to the load. According to [1], "If a particular gain setting in the previous version gave out a voltage ratio of p/q, then by connecting the ground terminal of the bottom-most charge-transfer capacitor during  $\varphi_1$  to the load terminal, a gain setting with a voltage ratio of p/(p + q) can be obtained."

The improved topology shown in Figure 2-5, results in charging the load capacitor in both phases of converter. This results in higher output current. It has also been observed that the improved topologies provide lower bottom plate parasitic losses [1]. Figure 2-6 shows some common topologies for SC converters with output current enhancing improvement.

Figure 2-5. SC converter structure improvement for higher output current

Figure 2-6. Improved gain setting of SC topologies a) 1by1 b) 1by2 c) 1by3 d) 2by3 e) 3by4 [1]

## 2.5 Output ripple

One of the major concerns in DC-DC converter design is the output voltage ripple, since many electronic circuits require extremely smooth output voltage. Therefore, the need for low ripple DC-DC converters becomes evident. It has been observed that the output ripple of SC DC-DC converter can be reduced by [21]:

- 1. Increasing the switching frequency.

- 2. Decreasing the load current.

- 3. Increasing the charge-transfer capacitor value.

- 4. Increasing the load capacitor value.

- 5. Reducing the  $R_{ESR}$  of the capacitors

- 6. Keeping the clock duty cycle far from 0 and 100%

Among all, the most influential parameters for output ripple in SC converters are load capacitance and duty cycle. An optimum value of duty cycle and bigger load capacitance value will result in smaller output ripple [24].

In designs where smooth output voltage is of main importance, various schemes have been implemented to reduce the output ripple voltage. One major approach is known as **Interleaving** [25]. The main idea of interleaving scheme is to give less time for discharge the output capacitor, so to lower the output ripple [26].

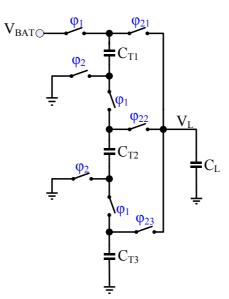

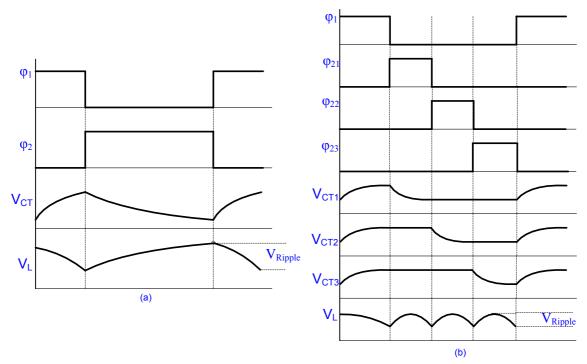

Figure 2-7 shows a basic 1/3 SC topology. The topology can be operated with or without interleaving as explained below.

In normal operation of the converter without interleaving, each capacitor gets charged to 1/3 of input voltage during  $\varphi_1$ . In  $\varphi_2$ , all the charge transfer capacitors are connected in parallel with each other and get discharged through C<sub>L</sub> simultaneously. This results in the voltage curves shown in Figure 2-8 (a). If lower output ripple is desired, interleaving approach is implemented. The main idea is to discharge each charge transfer one by one into the load capacitor. This will result in lesser time to discharge the capacitors and hence the output ripple will be smaller. Voltage waveforms of SC converter with interleaving are shown in Figure 2-8(b).

### 2.6 Control schemes

Various schemes have been presented in the literature, which can regulate the output voltage of an SC DC-DC converter by changing some relevant parameters like switch ing frequency, pulse width, charging current and charge transfer capacitor value. Some of the most important schemes are presented below.

Figure 2-7. Basic 1/3 SC topology [25]

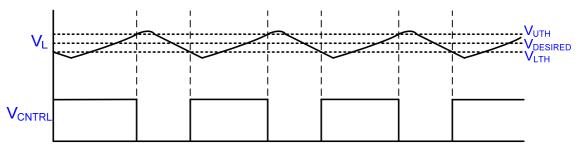

#### 2.6.1 Pulse Frequency Modulation (PFM)

Pulse frequency modulation, or pulse skipping modulation, is one of the most common schemes employed in SC dc-dc converter designs [18]. Its main principle of operation is shown in Figure 2-9.

Figure 2-8. (a) Voltage Waveforms without interleaving (b) Voltage waveforms with interleaving [25]

Figure 2-9. Pulse Frequency Modulation

When load voltage  $V_L$  falls below a certain defined lower threshold voltage  $V_{LTH}$ , the  $V_{CNTRL}$  signal goes to its high level. A high level  $V_{CNTRL}$  permits the clock signal to get connected to the SC stage, allowing the output capacitor to get charged through the charging capacitors. This will eventually raise the output voltage back to the  $V_{DESIRED}$  value. In the same manner, when the load voltage goes above the defined threshold voltage  $V_{UTH}$ , the  $V_{CNTRL}$  signal goes low, disabling the clock connection from SC stage, thereby bringing the  $V_L$  back to  $V_{DESIRED}$ .

In some implementations of the pulse frequency modulation scheme, the clock frequency can also be changed to control the output voltage  $V_L$ . As higher switching frequency leads to more switching losses, the decrease in frequency at smaller loads results in higher efficiency for lighter loads [19].

#### 2.6.2 Pulse Width Modulation (PWM)

By controlling the pulse width of the clock pulse in SC converters, the charging time of the capacitors can be controlled. This charging time eventually controls the amount of charge transferred to the load capacitor and, therefore, the output voltage. This form of feedback scheme, implementing changing pulse width to the clock signal, is known as pulse width modulation. It has been observed that the output ripples and efficiency of SC converter are dependent on the pulse width [20],[21]. A changing pulse width will result in varying output ripple voltage and efficiency. Pulse width modulation scheme, in this context, has the drawback of not achieving optimum efficiency and minimum output ripples.

#### 2.6.3 Digital Capacitance Modulation (DCM)

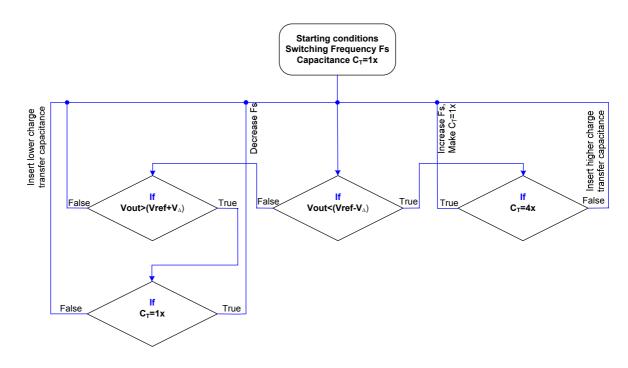

In a digital capacitance modulation scheme, in order to control the output voltage, the amount of charge transfer capacitance involved in the SC converter is changed. For example, if a 4 bit DCM scheme is used, SC structure can be designed with 1x, 2x, 4x and 8x sized charging capacitors. In the beginning 1x topology is inserted into the main circuit and if the load current demands are not met, a 2x or higher topology can be inserted in the main circuit to meet to load current demand. [19]. One example of DCM algorithm can be seen in Figure 3-2.

For optimum efficiency, the switch resistance should be such that the charging capacitors settle down during phase 1 or phase 2. This means that the switch width is also changed in DCM when changing the charging capacitor value. This will help in reducing the bottom plate parasitic capacitance and/or switching losses [1].

A DCM control scheme has the advantage of having lower EMI interference compared to PFM, due to constant frequency operation. This property makes this scheme useful for the mixed signal IC designs where the noise generated can interfere with digital circuits [19]. Additionally, DCM bottom plate capacitance and switching losses scale down at lower load currents due to smaller transistor widths.

#### 2.6.4 Quasi Switched-Capacitor (QSC) configuration

In a quasi switched-capacitor scheme, capacitor charging current is changed in order to control the output current. In this scheme, the MOS transistors are operated in the satu-

ration region and the gate voltage of the MOS is used to control the output voltage. QSC scheme has got two main problems: 1) the conduction loss of the MOS transistors increase in the saturation region; 2) when the load current increases and comes to a limit, the switch will work from the saturation to the triode region, so it doesn't let the input current control achieve the fixed output voltage [22].

Using the QSC scheme makes the input current of the converter continuous. This reduces the EMI introduced by a pulsating current and the transistors do not need to be over-rated in order to cope with the short duration of instantaneous charging current stress. These converters are small, have low EMI and a lower output ripple. The design approach consists of two SC topologies in parallel working in anti-phase with each other. Because the linear charging process of the capacitors is dependent on the applied gate voltage, the output voltage is less affected by the supply voltage variations [23].

A brief summary for advantages/disadvantages of different feedback control schemes is presented in Table 3

| Control Schemes             | Advantages                                                                    | Disadvantages                                                                                          |  |

|-----------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--|

| Pulse Frequency Modulation  | • Ease of implementation                                                      | • Generates EMI problem due to<br>presence of harmonic compo-<br>nent of changing clock fre-<br>quency |  |

|                             |                                                                               | 0                                                                                                      |  |

| Pulse Width Modulation      | <ul><li>Ease of implementation</li><li>Constant frequency scheme so</li></ul> | • Optimum efficiency is not achieved due to changing pulse                                             |  |

|                             | less EMI generation problem                                                   | width                                                                                                  |  |

|                             |                                                                               | • Minimum output ripple is not                                                                         |  |

|                             |                                                                               | possible due to changing pulse                                                                         |  |

|                             |                                                                               | width. Output ripple is depend-                                                                        |  |

|                             |                                                                               | ent on clock pulse width                                                                               |  |

|                             |                                                                               | • Constant frequency makes the                                                                         |  |

|                             |                                                                               | switching losses higher at smaller loads                                                               |  |

| Digital Capacitance Modula- | • Constant frequency scheme so                                                | • Requires more complicated                                                                            |  |

| tion                        | less EMI problem                                                              | structure of charge transfer ca-                                                                       |  |

|                             | • Bottom plate parasitic capaci-                                              | pacitors                                                                                               |  |

|                             | tance losses and/or switching                                                 |                                                                                                        |  |

|                             | losses reduce at smaller load                                                 |                                                                                                        |  |

|                             | currents.                                                                     |                                                                                                        |  |

Table 3. Advantages/disadvantages of different feedback control schemes in dc-dc converters

| Quasi Switched Capacitor con- | • Low EMI due to continuous      | • Conduction loss of MOS tran-      |

|-------------------------------|----------------------------------|-------------------------------------|

| figuration                    | input current                    | sistors is more                     |

|                               | • Smaller size                   | • In limiting case of load current, |

|                               | • Lower output ripple            | MOS transistor goes from satu-      |

|                               | • Less influence of supply volt- | ration to triode region There-      |

|                               | age variations                   | fore, not allowing the input cur-   |

|                               |                                  | rent to control the output volt-    |

|                               |                                  | age.                                |

## 2.7 Implementation issues

Main circuit components in SC converters are capacitors and switches. These switches were implemented before by diodes but with the advent of MOS technology, MOS transistors are becoming increasingly popular due to their small dropout voltage in integrated circuits. Implementing MOS transistors as switches, pose a number of implementation issues. We will address these practical implantation details, one by one for MOS transistors and integrated capacitors in the topics to follow:

### 2.7.1 MOS transistor switch implementation

An ideal switch in SC converter has zero on-resistance and no parasitic capacitance associated with it. In practice, there is always a compromise between on-resistance and parasitic capacitance. Increasing the width 'W' of the MOS transistor will result in smaller on-resistance, but on the other hand it increases the parasitic capacitance of the switch. As discussed in Section 2.3.3, smaller switch-on resistance decreases the conduction loss and bigger parasitic capacitance increases the switching losses. A bigger gate parasitic capacitance will also require larger current to charge it up. This will result for a need of bigger input buffer. Therefore, there is optimum width  $W_{opt}$  of the transistor at which both losses are minimal and efficiency is at maximum.

MOS transistors need to be operated in triode region for minimum on-resistance. Gate voltages should also need to be close to the transistor rating to improve conduction. A higher gate voltage will be able to charge the gate parasitic capacitance faster and there-fore conduction will be improved. However, higher gate drive voltages increase the gate drive loss. Some important concerns about MOS switch implementation are mentioned below:

- 1. Drive the transistors with the maximum drive level possible to improve conduction.

- 2. NMOS is preferred option over PMOS because of higher mobility and smaller size.

- 3. Use the transistors with the voltage rating close to the gate drive voltage to optimize their size.

- 4. Implement a dead time between different phases of converters, to eliminate possible short-circuit current.

- 5. Bulk terminal is normally biased with the highest voltage possible in PMOS and with lowest possible voltage in case of NMOS.

- 6. Instantaneous voltages appearing at the nodes of circuit after the switching from one phase to another are important and can damage the devices. Their affects should also be considered [27].

Due to the presence of different driving voltage requirements of transistors, in SC converters, required gate voltages of the MOS transistors in SC converter can be different. These driving voltage requirements pose a need to design level shifters for driving the transistors operating at different voltage levels.

#### 2.7.2 Integrated capacitor implementation issues

Shrinking size of electronic devices with technology improvements has resulted in the need for smaller and more efficient integrated circuits. Therefore, technology is shifting now from off-chip implementation of capacitors to on-chip integrated capacitors. On-chip capacitor implementation poses a lot of problems: 1) the quality factor associated with integrated capacitors is very small compared to the off-chip capacitors; 2) the parasitic capacitance associated with the on-chip capacitors can be huge proportion of total capacitance. Moreover, it is very difficult to achieve bigger on-chip capacitance without compromising on the chip area.

Integrated capacitors can be implemented by different techniques e.g. Metal Insulator Metal (MIM) capacitors, Metal Oxide Metal (MOM) capacitors, Gate-oxide capacitors, Poly-metal capacitors, double poly capacitors, etc. Gate oxide capacitors offer the largest capacitance per area, but they are highly non-linear and, additionally, gate oxide capacitors have high bottom plate capacitance to the substrate (5-15%). Double poly capacitors can be the second efficient solution. They have lower capacitance per unit area than thin oxide, but have smaller stray capacitance (about 5%) [29]. Other integrated capacitors have low energy densities with lower parasitics e.g. MIM capacitors. Some specialized processes offer a high-metal layer high density capacitor with a reasonable energy density and low parasitics [28]. Table 4 summarizes the parasitic capacitance factor  $\alpha$  and maximum efficiency  $\eta$  of common capacitor types. A 0.1 value of  $\alpha$  will mean that the parasitic capacitance is 10% of original value.

| Capacitor type | α         | η (max) % |

|----------------|-----------|-----------|

| Poly-metal     | 0.2-0.5   | 50-64     |

| Thin oxide     | 0.05-0.15 | 68-80     |

| Double-poly    | 0.05      | 80        |

| External       | 0.002     | 95.6      |

| Table 4 Practical capacitor | type properties | [29]. |

|-----------------------------|-----------------|-------|

|-----------------------------|-----------------|-------|

# 3 INTEGRATED IMPLEMENTATION OF SC DC-DC CONVERTER

Chapter 2 provided a basic theoretical knowledge related with switched capacitor converters. Performance differences of SC technique were compared with other conventional approaches. Moreover, different loss mechanisms associated with SC converters were elaborated in details. This knowledge will now form basis for the design of state of the art DC-DC converter presented in this chapter. Based on the current design needs, as presented in 1.3, key specifications for the required dc-dc converter are given in Table 2

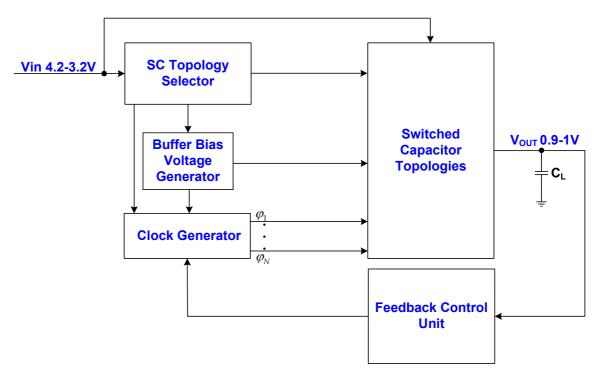

## 3.1 Proposed Design

The proposed design for SC DC-DC converter is presented in Figure 3-1. Apart from SC power stage, the circuit requires additional blocks for operating as a DC-DC converter. A short explanation of these blocks with their intended operation is provided below.

### 3.1.1 Feedback Control Unit

Function of feedback control unit is to change the necessary parameters in clock generator based on the comparison of output voltage with a reference voltage. For example, if the output demands more current, feedback control unit can ask the clock generator to increase the clock frequency. Similarly, if Digital Capacitance Modulation feedback is used, control unit can ask the clock generator to insert additional capacitance for heavier load current demand. This is done by providing clock signal path to additional capacitance stage. Feedback control unit will also ask the clock generator to change the SC power stage topologies, by blocking clock to some transistors, in case load current/voltage requirements are not met.

One example of Digital Capacitance Modulation feedback algorithm is presented in Figure 3-2. Operation starts with initial charge transfer capacitance of 1x. Feeback compares the output voltage with two threshold voltages Vref+ $\Delta V$  and Vref- $\Delta V$ . If the output voltage is lower than Vref- $\Delta V$ , either charge transfer capacitance or switching frequency Fs is increased to meet load demand. On the other hand, for output voltages higher than Vref+ $\Delta V$ , SC structure switches to lower charge transfer capacitance values and/or lower switching frequencies.

Figure 3-1. Proposed SC DC-DC converter block diagram

Figure 3-2. One example for DCM Feedback Algorithm

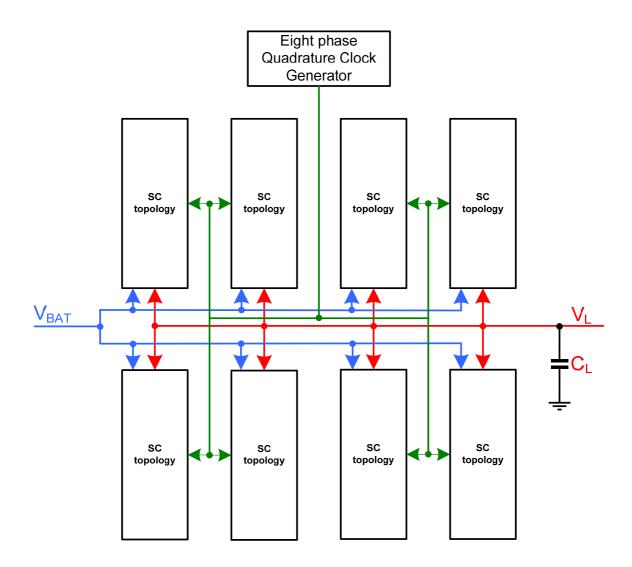

#### 3.1.2 8-Phase Quadrature Clock Generator

The proposed SC topologies work with eight phase interleaving approach. Interleaving requires designing of eight phase quadrature clock generator. In addition to clock gen-

eration, the clock circuit should be able to block clock signals to some transistors in power stage. This is done in order to change the SC topologies.

A four stage differential ring oscillator was designed to implement the clock generator. Output of the clock generator is followed by level shifters in order to meet the requirements of some transistor clock voltages. Design of differential ring oscillator and level shifters in explained in detail in Section 3.7.

#### 3.1.3 Topology Selector

SC topologies need to be switched based on the different input voltage requirements. This is required in order to preserve linear efficiency of converter. Topology selector

will compare input voltage with certain set of reference voltages and select certain topology which provides best possible efficiency for that range of input voltage.

#### 3.1.4 Bias Voltage Generator

Additional bias voltages are required for buffer drivers attached with the power transistors. A separate internal bias voltage generator is required in order to generate these voltages. Design of bias voltage generator should take this fact into consideration that the bias voltages are in relation with input voltage. If the input voltage changes, some of the bias voltages in circuit should also change in same amount. For example a 1V increase/decrease in input voltage will require 1V increase/decrease in some of the bias voltages.

Next sections from 3.2 to 3.4 explain the design of SC power stage in more detail.

## 3.2 Topology Selection

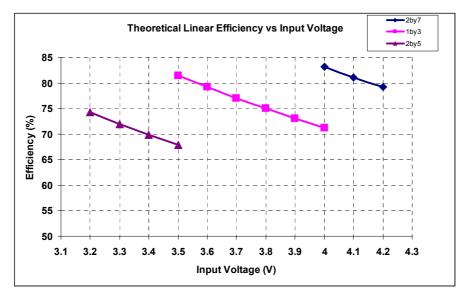

Wide range of input voltage requirement poses a design challenge due to linear efficiency loss, given by equation (2.1). Different SC topologies need to be switched in the main circuit to preserve efficiency. For our design requirements three SC topologies 2/5, 1/3, and 2/7 were chosen for the varying input voltage requirements. Assuming 0.2-0.25 V  $\Delta$ V is required to meet load current demands, calculations below show that the maximum theoretical efficiency will vary from 83.33 to 67.85%.

| First Input Voltage Range: 3.2-3.5V  |                                             |  |

|--------------------------------------|---------------------------------------------|--|

| SC topology chosen: 2/5              | $V_L$ (required) = 0.95V                    |  |

|                                      |                                             |  |

| $V_{NL}$ @ 3.2 = (3.2).(2/5) = 1.28V | $\eta = (1 - (1.28 - 0.95)/1.28) = 74.21\%$ |  |

| $V_{NL}$ @ 3.5 = (3.5).(2/5) = 1.4V  | $\eta = (1 - (1.4 - 0.95)/1.4) = 67.85\%$   |  |

| Second Input Voltage Range: 3.5- 4V  |                                             |

|--------------------------------------|---------------------------------------------|

| SC topology required: 1/3            | $V_L$ (required) = 0.95V                    |

|                                      |                                             |

| $V_{NL}$ @ 3.5 = (3.5).(1/3) = 1.16V | $\eta = (1 - (1.16 - 0.95)/1.16) = 81.89\%$ |

| $V_{NL}$ @ 4 = (4).(1/3) = 1.33V     | $\eta = (1 - (1.33 - 0.95)/1.33) = 71.42\%$ |

|                                      |                                             |

| Third Input Voltage Range: 4-4.2 V   |                                             |

| SC topology chosen: 2/7             | $V_L$ (required) = 0.95V                    |

|-------------------------------------|---------------------------------------------|

| $V_{NL}$ @ 4 = (4).(2/7) = 1.14V    | $\eta = (1 - (1.14 - 0.95)/1.14) = 83.33\%$ |

| $V_{NL}$ @ 4.2 = (4.2).(2/7) = 1.2V | $\eta = (1 - (1.2 - 0.95)/1.2) = 79.16\%$   |

Figure 3-3 shows calculated theoretical linear efficiency for different input voltages

Figure 3-3. Theoretical linear efficiency versus Input voltage

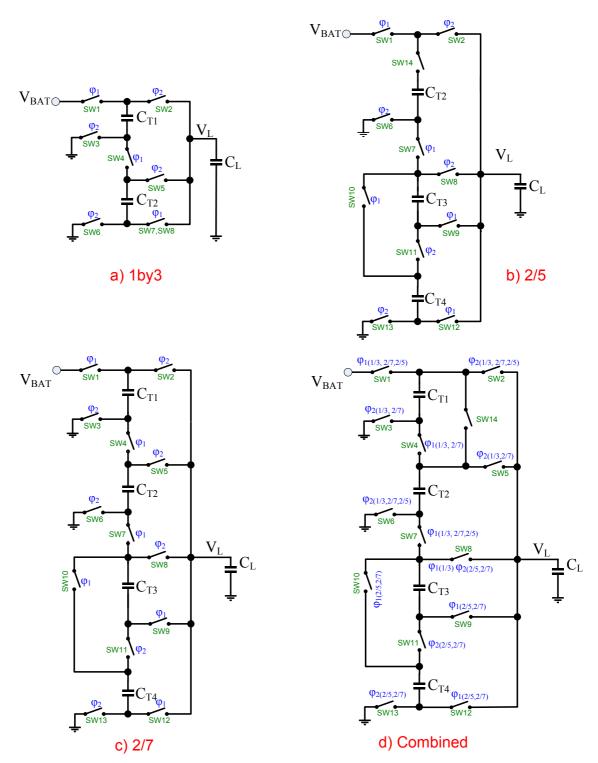

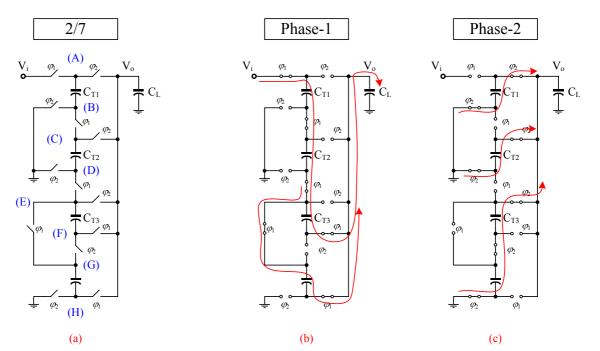

The proposed 2/5, 1/3 and 2/7 topologies are presented in Figure 3-4. The combined topology was made by uniting all topologies together. During the operation of SC, these topologies will switch into the circuit depending upon the load and input voltage requirements. The operation of the above mentioned topologies is shown in Figure 3-5 to Figure 3-7.

During the  $\varphi_{1,}$  Load capacitor  $C_L$  is charged from battery voltage, through chargetransfer capacitors  $C_{T1}$  to  $C_{T4}$ . Charge transfer paths for each topology are shown by red arrows in respective figures. Similarly in  $\varphi_2$ , charge accumulated by charge transfer capacitors is transferred to load capacitor by connecting them together. Different capacitor arrangement in SC topologies results in the unique no-load voltages at the output.

Figure 3-4. Proposed SC topologies for required design a) 1by3 b) 2/5 c) 2/7 d) Combined

#### 3. Integrated Implementation of SC DC-DC converter

Figure 3-5. Working operation of 2/7 topology a) 2/7 topology b) phase 1 operation b) phase 2 op-

Figure 3-6. Working operation of 1/3 topology, a) 1/3 topology b) phase 1 operation b) phase 2 operation

Figure 3-7. Working operation of 2/5 topology, a) 2/5 topology b) phase 1 operation b) phase 2 operation

During the closed loop operation of SC converter, above topologies will be configured in the main switching matrix based on the input voltage range and output voltage. If the output voltage falls below a certain value for a certain topology, a higher topology is needed to meet up the load current requirements.

The design of a closed-loop feedback circuit was not in the scope of this work. The selected topologies will be switched manually in simulations and measurements to check the performance for all voltage range.

#### 3.3 Switch Implementation

Advanced CMOS processes with gate lengths of 45nm or lower possess a drawback of having break down voltages of 1.8V or lower. Currently many of the portable electronics devices are operated from Li-ion batteries whose voltages can go up to 4.2V. Therefore, design an integrated DC-DC converter operating at such higher input voltages becomes a challenge due to lower MOS breakdown voltages.

One solution of above problem is to use cascoded MOS structures. The idea is to connect the MOS transistors in cascoded configuration so that the overall voltage across the single MOS transistor does not go beyond 1.8V. As an example, consider 2/7 topology shown in Figure 3-8. During the circuit operation, maximum and minimum possible voltages appearing at different nodes are shown in blue color. These voltages are calculated with assumption of no-load condition and ideal switches. It can be seen that SW1, SW2 and SW3 have maximum voltage of 3V across them. Therefore, transistor implementation of these switches, need to be cascoded in order to eliminate breakdown conditions.

Some practical limitations still remain in cascoded implementation of transistors. Firstly, in order to provide the same on-resistance, transistor sizes in cascoded implementation will be approximately double than their normal size, which will result in bigger size of overall layout. Secondly, the clock signal requirements will become complex for the cascoded implementation.

The choice of using NMOS or PMOS depends on the specific location of MOS switch in the SC configuration. In normal cases, NMOS implementation is preferred over the PMOS because of higher mobility and smaller size for the same on-resistance. This choice is also dictated by the ease of gate drive voltage generation. In some cases of SC implementation, PMOS transistor was preferred over NMOS because the drive voltages were easier to generate from level shifters. 2/7 SC converter topology with MOS switch implementation is shown in Figure 3-9.

Figure 3-8. Maximum voltage conditions for 2/7 topology

SW1, SW2 and SW3 have been implemented using cascoded transistors SW1a, SW1b, SW2a, SW2b, SW3a, and SW3b respectively. This was decided by observing the drain to source voltage  $V_{DS}$ , gate to source voltage  $V_{GS}$ , and gate to drain voltages  $V_{GD}$ , across the MOS transistors, at highest input voltage of 4.2V. The voltage across SW1-3 in such condition is 3V at no load condition. Therefore, connecting two MOS transistors in cascode, each rated 1.8V, avoids breakdown conditions.

#### 3.4 Capacitor Selection

As discussed in section 2.3.2, bottom plate capacitance can be a major loss component in SC topologies, where floating capacitors are used. Proposed design in this work is quite sensitive to bottom plate capacitance loss due to presence of floating capacitors. Moreover, high current at output demands the need for high density capacitor. These two requirements made the selection of the capacitors quite challenging.

Three types of integrated capacitors, namely Metal-Insulator-Metal (MIM), Metal-Oxide-Semiconductor (MOS) and Metal-Oxide-Metal (MOM), were analyzed for the proposed design. Table 5 shows the advantages and disadvantages of these capacitors for integrated implementation.

Figure 3-9. MOS implementation of 2/7 topology

| Capacitor type | Pros                                                                                                                     | Cons                                                                                         |

|----------------|--------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| MOS capacitor  | • High capacitance density 7-9 fF/um <sup>2</sup>                                                                        | <ul> <li>Higher bottom Plate capacitance 5-15% [29].</li> <li>Non-linear CV curve</li> </ul> |

| MOM capacitor  | <ul> <li>Higher capacitance density<br/>then MIM cap.~ 3.8-<br/>4.4fF/um<sup>2</sup></li> <li>Linear CV curve</li> </ul> | • Higher Bottom plate capaci-<br>tance then MIM capacitors                                   |

| MIM Capacitor  | <ul><li>Low bottom plate capacitance</li><li>Linear CV curve</li></ul>                                                   | • Smaller capacitance density.~<br>1-2 fF/um <sup>2</sup>                                    |

Table 5 Integrated Capacitors advantages/disadvantages

In regard of smaller bottom plate capacitance, MIM capacitors offer the best choice. However, MIM capacitors are not suitable in higher current designs due to extremely bigger size. On the other hand, MOS capacitor, offer the best possible capacitance density, but it has high bottom-plate capacitance. Simulation results showed a drastic decrease in efficiency from 70% to 44% because of the MOS capacitor bottom plate capacitance. Therefore, a compromise was made to choose MOM capacitors which offer acceptable capacitance density and lower bottom plate capacitance at the same time.

MOM capacitor still consumes a huge portion of silicon chip. Standard eight phase Interleaving has been adopted to lower the output capacitor size for the required output ripple. In addition, output current specifications have been lowered from 100mA to 16mA in order to keep the chip size in practical limits.

Cadence design kit did not have a simulation model available for MOM capacitor so the value of capacitor was calculated using simple assumptions provided below. See Figure 3-10 for reference.

Figure 3-10. Metal Insulator Metal (MOM) capacitor physical structure

Metal Layer 2-8 thickness  $T_M = 0.15$ um [35] Dielectric (between metal layers) thickness  $T_D = 0.30$ um [35] Dielectric relative permittivity  $\varepsilon_r = 2.6$  [35] Metal Layer width W<sub>M</sub>= 0.08um (minimum possible width) [33] Metal Layer Length L<sub>M</sub>= 10um (assumption) Separation between adjacent Metal layers d =0.07um (minimum possible separation)

Assumption: Space covered by Vias is approximately half the area of metal layers. Therefore, the effective dielectric thickness becomes half of its original value i.e. 0.30 um/2 = 0.15 um