### HELENA ASTOLA COMBINING ERROR-CORRECTING CODES AND DECISION DIAGRAMS FOR THE DESIGN OF FAULT-TOLERANT LOGIC Master of Science Thesis

Examiners: Prof. Ioan Tabus Prof. Radomir Stanković Subject approved in the meeting of The Faculty Council of Computing and Electrical Engineering on April 6, 2011

## ABSTRACT

TAMPERE UNIVERSITY OF TECHNOLOGY Master's Degree Programme in Information Technology HELENA ASTOLA : Combining Error-Correcting Codes and Decision Diagrams for the Design of Fault-Tolerant Logic Master of Science Thesis, 63 pages September 2011 Major: Signal Processing Examiners: Prof. Ioan Tabus and Prof. Radomir Stanković Keywords: Error-correcting codes, logic design, fault-tolerant circuits, decision diagrams

In modern logic circuits, fault-tolerance is increasingly important, since even atomicscale imperfections can result in circuit failures as the size of the components is shrinking. Therefore, in addition to existing techniques for providing fault-tolerance to logic circuits, it is important to develop new techniques for detecting and correcting possible errors resulting from faults in the circuitry.

Error-correcting codes are typically used in data transmission for error detection and correction. Their theory is far developed, and linear codes, in particular, have many useful properties and fast decoding algorithms. The existing fault-tolerance techniques utilizing error-correcting codes require less redundancy than other error detection and correction schemes, and such techniques are usually implemented using special decoding circuits.

Decision diagrams are an efficient graphical representation for logic functions, which, depending on the technology, directly determine the complexity and layout of the circuit. Therefore, they are easy to implement.

In this thesis, error-correcting codes are combined with decision diagrams to obtain a new method for providing fault-tolerance in logic circuits. The resulting method of designing fault-tolerant logic, namely error-correcting decision diagrams, introduces redundancy already to the representations of logic functions, and as a consequence no additional checker circuits are needed in the circuit layouts obtained with the new method. The purpose of the thesis is to introduce this original concept and provide fault-tolerance analysis for the obtained decision diagrams.

The fault-tolerance analysis of error-correcting decision diagrams carried out in this thesis shows that the obtained robust diagrams have a significantly reduced probability for an incorrect output in comparison with non-redundant diagrams. However, such useful properties are not obtained without a cost, since adding redundancy also adds complexity, and consequently better error-correcting properties result in increased complexity in the circuit layout.

## TIIVISTELMÄ

TAMPEREEN TEKNILLINEN YLIOPISTO Tietotekniikan koulutusohjelma HELENA ASTOLA: Combining Error-Correcting Codes and Decision Diagrams for the Design of Fault-Tolerant Logic Diplomityö, 63 sivua Syyskuu 2011 Pääaine: Signaalinkäsittely Tarkastajat: Prof. Ioan Tabus ja Prof. Radomir Stanković Avainsanat: Virheitäkorjaavat koodit, logiikkasuunnittelu, vikasietoiset piirit, päätösdiagrammit

Moderneissa logiikkapiireissä vikasietoisuuden merkitys on entistä suurempi, sillä komponenttien pienentyessä jopa atomitason epätäydellisyydet voivat aiheuttaa häiriöitä piirien toiminnassa. Olemassaolevien tekniikoiden lisäksi onkin tärkeää kehittää uusia menetelmiä, joilla häiriöistä johtuvat virheet voidaan havaita ja korjata.

Virheitäkorjaavia koodeja käytetään tyypillisesti tiedonsiirrossa aiheutuvien virheiden havaitsemiseen ja korjaamiseen. Näiden koodien teoria on pitkälle kehittynyttä, ja erityisesti lineaarisilla koodeilla on useita hyödyllisiä ominaisuuksia ja tehokkaita dekoodausalgoritmeja. Logiikkapiirien vikasietoisuuden lisäämisessä käytetyt menetelmät, jotka pohjautuvat virheitäkorjaaviin koodeihin, toteutetaan tavallisesti liittämällä piiristöön erityisiä dekoodauksen suorittavia piirejä, ja nämä menetelmät vaativat usein vähemmän redundanssia kuin muut vastaavat tekniikat.

Päätösdiagrammit ovat tehokas keino esittää logiikkafunktioita, jotka toteutuksen teknologiasta riippuen määrittävät suoraan suunniteltavan piirin kompleksisuuden, ja niiden toteuttaminen piiritasolla on helppoa.

Tässä opinnäytetyössä virheitäkorjaavat koodit ja päätösdiagrammit yhdistämällä on kehitetty uudenlainen tekniikka vikasietoisen logiikan suunnitteluun. Kehitetyllä menetelmällä redundanssi saadaan jo logiikkafunktioiden esitysmuotoihin eikä valmiissa piireissä näin ollen tarvita ylimääräisiä virheiden havainnoinnin tai korjaamisen suorittavia osia. Opinnäytetyön tarkoituksena on esittää tämä uusi menetelmä ja arvioida saatujen päätösdiagrammien vikasietoisuutta.

Opinnäytetyössä on mallinnettu kehitetyn menetelmän suorituskykyä vikasietoisuuden kannalta ja osoitettu, että suunnittelun tuloksena saaduilla virheitäkorjaavilla päätösdiagrammeilla on huomattavasti pienempi todennäköisyys virheellisiin ulostuloihin kuin vastaavilla tavanomaisilla diagrammeilla. Redundanssin lisääminen kuitenkin lisää myös kompleksisuutta, ja tehokkaamman virheenkorjauksen myötä piirin kompleksisuus kasvaa. Kuitenkin jo maltillisella kompleksisuuden lisäämisellä saavutetaan huomattavia parannuksia piirin vikasietoisuudessa.

## PREFACE

This Master of Science thesis has been written for the Department of Signal Processing at the Tampere University of Technology. The research done for this thesis in the Department of Signal Processing has also resulted in two research papers, [4] and [5], which introduce and analyze the fault-tolerant logic design application discussed in this thesis.

I wish to thank my supervisors Prof. Ioan Tabus and Prof. Radomir Stanković for their valuable comments and guidance, and Ph.D. Stanislav Stanković for his help and taking part in the research. I am also grateful to Prof. Jaakko Astola for his help and support.

Tampere, August 15, 2011

Helena Astola helena.astola@tut.fi

# CONTENTS

| 1. Intre | $\operatorname{oduction}$                                           | 1  |  |  |  |  |  |  |

|----------|---------------------------------------------------------------------|----|--|--|--|--|--|--|

| 2. Mat   | hematical Background                                                | 3  |  |  |  |  |  |  |

| 2.1      | Discrete Functions                                                  | 3  |  |  |  |  |  |  |

| 2.2      | Decision Diagrams                                                   | 5  |  |  |  |  |  |  |

| 2.       | 2.1 Binary Decision Diagrams                                        | 6  |  |  |  |  |  |  |

| 2.       | .2.2 Multiple-Valued Decision Diagrams                              | 8  |  |  |  |  |  |  |

| 2.       | .2.3 Multi-terminal and Shared Decision Diagrams                    | 9  |  |  |  |  |  |  |

| 2.3      | Fields and Vector Spaces                                            | 9  |  |  |  |  |  |  |

| 2.4      | Error-Correcting Codes                                              | 11 |  |  |  |  |  |  |

| 2.       | 4.1 Linear Codes                                                    | 11 |  |  |  |  |  |  |

| 2.       | 4.2 The Hamming Metric                                              | 13 |  |  |  |  |  |  |

| 2.       | 4.3 The Lee Metric                                                  | 15 |  |  |  |  |  |  |

| 2.       | 4.4 Decoding of Linear Codes                                        | 15 |  |  |  |  |  |  |

| 3. Faul  | lt-Tolerance in Logic Circuits                                      | 18 |  |  |  |  |  |  |

| 3.1      | Faults in Digital Systems                                           | 18 |  |  |  |  |  |  |

| 3.2      | Fault-Tolerance Strategies                                          | 19 |  |  |  |  |  |  |

| 3.3      |                                                                     |    |  |  |  |  |  |  |

| 3.4      | Self-Checking Circuits                                              | 22 |  |  |  |  |  |  |

| 3.5      | The $(N, K)$ Concept                                                | 23 |  |  |  |  |  |  |

| 3.6      | Low-Density Parity-Check Codes                                      | 24 |  |  |  |  |  |  |

| 4. Erro  | or-Correcting Decision Diagrams                                     | 26 |  |  |  |  |  |  |

| 4.1      | Introduction to Error-Correcting Decision Diagrams                  | 26 |  |  |  |  |  |  |

| 4.2      | Formal Definition of Error-Correcting Decision Diagrams             | 29 |  |  |  |  |  |  |

| 4.3      | Constructing Error-Correcting Decision Diagrams                     | 29 |  |  |  |  |  |  |

| 4.4      | 1                                                                   | 31 |  |  |  |  |  |  |

| 4.       | 4.1 Binary $(5,2)$ Code                                             | 31 |  |  |  |  |  |  |

| 4.       | 4.2 Hamming $(7,4)$ Code $\ldots$                                   | 33 |  |  |  |  |  |  |

| 4.       | 4.3 Shortened Hamming Code                                          | 34 |  |  |  |  |  |  |

| 4.       | 4.4 Ternary Hamming $(4,2)$ Code $\ldots$                           | 37 |  |  |  |  |  |  |

| 4.       | 4.5 Repetition Codes                                                | 38 |  |  |  |  |  |  |

| 4.       | 4.6 One-Lee-Error-Correcting Code for $q = 5$                       | 40 |  |  |  |  |  |  |

| 5. Faul  | lt-Tolerance Analysis of Error-Correcting Decision Diagrams         | 42 |  |  |  |  |  |  |

| 5.1      | The Probability Model for Diagrams based on Codes in the Hamming    |    |  |  |  |  |  |  |

|          | Metric                                                              | 43 |  |  |  |  |  |  |

| 5.2      | The Probability Model for Diagrams based on Codes in the Lee Metric | 45 |  |  |  |  |  |  |

| 5.3      | 5.3 Results of the Fault-Tolerance Analysis                         |    |  |  |  |  |  |  |

| 5.4      | 5.4 Approximating the Probability of Correct Outputs                |    |  |  |  |  |  |  |

| 6. Discussion                                          | 6 |

|--------------------------------------------------------|---|

| 6.1 Discussion on Error-Correcting Decision Diagrams 5 | 6 |

| 6.2 Discussion on the Fault-Tolerance Analysis         | 7 |

| 7. Conclusions                                         | 0 |

| References                                             | 1 |

# ABBREVIATIONS AND NOTATION

| $\oplus$                      | Logical exclusive OR.                                                     |  |  |  |

|-------------------------------|---------------------------------------------------------------------------|--|--|--|

| с                             | A codeword.                                                               |  |  |  |

| $d_H(\mathbf{x},\mathbf{y})$  | The Hamming distance between the vectors $\mathbf{x}$ and $\mathbf{y}$ .  |  |  |  |

| $d_L(\mathbf{x}, \mathbf{y})$ | The Lee distance between the vectors $\mathbf{x}$ and $\mathbf{y}$ .      |  |  |  |

| e                             | The number of errors a code corrects.                                     |  |  |  |

| $\mathbb{F}_q$                | The finite field of $q$ elements.                                         |  |  |  |

| $\mathbb{F}_q^i$              | The vector space of length $i$ vectors over $\mathbb{F}_q$ .              |  |  |  |

| G                             | A generator matrix of a linear code.                                      |  |  |  |

| Н                             | A parity check matrix of a linear code.                                   |  |  |  |

| $\mathbf{I}_i$                | The identity matrix of size $i \times i$ .                                |  |  |  |

| k                             | The number of inputs of a function; the dimension of a linear code,       |  |  |  |

|                               | which equals the number of inputs of a non-robust function.               |  |  |  |

| K                             | The number of repeated memory elements.                                   |  |  |  |

| l                             | The number of outputs of a function.                                      |  |  |  |

| L                             | The number of subsets of $\{1, 2, \ldots, M\}$ .                          |  |  |  |

| $\mu_i$                       | A random variable.                                                        |  |  |  |

| M                             | The number of non-terminal nodes in a decision diagram.                   |  |  |  |

| n                             | The length of a code, which for robust diagrams equals the number of      |  |  |  |

|                               | variables.                                                                |  |  |  |

| N                             | The number of repeated modules (processors in the $(N, K)$ concept).      |  |  |  |

| p                             | The probability that a decision node is faulty.                           |  |  |  |

| $P_i$                         | A subset of the set $\{1, 2, \ldots, M\}$ .                               |  |  |  |

| q                             | The size of the domain and range of a $q$ -ary function, i.e., the number |  |  |  |

|                               | of elements in the finite field $\mathbb{F}_q$ .                          |  |  |  |

| ρ                             | A binary relation.                                                        |  |  |  |

| r                             | The number of repetitions in a repetition code.                           |  |  |  |

| S                             | The syndrome of a word $\mathbf{v} \in \mathbb{F}_q^n$ .                  |  |  |  |

| au                            | The covering radius of a code.                                            |  |  |  |

| $w_H$                         | The Hamming weight of a vector.                                           |  |  |  |

| $w_L$                         | The Lee weight of a vector.                                               |  |  |  |

| BDD                           | Binary decision diagram.                                                  |  |  |  |

| BDT                           | Binary decision tree.                                                     |  |  |  |

| DNF                           | Disjunctive normal form.                                                  |  |  |  |

| ECC                           | Error-correcting code.                                                    |  |  |  |

| LDPC<br>MTPDD                 | Low-density parity-check (code).                                          |  |  |  |

| MTBDD                         | Multi-terminal binary decision diagram.                                   |  |  |  |

- MTDD Multi-terminal decision diagram.

- **NMR** *N*-modular redundancy.

- **OBDD** Ordered binary decision diagram.

- **PLA** Programmable logic array.

- **TMR** Triple modular redundancy.

- **TSC** Totally self-checking (circuit).

## 1. INTRODUCTION

The role of digital systems in modern life is increasingly important, and often these systems handle critical information and their accurate performance is essential for a given application. This high dependability is required, for example, in military and aerospace computing. In addition to these areas where the demands are extremely high, in most applications high dependability makes the products more competitive as their digital circuits perform their designed functions with a lower error rate. In modern logic circuits, the transistors are shrinking, which means that even atomicscale imperfections in each transistor can have a negative effect on the performance of these circuits. Therefore, in addition to existing techniques against failures in digital systems, it is important to develop new techniques for detecting and, in particular, correcting errors resulting from different types of faults in digital circuits.

Due to the importance of fault-tolerance in digital systems, numerous techniques have been developed against hardware failures. The most well-known such technique is triple modular redundancy, for which the groundwork was laid by von Neumann in [35]. It is a technique, which introduces redundancy to logic circuits by module triplication. Several authors have later further analyzed and developed this technique (see, for instance, [2], [17]).

Error-correcting codes have many useful properties and they are most typically used in data transmission to detect and correct errors on noisy communication channels [34]. With error-correcting codes, error detection and correction in logic circuits can often be implemented with less redundancy than when using other methods [26]. The properties of error-correcting codes are widely studied, and the highly developed theory behind them makes them a fruitful basis for new error detection and correction schemes. Coding theory has been exploited in several techniques for providing fault-tolerance in logic circuits, usually by introducing special circuits into logic modules, which handle the detection and correction of possible errors [26].

Since error correction in logic circuits is increasingly important, it is essential to find systematic ways to increase fault-tolerance already in the representations of switching functions, i.e., functions realized by the circuits. The method for providing fault-tolerance introduced in this thesis combines the theory of error-correcting codes and decision diagrams to obtain robust representations for functions, which are easily implemented with the suitable technology. The main advantage of using decision

#### 1. Introduction

diagrams for representing switching functions is that the layout and complexity of a circuit is directly determined by the decision diagram. The idea is to create error-correcting decision diagrams, i.e., a way of representing switching functions in a robust manner that can directly be mapped to technology. The purpose of the thesis is to introduce this original concept and provide fault-tolerance analysis for the obtained decision diagrams. The idea of combining error-correcting codes and decision diagrams introduced in this thesis has also resulted in two conference papers [4], [5], where error-correcting decision diagrams and their performance is discussed.

The thesis is structured as follows. In Chapter 2, the mathematical background for the topics discussed in this thesis is reviewed. This includes the definitions for decision diagrams and the theory of error-correcting codes, as well as some basic concepts related to discrete functions and their representations. Fault-tolerance in digital systems is explained in more detail in Chapter 3, where also existing error correction and detection schemes, in particular those utilizing coding theory, are discussed.

In Chapter 4, an original technique, namely error-correcting decision diagrams, for providing fault-tolerance in logic circuits is presented for binary and multiplevalued logic. The performance of this technique is analyzed in Chapter 5, where the probabilities for correct outputs in such constructions are determined. Since determining exact probabilities for larger configurations is very time-consuming, a method of approximating these probabilities is also introduced. Further discussion based on the analysis is included in Chapter 6.

## 2. MATHEMATICAL BACKGROUND

In this chapter, the mathematical background for the topics in this thesis is provided. Since digital circuits realize discrete functions, we begin by defining discrete functions. Then, decision diagrams are introduced as representations of discrete functions. The fault-tolerant circuit designs introduced in this thesis are derived using the theory of error-correcting codes, which are explained in the final section of this chapter. However, before moving on to the theory of error-correcting codes, some basic definitions regarding fields and vector spaces are provided for a better understanding of the theory.

#### 2.1 Discrete Functions

The functions discussed in this thesis belong to the class of discrete functions, which can be defined in the following way [6]:

**Definition 2.1** Let A and B be sets. Let  $\rho$  be a binary relation from A to B. If for every element  $a \in A$  there exists a unique element in  $b \in B$  such that  $(a, b) \in \rho$ , then  $\rho$  is a function from A to B, which is denoted by  $\rho : A \to B$ . If A and B are finite, then  $\rho$  is a discrete function.

The applications in this thesis concern discrete functions on finite sets, i.e., functions for which the domain A and range B are finite. A function f of k variables (inputs) is denoted as  $f(x_0, x_1, \ldots, x_{k-1}), x_i \in A, f(x_0, x_1, \ldots, x_{k-1}) \in B$ , and a multi-output function is defined as:

**Definition 2.2** Let A and B be finite sets,  $k \ge 0$ ,  $l \ge 0$  and  $f : A^k \to B^l$  a function. Then f is a multi-output function.

Thus, a multi-output function is equivalent to a system of single-output functions  $f = (f_0, f_1, \ldots, f_{l-1}).$

The most commonly used functions in digital logic are switching (Boolean) functions, i.e., functions  $f : \{0,1\}^k \to \{0,1\}$ , which describe the behavior of binary logic circuits. Logic systems with multiple inputs or outputs are represented by multioutput switching functions that are functions of the form  $f : \{0,1\}^k \to \{0,1\}^l$ .

Multiple-valued functions are functions with a domain  $A^k$  and range  $B^l$ , where |A| = |B| = q > 2. For example, ternary functions are a class of functions of the

form  $f: \{0, 1, 2\}^k \to \{0, 1, 2\}^l$ . Hence, for ternary functions, q = 3. Functions with q = 4 are called quaternary functions. Generally, a function with a domain having q values is a q-ary function. Notice that in this thesis we only refer to q-ary functions, where q is the number of elements of the finite field  $\mathbb{F}_q$  (see, Section 2.3), but in general, q can be any integer, which is larger than 2.

There exist several methods of representing discrete functions, e.g. truth-tables, algebraic expressions, and graphic representations. Decision diagrams are a graphic method of representing discrete functions, and they are explained in detail in Section 2.2. For understanding decision diagrams, certain representations and expressions of logic functions are explained here.

Consider a switching function  $f(x_0, x_1, x_2) : \{0, 1\}^3 \to \{0, 1\}$ . This function can be given by listing its values as  $(x_0, x_1, x_2)$  run through the values of the domain  $\{0, 1\}^3$ . For a binary switching function, listing these values into a tabular form is called a truth table (Table 2.1). The function  $f_1 = f(x_0, x_1, x_2)$  may also be represented by a vector of the function values, which in case of switching functions is called a truth-vector. The truth-vector of the switching function  $f_1$  defined in Table 2.1 is  $\mathbf{F}_1 = [0, 1, 1, 1, 0, 1, 0, 1]^T$ . When representing switching functions with truth-vectors, the ordering of the  $2^k$  binary input sequences should be specified. Unless otherwise stated, we use lexicographic ordering as in Table 2.1.

| $x_0x_1x_2$ | $f_1(x_0, x_1, x_2)$ |

|-------------|----------------------|

| 000         | 0                    |

| 001         | 1                    |

| 010         | 1                    |

| 011         | 1                    |

| 100         | 0                    |

| 101         | 1                    |

| 110         | 0                    |

| 111         | 1                    |

Table 2.1: The truth-table of a binary switching function  $f_1$ .

Switching functions can also be represented as a formula written in terms of some operations over an algebraic structure. For these representations, some basic definitions must be introduced. The following definitions are given for switching functions but can directly be generalized to q-ary functions [6].

A two-valued variable  $x_i$  may be written in terms of a positive literal  $x_i$  or a negative literal  $\bar{x}_i$ . A positive literal is just an atom, which is a logical formula containing no subformulas, and a negative literal is the negation of an atom [29]. Denote by  $\cdot$  the logical AND operation corresponding to a product of variables and by + the logical OR operation corresponding to a sum of variables. Any switching

#### 2. Mathematical Background

function can be written with literals and operations  $\cdot$  and +.

For example, we can represent the function  $f_1$  in Table 2.1 as a canonical sum of products, i.e., in the complete disjunctive normal form (DNF), which corresponds to the lines on the table where f has the value 1 ( $\cdot$  omitted):

$$f_1 = \bar{x}_0 \bar{x}_1 x_2 + \bar{x}_0 x_1 \bar{x}_2 + \bar{x}_0 x_1 x_2 + x_0 \bar{x}_1 x_2 + x_0 x_1 x_2, \tag{2.1}$$

or equivalently in a more compact DNF as

$$f_1 = x_2 + \bar{x}_0 x_1. \tag{2.2}$$

The expression in (2.2) is not canonical and can be derived from the sum of the two functions  $f_2 = x_2$  and  $f_3 = \bar{x}_0 x_1$  as shown in Table 2.2.

| $x_0 x_1 x_2$ | $f_2$ |   | $x_0 x_1 x_2$ | $f_3$ |   | $x_0 x_1 x_2$ | $f_1$ |

|---------------|-------|---|---------------|-------|---|---------------|-------|

| 000           | 0     |   | 000           | 0     |   | 000           | 0     |

| 001           | 1     |   | 001           | 0     |   | 001           | 1     |

| 010           | 0     |   | 010           | 1     |   | 010           | 1     |

| 011           | 1     | + | 011           | 1     | = | 011           | 1     |

| 100           | 0     |   | 100           | 0     |   | 100           | 0     |

| 101           | 1     |   | 101           | 0     |   | 101           | 1     |

| 110           | 0     |   | 110           | 0     |   | 110           | 0     |

| 111           | 1     |   | 111           | 0     |   | 111           | 1     |

Table 2.2: The representation of  $f_1$  as the sum of  $f_2$  and  $f_3$ .

### 2.2 Decision Diagrams

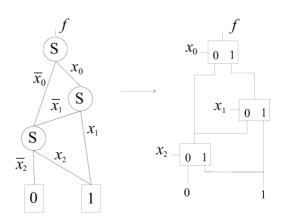

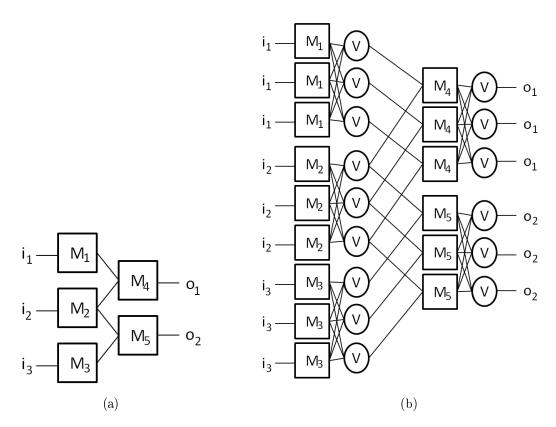

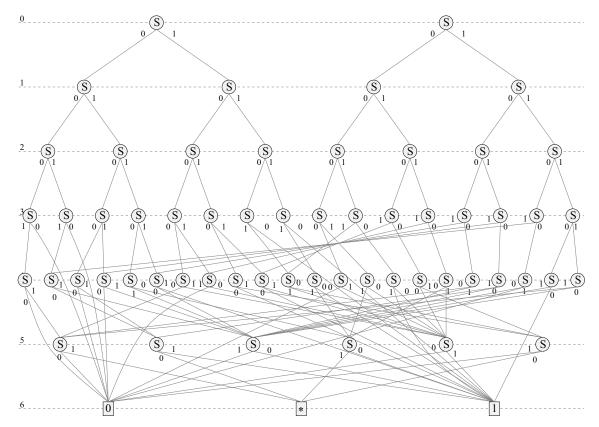

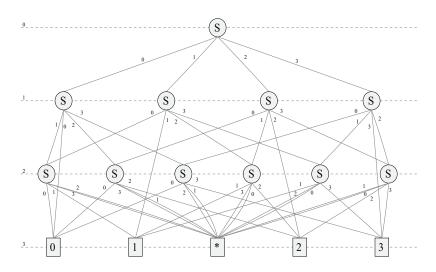

Decision diagrams are an effective way of representing discrete functions graphically. The idea of representing switching circuits using reduced binary decision diagrams (BDDs) was formalized by Bryant in [9], and the topic has been further explored by numerous authors. Binary decision diagrams have many applications in logic design, e.g., in logic circuit minimization [3] and probabilistic analysis of digital circuits [33]. Decision diagrams can also be used for representing other discrete functions than binary switching functions, namely multiple-valued functions. An important feature of decision diagrams is that they are easily mapped to technology. For example, depending on the technology, the number of gates in the circuit directly relates to the number of nodes in the decision diagram and the delay of the circuit is related to path lengths. In Figure 2.1 is an example of the correspondence of a binary decision diagram to a circuit layout, where the circuit is constructed using multiplexers. More on circuit realization can be found in, for example, [28].

#### 2. Mathematical Background

Figure 2.1: Correspondence between BDDs and networks of multiplexers [6].

In this section, the definitions of binary decision diagrams, multiple-valued, i.e., q-ary decision diagrams, multi-terminal decision diagrams (MTDDs) and shared decision diagrams are given. The definitions and basic concepts and properties related to decision diagrams are given according to [6], [23].

#### 2.2.1 Binary Decision Diagrams

Binary decision diagrams are used to represent switching functions, i.e., functions of the form  $f : \{0, 1\}^k \to \{0, 1\}$ . We define binary decision diagrams using binary decision trees, which are graphic representations of functions in the complete DNF.

**Definition 2.3** A binary decision tree (BDT) is a rooted directed graph having k+1 levels with two different types of vertices. On level *i*, where i = 0, ..., k-1, are the non-terminal nodes, each having two outgoing edges labeled by 0 and 1 or by corresponding literals  $\bar{x}_i$  and  $x_i$ . On level *k* are the terminal nodes having the label 0 or 1 and no outgoing edges.

A BDT has a direct correspondence to the truth-table of a function. Let  $f(x_0, x_1, \ldots, x_{k-1})$  be a switching function. In the binary decision tree of f, each node on level i corresponds to a specific variable  $x_i$ , and by following the edges the value of the function at  $(x_0, x_1, \ldots, x_{k-1})$  is found in the terminal node. Figure 2.2 shows a BDT representing the function  $f_1$  defined in Table 2.1.

**Definition 2.4** A binary decision diagram is a rooted directed graph obtained from a binary decision tree by the following reduction rules:

- 1. If two sub-graphs represent the same function, delete one, and connect the edge pointing to its root to the remaining subgraph.

- 2. If both edges of a node point to the same sub-graph, delete that node, and directly connect its incoming edge to the sub-graph.

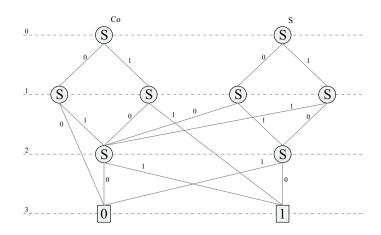

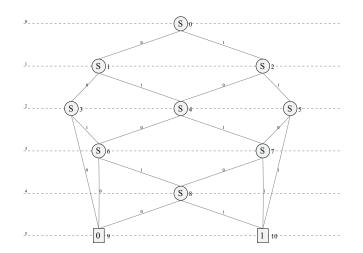

Figure 2.2: A BDT for the function  $f_1$  in Table 2.1.

In Figure 2.3 is a BDD representing the function  $f_1$  defined in Table 2.1.

Figure 2.3: A BDD for the function  $f_1$  in Table 2.1.

The letter  $\mathbf{S}$  in the nodes means that the nodes in the diagrams are Shannon nodes, i.e., the decision diagram is a graphic representation of the Shannon expansion of the function, which is defined as follows.

**Definition 2.5** The Shannon expansion of the switching function  $f(x_0, x_1, \ldots, x_{k-1})$ with respect to the variable  $x_i$  is  $f = \overline{x}_i f_0 \oplus x_i f_1$ , where  $f_0 = f(x_0, \ldots, x_{i-1}, 0, x_{i+1}, \ldots, x_{k-1})$  and  $f_1 = f(x_0, \ldots, x_{i-1}, 1, x_{i+1}, \ldots, x_{k-1})$ , and  $\oplus$  denotes the logical Exclusive OR.

As in most literature, when discussing BDDs, we refer to ordered binary decision diagrams (OBDDs), where the variable  $x_i$  corresponds to the level *i* of the decision

tree. In [9], it has been shown that the OBDD of a given function is canonical, i.e., for a given ordering, the OBDD of a given function is unique up to function graph isomorphism, for which the definition was given by Bryant in [9]. Several important consequences follow from the uniqueness of OBDDs, for example, equivalence of functions can easily be tested using OBDDs. The property of the representation of functions as BDDs being canonical means, that when we reduce the BDT of a function with a given variable ordering into a BDD, the operations of reduction cannot be made in such a way or order, that two non-isomorphic BDDs could be obtained starting from the same BDT.

#### 2.2.2 Multiple-Valued Decision Diagrams

The definition of a BDD is easily extended to the q-ary case for representing functions with a larger than two-valued domain. Again, we define the decision diagram using the definition of a decision tree.

**Definition 2.6** A q-ary decision tree is a rooted directed graph having k + 1 levels with two different types of vertices. On level i, where i = 0, ..., k - 1 are the nonterminal nodes, each having q outgoing edges with labels from the set  $\{0, 1, ..., q-1\}$ or the set of q-ary literals  $X_i^0, X_i^1, ..., X_i^{q-1}$ . On level k are the terminal nodes, which have labels from the set  $\{0, 1, ..., q-1\}$  and no outgoing edges.

**Definition 2.7** A q-ary decision diagram is a rooted directed graph obtained from a q-ary decision tree by the reduction rules in Definition 2.4.

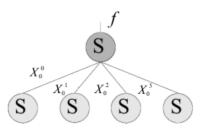

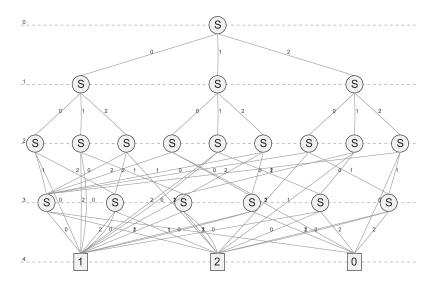

In Figure 2.4 is an example of the structure of nodes in a q-ary decision diagram when q = 4.

Figure 2.4: The node structure in a quaternary decision diagram.

In the case of a *q*-ary function  $f(x_0, x_1, \ldots, x_{k-1})$ , the Shannon expansion of f with respect to the variable  $x_i$  is  $f(x_0, x_1, \ldots, x_{k-1}) = X_i^0 f(x_0, x_1, \ldots, x_{i-1}, 0, x_{i+1}, \ldots, x_{k-1}) + X_i^1 f(x_0, x_1, \ldots, x_{i-1}, 1, x_{i+1}, \ldots, x_{k-1}) + \cdots + X_i^{q-1} f(x_0, x_1, \ldots, x_{i-1}, q-1, x_{i+1}, \ldots, x_{k-1})$ [30].

#### 2.2.3 Multi-terminal and Shared Decision Diagrams

The number of terminal nodes in decision diagrams is not necessarily limited to q nodes. Such decision diagrams are called multi-terminal decision diagrams and are used to represent functions with a range having more than q elements. The only difference between a decision diagram and a MTDD is the number of terminal nodes. For example, a multi-terminal binary decision diagram (MTBDD) is a BDD having more than two terminal nodes. In other words, a MTBDD represents a function  $f : \{0,1\}^k \to B$ , where B has more than two elements. The construction of a MTDD or MTBDD can be derived from decision trees similarly as described for BDDs and q-ary decision diagrams.

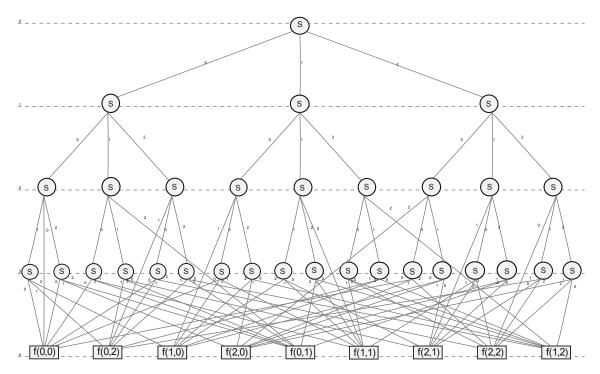

MTDDs and shared decision diagrams are useful when dealing with multi-output functions or systems of functions, where terminal nodes are labeled by the values that the system can get. For example, for switching functions, the binary *l*-tuples of the outputs are interpreted as binary representations of the corresponding integers and terminal values are labeled by these integer values. Shared decision diagrams are constructed by first constructing the decision diagrams for the different outputs, and then sharing the isomorphic subgraphs of the obtained decision diagrams.

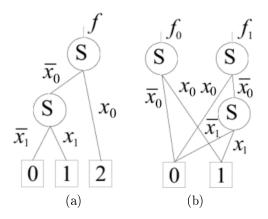

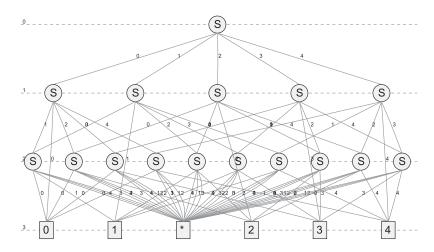

In Figures 2.5a and 2.5b are examples of a MTBDD and a shared BDD. Both diagrams represent a two-output function  $f = (f_0, f_1)$  where  $f_0 = x_0$  and  $f_1 = \bar{x}_0 x_1$ . In the MTBDD, the output values are interpreted as the corresponding integers. For example, with the input (0, 1), the output values are  $f_0 = 0$  and  $f_1 = 1$ , which in the MTBBD is interpreted as the binary representation 01, which corresponds to the integer value 1.

Figure 2.5: A MTBDD (a) and a shared binary decision diagram (b) [6].

### 2.3 Fields and Vector Spaces

Linear error-correcting codes are defined as subspaces of vector spaces over fields. Therefore, some basic concepts related to fields and vector spaces must be provided here. The following definitions and properties are given according to [13], [20].

A field is defined using the definition of a group, which can be stated as:

**Definition 2.8** A group (G, \*) is a set G together with a binary operation \* on G, such that the following properties for G and \* are satisfied:

- 1. The set G is closed under the operation \*, i.e., for  $a, b \in G$  the result of the operation a \* b is also in G.

- 2. The operation \* is associative, i.e., (a \* b) \* c = a \* (b \* c).

- 3. There is an element  $e \in G$  such that e \* a = a \* e = a for all  $a \in G$ . The element e is called the identity element of G.

- 4. For each  $a \in G$  there is an element  $a' \in G$  such that a \* a' = a' \* a = e. The element a' is called the inverse of a.

The group G is called Abelian if commutativity, i.e., a\*b = b\*a holds for all  $a, b \in G$ . The identity element (neutral element) of an Abelian group is usually denoted by 0. A subset H of the set G is a subgroup if it also forms a group under the operation \*.

**Definition 2.9** If (G, \*) is a group, g an element of G, and H a subgroup of G, then  $gH = \{g * h : h \in H\}$  is a left coset of H in G and  $Hg = \{h * g : h \in H\}$  is a right coset of H in G.

Cosets appear in the decoding process of linear codes. For Abelian groups, the left and right cosets coincide.

**Definition 2.10** A field is a set  $\mathbb{F}$  together with two operations, "+" and ".", such that the set is an Abelian group under the operation "+", the nonzero elements of the set form an Abelian group under the operation "." and the distributive law  $a \cdot (b+c) = a \cdot b + a \cdot c$  holds.

The multiplicative identity element (the identity element of the Abelian group under " $\cdot$ ") of a field is called the unit element and it is usually denoted by 1.

**Definition 2.11** Let  $\mathbb{F}$  be a field. A vector space V over the field  $\mathbb{F}$  is an additive Abelian group, together with the association

$$(x,v) \to xv,$$

where  $x \in \mathbb{F}$  and  $v \in V$ , satisfying:

1. If 1 is the unit element of  $\mathbb{F}$ , then 1v = v for all  $v \in V$ .

- 2. If  $c \in \mathbb{F}$  and  $v, w \in V$ , then c(v+w) = cv + cw.

- 3. If  $x, y \in \mathbb{F}$  and  $v \in V$ , then (x + y)v = xv + yv.

- 4. If  $x, y \in \mathbb{F}$  and  $v \in V$ , then (xy)v = x(yv).

**Definition 2.12** A subset W of V is a subspace of V if the following conditions are satisfied:

- 1. If  $v, w \in W$ , their sum v + w is also an element of W.

- 2. The identity element 0 of V is an element of W.

- 3. If  $v \in W$  and  $c \in \mathbb{F}$ , then  $cv \in W$ .

We denote a field of q elements by  $\mathbb{F}_q$  and the vector space of length i vectors over this field by  $\mathbb{F}_q^i$ . For vectors  $\mathbf{x} \in \mathbb{F}_q^i$  we take the convention of them being column vectors, hence, a vector  $\mathbf{x}^T$  is always a row vector.

#### 2.4 Error-Correcting Codes

Error-correcting codes are typically used for reliable delivery of digital information over communication channels, which may introduce errors to the transmitted message due to channel noise. Error-correcting codes add redundancy to messages, which enable error detection and correction at the receiver. The theory of errorcorrecting codes is in general a deep topic and many algorithms for the encoding and decoding processes have been developed for particular code classes. However, in principle for linear error-correcting codes with short codelengths, encoding and decoding can be done using simple matrix and lookup operations, so their implementation is easy.

In the following, we define and discuss important properties of error-correcting codes. Some example codes are also given, but mostly the codes considered for particular applications will be introduced later in the thesis as the corresponding applications are discussed.

#### 2.4.1 Linear Codes

In this section we recall basic definitions and properties of error-correcting codes, focusing on linear codes, i.e., linear subspaces of  $\mathbb{F}_q^n$ . The error-correcting properties of a code are defined over the metric, which is used for the given code, and for the purposes of this thesis we consider linear codes over the Hamming metric and the Lee metric. For general properties of error-correcting codes we refer to [7], [21], [34].

**Definition 2.13** A code C is a subset of  $\mathbb{F}_q^n$ . C is called a linear code if C is a linear subspace of  $\mathbb{F}_q^n$ .

The elements of C are length n vectors, which are called codewords. A linear code C of dimension  $k \leq n$  is spanned by k linearly independent vectors of C, i.e., every codeword can be written as a linear combination of these k linearly independent vectors.

**Definition 2.14** A matrix **G** having as rows any k linearly independent vectors of C is called a generator matrix of the code C.

If the code has length n and dimension k it is called an (n, k) code.

Define that two column vectors  $\mathbf{x}$  and  $\mathbf{y}$  are orthogonal if  $\mathbf{x}^T \mathbf{y} = 0$ . The code C of length n and dimension k can equivalently be specified by listing n - k linearly independent vectors of  $C^{\perp}$ , where  $C^{\perp}$  is the subset of  $\mathbb{F}_q^n$  consisting of all vectors orthogonal to all vectors of C. Any matrix  $\mathbf{H}$  having as rows such n - k linearly independent vectors is called a parity check matrix of C.

**Definition 2.15** Two codes are equivalent if and only if their generator matrices are obtained from each other by column permutations and elementary row operations.

Since the rows of the generator matrix are linearly independent and span the linear code, i.e., linear subspace of  $\mathbb{F}_q^n$ , elementary row operations leave the space unchanged. The permutation of columns corresponds to permutation of symbols in the codewords. When these operations are performed for the generator matrix **G** of the code C, the resulting code will be only trivially different from C.

A generator matrix  $\mathbf{G}$  of the code C is in systematic form if

$$\mathbf{G} = [\mathbf{I}_k | \mathbf{P}]$$

$$= \begin{bmatrix} 1 & 0 & 0 & \cdots & 0 \\ 0 & 1 & 0 & \cdots & 0 \\ \vdots & \vdots & \vdots & \ddots & \vdots \\ 0 & 0 & 0 & \cdots & 1 & p_{k,1} & p_{k,2} & \cdots & p_{k,n-k} \end{bmatrix},$$

where  $\mathbf{P}$  is called the parity part of the generator matrix. Any generator matrix of C can be put into this form by column permutations and elementary row operations. The resulting generator matrix defines a systematic code, which is equivalent to C. Also, if the generator matrix of C is  $\mathbf{G} = [\mathbf{I}_k | \mathbf{P}]$ , it is clear that the parity check matrix  $\mathbf{H}$  is of the form  $[-\mathbf{P}^T | \mathbf{I}_{n-k}]$ , since

$$\mathbf{G}\mathbf{H}^T = [\mathbf{I}_k \ \mathbf{P}] \left[ egin{array}{c} -\mathbf{P} \ \mathbf{I}_{n-k} \end{array}

ight] = -\mathbf{P} + \mathbf{P} = \mathbf{0}.$$

#### 2. Mathematical Background

For binary codes, we may write **H** in the form  $[\mathbf{P}^T | \mathbf{I}_{n-k}]$ .

The code *C* encodes an information word  $\mathbf{i} = [i_0, i_1, \dots, i_{k-1}]^T$  to a length *n* codeword  $\mathbf{c} = [c_0, c_1, \dots, c_{n-1}]^T$  by matrix multiplication  $\mathbf{c}^T = \mathbf{i}^T \cdot \mathbf{G}$ . Thus, the code *C* can be defined as

$$C = \{\mathbf{i}^T \mathbf{G} \mid \mathbf{i} \in \mathbb{F}_q^k\}$$

and equivalently with the parity check matrix  $\mathbf{H}$  as

$$C = \{ \mathbf{c} \in \mathbb{F}_q^n \mid \mathbf{c}^T \mathbf{H}^T = 0 \}$$

For example, if we have the following generator matrix:

$$\mathbf{G} = \left[ \begin{array}{ccc|c} 1 & 0 & 1 & 1 & 0 \\ 0 & 1 & 1 & 0 & 1 \end{array} \right],$$

then the parity check matrix H for this code is:

$$\mathbf{H} = \begin{bmatrix} 1 & 1 & 1 & 0 & 0 \\ 1 & 0 & 0 & 1 & 0 \\ 0 & 1 & 0 & 0 & 1 \end{bmatrix},$$

and encoding the information word  $\mathbf{i} = [0, 1]^T$  we get the corresponding codeword  $\mathbf{i}^T \mathbf{G} = [0, 1] \cdot \begin{bmatrix} 1 & 0 & 1 & 1 & 0 \\ 0 & 1 & 1 & 0 & 1 \end{bmatrix} = [0, 1, 1, 0, 1]$ . Here k = 2 and n = 5.

#### 2.4.2 The Hamming Metric

The vector space  $\mathbb{F}_q^n$  can be made into a metric space by defining the distance between two vectors  $\mathbf{x}$  and  $\mathbf{y}$ . The Hamming metric is the most commonly used metric for defining this distance and the properties of the error-correcting code.

**Definition 2.16** The Hamming distance  $d_H(\mathbf{x}, \mathbf{y})$  of vectors  $\mathbf{x}$  and  $\mathbf{y}$  of length n is the number of coordinates where  $\mathbf{x}$  and  $\mathbf{y}$  differ, i.e.,  $d_H(\mathbf{x}, \mathbf{y}) = |\{i \mid x_i \neq y_i\}|$ .

Consider the vectors  $\mathbf{x} = [0, 1, 0, 0]^T$  and  $\mathbf{y} = [1, 1, 0, 0]^T \in \mathbb{F}_2^4$ . The vectors differ in the first entry, hence, the Hamming distance is  $d_H(\mathbf{x}, \mathbf{y}) = 1$ .

**Definition 2.17** The Hamming-weight  $w_H$  of a vector  $\mathbf{x}$  is  $w_H = d_H(\mathbf{0}, \mathbf{x})$ .

**Definition 2.18** A code C is e-error correcting if the minimum Hamming distance between two codewords is 2e + 1.

An e-error-correcting code can detect and correct up to e errors in the encoded information word. This means, that if the values of the encoded information word

$\mathbf{i}^T \mathbf{G}$  change in  $\leq e$  positions, the decoder of the code will be able to detect and correct the errors, i.e., interpret the received sequence as the correct information word.

**Definition 2.19** A code  $C \in \mathbb{F}_q^n$  is called a q-ary  $\tau$ -covering code of length n if for every word  $\mathbf{y} \in \mathbb{F}_q^n$  there is a codeword  $\mathbf{x} \in C$  such that the Hamming distance  $d_H(\mathbf{x}, \mathbf{y}) \leq \tau$ . The smallest such  $\tau$  is called the covering radius of the code.

In other words, the covering radius of the code is the smallest  $\tau$  such that the finite metric space  $\mathbf{F}_q^n$  is exhausted by spheres of radius  $\tau$  around the codewords.

**Definition 2.20** A code is called perfect if it is e-error correcting and its covering radius is e.

For a perfect code, the entire metric space is filled by the radius e spheres around the codewords, with no overlaps. This means, that every length n sequence can be traced back to a length k information word. However, if more than e errors occur, the interpretation will be incorrect.

An important example of perfect codes in the Hamming metric are the Hamming codes. Binary Hamming codes are a family of  $(2^m - 1, 2^m - m - 1)$  codes with parity check matrices consisting of all  $2^m - 1$  distinct non-zero *m*-tuples. Since all of the columns are distinct, no sum of two columns can be the zero vector, and hence the code has minimum distance of  $\geq 3$ . Therefore, Hamming codes are one error correcting. Hamming codes have the covering radius of one, hence they are perfect codes. This means that for each binary vector  $\mathbf{v}$  of length  $2^m - 1$  there is a unique codeword within distance 1 from  $\mathbf{v}$ .

For example, the parity check matrix  $\mathbf{H}$  of the binary (7,4) Hamming code can be constructed by listing all vectors of length 3 as columns:

$$\mathbf{H} = \begin{bmatrix} 1 & 1 & 1 & 0 & | & 1 & 0 & 0 \\ 1 & 1 & 0 & 1 & | & 0 & 1 & 0 \\ 1 & 0 & 1 & 1 & | & 0 & 0 & 1 \end{bmatrix}$$

Therefore, its generator matrix is

$$\mathbf{G} = \begin{bmatrix} 1 & 0 & 0 & 0 & | & 1 & 1 & 1 \\ 0 & 1 & 0 & 0 & | & 1 & 1 & 0 \\ 0 & 0 & 1 & 0 & | & 1 & 0 & 1 \\ 0 & 0 & 0 & 1 & | & 0 & 1 & 1 \end{bmatrix}$$

Hamming codes are easily defined for vector spaces  $\mathbb{F}_q^n$  having parameters  $(\frac{q^m-1}{q-1}, \frac{q^m-1}{q-1} - m)$ . For each m, there are  $(q^m - 1)$  different nonzero vectors, but since the

minimum distance of the code is  $\geq 3$ , the columns of the parity check matrix have to be pairwise linearly independent. Therefore, there are  $\frac{q^m-1}{q-1}$  distinct q-ary vectors that we can list as columns of the parity check matrix **H**.

#### 2.4.3 The Lee Metric

Another metric used for error-correcting codes is the Lee metric. Let us call a Lee-error-correcting code any error-correcting code defined for the Lee metric.

**Definition 2.21** The Lee distance  $d_L(\mathbf{x}, \mathbf{y})$  of q-ary vectors  $\mathbf{x}$  and  $\mathbf{y}$  of length n is the sum  $\sum_{i=1}^{n} \min(|x_i - y_i|, q - |x_i - y_i|)$ .

For example, for q = 5,

$$d_L(0,1) = 1$$

,  $d_L(0,2) = 2$ ,  $d_L(0,3) = 2$  and  $d_L(0,4) = 1$ .

And similarly for vectors  $\mathbf{x} = [2, 1, 3]^T$  and  $\mathbf{y} = [1, 1, 0]^T$ ,  $\mathbf{x}, \mathbf{y} \in \mathbb{F}_5^3$ , the Lee distance  $d_L(\mathbf{x}, \mathbf{y}) = 1 + 0 + 2 = 3$ .

Also,  $d_L(\mathbf{a} + \mathbf{k}, \mathbf{b} + \mathbf{k}) = d_L(\mathbf{a}, \mathbf{b})$ , i.e., like the Hamming metric, the Lee metric is translation invariant. Notice, that for q = 2 and q = 3, the Hamming and the Lee metric coincide.

**Definition 2.22** The Lee-weight  $w_L$  of a vector  $\mathbf{x}$  is  $w_L = d_L(\mathbf{0}, \mathbf{x})$ .

An *e*-Lee-error-correcting code will be able to detect and correct errors, which are at the Lee distance  $\leq e$  from the encoded sequence  $\mathbf{i}^T \mathbf{G}$ , i.e., have Lee-weight  $\leq e$ .

Perfect codes exist for the Lee metrics also. For example, for any given e, there exists a perfect e-Lee-error-correcting code with n = 2 over  $\mathbb{F}_q$  such that  $q = 2e^2 + 2e + 1$ .

#### 2.4.4 Decoding of Linear Codes

When error-correcting codes are used in communication, the underlying assumption is that a digit in a codeword has a small probability to change from one value to another during the transmission over a noisy channel. Thus the most likely original codeword is the one that is closest in the used metric to the received one. Hence the decoding is unique (though not necessarily correct) as long as there is a unique codeword closest to the received vector.

Consider the codewords of an *e*-error-correcting linear code **C**. Around each  $\mathbf{c} \in \mathbf{C}$  there is a sphere of radius *e* containing all the words at distance  $\leq e$  from  $\mathbf{c}$ , i.e., all the words that will be decoded into the word *c*. Hence, the decoding process

can be done by listing all the members of every sphere or more efficiently by using a structure called the standard array.

The standard array uses the coset decomposition of the additive group of  $\mathbb{F}_q^n$ . Since a linear code is a subspace of  $\mathbb{F}_q^n$ , it is a subgroup of the additive group of  $\mathbb{F}_q^n$  and hence the all-zero word is always a codeword. Thus each vector in the space belongs to exactly one coset of the code. The vectors with minimum weight (i.e., minimum distance from the all-zero codeword) are called coset leaders. It is clear that for an *e*-error correcting code, all vectors of weight at most *e* are coset leaders. This follows immediately from the fact that the difference of two vectors in the same coset belongs to the code. A moment of thought shows that if each coset has only one leader then for each element in the space there is a unique closest codeword. Choosing that closest codeword when decoding the received vector corresponds to maximum likelihood decoding [34].

The standard array in Table 2.3 is constructed as follows. Let  $\mathbf{0}, \mathbf{c}_2, \ldots, \mathbf{c}_{q^k}$  be the codewords of  $\mathbf{C}$ , which is a subspace of  $\mathbb{F}_q^n$ . Begin by listing these words on the first row of the standard array. Then, choose one unused word  $\mathbf{v}_1$  at distance  $\leq e$  from the all-zero word, i.e., a coset leader, and place it as the first entry of the second row. The rest of the words on the second row will be  $\mathbf{v}_1 + \mathbf{c}_2, \ldots, \mathbf{v}_1 + \mathbf{c}_{q^k}$ , i.e., the word  $\mathbf{v}_1$  translated by each of the codewords. These are the words belonging to the coset of  $\mathbf{v}_1$ . Then, choose again an unused word at distance  $\leq e$  from the all-zero codeword and translate it with each codeword to get the next row corresponding to the next coset. Repeat this until there are no unused coset leaders. If there are still unused words that do not appear in the standard array, draw a horizontal line across the array, and to obtain the next row of the array, choose a word  $\mathbf{v}_j$  by each of the codewords. Repeat this until there are no unused to set  $\mathbf{v}_j$  by each of the codewords. Repeat this until there are no unused to set  $\mathbf{v}_j$ .

Table 2.3: The standard array.

| 0                                                        | $\mathbf{c}_2$                                                 |   | $\mathbf{c}_{q^k}$                                                   |

|----------------------------------------------------------|----------------------------------------------------------------|---|----------------------------------------------------------------------|

| $\mathbf{v}_1$                                           | $\mathbf{v}_1 + \mathbf{c}_2$                                  |   | $\mathbf{v}_1 + \mathbf{c}_{q^k}$                                    |

| ÷                                                        | ÷                                                              | ÷ | ÷                                                                    |

|                                                          |                                                                |   |                                                                      |

| $\mathbf{v}_i$                                           | $\mathbf{v}_i + \mathbf{c}_2$                                  |   | $\mathbf{v}_i + \mathbf{c}_{q^k}$                                    |

| $egin{array}{c} \mathbf{v}_i \ \mathbf{v}_j \end{array}$ | $\mathbf{v}_i + \mathbf{c}_2$<br>$\mathbf{v}_j + \mathbf{c}_2$ |   | $rac{\mathbf{v}_i+\mathbf{c}_{q^k}}{\mathbf{v}_j+\mathbf{c}_{q^k}}$ |

In terms of the standard array, a decoder would assign a received word having at most e errors (i.e., appearing above the horizontal line), into the codeword, which lies above it in the standard array. Words below the horizontal line are either assigned

to a codeword similarly as the words at distance e from the codeword, or the decoder refuses to decode such a word indicating more than e errors in the received word. For perfect codes, there are no words under the horizontal line, since the spheres around the codewords fill the entire metric space.

The coset leaders can be used to construct a fast decoding strategy by introducing the syndrome **s** of a word  $\mathbf{v} \in \mathbb{F}_q^n$ , which is defined as  $\mathbf{s}^T = \mathbf{v}^T \mathbf{H}^T$ . It can be shown that all vectors in the same coset have the same syndrome, which is unique to that coset [34]. Hence, for efficient decoding, we only need to list the coset leaders and the syndromes. Then, for each received word, it is enough to compute the syndrome and find the corresponding coset leader. Subtracting the coset leader from the received word will correct the error.

## 3. FAULT-TOLERANCE IN LOGIC CIRCUITS

Fault-tolerance is an important topic in logic design and there exist several techniques for providing tolerance against hardware component failures. In some cases, for example in military and aerospace computing, fault-tolerance is critical, and it is often desirable in other applications. Even when using high-quality components and the best design techniques, system failures can still occur, and therefore techniques for providing fault-tolerance are necessary. The first ideas for fault-tolerant logic were given by von Neumann [35] and Shannon and Moore [24] already in the 1950s. In the work of Shannon and Moore it was shown that arbitrarily reliable circuits can be built from unreliable components when the number of these unreliable components is sufficiently large.

Failures in digital systems may be due to numerous reasons, and we begin by an overview of the most common types of faults that may result in errors. Next, the basic strategies for increasing fault-tolerance are discussed in Section 3.2. One of the most well-known techniques against hardware component failures is triple modular redundancy (TMR), which is explained in Section 3.3. The TMR technique has been studied and improvements have been presented in several papers. There exist also methods for increasing fault-tolerance, which utilize more complicated error-correcting codes, and some of these techniques are reviewed in Sections 3.4-3.6.

#### 3.1 Faults in Digital Systems

In digital systems, a system failure means that an element is unable to function due to errors in the element or in its environment, the errors being caused by various faults [26]. Faults are physical defects that can be caused by numerous reasons, e.g. design errors, damage or external disturbances. Faults are manifested by errors, thus a fault may change the value of the signal. A fault does not necessarily result in an error, which gives meaning for the term fault-tolerance. The purpose of faulttolerant design is to ensure that a system can perform its intended function even in the presence of a given number of faults.

Such faults, which change the value of the signal, e.g. from a 0 to a 1 or vice versa, are called logical faults [19]. Other types of faults are referred to as nonlogical, which include, for example, the malfunction of the clock signal or a power failure. Logical faults are the type of faults that are of interest for the fault-tolerance methods

discussed in this thesis, and they can be further characterized by their value, extent and duration [19]:

- 1. Value: Logical faults can cause fixed or varying erroneous logical values.

- 2. Extent: The effect of a logical fault can be local or distributed.

- 3. Duration: A logical fault can be either permanent or temporary.

Different types of faults are described by fault models. The most common model used for logical faults is the single stuck-at fault. A stuck-at-fault is a fault, in which one of the inputs or the output of a gate is fixed to some value, e.g. in switching circuits to a 0 or a 1 [19]. The stuck-at-fault model is used for modeling the most common types of physical defects in circuits, e.g. shorts, which may cause damage to the circuit due to very low resistance in the circuit, and opens, in which the path of the current gets broken. The stuck-at-model can also be used for representing multiple faults in a circuit, when there are multiple stuck-at-faults in the circuit at the same time.

When signal lines in a circuit get accidentally connected to each other, it results in a permanent fault called a bridging fault [19]. Bridging faults are connected to stuck-at-faults, since, depending on the technology, a bridging fault may manifest as a stuck-at-fault. It may also cause a circuit to oscillate. The bridging fault model is more applicable when the line widths are small.

A defect in a circuit may also be small enough not to alter the logic function, which the circuit realizes, but will only cause the circuit to fail to meet its timing specifications [19]. Such defects delay the transition of a signal on a line to the correct value, and are modeled by delay faults.

### 3.2 Fault-Tolerance Strategies

The foundation for fault-tolerance is in redundancy. Redundancy may be introduced to hardware, software, information and computations, and the amount of redundancy depends on the applied fault-tolerance technique. Fault-tolerance strategies include one or more of the following elements [26]:

- 1. Masking, i.e., dynamic correction of generated errors.

- 2. Detection of an error, i.e., a symptom of a fault.

- 3. Containment, which means the prevention of error propagation.

- 4. Diagnosis, i.e., identification of the faulty module.

- 5. Repair or reconfiguration of the faulty component by replacement, elimination or bypassing it.

6. Recovery, i.e., correction of the system to an acceptable state.

Masking, detection and correction are most important with respect to the topic of this thesis, and several fault-tolerance techniques carry out one or more of these three. Error detection, i.e., the ability to tell the incorrect values apart from the correct ones, is the easiest of these to implement. An example of an error detection scheme is simple parity checks in buses, memory and registers. Masking and correcting errors is more difficult, and often requires a lot of redundancy. This redundancy can be obtained, for example, by copying modules, which is the basic principle in TMR technique (Section 3.3).

Error-correcting codes are an effective way of obtaining redundancy, and they often require less redundancy than other error detection and correction schemes. Their theory is well developed and exploited in numerous applications. In logic circuits, error detection and correction is usually implemented in special decoding circuits [26]. The performance of the error-correcting scheme depends on the properties of the code, and better error-correction ability usually requires more redundancy and therefore, more physical space on circuits.

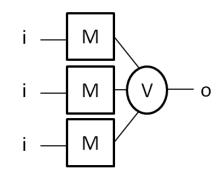

### 3.3 Triple Modular Redundancy

The TMR technique was first introduced by von Neumann in [35], where he proposed a configuration of independently computed copies of a signal and a restoring organ in between logical operations. The basic idea of the TMR technique is to triplicate the modules and then use a majority voter to decide the output of the whole system. This way, if one of the modules produces an incorrect output, the majority vote will still guarantee a correct output for the entire system. The TMR technique can be generalized to N-modular redundancy (NMR), where there are in total N modules and a voter, which decides the output based on the outputs of the modules.

The NMR technique can be described in terms of a (r, 1) repetition code, where r = N. Repetition code is the simplest linear code. In an (r, 1) binary repetition code a digit is encoded as a sequence of r repetitions of the digit itself, and the decoding is done by majority-vote decoding. For example, in the binary (3, 1) repetition code, which relates to the TMR technique, a 0 is encoded as the sequence 000, and if the decoder receives either 000, 001, 010 or 100, it decodes the sequence as a 0 by majority-vote decoding. Therefore, the (3, 1) repetition code is one error correcting.

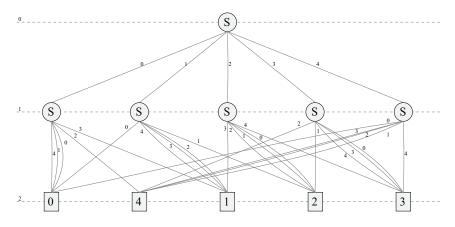

In the TMR technique, usually an entire module realizing some logical operation is encoded, i.e., triplicated, and a single voter is placed after the three modules (Figure 3.1) or, more typically, a voter is placed after each module. These voters together decode the output to a single output value. This output can be a symbol, i.e., a sequence of bits, and therefore the TMR network can correct single symbol errors. In Figure 3.2a is a network of modules and in Figure 3.2b is a typical TMR version of this network, where the circles correspond to voters. The inputs are  $i_1, i_2, i_3$  and outputs  $o_1, o_2$ .

Figure 3.1: The simplest TMR structure, with input i and output o.

Figure 3.2: A network of modules (a) and its TMR version (b) with three inputs  $i_1, i_2, i_3$  and two outputs  $o_1, o_2$ .

In a TMR computer architecture, a module consisting of a memory and a processor is triplicated, and a voter is added after each triplicated module. This allows correction of single symbol errors, but bit errors distributed over the modules cannot be corrected. In [17], an improvement for the TMR technique was proposed, where the memory part of the modules is organized in a bit-sliced way, i.e., from modules of smaller bit width, which increases the amount of hardware in the configuration, but can tolerate arbitrary bit-slice failures. It can also tolerate the failure of arbitrary bit-slices even if one of the modules is disabled. This idea of combined symbol- and bit-error-correcting in a computer architecture originates from the (N, K) concept, which is discussed in Section 3.5.

The TMR technique is the most widely used fault-tolerance technique. It has been used in highly critical applications, e.g. in space technique [11], as well as in some ECC memory, where ECC refers to error-correcting codes, although ECC memory more typically uses Hamming codes [14].

#### 3.4 Self-Checking Circuits

Self-checking circuits utilize the theory of error-correcting codes and have built-in error detection capability. They are multi-output circuits, which produce an output vector, from which the possible faults in the circuit can be detected. Formally, the output of a self-checking circuit is a vector  $\mathbf{Y}(\mathbf{X}, f)$  which is a function of the input vector  $\mathbf{X}$  and the fault f in the circuit [36]. The inputs and outputs are codewords, and the use of different error-correcting codes in these circuits has been studied by several authors. When no faults occur in a self-checking circuit, the output vector is a codeword, but a fault should result in a non-codeword output vector (detectable error). However, it may happen that faults in the circuit result in an incorrect codeword, in which case the fault will result in an undetectable error.

Self-checking circuits are divided to fault secure circuits, self-testing circuits or totally self-checking (TSC) circuits [26]. In fault secure circuits, a correct input codeword never causes an incorrect output codeword for a specified fault in the circuit, i.e., no undetectable errors for correct input codewords can occur. However, a fault might not result in a detectable error either. For self-testing circuits, if a fault occurs in the circuit, the output is a non-codeword for at least one input codeword. This means that if all input codewords occur in the operation of the circuit, a fault will be detected by at least one of these input codewords. TSC circuits have the properties of both self-testing and fault secure circuits, since a fault in the circuit, in principle, cannot cause an error in the outputs without detection of the fault [27]. Therefore, an incorrect input cannot result in a correct output and at least one correct input will detect possible faults in the circuit.

TSC circuits are the most important class of self-checking circuits, and the above properties guarantee that if the output is a codeword, it is safe to assume that it is correct, and on the other hand, if there is a fault in the circuit, it will be detected at some point. However, it may happen that faults are not detected in the order of their appearance [27]. This might be the case if the first fault is detectable only by a particular input codeword. Also, implementing the self-testing properties in an economical way has been problematic.

The basic implementation of a TSC network is introducing a TSC checker into the network [27]. The TSC checker is a circuit, which takes as inputs the outputs of the TSC network and is designed to detect errors in the error-correcting code used in the network. Hence, the TSC checker is an additional piece of hardware, which handles the error detection of the designed network. Possible faults can be detected from the outputs of the checker. However, there is no information on whether the fault occurred in the TSC network or in the checker.

### **3.5** The (N, K) Concept

The (N, K) concept was introduced by Krol in [18] as a new fault-tolerant computer architecture based on a distributed implementation of a symbol-error-correcting code. It is essentially a generalization of the TMR technique in which different coding schemes are applied to memory data and processor data. In a TMR computer architecture, both the memory data and the processor data are encoded using the (3, 1) repetition code, but with the (N, K) concept, the amount of additional memory hardware can be reduced. In [18], the concept was explained in more detail for the case where N = 4 and K = 2, in which the fault-tolerant computer architecture is designed using a specific symbol- and bit-error-correcting code. The term symbol refers to a sequence of bits, so within a faulty symbol, any number of bits can be incorrect.

The (N, K) concept makes it possible to choose a ratio between memory and processor redundancy and therefore makes it possible to optimize the total amount of redundancy. In [18], the TMR technique was described as the (3, 1) concept, where the computer architecture consists of three identical modules, each having memory, a processor and a voter. All data in the system is triplicated, and voters mask the possible failures in a single module. In the (N, K) concept, the processor data is similarly encoded into a (N, 1) symbol-error-correcting code, but the memory part is encoded into an (N, K) symbol-error-correcting code, where each of the N modules contains one symbol of the code word. However, the symbol size in the (N, K) code is K times smaller than the symbol size of the (N, 1) code, which means that less redundancy is introduced when using the (N, K) concept.

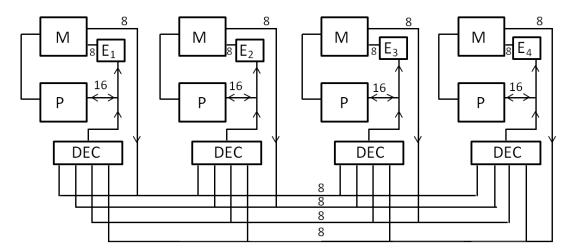

The concept is easier to understand by means of an example, e.g. the (4, 2) concept. In this case, the computer architecture consist of four modules, each having memory and a processor. The processors are identical in all modules, but the memory part of each module has a wordlength of half a data word, i.e., the memory in the (4, 2) concept is only doubled. The memory in each module is protected by a symbol- and bit-error-correcting code, which can correct single symbol errors and

double bit errors even if the bit errors occur in different modules. If symbol errors occur in more than one of the modules, the code can no longer correct the errors. In Figure 3.3 is the layout of the modules, in which the wordlengths in each line is written on the transfer lines. The boxes labeled  $E_1, E_2, E_3, E_4$  together form the encoder of the (4, 2) symbol-error-correcting code. This way, data is encoded when it is transmitted from the processors to the memories, but the encoding is distributed over the modules to reduce redundancy. When the data is transmitted from the memories to the processors, each module receives the complete codeword and the decoders mask the faulty symbols.

Figure 3.3: The layout of the (4, 2) concept fault-tolerant computer architecture.

Since the (N, K) concept discusses a complete fault-tolerant computer architecture, it is not as such applicable to circuit design. It is, in principle, a generalization of the TMR technique, which enables the usage of more complicated error-correcting codes and the choice in the ratio between the memory and processor redundancy. The advantage of the (N, K) concept compared to the TMR technique is the possibility of minimizing the total amount of hardware.

#### 3.6 Low-Density Parity-Check Codes

Low-density parity-check (LDPC) codes were introduced already in the 1960s by Gallager in [15], but they were rediscovered for applications in the 1990s. LDPC codes are a class of codes, which are specified by sparse matrices, i.e., matrices containing mostly zeros. They have been popular in many communication applications, since the encoding matrices have low density and decoding can be done iteratively in an easy manner. Here we briefly review some selected applications of LDPC codes in fault-tolerant logic, in which the use of LDPC codes is motivated by their high error detecting and correcting ability, and because the resulting encoding, decoding and checker circuits are sparse. In [10] and [16], LDPC codes are considered for error correction in fault-tolerant memory, and in [22] the application of LDPC codes in fault-tolerant finite field multipliers is introduced.

The application of LDPC codes in nanoscale ECC memory in [16] is interesting, since it considers modern nanoscale logic. A particular type of LDPC codes is used in the application, namely Euclidean Geometry LDPC codes, see [32], since the decoding process for these codes can be implemented with multistep majority decoders, thus making the decoding fast and giving low latency, i.e., time delay, for memory operations. In [16], the possibility of faults in the encoder and checker circuits is taken into account, since they are also fabricated out of nanoscale components, which are prone to faults. An efficient way of fabricating the encoder and decoder circuits using nanowire-based programmable logic arrays (PLAs) is proposed in [16], and the error detection and correction capacities of the resulting ECC nanomemories are analyzed.

In [10], LDPC codes are used for a fault-tolerant memory architecture. The motivation behind the application is again in the decrease of transistor sizes, which increases the unreliability of the components. In particular, the authors consider unreliable components, which are subject to transient errors, i.e., errors, which appear at particular time steps. The idea is to build a reliable memory entirely of unreliable components using LDPC codes. The existence of such reliable memories is proved in [10], and it is also shown that the resulting architecture will have fairly low redundancy.

The application of LDPC codes in [22] is motivated by fault related attacks in cryptographic hardware, which is used, for example, for digital signature and identification schemes. It has been shown that attackers can inject faults into the hardware causing incorrect outputs, which expose the digital signatures. Cryptography applications use finite field arithmetic, and in [22], a method for designing error-correcting multiplier circuits for finite fields is proposed, in which LDPC codes are used due to their reduced decoding complexity. The resulting applications are shown to have significantly less redundancy than the traditional TMR technique, but additional delay is introduced to the circuits due to encoding and decoding procedures.

# 4. ERROR-CORRECTING DECISION DIAGRAMS

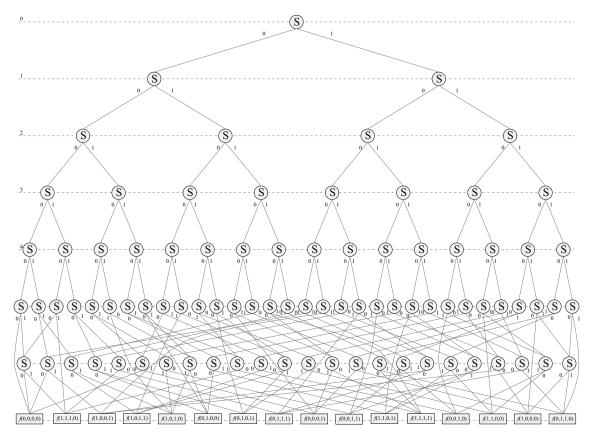

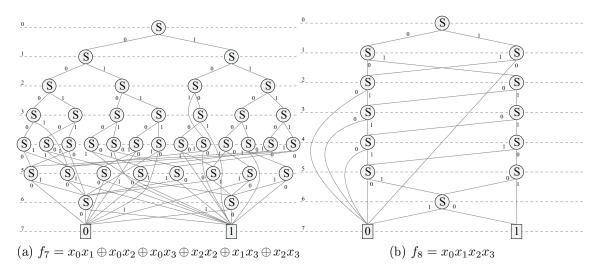

Many of the existing fault-tolerance techniques, e.g. the TMR technique (Section 3.3), are based on repetition of logic modules and additional checking circuitry. In modern logic circuits, transistors are becoming smaller and smaller, and even atomicscale imperfections and variations within each transistor can result in circuit failures. Therefore, in addition to testing and fault detection procedures, it is important to find systematic ways of introducing fault-tolerance already into the representations of switching functions. When redundancy is introduced to the representations of functions, no additional voters or checker circuits are required. This is the motivation behind combining the theory of error-correcting codes and decision diagrams, since decision diagrams are an efficient way of representing functions. The original method presented in this chapter introduces robustness to the representations of functions, and due to the properties of decision diagrams, the information on the complexity and layout of the resulting circuits is contained in these robust representations. Each robust diagram is specified by an error-correcting code, and the properties of the given code affect the complexity and layout of the diagram. The procedure of constructing the robust diagram is analogous to the decoding process of the code, which for linear codes is, in principle, based on simple matrix and lookup operations.

First, some introduction to the subject is provided in Section 4.1 before moving onto definitions and details. The definition of error-correcting decision diagrams is given in Section 4.2, and the step by step procedure of constructing such a diagram is described in Section 4.3. In Section 4.4, several examples of error-correcting decision diagrams in both binary and multiple-valued logic are given.

#### 4.1 Introduction to Error-Correcting Decision Diagrams

Consider the TMR technique described in Section 3.3. If instead of logic modules, we simply consider variables, then TMR realizes the majority function  $f_4$  of three variables, for which the truth vector is given in Table 4.1. On the other hand, the majority function  $f_4$  has a direct correspondence to the binary (3, 1) repetition code, since the function has the values 0 and 1, when the received length 3 vector is decoded to 0 and 1, respectively, by the decoding rule of the repetition code.

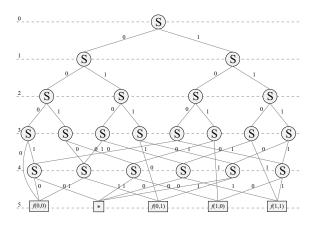

The majority function  $f_4$  can be represented by its BDD, which is shown in Figure

#### 4. Error-Correcting Decision Diagrams

| $x_0 x_1 x_2$ | $f_4(x_0, x_1, x_2)$ |

|---------------|----------------------|

| 000           | 0                    |

| 001           | 0                    |

| 010           | 0                    |

| 011           | 1                    |

| 100           | 0                    |

| 101           | 1                    |

| 110           | 1                    |

| 111           | 1                    |

Table 4.1: The truth-table of the majority function  $f_4$  of 3 variables.

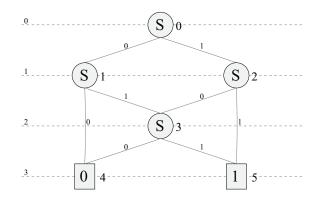

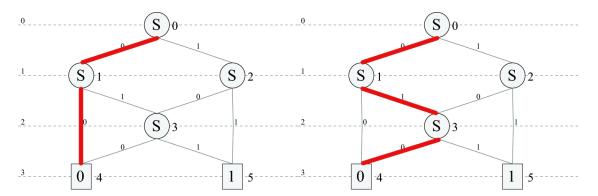

4.1. There is some similarity between the structure of the BDD and the structure of a logic module with TMR (Figure 3.1), i.e., the four nodes correspond to the triplicated units and a voter. Also, due to the correspondence between the majority function  $f_4$  and the (3, 1) repetition code, this diagram can be thought of as the BDD representing the decoding rule of the (3, 1) repetition code, where by following the edges corresponding to the received sequence, the original information word is found in the terminal node. In other words, the received vector is the input and the output is given by the decoding rule of the (3, 1) repetition code. Hence, the BDD in Figure 4.1 is the simplest error-correcting decision diagram.

Figure 4.1: The BDD of the majority function  $f_4$ .

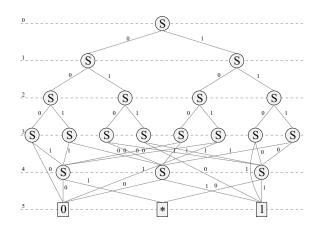

The above diagram is a robust representation of the 1-variable function  $f_5$ , which is 0 when the input is 0, and 1 when the input is 1. The binary decision diagram of the function  $f_5$  consists of just a single non-terminal node and two terminal nodes. The basic idea of how the decision diagram in Figure 4.1 is obtained from  $f_5$  is to map the function  $f_5$  to the majority function  $f_4$  given in Table 4.1. The mapping is done by assigning such length 3 vectors to 0 (1), which would be decoded to 0 (1) by the decoding rule of the (3, 1) repetition code. Then, the BDD of the majority function  $f_4$  will be the error-correcting BDD of the function  $f_5$ . Hence, the BDD in Figure 4.1 is a robust version of a single decision node.

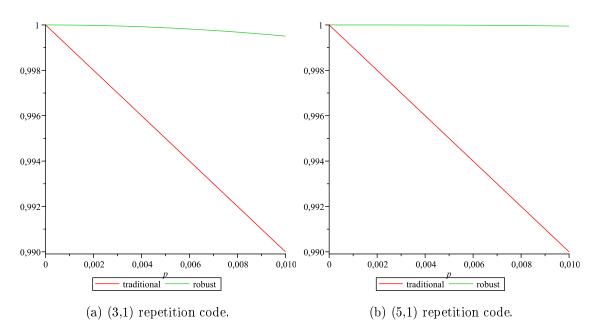

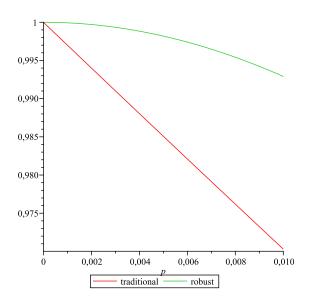

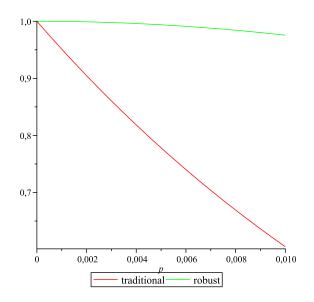

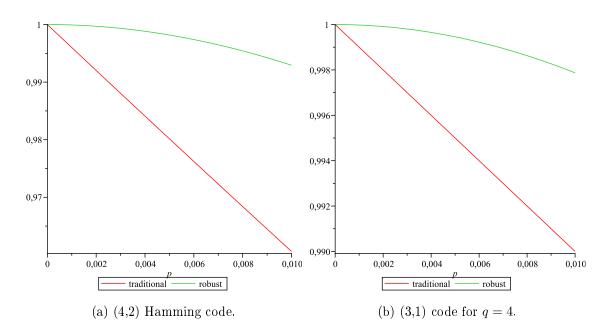

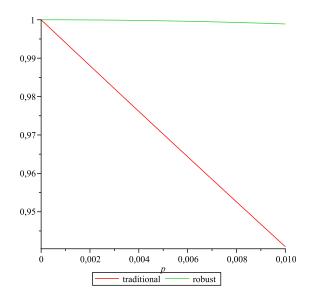

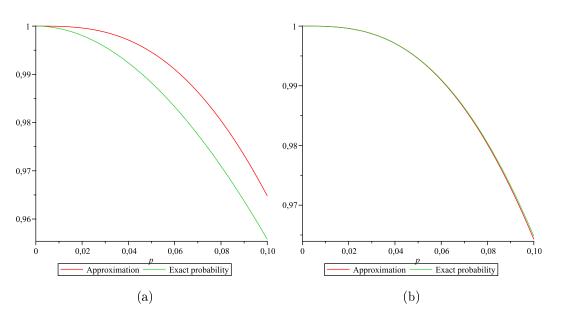

The idea can be generalized to arbitrary functions and codes. The procedure of generating error-correcting decision diagrams follows the decoding rule of the code, and the error-correcting properties of the diagrams depend on the given code. Using an *e*-error-correcting code leads to an error-correcting decision diagram, which corrects *e* decision errors. If the utilized code is a linear (n, k) code, it is a subspace of the vector space  $\mathbb{F}_q^n$ , and the paths of an error-correcting decision diagram correspond to the elements of the additive group of  $\mathbb{F}_q^n$ . The paths corresponding to elements belonging to cosets having coset leaders at distance  $\leq e$  from the all-zero codeword lead to the correct output value.