Juho Tieaho

# DATA PLANE PROGRAMMABILITY

in network-attached FPGA accelerators

Faculty of Information Technology and Communication Sciences Master of Science thesis June 2020

## ABSTRACT

Juho Tieaho: Data plane programmability in network-attached FPGA accelerators Master of Science thesis Tampere University Master's Degree Programme in Electrical Engineering June 2020

To increase capital efficiency and flexibility in networking, virtualization methods, following the concept of Network Function Virtualization (NFV), can be used. In NFV, network functions conventionally implemented on proprietary hardware appliances are migrated to Commercial Off-The-Shelf (COTS) hardware as software-implemented virtualized functions. This may come at the cost of performance, and some performance-critical functions may require the usage of specialized hardware as hardware accelerators.

This work is focused around the reconfigurable Field-Programmable Gate Array (FPGA) accelerators, and more specifically, FPGA accelerators that are network-attached, as in accessible directly via network. In this thesis, a data plane programmability language, P4 (Programming Protocol-independent Packet Processors), was trialled as a method for implementing packet processors in the FPGA ingress and egress paths as networking logic surrounding the core accelerator functionality. This was done to map its usability as an alternative to a Register-Transfer Level (RTL) Hardware Description Language (HDL).

For the study, three design variants were implemented, all providing the same networking functionality of Virtual Tunnel Endpoint (VTEP) termination and a five-tuple based firewall. The design variants were a software interfaced P4 design, a reference hard-coded VHDL (Very High Speed Integrated Circuit Hardware Description Language) design, and finally, a hard-coded P4 design for more comparable hardware resource utilization metrics. As the P4 language is a plat-form-independent high-level description language, a third-party back end compiler was used in the hardware design.

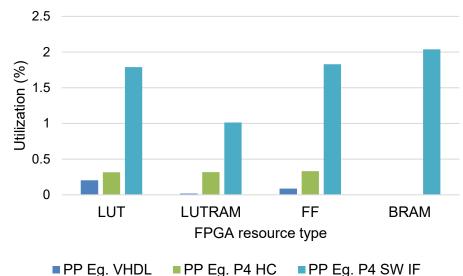

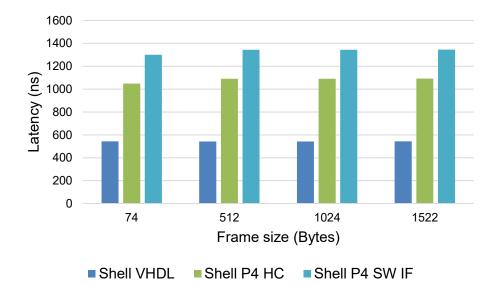

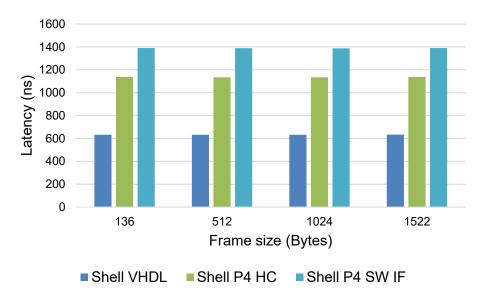

The P4-based implementations were compared against the VHDL-based implementation in terms of FPGA resource utilization, performance, as in latency and throughput, and design automation, as in lines of source code. From the variants, the VHDL design proved to be superior by the lowest resource utilization. Additionally, the VHDL design achieved the lowest latency from the variants, being able to process 1kB frames in 0,5 $\mu$ s, whereas the P4 software interfaced and hard-coded design variants achieved latencies of 1,1 $\mu$ s and 1,3 $\mu$ s, respectively. However, the P4 proved to provide a more automated implementation design flow, indicated by the lines of code: the VHDL description consisted of 8,1x more lines than the P4 software interfaced variant.

Keywords: Data plane programmability, FPGA, hardware accelerator, P4, NFV

The originality of this thesis has been checked using the Turnitin OriginalityCheck service.

# TIIVISTELMÄ

Juho Tieaho: Reititystason ohjelmoitavuus verkkoon kytketyissä FPGA-kiihdyttimissä Diplomityö Tampereen yliopisto Sähkötekniikan diplomi-insinöörin tutkinto-ohjelma Kesäkuu 2020

Verkkofunktioiden virtualisointikonseptin (engl. Network Function Virtualization, NFV) mukaisia menetelmiä voidaan käyttää tiedonsiirtoverkkojen kustannustehokkuuden ja joustavuuden lisäämiseksi. Tämä konsepti tarkoittaa verkkotoimintojen toteutusta virtuaalisina ohjelmistofunktioina. Tällöin perinteisten, erikoiskäyttöisten ja patentoitujen verkkolaitteiden käyttöä voidaan korvata yleiskäyttöisellä ja yleisesti saatavilla olevalla laitteistolla. Ohjelmistototeutuksien käyttö voi kuitenkin näkyä suorituskyvyn heikkenemisenä, jolloin vaativimpien toimintojen suorittamisessa voidaan käyttää apuna erillisiä laitteistokiihdyttimiä.

Tämä työ keskittyy verkkoon kytkettyihin uudelleenohjelmoitaviin FPGA-kiihdyttimiin (engl. Field-Programmable Gate Array). Työssä koekäytettiin reititystason (engl. data plane) ohjelmointiin tarkoitettua P4-kieltä (engl. Programming Protocol-independent Packet Processors) FPGA-kiihdyttimen verkkotoiminnallisuuden toteutuksessa. Työn tavoitteena oli kartoittaa P4-kielen käytettävyyttä tässä käyttökohteessa vaihtoehtona perinteiselle rekisterisiirtotason (engl. Register-Transfer Level, RTL) laitteistokuvauskielelle (engl. Hardware Description Language, HDL).

Tutkimuksessa tuotettiin kolme reititystason toiminnallisuudeltaan vastaavaa toteutusta, jotka toteuttivat virtuaalitunnelin päätepisteen (engl. Virtual Tunnel Endpoint, VTEP) terminnoin, sekä protokollikenttien avulla muodostettuun monikkoon pohjautuvan palomuurin. Toteutuksina olivat ohjelmistorajapinnallinen P4-totetutus, vertailukohtana toimiva kovakoodattu VHDL-toteutus (engl. Very High Speed Integrated Circuit Hardware Description Language), sekä tarkemman resurssien käyttöasteen vertailun mahdollistava kovakoodattu P4-toteutus. P4-kielen kuvaukset käännettiin käyttäen kolmannen osapuolen kääntäjää.

P4-toteutuksia vertailtiin VHDL-toteutukseen käyttäen vertailukohtina FPGA:n resurssien käyttöastetta, suorituskykyä, sekä suunnitteluvuon automaatiota lähdekoodiriveissä mitattuna. VHDL-toteutuksen resurssien käyttöaste osoittautui matalimmaksi. VHDL-toteutus kykeni myös matalimpaan käsittelyviiveeseen, joka oli noin 0,5 µs käsiteltävien pakettien ollessa 1 kilotavun kokoisia. Täyden ohjelmistorajapinnallisen P4-toteutuksen viive oli 1,4 µs, ja kovakoodatun P4-toteutuksen viive 1,1 µs. Automaatioltaan, tässä työssä lähdekoodirivien lukumäärässä mitattuna, P4-toteutus oli ylivertaisin: VHDL-toteutuksessa käytettyjen koodirivien määrä oli 8,1-kertainen P4-toteutukseen nähden.

Avainsanat: Reititystason ohjelmoitavuus, FPGA, laitteistokiihdytin, P4, NFV

Tämän julkaisun alkuperäisyys on tarkastettu Turnitin OriginalityCheck -ohjelmalla.

# PREFACE

Big thanks to Prof. Timo D. Hämäläinen and Arto Oinonen from Tampere University and Jouni Markunmäki from Nokia for supervision and help throughout the writing process of this thesis.

I also want to express my gratitude for Nokia and my excellent colleagues in the company. Special thanks to Hannu Tulla for assistance in all technical matters, as well as Talita Tobias Carneiro and Daniel Koslopp for collaboration throughout the CRUN project.

Tampere, 12.06.2020.

Juho Tieaho

# CONTENTS

| 2.NETWOF<br>2.1  | RKING PARADIGMS<br>NFV                                               |          |

|------------------|----------------------------------------------------------------------|----------|

| 2.2              | SDN                                                                  | 6        |

| 3.HARDWA<br>3.1  | ARE ACCELERATION IN THE NFV CONTEXT<br>FPGA accelerators             |          |

| 4.DATA PL<br>4.1 | ANE PROGRAMMABILITY<br>Programmability to the forwarding plane: How? |          |

| 4.2              | P4 brought into focus                                                | 16       |

|                  | 4.2.1 P4 targets and compilers                                       |          |

| 5.METHOD<br>5.1  | OLOGY<br>Hardware design methodology                                 | 20<br>21 |

| 5.2              | Test and measurement setup                                           | 21       |

| 6.SYSTEM<br>6.1  | DESCRIPTION<br>CRUN framework                                        |          |

| 6.2              | Top level FPGA design                                                | 26       |

| 6.3              | Use case description                                                 | 28       |

| 7.IMPLEME<br>7.1 | ENTATION<br>VHDL implementation                                      |          |

| 7.2              | Software interfaced P4 implementation                                | 35       |

| 7.3              | Hard-coded P4 implementation                                         | 39       |

| 8.RESULTS<br>8.1 | S AND ANALYSISUtilization                                            |          |

| 8.2              | Performance                                                          | 44       |

| 8.3              | Degree of automation                                                 | 48       |

|                  | SIONS<br>CES                                                         |          |

|                  |                                                                      |          |

# LIST OF FIGURES

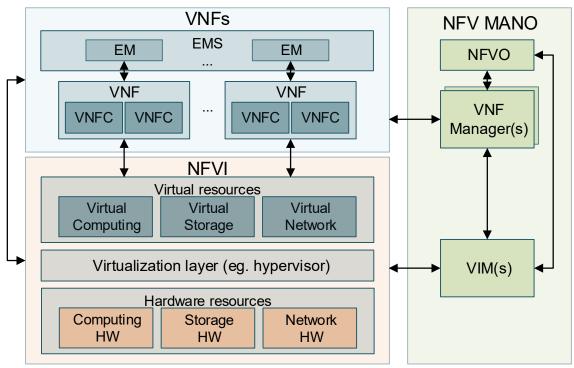

| Figure 1.    | The architectural framework of NFV. Adopted from [6]                                                                                                                                                     | 5    |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

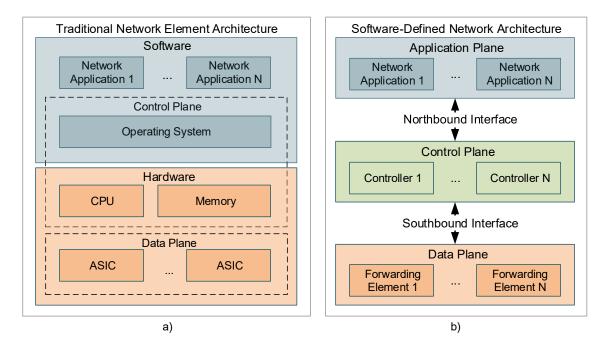

| Figure 2.    | The architecture of a) a traditional network element and b) SDN.<br>Adopted from [15].                                                                                                                   | 7    |

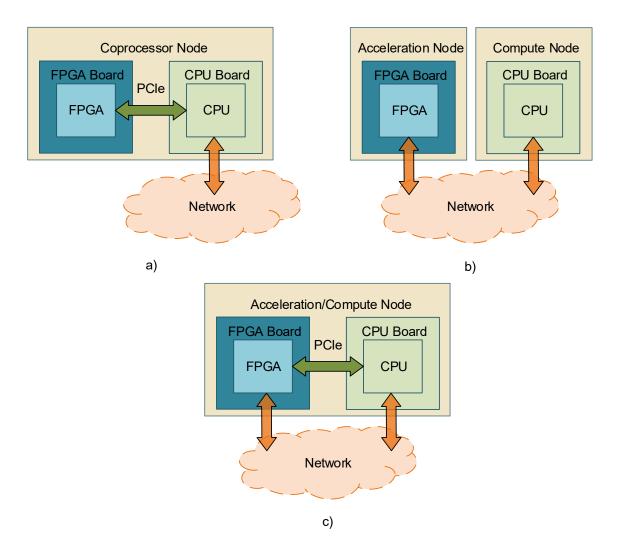

| Figure 3.    | FPGA accelerator attachment options: a) a tightly coupled<br>coprocessor model, b) a network-attached, network appliance<br>model, c) a tightly coupled and network-attached model. Adapted<br>from [23] | . 12 |

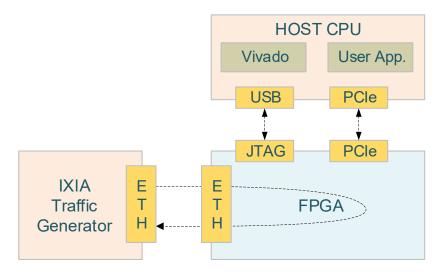

| Figure 4.    | Testing and measurement system description.                                                                                                                                                              | . 22 |

| Figure 5.    | Network architecture in CRUN.                                                                                                                                                                            | . 25 |

| Figure 6.    | Server architecture in CRUN                                                                                                                                                                              | . 25 |

| Figure 7.    | Top level accelerator shell design implementation on the FPGA                                                                                                                                            | . 27 |

| Figure 8.    | Protocol stack supported by the packet processors. Fixed header lengths in bytes (B).                                                                                                                    | . 28 |

| Figure 9.    | Packet processing flow diagram for a) ingress and b) egress packet processors                                                                                                                            | . 30 |

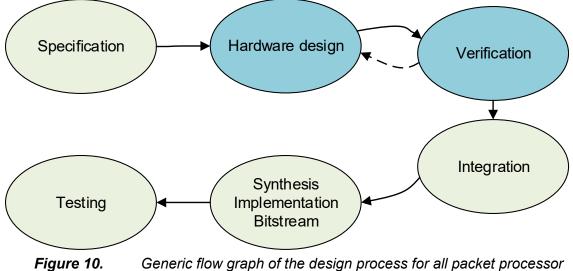

| Figure 10.   | Generic flow graph of the design process for all packet processor variants.                                                                                                                              | . 31 |

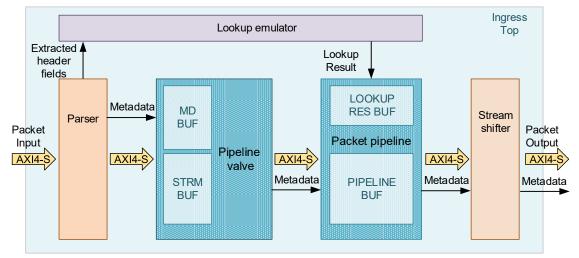

| Figure 11.   | Design architecture of the VHDL-implemented ingress packet processor.                                                                                                                                    | . 33 |

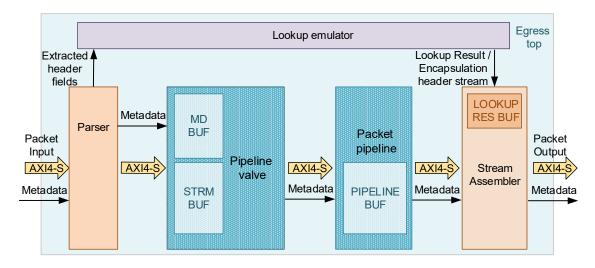

| Figure 12.   | Design architecture of the VHDL-implemented egress packet processor.                                                                                                                                     | . 34 |

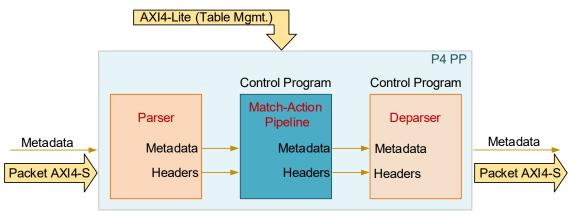

| Figure 13.   | P4-defined packet processor IP.                                                                                                                                                                          | . 39 |

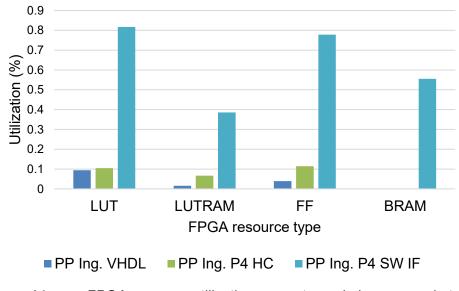

| Figure 14.   | FPGA resource utilization percentages in ingress packet                                                                                                                                                  |      |

| - gui e i ii | processors.                                                                                                                                                                                              | . 42 |

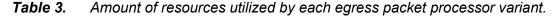

| Figure 15.   | FPGA resource utilization percentages in egress packet                                                                                                                                                   | –    |

| -            | processors.                                                                                                                                                                                              | . 43 |

| Figure 16.   | Latencies with only inner headers for each design variant per frame size.                                                                                                                                | . 47 |

| Figure 17.   | Latencies with VxLAN encapsulation headers on top of inner headers for each design variant per frame size                                                                                                | . 47 |

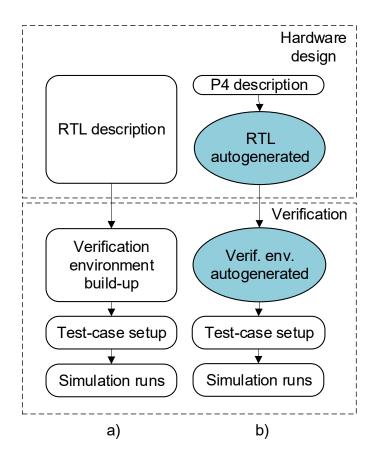

| Figure 18.   | Design and verification workflow graphs for a) VHDL and b) P4                                                                                                                                            |      |

|              | design in this work.                                                                                                                                                                                     | . 49 |

# LIST OF SYMBOLS AND ABBREVIATIONS

| 4G              | Fourth Generation                                                    |

|-----------------|----------------------------------------------------------------------|

| 5G              | Fifth Generation                                                     |

| API             | Application-Programming Interface                                    |

| ASIC            | Application-Specific Integrated Circuit                              |

| ASSP            | Application-Specific Standard Product                                |

| BCAM            | Binary Content-Addressable Memory                                    |

| BRAM            | Block Random-Access Memory                                           |

| BSV             | Bluespec SystemVerilog                                               |

| COTS            | Commercial Off-The-Shelf                                             |

|                 |                                                                      |

| CPU             | Central Processing Unit                                              |

| DMA             | Direct Memory Access                                                 |

| DUT             | Device Under Test                                                    |

| EM              | Element Manager                                                      |

| EMS             | Element Management System                                            |

| ETSI            | European Telecommunications Standards Institute                      |

| FF              | Flip-flop                                                            |

| FIFO            | First In, First Out                                                  |

| ForCES          | Forwarding and Control Element Separation                            |

| FPGA            | Field-Programmable Gate Array                                        |

| FSM             | Finite State Machine                                                 |

| GPP             | General Purpose Processor                                            |

| GPU             | Graphics Processing Unit                                             |

| HDL             | Hardware-Description Language                                        |

| ID              | Identifier                                                           |

| ILA             | Integrated Logic Analyzer                                            |

| iNIC            | Intelligent Network Interface Controller                             |

| IP              | Intellectual Property                                                |

| <br>IPv4        | Internet Protocol version 4                                          |

| JTAG            | Joint Test Action Group                                              |

| LOC             | Lines of Code                                                        |

| LUT             |                                                                      |

|                 | Lookup Table                                                         |

| LUTRAM          | Lookup Table Random-Access Memory                                    |

| MANO            | Management and Orchestration                                         |

| NFP             | Network Flow Processor                                               |

| NFV             | Network Function Virtualization                                      |

| NFVI            | Network Function Virtualization Infrastructure                       |

| NIC             | Network Interface Controller                                         |

| NOS             | Network Operating System                                             |

| NPU             | Network Processing Unit                                              |

| OS              | Operating System                                                     |

| OVS             | Open vSwitch                                                         |

| P4              | Programming Protocol-independent Packet Processors                   |

| рсар            | Packet capture                                                       |

| PCle            | Peripheral Component Interconnect Express                            |

| PHY             | Physical layer                                                       |

| POC             | Proof of Concept                                                     |

| PP Eg. P4 HC    | Hard-coded P4 implementation of the egress packet processor          |

| PP Eg. P4 SW IF | Software interfaced P4 implementation of the egress packet processor |

|                 | sor                                                                  |

| PP Eg. VHDL     | VHDL implementation of the egress packet processor                   |

|                 |                                                                      |

| PP Ing. P4 HC   | Hard-coded P4 implementation of the ingress packet processor         |

| PP Ing. SW IF  | Software interfaced P4 implementation of the ingress packet processor             |

|----------------|-----------------------------------------------------------------------------------|

| PP Ing. VHDL   | VHDL implementation of the ingress packet processor                               |

| RAM            | Random-Access Memory                                                              |

| RAN            | Radio Access Network                                                              |

| RTL            | Register-Transfer Level                                                           |

| RX             | Receive                                                                           |

| SDN            | Software-Defined Networking                                                       |

| Shell P4 HC    | Shell design with hard-coded P4 implementations of the packet pro-<br>cessors     |

| Shell P4 SW IF | Shell design with software interfaced P4 implementations of the packet processors |

| Shell VHDL     | Shell design with VHDL implementations of the packet processors                   |

| SR-IOV         | Single Root Input/Output Virtualization                                           |

| ТХ             | Transmit                                                                          |

| UDP            | User Datagram Protocol                                                            |

| UVM            | Universal Verification Methodology                                                |

| VHDL           | Very High Speed Integrated Circuit Hardware Description Language                  |

| VLAN           | Virtual Local Area Network                                                        |

| VM             | Virtual Machine                                                                   |

| VNF            | Virtual Network Function                                                          |

| VNFM           | Virtual Network Function Manager                                                  |

| VNI            | Virtual Network Identifier                                                        |

| vRAN           | virtualized Radio Access Network                                                  |

| VTEP           | Virtual Tunnel Endpoint                                                           |

| VxLAN          | Virtual Extensible Local Area Network                                             |

### 1. INTRODUCTION

Mobile traffic is increasing, both in volume and variety, due to growing amounts of smart phones and other connected devices [1], creating an increasing demand for lower latency and greater capacity in mobile networks [2]. The telecommunications industry is pressured for higher data rates by the subscribers [3], and for example with the fifth generation (5G) mobile networks, the data rate demand can be up to 100x compared to the fourth generation (4G), while the end-to-end latency must be reduced to a fifth [4]. The higher capacity requirements force the communications service providers to invest in the network, while concurrently finding ways to preserve profitability [1].

For a telecommunications service provider, the Radio Access Network (RAN) causes a major part of capital and operating expenses, respectively up to 80% and 60%. This makes RAN a compelling choice for expense reduction [3]. One method to achieve this is to utilize the concept of Network Function Virtualization (NFV).

In the NFV concept, network functions are separated from proprietary hardware devices and implemented as software virtual functions, running on Commercial Off-The-Shelf (COTS) hardware, for example x86 architecture high volume servers [5]. In the domain of a virtualized RAN (vRAN), this means the virtualization of baseband unit functions to run on a shared physical infrastructure, separating the baseband units from their dedicated remote radio units [3].

With the usage of COTS hardware and virtualized, software-implemented functions, the NFV concept brings benefits such as capital efficiency and flexibility to the network [6]. However, some virtual network functions may require performance not attainable with standard servers and require the usage of specialized hardware as hardware accelerators [7].

One candidate for a hardware accelerator is the Field-Programmable Gate Array (FPGA), which is a reconfigurable platform, and due to its hardware structure can offer improved performance compared to General-Purpose Processors (GPP). In addition to serving as local accelerators for their host server, they can be connected directly to a data centre network. As network-attached, the FPGA is additionally enabled for network acceleration as well as global acceleration [8]. This work is focused on the networking logic on these FPGAs, bringing in the concept of data plane programmability.

Software-Defined Networking (SDN) is a networking paradigm which aims to decouple the control plane from the data plane and to centralize it. The data plane then forwards traffic based on the control plane instructions via a well-defined Application-Programming Interface (API). [9]

On the data plane level, its programmability can be enabled with different programming models and abstractions that are exposed to the control plane. One of the abstractions is the match-action abstraction, where the controller configures the packet processing of the device by managing entries in flow tables. [10] The target is programmed to match values from protocol headers against the values in flow tables and based on the match result and the configuration of the table a certain action is executed. A programming language using this abstraction is the P4 (Programming Protocol-independent Packet Processors).

P4 is a platform-agnostic, domain specific language for the programming of protocolindependent packet processors. In a P4 program, the programmer defines the supported set of protocols, a protocol parser and control programs. The control programs contain the match-action tables and action definitions, which determine how the packets are processed. [11]

The goal of this thesis is to map the feasibility and use cases of using a data plane programmability method, the P4 language, in the implementation of networking logic in network-attached FPGA accelerators. The thesis was done as a part of a larger in-house framework, the CRUN, which presented a cloudified datacentre architecture, where FPGAs could be flexibly provided as hardware accelerator resources, accessible both locally and via network.

The feasibility study was done by implementing packet processors, i.e. the networking logic surrounding the accelerator on the FPGA, with both the P4 language and VHDL (Very High Speed Integrated Circuit Hardware Description Language). The resulting hardware designs were compared against each other by performance metrics, latency and throughput, utilization, as well as by the degree of automation in the design flows.

This thesis is structured as follows. Chapter 2 presents the main networking paradigms behind this work, the NFV and SDN, focusing on an architectural description. Chapter 3 presents hardware acceleration with the NFV framework, as well as an introduction to FPGA accelerators in this context. Chapter 4 opens the domain of data plane programmability, alongside a description of the P4 language as a part of this work. Chapter 5 describes the methodology, tools, and platforms used in this work. Chapter 6 presents

the project framework, implemented top level FPGA design, and the implemented networking functionality. Chapter 7 gives a more detailed description of the VHDL and P4 packet processing designs, and of how they were implemented. Chapter 8 presents the utilization, performance and degree of automation results for all design variants, and chapter 9 concludes the thesis.

### 2. NETWORKING PARADIGMS

In conventional networking, the implementation of network functions often includes the usage of proprietary hardware appliances. Addition of new features is costly and complex, as it requires the purchase of new devices [12]. A large variety of equipment, such as switches and middleboxes, further increases the complexity and slows innovation, as these devices often come with closed and proprietary control software and configuration interfaces varying across vendors [9]. This chapter presents the networking concepts of SDN and NFV, which aim to address these issues.

#### 2.1 NFV

Network Function Virtualization is a networking paradigm which aims to bring capital efficiency and flexibility to networking by replacing proprietary hardware devices with COTS hardware and providing the network functions implemented by them as virtualized functions (Virtualized Network Function, VNF) [6]. This is purposed for a more cost-effective, shareable and homogenous hardware architecture. Additionally, with VNFs flex-ibly assignable to hardware, functionality is decoupled from location, scalability is increased, and the software-based deployment model enables faster innovation for new services. In conclusion, the European Telecommunications Standards Institute (ETSI) group specification in [6] summarizes the service provisioning differences in NFV compared to non-virtualized traditional networks as follows:

- Decoupled software and hardware, enabling independent evolution for both, and leading to

- flexible network function deployment and dynamically scalable operation, adjusting the performance capacity as required by traffic in the network.

To better understand the NFV framework, it can be divided into 3 main working domains, as in [6]:

- VNFs, software-implemented network functions running on top of the

- NFV Infrastructure (NFVI), which in turn includes all the physical resources and their virtualization methods, and finally the

- NFV Management and Orchestration (MANO), including the orchestration and management of hardware and software resources supporting the virtualization and the VNFs.

How these domains are connected is depicted in the NFV architectural framework in figure 1. The NFVI can be seen as the data plane of the network [13]. It consists of hardware resources, which are virtualized as virtual resources by the virtualization layer. The computing hardware is realized by general-purpose COTS compute nodes. Storage hardware consists of data storage devices divisible into for example shared network attached storage and server-specific storage. Finally, the networking hardware is a combination of switches, routers, and wired or wireless links. [6]

Figure 1. The architectural framework of NFV. Adopted from [6]

The virtualization layer decouples the hardware resources from the VNF software. The physical resources are abstracted and partitioned as virtual resources for the VNFs to use. A typical solution to provide the virtual resources is the usage of hypervisors, which in turn provide Virtual Machines (VMs). A VNF can then be implemented on one or several VMs. [6] Virtual resources are interconnected with typically software-based virtual networking, implemented with for example virtual switches [13]. Techniques such as virtual networks and network overlays, e.g. Virtual Local Area Network (VLAN) or Virtual Extensible Local Area Network (VxLAN) can be used to create virtualized paths to interconnect VMs and VNFs [6].

The VNF domain consists of VNFs and the Element Management System (EMS). The VNFs are software-implementations of network functions, providing the same functionality and external operational interfaces as physical implementations on dedicated hardware. The implementation of a VNF can be distributed to components (VNF Component, VNFC) on different VMs. The VNFs are managed by Element Managers (EM), which together form the EMS. [13]

In the NFV MANO, the responsibility of the NFV Orchestrator (NFVO) is the management and orchestration of the NFVI and its resources, and realizations of the networking services in it. The VNF lifecycle from instantiation to termination is managed by VNF managers (VNFM). A VNF is tied to a single VNFM, whereas a VNFM may manage several VNFs. Finally, the Virtual Infrastructure Managers (VIM) are responsible for resource management and monitoring of the NFVI, including tasks such as VM allocations to hypervisors, resource adjustments to VMs, and fault information collection from the NFVI. [6]

### 2.2 SDN

Whereas NFV focused on the separation of software and hardware, Software-Defined Networking focuses on the decoupling of the data plane from the control plane [14]. Conventionally, a network consists of separate network devices, which in turn are entities of tightly coupled hardware and software, performing both data and control plane functions (figure 2 a)). In SDN, the planes are separated by centralizing the control of the network onto SDN controllers, which configure the data plane according to rules set by network applications in the application plane (Figure 2 b)). [15]

The SDN survey in [14] describes a software-defined network by an architecture based on 4 principles:

- 1. Decoupled control and data planes, resulting in network devices becoming simple forwarding elements.

- 2. Forwarding rules are based on flows instead of destinations, i.e. sets of packet field values matched for a set of actions.

- 3. Control is centralized and moved to the SDN controller, or the network operating system (NOS), which is running on server hardware.

- 4. The programming of the network is done by applications on top of the NOS.

*Figure 2.* The architecture of a) a traditional network element and b) SDN. Adopted from [15].

The centralized control is purposed to maintain a global view of the network, and to provide a more abstracted model of the underlying hardware, enabling the use of high-level programming languages and software components. Through this centralization, state and information of the network is available to all applications, and the applications are less tied to location. The higher-level abstractions are also more shareable and reusable between applications. [14]

The decoupled planes in the SDN architecture, and the interfaces between them, can be seen in figure 2 b). In the bottom of the figure reside the forwarding elements, also referable as forwarding devices as in [14]. These devices, e.g. routers and switches [15], perform actions such as forwarding and dropping of packets, or header modifications [14]. These actions are taken based on flow rules, which are received from the control plane through the southbound interface [14, 15]. Interconnected by wireless or wired connections, together these devices form the data plane [14].

The control plane is the centralized intelligence of the network [14], consisting of a controller or controllers [15]. The controllers generate configuration rules derived from the application plane, and pass these rules to the data plane devices via the southbound interface [14, 15]. The southbound interface, implemented with for example OpenFlow [16], defines the communication protocol between the forwarding elements and the control plane [14]. On the top of the figure is the application plane, also referable as the management plane [14]. This plane consists of applications for example routing [15], quality of service mechanisms [15], firewalling [14] and load balancing [14]. These applications use an API, the northbound interface, and its functions to generate and deliver rules for network traffic treatment to the control plane [14].

# 3. HARDWARE ACCELERATION IN THE NFV CONTEXT

In NFV, networks gain flexibility, scalability and capital efficiency by replacing the proprietary hardware middleboxes with COTS hardware. However, this comes with a tradeoff: using software virtualizations to run network functions in place of specially tailored ASICs (Application-Specific Integrated Circuit) can have a negative impact in throughput and latency [17]. To improve performance, whether the goal is in relation to e.g. cost, power, area, or to reach the sheer maximum, acceleration techniques can be introduced into the NFVI. The usage of specialized hardware to gain this performance improvement, is called hardware acceleration. [7]

Hardware accelerators can be such as custom ASICs, FPGAs, NPUs (Network Processing Unit) or GPUs (Graphics Processing Unit). A further classification for VNF hardware accelerators can be done by their type, and according to [18] these types can generally be divided in the following categories:

- in-line accelerators, which process packets in-line with software [7], as they traverse to or from the network, i.e. on the fly [18].

- look aside accelerators, which typically operate on data and commands submitted by software. Based on the command, the accelerator processes the data and sends a response. [7]

Look aside accelerators are typically associated with compute-intensive algorithmic acceleration, such as crypto or compression [7]. Compute-intensive functions characterize with the complexity and dynamism being in the calculations, while the processed data is more static, in relation to network-intensive functions. Network-intensive functions, e.g. network address translation and load balancing, have high throughput constraints and the data is dynamic, while the processing code itself can be relatively small. [19] Due to the data being mediated by a Central Processing Unit (CPU), look-aside acceleration can introduce higher latencies and more limited throughput by the CPU I/O in comparison to in-line acceleration [18].

Additional taxonomy for the hardware accelerators can be brought by their housing. The ETSI group specification for NFV acceleration [7] lists accelerator housings as

integrated CPU, as in the accelerator (e.g. ASIC, GPU, FPGA) is implemented as a hardware function in the CPU socket

- iNICs (intelligent Network Interface Controller) or smartNICs, which are programmable and can be based around CPU or NPU cores (multicore system-on-chipbased, or an FPGA (FPGA-based). Additionally, the programmable cores on a SmartNIC can be accompanied by custom hardware blocks as acceleration engines. [4]

- bus attached, or

- network-attached, where the accessing is done over the network.

All of the above housings support both inline and look-aside acceleration, excluding the network-attached housing model, which is tied to only in-line acceleration in the group specification.

For the location of the accelerators, as in deployment models, generally two options for data centres can be identified [20] as in having the accelerators deployed in clusters, in centralized pools, or each server is coupled with acceleration hardware. Pooling of the accelerator hardware is a way of retaining uniformity in the core server infrastructure. On the other hand, from the perspective of the complete data centre, the homogeneity of the infrastructure is reduced. Whether to deploy the accelerators with each server, or in a subset of servers with the downside of more complex management and configuration is essentially a matter of cost-effectiveness. [20]

### 3.1 FPGA accelerators

An FPGA is a reprogrammable silicon device used to implement hardware circuitry. It consists of a certain amount of basic circuit elements, which are used and interconnected according to an architecture definition. Generally, the programmer writes this definition using an HDL, such as VHDL or Verilog. With automated tools, the hardware design is translated into a binary file, a bitstream, which, once loaded onto the FPGA, implements the circuit. As computational data paths are customisable and parallelization can be exploited, an FPGA can offer considerable performance gain in comparison to software implementations running on GPPs. [21]

The reconfigurability of an FPGA is a crucial feature in an accelerator, as cloudified environments come with a large variety of workloads changing in a fast pace. [20] With FPGAs, as opposed to ASICs, there is no manufacturing process as the functionality can be changed with a binary file, enabling more rapid design changes. [21] In comparison to another commonly used [20, 21] accelerator, the GPU, FPGAs are less demanding on size and power [20]. Besides, even though well-suited for their original purpose of

video and image processing offloading, the GPU-provided performance gain in domains such as signal processing and ciphering is neglectable [22].

A common way of bringing FPGA accelerators to data centres is by tightly-coupling them with a host CPU in a co-processor manner [23] (figure 3 a)), most commonly on by using a daughter-card with a point-to-point connector such as PCIe (Peripheral Component Interconnect Express) [24]. A tighter coupling could be achieved by integrating the CPU and the FPGA on the same board for latency and memory access benefits [25], but the approach breaks server compute module homogeneity, power and size limits for a server board could be exceeded, and a fault on the CPU would lead to the waste of the FPGA resource [24]. The tightly-coupled option in general can be effective on local compute acceleration [8], but without network connectivity, the accelerators are more prone to under- or overutilization by their host CPUs [23].

By making the FPGA network-attached as in figure 3 b), it can be used as a standalone appliance essentially a peer processor in the network with CPUs [24]. Additionally, for more efficient hardware and software co-processing, the FPGA can be made both tightly coupled and network attached [23], as in figure 3 c). For example in [8], FPGA accelerators are network-attached and PCIe-connected to a server, enabling local compute acceleration via PCIe, as well as network acceleration and global accelerator. In network-acceleration, the FPGA can function as an in-line, bump-in-a-wire accelerator for tasks such as network encryption and deep-packet-inspection. In global acceleration, the FPGAs unused by their hosts can function as remote accelerators for large-scale applications, e.g. machine learning. [8]

Network-attachment also brings varying amounts of required logic on the FPGA, as some functionalities, such as protocol parsing [26], are essential on all network-attached devices. In for example [24], where the FPGA is a stand-alone network appliance, network-ing layer is done completely on the FPGA itself, removing the need for an external Network Interface Controller (NIC) and enabling the implementation of a protocols as demanded by the network environment. NIC functionalities, however, utilize resources which could be otherwise used for accelerator functionalities [8].

**Figure 3.** FPGA accelerator attachment options: a) a tightly coupled coprocessor model, b) a network-attached, network appliance model, c) a tightly coupled and network-attached model. Adapted from [23].

### 4. DATA PLANE PROGRAMMABILITY

A network device, be it a router, switch or a NIC, may have a varying amount of network functions to fulfil. These functions can range from switching and routing to for example firewalling, network telemetry, quality of service management and load balancing. [10, 15] Traditionally, the devices often implement these functions utilizing vendor-specific protocols, algorithms and interfaces, [15] in a way leaving the devices black boxes for the network operators [27]. Because of this, the operators dependent on the device vendor when it comes to device configuration, maintenance and re-deployment [15, 27]. Additionally, as compatibility between devices in larger networks needs to be ensured, the requirement of interface and protocol standardization can be seen as an obstacle for innovation, driving development time up alongside the cost [15].

At the same time as the operators are depending on the vendors, the network device vendors are facing the burden of implementing and supporting new functionalities on top of pre-existing ones, as per requests from the operators. New protocols and functions, such as new encapsulation methods in datacentre networks [28], are following the requirements set by evolving trends in for example 5G, machine learning and cloud computing [10]. With a rigid data plane, as in one implemented with dedicated hardware, adding these new features requires continuous development and manufacturing of new and increasingly complex devices. Additionally, an overly extensive supported feature set on a device might lead into unnecessary hardware resource utilization or performance degradation, should a specific deployment of the device not require it in its entirety [10].

Bringing programmability to the network devices to address these issues is not exactly a novel idea, as research on active networks was started in the 1990's. Active network research was based on the idea of bringing the analogy of a programmable computer to networking, with usage of smart packets to program the network device for wanted functionality. [29] More recently, in the 2000s, the architecture standardization for SDN began with the Forwarding and Control Element Separation (ForCES) specification [30] by Internet Engineering Task Force and with OpenFlow [15, 16]. Both ForCES and OpenFlow stated, that the programmability in the network devices requires the decoupling of the control and forwarding planes, with an open, standardized API in between. For this interface in SDN, OpenFlow has gained the most traction [27]. With SDN, the OpenFlow provides a standard API to give the network control plane a possibility for configuring the data plane [16]. However, OpenFlow and the switches utilizing it are limited by a predefined set of supported protocols, and the programmability of the forwarding device is limited to flow-rule setting with a predefined set of actions [28].

### 4.1 Programmability to the forwarding plane: How?

One fundamental factor to the programmability and flexibility of the data plane is the choice of hardware platform in the network devices. SDN is targeted to utilize general-purpose hardware in the network for programmability [31], but at the same time, from the network parts, the data plane is the most heavily constrained by performance requirements [10].

The highest programmability comes with software switches implemented on CPUs, or GPPs. High abstraction levels in programming languages and design tools provide flexibility and speed in the implementation, at the cost of limited performance due to the general-purposed nature of the hardware architecture. [31]

Network processing units or Network Flow Processors (NFPs), similarly as GPPs, are hardware platforms for software switches. Unlike GPPs, these platforms are specifically designed with network processing in mind, e.g. by using dedicated accelerator units [32] and an architecture enabling processing parallelization. Utilization of this architecture, on the other hand, requires more specific programming than with GPPs, at the cost of flex-ibility. [31]

Moving to the domain of hardware switches, programmable logic devices, such as FPGAs, offer the highest flexibility [31]. These reconfigurable hardware devices enable parallel and pipelined processing with wanted functionality. As a downside, the available logic is limited per-chip, and compared to ASICs, these chips consume more power, come with a higher per-chip-cost, and are more limited in performance due to the general-purpose architecture.

Application-Specific Standardized Products (ASSP) are designed to implement functions commonly used or targeted for high-volume products. ASSP use cases can be for example physical and data link layer products [31] and switching fabric implementations [33] in network devices. Performance for the targeted function come with the downside of functionality configuration limitations. [31]

Performance-wise, the Application-Specific Integrated Circuits (ASICs) reside at the top of the curve. These devices are custom made for a certain purpose, designed for the

applications where either the required features are outside the scope of standard products, or the performance requirements are too strict for programmable platforms [31]. Consequence from the custom application-specification, the ASICs have the poorest reconfigurability from the platform choices.

In reality, forwarding element devices are not strictly limited to a one certain platform, and the optimal trade-off between performance, cost and programmability can be also reached with hybrid platforms [10, 31]. A hardware switch appliance can for example use a CPU for functions less demanding on performance, and vice versa, a software switch could use external hardware components for efficiency. [10]

As seen in survey [10], one classification criteria for data plane programmability methods is the abstraction model of the data plane exposed to the control plane. These abstractions provide language constructs for an architectural model and means to configure the programmable target with. The survey identifies three common abstractions for the data plane:

- The data flow graph abstraction,

- the match-action pipeline abstraction, and finally,

- the hybrid-switch abstraction.

Data flow graph abstractions are based on division of processing logic into smaller entities, nodes, which are connected by edges. This abstraction model lets the programmer choose and connect the processing functions modularly, in the wanted order. An example of a data flow graph software switch architecture is Click [34]. Click implements the processing nodes of a software switch, called elements, as C++ objects, which are interconnected with pointers, called connectors.

The match-action pipeline abstraction, as used in for example OpenFlow [16], P4 [28], Protocol-Oblivious Forwarding [27] and Domino [35], describes the packet processing logic with lookup tables containing flow rules. The lookup keys, based on the processed packets' protocol headers, are matched for values in these flow tables. These values are stored together with corresponding actions, which determine the following processing steps, such as additional lookups on another flow tables or dropping of the packet. Thus, the configuration of the packet processing functionality is done by managing the entries in the lookup tables.

The last of the abstractions presented in the survey is the hybrid-switch abstraction, used by architectures combining features from both data flow graph and match-action abstractions [10]. One presented example application falling into this category is the disaggregated Reconfigurable Match-Action Table [36].

### 4.2 P4 brought into focus

P4, a high-level programming language, receiving its name from its intended use of Programming Protocol-independent Packet Processors, is defined to describe the data plane packet processing logic of a forwarding element [11]. As stated in the original P4 paper [28], it is designed around three main goals:

- Reconfigurability of the packet parsing and processing logic, post-deployment, in the field.

- Protocol independence through a protocol header stack defined by the control plane, alongside the parser extracting these headers, and the set of match-action tables to process them.

- Target independence by a high-level functionality description, leaving the generation of a target-dependant program for compilers.

P4 is a domain-specific language, and provides the match-action pipeline abstraction of the data plane of a forwarding element with programs containing the following main elements [11, 28]:

- Header definitions,

- parsers,

- match-action tables,

- actions,

- control programs.

All of the protocol headers accessed in the program are defined with their set, order, and bit widths of fields. How these headers can be sequenced, and how the sequences are identified, is defined in the parser. The parser also defines which of these headers are extracted from the packets. [11, 28]

Program 1 presents a simple example snippet of a parser state machine definition, based on the P4 programs used in this work and written according to the P4 specification [11]. Keywords reserved by P4 are bolded. The parser declaration with its interface starts on line 1, where the input is a P4 core library extern object packet\_in [11], and the output is a user-defined struct of headers. Lines 3 to 10 describe the initial state, where, in this example, the Ethernet header is extracted from the packet and based on the value of the type-field of the header the next state is chosen. On line 8, the default transition is defined to be accept, which results into ending the parsing in the initial state for unmatched packets. Functionality of other states on lines 11 to 17 are abstracted away from the snippet. The match-action unit abstraction is provided by the tables and the actions tied to these tables. The tables are defined with lookup keys, which can be header fields or other values calculated in the P4 program, and actions which are executed based on the matches in the table. The actions are functions, which may have optional input parameters from the table. Tables and actions are contained inside control programs, which determine the order of execution of the match-action units. Additionally, the re-assembling of the packet, deparsing, can be defined in a control program. [11]

```

parser MyParser(packet_in pkt, out hdrs_s hdr) {

2

state start {

4

pkt.extract(hdr.ethernet);

transition select(hdr.ethernet.type) {

0x0800 : parse_ipv4;

6

0x8100 : parse vlan;

8

default : accept;

}

}

10

state parse_ipv4 {

12

... // state transition rules

14

state parse_vlan {

... // state transition rules

16

}

18 }

```

#### Program 1. Example program of parser declaration in P4.

Program 2 presents an example snippet from a control program including a match-action unit, again based on the P4 programs used in this work, written according to the specification [11]. Line numbers 9 to 16 define the lookup table. Lookup key is set as a sourcefield from an Ethernet field, which in turn belongs to a user defined header struct (hdr). Matching method is chosen as exact match, but P4 core library additionally supports longest prefix and ternary matching with "don't care" bits [11]. Actions tied to each table value are declared on lines 11 to 14. Each value in the table will trigger either of the two actions, "Forward\_pkt" or "Drop\_pkt", with the latter one being also declared as a default action on line 16. The default action is triggered if the lookup results in no match. Maximum amount of entries in the table is defined on line 15 with the "size" parameter being set to 1024.

```

action Forward_pkt (bit<4> route_id) {

2

md.route_ID = route_id;

}

4

action Drop_pkt () {

6

md.route_ID = DROP_ID; //constant

}

8

table Eth_match {

10

= { hdr.ethernet.src : exact; }

key

actions = {

Forward_pkt;

12

Drop_pkt;

14

}

size = 1024;

default_action = Drop pkt;

16

}

```

#### Program 2. Example of a match-action unit declaration in P4.

Actions definitions are on lines 1 to 7. The action "Forward\_pkt" has been defined with an input parameter, which is received from the table, set by control plane. This received parameter is set as the value of a user-defined metadata (md) field "route\_ID". Action "Drop\_pkt" similarly sets the value of the metadata field, in this case to a value "DROP\_ID" depicting a user-defined constant.

#### 4.2.1 P4 targets and compilers

As a domain-specific and target-independent language, P4 is designed to be targetable for both software switches and hardware platforms such as NICs, FPGAs and ASICs. [11] To produce an actual target-specific data plane configuration and a control plane API, an implementation framework, architecture definition and a target-specific P4 compiler is required from the target manufacturer [11]. An open-source reference compiler is available in [37], designed as modular to provide a standard front end compiler to be combined with a platform-specific back end compiler.

An example of a software switch target for P4 is PISCES [38]. It is based on the Open-Flow-enabled Open vSwitch (OVS) [39]. OVS has gained wide use in data centres, running inside a hypervisor and switching traffic among virtual and physical interfaces. PI-SCES prototype brings protocol-independency to the OVS by three main modifications, possibly required by a P4 program, and a P4-to-OVS compiler. The modifications are the addition of arbitrary encapsulation and decapsulation with new header adding and removal primitives, conditional action executions, and checksum optimizations. The PI-SCES compiler compiles a P4 program into OVS C code, with the parse, match and action codes replaced according to the P4. This modified OVS can then be compiled with a C compiler into switch binary. [38]

P4-programmable smartNICs can be found from Netronome. Their Agilio class Smart-NICs are based around Netronome NPUs. [40] The compilation process uses the opensource P4 front end compiler together with a Netronome back end compiler for a targetspecific C implementation of the data path. Finally, firmware for the SmartNIC is generated from these C files and downloaded to the device. [32]

On the FPGA side, several P4 compilers and projects exist [41-44]. SDNet is a design environment from Xilinx, which, supported with a P4 back end compiler, compiles P4 descriptions into packet processor IPs for Xilinx FPGAs. In addition to the IP, the tool generates a testbench for simulations.[41]

P4FPGA is an open source compiler and runtime, presented in [42]. Similarly as SDNet, it is targeted for generating HDL code for FPGAs from P4. P4FPGA uses the P4 front end compiler for an intermediate representation, which is then compiled with the P4FPGA compiler into a Bluespec SystemVerilog (BSV) representation. The P4FPGA BSV-based runtime includes support for external IPs and management units for transceivers and host communication, enabling FPGA-targets from multiple vendors. Additionally, the P4FPGA generates a C++ based API for table management and debugging. [42]

Examples of ASIC targets for P4 programming are the switching ASIC Barefoot Tofino [45] and RMT [46]. Leveraging the common abstractions in the chip, a P4 compiler targeting the latter is presented in [47].

## 5. METHODOLOGY

This work evaluates the feasibility of data plane programmability in network-attached FPGA accelerators. More precisely, the evaluation is fixed on evaluating the usability of P4 language in the design of protocol processing blocks on an accelerator FPGA, in comparison to implementing such functionality directly in RTL. Surrounding the actual accelerator Intellectual Property (IP) on the FPGA, these blocks are responsible for networking related tasks, such as protocol parsing and header modifications.

For the evaluation, an accelerator shell design was implemented on the FPGA. The top level in the design hierarchy consists of an accelerator wrapper for the acceleration functions, and the shell design providing connectivity, packet processing, and routing functionalities. Three variants of the shell were implemented, each having a different implementation of the packet processors, yet providing the same data plane functionality. These different implementations were

- 1) a P4 implementation with a software interface for dynamic table updates,

- a hard coded VHDL implementation without a software interface, and finally, for more accurate comparison with the VHDL variant,

- 3) a hard coded P4 implementation without a software interface.

The shell designs with P4 implementations were compared against the shell design with the VHDL implementation in terms of utilization of FPGA resources, performance, and degree of automation in the design flow.

The FPGA has a fixed amount of programmable logic and on-chip memory, and therefore the utilization of resources by the shell dictates the resources available for the main acceleration functionality. To maximize the logic available for the accelerator, the shell design should be aimed to provide the wanted functionality with the lowest utilization percent possible. The utilization is measured as the use of Lookup Tables (LUTs), Flip-Flops (FFs), random-access memories (RAMs) implemented with LUTs (LUTRAMs), and onchip block RAM memory tiles (BRAMs).

The performance is measured with two parameters, latency and throughput. Latency is measured as time between the moment the chosen test data is sent out from a traffic generator and the moment it has been processed by the Device Under Test (DUT) and is received back at the traffic generator. More specifically, latency is measured as cut-through latency, meaning the measurement begins when the first bit of data is sent out

and ends as the first bit is received back. While latency of a network-attached device is generally desired to be as minimal as possible, throughput, on the other hand, is most feasible as maximal. Throughput is the amount of data the DUT can process in a time unit, measured by bits per second in this work.

While being a less quantitative parameter, the degree of automation in the design flow still provides a valuable insight to the feasibility of an implementation method. As the design flows differ between the three implementations, the degree of automation can be measured by comparing which of the intermediate steps between a design specification and an implemented design in each variant is automated, and by how much, in terms of lines of code required.

#### 5.1 Hardware design methodology

The VHDL-implemented packet processors developed in this work were manually written, and verified with an in-house developed Universal Verification Methodology (UVM) [48] testbench. For the P4 implementations, the packet processor design and verification steps were done with the Xilinx SDNet [41], which is a design environment providing a back end compiler for P4 designs targeting Xilinx FPGAs. Additionally, the tool provides a flow for RTL simulations with user-provided stimuli, and therefore no user-made testbenches were required. For more reference on the tool, newer SDNet documentation is available by contacting Xilinx.

Packet data leveraged in the verification of all packet processor variants was generated and captured with a traffic generator, TRex version 2.45, from Cisco [49].

The integration of the packet processor components to the top-level FPGA design, and the synthesis, implementation, and generation of bitstreams, was done by using the Vivado Design Suite [50].

#### 5.2 Test and measurement setup

The system used in the FPGA design comparisons and measurements (figure 9) consists of three main hardware components: the FPGA, the host CPU, and the traffic generator.

The FPGA used in this work was a Xilinx VU9P Virtex Ultrascale+, attached to a Xilinx VCU1525 PCIe development board. More detailed description of the board can be found in [51]. The FPGA has three interfaces in use: an Ethernet interface for packet data, a

JTAG (Joint Test Action Group) interface used for programming and resetting the FPGA, and a PCIe interface for runtime dynamic configurations from the host CPU.

The test data traffic was generated by an IXIA NOVUS-r100GE8Q28 load module. A single port from the traffic generator was connected to one of the VCU1525 board transceivers with the configured link speed of 10 Gbps and the IXIA software used for test configurations was IxNetwork.

The host CPU has a 64-bit x86 architecture and is running a release 7.4.1708 CentOS Linux operating system. With the software interfaced P4 design variant, a C language program code was compiled into an executable user application, which uses a Xilinx PCIe driver for PCIe access to the FPGA. These PCIe accesses are table initializations and updates.

A Lab Edition of Vivado Design Suite was used on the host CPU for programming the FPGA with JTAG connection. The JTAG was converted from an USB connection by the USB to JTAG converter of the VCU1525 board. Vivado was additionally used for controlling the system reset on the design with a Virtual I/O [52], and monitoring ILA (Integrated Logic Analyzer) debug cores [53] in the testing phase. The ILA cores were removed before the utilization measurements.

Figure 4. Testing and measurement system description.

Two different base traffic items, originally generated with TRex,. were used in the testing:

- a packet with a maximum supported header stack of outer Ethernet, outer VLAN, outer IPv4, outer UDP, VXLAN, inner Ethernet, inner VLAN, inner IPv4 and inner UDP, and

- 2) a packet with the minimum supported header stack of inner Ethernet, inner IPv4, and inner UDP.

These two different packet types were chosen to expose possible performance differences between design variants caused by the varied set of headers parsed and encapsulation and de-encapsulation processes.

The performance measurement method used was an implementation of the RFC 2544 Throughput/Latency test [54] by IXIA, with frame sizes of 74, 512, 1024 and 1522 bytes with the minimal header stack, and 136, 512, 1024 and 1522 bytes with the maximal header stack. IXIA requires a certain amount of payload for measurement-related tagging of the packet, hence the difference in the smallest possible frame sizes with different header stacks. The latency was measured as average, minimum and maximum cut-through latency, and maximal throughput was tested by incrementing the transmission rate from 10% of the maximum line rate of 10Gbps, until a frame loss threshold of 0 was crossed. Test duration for each transmission rate was 20 seconds.

## 6. SYSTEM DESCRIPTION

This work was done as a part of a larger in-house developed CRUN project. The project was based around a concept of a cloud architecture with virtual overlay networks on top of a physical network, consisting of server nodes interconnected by switches. These server nodes were attached with virtualizable hardware accelerator FPGAs. This chapter describes the CRUN architecture, the top level of the FPGA design architecture used as the evaluation framework, and the specific use-case the packet processors in the design are designed for.

#### 6.1 CRUN framework

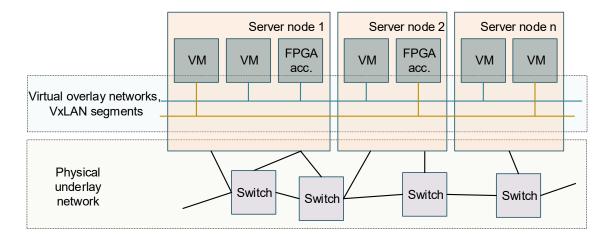

This section briefly presents the CRUN in a top-down manner, starting from the network architecture and then the server architecture, presenting the framework for the FPGA design, which is the main subject of this thesis. The layered networking scheme of the framework is presented in figure 4. The two main layers depicted are

- the physical underlay network, consisting of the hardware components building the cloud infrastructure, and

- the overlay network, a virtual network consisting of virtual machines and accelerators, interconnected in VxLAN segments.

Virtualized network functions are provided by VMs, accelerators and their combinations. These VMs and accelerators are physically located on hardware server nodes, but virtually contained and connected in overlaying virtual networks. For example, a VM on a server node 1 might operate together in the same virtual network with an FPGA accelerator unit on a server node 2, together providing a VNF. Their connection is established over a virtual tunnel, with the virtual tunnel endpoints residing on the server node 1 hypervisor and the FPGA networking logic on server node 2. In the underlay network, the server nodes are connected to switches via NIC and FPGA Ethernet transceivers, forming a physical cloud infrastructure connection.

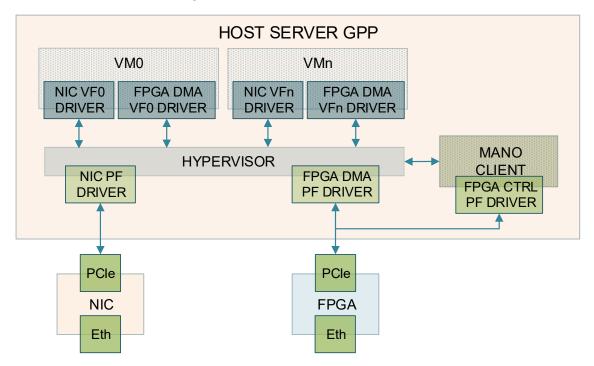

Figure 5 presents the CRUN server architecture, depicting its most relevant components. The main hardware components are the host GPP, the PCIe-attached NIC, and the optional PCIe attached FPGA accelerator.

Figure 5. Network architecture in CRUN.

Figure 6. Server architecture in CRUN.

The host GPP is running a hypervisor and management and orchestration client application on top of a host Operating System (OS). The hypervisor creates and manages VMs and utilizes SR-IOV (Single Root Input/Output Virtualization) to provide the VMs virtual functions to access the PCIe physical functions. The hypervisor is in turn managed by the MANO client application.

The MANO client is managing the host OS, the hypervisor and the FPGA, and is a part of a larger centralized management application. A more detailed description of the management and orchestration software used in CRUN is given in [55].

The FPGA, attached to the host GPP via PCIe, is an optional hardware accelerator component. Its main data plane interface is the Ethernet network interface, but CRUN defines an additional possibility of Direct Memory Access (DMA) to and from VMs on the host server via PCIe. The main purpose of the PCIe connection, and the only purpose, in the scope of this work, is to provide a control plane interface for flow control of the networking logic on the FPGA. The FPGA itself is functioning as a network-attached hardware accelerator.

The CRUN project also set performance requirements for the FPGA accelerators:

- The FPGA networking logic cannot limit the throughput of the accelerator and it must operate at line rate.

- The FPGA networking logic latency must be in the scale of microseconds, with the maximum of 8µs.

The maximum latency for the networking logic originates from a neural network inference acceleration trial done with CRUN, presented in [56]. A goal in the trial was to achieve an ultra-low latency of 20µs to 40µs in the software level. In the trial, this set the requirement for the latency on the FPGA hardware between 10µs and 30µs. The largest latency on the FPGA came with the baseline implementation of the neural network, itself causing a latency of roughly 22µs. This left the networking logic with 8µs to meet the maximum limit of 30µs hardware latency.

### 6.2 Top level FPGA design

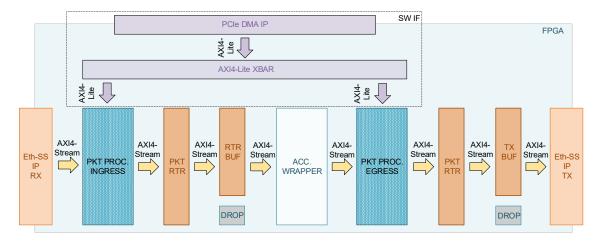

The top level of the FPGA design used in this work is depicted in the figure 6. The implementation, excluding the accelerator, is designed to operate at line rate and with minimal latency. Throughout this thesis, the design excluding the accelerator is generally referred to as the shell design. In figure 6, the blocks independent of the shell design variant are coloured as orange. The software interface (SW IF) section, consisting of the PCIe DMA IP and the AXI4-Lite interconnection (AXI4-Lite XBAR) and its related AXI4-Lite interfaces are present only in the full P4 implementation with the software interface, whereas the packet processor blocks (PKT PROC. INGRESS and PKT PROC. EGRESS) coloured with blue are present in each variant, but with different implementations.

The data plane interface in and out of the FPGA is implemented with a Xilinx Ethernet Subsystem (Eth-SS) IP [57] for receive (RX) and transmit (TX) operations. On the RX side, the IP converts the incoming physical layer (PHY) traffic into AXI4-Stream (AXI4-S) protocol. The IP is configured for the speed of 10 Gigabits per second, with the clock frequency of 161MHz, and a data bus width of 64 bits. This bus width is used in the AXI4-

S interfaces throughout the design, and the majority of the design operates in the same clock domain, with only the SW IF segment functioning within a clock domain dictated by the PCIe DMA IP.

The ingress packet processor parses the incoming packets' headers and does possible lookup operations and header modifications before forwarding the data to the packet router (PKT RTR) as AXI4-Stream traffic, alongside a metadata bus carrying possible packet-specific information for following blocks, as well as a route identifier (ID).

#### Figure 7. Top level accelerator shell design implementation on the FPGA.

The packet router connects the AXI4-Stream interface to either the router buffer (RTR BUF) or drops the packet, based on the received route ID. The RTR BUF component is a BRAM FIFO (First In, First Out) buffer generated with the Vivado FIFO Generator IP [58], and is purposed for migitating backpressure from the accelerator, ensuring that only complete packets are forwarded.

The accelerator wrapper, in this work, does not contain any acceleration logic, and its entity consists of direct connections from its inputs to outputs, as the evaluation is focused on the shell design.

The egress packet processor does use-case dependent protocol parsing and header modifications, and forwards the packet to the output packet router. This packet router and the buffer component connected to it are instances of the same IPs as the packet router and the FIFO buffer described earlier.

Finally, following the buffer, the outoing packet is converted from AXI4-Stream into PHY by ETH-SS IP TX, and sent out from the FPGA.

For the control plane, the FPGA is connected to software via PCIe, with the Xilinx DMA (XDMA) IP [59] converting the PCIe procotol into AXI4-Lite protocol. The AXI4-Lite interfaces are operating in a clock domain of 125MHz. The XDMA AXI4-Lite interface is

connected to the ingress and egress packet processors with an AXI4-interconnect IP [60], which maps certain address segments into separate AXI4-Lite interfaces. This design segment is only present in the P4 implementation with the software interface, and is used there for dynamic table updates for the lookup engines in the packet processors.

#### 6.3 Use case description

The chosen application for the packet processors is VTEP termination, meaning VxLAN decapsulation in the ingress, and VxLAN encapsulation in egress. In addition to this, the packet processors are inspecting and modifying the protocol headers underlaying the VxLAN encapsulation. This depicts the accelerator to function in VM, or VNF context, while the broader system is operating in cloud infrastructure context. More about VxLAN can be found in [61].

| VxLAN encapsulation headers:<br>Cloud-infra context |               |               |              |       |                   | ner header<br>F/VM cont |               |              |         |

|-----------------------------------------------------|---------------|---------------|--------------|-------|-------------------|-------------------------|---------------|--------------|---------|

| 14 B                                                | 4 B           | 20 B          | 8 B          | 8 B   | 14 B              | 4 B                     | 20 B          | 8 B          | N B     |

| Outer<br>Ethernet                                   | Outer<br>VLAN | Outer<br>IPv4 | Outer<br>UDP | VxLAN | Inner<br>Ethernet | Inner<br>VLAN           | Inner<br>IPv4 | Inner<br>UDP | Payload |

*Figure 8.* Protocol stack supported by the packet processors. Fixed header lengths in bytes (B).

The set of networking protocol headers supported and processed by the packet processors are visible in the figure 7. For the data (payload in figure 7) to reach the accelerator in the design, it must be included in a User Datagram Protocol (UDP) packet. This UDP packet must in turn be encapsulated in an Internet Protocol version 4 (IPv4) packet and contained inside an Ethernet frame with an optional VLAN tag. In figure 7, the headers of these protocols are shown as the inner headers. In case of VxLAN encapsulated by a VxLAN header, an outer UDP header, an outer IPv4 header and an outer Ethernet header with an optional VLAN tag. In the following sections, the operations of the packet processors are divided into two contexts: The Cloud Infrastructure (Cloud-infra) context, which includes the operations related to the VxLAN encapsulation headers, and the VNF (or VM) context, which includes the operations related to the inner headers.

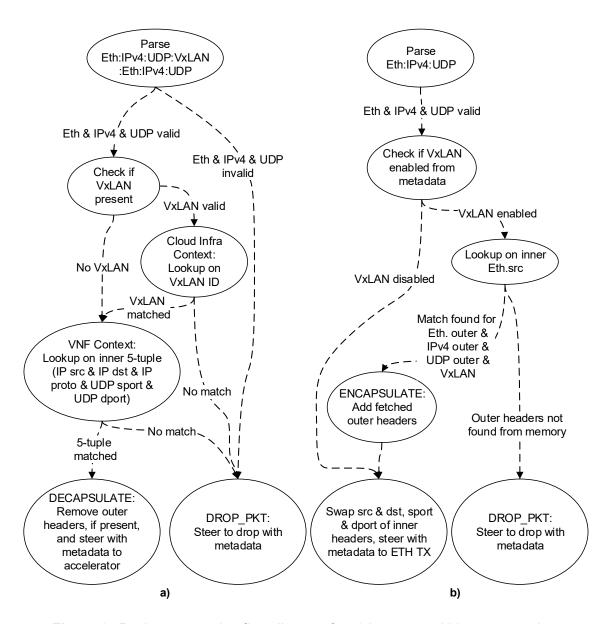

The processing flow of the packet processors is described in the figure 8, where the figure 8 a) describes the ingress operations, and 8 b) the operations in the egress packet processor.

The ingress side operation begins with protocol parsing, starting from the outer headers. Once the parsing reaches the UDP header, the destination port field is checked. If the field holds the value 4789, the parsing continues to VxLAN and inner headers. If the VxLAN and inner headers are parsed successfully, the processing starts in the cloud infrastructure context. If the outer UDP destination port value differs from 4789, the parsing ends and the processing starts directly in the VNF context.

In cloud infrastructure context, the VxLAN header field Virtual Network Identifier (VNI) is matched for VNI values in the on-chip memory. If a match is found, the processing moves to VNF context, and if not, the packet is dropped.

In VNF context, a five-tuple lookup operation determines whether the packet is forwarded or dropped. This five-tuple value consists of the values of the following header fields in the innermost headers: IPv4 protocol, IPv4 source and destination addresses, and UDP source and destination ports. If the lookup operation returns a match, and the five-tuple value is found in the on-chip memory, the packet is forwarded. If the packet reached the VNF context through the cloud infrastructure context, the VxLAN encapsulation headers are removed, and a metadata signal is sent out with the packet, indicating that the original packet is to be VxLAN encapsulated in the egress.

The egress processing, similarly to ingress processing, begins with protocol parsing. If the parsing of the inner headers is successful, the processing checks the metadata for information if the original packet in ingress had VxLAN encapsulation. If the inner headers are not parsed successfully, the packet is dropped.

If the metadata indicates that VxLAN encapsulation was indeed present in the original packet received in ingress, a lookup operation is initiated with the source address of the Ethernet header. These source addresses are saved as keys in the on-chip memory as key-value pairs where the return value is a set of outer headers (Ethernet, VLAN, IPv4, UDP and VxLAN). If the lookup results in a match, these returned headers are used to re-encapsulate the packet. If the on-chip memory is missing a configuration for a particular Ethernet source address, and a match is not found, the packet is dropped.

Finally, if the packet has not been set to be dropped, the innermost headers are modified with a swap operation. This operation swaps the Ethernet source and destination addresses, IPv4 source and destination addresses, and the UDP source and destination ports.

*Figure 9.* Packet processing flow diagram for a) ingress and b) egress packet processors.

## 7. IMPLEMENTATION

This chapter describes the hardware design steps from specification to testing which were gone through in this work and presents the design architectures which were created to implement the functionality based on the use case description in chapter 8.2. Figure 10 pictures the design steps on a generic level to apply to all three design variants.

variants.