Jere Miettinen

# HIGH-LEVEL SYNTHESIS IMPLEMENTA-TION OF HEVC MOTION ESTIMATION ON FPGA

Master of Science Thesis Information Technology and Communication Sciences Ass. Prof. Jarno Vanne Postdoc. Alexandre Mercat April 2020

#### ABSTRACT

Jere Miettinen: High-Level Synthesis Implementation of HEVC Motion Estimation on FPGA Master of Science Thesis Tampere University Master's Degree Programme in Electrical Engineering April 2020

The need for transmitting high quality videos fast and effectively has increased in the recent years. Main reason for that is the increase in resolutions and frame rates, and the growing use of mobile devices and streaming. High Efficiency Video Coding (HEVC) is the latest video coding standard designed to respond those needs. HEVC achieves better compression compared to previous standards without compromising the video quality.

High-Level Synthesis (HLS) tools bring automation to the complex design processes and the designer can focus more on the algorithm functionality. The HLS design flow is on a higher abstraction layer compared to the traditional hardware design flows. Programming language such as C can be used instead of one of the hardware description languages (HDL) such as VHDL or Verilog. HLS was chosen for this Thesis, instead of traditional register transfer level (RTL) design, for faster and easier development.

Kvazaar is an open source HEVC video encoder developed at Tampere University. The encoding is done by removing temporal or spatial data redundancy. Motion estimation (ME) aims to reduce the temporal data redundancy. ME can be done using one of the various block matching algorithms (BMA), such as full search (FS) or hexagon-based search (HEXBS). The main goal of this Thesis was to evaluate Kvazaar's ME algorithms and then implement a ME accelerator on hardware using HLS. The accelerator was aimed for a Field Programmable Gate Array (FPGA) circuit.

ME is one of the most complex parts of the encoding and takes a significant amount of time of the whole encoding process and it is a good candidate for HW acceleration. FS algorithm was chosen for hardware acceleration in this Thesis and the hardware implementation was done using Catapult-C HLS tool. The accelerated algorithm was synthesized to Arria 10 FPGA platform and integrated as a part of Kvazaar's encoding process.

The synthesized Accelerator works on 150 MHz frequency and takes 18% of the available logic resources on Arria 10. It uses 6% of the available M20K memory elements and 6% of the platform's registers. The Accelerator achieved ×66.26 speedup compared to the software only algorithm. Once integrated to the Kvazaar's encoding process the speedup was still ×1.94. The drop in the speedup can be explained with the throughput limitations of the PCIe bus used in the communication between Kvazaar and the Arria 10 platform.

Keywords: High Efficiency Video Coding (HEVC), motion estimation (ME), High-Level Synthesis (HLS), Kvazaar, Field Programmable Gate Array (FPGA)

The originality of this thesis has been checked using the Turnitin OriginalityCheck service.

### TIIVISTELMÄ

Jere Miettinen: HEVC-videokoodekin liikkeentunnistuksen toteutus FPGA-piirille C-kielestä syntetisoimalla Diplomityö

Tampereen yliopisto Sähkötekniikan diplomi-insinöörin tutkinto-ohjelma Huhtikuu 2020

Tarve siirtää hyvälaatuista videokuvaa nopeasti ja tehokkaasti on lisääntynyt viime vuosina. Suurimmat syyt tähän ovat kasvaneet resoluutiot ja kuvataajuudet sekä lisääntynyt mobiililaitteiden käyttö ja striimauksen tarve. High Efficiency Video Coding (HEVC) on viimeisin videonpakkausstandardi, joka on suunniteltu vastaamaan edellä mainittuihin tarpeisiin. HEVC vähentää pakkauskompleksisuutta verrattuna aiempiin standardeihin tinkimättä kuitenkaan laadusta.

High-Level Synthesis (HLS) työkalut tuovat automaatiota monimutkaiseen suunnitteluprosessiin ja suunnittelija voi keskittyä paremmin algoritmin toiminnallisuuteen. HLS suunnitteluvuo on korkeammalla tasolla verrattuna perinteiseen RTL (register transfer level) suunnitteluun. Korkeamman tason ohjelmointikieltä, kuten C:tä, voidaan käyttää laitteistoläheisten kielten, kuten VHDL:n ja Verilogin, sijaan. Tässä työssä käytetään HLS työkaluja RTL työkalujen sijaan nopeamman ja helpomman kehityksen vuoksi.

Kvazaar on avoimen lähdekoodin HEVC videokoodekki, joka on kehitetty Tampereen Yliopistossa. Videon pakkaaminen perustuu joko ajallisen tai spatiaalisen dataylimäärän vähentämiseen. Liikkeenestimointi on ajallinen menetelmä ja sitä tehdään käyttämällä yhtä monista *block matching* algoritmeista (BMA), kuten *full search* (FS) tai *hexagonbased search* (HEXBS). Tämän työn päätavoitteena oli valita liikkeenestimointialgoritmi kiihdytettäväksi ja suunnitella ja toteuttaa kiihdytin ohjelmoitavalle logiikka piirille (FPGA) käyttäen HLS työkaluja.

Liikkeenestimointi on yksi pakkauksen laskennallisesti työläimmistä osista ja vie huomattavan osan koko pakkausajasta ja siksi se vaatii kiihdyttämistä. Kiihdytettäväksi algoritmiksi valittiin FS ja se toteutettiin käyttäen Catapult-C HLS työkalua. Kiihdytetty algoritmi syntetisoitiin Arria 10 piirille ja liitettiin osaksi Kvazaarin pakkausprosessia.

Syntetisoitu kiihdytin toimii 150 MHz taajuudella ja vie 18% käytettävissä olevasta logiikasta Arria 10 piirillä. Se käyttää 6% M20K muistilohkoista ja 6% käytettävissä olevista rekistereistä. Kiihdytin saavutti 66.26 kertaisen suhteellisen nopeuden verrattuna puhtaasti CPU (central processing unit) pohjaiseen algoritmiin. Kun kiihdytin oli liitetty Kvazaariin, suhteellinen nopeutus oli edelleen 1.94 kertainen. Pudotusta suhteellisessa nopeutuksessa selittää Kvazaarin ja kiihdyttimen kommunikointiin käytetyn PCIe väylän suorituskykyrajoitukset.

Avainsanat: High Efficiency Video Coding (HEVC), liikkeenestimointi, High-Level Synthesis (HLS), Kvazaar, Field Programmable Gate Array (FPGA)

Tämän julkaisun alkuperäisyys on tarkastettu Turnitin OriginalityCheck –ohjelmalla.

# PREFACE

This Master of Science Thesis was written as a part of research in the Faculty of Information Technology and Communication Sciences at Tampere University.

I would like to thank my examiners, Jarno Vanne and Alexandre Mercat for their input and guidance to write this Thesis. I want also to thank Panu Sjövall and my other coworkers who helped me during my work.

Finally, I would like to thank my family and Sabrina for their endless support during my work and writing.

Tampere, 27<sup>th</sup> April 2020

Jere Miettinen

# CONTENTS

| INTF | RODUCTION                                                                                                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BAC  | KGROUND                                                                                                                                                                                    | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.1  | High-Level Synthesis (HLS)                                                                                                                                                                 | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 2.1.1 HLS design flow with Catapult-C                                                                                                                                                      | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 2.1.2 Field Programmable Gate Arrays (FPGAs)                                                                                                                                               | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 2.1.3 Arria 10 FPGA platform                                                                                                                                                               | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.2  | High efficiency video coding (HEVC)                                                                                                                                                        | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 2.2.1 Kvazaar HEVC Encoder                                                                                                                                                                 | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 2.2.2 FPGA Acceleration of Kvazaar Intra Encoder                                                                                                                                           | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2.3  | Related work                                                                                                                                                                               | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| INTE | ER PICTURE PREDICTION IN HEVC                                                                                                                                                              | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3.1  | Block partitioning                                                                                                                                                                         | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3.2  | Motion estimation and compensation                                                                                                                                                         | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3.3  | Block matching algorithms (BMA)                                                                                                                                                            | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | 3.3.1 Full search (FS)                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      | 3.3.2 Fast block matching algorithms                                                                                                                                                       | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3.4  | Inter picture prediction modes                                                                                                                                                             | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| MET  | HODOLOGY                                                                                                                                                                                   | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4.1  | Coding efficiency                                                                                                                                                                          | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4.2  | Test materials                                                                                                                                                                             | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4.3  | Design method                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| HAR  | DWARE SPECIFICATION                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5.1  | Algorithm selection for hardware acceleration                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5.2  | Algorithm limiting                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5.3  | Design limitations                                                                                                                                                                         | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5.4  | Memory limitations                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ACC  | ELERATOR DESIGN                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6.1  | Architecture overview                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6.2  | Read and write blocks                                                                                                                                                                      | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6.3  | Calculation block                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6.4  | Memory indexer                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| PERI | FORMANCE                                                                                                                                                                                   | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7.1  | Implementation results                                                                                                                                                                     | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | 7.1.1 Catapult-C                                                                                                                                                                           | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | 7.1.2 Synthesis on Quartus                                                                                                                                                                 | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | 7.1.3 Encoding speedup                                                                                                                                                                     | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7.2  | Comparison with related work                                                                                                                                                               | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7.3  | Discussion                                                                                                                                                                                 | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| CON  | ICLUSION                                                                                                                                                                                   | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | BAC<br>2.1<br>2.2<br>2.3<br>INTI<br>3.1<br>3.2<br>3.3<br>3.4<br>MET<br>4.1<br>4.2<br>4.3<br>HAR<br>5.1<br>5.2<br>5.3<br>5.4<br>ACC<br>6.1<br>6.2<br>6.3<br>6.4<br>PER<br>7.1<br>7.2<br>7.3 | 2.1.1       HLS design flow with Catapult-C.         2.1.2       Field Programmable Gate Arrays (FPGAs)         2.1.3       Arria 10 FPGA platform         2.2       High efficiency video coding (HEVC)         2.2.1       Kvazaar HEVC Encoder         2.2.2       FPGA Acceleration of Kvazaar Intra Encoder         2.3       Related work         INTER PICTURE PREDICTION IN HEVC         3.1       Block partitioning.         3.2       Motion estimation and compensation         3.3       Block matching algorithms (BMA)         3.3.1       Full search (FS)         3.3.2       Fast block matching algorithms.         3.3.1       Full search (FS)         3.3.2       Fast block matching algorithms.         3.4       Inter picture prediction modes.         METHODOLOGY       4.1         Coding efficiency       4.2         4.3       Design method.         HARDWARE SPECIFICATION       5.1         Algorithm selection for hardware acceleration         5.2       Algorithm limiting.         5.3       Design limitations         5.4       Memory limitations         6.2       Read and write blocks         6.3       Calculation block.      < |

# LIST OF SYMBOLS AND ABBREVIATIONS

| AI            | All Intra                                 |

|---------------|-------------------------------------------|

| ALM           | Adaptive Logic Module                     |

| Avalon-MM     | Avalon Memory-Mapped                      |

| AVC           | Advanced Video Coding                     |

| BD-BR         | Bjøntegaard-Delta Bit Rate                |

| BMA           | Block Matching Algorithm                  |

| CMOS          | Complementary Metal Oxide Semiconductor   |

| CPU           | Central Processing Unit                   |

| CTCs          | Common Test Conditions                    |

| CTU           | Coding Tree Unit                          |

| CU            | Coding Unit                               |

| DMA           | Direct Memory Access                      |

| DSP           | Digital Signal Processing                 |

| EPROM         | Erasable Programmable Read Only Memory    |

| FIFO          | First-In-First-Out                        |

| FME           | Fractional Motion Estimation              |

| FPGA          | Field Programmable Gate Array             |

| FPS           | Frames Per Second                         |

| FS            | Full Search                               |

| full HD       | full High Definition                      |

| HDL           | Hardware Description Language             |

| HEVC          |                                           |

| HEXBS         | High Efficiency Video Coding              |

| HDR           | Hexagon-Based Search                      |

| HLS           | High Dynamic Range                        |

|               | High-Level Synthesis<br>HEVC test Model   |

| HM            |                                           |

| HSSI          | High-Speed Serial Interface               |

| II            | Initiation Interval                       |

| IME<br>ICT VC | Integer Motion Estimation                 |

| JCT-VC        | Joint Collaborative Team on Video Coding  |

| LAB           | Logic Array Block                         |

| LUT           | Lookup Table                              |

| MAD           | Mean Absolute Difference                  |

| MC            | Motion Compensation                       |

| ME            | Motion Estimation                         |

| MPEG          | Moving Picture Experts Group              |

| MSE           | Mean Square Error                         |

| MV            | Motion Vector                             |

| PCIe          | Peripheral Component Interconnect express |

| PLL           | Phased Locked Loop                        |

| PU            | Prediction Unit                           |

| RAM           | Random Access Memory                      |

| SAD           | Sum of Absolute Differences               |

| SoC           | System-on-Chip                            |

| SRAM          | Static Random Access Memory               |

| TZ            | Test Zone                                 |

| VCEG          | Video Coding Experts Group                |

| VHDL          | VHSIC Hardware Description Language       |

|               |                                           |

VHSIC

# 1. INTRODUCTION

The amount of video in the global networking has been growing fast in the recent years and will take approximately 82% of the whole traffic by the end of 2021 [1]. This is mainly because of the increased resolutions and frame rates, the growth of mobile users, the increased use of *high dynamic range* (HDR) and 360° videos. The streaming has become popular and video calls are established as a part of everyday life. This generates need for transmitting videos as effectively as possible without compromising on the quality.

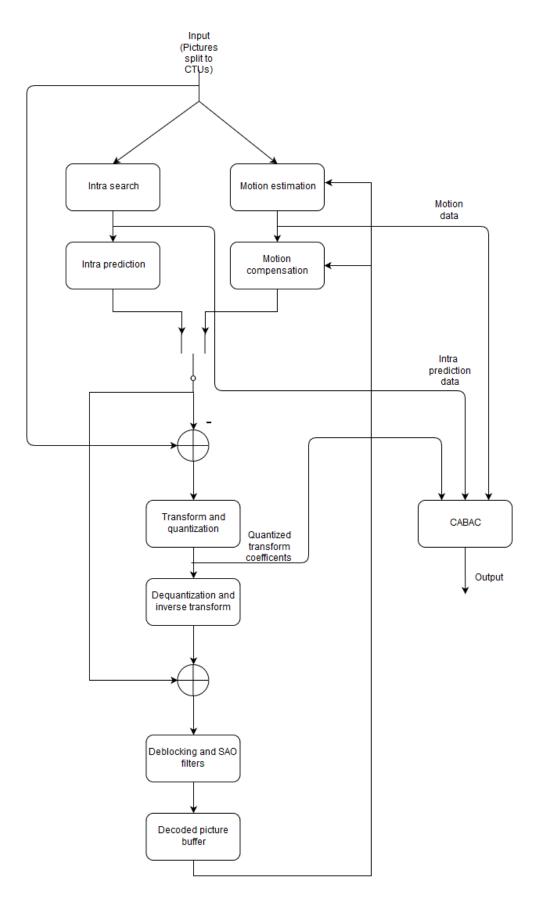

*High Efficiency Video Coding* (HEVC) is the newest video coding standard [2] and is designed to address those needs. HEVC encoders are complex and thus considerable candidates for hardware acceleration. Kvazaar is an open source HEVC video encoder developed as a part of the research in Ultra Video Group at Tampere University [3]. The encoding is done reducing either temporal or spatial data redundancy. *Motion estimation* (ME) aims to reduce the temporal redundancy. It is one of the most computationally heavy parts of Kvazaar encoder and it stands as a starting point for the *Field Programmable Gate Array* (FPGA) acceleration in this Thesis.

*High-Level Synthesis* (HLS) is an alternative to the traditional hardware design. It brings automation to the hardware design flow. The design process is done on a higher abstraction level and the implementation and verification times can be greatly reduced compared to the traditional *register transfer level* (RTL) design. HLS is used in this Thesis to implement a ME accelerator for Kvazaar. The main goals of this Thesis are to choose a suitable ME algorithm to accelerate, design an FPGA accelerator using HLS tools for the chosen algorithm and finally integrate the designed accelerator as a part of Kvazaar's encoding process.

The Thesis is organized as follows: HLS, FPGAs, HEVC, Kvazaar, and related work are introduced in Chapter 2. In Chapter 3, the inter picture prediction and ME in HEVC are discussed. Chapter 4 presents the methodology, such as evaluating tools and design method. Also test materials are discussed. Chapters 5 and 6 are reserved for the hardware specification and implementation, respectively. The results are presented and discussed in Chapter 7. Chapter 8 concludes the Thesis.

# 2. BACKGROUND

This chapter introduces the main topics of this Thesis. Basic background information of High-Level Synthesis (HLS) and its tools, Field Programmable Gate Array (FPGA) circuits, Kvazaar High Efficiency Video Coding (HEVC) encoder and its accelerated intra encoder are given. Related work is also discussed.

#### 2.1 High-Level Synthesis (HLS)

The concept of High-Level Synthesis (HLS) brings more automation to hardware design flow. The main purpose is to generate functioning register transfer level (RTL) description from higher abstraction programming languages [4]. HLS synthesis tools generate synthesizable *hardware description language* (HDL), such as *Very High Speed Integrated Circuit* (VHSIC) *Hardware Description Language* (VHDL) [5] or Verilog, that allows hardware designers to focus on the functionality of the design.

As hardware systems and applications grow bigger and more complex, the design and verification times increase significantly. The cost of using standard RTL development tools becomes too high. HLS promises to reduce design and verification times by needing less detail for the design specifics, e.g. the need for specifying a clock, and automized generation of RTL structures based on the targeted technology [4]. Using HLS, the designs are more generic because of the higher abstraction level. This means that the same algorithm could be easier used on different platforms as HLS takes care of the platform specific design constraints.

An important thing to consider when using HLS is bit accurate data types. This becomes important when modeling hardware directly from C or C++, as they only offer data types with limited widths [4]. Mentor Graphics has developed their own standardized bit accurate data type, which is called Algorithmic-C data types. Another option for the bit accurate data types is SystemC types. However, it has various limitations compared to Algorithmic-C data types, such as slow execution times. Therefore, the Algorithmic-C data types are used in this Thesis.

The most commonly used Algorithmic-C data types are signed and unsigned integers [4]. They allow the designer to model bit vectors with a constant bit width and a sign. Algorithmic-C allows also the use of fixed-point arithmetic with its fixed-point data type. This is something what cannot be done automatically with regular RTL design methods and is a big advantage of HLS. All the basic logical and arithmetical operators are included in the Algorithmic-C standard. The Algorithmic-C offers also a set of built-in methods, such

as slice read, and slice write. These are used to get access to a specific set of bits within a variable. In addition, the bitwise operators are designed so that there is no loss of precision.

The first step of HLS is the analysis of the written algorithm [4]. This step forms the dependencies within the algorithm, and in which order the operations must be executed. The results are illustrated as data flow graphs. The next step is resource allocation where the operators are mapped to the hardware components of the targeted platform. Already at this point, the required area and latency are known. The timing of the designed system is determined in the final step called scheduling. During scheduling, the exact timing of the system is decided. This means deciding which operation to execute in what clock cycle. In practice this means that the HLS tool adds registers to the design between processes according to the assigned clock frequency. The operations are assigned to a specific clock cycle based on the critical path of the design and registers are put in between to reduce delay when needed.

HLS introduces also the concept of loop optimization, which brings parallelism to the design. There are two ways of implementing it, loop pipelining and loop unrolling. Loop pipelining means that a new iteration of a loop can be started before the previous one has finished. Loop pipelining is controlled with *Initiation Interval* (II), which determines how many clock cycles are waited before the next cycle is started. Loop unrolling, on the other hand, means how many parallel duplications there are for the loop. The loops can be fully or partially unrolled. Partial loop unrolling means, that specified number of iterations are started at once and full loop unrolling means that all iterations are started at once.

#### 2.1.1 HLS design flow with Catapult-C

Catapult-C is an HLS platform offered by Mentor Graphics. It makes possible to get RTL logic description automatically from industry-standard C/C++ and SystemC languages [6]. The key features for Catapult-C are functioning RTL, fast verification time and power optimization. It promises 80% less code writing, easier debugging and 80% less verification cost compared to the traditional RTL design. The output from Catapult-C is VHDL and/or Verilog code.

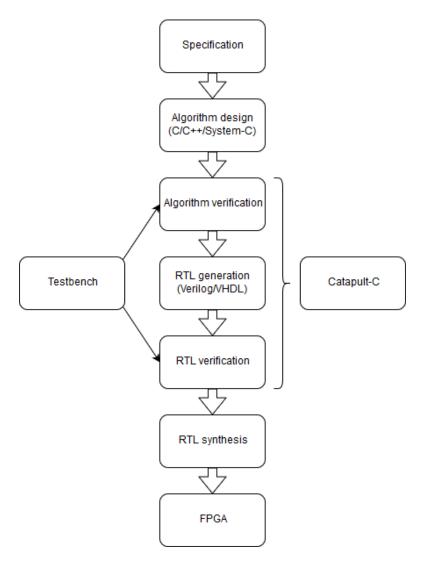

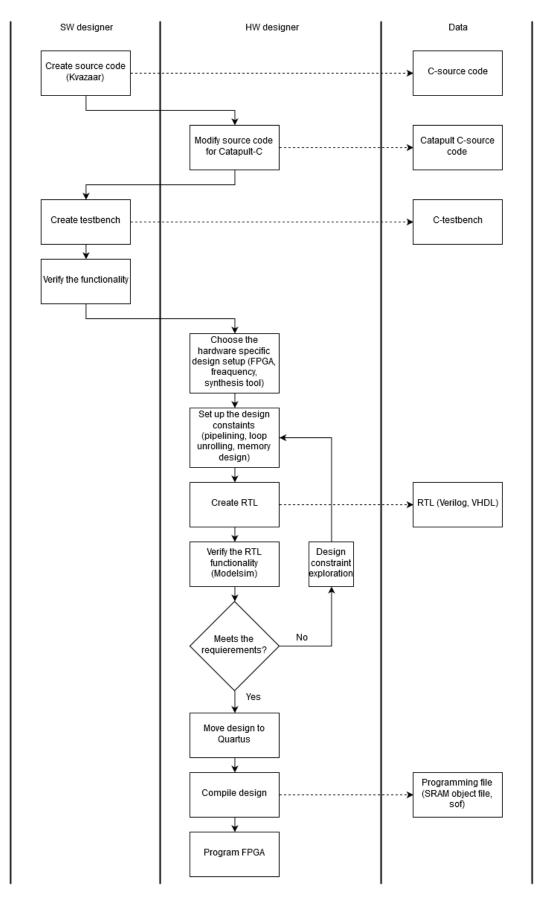

The HLS design flow with Catapult-C is simpler than with traditional RTL design tools. Figure 2.1 illustrates the design flow with Catapult-C tool from the specification of the system to the synthesized hardware on FPGA. The flow is simpler and faster to execute

Figure 2.1 HLS design flow.

than with traditional hardware design flow. The same results as with the traditional hardware design flow can be achieved with HLS in a matter of hours instead of days or weeks.

The flow starts from the specification of the algorithm and its functionality. The untimed algorithm is then written with the chosen high abstraction level programming language. At this stage there are no specifications for clocks and reset signals. The functionality of the design is tested with a test bench, which is written in the same language as the algorithm. Once the functionality is tested, the RTL is generated.

Catapult-C also offers automation for RTL verification [6]. The same test bench used for functionality testing is used also for generating the stimulus and testing the RTL. During the RTL simulation, the RTL functionality is verified against the untimed algorithm. After the verified RTL description is obtained, the VHDL or Verilog code is transferred to the platform specific synthesis tool, i.e. Intel Quartus, and synthesized to the target platform.

```

void accumulator(ac_int<32, true> input[4], ac_int<32, true> &output)

{

ac_int<32, true> accumulate = 0;

for(ac_int<32, true> i = 0; i < 4; i++){

accumulate += input[i];

}

output = accumulate;

}

Listing 2.1 Accumulator example.</pre>

```

Listing 2.1 shows an example of hardware design using Catapult-C. It accumulates the values from the input table and assigns the result to the output variable. The example does not contain control signals, such as clocks or resets, as Catapult-C adds them during the workflow.

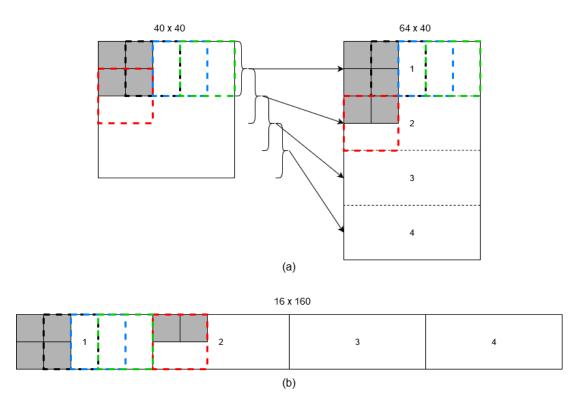

Catapult-C also offers tools to manipulate the memories used in the design [4]. There are three important parameters which are used to simplify the memory architecture, and in the best case, greatly decrease the needed memory accesses. These parameters are word width, block size, and interleave.

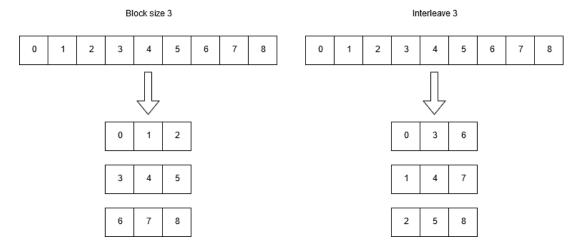

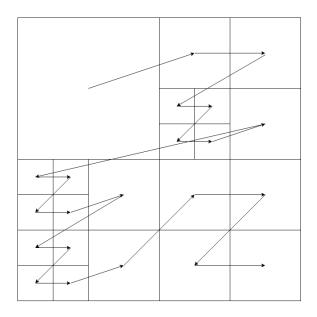

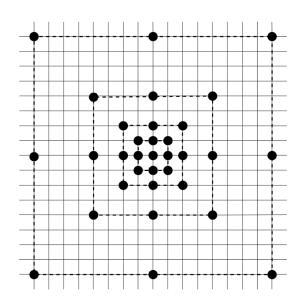

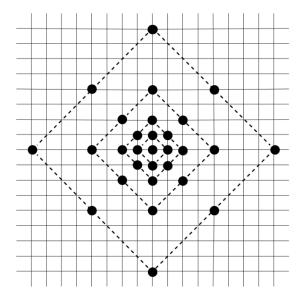

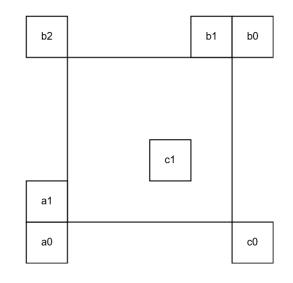

Word width sets the width of each memory location, allowing data to be stored in parallel to the memories [4]. The parameter allows Catapult-C to automatically combine multiple reads or writes to the memory, without any manual coding. Left image on Figure 2.2 illustrates the block size parameter, which determines the number of blocks the memory is divided into. In the example, the block size is set three, which then divides the nine memory locations into three smaller memories, with three memory locations in each.

Right side of Figure 2.2 demonstrates how memory interleaving works. The same memory is now interleaved with three. The memory elements are stored again into three different memories, but this time the order is changed so that every third element is stored into the same memory. Memory interleaving and block size changing gives the designer

Figure 2.2 Block size and interleaving.

possibility to modify easily the designs memory interface. With these tools, parallel memory architectures are possible to implement in reasonable amount of time.

### 2.1.2 Field Programmable Gate Arrays (FPGAs)

Field Programmable Gate Arrays (FPGAs) are programmable silicon circuits. They are used as a part of various kind of systems and applications because of their flexibility, configurability and rather cheap prize [7]. FPGA based systems have also very short development times. These are the main advantages compared to *Application Specific Integrated Circuits* (ASICs). However, re-programmability brings also disadvantages. FPGAs have usually more delay and their power consumption is higher as well as resource usage.

Modern FPGAs are based on three basic programming technologies. These are *static random access memory* (SRAM), anti-fuse and flash [8]. Programming an anti-fuse-based FPGA is done by applying current and high voltage pulse to the device. The biggest disadvantage with anti-fuse technology is that it cannot be reprogrammed but the FPGAs using that technology have usually lower power consumption and are faster.

SRAM technology, on the other hand, uses static memory cells to store the data [7]. However, the data is lost from them when the FPGA is powered down. Another drawback is the needed size of the SRAM cell. One SRAM cell can require up to six transistors while no transistors are needed to use anti-fuse technology and only one transistor is required for flash technology.

Flash technology is relatively new and tries to overcome the problems of the SRAM technology. It is based on *erasable programmable read-only memories* (EPROM). Its biggest advantages compared to the SRAM are the resource usage and that the data is not lost once powered down.

The most widely used programming technology is the SRAM mainly because of the reprogrammability and that it uses the standard *Complementary Metal Oxide Semiconductor* (CMOS) manufacturing process [7]. Thus, there is no need for special development regarding to the programming as it would be the case with flash technology. The major FPGS producers, such as Intel, use SRAM based technologies in most of their FPGAs.

The FPGA circuits are built from logic blocks. These blocks are used for implementing the logical operations, routing, storage and off-chip connections [7]. The architecture of FPGAs is based on a *lookup table* (LUT) or a multiplexer. Each vendor has their proper names and definitions for their technologies, but the basic principle stays the same.

#### 2.1.3 Arria 10 FPGA platform

The FPGA platform used in this Thesis is from Intel's Arria 10 device family. The FPGA device consists of *Logic Array Blocks* (LABs), which are its basic building blocks, memory blocks and various *digital signal processing* (DSP) blocks [9]. The LAB blocks are formed with several *Adaptive Logic Modules* (ALM) which perform logical functions and calculations. Fundamentally ALMs are based on LUTs. In addition, up to the quarter of the LAB blocks can be used as a memory (MLAB). The external communication with PC is done via *Peripheral Component Interconnect express* (PCIe) [10] bus.

| Device | Arria 10 |  |

|--------|----------|--|

| ALMs   | 427200   |  |

| DSP    | 1518     |  |

| LAB    | 42720    |  |

| M20K   | 2713     |  |

| PCie   | Gen2:x8  |  |

| PLL    | 144      |  |

Table 2.1 Arria 10 FPGA overview.

The specific board used in this Thesis is the Arria 10 GX FPGA Development Kit. Table 2.1 lists the main characteristics of the platform. Arria 10 is Intel's midrange FPGA platform and has a large amount of ALMs LABs and DSPs in use. It supports the 1<sup>st</sup>, 2<sup>nd</sup> and 3<sup>rd</sup> generation PCIe busses. The characteristics make the platform suitable for heavy calculations which are needed to design an accelerator.

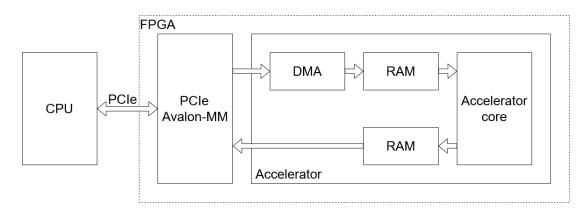

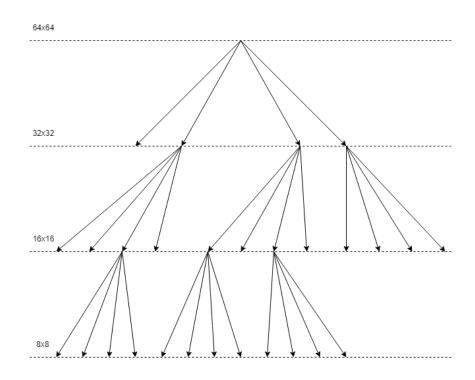

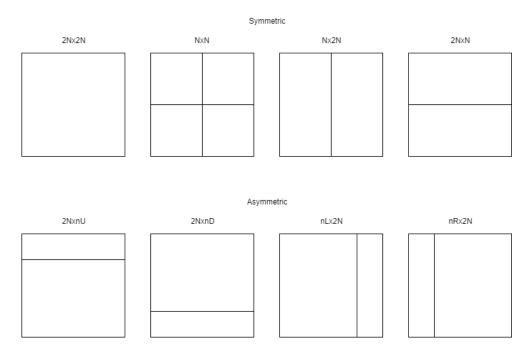

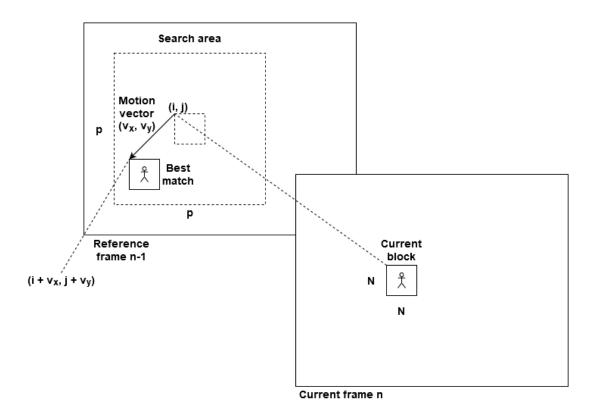

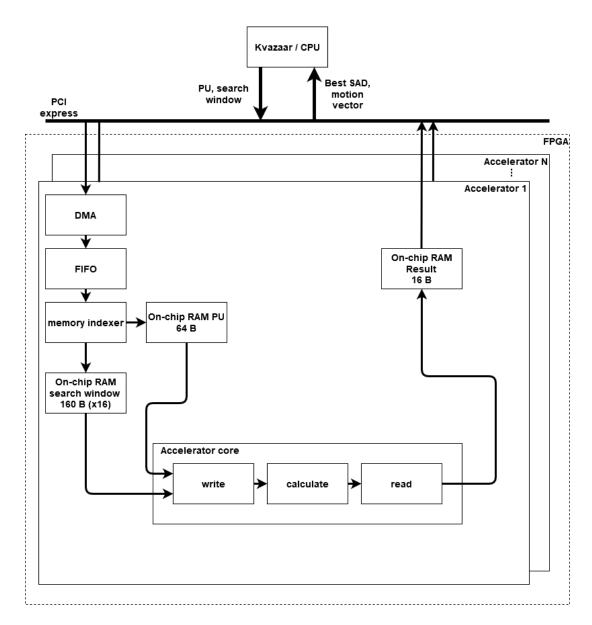

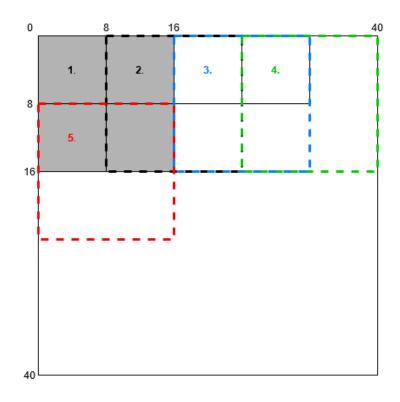

The Arria 10 platform in this Thesis is configured to use Gen 2 PCIe bus with 8 lanes for data transfer between FPGA and the *central processing unit* (CPU) of the computer. The Intel PCIe IP on the FPGA runs at 250 MHz and uses a 128-bit Avalon bus as its interface. The theoretical maximum throughput for the PCIe bus with the presented settings is 32 Gbit/s.