Ville Eerola

**Design and Silicon Area Optimization of Time-Domain GNSS Receiver Baseband Architectures**

Julkaisu 1582 • Publication 1582

| Tampereen teknillinen yliopisto. Julkaisu 1582<br>Tampere University of Technology. Publication 1582 |  |

|------------------------------------------------------------------------------------------------------|--|

|                                                                                                      |  |

Ville Eerola

# **Design and Silicon Area Optimization of Time-Domain GNSS Receiver Baseband Architectures**

Thesis for the degree of Doctor of Science in Technology to be presented with due permission for public examination and criticism in Festia Building, Auditorium Pieni Sali 1, at Tampere University of Technology, on the 26<sup>th</sup> of October 2018, at 12 noon.

Doctoral candidate: Ville Eerola

Laboratory of Electronics and Communications

Engineering

Faculty of Computing and Electrical Engineering

Tampere University of Technology

Finland

Supervisor: Prof. Jari Nurmi

Laboratory of Electronics and Communications

Engineering

Faculty of Computing and Electrical Engineering

Tampere University of Technology

Finland

Pre-examiners: Dr. Hannu Heusala

FiNoC Design Consulting

Finland

Dr. Jari Syrjärinne HERE Technologies

Finland

Opponents: Prof. Jorma Skyttä

Department of Signal Processing and Acoustics

Aalto University

Finland

Dr. Jari Syrjärinne HERE Technologies

Finland

## **ABSTRACT**

The use of Global Navigation Satellite Systems (GNSSs) in a wide range of portable devices has exploded in the recent years. Demands for a lower cost while expecting longer battery life and better performance are constantly increasing. The general GNSS receiver operation and algorithms are already well studied in the literature, but the hardware architectures and designs have not been discussed in detail.

This thesis introduces a high level gate count estimation method that provides good accuracy without requiring the hardware being fully specified. It is based on developing hierarchical models, which are parameterizable, while requiring minimal amount of information about the silicon technology used for the implementation. The average accuracy has been shown to be 4%.

Three time-domain, real-time GNSS receiver baseband architectures are described with a discussion about various optimization methods for efficient implementation: the correlator, the matched filter, and the group correlator, which is a new architecture combining some of the features of the two first ones.

Four use cases are defined for different GNSS operating modes: Acquisition, tracking, assisted GNSS, and the combination of the first three modes. A comparison is made for receiver basebands including all necessary blocks

ii Abstract

for full functionality to find out which of the three architectures provides the most silicon area efficient implementation.

It is shown that the correlator offers good flexibility, but yields the highest silicon area for acquisition use cases. The matched filter is best suited for the acquisition, but has large overhead when it comes to tracking the signals. The group correlator offers a reasonably good flexibility and area efficiency in all use cases.

The main contributions of the thesis are: Development of domain specific optimizations for GNSS receivers and an accurate gate count estimation method, which are applied for a quantitative comparison of different GNSS receiver architectures. The results show that no single architecture excels in all cases, and the best choice depends on the actual use case.

## **PREFACE**

The work presented in this thesis has been carried out during the years 1999–2017 while being employed in VLSI Solution Oy, u-Nav Microelectronics, Inc., Nokia Oyj, and u-Blox Espoo Oy. The thesis has also been supported by the Alfred Kordelin Foundation.

I wish to express my thanks to my supervisor, Prof. *Jari Nurmi*, for his encouragement, guidance, patience, fruitful discussions, and helpful feedback throughout the work. I would also like to thank the reviewers of this thesis, Dr. Tech. *Jari Syrjärinne* and Prof. *Hannu Heusala* for their helpful feedback.

I would like to thank all my colleagues in the companies I have worked while working on this thesis. I would like to express special gratitude to *Tapani Ritoniemi*, who drove me to try harder to find new solutions to problems that seemed almost impossible at the first glance; *Kim Kaisti*, who was always very enthusiastic about trying out new things and getting them done; and Dr. Tech. *Seppo Turunen* for his insight, inspiring discussions, and example. I also wish to thank my co-authors, *Harri Valio* and Lic. Tech. *Samuli Pietilä*.

Finally, I would like to thank my family and especially my beloved wife, *Sanna* for her support and encouragement during this work.

Hämeenlinna, September 2018 Ville Eerola iv Preface

## TABLE OF CONTENTS

| At  | strac   | t                                        | i   |

|-----|---------|------------------------------------------|-----|

| Pr  | eface   | i                                        | iii |

| Ta  | ble o   | f Contents                               | v   |

| Lis | st of l | Publications                             | ix  |

| Lis | st of l | Figures                                  | xi  |

| Lis | st of   | Tables                                   | iii |

| Lis | st of 2 | Abbreviations                            | ζV  |

| 1.  | Intro   | oduction                                 | 1   |

|     | 1.1     | Research Problem and Scope of the Thesis | 2   |

|     | 1.2     | Main Contributions                       | 5   |

|     | 1.3     | Author's Contribution                    | 6   |

|     |         | 1.3.1 Publications                       | 7   |

|     |         | 1.3.2 Patents                            | 9   |

|     | 1.4     | Thesis Outline                           | 10  |

| 2.  | Intro   | oduction to GNSS Receiver Technology     | 13  |

|     | 2.1     | Global Navigation Satellite Systems      | 13  |

|     | 2.2     | Direct-Sequence Spread-Spectrum Systems  | 6   |

|    | 2.3  | GNSS    | Receivers                                           | 17 |

|----|------|---------|-----------------------------------------------------|----|

|    | 2.4  | GNSS    | Receiver Signal Processing Tasks                    | 21 |

|    |      | 2.4.1   | Signal Acquisition                                  | 21 |

|    |      | 2.4.2   | Signal Tracking                                     | 23 |

|    |      | 2.4.3   | Data Reception                                      | 25 |

|    |      | 2.4.4   | Measurement Processing                              | 26 |

| 3. | Gate | e Count | Estimation                                          | 29 |

|    | 3.1  | Earlier | Work                                                | 29 |

|    | 3.2  | Estima  | ation Method Summary                                | 32 |

|    | 3.3  | Param   | eterized Model Creation                             | 33 |

|    | 3.4  | Estima  | ation Method Flow                                   | 35 |

|    | 3.5  | Gate (  | Count Estimation Accuracy                           | 37 |

|    | 3.6  | Memor   | ry Mapping to a Gate Count Estimate                 | 39 |

|    | 3.7  | Small   | Example                                             | 43 |

| 4. | Base | eband H | Iardware Optimization                               | 47 |

|    | 4.1  | Genera  | al GNSS Receiver Baseband Considerations            | 47 |

|    | 4.2  | Correla | ator                                                | 49 |

|    |      | 4.2.1   | Correlator Functionality                            | 50 |

|    |      | 4.2.2   | Word Length Optimization                            | 53 |

|    |      | 4.2.3   | Time-Multiplexed Correlator Architectures           | 54 |

|    |      | 4.2.4   | Advanced Correlator Functionality                   | 56 |

|    |      | 4.2.5   | Correlator-Based Receiver for Gate Count Comparison | 59 |

|                  | 4.3    | Match    | ed Filter                                                       | 60  |

|------------------|--------|----------|-----------------------------------------------------------------|-----|

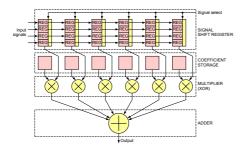

|                  |        | 4.3.1    | Matched Filter Functionality                                    | 61  |

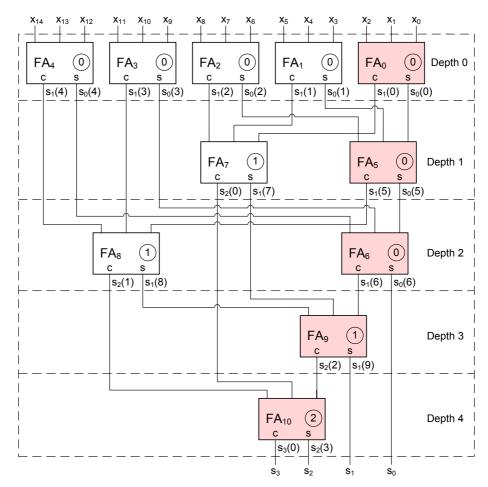

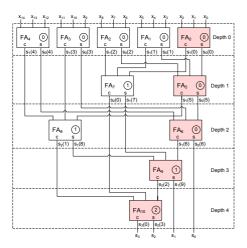

|                  |        | 4.3.2    | Reduction Adder Tree                                            | 63  |

|                  |        | 4.3.3    | Input Multiplexing with 1-bit MF Core                           | 65  |

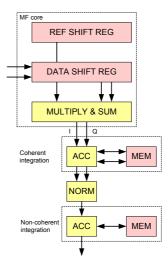

|                  |        | 4.3.4    | Integrating the MF Output Signal                                | 68  |

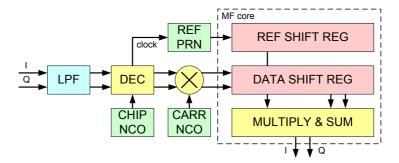

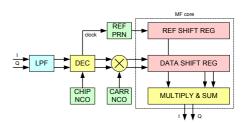

|                  |        | 4.3.5    | Input Decimation to a Multiple of the Chipping Rate             | 69  |

|                  |        | 4.3.6    | MF-Based Receiver for Gate Count Comparison                     | 71  |

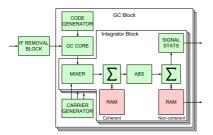

|                  | 4.4    | Group    | Correlator                                                      | 72  |

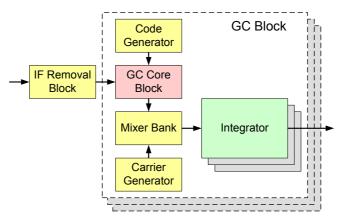

|                  |        | 4.4.1    | Derivation of the GC structure                                  | 73  |

|                  |        | 4.4.2    | GC Implementations                                              | 75  |

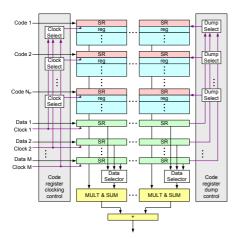

|                  |        | 4.4.3    | $\operatorname{GC-Based}$ Receiver for Gate Count Comparison $$ | 79  |

| 5.               | Arch   | iitectur | e Comparison                                                    | 81  |

|                  | 5.1    | Test C   | l'ases                                                          | 81  |

|                  |        | 5.1.1    | Acquisition                                                     | 82  |

|                  |        | 5.1.2    | Tracking                                                        | 82  |

|                  |        | 5.1.3    | Assisted GPS                                                    | 84  |

|                  |        | 5.1.4    | Worst Case                                                      | 84  |

|                  | 5.2    | Compa    | arison Results                                                  | 85  |

| 6.               | Cone   | clusions | s and Future Work                                               | 89  |

| Bi               | bliogr | aphy     |                                                                 | 93  |

| $\mathbf{p}_{i}$ | ıhlicə | tions    | -                                                               | 107 |

## LIST OF PUBLICATIONS

This thesis is based on the following papers published in open literature. In the text, these publications are referred to as [P1], [P2],..., and [P6] and are appended in the concluding half of the thesis.

- [P1] Ville Eerola and Jari Nurmi, "Correlator Design and Implementation for GNSS Receivers," in NORCHIP, 2013, Nov 2013.

- [P2] Ville Eerola, "Rapid Parallel GPS Signal Acquisition," in Proceedings of the 13th International Technical Meeting of the Satellite Division of The Institute of Navigation (ION GPS 2000), Salt Lake City, UT, Sep. 2000, pp. 810–816.

- [P3] Ville Eerola, "Optimizing Matched Filters for GNSS Receivers," in 2017 International Conference on Localization and GNSS (ICL-GNSS). IEEE, 2017.

- [P4] Ville Eerola, Samuli Pietilä, and Harri Valio, "A Novel Flexible Correlator Architecture for GNSS Receivers," in *Proceedings of the 2007 National Technical Meeting of The Institute of Navigation (ION NTM 2007)*, San Diego, CA, Jan. 2007, pp. 681–691.

- [P5] Ville Eerola and Jari Nurmi, "High-level parameterizable area estimation modeling for ASIC designs," *Integration, the VLSI Journal*, vol. 47, no. 4, pp. 461–475, Sep. 2014.

- [P6] Ville Eerola and Jari Nurmi, "Area Estimation of Time-Domain GNSS Receiver Architectures," in 2014 International Conference on Localization and GNSS (ICL-GNSS). IEEE, 2014.

# LIST OF FIGURES

| 1  | Taxonomy of GNSS receiver implementations           | 4  |

|----|-----------------------------------------------------|----|

| 2  | Block diagram of DSSS transmission system           | 16 |

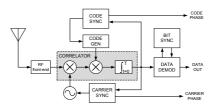

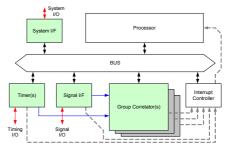

| 3  | Generic GNSS receiver block diagram                 | 18 |

| 4  | Diagram of GNSS receiver channel                    | 19 |

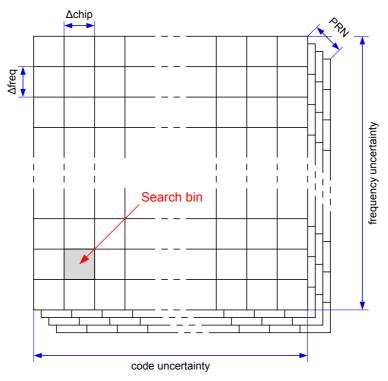

| 5  | Visualization of the acquisition space              | 22 |

| 6  | Generic code tracking loop                          | 24 |

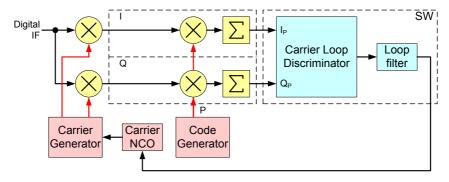

| 7  | Generic carrier tracking loop                       | 25 |

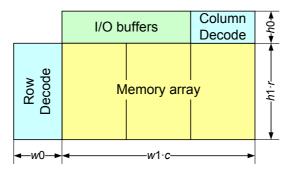

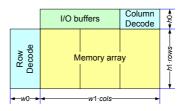

| 8  | Floorplan of embedded SRAM                          | 41 |

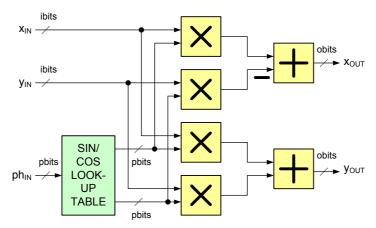

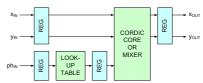

| 9  | Schematic picture showing the complex mixer         | 43 |

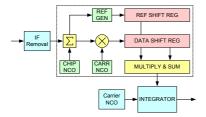

| 10 | Common integrator block for gate count comparison   | 50 |

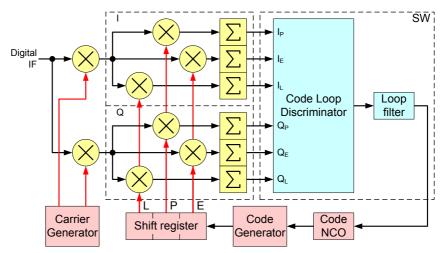

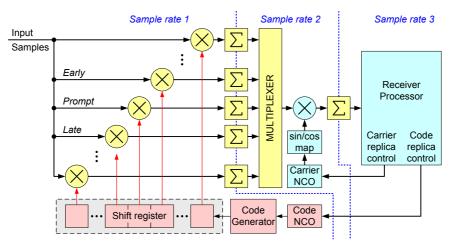

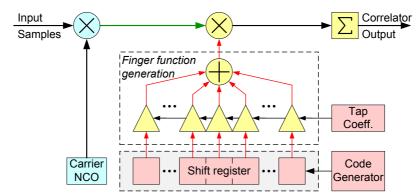

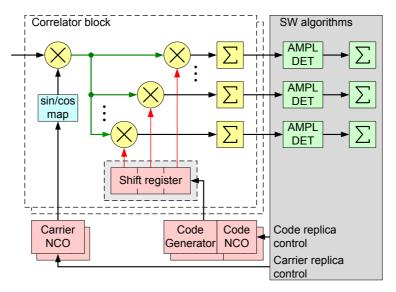

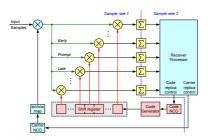

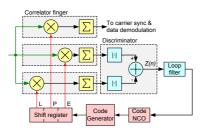

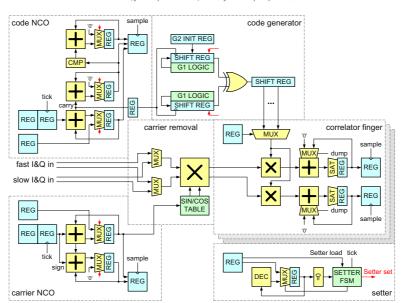

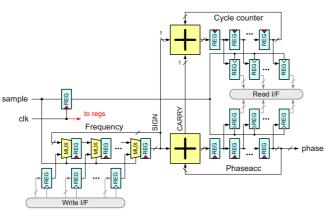

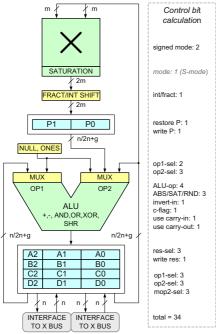

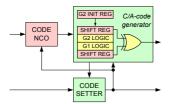

| 11 | Diagram of GNSS receiver channel                    | 51 |

| 12 | Traditional correlator channel architecture         | 52 |

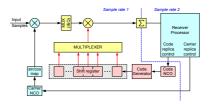

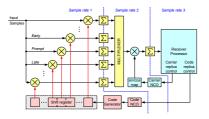

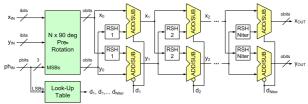

| 13 | Rearranged correlator                               | 55 |

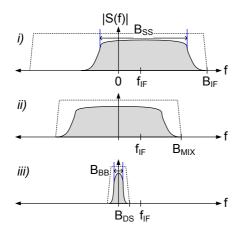

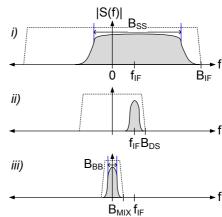

| 14 | Signal spectra within correlators                   | 56 |

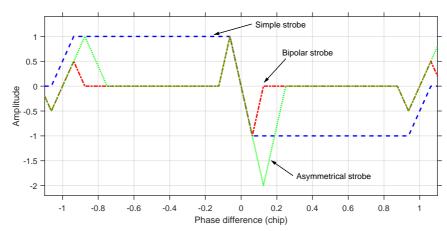

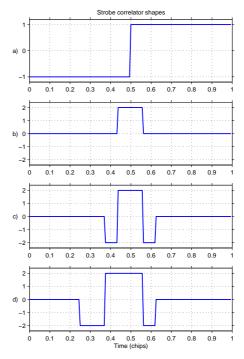

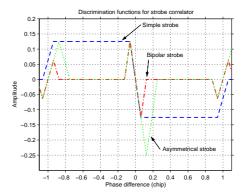

| 15 | Strobe correlator discriminator examples            | 58 |

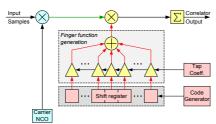

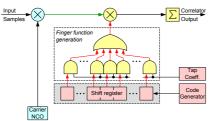

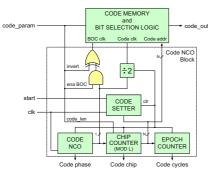

| 16 | Correlator finger function implementation           | 58 |

| 17 | Correlator-based receiver for gate count comparison | 60 |

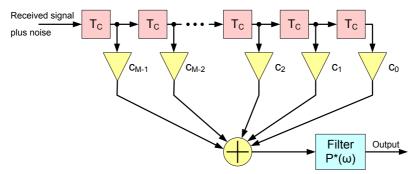

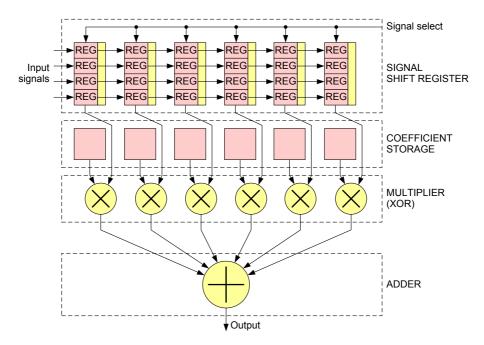

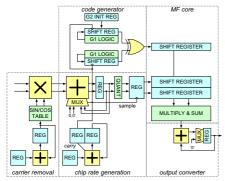

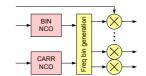

| 18 | Tapped delay line implementation of MF          | 61 |

|----|-------------------------------------------------|----|

| 19 | 15-input binary reduction adder                 | 64 |

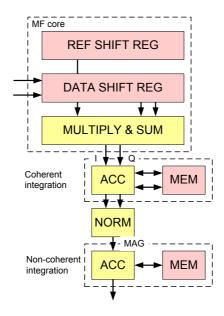

| 20 | Multiplexed MF input                            | 66 |

| 21 | Post-MF integration                             | 69 |

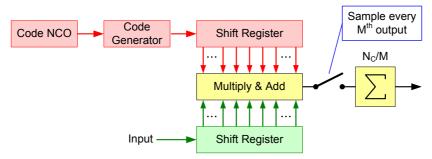

| 22 | MF input decimation                             | 70 |

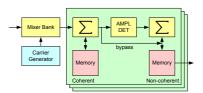

| 23 | MF-based receiver for the gate count comparison | 71 |

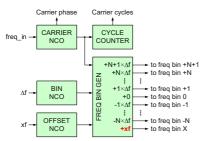

| 24 | Serial-parallel correlator                      | 73 |

| 25 | Modified serial-parallel correlator             | 74 |

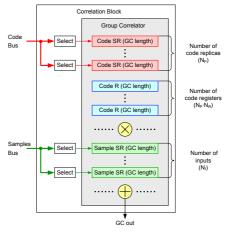

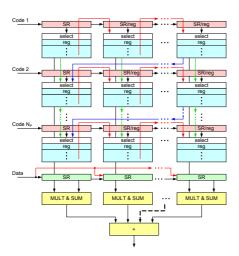

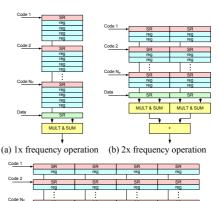

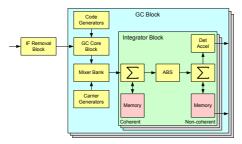

| 26 | Conceptual block diagram of GC                  | 76 |

| 27 | Different configurations of programmable GC $$  | 77 |

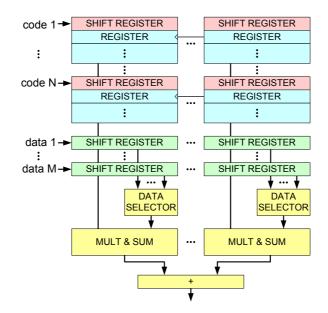

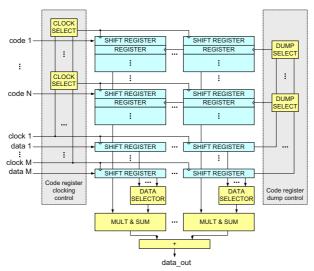

| 28 | Programmable GC with multiple input SR          | 78 |

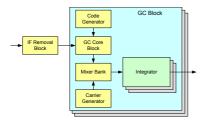

| 29 | GC-based receiver for the gate count comparison | 80 |

# LIST OF TABLES

| 1  | Current GNSS systems                        | 14 |

|----|---------------------------------------------|----|

| 2  | Properties of GNSS signals on L1 band       | 15 |

| 3  | Area estimation references comparison       | 32 |

| 4  | Primitive library for gate count estimation | 34 |

| 5  | Basic block library examples                | 35 |

| 6  | Properties of memories for SRAM model       | 39 |

| 7  | Memory area parameters                      | 41 |

| 8  | Memory model errors                         | 42 |

| 9  | Strobe shapes generation formulas           | 57 |

| 10 | Finger function implementations             | 59 |

| 11 | Acquisition test case parameters            | 83 |

| 12 | Tracking test case parameters               | 83 |

| 13 | A-GPS test case parameters                  | 85 |

| 14 | Receiver area comparison results            | 86 |

## LIST OF ABBREVIATIONS

**3GPP** Third Generation Partnership Project

A-GNSS Assisted GNSS

A-GPS Assisted GPS

ADC Analog to Digital Converter

**AFC** Automatic Frequency Control, an alternative term for FLL

ASIC Application Specific Integrated Circuit

**AWGN** Additive White Gaussian Noise

BB Baseband

BDD Binary Decision Diagram

BER Bit Error Rate

BIST Built In Self-Test

BOC Binary Offset Carrier

BPSK Binary Phase-Shift Keying

CAD Computer Aided Design

CBOC Composite Binary Offset Carrier, a particular

implementation of MBOC  $\,$

**CDFG** Control Data Flow Graph

**CDMA** Code Division Multiple Access

CMOS Complementary Metal Oxide Semiconductor

DFG Data Flow GraphDLL Delay Locked Loop

**DSP** Digital Signal Processing

**DSSS** Direct-Sequence Spread Spectrum

**E911** Enhanced 911

**EDA** Electronic Design Automation

**EU** European Union

FCC Federal Communication Commission

FDMA Frequency Division Multiple Access

**FFT** Fast Fourier Transform

**FLL** Frequency Locked Loop, an alternative term for AFC

FOC Full Operational Capability

FPGA Field Programmable Gate Array

**GC** Group Correlator

**GEO** Geostationary Earth Orbit

GLONASS GLObal'naya NAvigatsionnaya Sputnikovaya Sistema,

GLObal NAvigation Satellite System

**GNSS** Global Navigation Satellite System

**GPS** Global Positioning System

**HW** Hardware

IC Integrated Circuit

ICD Interface Control Document

**IF** Intermediate Frequency

IGSO Inclined Geosynchronous Satellite Orbit

I/O Input and OutputIOV In Orbit Validation

**IP** Intellectual Property, in HW design context, often

interpreted to mean a subdesign licensed from a 3<sup>rd</sup> party

LFSR Linear Feedback Shift Register

**LNA** Low Noise Amplifier

LSB Least Significant Bit

MBOC Multiplexed BOC

MEO Medium Earth Orbit

MF Matched Filter

MSB Most Significant Bit

**NAND** NOT-AND is a logic gate which produces an output which

is false only if all its inputs are true.

**NAND2** Two-input NAND gate

NCO Numerically Controlled Oscillator

NTT Number Theoretic Transform

PLL Phase Locked Loop

PRN Pseudo Random Number

C/A Coarse/Acquisition

PVT Position, Velocity, and Time

QMBOC Quadrature Multiplexed BOC

RAM Random Access Memory

RF Radio Frequency

**ROM** Read Only Memory

RTL Register Transfer Level

SBAS Satellite Based Augmentation System

SDR Software Defined Radio

SIS-ICD Signal-In-Space Interface Control Document

**SNR** Signal to Noise Ratio

SR Shift Register

SRAM Static Random Access Memory

SS Spread Spectrum

**SW** Software

**TMBOC** Time-Multiplexed BOC

**TTFF** Time-To-First-Fix

VHDL VHSIC Hardware Description Language

VHSIC Very High Speed Integrated Circuit, a 1980s United States

government program

## 1. INTRODUCTION

The number of GNSS receivers has exploded with the introduction of personal navigation devices and inclusion of GNSS receivers in mobile phones, which was originally driven by the Federal Communication Commission (FCC) e-Call, Enhanced 911 (E911), mandate [1]. The great potential of ubiquitous location information availability for a wide range of applications ranging from advertising to personal navigation is now taken for granted by the general public. Today, GNSS receivers are becoming a common feature in a wide range of electronic devices ranging from digital cameras to sports watches and tracking tags for valuables. These battery powered, portable consumer devices place great demands on their components for small size, low power consumption and low cost.

Three qualities characterize the performance of any Integrated Circuit (IC): space, time, and energy. Space determines how big the IC is, which is usually also tied to the cost of the device. Time is a measure of how quickly a certain task is performed by it. Finally, any task performed by the IC requires some energy. Energy is the product of power and time. Since time itself is already a performance characteristic, power consumption is often used instead of energy as a performance characteristic of ICs. In any case, these three parameters are not independent, so that it is not possible to optimize just one of the three characteristics without affecting the others. Cost and power consumption are critical figures of merit for any portable

electronic devices, and certainly also for GNSS receivers. The equivalent gate count of digital integrated circuits is an important measure as it affects both the cost and the power consumption [2].

## 1.1 Research Problem and Scope of the Thesis

While the operation and implementation of the GNSS receivers are well researched subjects, there seems not to exist a good analysis of the different receiver architectures and use cases affecting their gate counts. As GNSS receivers are targeted toward cheaper and lower power applications, good understanding of the receiver gate count becomes more important. The performance metric of time is affected most by the selection of the algorithms, which is covered well in the existing literature. However, the architecture selection will also have an effect on the size of the resulting circuit, and estimating the size, will give the algorithm designers the possibility of taking this metric into account when they are selecting the proper architecture for each use case.

The power consumption of a digital circuit can be divided into a static and a dynamic part. The static part is proportional to the gate count and the dynamic part is proportional to the frequency and operating voltage in addition to the gate count. Thus, understanding the gate count of the circuit is important part of understanding the power consumption. However, in order to reduce the scope of the thesis, we will not consider the power consumption as a parameter to be optimized.

The gate count measure used in this thesis is based on the relative cell area of the implemented digital logic compared with the area of a single Two-input NAND gate (NAND2). Common Electronic Design Automation

(EDA) software for logic synthesis and optimization, such as the Synopsys Design Compiler [3], report the total cell area of the resulting design, which can be turned into the relative cell area by dividing the total area by the area of a single NAND2 gate. The definition of the equivalent gate count can be based on either the area or the number of NAND2 gates needed to implement the same logic. There is a slight difference here, as it is more efficient to create the more complex gates directly instead of building them from the NAND2 gates. The selection of the area-based gate count measure in this thesis is pragmatic: The gate area has more direct relationship to the final silicon area, which defines the cost of the silicon. The product cost also includes other parts, such as the package, but they are out of the scope of this thesis.

In this thesis, we will concentrate on the implementation and optimization of digital receiver channels for GNSS receivers. The target of the optimizations is to minimize the silicon area of the resulting implementation while fulfilling the requirements for performance in a given operating scenario. For this purpose we will take a look of three different receiver Baseband (BB) implementations in four separate cases. The comparison results will then show which architecture is best suited for each case, so that we can do a quantitative analysis for their optimality.

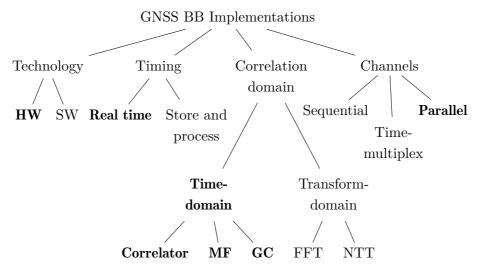

There are several ways the GNSS receivers can be implemented. Figure 1 illustrates some of the possibilities for the baseband implementation. The ones selected for this thesis are marked with a **boldface** font. The first selection to make is to decide whether the baseband algorithms are implemented in Hardware (HW) or Software (SW). Traditionally, all GNSS receivers have been implemented in hardware. The Software Defined Radio (SDR) concept [4] was applied to GNSS receivers only later [5]. We will concentrate on the hardware implementations, since they have a direct

Fig. 1: Taxonomy of various GNSS receiver BB implementations.

relationship with the gate counts, whereas the software implementation gate counts depend in a much more complex way from the architecture. It is possible to implement the GNSS receiver in a way that the incoming signal is stored first in a memory, and the processing will read the samples of there instead of processing them in real time as they arrive from the Analog to Digital Converter (ADC) [6]. The store and process implementation allows processing the data with potentially smaller hardware running at a much higher clock frequency compared with the signal sample rate. The second way is more traditional, since it limits the amount of memory needed, and simplifies the control requirements of the implementation. All the early GNSS receivers, e.g. [7], were implemented to process the signal in real time. We have chosen to restrict ourselves in this thesis to the real-time implementations. The most critical operation in a GNSS receiver baseband is performing a cross-correlation between the received signals and locally generated replicas. The correlation can be done in sample-

by-sample fashion, i.e. in time-domain, or in a transform-domain by first transforming the signal e.g. to frequency-domain using a Fast Fourier Transform (FFT) [8] or Number Theoretic Transform (NTT) [9]. There are a multitude of different ways to do the correlation in time-domain, such as traditional correlator [P1], Matched Filters (MFs) [P2], [P3], and Group Correlator (GC) [P4]. The transform-domain processing is done in a block-wise manner and is more popular with SW and/or store-and-process implementations, so we have chosen to concentrate on time-domain implementations. The channels can be operated in sequential, time-multiplexed or parallel, by making different trade-offs. Sequential and time-multiplexing receivers both dedicate a single channel hardware to the reception of one satellite signal at a time and sequencing the channel for the available signals over time. The difference between these two is in the time spent in tracking one satellite. Sequential receivers would spend at least one second tracking a single satellite at a time whereas time-multiplexed receivers would use just a few milliseconds per satellite [10]. Practically all modern GNSS receivers use a parallel channel implementation which processes the channels in parallel even if internally the hardware would be time multiplexed and we will consider parallel receivers in this thesis. We will take a more detailed look on the correlation implementations in Chapter 4.

## 1.2 Main Contributions

The main contributions of the thesis can be grouped into three main categories and are summed up as follows:

1. Presenting an easy-to-use, accurate method for gate count estimation, which allows parameterizable models to be created for designs at very early stage. The model is built in a hierarchical way from sub-models,

- which can later be refined to improve the accuracy. The method is well suited for architectural exploration before the design has been fully refined.

- 2. Developing domain-specific ways to optimize digital baseband blocks of GNSS receivers using different architectures. These range from arranging operations in optimal order, devising an optimal new way for adding a large amount of numbers, adjusting the sample rate to alter filter length in time, to creating completely new architectures.

- 3. Comparing different GNSS receiver baseband architectures in multiple use cases showing which of the architectures can be implemented in the smallest silicon area for each given case. The comparison was performed for realistic but limited use cases and can be used as an example for selecting the correct implementation for any given use case.

#### 1.3 Author's Contribution

This thesis summarizes the author's work on GNSS receiver development. The research has been done while working on commercial IC projects, and thus has direct relevance in advancing the state of the art in the GNSS industry. The scientific contributions are captured in the published papers. The commercially valuable contributions are also filed and granted as patents. The publications that are part of this thesis and the related patents as well as the author's contributions to each of them are elaborated next.

#### 1.3.1 Publications

Publication [P1] documented ideas for optimizing correlator-based GNSS receivers that were developed earlier by the author and used in commercial GNSS receiver ICs. Many of the ideas presented in this paper were also filed earlier as patents invented by the author. The highlights include discussion on time-multiplexing the correlator hardware and smartly implementing additional signal processing functions within the correlator to reduce the number of the correlator fingers needed. There was a short section about power optimization using time-multiplexing, but the treatment was very superficial and based on some rough estimates about the switching activity of the logic gates. It is not intended to include this part of the manuscript in this thesis as it is out of the scope of it. The author was the main contributor of the paper.

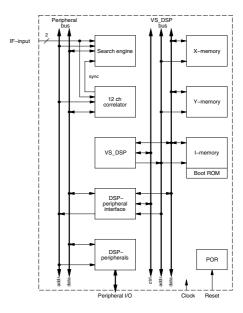

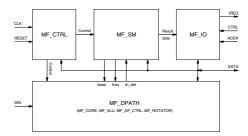

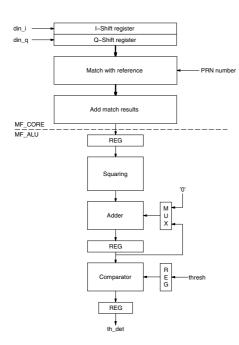

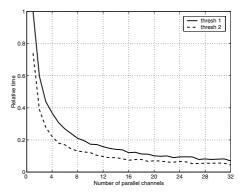

Publication [P2] describes a search unit based on a Matched Filter and optimized for cold start. The work was done when massively parallel search engines for GNSS were not yet commonly considered for commercial receivers. The developed implementation was extremely area-efficient and it enabled searching all Global Positioning System (GPS) satellites in less than two seconds. The author's contribution to the paper was designing and verifying the search unit as well as being the main contributor to the paper.

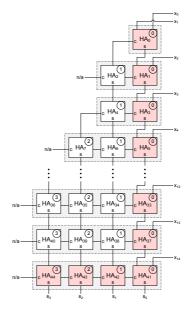

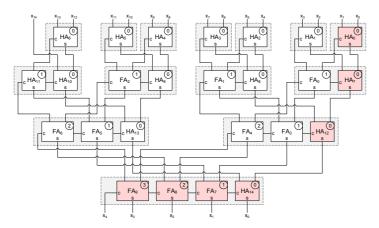

Publication [P3] summarizes the work of the author on optimizing MF-based GNSS receivers which was carried out over the course of several years. The main contributions include a way to optimally implement the adder in the MF where a huge number of inputs need to be added together in very short time, as well as ideas to improve the usability of the MF for GNSS receivers by allowing its apparent length in time to be adjusted according

to the incoming signal and allowing further coherent and non-coherent integration to be applied after the MF. Many of the ideas presented in this paper were filed earlier as patents invented by the author. The author was the sole author of this publication.

Publication [P4] presented the Group Correlator architecture as an alternative for the traditional correlator or MF-based GNSS receivers. Extensive simulations were performed to optimize the design parameters, and simulation results were included to show that the new receiver architecture met the performance targets. The author's contribution was to develop the original GC idea into an implementable hardware block and at the same time generalize the idea for multiple sample rates and input signals. The author was the main contributor of the paper, Samuli Pietilä was responsible for the word-length and sensitivity simulations, and Harri Valio's role was advisory as the father of the GC concept.

Publication [P5] introduced the gate count estimation method that has been used in this thesis to evaluate the silicon area estimates of the different baseband architectures. The key advantage of this method is that it enables parameterized models of the design to be developed at a very early stage of the project. The models can be refined when more accurate information becomes available. The estimation method was applied to a variety of real designs and its accuracy was verified to be extremely good. The estimation method was developed by the author while he was working on the development of multiple commercial GNSS receivers. The author also wrote the paper. The role of the second author (J. Nurmi) was advisory.

Publication [P6] continued to expand the gate count estimation method of [P5] by adding a method for mapping embedded memories to a gate count number. This enabled comparison of designs that used different amounts of

embedded memories in addition to the digital logic. Another contribution was to apply the gate count estimation on different GNSS receiver baseband architectures. The receiver comparison results of this thesis were presented in this publication. The author was responsible for the estimation method development, receiver comparison including developing the test cases, and writing the paper. The role of the second author (J. Nurmi) was advisory.

## 1.3.2 Patents

During the work, which was the basis of this thesis, multiple patents have been filed and granted to protect the inventions. The following patents are related to this thesis but are not included as part of it. The author's contribution was to come up with the original idea and develop it into a practical implementation for the listed patents:

Patent US 6,850,558 [11] shows how to time-multiplex the data path of a correlator to reduce the silicon area and power consumption. These correlator optimizations are explained in more detail in Section 4.2.

Patents US 7,283,582 and US 7,471,719 [12,13] disclose the correlator finger functions, discussed in Section 4.2 This is shown to be a way to reduce the silicon area in the correlator-based GNSS receivers.

Patent US 6,909,739 [14] discloses methods to alter the apparent length in time of the Matched Filter using decimation, and the way to perform coherent and non-coherent integration after the MF. These ideas are reviewed in Section 4.3.

Patents US 7,010,024 and US 7,505,511 [15,16] describe a way to timemultiplex the MF computation by utilizing multiple input shift registers and multiple reference coefficient registers. The time-multiplexing is explained in Section 4.3 in this thesis.

Patent US 7,852,907 [17] presents a practical implementation of a Group Correlator-based GNSS receiver. It also introduces a reconfigurable GC that allows switching between search and tracking modes in the receiver utilizing a single hardware block. The GC idea was invented by Harri Valio and Samuli Pietilä earlier [18], but the development into a practical implementation as well as the extensions to the original idea were the author's responsibility. The GC is discussed in more depth in Section 4.4.

Patent US 8,391,335 [19] discloses the multiple input and output version of the Group Correlator. This patent is a good example of how a patent publication can obscure the original idea of the invention so that it becomes almost indecipherable. The idea behind this patent is explained more clearly in Section 4.4.

## 1.4 Thesis Outline

The thesis is composed of an introductory part and six publications. The introductory part briefly introduces the GNSS receiver technologies to the reader and contains a summary of the material presented in the papers.

Chapter 2 shortly discusses the concepts required for understanding GNSS receivers. The GNSS field is already well established so that we will not explain the basic principles in depth. The reader is referred to any introductory GNSS book, such as [20,21], for these. We will only briefly touch the most important things that are needed for the work presented in this thesis. We start the chapter by giving a quick view of the current GNSS systems. Next, we will take a look on the blocks needed for building a

GNSS receiver and describe what a general GNSS receiver baseband part contains. We will then review the operations that are performed in the receiver digital baseband and the most important performance criteria for them.

Chapter 3 contains an outline of the gate count estimation method developed by the author. The method is later used to compare the baseband architectures using a selection of use cases. This chapter presents a condensed overview of the contents of publications [P5] and [P6]. The chapter begins with a review of the existing literature and then describes the developed method briefly. Next, the mapping of embedded memories into gate count estimates is shortly explained. The chapter concludes with a simple example case which illustrates how the method is used.

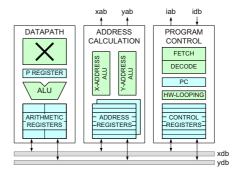

Chapter 4 is by far the longest one, discussing three different time-domain GNSS receiver baseband architectures. We start the chapter by describing the oldest, correlator-based architecture and illustrate two different ways for optimizing the correlator block and show how to alter the basic correlator slightly to perform some more advanced operations. Then we will move on to the MF-based design. Again, we start by briefly introducing the MF in the context of GNSS receivers before showing different ways to optimize the MF-based designs by an efficient implementation of the summation, using time-multiplexing, and enabling further signal integration after the MF. The third architecture considered here is the GC, which combines the characteristics of the correlator and the MF. We describe first how the GC can be derived and then shortly discuss realistic implementations. For each of the proposed three architectures, we present the block diagrams of the GNSS receiver basebands, which are used later in the gate count comparison of Chapter 5.

Chapter 5 is largely based on publication [P6] and contains the receiver comparison results of this thesis. We start the chapter by introducing the test cases for which each compared receiver architecture is parameterized. This makes the comparison fair in the sense that all receivers are configured to fulfill the same set of requirements for the comparison. Next, we present the results with some discussion.

Chapter 6 contains the conclusions and some ideas for future work.

## 2. INTRODUCTION TO GNSS RECEIVER TECHNOLOGY

In this chapter, we will shortly review the background to the thesis. We start with a quick overview of the global navigation satellite system to introduce the field of technology in next Section 2.1. Then, in Section 2.3, we will introduce the GNSS receivers, providing the framework for the subject of this thesis. Finally, Section 2.4 contains a slightly more detailed look on the signal processing tasks implemented in a GNSS receiver.

## 2.1 Global Navigation Satellite Systems

Global Navigation Satellite System (GNSS) refers to a satellite-based navigation system, which offers a worldwide coverage and provides its users with information about their Position, Velocity, and Time (PVT). The GNSS is based on a set of satellites broadcasting a signal, which enable the users to compute the PVT at the receiver antenna. The users don't need to transmit any information towards the system. A typical GNSS is comprised of three segments: the Space segment, the Control segment, and the User segment. The space segment consists of the satellites which transmit the signals used for positioning. The ground segment includes a master control station, a set of ground antennas for uploading data to the satellites, and a set of monitoring stations covering various regions of the earth. The user segment refers to the user equipment for receiving the sig-

|                        |        |               |                        | -                   |  |  |

|------------------------|--------|---------------|------------------------|---------------------|--|--|

| System                 | GPS    | GLONASS       | Galileo                | BeiDou-3            |  |  |

| Nominal Satellites     | 24 MEO | 24 MEO 30 MEC |                        | $24~\mathrm{MEO}$ / |  |  |

|                        |        |               |                        | $3~{ m GEO}$ /      |  |  |

|                        |        |               |                        | 3  IGSO             |  |  |

| Operational Satellites | 31     | 23            | $4 \text{ IOV}^a$      | $3~{ m MEO}$ /      |  |  |

| (as of May 2018)       |        |               | $18 \; \mathrm{FOC}^b$ | $6~\mathrm{GEO}$ /  |  |  |

|                        |        |               |                        | 6 IGSO $^{c}$       |  |  |

| Operational            | 1995   | 1993          | 2020                   | 2020                |  |  |

| Owner                  | USA    | Russia        | EU                     | China               |  |  |

**Table 1:** Current GNSS systems [22–27]

nal from the satellites and computing their PVT. There are several GNSS systems in use and in planning. The oldest and best known GNSS system is the United States Navstar Global Positioning System (GPS). The Russian GLObal'naya NAvigatsionnaya Sputnikovaya Sistema (GLONASS) was available next, and the European Galileo and Chinese BeiDou systems came later.

Table 1 shows a list of the most important GNSSs currently available. All of the systems are constantly evolving by improving the system performance through various means such as adding new signals. GPS, GLONASS, and Galileo satellites utilize only Medium Earth Orbits (MEOs), where the satellites have orbital periods of approximately 12 hours. Some of the BeiDou satellites also use Geostationary Earth Orbits (GEOs), where the satellites appear to stay at the same spot above the earth. Some BeiDou satellites are also in an Inclined Geosynchronous Satellite Orbits (IGSOs),

<sup>&</sup>lt;sup>a</sup>In Orbit Validation

<sup>&</sup>lt;sup>b</sup>Full Operational Capability

<sup>&</sup>lt;sup>c</sup>BeiDou-2 satellites shown, as no BeiDou-3 satellites are operational yet

**Table 2:** Some properties of current and future GNSS signals on L1 band. The references point to the corresponding ICD documents that contain full details of the signals.

| Signal             | Carrier         | Code            | Code    | Sec             | Modu-    | data            |

|--------------------|-----------------|-----------------|---------|-----------------|----------|-----------------|

|                    | $\mathbf{freq}$ | $\mathbf{freq}$ | length  | $\mathbf{code}$ | lation   | $\mathbf{rate}$ |

|                    | (MHz)           | (MHz)           | (chips) | (chips)         |          | (Hz)            |

| Original signals   |                 |                 |         |                 |          |                 |

| GPS L1 C/A [28]    | 1575.24         | 1.023           | 1023    | -               | BPSK     | 50              |

| GLONASS L1OF [29]  | 1598.06         | 0.511           | 511     | -               | BPSK     | 50              |

|                    | -1603.38        |                 |         |                 |          |                 |

| Galileo E1-B [30]  | 1575.42         | 1.023           | 4092    | -               | CBOC     | 250             |

| Galileo E1-C [30]  | 1575.42         | 1.023           | 4092    | 25              | CBOC     | -               |

| BeiDou B1I [31]    | 1561.09         | 2.046           | 2046    | 20              | BPSK     | 50              |

| Modernized signals |                 |                 |         |                 |          |                 |

| GPS L1C-D [32]     | 1575.24         | 1.023           | 10230   | -               | BOC(1,1) | 100             |

| GPS L1C-P [32]     | 1575.24         | 1.023           | 10230   | 1800            | TMBOC    | -               |

| GLONASS L1OCd [33] | 1600.99         | 0.511           | 1023    | -               |          | 250             |

| GLONASS L1OCp [33] | 1600.99         | 0.511           | 4092    | -               | BOC(1,1) | -               |

| BeiDou B1C-D [34]  | 1575.42         | 1.023           | 10230   | -               | BOC(1,1) | -               |

| BeiDou B1C-P [34]  | 1575.42         | 1.023           | 10230   |                 | QMBOC    | 100             |

in which they appear to trace out a small figure-eight shape in the sky. Typically, the GNSS satellites transmit a multitude of signals aimed for different usage. The satellites are currently transmitting on one to three Radio Frequency (RF) bands: L1, L2, and L5. In the past, the L1 signals were intended for civil use, and the L2 signals were designed for military use only. Recently, some civil use signals have been added to the L2 band as well. The L5 band is a recent addition, and its signal structure is the most complex, even if it is also generally available for civil use. Table 2 lists the current and future GNSS signals at the L1 band of frequencies as an example of the signal properties. The details of the GNSS signals

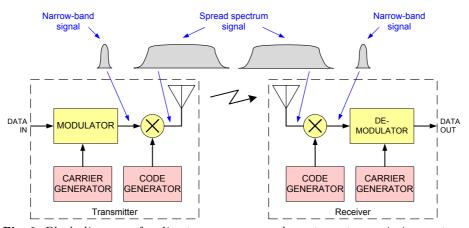

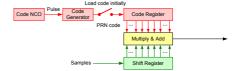

Fig. 2: Block diagram of a direct-sequence spread-spectrum transmission system.

are documented in Interface Control Documents (ICDs) published by the owners of the systems. A good source for further information is for example [35, Part B].

# 2.2 Direct-Sequence Spread-Spectrum Systems

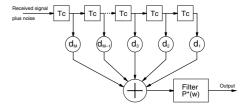

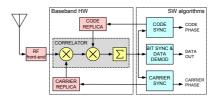

All GNSS systems use Direct-Sequence Spread Spectrum (DSSS) transmission. Good introduction to Spread Spectrum (SS) technique can be found in [36] and an in depth review of its history from [37–39]. There are also several books with a good, in-depth treatment of SS such as [40–42]. In DSSS, the signal is transmitted using a bandwidth that is many times wider than it what would be needed for the data [36]. A conceptual block diagram of a DSSS system is illustrated in Figure 2. In the transmitter, the modulated data is multiplied by a spreading sequence, which typically is a Pseudo Random Number (PRN) sequence, and then it is mixed up to the carrier frequency and fed to the antenna. The receiver multiplies it first by a local oscillator signal to translate the received signal back

to the baseband. Then it needs to multiply the incoming signal by a despreading sequence, which needs to be correctly aligned in time with the spreading code in the transmitter. The spreading and de-spreading codes are designed to cancel each other, when the signals are aligned, so that the original modulated data stream will be recovered. If the spreading code is a binary code interpreted as  $\pm 1$ , then the spreading and de-spreading codes can be identical, which is the typical implementation.

There are two reasons for using DSSS in GNSS. The first is that it enables high resolution ranging [43, 44, Chap. 8], which is crucial for accurate PVT determination. The second is that it enables multiple signals to be transmitted at the same frequency. This is a form of multiple access, called Code Division Multiple Access (CDMA) [45]. The GLONASS system does not rely on CDMA for the transmission from multiple satellites, but it uses Frequency Division Multiple Access (FDMA), where each transmitter uses a separate frequency.

#### 2.3 GNSS Receivers

The function of the GNSS receiver is to acquire and receive the signals from the satellites of each supported GNSS system, and to measure the signal transmit times modulo the spreading duration. Using the transmitted data messages from the satellites and a time-code embedded in the data frames, the receiver can then compute the full signal transmission time and the position of the satellites at that time. With four transmit times it is possible to solve for the four unknowns, namely three coordinates (X, Y, Z) and the reception time assuming that the reception time is common or can be propagated to a common time for all satellites [46]. In a similar fashion by measuring the Doppler frequencies of the received

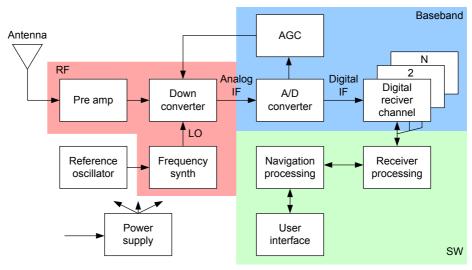

Fig. 3: Generic GNSS receiver block diagram (adapted from [20]).

signals, it is possible to solve for the velocity in three dimensions together with the common frequency offset of the local clock of the receiver. This, of course, is a greatly simplified description of what actually happens in a modern GNSS receiver. These calculations are typically performed by the software algorithms running in a microprocessor which is part of the GNSS receiver. There is a vast amount of literature devoted for the PVT calculation and other GNSS algorithms. Good sources for further information include [20, 21, 35].

A generic GNSS receiver is illustrated in Figure 3. The signal is received at the antenna and it is then amplified by a Low Noise Amplifier (LNA) since the signal power is too weak at this point to be directly used. Next, the signal is down-converted from the RF carrier frequency to a lower Intermediate Frequency (IF) for further processing in the baseband. The analog baseband chain also contains filtering and further amplification which is not shown in the figure. The baseband amplification is also ad-

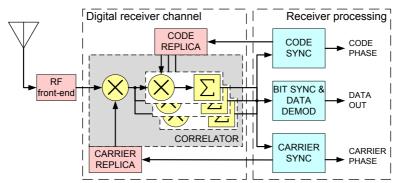

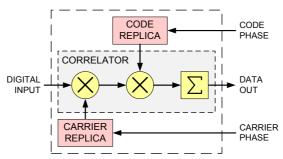

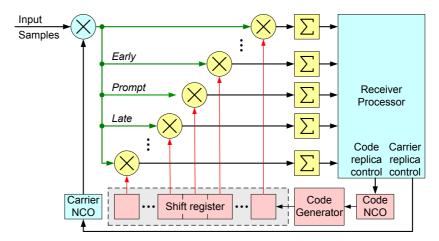

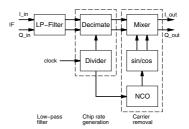

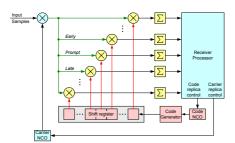

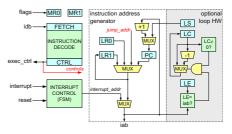

Fig. 4: Conceptual diagram of GNSS receiver channel structure (adapted from [P6]).

justable to control the signal level at the ADC. This will ensure that the quantization losses are minimized. As the received signal to noise ratio is low [47], the ADC needs only a small number of bits [48,49], usually between 1 to 3 [50]. The signal chain until this point contains usually just one path per RF band, as the RF chain bandwidth covers the transmit frequencies of all the satellites in that band. As we need to receive the signals from all of the satellites, the digital part contains one receiver channel for each signal received from each satellite. As each satellite can transmit multiple signals, the receiver might also need multiple channels per satellite. The receiver uses different SW algorithms to control the hardware for receiver control, signal acquisition and tracking. Finally, the navigation processing is responsible for calculating the PVT outputs that the user needs.

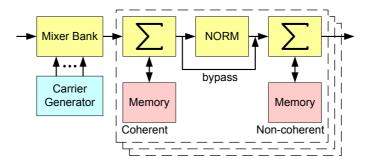

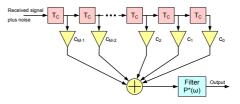

In this thesis, we will concentrate on the implementation and optimization of the digital receiver channels. A conceptual block diagram of the receiver channel along with some associated functions is depicted in Figure 4. The digital baseband signal enters the receiver channel, where it is multiplied by a replica of the remaining carrier (including IF, satellite Doppler frequency

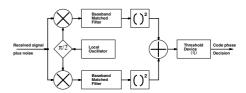

and any local oscillator errors) and the locally generated replica of the spreading code. After the multiplication, the signal is accumulated until it is forwarded to the software algorithms for further processing. Mathematically, this function performs a cross-correlation between the incoming signal and the locally generated replicas, and thus it is termed as *correlator*. The correlator is a key component in the GNSS receivers and there are numerous widely different implementations. The correlator itself does not produce the measurements necessary for the PVT computation. The data message transmitted by the satellites is extracted by demodulating the correlator output signal. The message can only be received when the replica code and carrier are aligned with the incoming signal; otherwise, the correlator output is just noise.

In 1988, the first commercial, handheld GPS receiver, the Magellan GPS NAV 1000, was introduced to the market [51,52]. It had only only one hardware channel in the entire receiver, which was time-shared between the different satellites to facilitate the reception of enough signals for the PVT computation [53]. However, as the digital technology advanced, it soon became possible to implement more parallel hardware channels, which improved the receiver performance [54]. The early receivers were designed for one GNSS system only, and the number of receiver channels was low. With the nominal GPS constellation, there are maximally 11 satellites visible at any place and time [46], so 12 receiver channels became the norm for some time for tracking all visible satellites and one channel tracking a Satellite Based Augmentation System (SBAS) signal. Nowadays it is not uncommon to have several hundreds of channels [55]. This is needed for using more than just one RF band and GNSS and increasing the performance of the receivers.

## 2.4 GNSS Receiver Signal Processing Tasks

After the incoming signals are down-converted to a lower Intermediate Frequency (IF) and converted to digital discrete time samples, the next step is to process them at the baseband. There are four main tasks to perform:

- 1. Find the coarse parameters for the local replicas for all signals available

- 2. Track the incoming signals so that the local replicas stay aligned

- 3. Receive and extract the messages sent by the satellites

- 4. Measure the frequency and time of the received signals as accurately as possible

Usually, the functions are performed in sequence, but the last three are continued as long as a particular satellite signal remains available. There are some measures that allow us to determine how well these tasks are performed.

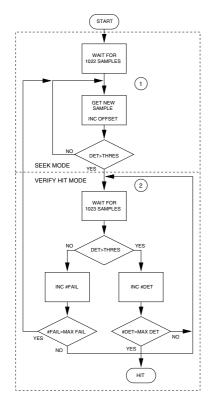

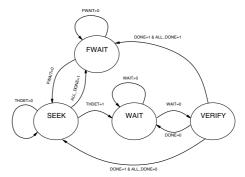

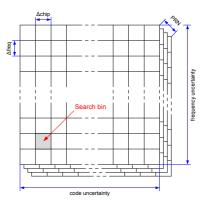

### 2.4.1 Signal Acquisition

The signal acquisition process always needs to happen first so that we know the parameters needed to generate the local replicas accurately enough for the receiver can start tracking the signals [56]. The signal acquisition is a three-dimensional search problem, where the search limits are known to a certain degree. In a cold start situation [57], the receiver does not have any a-priori knowledge of its own location, the time, the available satellite signals, or their parameters. The system itself gives some limits:

Fig. 5: Visualization of the GNSS acquisition space (from [P6]).

There is a finite number of satellites in each system, their orbits and the receiver motion limits provide bounds to the Doppler range, and the local reference oscillator has some known limits of the frequency uncertainty. Only the time is unlimited, but on the other hand, the spreading code is repeating, so we only need to find the signal transmit time modulo the code duration. The search space is divided into discrete points in the three dimensions, where the point distance is set by the search algorithm. This acquisition space is depicted in Figure 5. There are also some other commonly used acquisition scenarios. In the warm start case [57], we do have some a-priori knowledge of the satellite orbital parameters, location

and time, which allow us to predict which satellites are available, and what are their estimated Dopplers. The user motion and the time, within the code period, are still unknown. This results in a bounded search space in two dimensions. The hot-start case [57] adds more exact satellite orbital parameters and time down to a few code chips. Also, in many cases the receiver motion can be guessed accurately enough to make the frequency uncertainty very small.

The important performance criteria for the search phase are the sensitivity or minimum signal level for successful acquisition, the acquisition time, the probability of detection and false alarm, and the frequency and time estimation accuracy for the found signal. These criteria are not independent and improving one usually means making one or more of the others worse.

## 2.4.2 Signal Tracking

The purpose of the signal tracking is to keep the locally generated replica carrier and code as well aligned as possible to the incoming signal. The art of signal tracking is a well-researched topic in communications, but the GNSS application brings some additional requirements. For general communication applications it is sufficient that the tracking is good enough for the data to be received successfully. For the GNSS receivers, this is often not good enough. The phase of the generated replicas is measured and used for determining the signal reception time. The high precision GNSS receivers are able to determine the position down to the millimeter level or better. At 1.5 GHz carrier frequency, this translates to carrier phase accuracy of about two degrees, which is much better than what is typically required in data receiving. The phase tracking accuracy will become significant for the Bit Error Rate (BER) only when it exceeds 18 degrees [58, Chap 10].

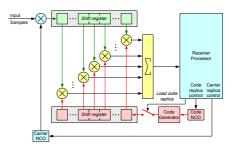

Fig. 6: Generic block diagram of GNSS receiver code tracking loop (adapted from [20]).

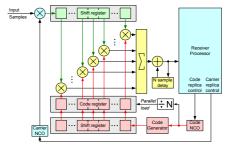

Typical code tracking in GNSS receivers is implemented using a Delay Locked Loop (DLL) [59], which utilizes two differently timed correlators for advanced (early) and delayed (late) versions of the replicas. The carrier tracking is implemented with either a Phase Locked Loop (PLL), usually employing a Costas-loop [60,61] or a Frequency Locked Loop (FLL), which is also sometimes referred to as Automatic Frequency Control (AFC) [62]. It uses the precisely timed (prompt) correlator, which provides the highest signal level. The PLL is more accurate, but it needs a higher Signal to Noise Ratio (SNR) compared with the FLL [63]. Good references for spread spectrum signal tracking can be found in [40,41]. GNSS specific good general references are [20,64]. A typical implementation for code tracking is illustrated in Figure 6, and a carrier tracking implementation is shown in Figure 7.

The main performance criteria for GNSS signal tracking are the sensitivity, the tolerance to receiver dynamics (velocity, acceleration and jerk), and

Fig. 7: Generic block diagram of GNSS receiver carrier tracking loop (adapted from [20]).

the tracking accuracy. Again, they are not independent, but depend on each other in addition to the tracking loop algorithms used.

## 2.4.3 Data Reception

Each GNSS satellite transmits data messages containing information about its orbit and clock, called *ephemeris*. This allows the receiver to compute the exact location of each satellite and the signal transmit time. This information is needed for computing the PVT at the receiver. The data messages also contain the rough orbital parameters of the other satellites, called the *almanac*, to allow predicting when they are visible to the receiver. The satellites also transmit some other information, which is not needed for the PVT computation. The exact format and content of the data messages are defined in detail in the Signal-In-Space Interface Control Document (SIS-ICD) of each GNSS system. The data reception uses the prompt correlator output signal, and the data demodulation and message decoding is usually done in the receiver SW [65]. Thus, it is not an important part of the receiver baseband hardware.

The data reception performance is measured by the sensitivity and bit or frame error rates. Typically, the data reception sensitivity is worse than the acquisition and tracking sensitivities, so it determines the cold start sensitivity of the whole GNSS receiver. In some cases e.g. with Assisted GNSS (A-GNSS), the data can be provided for the receiver through a different communication channel, which enables it to operate with weaker signals that would be possible without the assistance.

### 2.4.4 Measurement Processing

The accurate measurement of the carrier and spreading code timing of the received signal with respect to the receiver local clock is the key to high accuracy PVT determination. The receiver position can be computed from the signal propagation times, and the velocity from the derivative of time, i.e. frequency. The accurate time at signal reception time is a by-product of determining the position. In similar fashion the receiver clock frequency will be solved as a by-product from the velocity computation. There are numerous well known algorithms for PVT determination and the reader is referred to for example Kaplan [66] as an introduction or the GNSS Handbook [67–69] for a more thorough treatment of this subject.

From the hardware perspective, there are two common methods for performing the raw measurements. The first and oldest is to keep track of the phase and frequency of the generated replicas inside the receiver software implementing the signal tracking. This is doable, as the replicas are generated using Numerically Controlled Oscillators (NCOs), whose frequencies are updated at regular intervals. It is then possible to compute their phases at the next update time, and this process can be continued as long as the tracking continues. If the channel NCO update times are identical, then it

is trivial to get the measured phases and instantaneous frequencies at a common time. However, if the channels are sampled at the end of the code periods, which aligns the integration periods accurately with the bits of the satellite data message, then each channel has different update time, and it becomes more tedious task to align the measured values to a common reference time. Implementing the replica phase and frequency sampling in hardware allows sampling the values at a common instant by storing the values at sample registers when a hardware signal is toggled. This hardware measurement method has been used in some receiver implementations, especially those with individual dump for the channel outputs.

## 3. GATE COUNT ESTIMATION<sup>1</sup>

Design optimization for digital ASICs<sup>2</sup> and IP<sup>3</sup> blocks is easier and more efficient when the design space exploration can be done early in the design process, before the implementation is frozen. Financial feasibility of the design may depend on its manufacturing cost and ensuring rapid time to market will demand knowledge of the design complexity early in the project. Modern digital designs are based on pre-built digital gates for all but the most performance critical parts and silicon area is almost directly proportional to the number of gates. Thus, the gate count is a good metric for the complexity of a digital circuit. The gate count also has a relation to the power consumption via the capacitance accountable to the gates. Furthermore, the testability and the test time are affected by the complexity so it affects to the cost of the chip also via the cost of the testing.

#### 3.1 Earlier Work

The idea of estimating the design complexity using silicon area, gate count, or Field Programmable Gate Array (FPGA) resource usage is not a new one. Several approaches have been proposed in the literature through the years.

<sup>&</sup>lt;sup>1</sup>The material in this chapter is based on the publications [P5] and [P6].

<sup>&</sup>lt;sup>2</sup>Application Specific Integrated Circuits

<sup>&</sup>lt;sup>3</sup>Intellectual Property

Shannon [70] can be credited for being the first to propose the estimation of the switch count for implementing Boolean functions. He proposed that the *upper limit* of the complexity of Boolean functions is proportional to the exponential of the number of inputs. Müller [71] used the same approach applied to the gate count estimation for implementations of Boolean functions.

Kellerman [72] proposed that the area of a function depends only on the number of conditions which must be differentiated by a one or a zero output and presented a formula for the computation of the area estimate based on that idea. Pippinger [73] and Cook et al. [74], amongst others, have studied the relationship between the entropy and the area complexity of Boolean functions. The entropy measure based estimation method was then expanded to the multiple-output Boolean functions by Cheng and Agrawal [75].

The earlier work was based on randomly generated Boolean functions with a small number of inputs, and the estimates developed using those greatly overestimated the gate count of real circuits. This problem was pointed out by Nemani and Najm [76], who proposed that typical circuits are far from random in their structure and developed a new linear measure of Boolean functions, which is dependent on the complexity of the on and off-sets of the function. Using the new method gave more realistic results for typical circuits. The estimation method was further developed by Büyükşahin and Najm [77], whose work enabled estimation at a higher level of abstraction by using a Boolean network representation of the circuit instead of Register Transfer Level (RTL) level description. In the end, using these kinds of methods still requires the knowledge of the accurate Boolean functions of the logic, which may not be available at early phases of the design. Another approach by Akers [78] was based on representing the Boolean functional

graphically as *Binary Decision Diagrams (BDDs)*. Bryant [79] applied this method on integer multiplication in order to estimate its complexity.

Enzler et al. [80] described a method for FPGA design complexity estimation. Starting from a Data Flow Graph (DFG) or block diagram, they created a characterization vector describing the features of the design, which consists of numbers and word lengths of design building blocks such as adders and multipliers as well as some other block characteristics. The vector can then be mapped into the FPGA resource use, which is similar to the gate count of an ASIC. In addition, they also use the method to generate timing estimates, which is possible to do in FPGA, as the blocks and routing have predictable delays. Their method resembles the one in this thesis, but our method offers more freedom in the characterization since it is not tied to the fixed vector format. Since our method allows selecting the basic functions in which the design is mapped to, it can be tuned to different classes of designs. In our method, it is also possible to increase the accuracy of the estimation incrementally by adding more basic blocks to the estimation process over time.

The references are summarized in Table 3 illustrating the used design description (input). The table also lists the accuracy of the method if it is reported in the publication. For a further introduction to the area estimation methods, Meeuws [82] provides a good introduction to the hardware characteristics estimation techniques in the scope of hardware/software partitioning. As a summary, it is obvious that most of the earlier work has concentrated in finding formulas for mapping a small, combinatorial, and accurately described logic function to an estimate for the hardware complexity. Also, most of the earlier efforts on the gate count and area estimation were aimed to develop the algorithms to be integrated into Computer Aided Design (CAD) tools for building comprehensive frame-

| (j, [- •]) |                   |          |          |                      |  |

|------------|-------------------|----------|----------|----------------------|--|

| Ref        | Input             | Cost     | Accuracy | Notes                |  |

| [70]       | Boolean functions | switches | n/a      | Theoretical work     |  |

| [71]       | Boolean functions | gates    | n/a      | Theoretical work     |  |

| [72]       | Boolean functions | diodes   | 15%      | for random logic     |  |

|            |                   |          | 33%      | for realistic logic  |  |

| [74]       | Boolean functions | diodes   | n/a      | Theoretical work     |  |

| [73]       | Boolean functions | gates    | n/a      | Theoretical work     |  |

| [75]       | Boolean functions | gates    | 30%      |                      |  |

| [76]       | Boolean equations | gates    | 22%      | Based on on/off sets |  |

|            |                   |          |          | of function          |  |

| [77]       | Boolean network   | gates    | 24%      |                      |  |

| [80]       | Block diagram /   | FPGA     | 12%      | Intermediate vector  |  |

|            | DFG               | cells    |          | representation       |  |

| [81]       | VHDL              | FPGA     | 3.5%     | Intermediate CDFG    |  |

|            |                   | cells    |          | representation       |  |

| [P5]       | Block diagram /   | gates    | 4.0%     | Parameterizable $/$  |  |

|            | DFG               |          |          | extendable models    |  |

**Table 3:** Area estimation references comparison (from [P5])

works like Abdelhalim et al. in [81]. In contrast, the method presented in this thesis aims to provide a tool for early stage estimation for architecture exploration at a high level of design abstraction, which would work on complex and realistic designs.

# 3.2 Estimation Method Summary

Development of integrated circuits is very complex and time-consuming process and optimization is more efficient when done at higher design abstraction levels. However, no such systematic methods existed for ASIC design, and architects needed to resort to rules of thumb, their experience in the field and ad-hoc rough estimations. The method proposed here will offer a way to early estimates of the gate counts of incomplete designs quickly and efficiently. The method is especially suited for area estimation of new data flow modules.

The successful use of the proposed method requires only gate size information about a few key gate types in the standard-cell library that will be used in the synthesis of the design. In many cases, default gate size values could be used for the primitives with only a minor loss of accuracy. Different alternative designs can be compared successfully against each other with good accuracy as long as the same sizes are used for the primitives.

#### 3.3 Parameterized Model Creation

The proposed gate count estimation method is based on a bottom-up modeling approach, but the design will be processed from top to down. The developed model of the design for the gate count estimation can be parameterized so that it will be easy to explore the effect of parameter changes to the silicon area. The models are built from parts at three abstraction levels:

- 1. *Primitive library*, which includes elements that correspond directly to standard-cell gates of the implementation technology.

- 2. Basic block library, which is built from a pre-defined, but extensible set of functional blocks such as adders, multipliers, and registers. The basic blocks are re-usable and parameterized in such a way that they can be used in modeling of many different designs.

- 3. Design level models, which are specific to the design under estimation.

|                      |         | (* ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' |

|----------------------|---------|------------------------------------------|

| Primitive            | Size    | Notes                                    |

| 2-input NAND (NAND2) | 1 gate  | 1-gate area definition                   |

| Inverter (INV)       | 1 gate  | Slightly larger than a                   |

|                      |         | minimum inverter                         |

| Register bit (FF)    | 5 gates | With synchronous reset                   |

| Full-adder (FA)      | 5 gates |                                          |

| 2-input MUX (MUX2)   | 3 gates |                                          |

| Half-adder (HA)      | 3 gates |                                          |

| 2-input XOR (XOR2)   | 3 gates |                                          |

**Table 4:** Primitive library for gate count estimation (from [P5]).

The primitive library contains typical standard cells, which should be available for any chosen implementation technology. The gate sizes of these key cells, which form the primitive library, are the only required information needed for the proposed method. The primitive library, which was used in [P5] and [P6] is listed in Table 4, where the default gate counts for the cells are also given.

The basic block library contains parameterized, low level building blocks, which are used in most designs. It is also possible to add sub-blocks, which are used many times in the design, into the basic block library to allow their re-use. To get the best advantage of the new basic blocks, they need to be parameterized for maximal re-use and developed carefully to maximize the accuracy of the estimation. For the basic blocks, it is usually a reasonable first guess to base them on their minimal area implementation. It is possible that, for example, some very high-speed designs might need a different implementation with inserted pipeline stages. The basic building blocks

| Function             | Size                                                                                                                         |

|----------------------|------------------------------------------------------------------------------------------------------------------------------|

| Adder                | $\mathcal{G}(\operatorname{add}(N)) = N \times \mathcal{G}(\operatorname{FA})$                                               |

| Subtractor           | $\mathcal{G}(\mathrm{sub}(N)) = N \times (\mathcal{G}(\mathrm{FA}) + \mathcal{G}(\mathrm{INV}))$                             |

| Increment by 1       | $\mathcal{G}(\mathrm{inc}(N)) = N \times \mathcal{G}(\mathrm{HA})$                                                           |

| Absolute value       | $\mathcal{G}(\operatorname{abs}(N)) = N \times (\mathcal{G}(\operatorname{XOR2}) + \mathcal{G}(\operatorname{HA}))$          |

| Multiply (uns.)      | $\mathcal{G}(\mathrm{mult}_{\mathrm{uu}}(N, M)) = N \times M \times (\mathcal{G}(\mathrm{FA}) + \mathcal{G}(\mathrm{AND2}))$ |

| Multiplexer $M$ -to- | 1 $\mathcal{G}(\max(N, M)) = N \times (M - 1) \times \mathcal{G}(MUX2)$                                                      |

| Register             | $\mathcal{G}(\text{reg}(N)) = N \times (\mathcal{G}(\text{FF}) + \mathcal{G}(\text{MUX2}))$                                  |

**Table 5:** Examples of basic block library elements from [P5].

are usually modeled with a set of basic primitives, but they could also contain other basic blocks as parts. Some representative, simple basic blocks are listed in Table 5, where the notation  $\mathcal{G}(\mathcal{B})$  means the gate count  $\mathcal{G}$  for a block  $\mathcal{B}$ . There can also be more complex basic blocks such as register banks, signed multipliers, mixers, and so on. They are developed using the simple basic blocks and the primitives as parts.

#### 3.4 Estimation Method Flow

The gate count estimation method is split into two distinct phases. The first one is building a model of the design and this process is illustrated in Algorithm 1. The process starts by creating a data-flow graph or a block diagram of the design to be estimated. This will be done in top-down fashion so that a sub-block diagram is made for each block at the top level. At each level, we can use new sub-blocks, basic blocks or primitives from the libraries. The process is repeated until we have just basic blocks or

## **Algorithm 1** The model creation (from [P5])

- 1: **procedure** CreateModel(block)

- 2: **Divide** to sub-blocks as needed

- 3: **for all** sub-blocks **do**

- 4: CreateModel(sub-block)

- 5: **end for**

- 6: **Define** parameters as desired

- 7: Create a data-flow graph / block diagram

- 8: **Map** remainder to basic blocks or primitives

- 9: end procedure

primitives left at the lowest level. Next, the design can be parameterized from bottom-up so that the lower level parameters can be derived from those at the next level up. For example, one common parameter is the word length for all data elements.

The next phase uses the model with a suitable set of parameters to compute the estimate, as shown in Algorithm 2. The process simply sums up the gate count of all instantiated sub-blocks, basic blocks, and primitives recursively applying the parameters as given by the user at the top level.

There are a few caveats in the use of this method. The first one is the accuracy of the primitive library. In most cases, the default values will suffice, but there could be cases where the relative sizes of the primitives will dictate which of the two architectures leads to a smaller size. This can happen e.g. when the size of the register cell compared with the sizes of combinatorial cells is smaller or larger, and the two architectures differ in the number of register bits needed. In such cases it is important to use the correct values for the chosen implementation technology during the

## **Algorithm 2** The model evaluation (from [P5])

```

1: function EVALMODEL(block, params...)

count \leftarrow 0

2:

3:

for all \mathcal{B} \leftarrow instantiated sub-blocks do

count \leftarrow count + \text{EVALMODEL}(\mathcal{B}, \text{params...})

4:

end for

5:

for all \mathcal{B} \leftarrow instantiated basic-blocks do

6:

count \leftarrow count + \text{EVALMODEL}(\mathcal{B}, \text{ params...})

7:

end for

8:

count \leftarrow count + \sum (gate count of primitives)

9:

return count

10:

11: end function

```

process. Fortunately, it is also possible to change the primitive cell sizes during the process and just re-evaluate the estimate. The modeling phase does not need to be repeated. The other shortcoming is that the presented methodology does not take the routing area into account. The result of the estimate is really the gate count value and not silicon area. If a physical size estimate is needed, the routing area needs to be estimated. In some cases, one could also use the average gate count per mm<sup>2</sup> value given by the silicon vendor.

## 3.5 Gate Count Estimation Accuracy

In [P5], we have shown that the average gate count estimation accuracy was 4%. The accuracy was computed simply as the average of the absolute values of the relative errors between the estimated gate count given by the model and the actual gate count as reported by the logic synthesis

tool used. In computing the accuracy, we used blocks from two different GNSS receivers and a Digital Signal Processing (DSP) processor core. The gate counts of the blocks ranged from 20 to 250 kilo-gates. The designs included some embedded memories, but these were excluded from the accuracy analysis. A detailed description of the architectures of these blocks can be found in [P5]. In the paper, we also had a number of smaller examples, which were compared with actual gate counts from the synthesis tool. These smaller cases had an average error of 3.2%. The gate counts of these smaller cases ranged from 0.4 to 12 kilo-gates.

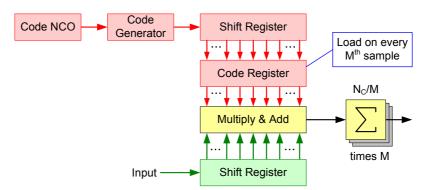

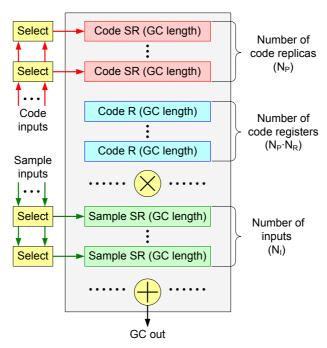

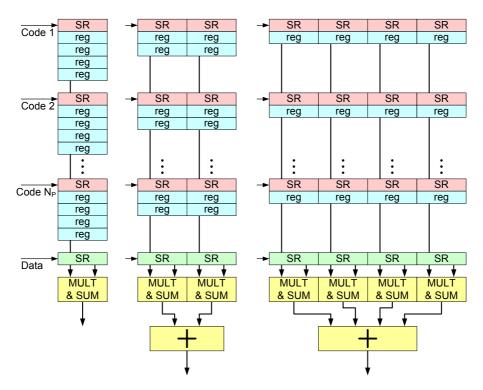

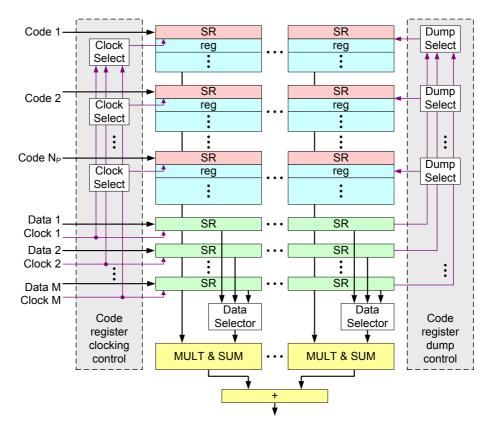

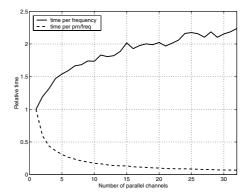

The accuracy evaluation method follows its intended use. We started from a high level description and created the estimation from it. Then using the same description, a VHSIC Hardware Description Language (VHDL) implementation was developed and synthesized. Finally, the gate count given by the estimate was compared against the gate count of the actual implementation. Only high level description of the design was used for the gate count estimation model development. For the GNSS receivers, we used the design specifications. For the VS\_DSP, the input document was its user's manual [83]. The actual gate counts were obtained from the implementation documentation of the corresponding ICs.