# MARKUS ALLÉN NONLINEAR DISTORTION STUDIES IN WIDEBAND ANALOG-TO-DIGITAL CONVERTERS

Master of Science Thesis

Examiners: Professor Mikko Valkama, Professor Markku Renfors, M.Sc. Vesa Lehtinen Examiners and topic approved in the Computing and Electrical Engineering Faculty Council meeting on 4 March 2009

# **ABSTRACT**

TAMPERE UNIVERSITY OF TECHNOLOGY

Master's Degree Programme in Signal Processing and Communications Engineering

**ALLÉN, MARKUS**: Nonlinear Distortion Studies in Wideband Analog-to-Digital Converters

Master of Science Thesis, 78 pages, 4 Appendix pages

May 2010

Major: Communication Systems

Examiners: Professor Mikko Valkama, Professor Markku Renfors, M.Sc. Vesa

Lehtinen

Keywords: analog-to-digital converter, clipping, integral nonlinearity, interference cancellation, interpolation, nonlinear distortion, radio receiver

This thesis discusses nonlinearities of analog-to-digital converters (ADCs) and their mitigation using digital signal processing (DSP). Particularly wideband radio receivers are considered here including, e.g., the emerging cognitive radio applications. In this kind of receivers, a single ADC converts a mixture of signals at different frequency bands to digital domain simultaneously. Different signals may have considerably different power levels and hence the overall dynamic range can be very large (even 50–60 dB). Therefore, even the smallest ADC nonlinearities can produce considerable amount of nonlinear distortion, which may cause a strong signal to block significantly weaker signal bands.

One concrete source of nonlinear distortion is waveform clipping due to improper signal conditioning in the input of an ADC. In the thesis, a mathematical model for this phenomenon is derived through Fourier analysis and is then used as a basis for an adaptive interference cancellation (AIC) method. This is a general method for reducing nonlinear distortion and besides clipping it can be used, e.g., to compensate integral nonlinearity (INL) originating from unintentional deviations of the quantization levels. Additionally, an interpolation method is proposed in this thesis to restore clipped waveforms and hence reduce nonlinear distortion.

Through several computer simulations and corresponding laboratory radio signal measurements, the performance of the proposed post-processing methods is illustrated. It can be seen from the results that the methods are able to reduce nonlinear distortion from a weak signal band in a considerable manner when there are strong blocking signals in the neighboring channels. According to the results, the AIC method would be a highly recommendable post-processing technique for modern radio receivers due to its general ability to reduce nonlinear distortion regardless of its source.

# TIIVISTELMÄ

TAMPEREEN TEKNILLINEN YLIOPISTO

Signaalinkäsittelyn ja tietoliikennetekniikan koulutusohjelma

ALLÉN, MARKUS: Epälineaarinen vääristymä laajakaistaisissa analogia-

digitaalimuuntimissa

Diplomityö, 78 sivua, 4 liitesivua

Toukokuu 2010

Pääaine: Tiedonsiirtotekniikka

Tarkastajat: professori Mikko Valkama, professori Markku Renfors, DI Vesa Leh-

tinen

Avainsanat: analogia-digitaalimuunnin, epälineaarinen vääristymä, häiriönpoisto, integraalinen epälineaarisuus, interpolointi, leikkaantuminen, radiovastaanotin

Tässä työssä käsitellään analogia-digitaalimuuntimien (AD-muuntimien) epälineaarisuuksia ja niiden lieventämistä digitaalisen signaalinkäsittelyn (DSP) avulla. Tätä on tarkasteltu erityisesti laajakaistaisten radiovastaanottimien näkökulmasta, joka käsittää mm. tulevat kognitiiviseen radioon liittyvät sovellukset. Tällaisissa vastaanottimissa yksittäinen AD-muunnin muuntaa samanaikaisesti useita eri taajuuskaistoilla olevia signaaleita digitaaliseen muotoon, jolloin yhteenlaskettu dynaaminen alue voi olla hyvin suuri (jopa 50–60 dB). Tämän takia AD-muuntimen pienimmätkin epälineaarisuudet voivat aiheuttaa huomattavasti epälineaarista vääristymää, minkä vuoksi voimakas signaali saattaa häiriöllään peittää muilla taajuuskaistoilla olevia selkeästi heikompia signaaleja.

Eräs konkreettinen epälineaarisen vääristymän aiheuttaja on aaltomuodon leikkaantuminen AD-muuntimen sisäänmenossa jännitealueen ylittymisen vuoksi. Tässä työssä johdetaan matemaattinen malli kyseiselle ilmiölle Fourier-analyysin avulla ja käytetään sitä lähtökohtana adaptiiviselle häiriönpoistomenetelmälle (AIC-menetelmä). Se on yleisluonteinen menetelmä epälineaarisen vääristymän vähentämiseksi, ja leikkaantumisen lisäksi sitä voidaan käyttää esimerkiksi kompensoimaan integraalista epälineaarisuutta (INL), joka on peräisin kvantisointitasojen tahattomista poikkeamista. Lisäksi tässä työssä esitellään interpolointimenetelmä leikkaantuneen aaltomuodon ehostamiseen siten, että epälineaarinen häiriö vähenee.

Esiteltyjen jälkikäsittelymenetelmien suorituskykyä analysoidaan ja havainnollistetaan useilla tietokonesimulaatiolla sekä niitä vastaavilla radiosignaalien laboratoriomittauksilla. Tuloksista voidaan nähdä, että nämä menetelmät kykenevät poistamaan huomattavasti epälineaarista vääristymää heikolta signaalikaistalta silloin, kun naapurikaistoilla on voimakkaita häiriösignaaleja. Tulosten perusteella AIC-menetelmä olisi erittäin suositeltava jälkikäsittelytekniikka moderneihin radiovastaanottimiin, koska se pystyy yleisesti vähentämään epälineaarista vääristymää riippumatta häiriön alkuperästä.

IV

**PREFACE**

The research behind this thesis was conducted during the years 2008 and 2009 at the

Department of Communications Engineering at Tampere University of Technology

(TUT) under the project entitled "Dirty-RF: Advanced Techniques for RF Impairment

Mitigation in Future Wireless Radio Systems". The research was supported by the

Academy of Finland, the Finnish Funding Agency for Technology and Innovation

(Tekes) and the Technology Industries of Finland Centennial Foundation.

First I would like to thank my supervisor Professor Mikko Valkama not only for of-

fering me a topic for the thesis but also for providing guidance and a very educative job

as a research assistant, which has given me a good starting point for my career. I would

also like to express my gratitude to other examiners of my thesis Professor Markku Ren-

fors and M.Sc. Vesa lehtinen for all of their efforts. Special thanks go to my co-worker

Jaakko Marttila, who started examining the wonderful world of analog-to-digital con-

verters with me from the beginning and has ever since shared his knowledge to advance

my research. In addition, I would like to thank all the co-workers and the staff of our

department for creating a pleasurable working environment, especially my "nearest

neighbors" M.Sc. Jukka Talvitie, M.Sc. Ville Syrjälä and M.Sc. Toni Levanen for giv-

ing valuable tips and sharing their thoughts with me.

Furthermore, I am most indebted to my parents Anja and Matti as well as my broth-

er Timo for all their support towards everything I have achieved so far. Last but not

least I would like to thank all my friends for giving me precious time of joy every now

and then during the thesis project.

Tampere, 15 April 2010

Markus Allén

E-mail: markus.allen@tut.fi

Tel.: +358 50 301 0625

# **CONTENTS**

| 1. | Introduction                        |                                                         | 1  |

|----|-------------------------------------|---------------------------------------------------------|----|

| 2. | Analog-to-Dig                       | ital Converters and Nonlinearities                      | 5  |

|    | 2.1. Quantization Process           |                                                         |    |

|    | 2.2. Non-Idealities in Quantization |                                                         | 8  |

|    | 2.3. High-Speed ADC Architectures   |                                                         | 11 |

|    | 2.3.1.                              | Flash ADC                                               | 11 |

|    | 2.3.2.                              | Subranging ADC                                          | 12 |

|    | 2.3.3.                              | Successive Approximation ADC                            | 14 |

|    | 2.3.4.                              | Sigma-Delta ADC                                         | 15 |

|    | 2.4. Com                            | pensation Methods                                       | 17 |

|    | 2.4.1.                              | Look-Up Table                                           | 18 |

|    | 2.4.2.                              | Dithering                                               | 19 |

|    | 2.4.3.                              | Model Inversion                                         | 20 |

|    | 2.5. Clip                           | ping Effect in ADCs                                     | 21 |

|    | 2.5.1.                              | Clipping in Radio Transmitters                          | 23 |

|    | 2.5.2.                              | Clipping in Radio Receivers                             | 23 |

| 3. | Radio Receive                       | r Architectures and Analog-to-Digital Converters        | 25 |

|    | 3.1. Trad                           | le-Offs Between Speed, Resolution and Power Dissipation | 25 |

|    | 3.2. Common Receiver Architectures  |                                                         | 27 |

|    | 3.2.1.                              | Superheterodyne Receiver                                | 27 |

|    | 3.2.2.                              | Direct Conversion Receiver                              | 28 |

|    | 3.2.3.                              | RF-Sampling Receiver                                    | 29 |

|    | 3.3. Syst                           | em Performance Requirements                             | 30 |

| 4. |                                     | cortion Compensation Studies                            |    |

|    | 4.1. Mat                            | hematical Analysis of Symmetric Clipping                | 32 |

|    | 4.1.1.                              | Model for a Real Band-Pass Signal                       | 32 |

|    | 4.1.2.                              | Model for a Complex Band-Pass Signal                    |    |

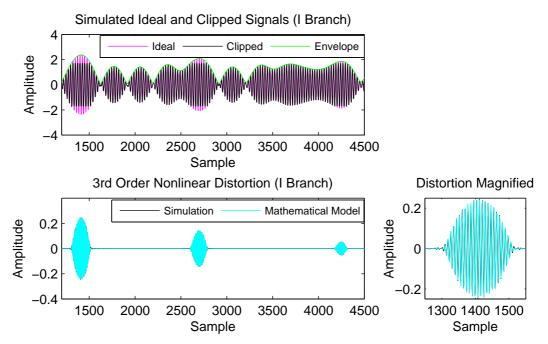

|    | 4.1.3.                              | Example of Clipping Distortion                          |    |

|    | 4.2. Ada                            | ptive Interference Cancellation                         | 40 |

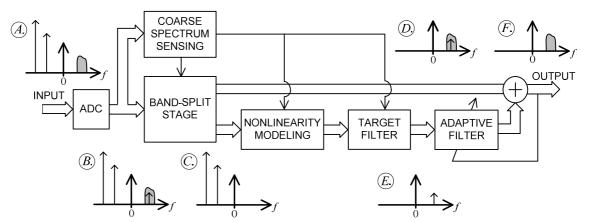

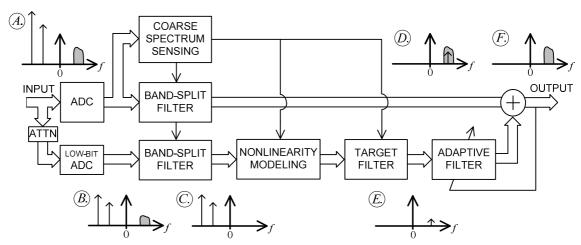

|    | 4.2.1.                              | Introduction to the Post-Processing Principle           | 41 |

|                                                                   | 4.2.2.                | Utilization for Clipping Compensation | 43 |

|-------------------------------------------------------------------|-----------------------|---------------------------------------|----|

|                                                                   | 4.2.3.                | Utilization for INL Compensation      | 44 |

|                                                                   | 4.3. Cli <sub>j</sub> | pping Compensation with Interpolation | 45 |

| 5.                                                                | Performance           | experiments                           | 49 |

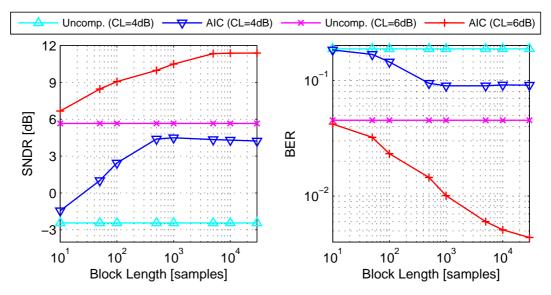

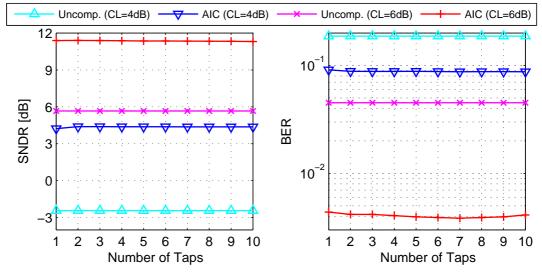

|                                                                   | 5.1. Cli <sub>1</sub> | pping Compensation                    | 49 |

|                                                                   | 5.1.1.                | Adaptive Interference Cancellation    | 52 |

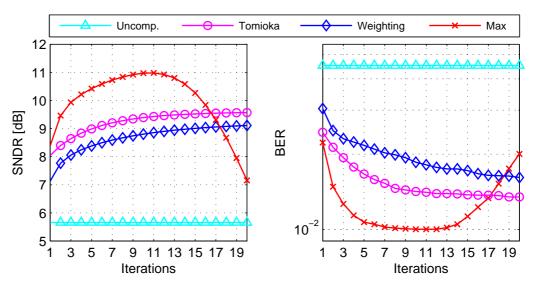

|                                                                   | 5.1.2.                | Interpolation                         | 57 |

|                                                                   | 5.1.3.                | Comparison                            | 61 |

|                                                                   | 5.1.4.                | Laboratory Measurements               | 63 |

|                                                                   | 5.2. INI              | L Mitigation                          | 69 |

| 6.                                                                | Conclusion            |                                       | 73 |

| References                                                        |                       |                                       |    |

| Appendix: Derivation of the Fourier Series for Symmetric Clipping |                       |                                       |    |

# **ABBREVIATIONS**

ADC Analog-to-Digital Converter

AGC Automatic Gain Control

AIC Adaptive Interference Cancellation

BER Bit Error Rate

DAC Digital-to-Analog Converter

DNL Differential Nonlinearity

DSP Digital Signal Processing

FIR Finite Impulse Response

FS Full Scale

HCF High Code Frequency

IF Intermediate Frequency

INL Integral Nonlinearity

IQ In-phase/Quadrature

LCF Low Code Frequency

LMS Least Mean Squares

LNA Low-Noise Amplifier

LO Local Oscillator

LSB Least Significant Bit

LUT Look-Up Table

MSB Most Significant Bit

Msps MegaSamples Per Second

OFDM Orthogonal Frequency Division Multiplexing

OSF Oversampling Factor

PAPR Peak-to-Average Power Ratio

QPSK Quadrature Phase Shift Keying

RF Radio Frequency

rms Root Mean Square

SAR Successive Approximation Register

SDR Software Defined Radio

SNDR Signal-to-Noise-and-Distortion Ratio

SQNR Signal-to-Quantization-Noise Ratio

WCDMA Wideband Code Division Multiple Access

# **SYMBOLS**

$\varepsilon(n)$  Compensation value retrieved from a LUT

$\varepsilon[k]$  Error between the ideal and the actual value of T[k]

$\theta_c(t)$  Argument for the carrier defined as  $\omega_c t + \phi(t)$

$\phi(t)$  Phase of the carrier

$\omega_c$  Angular frequency of the carrier

a Polyphase branch index

A(t) Signal envelope

$a_m(t)$  Time-variant Fourier coefficients

b Number of bits in a quantizer

c Polynomial weight

C Crest factor in linear scale

CF Crest factor in logarithmic scale (dB)

$f_B$  Useful signal bandwidth

h(n) Impulse response of an interpolation filter

$INL_{HCF}(T[k])$  HCF part of INL for transition T[k]  $INL_{LCF}(T[k])$  LCF part of INL for transition T[k]  $INL_{noise}(T[k])$  Noise part of INL for transition T[k]

L Oversampling factor

m Index for Fourier series

M Order of sigma-delta noise shaping

n Sample index N Signal length

p Number of conversion stages in a subranging ADC

$P_{\text{avg}}$  Average power of the signal

Q Ideal code width

$\begin{array}{ll} r_I(t) & \text{Auxiliary variable defined as } \arccos \frac{V_0}{A(t)} \\ r_Q(t) & \text{Auxiliary variable defined as } \arcsin \frac{V_0}{A(t)} \\ \tilde{s} & \text{Input signal } s \text{ after nonlinearity } g(\cdot) \end{array}$

$\hat{s}(n)$  Compensated output signal

$\hat{s}'(n)$  Digital estimate of the derivative of the input signal s(t)

s(t) Continuous-time input signal

$\overline{s}_f$  Mean value of  $s_f(n)$

$s_f(n)$  Ideal test signal filtered to contain only the frequency band

around 3 MHz

t Time variable

T[k] Actual input voltage corresponding to kth transition

$T_1$  Ideal value of T[1]

$T_{ideal}[k]$  Ideal value for kth transition

$V_0$  Clipping level

$v_{cl}(t)$  zero-symmetric hard-clipped signal

$egin{aligned} v_{in}(t) & ext{continuous-time input signal} \ V_{in(rms)} & ext{Rms value of the input signal} \ v_{ ext{lim}}(t) & ext{Clipped output signal (limiter)} \end{aligned}$

$V_{os}$  Output offset of an ADC

$v_{out}(t)$  Clipped output signal (hard clipping)

$V_{pp}$  Peak-to-peak input voltage

$V_{Q(rms)}$  Rms value of the quantization error

W[k] Actual kth code width y(n) Output signal of an ADC

$\hat{y}(n)$  Estimate of the ADC output given by a black-box model

$\overline{y}_f$  Mean value of  $y_f(n)$

$y_f(n)$  Distorted test signal filtered to contain only the frequency

band around 3 MHz

# 1. INTRODUCTION

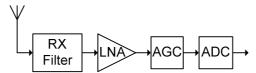

All modern mobile communication devices deploy digital transmission as well as digital signal processing and thus analog-to-digital conversion is an inevitable part in their radio receivers. There has been remarkable increase in the performance of the radio receivers in recent years. Unfortunately the development of analog-to-digital converters (ADCs) has not been as rapid [24], [41]. Therefore, the ADC has become a bottle neck for the whole receiver. This can be explained with one of the modern trends where the ADC is located as close to the antenna as possible in the receiver chain. In this way, the smallest possible number of analog components in the receiver can be achieved. Cutting down the amount of the analog parts is desired in order to reduce, for example, power consumption and required chip area of the receiver. Moreover, selectivity of the receiver is easier, more flexible and cheaper to implement in digital domain. In that case, receiver doesn't necessarily have to have several parallel receiver front-ends for different wireless standards. [19], [26]

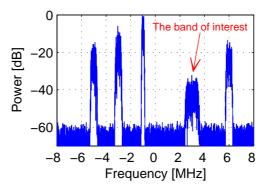

The ultimate goal in receiver design would be a so-called software defined radio (SDR). It is a re-configurable receiver where all or most of the selectivity is implemented with digital signal processing (DSP). In extreme case, the received signal is digitized straight from the radio frequency (RF). Another possibility is a direct conversion principle, where the received signal is downconverted from RF to baseband and then, after an analog-to-digital conversion, the channel selection is performed. [31] In both cases, a wideband signal, which may consist of several separate frequency bands, is digitized as a whole. A wideband receiver front-end enables the cognitive radio concept, which uses spectrum sensing in order to exploit any feasible part of the spectrum [10]. This is the main case which is considered throughout the thesis. A wideband receiver sets very strict requirements for analog-to-digital converters. In practice it means that high resolution and especially high sampling rate are needed. The requirement for high resolution is stemming from the large dynamics of modern communications signals and also from the need to detect low-power frequency bands when there are considerably

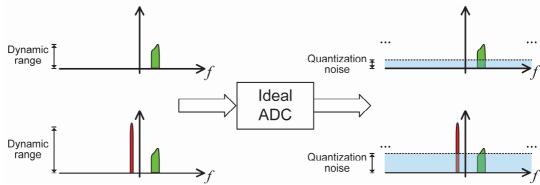

stronger frequency bands in the same signal. This is illustrated in Figure 1.1. The dynamic range can be several tens of dB's. As a matter of fact, the sampling rate is a more limiting aspect than the resolution. When selectivity is implemented in digital domain, the ADC usually has to digitize wider frequency band and hence higher sampling rate is required. The trend towards wider bandwidths in the receivers can be seen clearly by studying the development of ADC technologies. After the year 1995 the maximum resolution of commercial ADCs hasn't increased but the sampling rate has been developing very fast [24]. In addition, the power consumption is a very critical aspect in mobile devices. As a general rule, high-resolution and high-speed ADCs tend to have very significant power dissipation.

**Figure 1.1.** Spectrum illustrations of the upper part show how an ideal ADC induces quantization noise to the signal due to finite resolution. In the lower part, the dynamic range is increased due to a strong blocking signal and hence the weaker signal is more affected by the quantization noise when the same ideal ADC is used.

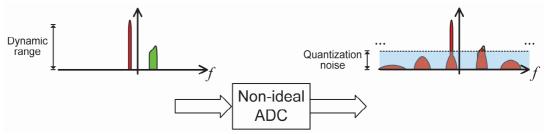

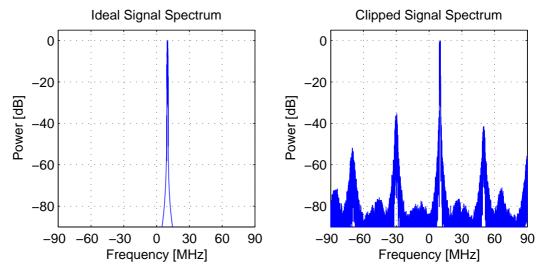

Especially when considering wideband receivers, it is important to be aware of the fact that real-world ADCs are not ideal. There are many different non-idealities that can distort the received signal. For example, due to nonlinear behavior of the ADC a strong signal can severely interfere with weaker signals on different frequency bands [27]. To be exact, the interference is mainly intermodulation distortion of the strong signal. This is illustrated in Figure 1.2. Fortunately, the technical development has noticeably increased the available computational resources. This has created a possibility to add more DSP to the receivers and thus digitally enhance the signal that is distorted by the ADC. Therefore, it is possible to create better receivers by exploiting DSP than it would be otherwise with the current hardware technology. On the other hand, if the additional performance is not needed, the DSP enhancement is still useful. That is because more nonlinear and therefore cheaper or less power-consuming ADCs can be used to provide the same performance as a whole.

**Figure 1.2.** Spectral illustrations from the input and output of a non-ideal ADC. The weak signal band is heavily affected by the nonlinear distortion stemming from the strong blocker signal.

The nonlinearities in analog-to-digital converters are originating from several different sources and thus behave differently [25], [27]. The first goal of the thesis is to discuss what kind of nonlinearities there are in the ADCs and how they affect the received signal. Especially the case of wideband signal with several separate frequency bands is considered here. Such a survey gives a good starting point for developing new DSP methods for ADC nonlinearity compensation. The thesis concentrates specifically on nonlinearities in analog-to-digital conversion. Other non-idealities, such as sampling jitter, are omitted from the thesis, because it is a rather independent topic which is already widely covered in the existing literature.

One interesting source of nonlinear distortion, which is covered in this thesis among others, is waveform clipping in the input of the ADC. The phenomenon is stemming from the improper input signal conditioning due to the rapidly changing signal dynamics. This is a potential situation in the wideband receivers where different signals may have considerably different power levels. The amount of literature about the ADC clipping, especially in the radio receivers, is rather limited. This is one strong motive to study the clipping topic in more detail in this thesis.

There is a great need for ADC nonlinearity compensation methods not only due to emerging wideband radio receivers in mobile devices but also because most of the existing methods proposed in the literature have been designed for laboratory equipment. These methods may require, e.g., a considerable amount of memory or offline calibration and thus are not suitable for real-time mobile devices with limited resources. The second goal of the thesis is to cover the most used methods for nonlinearity compensation in ADCs which are proposed in the literature. After that, the goal is to develop and propose new nonlinearity compensation methods which are not, until this thesis, covered in the literature in the context of ADCs.

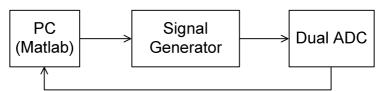

In the research for this thesis, the primary tool for developing new ADC nonlinearity compensation methods and confirming their performance is the well-known software called MATLAB by The MathWorks Inc. Furthermore, the developed algorithms are tested, to the extent possible, in a laboratory environment with a real commercial analog-to-digital converter [5]. In this way, it can be verified that the ADC model in the computer simulations has been accurate enough to model the nonlinear behavior. The technical contribution of this thesis has been also published in [1]–[3].

The structure of the thesis is organized as follows. Chapter 2 gives an overview of quantization and analog-to-digital converters based on the latest scientific literature. It goes through typical high-speed ADC architectures that can be used in radio receivers. After that, DSP-based compensation methods for ADC nonlinearities are discussed. It is worth mentioning that even though sigma-delta ADCs [35] are a potential option for modern radio receivers, their working principle and thus their nonlinearities are significantly different from all the other ADC architectures. Nonlinearity compensation of the sigma-delta ADCs deserves its own research and is therefore omitted from this thesis. Chapter 3 continues with the overview of the radio receiver architectures. It discusses especially how the receiver architecture choice affects ADC requirements. Some examples of the modern wireless standard specifications are considered here. Chapter 4 starts with proposing a mathematical model for a clipped signal. The model was derived to achieve better understanding of the clipping phenomenon and apparently it has not been presented in the literature until now. Next, Chapter 4 proposes two approaches for compensating ADC nonlinearities. Concrete examples of their performance are given in Chapter 5. Both computer simulations and laboratory measurements are considered here. Finally, Chapter 6 gathers everything together by drawing conclusions. Appendix gives details on deriving the mathematical clipping model introduced in Chapter 4.

# 2. ANALOG-TO-DIGITAL CONVERTERS AND NONLINEARITIES

Analog-to-digital converter interprets analog electrical quantities to digital code words. In real-life ADCs, there are several kinds of non-idealities that interfere with the conversion process. Modern communication systems have tight requirements for the ADCs in receivers, e.g. high sampling rate and resolution, and thus the non-idealities may have a significant role. In general, digital signal processing can be used to compensate these non-idealities after the conversion.

First, in Section 2.1 very basics of ideal quantization are discussed followed by the most essential non-idealities described in Section 2.2. Because different ADC architectures have different kinds of impact to digitalization process, the most common high-speed architectures are described in Section 2.3. After that, an introduction to digital compensation methods is given in Section 2.4. Finally, in Section 2.5, one special topic called clipping is covered. Although the so-called sigma-delta ADC architecture is presented in Subsection 2.3.4 due to its attractive features for modern radio receivers, its nonlinearities and their compensation are omitted from this thesis because the sigma-delta architecture differs considerably from all the other ADCs and would require a thesis of its own.

#### 2.1. Quantization Process

Quantization implies presenting large number of values or even a continuous range with limited number of discrete code words. Therefore, input values are rounded to nearest corresponding output values. This means that quantization induces information loss and even in the ideal case it is a nonlinear operation. A coding method in a quantizer is related to the input range of an ADC. If the input range only consists of positive voltages, the quantizer is said to be unipolar. Similarly, an input range with both positive and negative voltages corresponds to a bipolar quantizer. [7]

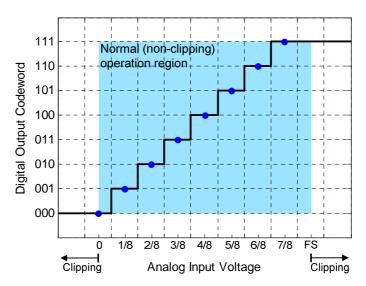

Figure 2.1 illustrates typical transfer function for an ideal unipolar 3-bit ADC. The appropriate input range is marked between 0 and full scale (FS). First quantization level (ideally) starts from 0 V and its width is 0.5 LSB (least significant bit). The width of the last (highest) quantization level is 1.5 LSB. This is because there is -0.5 LSB offset in the positions of all the codeword transitions as is highlighted with a light blue region in Figure 2.1. The offset is intentional and desirable since the potential quantization error is then between -0.5 LSB and +0.5 LSB. Blue dots in Figure 2.1 illustrate locations where the quantization error is zero. Quantization error would be from 0 LSB to 1 LSB without the offset. [7] The lowest and highest quantization level in Figure 2.1 are drawn to continue outside the full scale range to emphasize the ADC behavior outside the intended scale. This phenomenon is called clipping and is discussed in more detail in Section 2.5.

**Figure 2.1.** *Transfer function of an ideal unipolar 3-bit analog-to-digital converter.*

Quantization thresholds do not have to be uniformly spaced. For example, in some applications values near zero can be more important than large values. While keeping the number of bits constant, resolution for small values can be increased at the expense of accuracy in large values by using non-uniform quantizer. For instance, in logarithmic converters the code width increases logarithmically as a function of input voltage. This kind of approach has been used, e.g., in some communications, instrumentation and hearing aid applications. [16] Somewhat different approach is used in a floating-point ADC. It operates dynamically with respect to the amplitude of the input signal, i.e., code widths change when the dynamics of the input signal change [30].

Information loss as a result of finite word length is called quantization noise. It can be expressed conveniently with signal-to-quantization-noise ratio (SQNR). After ideal quantization, the SQNR in decibels is defined as

$$SQNR = 20 \log_{10} \left( \frac{V_{in(rms)}}{V_{Q(rms)}} \right), \tag{2.1}$$

where  $V_{in(rms)}$  is the root mean square (rms) value of the input signal and  $V_{Q(rms)}$  is the rms value of the quantization error. Furthermore, a common assumption is that the quantization noise is white and uniformly distributed between  $\pm 0.5$  LSB and hence

$$V_{Q(rms)} = \frac{Q}{\sqrt{12}},\tag{2.2}$$

where Q denotes the width of one LSB, i.e.,  $Q = \mathrm{FS}/2^b$ . The rms value of the input signal can be given with respect to the peak-to-peak input voltage  $V_{pp}$  and the crest factor C so that

$$V_{in(rms)} = \frac{V_{pp}}{2C}. (2.3)$$

This follows from the fact that the crest factor is defined as a ratio of the peak amplitude and the rms voltage of the signal. In addition, a possible oversampling gain should be taken into consideration when defining the SQNR. The oversampling gain stems straight from the oversampling factor which, for one, is defined as a ratio of the sampling frequency and the double-sided useful signal bandwidth. When all the abovementioned details are substituted in Equation (2.1), the SQNR finally becomes

$$SQNR = 6.02b + 4.77 - CF + 10\log_{10}\left(\frac{f_s}{2f_B}\right),$$

(2.4)

where b is the number of bits in the quantizer, CF is the crest factor of the input signal in dB's,  $f_s$  denotes the sampling frequency and  $f_B$  is the useful signal bandwidth. [22] Oversampling can be utilized to spread the quantization noise on a wider band and hence reduce the in-band noise. The out-of-band part of the noise can then be filtered away.

The SQNR equations in the previous paragraph considered white quantization noise. However, there is one special ADC structure that can shape the quantization noise so that most of it is outside the band of interest. It is called a sigma-delta ADC and its operational principle is more carefully discussed in Subsection 2.3.4. By making an assumption that the oversampling factor is significantly larger than one, the SQNR for a sigma-delta ADC with first-order noise shaping can be written as

$$SQNR_{SD,1} = 6.02b + 4.77 - CF - 10\log_{10}\left(\frac{\pi^2}{3}\right) + 30\log_{10}\left(\frac{f_s}{2f_B}\right).$$

(2.5)

It can be seen that doubling the oversampling factor increases SQNR by 9 dB when first-order noise shaping is used. As a comparison, Equation (2.4) shows that without noise shaping only 3 dB gain can be achieved by doubling the oversampling factor. If the sigma-delta ADC uses second-order noise shaping, the SQNR becomes

$$SQNR_{SD,2} = 6.02b + 4.77 - CF - 10\log_{10}\left(\frac{\pi^4}{5}\right) + 50\log_{10}\left(\frac{f_s}{2f_B}\right).$$

(2.6)

In this case, the SQNR is improved by 15 dB every time the oversampling factor is doubled. In general, for Mth-order noise shaping, the SQNR equation is

$$SQNR_{SD,M} = 6.02b + 4.77 - CF - 10\log_{10}\left(\frac{\pi^{2M}}{2M+1}\right) + (20M+10)\log_{10}\left(\frac{f_s}{2f_B}\right).$$

(2.7)

Therefore, doubling of the oversampling factor increases the SQNR by (6M + 3) dB. [8], [22]

#### 2.2. Non-Idealities in Quantization

Real-life ADCs have several different kinds of unwanted nonlinearities. Gain and offset errors are significant but their effects are rather trivial to mitigate. Other important non-linearities are differential nonlinearity (DNL) and integral nonlinearity (INL). Various definitions for these nonlinearities can be found from the literature. The most used ones are presented in following paragraphs.

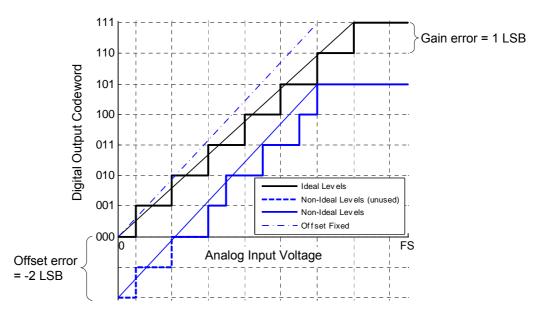

According to an application note of Maxim Integrated Products Inc. [29], offset error is defined as a constant shift of transfer function from its ideal location. Gain error can be evaluated after the offset error has been corrected. It is defined as a difference between the actual codeword after the last transition and the corresponding ideal one. An example of both offset and gain error in case of a unipolar ADC is illustrated in Fig-

ure 2.2. Ideal and non-ideal transfer functions are presented with solid black and blue lines, respectively. Straight lines are fitted through the starting point and the last transition of transfer functions to make the offset error of -2 LSB and the gain error of 1 LSB more visible. The dashed blue line in Figure 2.2 represents the non-ideal transfer function after correcting the offset error. Occasionally, also a term full-scale error is used in ADC datasheets. It is defined as a sum of offset error and gain error. In Figure 2.2, the full-scale error can be thought as a difference of the actual codeword after the last transition compared to the ideal transfer function. Therefore, in this case the numerical value is -1 LSB. It is also worth noticing that some of the quantization levels may be left unused in unipolar converters because of the offset error.

**Figure 2.2.** Example of offset and gain errors in an unipolar 3-bit ADC.

IEEE standard 1241-2000 for analog-to-digital converters [17] introduces another approach for defining offset and gain errors. The transfer function of an ADC can be described with the equation

$$G \times T[k] + V_{os} + \varepsilon[k] = Q \times (k-1) + T_1, \qquad (2.8)$$

where G is the gain, T[k] is the actual input value corresponding to kth transition,  $V_{os}$  is the output offset,  $\varepsilon[k]$  is the residual error of kth transition, Q is the ideal code width and  $T_1$  is the ideal value of T[1]. The IEEE standard [17] describes two ways of identifying offset and gain errors based on Equation (2.8). In independently-based method G and  $V_{os}$  get values that minimize the mean squared value of  $\varepsilon[k]$  over all k. Another

method is called terminal-based, which defines that the offset and the gain are the values which cause the deviations of the first and last codes to be zero. In other words, the offset and the gain are evaluated when  $\varepsilon[1] = 0$  and  $\varepsilon[2^b - 1] = 0$ , where b is the number of bits in quantizer.

INL and DNL errors can be calculated only after correction of offset and gain errors. DNL is the relative difference between the actual and ideal code widths compared to the ideal code width. It is defined as

$$DNL[k] = \frac{W[k] - Q}{Q} \tag{2.9}$$

in which W[k] is the kth actual code width [17]. In a similar manner, INL is the difference between the actual and the ideal code transition threshold. Another way of interpreting the INL is thinking it as a cumulative sum of the DNL. According to [17], INL can be defined as

$$INL[k] = 100\% \times \frac{T[k] - T_{ideal}[k]}{2^b \times Q},$$

(2.10)

where  $T_{ideal}[k]$  is the ideal value for the kth transition. It should be taken into account that Equation (2.9) gives DNL as a multiple of LSB, but INL in (2.10) is given in relation to the full scale. In some cases, a more convenient equation is

$$INL[k] = \frac{T[k] - T_{ideal}[k]}{O},$$

(2.11)

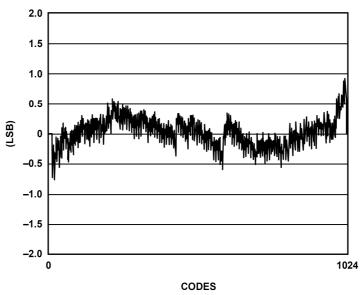

which gives INL as a multiple of LSB. For instance, ADC datasheets typically use LSB unit. In addition to that, usually when DNL or INL is expressed as a single value it is the maximum of (2.9) or (2.11) over all k.

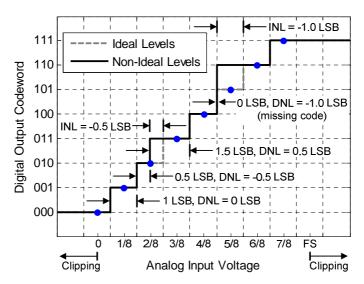

An example of DNL and INL errors is presented in Figure 2.3 so that more concrete conception can be attained. The dashed gray line indicates the ideal transfer function and the black line represents an example of non-ideal transfer function for a 3-bit unipolar ADC. The corresponding DNL and INL errors have been marked in Figure 2.3. There is an example of missing code, which means a situation where the DNL error is less than or equal to -1 LSB and therefore two quantization levels are fully overlapped. In case of Figure 2.3, the codeword *101* doesn't correspond to any input voltage. In some situations the errors can make the transfer function to be non-monotonic (not illusor).

strated in Figure 2.3). It means that there are two separate ranges of input voltages that correspond to the same digital output codeword. The non-monotonicity is not possible in every ADC architecture, but it can happen, for instance, in pipelined ADCs. [7]

Figure 2.3. Example of DNL and INL errors in a 3-bit ADC.

### 2.3. High-Speed ADC Architectures

This section provides a small overview to different kinds of high-speed ADC architectures which can be classified to flash, subranging, successive approximation and sigmadelta ADCs. The operational principle of every architecture is described and also some examples of their practical applications and present performance are discussed. It is worth noticing that the sigma-delta ADC principle differs significantly from all the other aforementioned architectures not only by its noise shaping properties but also by its non-idealities.

Comparator is an essential building block in any ADC architecture. One or more of them can be found from every ADC structure described in the following. Basically, the comparator can be considered to be a 1-bit ADC. It outputs binary values by comparing the input signal voltage level to a constant threshold level. [7]

#### 2.3.1. Flash ADC

A flash ADC is also called a parallel ADC which clearly describes its data conversion principle. It consists of  $2^b$ -1 comparators as shown in Figure 2.4. The comparators are biased to correspond to the wanted quantization levels. The input signal after a sample-and-hold circuit is applied to all comparators at the same time. Therefore, the conver-

sion takes only one cycle and high-speed conversion can be achieved. Parallel comparators as a whole produce a thermometric representation and for this reason the level encoder is used to construct a more practical *b*-bit digital output. [13]

**Figure 2.4.** *Operational principle of flash ADC with b-bit output.*

As mentioned already, flash ADCs are suitable for high-speed applications. However, due to practical limitations the resolution can't be very high. It is worth noticing that the number of comparators increases exponentially as a function of bits used in quantization. This is directly proportional to the required silicon area and, especially, the power consumption. The high resolution also refers to very small differences between the reference voltages of the comparators. In practice, very small differences are challenging to achieve with a high enough accuracy. [27] The above-mentioned matters are the reason for which flash ADCs are mainly used in high-speed oscilloscopes and RF test instruments. Modern flash ADCs can reach sampling rates of even several gigasamples per second but the resolution isn't usually more than 8 bits. [33]

#### 2.3.2. Subranging ADC

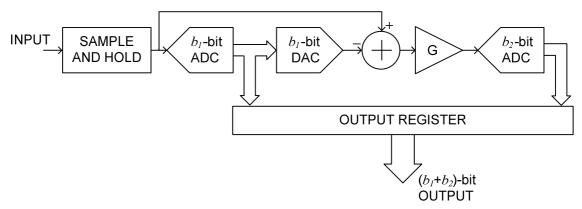

A subranging ADC was originally developed to overcome the limitations of the flash converters. It is composed of several consecutive low-resolution flash or other type ADCs. A simple two-stage subranging ADC is illustrated in Figure 2.5. After the sample-and-hold process, a coarse conversion is done by the  $b_I$ -bit ADC. This results in the most significant bits (MSB) of the final output. Then, the bits are converted back to an analog signal by the  $b_I$ -bit DAC and subtracted from the original input signal. The residue is amplified by the amplifier with gain G to precisely cover the input range of the  $b_2$ -bit ADC. The latter ADC provides the LSBs of the input signal which are joined together with MSBs in the output register. Hence, the final output has a word length of

$b_1+b_2$  bits. [7] A little bit modified version of subranging ADC is called pipelined ADC. It consists of identical consecutive stages where every stage is independent, containing a sample-and-hold circuit, an ADC, a DAC, an adder and an amplifier.

**Figure 2.5.** *Operational principle of two-stage*  $(b_1+b_2)$ *-bit subranging ADC.*

Compared to the flash ADC, the subranging architecture has an ability to provide high-resolution output with low-resolution converters. Therefore, the number of comparators is decreased to  $p \times (2^b - 1)$ , where p is the number of the conversion stages. The drawback is that the total conversion time is directly proportional to p. [13] One challenging problem in real-life subranging ADCs is the proper scaling of the residue signal. If the signal is not accurately scaled to the full scale of the subsequent ADC, a missing code situation may appear as described in Section 2.2. This is usually avoided by increasing the number of bits in the converter for internal use so that the final output resolution does not increase. [7]

Subranging ADCs can provide low power consumption and high resolution compared to flash ADCs and still being able to achieve rather high conversion speed. Hence, these converters are typically used in RF test equipment, lower speed digitizing oscilloscopes and high-end PC data acquisition systems. [33] In addition to that, subranging ADCs have their place in consumer electronics and communications. Intermediate frequency (IF) sampling, software radio, base stations and set-top boxes are good examples of the communications applications in question. Nowadays sampling rates of subranging ADCs can be up to slightly over 100 Msps (megasamples per second) and the resolution can be up to 14 bits. [23]

#### 2.3.3. Successive Approximation ADC

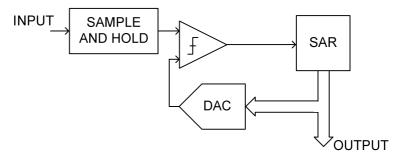

A successive approximation ADC can perform high resolution analog-to-digital conversion using only one comparator. This can be achieved by exploiting the information about previously determined bits when making the decision of the next significant bit. The operation principle of the successive approximation ADC is partially similar to the subranging technique but it processes iteratively one output bit per conversion cycle. If the dynamic range of the ADC is from  $\theta$  to  $\theta$ , the conversion process begins with determining whether the input signal is above or below  $\theta$  above. This corresponds to MSB of the final output codeword. After that, the input signal is compared with the threshold level of  $\theta$  at  $\theta$  if the input signal was below  $\theta$  and  $\theta$  is continued in a similar manner until the desired bit resolution is accomplished. [27] In other words, during the conversion process the (already) quantized bits define the remaining possible value range. Then on the next conversion cycle it is determined, whether the input signal level belongs to the upper or lower half of the possible value range.

In practice, the successive approximation algorithm can be implemented as shown in Figure 2.6. The sample-and-hold circuit takes a sample from the input signal and holds it steady for comparator until all the conversion cycles for the current sample have passed. Threshold level of the comparator is varied by the DAC which is controlled with successive approximation register (SAR). In the initial state, SAR is set to zero but MSB to one. Then it is compared with the input signal and the output of the comparator is stored as the MSB of the SAR. On the next cycle, second most significant bit of the SAR is set to 1, compared with the input signal and replaced with the output of the comparator. This continues until the target bit precision b is achieved. For the next input sample, the SAR is reset to the initial state. [27]

**Figure 2.6.** Operational principle of successive approximation ADC.

The conversion process in the successive approximation ADC is rather slow due to minimum of *b* conversion cycles per sample. In real-life implementations, one problem is the inaccuracy of the DAC. That can lead to a wrong decision in the comparator and, what is more, the error will propagate along all the conversion cycles. In the literature some error correction algorithms are proposed, however these are prone to increase the number of required conversion cycles. [27] Nonetheless, high resolution (up to 16 bits) can be achieved and modern successive approximation ADCs can have sampling rate of a few Msps. Successive approximation ADCs are cheaper and require less power than flash and subranging ADCs. Converters based on SAR are usually used in measurement products such as PC data acquisition systems. [33]

#### 2.3.4. Sigma-Delta ADC

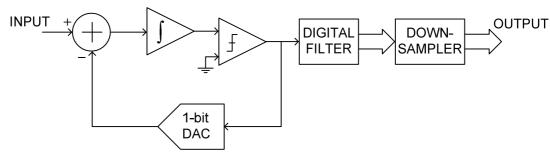

Sigma-delta converters work with high oversampling ratios and therefore even only a 1-bit analog-to-digital conversion combined with digital filtering can eventually provide a very high resolution. However, the fundamental trade-off in the sigma-delta method is that the high resolution achieved with the high oversampling ratio means low final sampling rate. The operational principle of the simplest sigma-delta ADC structure is illustrated in Figure 2.7.

The (oversampled) analog input signal is fed through an integrator to a comparator. After that, the output of the comparator is converted back to the analog domain in a feedback loop and then subtracted from the next input value before the integrator. This structure, which includes the integrator, the comparator and the DAC, is in general called a sigma-delta modulator. The final digital output signal of the sigma-delta ADC is formed by applying proper digital filtering to the output of the comparator and then downsampling it with the same factor as the input signal was oversampled. The integrator is also called a loop filter because it serves as the filter of the feedback loop shaping the quantization noise so that there is less noise at low frequencies than in high frequencies. Therefore the digitized signal is then less affected by the quantization noise because it can be mostly filtered out with a digital filter. [7] The noise shaping property is the fundamental reason for the whole sigma-delta structure and thus makes it distinct from all the other ADC architectures.

Figure 2.7. Operational principle of 1-bit low-pass sigma-delta ADC.

There are many improved versions from the basic sigma-delta ADC structure which provide better performance or other desired properties. For example, using a higher-order loop filter helps reducing the quantization noise even more from the wanted signal band and hence increasing the (effective) resolution of the ADC. The higher-order loop filter is implemented by increasing the number of integrators and feedback loops. In practice, the achievable resolution of the higher-order implementation will be limited due to stability issues. These issues can be relieved with a so-called multistage structure which means using several sigma-delta modulators in a cascade. Another way to increase the resolution is using a multi-bit quantizer instead of a comparator and correspondingly a multi-bit DAC is required in the feedback loop. The multi-bit implementation has a drawback that the multi-bit DACs tend to be rather nonlinear. This creates distortion which is not shaped in the loop and hence it is directly visible at the final output. [35]

Until now this subsection has only considered real low-pass sigma-delta ADCs which can be used for baseband signals. The sigma-delta principle is also applicable for band-pass signals. Practically this means modifying the transfer function of the loop filter so that it will push the quantization noise away from the band of interest towards higher frequencies as well as towards DC. When considering the digitalization of an in-phase/quadrature (IQ) signal with a sigma-delta ADC, there are essentially two options. First one is using two converters separately in parallel whereas another option is to use a so-called quadrature sigma-delta ADC, which exploits a loop filter with complex coefficients. Practically, it means that the noise shaping doesn't have to be symmetric and hence it can be more efficient. [35]

There is still one important structural aspect mainly related to the loop filter. Most of the sigma-delta ADCs are nowadays using discrete-time loop filters implemented with switched capacitors. These loop filters have good accuracy and linearity. The

switched-capacitor circuit structure is also independent of the clock rate and hence it is easy to design a discrete-time sigma-delta ADC to use various sampling rates. Unfortunately, the maximum signal bandwidth is limited by the finite settling time of the circuit. An increasingly popular solution is to use continuous-time loop filters. This way the sampling of the signal can be postponed to after the loop filter, which means that the non-idealities of the sampling process have milder effect. Theoretically the maximum clock rate of the continuous-time sigma-delta ADC is limited by the quantizer and the feedback DAC. Therefore, higher clock rates can be achieved than it is possible with the discrete-time implementation. On the other hand, the continuous-time loop filters are not as linear and accurate as the switched-capacitor filters. In addition, the continuous-time loop filters are not easy to design, because they have to be tuned and calibrated separately for every clock rate. [35]

Traditionally sigma-delta ADCs are used in applications where high resolution is needed but sampling rate requirements are rather modest. This kind of applications are, e.g., PC data acquisition systems, temperature measurements and various data loggers. [33] Additionally, sigma-delta ADCs are widely used in mobile phones. In practice, the achievable resolution in a discrete-time sigma-delta ADC is up to 24 bits while a signal bandwidth is in the order of a few MHz. In continuous-time sigma-delta ADCs, the signal bandwidth can be a few tens of MHz. The sigma-delta ADCs are tunable in the sense that it is possible to reduce the resolution in order to increase the sampling rate. In addition, the sigma-delta ADCs are rather power efficient. These are some aspects, besides noise shaping, that have led to consider the sigma-delta ADCs to be used in software defined radios. [19]

# 2.4. Compensation Methods

Digital post-processing is a powerful tool for compensating ADC errors caused by non-idealities. Hence, plenty of literature has been published about this topic especially in recent years. A journal article of state-of-the-art ADC compensation methods by E. Balestrieri *et al.* [9] classifies the methods in four categories. Look-up table (LUT) based methods, dithering methods and model inversion methods are discussed in the following subsections. These are more or less applicable for any ADC architecture. The fourth category mentioned by E. Balestrieri *et al.* [9] is architecture based methods. These models concentrate on specific details and typical problems of the particular converter

architecture. An architecture based method can be more effective but the number of suitable applications is limited compared to more general approaches.

#### 2.4.1. Look-Up Table

Look-up table methods are based on precalculated estimation values which are stored in a table. The output samples of an ADC are used for indexing to point out corresponding values from a LUT. The look-up table can carry values which are meant either for correction or replacement. In the correction scheme, the LUT value is added to the output sample of the ADC. Replacement scheme refers to replacing the output sample of the ADC with the corresponding value from the LUT. [25]

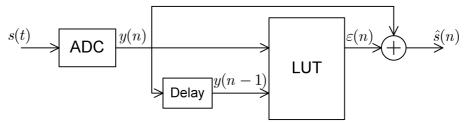

The indexing is one of the most important parts of the LUT method. Based on the literature, it can be done in several different manners. The simplest one is static correction where the same output value of the ADC is every time mapped into the same index. Here, two more advanced methods are discussed which are called state-space indexing and phase-plane indexing. Both take the memory of the nonlinearity into account. The state-space indexing exploits both the current output sample y(n) and the previous sample y(n-1) for creating the index. Therefore, the LUT can be considered as twodimensional. This principle is illustrated in Figure 2.8. The continuous-time input signal s(t) is converted with the non-ideal ADC and then output samples y(n) and y(n-1)are used to retrieve corresponding value  $\varepsilon(n)$  from the LUT. This value  $\varepsilon(n)$  is then used to create the compensated output sample  $\hat{s}(n)$ . The state-space indexing approach can be extended to use more than just one previous sample. Naturally, this increases the effectiveness of the compensation but, on the other hand, also the number of dimensions in the LUT increases. Consequently, the LUT then requires significantly more memory. One solution for this problem is to apply more quantization for delayed samples, i.e. to use less bits, so that the size of the index space can be reduced. [25]

**Figure 2.8.** Look-up table with state-space indexing, modified from [25].

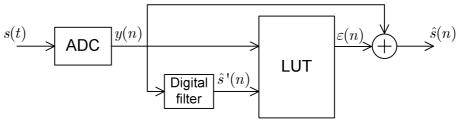

Another dynamic index method is phase-plane indexing. It is based on the present output sample y(n) and estimate of the slope (or derivative) of the input signal  $\hat{s}'(n)$ . The principle is visualized in Figure 2.9. As in the previous method, the continuous-time input signal s(t) is first converted with the ADC. Then a digital filter, for example a finite impulse response (FIR) differentiator, is used to produce the estimate  $\hat{s}'(n)$ . The corresponding LUT value  $\varepsilon(n)$  is, once again, added to the output sample y(n) to create compensated output sample  $\hat{s}(n)$ . Instead of using the digital filter, the slope can be acquired also by measuring the analog signal. [25]

**Figure 2.9.** *Look-up table with phase-plane indexing, modified from* [25].

Apart from the indexing, a further challenge is to properly calibrate the correction (or replacement) values in the LUT. Basically, a calibration signal is fed to the ADC under test and the output is compared with the digital version of the calibration signal. Unfortunately the process is never ideal because only an estimate of the calibration signal can be used. The LUT calibration can be performed, for example, by using an additional very accurate ADC to acquire the digital version of the calibration signal fed to the ADC under test. Another option is to generate a digital calibration signal and use a DAC to feed the signal for the ADC under test. More advanced calibration methods proposed in the literature includes signal processing, e.g. based on a probability density function or optimal filtering, in order to estimate the calibration signal. [25]

#### 2.4.2. Dithering

The essential idea of dithering is to intentionally add noise to ADC input signal before quantization and thus to reduce distortion induced by the quantization. The dithering reduces correlation between the input signal and the quantization error. For this reason, the pseudo quantization noise model can be made applicable. This model is exceedingly used because of its simplicity. It models the quantization error as an additive, uniformly distributed, white and zero-mean noise which is independent of the input signal. The dithering can also reduce distortion caused by quantizer non-idealities by randomizing

the DNL error pattern of a non-ideal uniform quantizer. Furthermore, dithering is able to increase the ADC resolution for slowly varying signals. It is typical that a quantized slowly varying signal has several consecutive output samples with the same value and thus quantization error cannot be reduced by averaging, i.e., low-pass filtering. By adding a proper dither signal prior to quantization, the output values are not all the same. Therefore in this case the averaging may yield better result and increase resolution. [25]

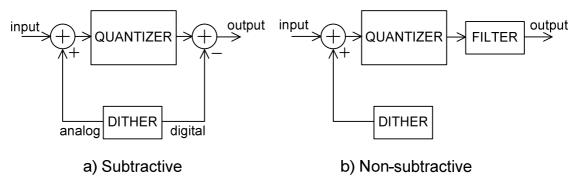

There are two types of dithering methods which are called subtractive and non-subtractive dithering. Both principles are illustrated in Figure 2.10. In the subtractive dithering, the dither noise is added to the input signal before the quantizer and the same noise is subtracted from the output after the quantization in the digital domain. However, it is worth noticing that the digital version of the dither noise is not always known explicitly and thus the subtraction is not ideal. On the contrary, the non-subtractive dithering method adds the dither noise prior to quantizer but is not even trying to remove all the noise after quantization. The method is based on the fact that the out-of-band noise can be filtered out in digital domain. Hence, only a part of the noise still exists in the final output signal. On the other hand, the non-subtractive method can never be expected to perform as well as ideal subtractive dithering. [25]

**Figure 2.10.** Basic structures of a) subtractive and b) non-subtractive dithering principles, modified from [25].

#### 2.4.3. Model Inversion

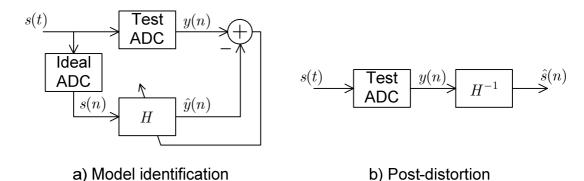

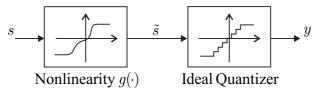

The fundamental principle of the model inversion is to identify a mathematical system model which approximates the input-output relationship of the ADC. Then the inverse system, or approximation of it, is calculated to mitigate non-idealities from the output signal. These two stages are depicted in Figure 2.11. The model identification is performed by feeding a continuous-time input signal s(t) to the ADC under test and to the ideal ADC. Then the test ADC output y(n) and the model output  $\hat{y}(n)$  are compared to

each other in order to tune the model H to match better with the test ADC. As presented in Figure 2.11 b), the post-distortion stage compensates ADC non-idealities by using the inverse of the model H, denoted with  $H^{-1}$ . There are several alternatives for the system modeling such as Chebyshev polynomials, but the most of the proposed methods in the literature are based on the Volterra model. Instead of the two-stage process illustrated in Figure 2.11, it is also possible to indentify the inverse model  $H^{-1}$  directly. In practice, this means tuning  $H^{-1}$  using error signal  $\hat{s} - s$ . [25]

**Figure 2.11.** *Stages of a) model identification and b) post-distortion for ADC correction in the model inversion method, modified from [25].*

Volterra theory is a mathematical approach for describing causal nonlinear time-invariant systems with memory. The theory is usable for systems where the linear term is dominant compared to nonlinearities. The downside of the Volterra model is the computational complexity due to large amount of parameters. Therefore, simplified models such as Hammerstein, Wiener and Kautz-Volterra models have been introduced. Their number of parameters is lower but they don't have the generality of Volterra series. [12]

# 2.5. Clipping Effect in ADCs

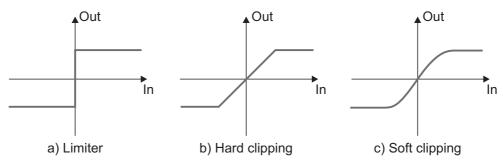

In general, clipping stands for limiting signal amplitude to a certain maximum value. This can be either intentional or unintentional depending on the application. There are basically three different types of clipping: a limiter, hard clipping and soft clipping. An ideal limiter essentially outputs only the sign of the input signal. For the input signal  $v_{in}(t)$  the ideal limiter is defined as

$$v_{\lim}(t) = V_0 \operatorname{sgn}\{v_{in}(t)\} = \begin{cases} +V_0, & \forall t : v_{in}(t) > 0\\ -V_0, & \forall t : v_{in}(t) < 0, \end{cases}$$

(2.12)

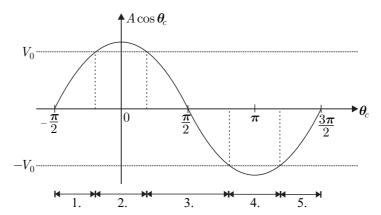

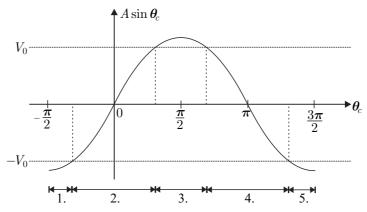

where  $v_{\rm lim}(t)$  is the clipped output signal and  $V_0$  is the clipping level. [14] It is also intuitive to present transfer characteristics of the limiter in a graphical form as it has been done in Figure 2.12 a). Hard clipping differs from the limiter so that it also has a linear region. Therefore symmetric hard clipping is formulated to be

$$v_{cl}(t) = \begin{cases} v_{in}(t), & \forall t : |v_{in}(t)| < V_0 \\ +V_0, & \forall t : v_{in}(t) \ge V_0 \\ -V_0, & \forall t : v_{in}(t) \le -V_0, \end{cases}$$

(2.13)

where  $v_{cl}(t)$  represents the clipped signal. Figure 2.12 b) presents these input-output characteristics for the symmetric hard clipping. Furthermore, soft clipping is like hard clipping but it has smoother behavior near the saturation region. [39] This is visible in Figure 2.12 c). This can be modeled, for instance, with the arcus tangent function but naturally this is highly application dependent. It is worth noticing that various names are used in literature for different clipping types. There is possibility of confusion, for example, when the limiter is called hard clipping or hard clipping is called soft clipping.

**Figure 2.12.** *Transfer functions for a) a limiter, b) hard clipping and c) soft clipping.*

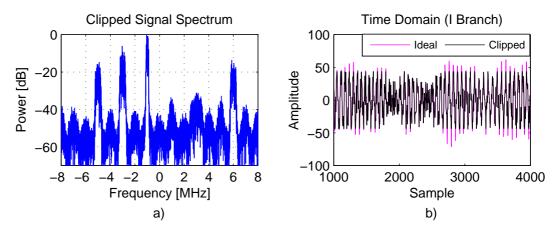

When an analog signal with amplitude higher than the full-scale range is fed to the input of an ADC, the converter saturates and the signal is clipped. It is a rather realistic assumption that the behavior of the ADC can be modeled with symmetric hard clipping. The clipping is an instantaneous phenomenon which causes nonlinear distortion. In case of zero-symmetric hard clipping only odd-order distortion exists. Symmetry is a fair assumption at least when the DC offset has been corrected. It is important to avoid or mitigate the clipping because even light clipping in time domain can have severe effects to the frequency content. Detailed mathematical analysis of the symmetric hard clipping is presented in Section 4.1 and examples of clipping effects are depicted in Section 5.1.

#### 2.5.1. Clipping in Radio Transmitters

Although this thesis focuses on radio receivers and ADCs, the transmitter side clipping is mentioned here for completeness. Deliberate clipping can be used in a radio transmitter to control the amplitude characteristics of the signal before transmitting. This has become more and more important due to more complex waveforms of modern communication systems. For example, orthogonal frequency division multiplexing (OFDM) and wideband code division multiple access (WCDMA) signals may have high peak-to-average power ratio (PAPR) which has to be controlled to ensure that power amplifiers and other critical components work on their optimal region.

If clipping has been used in a transmitter, it has to be compensated on receiver side. This is not a straightforward operation because of the filtering stages after clipping and especially due to the signal distortion stemming from the channel between the transmitter and the receiver. The literature proposes plenty of methods for the compensation. One possibility is to consider clipped samples as lost samples and reconstruct these by using other unclipped samples. This kind of method has been proposed by H. Saeedi et al. in [34] for OFDM systems. Their reconstruction algorithm is based on a least square method and requires an oversampled signal. Entirely different type of scheme, which doesn't need increased signal bandwidth, has been proposed by H. Chen et al. [15]. They used an iterative method to remove clipping noise from the received OFDM signal. First of all, symbols are normally decoded and detected from the received signal. After that the symbols are used to generate both clipped and unclipped estimate of the original transmitted signal. By subtracting these signals from each other, ideally only clipping noise remains. The clipping noise is then subtracted from the original received signal to achieve a cleaner signal for the next iteration cycle. However, the transmitter clipping compensation methods usually require exact knowledge of the clipping level and thus are not directly applicable for compensating receiver clipping, which is typically unintentional.

#### 2.5.2. Clipping in Radio Receivers

Clipping on the receiver side is typically unintentional. One possible situation is clipping in an ADC due to improper input signal conditioning. Automatic gain control (AGC) attempts to keep the signal within the full-scale range of the ADC but this is not

always possible because of finite reaction speed of the AGC. This problem arises especially in wideband receivers where very strong blocker signals can change the signal dynamics rapidly. From the clipping compensation point of view, one challenge is that the exact clipping level is not known like it is in the transmitter clipping case. However, the good thing is that in the receiver side clipping there is no channel between the clipping and the compensator affecting the compensation performance.

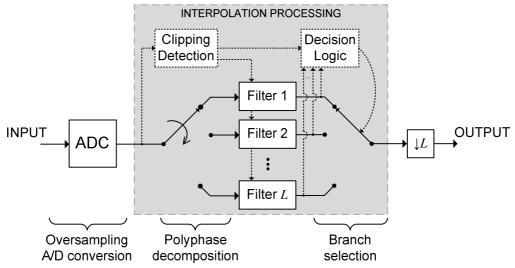

The amount of literature about the clipping effects in receiver side seems to be somewhat limited but some compensation solutions do exist. T. Tomioka *et al.* [37] have proposed an interpolation technique for clipping noise suppression in cognitive radio transceivers. It requires an oversampling ADC so that sampling rate is high compared to the signal band of interest, although the band can be very wide already in case of cognitive radio. Suggested oversampling factors (OSFs) in the paper [37] were two and four. The algorithm starts with searching a cluster of clipped samples. Then polynomial interpolation, using two unclipped samples from before and after the cluster, is applied to the clipped samples. In this case, the polynomial interpolation refers to linear interpolation when the OSF is two or cubic polynomial if the OSF is four. This is a pre-interpolation stage which makes a main interpolator perform better.

T. Tomioka *et al.* [37] have used a fractional delay FIR filter as a main interpolator, which impulse response is a sampled and truncated sinc function. The oversampled signal can be thought through a polyphase decomposition where samples Ln + a are in the same branch. Here the oversampling factor is denoted with L, the sample index is n and the polyphase branch index is a. The sinc interpolation is performed so that the center tap of the sinc impulse response is aligned with a clipped sample. Then a proper polyphase branch is chosen and a new value for clipped sample is calculated using the sinc-based polyphase filter of that branch. According to the paper [37] branch index a is selected by multiplying the nearest unclipped sample from both sides of the cluster with the corresponding sinc value. Then the sample that gives larger value is selected and the branch related to that sample is chosen.

Good compensation performance can be achieved with the interpolation of the over-sampled signal. Especially in wideband systems, the efficiency of compensation schemes is very important. Therefore, partially similar type interpolation methods as presented in [37], but with more optimized implementation and better performance, are proposed in Section 4.3 of this thesis.

# 3. RADIO RECEIVER ARCHITECTURES AND ANALOG-TO-DIGITAL CONVERTERS

This chapter is devoted for the requirements of analog-to-digital converters in different types of radio receivers. In the past, an ADC was not the main concern because most of the receiver's selectivity was implemented with analog components and the digitalization was performed at a low center frequency. However, a modern trend is to reduce analog components and move the ADC as close to the antenna as possible in the receiver chain [26]. By cutting down the number of analog parts, more configurability and better integrability as well as savings in size and power dissipation can be achieved. The ultimate goal will be the so-called software defined radio. This sets significantly stricter requirements for ADCs because most of the signal processing is done in the digital domain.

Section 3.1 first discusses about the key parameters of analog-to-digital converters and what kind of trade-offs there are between them in practical ADCs. Then, some of the most common radio receiver architectures are presented in Section 3.2. Also architectures' impacts on the ADC requirements are mentioned. After that, Section 3.3 presents a few specifications of modern wireless standards and summarizes their effect on the analog-to-digital converters.

# 3.1. Trade-Offs Between Speed, Resolution and Power Dissipation

Wireless system standards have different kinds of requirements for the dynamic range. Resolution of an analog-to-digital converter, i.e. number of bits in ADC, essentially defines the maximum possible dynamic range. That is because the resolution describes the size of the LSB which actually is the smallest change in a signal that the ADC can accurately describe in the digital domain. The Equation (2.4) gives SQNR for an ideal quantizer and therefore gives another point of view to what kind of effect resolution has on dynamic range. It is worth noticing that the dynamic range of an actual ADC is de-

termined not only by the number of bits but also by the linearity of the ADC. Different kinds of nonlinearities cause spurious frequency components that reduce dynamic range of the ADC.

Dynamic range and linearity are particularly important in a wideband receiver where several signal bands are digitized as a whole. Some signal bands can be significantly stronger than others and the difference can be in the order of tens of dB's. There is usually automatic gain control in front of the ADC so that the received waveform is properly scaled for the full-scale range of the ADC. The scaling is based on strength of the overall waveform and therefore sufficient resolution is needed to detect also the weakest signals and not only the strongest. If the weak signal is not buried in quantization noise, i.e. resolution is high enough, problems may still occur due to spurious frequencies. The nonlinear behavior of the ADC may cause the spurious frequencies stemming from the strong signals to fall on top of the weak signal. [27]

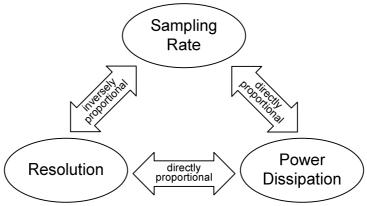

Although dynamic range can be increased by using a higher resolution converter, there are inevitable trade-offs. First of all, high resolution converters typically have low sampling rates. Dependency of resolution and speed varies between different ADC architectures but it can always be seen. [24], [41] Another issue is the trade-off between resolution and power dissipation. High precision converters are likely to consume more power due to their structure. [31] This is important consideration particularly in mobile devices because of their limited amount of energy stored in a battery. Added to this, the power dissipation is directly proportional to the sampling rate of the ADC. This is because the most of the power is consumed in a sample-and-hold circuit and comparators. ADC architecture affects the number of comparators and thus different architectures can have significantly different power consumption. [24]

Figure 3.1 pulls together the relationships between the three discussed performance parameters of ADCs. When considering ideal analog-to-digital converters theoretically, these trade-offs are not directly visible. Nevertheless, in practice the trade-offs are strongly present even in modern ADCs. The relationships between the sampling rate, the resolution and the power dissipation are not necessarily linear – at least not for all ADC architectures [24]. Figure 3.1 visualizes in a simplified manner that power dissipation is increased if sampling rate and/or resolution is increased. It also shows the fact that high-resolution converters tend to have lower sampling rates for given cost and power dissipation.

**Figure 3.1.** *Illustration of trade-offs between the three main performance parameters in analog-to-digital converters.*

#### 3.2. Common Receiver Architectures

This section is devoted to present the most common radio receiver architectures. Advantages and disadvantages of every architecture are discussed. Especially the ADC related aspects are considered.

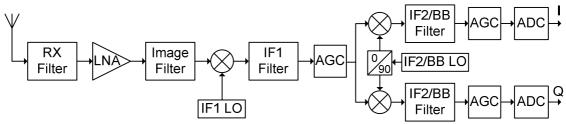

#### 3.2.1. Superheterodyne Receiver

One of the most popular radio receiver architectures in the past has been superheterodyne. Despite its advantages, technology improvements and a need for configurability have nowadays led to receiver architectures which have less analog components. Basic principle of the superheterodyne receiver is depicted in Figure 3.2. After proper RF filtering and amplification the signal is mixed to the first (constant) IF. This is usually done by tuning the LO (local oscillator) frequency so that regardless of the original center frequency of the received signal it is always mixed to the same IF. The receiver uses two separate IF stages to relieve filter requirements related to selectivity as well as image suppression. IQ mixing is used to bring the signal to the second (lower) IF or baseband (BB). After the final channel selection filtering, the I and Q signals are digitized with separate analog-to-digital converters. [31]

**Figure 3.2.** Block diagram of a traditional superheterodyne receiver with two IF stages, modified from [19], [31].

There is a substantial amount of analog processing in the superheterodyne receiver. Filtering, mixing and channel selection are all done before the analog-to-digital conversion. Therefore requirements are rather modest for an ADC considering linearity, dynamic range and bandwidth, especially because the final IF is usually rather low or even zero. Main disadvantages in the superheterodyne architecture are the poor configurability and analog parts that are challenging to integrate. [19]

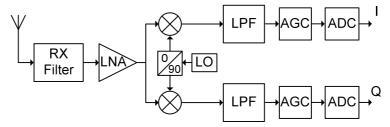

#### 3.2.2. Direct Conversion Receiver

Direct conversion architecture has a simpler analog side than the superheterodyne. It employs only a single mixing stage as illustrated in Figure 3.3. The direct conversion receiver has only the RF filtering and amplification stages before the signal is mixed to baseband. Therefore the LO frequency has to be tunable according the center frequency of the received signal as it was the case also with the superheterodyne architecture. Due to the IF being zero the image suppression filtering is not required. After IQ mixing, low-pass channel filtering is applied separately for both branches before the analog-todigital conversion. If the zero IF is not desirable, another option is to use some low frequency near the baseband. This is usually called a low-IF receiver. The rather simple structure of the direct conversion receiver means better integration capability, lower power consumption and some savings in component costs. On the contrary, there are more problems with the DC offset and second-order distortion when operating around the baseband. Additionally, I/Q mismatch is a problem in direct conversion receivers. It is stemming from imbalance in the I/Q mixing stage and in the branch components (low-pass filters, etc.). [19], [31] Direct conversion receivers are frequently proposed for implementing multi-standard software defined radios, see e.g. [36] and the references therein.

**Figure 3.3.** Block diagram of a direct conversion receiver with a single I/Q mixing stage, which converts the received signal to the baseband before the analog-to-digital conversion, modified from [19], [31].

Basic direct conversion architecture doesn't provide so much configurability because some amount of analog hardware is still needed. On the other hand, nowadays more wideband direct conversion receivers are designed. It means that several channels or even several separate signal bands can be digitized as a whole. There can be significant differences in the power levels of the separate signal bands and hence the large dynamic range has to be taken into account in the requirements for all receiver components. From the ADC point of view, requirements are rather relaxed if only a single channel is digitized at a time. This is because the analog filtering is rather selective and the signal with relatively low bandwidth is digitized at the baseband. [19] In the wideband direct conversion receiver, the dynamic range and the resolution as well as linearity of the ADC become key issues. High resolution is needed to make detection of weak signals possible when there are significantly stronger signals present in neighboring frequency bands. Nonlinearities in the ADC cause intermodulation distortion which means that signals at different frequency bands may interfere with each other.

#### 3.2.3. RF-Sampling Receiver

An RF receiver employing RF sampling would be highly desirable architecture option for software defined radios due to its configurability for various wireless standards. Figure 3.4 shows the simple structure of the RF receiver. The coarse receive filtering doesn't implement strict selectivity but only prevents excessive aliasing and thus the signal to be digitized can be very wideband. In practice, the bandwidth can be tens of megahertz or even hundreds of megahertz while the dynamic range can be as much as 100 dB. This sets harsh requirements especially for the ADC and practical implementations are somewhat out of the question with today's technology. This is especially true, if the power consumption limitations and manufacturing costs of mobile terminals are considered. Additionally, the quickly changing signal dynamics require short reaction times from the automatic gain control and this requirement is challenging to meet with this kind of single-stage gain control. [31] Improper input signal conditioning for the ADC may cause severe nonlinear distortion. This topic is elaborated further in Section 4.1. Moreover, the jitter (timing uncertainty) caused by the sampling circuit and sampling clock is also one major problem in RF receivers. This is because the highfrequency signals are sensitive for timing errors. On the other hand, the RF-sampling receiver provides high integration capability as well as flexibility to choose exact signal bands in the digital domain.

**Figure 3.4.** Block diagram of RF receiver with only minimal filtering and amplification before analog-to-digital conversion, modified from [31].

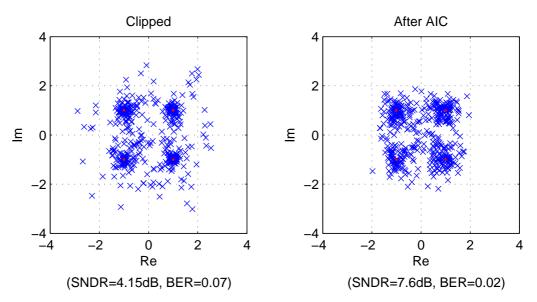

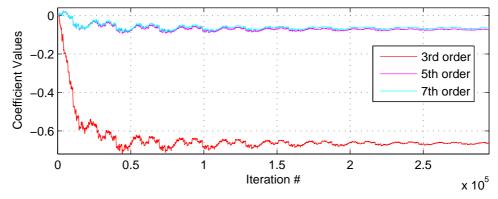

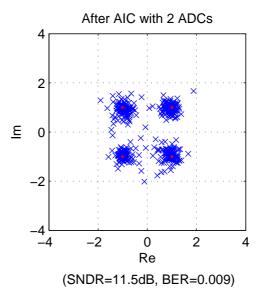

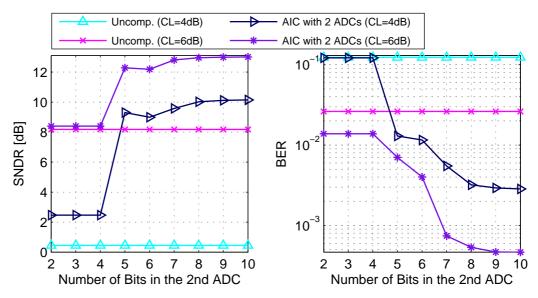

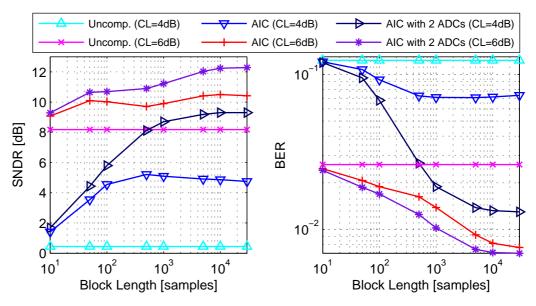

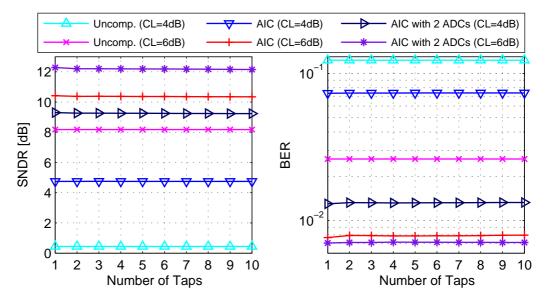

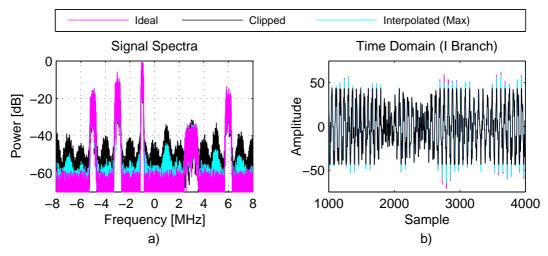

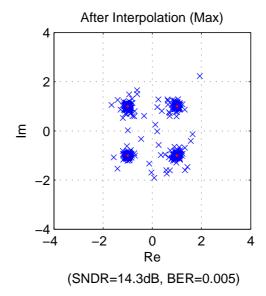

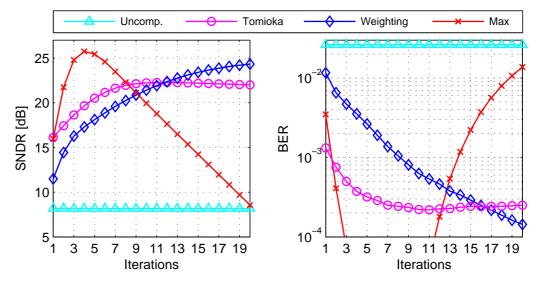

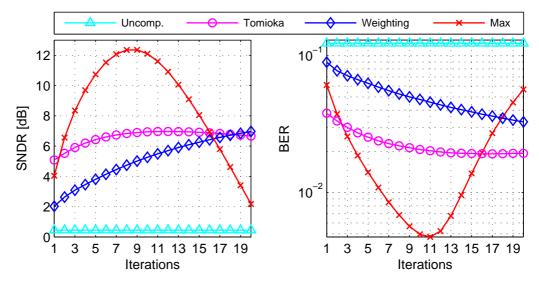

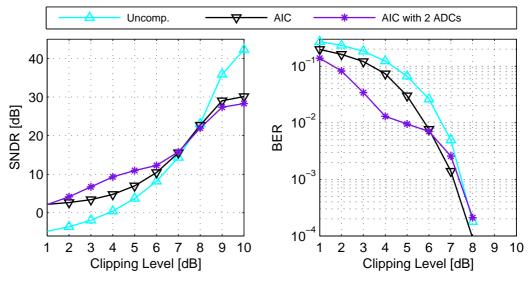

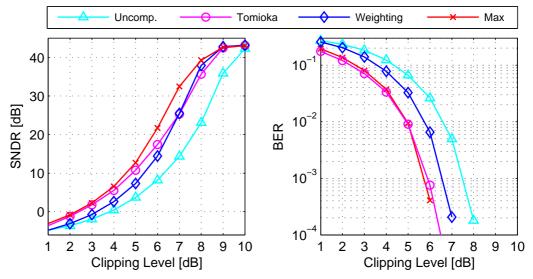

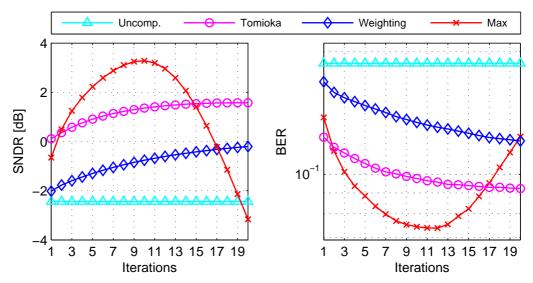

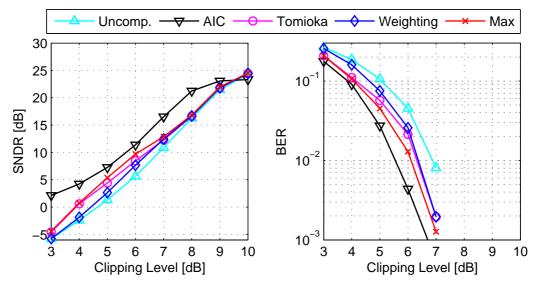

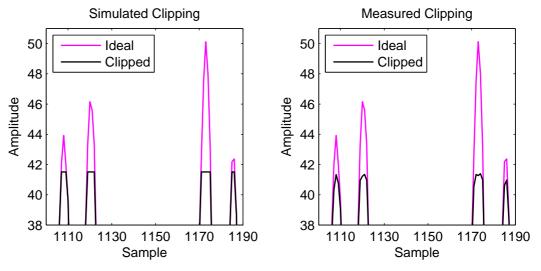

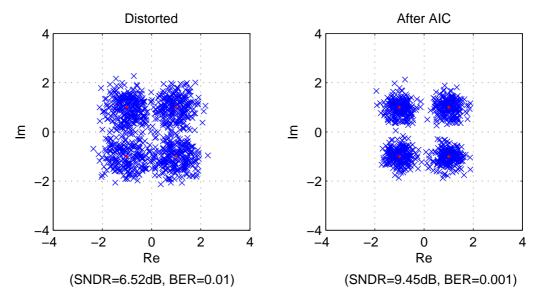

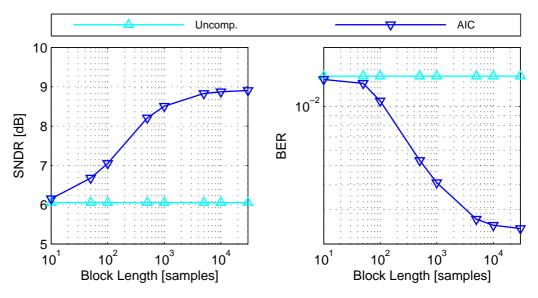

## 3.3. System Performance Requirements