## TERO JOENTAKANEN EVALUATION OF HLS MODULES FOR ASIC BACKEND

Master of Science thesis

Examiner: Prof. Timo D. Hämäläinen Examiner and topic approved by the Faculty Council of the Faculty of Computing and Electrical Engineering on 17th August 2016

## ABSTRACT

TERO JOENTAKANEN: Evaluation of HLS modules for ASIC backend Tampere University of Technology Master of Science thesis, 71 pages May 2017 Master's Degree Programme in Electrical Engineering Major: Embedded systems Examiner: Prof. Timo D. Hämäläinen Keywords: High-level synthesis, System-on-Chip, ASIC backend design

Digital systems continue growing in complexity, but the design and verification productivity has not been able to improve in the same manner, which has led to a productivity gap. Raising the abstraction level of the design with high-level synthesis (HLS) has been proposed to increase productivity. However, at the higher abstraction level, the designer has less control on the generated register-transfer level (RTL) code, which might cause problems later in the design flow. Moreover, certain design steps might be impractical to carry out with HLS.

This thesis work investigates if HLS is compliant with an existing ASIC implementation flow. The research is conducted by creating an IP (intellectual property) block with a modern HLS tool and passing the generated RTL code through the various steps in the flow. The quality of results and design effort are also compared to the manually coded RTL implementation of the same IP.

The HLS tool and the generated RTL code are found mostly compliant with the existing flow, but a few problems are identified in the ECOs (engineering change orders) and technology-specific component instantiation. The HLS design has almost equal physical area with the hand-written RTL design, and it meets the given timing constraints. Design effort with HLS is estimated 20-50% smaller compared to traditional RTL design, and the C++ code contains 60% fewer lines of code than the manually written VHDL code.

# TIIVISTELMÄ

**TERO JOENTAKANEN**: HLS-lohkojen evaluointi ASIC-piirien toteutusvuossa Tampereen teknillinen yliopisto

Diplomityö, 71 sivua Toukokuu 2017 Sähkötekniikan koulutusohjelma Pääaine: Sulautetut järjestelmät Tarkastaja: Prof. Timo D. Hämäläinen Avainsanat: Korkean tason synteesi, System-on-Chip, ASIC-piirien toteutus

Digitaalijärjestelmät kasvavat yhä monimutkaisemmiksi. Suunnittelun ja varmennuksen tuottavuus ei ole kuitenkaan pysynyt tämän kehityksen perässä, mikä on ajan myötä johtanut tuottavuusvajeeseen. Eräs ratkaisu tuottavuuden parantamiseksi on nostaa suunnittelun abstraktiotasoa käyttämällä korkean tason synteesiä (high-level synthesis, HLS). Korkeampi abstraktio rajoittaa kuitenkin suunnittelijan mahdollisuuksia vaikuttaa tuotettuun rekisterisiirtotason (register-transfer level, RTL) kuvaukseen ja saattaa myös vaikeuttaa suunnittelun muita vaiheita.

Tässä diplomityössä tutkitaan HLS:n soveltuvuutta ASIC-piirien toteutukseen. Tutkimusta varten luodaan IP-lohko (Intellectual Property) käyttäen HLS-työkalua, jonka tuottama RTL-koodi viedään suunnitteluvuon eri vaiheiden läpi. Myös työmäärää ja tulosten laatua verrataan käsinkirjoitettuun RTL-kuvaukseen, joka samasta IP:stä on saatavilla.

Tässä työssä käytetty HLS-työkalu ja sen tuottama RTL-koodi osoittautuvat soveltuvan olemassa olevaan suunnitteluvuohon, mutta myös muutamia ongelmia nousee esille ECO-muutoksissa (Engineering Change Orders) ja teknologiakomponenttien käytössä. HLS-lohkon pinta-ala on lähes sama kuin käsinkirjoitetulla, ja sen ajoitus pysyy vaadituissa rajoissa. Työmäärä HLS:llä on arviolta 20–50% pienempi verrattuna perinteiseen RTL-suunnitteluun, ja C++-koodi sisältää 60% vähemmän koodirivejä kuin käsinkirjoitettu VHDL-kuvaus.

# PREFACE

This thesis work was done in the SoC organization of Nokia during fall 2016 and early 2017.

I would like to thank all of my colleagues for the great working environment, and also for the support and guidance they have provided for this thesis work. Especially I want to thank my supervisors Dr. Erno Salminen and Prof. Timo D. Hämäläinen for their excellent and valuable feedback. I also want to thank my line manager Jyrki Hyrsylä for the opportunity to do this thesis at Nokia, and Dr. Ari Kulmala for providing an interesting topic to the thesis. Many thanks also to Rich Toone and Richard Langridge at Mentor Graphics for their excellent support in tool-related matters.

Finally, I want to thank my family and friends for supporting me during this thesis work and the many years of studies.

Tampere, 4.5.2017

Tero Joentakanen

# TABLE OF CONTENTS

| 1. | Introduc                                                | tion                                        | 1  |  |  |  |  |  |  |

|----|---------------------------------------------------------|---------------------------------------------|----|--|--|--|--|--|--|

| 2. | ASIC de                                                 | $\operatorname{sign}$                       | 3  |  |  |  |  |  |  |

|    | 2.1 Abs                                                 | straction levels                            | 5  |  |  |  |  |  |  |

|    | 2.2 Des                                                 | sign flow                                   | 7  |  |  |  |  |  |  |

|    | 2.3 Pro                                                 | oductivity                                  | 8  |  |  |  |  |  |  |

| 3. | High-leve                                               | el synthesis (HLS)                          | 11 |  |  |  |  |  |  |

|    | 3.1 Fun                                                 | ndamentals                                  | 12 |  |  |  |  |  |  |

|    | 3.1.1                                                   | Compilation and optimization                | 13 |  |  |  |  |  |  |

|    | 3.1.2                                                   | Constraints                                 | 14 |  |  |  |  |  |  |

|    | 3.1.3                                                   | Resource allocation, scheduling and binding | 16 |  |  |  |  |  |  |

|    | 3.1.4                                                   | RTL generation                              | 17 |  |  |  |  |  |  |

|    | 3.2 Adv                                                 | vantages                                    | 17 |  |  |  |  |  |  |

|    | 3.3 Pro                                                 | blem areas                                  | 20 |  |  |  |  |  |  |

| 4. | Case stu                                                | dy                                          | 22 |  |  |  |  |  |  |

|    | 4.1 Dec                                                 | cimator                                     | 22 |  |  |  |  |  |  |

|    | 4.1.1                                                   | Cascaded integrator-comb filter (CIC)       | 23 |  |  |  |  |  |  |

|    | 4.1.2                                                   | Polyphase decimator                         | 24 |  |  |  |  |  |  |

|    | 4.1.3                                                   | Arbiter                                     | 25 |  |  |  |  |  |  |

|    | 4.1.4                                                   | Packager                                    | 26 |  |  |  |  |  |  |

|    | 4.2 Cat                                                 | apult HLS                                   | 26 |  |  |  |  |  |  |

|    | 4.2.1                                                   | User interface                              | 27 |  |  |  |  |  |  |

|    | 4.2.2                                                   | Hardware interfaces                         | 28 |  |  |  |  |  |  |

|    | 4.2.3                                                   | Verification                                | 29 |  |  |  |  |  |  |

| 5. | Research                                                | questions                                   | 30 |  |  |  |  |  |  |

|    | 5.1 Tec                                                 | hnology library characterization            | 30 |  |  |  |  |  |  |

|    | 5.2 Tec                                                 | hnology library abstraction                 | 31 |  |  |  |  |  |  |

|    | 5.3 Design-for-testability (DFT) structures in RTL code |                                             |    |  |  |  |  |  |  |

|    | 5.4                  | Engineering change order (ECO) $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 34 |

|----|----------------------|------------------------------------------------------------------------------------------|----|

|    | 5.5                  | Static code analysis                                                                     | 34 |

|    | 5.6                  | Logical equivalence checking (LEC)                                                       | 35 |

|    | 5.7                  | Area and timing                                                                          | 36 |

|    | 5.8                  | Power efficiency                                                                         | 37 |

| 6. | Rest                 | ults                                                                                     | 41 |

|    | 6.1                  | Design entry and effort                                                                  | 41 |

|    | 6.2                  | Technology library characterization                                                      | 42 |

|    | 6.                   | 2.1 Flow evaluation                                                                      | 46 |

|    | 6.3                  | Technology library abstraction                                                           | 47 |

|    | 6.                   | 3.1 Memory libraries                                                                     | 47 |

|    | 6.                   | 3.2 Custom components                                                                    | 51 |

|    | 6.4                  | Design-for-testability (DFT) structures in RTL code                                      | 51 |

|    | 6.5                  | Engineering change order (ECO)                                                           | 52 |

|    | 6.6                  | Static code analysis                                                                     | 54 |

|    | 6.7                  | Logical equivalence checking (LEC)                                                       | 55 |

|    | 6.8                  | Area and timing                                                                          | 56 |

|    | 6.9                  | Power efficiency                                                                         | 61 |

| 7. | Reco                 | ommendations                                                                             | 62 |

|    | 7.1                  | Designers                                                                                | 62 |

|    | 7.2                  | Tool developers                                                                          | 63 |

| 8. | $\operatorname{Con}$ | clusions                                                                                 | 65 |

| Bi | bliogi               | raphy                                                                                    | 67 |

# LIST OF ABBREVIATIONS AND SYMBOLS

| AC             | Algorithmic C                           |

|----------------|-----------------------------------------|

| AES            | Advanced Encryption Standard            |

| ANSI           | American National Standards Institute   |

| ASIC           | Application-Specific Integrated Circuit |

| ASSP           | Application-Specific Standard Product   |

| BIST           | Built-In Self Test                      |

| CDC            | Clock Domain Crossing                   |

| CDFG           | Control and Data Flow Graph             |

| CIC            | Cascaded Integrator-Comb filter         |

| CMOS           | Complementary Metal-Oxide Semiconductor |

| CPLD           | Complex Programmable Logic Device       |

| DFG            | Data Flow Graph                         |

| $\mathrm{DFT}$ | Design For Testability                  |

| DMA            | Direct Memory Access                    |

| DSP            | Digital Signal Processing               |

| ECO            | Engineering Change Order                |

| FIFO           | First-In First-Out                      |

| FIR            | Finite Impulse Response filter          |

| $\mathrm{FF}$  | Flip-Flop                               |

| FPGA           | Field-Programmable Gate Array           |

| FSM            | Finite-State Machine                    |

| GUI            | Graphical User Interface                |

| HDL            | Hardware Description Language           |

| HLS            | High-Level Synthesis                    |

| IC             | Integrated Circuit                      |

| IP             | Intellectual Property                   |

| IQ             | In-phase and Quadrature                 |

| LEC            | Logical Equivalence Checking            |

| LTE            | Long-Term Evolution                     |

| LUT            | Look-Up Table                           |

| NRE            | Non-Recurring Engineering               |

| PCB            | Printed Circuit Board                   |

| RAM            | Random Access Memory                    |

| RTL            | Register-Transfer Level                 |

| SAIF           | Signal Activity Interchange Format      |

| $\mathbf{SC}$  | SystemC                                 |

|                |                                         |

| $\operatorname{SoC}$ | System-on-Chip                              |

|----------------------|---------------------------------------------|

| TCL                  | Tool Command Language                       |

| TLM                  | Transaction-Level Modeling                  |

| UART                 | Universal Asynchronous Receiver/Transmitter |

| USB                  | Universal Serial Bus                        |

| VHDL                 | VHSIC Hardware Description Language         |

| VHSIC                | Very High Speed Integrated Circuit          |

| XML                  | Extensible Markup Language                  |

|                      |                                             |

## 1. INTRODUCTION

Digital systems have grown extremely complex over the years, and the amount of functionality integrated in these systems will only keep increasing in the future. Designing and manufacturing an integrated circuit (IC) (Figure 1.1) may require years worth of design effort from hundreds of engineers. At the same time, the demand for shorter time-to-market and reduced costs limit the possibility to increase the product development time or the size of the engineering teams. Hence, the productivity per engineer has to improve to enable the development of the increasingly complex systems.

Figure 1.1 Integrated circuit on a printed circuit board [51].

Over the past two decades, the design work has been mainly carried out at registertransfer level (RTL) using hardware description languages (HDL), such as VHDL or Verilog. At this abstraction level, the designer describes the digital logic on a cycleaccurate basis, implying every register in their code. However, as the digital systems continue growing in complexity, designing them at RTL will eventually become impractical. Therefore, designers are nowadays looking to raise the abstraction level such that instead of hand-coding the architecture at RTL, they would describe the algorithmic behavior, which would then be synthesized to RTL using a high-level

#### 1. Introduction

#### synthesis (HLS) tool.

The demand for a higher abstraction level has led to the development of a large number of HLS tools, both academic and commercial. Many research papers have addressed this abundance by providing evaluation methods for choosing a suitable tool [27, 23]. Previous studies have also compared HLS to the traditional RTL design, and the current generation of tools have shown promising results in terms of design productivity and quality of results [53, 54, 17]. However, as these papers focus on the frontend design (i.e. generating the RTL description out of the given algorithm), only few of them consider the subsequent design steps and checks that the RTL code goes through before it is implemented as a physical circuit on silicon. Nevertheless, it is possible that the tool-generated RTL code contains structures that are not feasible to implement or otherwise cause problems in the later stages of the design flow.

This thesis work evaluates the suitability of HLS-generated RTL code to the backend design flow of ASICs (Application-Specific Integrated Circuit) and develops means to integrate HLS methodology into an existing RTL design flow. The purpose of this thesis is also to provide HLS tool vendors with feedback on how to improve the tools in the future to make them more suitable for ASIC design. This work is continuation to previous theses [45, 18, 30, 15] that have evaluated the frontend design flow with several HLS tools.

This study is carried out by creating a HLS design and passing the generated RTL code through the various steps of the backend implementation flow. Although the main focus of this thesis is on the backend flow, the HLS design is also briefly compared to the existing hand-coded RTL design in terms of the quality of results and design effort, and the problems are assessed that are still present in the current tools.

The structure of this thesis is following. Chapter 2 covers the design process of ASICs and introduces the abstraction levels of the design flow. The fundamentals of HLS are described in Chapter 3, as well as the advantages and problem areas of the current generation of the HLS tools. Chapter 4 presents the design that is used as a test case and the HLS tool that is evaluated in this thesis work. The research questions are covered in Chapter 5, which is followed by the results in Chapter 6. Chapter 7 provides recommendations for both the designers looking to use HLS and the tool vendors to further develop the HLS tools. Finally, Chapter 8 concludes the results of this thesis work.

## 2. ASIC DESIGN

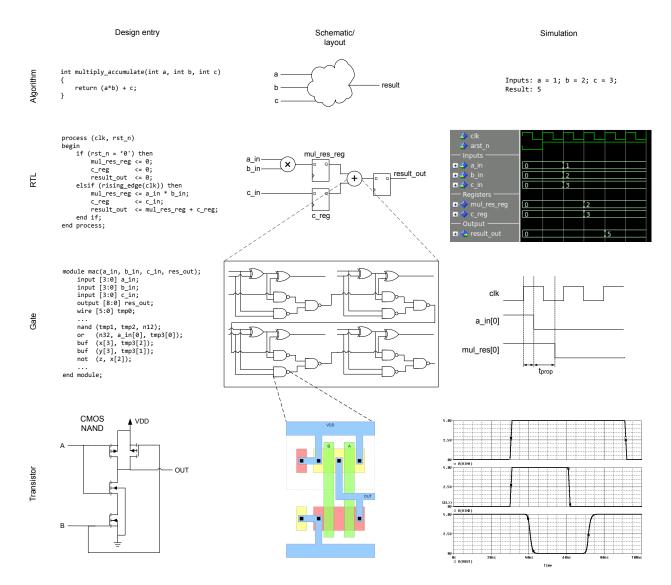

Digital systems are extremely complex nowadays. A single system might contain several processors, memories, and peripherals, which together may comprise billions of transistors [37]. Therefore, the only practical way to realize these systems is to use integrated circuits (IC) where a large amount of transistors are integrated on a single silicon die. In the past, the systems were built of several chips so that each component, such as processor or memory, had its own respective IC. However, as the level of integration has increased, a single chip has been able to contain more functionality, and nowadays whole systems can be included on a single chip. This kind of system is commonly known as a System-on-Chip (SoC) [38]. An example of a modern SoC is shown in Figure 2.1 that represents a layout of Qualcomm's Snapdragon 810 mobile chip used in smartphones and tablets. As can be seen, the chip contains several functional blocks, such as processing units, LTE (Long-Term Evolution) modem, and positioning systems.

Figure 2.1 Layout of Qualcomm's Snapdragon 810 SoC [10].

#### 2. ASIC design

For many applications, general-purpose processors and microcontrollers are suitable for implementing the desired functionality. However, these general-purpose components are typically designed for a wide range of applications, and thus they often contain excessive functionality. This overhead means wasted area and increased power consumption which might be impractical for certain applications. Furthermore, the performance of these components might not be sufficient for applications that require heavy computation and low latency [11]. When more specialized components are needed, there might be readily available ICs that are designed for a specific functionality. These application-specific standard products (ASSP) are typically available for applications that are needed often and by many manufacturers [38]. A typical example of an ASSP would be a bridge component for connecting a bus using USB (Universal Serial Bus) protocol to a UART (Universal Asynchronous Receiver/Transmitter) bus.

If there is no suitable component readily available, the manufacturer might have to design a customized logic circuit. In some cases, it might also be cheaper to produce own circuit instead of buying them from another manufacturer when a large amount of components is needed. In general, there are two options for implementing customized digital logic: one option is to use a programmable logic device, such as a FPGA (Field-Programmable Gate Array) or a CPLD (Complex Programmable Logic Device); the other option is to design an ASIC that is a customized IC where the logic is fixed and cannot be altered after fabrication.

There are naturally trade-offs for both options. Since the programmable devices are designed to be used in many applications, they will contain extra logic which degrades their performance and power efficiency [19]. On the other hand, designing them contains fewer risks since they allow fixing bugs afterwards by reconfiguring the logic. In contrast, a defective ASIC would have to be completely remanufactured in the worst case.

The development time and cost are also significant factors in the choice between an ASIC and a programmable device. The development time for FPGAs can be in the order of months whereas an ASIC design cycle may take more than a year to complete [19]. Moreover, the NRE (non-recurring engineering) costs of an ASIC are tremendously higher: creating the masks and fabricating the first sample might cost millions of dollars [19]. For FPGA designs, the NRE costs can be an order of magnitude lower. However, the unit price of an ASIC is generally less compared to a programmable device. Therefore, the more chips are needed, the more cost-effective option the ASIC will be.

#### 2.1 Abstraction levels

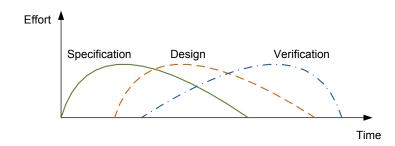

Digital logic is modeled at several abstraction levels to manage the design complexity [6]. The most often considered levels are algorithm level, register-transfer level, gate level, and transistor level. This is not an exhaustive list, however, as one might also include intermediate levels between these. For example, transaction-level modeling (TLM) can be used between algorithm level and RTL, so that the system is modeled at the level of transactions, such as sending a data packet to another module [9]. Moreover, all abstraction levels can be divided into more fine-grained levels. For instance, algorithm-level model may be timed or untimed, or it might use bit-accurate data types instead of floating point numbers. Nevertheless, these four abstraction levels are the main ones that are considered in most designs.

Figure 2.2 illustrates the abstraction levels in three different domains. Each row represents an abstraction level such that the uppermost row shows the highest abstraction level – which is the algorithm level – and below are the RTL, gate level, and transistor level in a descending order. The figures on the left show a typical input format at that particular abstraction. For example, in the case of RTL, the input is a VHDL process that implements the RTL architecture. The figures in the middle show a schematic or layout that represents the logic, and the rightmost figures show a typical output format that a simulator might provide at that abstraction level. At algorithm and RT levels, the figure shows an implementation of a multiply-accumulate circuit that calculates the result of ab + c. For the other two abstraction levels, only parts of the circuit are shown due to increasing complexity of the presentation.

Algorithm level is used to describe the behavior of the logic. In other words, it describes the function that relates its inputs to outputs, and it has no concept of timing. Algorithm level is often used in behavioral modeling, where the algorithm designer explores different options for the algorithm and investigates which of them fulfills the given specifications. Once a suitable algorithm is found, the model is often refined to a more accurate representation of the hardware [9]. For example, numbers can be presented with formats that are more suitable for hardware implementation, which also allows using the model to define the minimum data width that does not cause too much quantization noise in the results. A bit-accurate model has also the advantage that it can generate reference data for the functional verification that is carried out at lower abstraction levels.

A RTL description introduces timing to the model at the level of clock cycles [6]. Events happen only at the clock edges, and all the operations related to that event

**Figure 2.2** Abstraction levels in digital design. From top to bottom: algorithm level, RTL, gate level, and transistor level [49].

are executed instantaneously. RTL describes the data flow between registers, and the operations between registers are defined only at high level. For example, the RTL code might describe that the outputs of two registers are summed and stored to another register, but it does not care about the implementation details of the adder. RTL is nowadays the main abstraction level for designing digital logic.

At gate level, the logic is implemented with gates that are primitive logic elements such as NOT, AND, and OR [6]. Gate-level description is already close to the actual physical implementation. If the physical characteristics of the gates are known, it is possible to get rather accurate estimates of the design area and power, and it also allows analyzing the timing of the circuit. In a typical design flow, gate-level netlist is automatically generated from the hand-written RTL description using a

#### RTL synthesis tool.

The transistor level is considered mainly in the final layout design before the masks used in the silicon fabrication are created. Since the gate-level abstraction is already a rather accurate representation of the physical circuit, most of the physical design flow that contains, for example, the placing and routing of the components is done at the gate level. The transistor level is, nonetheless, important for the engineers developing new technologies and creating standard cell libraries. However, at transistor level, the design is no longer digital, but involves also the analog characteristics of the transistors [6].

#### 2.2 Design flow

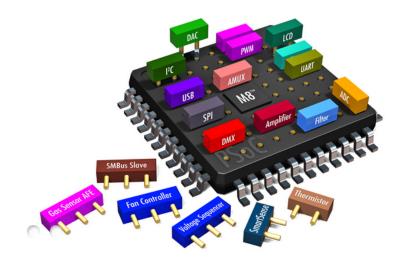

The design flow for digital systems can be roughly divided into three phases: specification, design, and verification. Each of these phases are carried out at several abstraction levels. For example, the specification phase consists of tasks such as specifying the algorithm, RTL architecture, and the target technology of the physical circuit. Hence, these three phases typically proceed in parallel in the design flow. This has been demonstrated in Figure 2.3 that shows how the design phases might progress in a typical ASIC project. It is also common that the design flow contains iteration loops between the phases. For instance, if a bug is found in the functional verification of the RTL, or the synthesized gate-level implementation does not meet the timing constraints, the RTL designer will fix the issue by modifying the RTL code according to the given feedback.

Figure 2.3 Design phases and their effort in the ASIC project timeline.

The design flow starts with the high-level specification of the functionality of the system. This specification is then partitioned and refined into a more detailed description, and eventually to an algorithm or behavioral model. In SoCs, this phase also includes decisions such as how the functionality is split between software and hardware [50]. In ASIC design, the target technology should also be specified

at an early stage to allow evaluating the feasibility of the physical implementation of the system.

The design phase consists of the implementation of the system, which can be generally divided into frontend and backend design [26]. The frontend design consists of implementing the RTL architecure based on the behavioral model provided by the algorithm designer. The backend design comprises the physical implementation steps, such as mapping the RTL structures to standard cells of the target technology (i.e. RTL synthesis), placing and routing the cells on the physical layout, and checking that the physical netlist meets all of the requirements related to the physical parameters, such as area, timing, and power.

Functional verification ensures that the designed logic behaves as described in the specification [9]. At algorithm level, the behavioral model is verified by simulating the model and examining the performance metrics or other measures depending on the application. As the high-level model is transferred to lower abstraction levels, the verification mainly checks that the functionality is equivalent with the higher level model. This can be accomplished by simulating both models with same stimulus and comparing their outputs, or the equivalence can be shown formally through a mathematical proof. In ASIC design, the role of functional verification is extremely important since even a small bug can make the chip unusable, which might lead to enormous costs.

### 2.3 Productivity

The exponential growth of digital systems increases the design and verification effort constantly. Increasing the engineering team sizes or extending the design cycle in the same vein is impractical, and hence the amount of logic designed per engineer has to increase. In other words, design productivity has to improve. There have been many technology advancements in the past that have improved productivity. Table 2.1 lists some of them and provides also estimates for their associated design productivity improvement [13]. Two methods that are especially relevant to this thesis work are design reuse and higher abstraction level.

Design reuse has been realized in the form of IP (intellectual property) blocks [47]. These IP blocks are design entities that implement certain functionality and can be instantiated multiple times in the system as well as reused in several chips. IP blocks can be relatively simple single-function designs such as FIFO (first-in firstout) buffers, but they can also comprise whole processor subsystems that are built of several smaller IPs. IPs typically use standardized bus interfaces such that they

| Nome         1990         (Guter Year: Designer)         Afforded           In-Hoase Place and Route         1993         38.90 %         5.55K HW         PD Integration         Automated block plecement and routin, time           Tail-Thin Engineer         1995         63.60 %         9.09K HW         Chipsicrouit/PD         Engineer capible of purvising all regined task complete a design block, from RTL to GDSH           Reuse—Small Blocks         1997         340 %         40K HW         Circuit/PD         Engineer capible of purvising all regined task complete a design block, from RTL to GDSH           Reuse—Large Blocks         1997         340 %         40K HW         Circuit/PD         Blocks from 75.00-14 gates           Reuse—Large Blocks         1999         38.90 %         56K HW         Chipsicrouit/PD         Blocks from 75.00-14 gates           RTL Functional Verification Tod         2001         63.60 %         91K HW. 87K SW         Chipsicrouit/PD         synthesis to GDSH fittorght C place and routing. Unsertained block placement and spees from RTL incident Sitte           Transactional Modeling         2005         60 %         200K HW, 250K SW         SW development verification to sate targets from RTL incident Sitte           Very Large Block Reuse         2007         200 %         600K HW, 323K SW         Chipcircuit/PD data match incident and sinalabrock for GDSH matrindent of the verification and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | DTL                             | V    | n l d'i n h         | n L C S                               | G . (G                     |                                                                                                                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------|---------------------|---------------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| In-House Place and Roate         1993         38.90 %         5.55K HW         PD Integration         Automated block placement and routing, trans-<br>from the seniconductor house to the design te<br>wertification           Tall-Thin Engineer         1995         63.60 %         9.09K HW         Chipicitoni/TD<br>Engineer capable of proving and particular<br>complete a design block, from RTL to CDS1           Reuse—Small Blocks         1997         340 %         40K HW         Circuit/TD<br>Engineer capable of proving and particular<br>complete a design block, from RTL to CDS1           Reuse—Large Blocks         1999         38.90 %         56K HW         Circuit/TD<br>Engineer capable of proving and particular<br>complete a design to<br>complete the sentence of the s                                                                                                                                                                                                                    | DT Improvement                  | Year | Productivity Delta  | Productivity<br>(Gates/Year/Designer) | Cost Component<br>Affected | Description of Improvement                                                                                                                                                                                                              |

| Image: Section of the section of the design term         Image: Section of the design term         Image: Section of the design term           Tail-Thin Engineer         1995         6.5.00 %         9.09K HW         Chip-circuit/PD complete a design block, from RTL to CDSH (complete a design block, from RTL to CDSH (complete) and through (complet                                                                                        | None                            | 1990 |                     | 4K HW                                 |                            |                                                                                                                                                                                                                                         |

| Number of the section of the sectin the section of the section of the section of the sec        | In-House Place and Route        | 1993 | 38.90 %             | 5.55K HW                              | PD Integration             | Automated block placement and routing, transferred<br>from the semiconductor house to the design team                                                                                                                                   |

| Control         Control         Control         Verification         Control Control           Reuse—Large Blocks         1999         38.90 %         56K HW         Chipcircuit/PD<br>integration<br>verification         Blocks from 75,000 – 1M gates           IC Implementation Suite         2001         63.60 %         91K HW, 57K SW         Chipcircuit/PD<br>integration         Tightly integrated tool set that goes from RTL<br>synthesis to GDS1 through IC place and rout<br>EDA support           RTL Functional Verification Tool<br>Suite         2003         37.50 %         125K HW, 57K SW         SW development<br>verification         Tightly integrated RTL verification tool steed<br>complete the verification process           Transactional Modeling         2005         60 %         200K HW, 250K SW         SW development<br>verification         Chipcircuit/PD<br>and consisting of behavioral (where the system<br>complete the verification process           Very Large Block Reuse         2007         200 %         600K HW, 523K SW         Chipcircuit/PD<br>everification         Mary identical cores provide specialized proc<br>and verification<br>and verification ostate of ablocks >1M gates; intellectual-property cores<br>and verification         Blocks >1M gates; intellectual-property cores<br>and verification and annihor proces           Software Virtual Prototype         2011         300% SW         1200K HW, 2584K SW         SW development<br>verification         Mary identical cores provide procesor, enabling preformant<br>poremeticant partical protesprovide procesor, enabling                                                                                                                                                                                                                                                                                                                                                                                                                                          | Tall-Thin Engineer              | 1995 | 63.60 %             | 9.09K HW                              |                            | Engineer capable of pursuing all required tasks to<br>complete a design block, from RTL to GDSII                                                                                                                                        |

| Including         Including         Instrumentation         Instrumentation           IC Implementation Suite         2001         63.60 %         91K HW, 87K SW         Chipticinuit/PD<br>integration<br>EDA support         Type           RTL Functional Verification Tool<br>Suite         2003         37.50 %         125K HW, 87K SW         SW development<br>verification         Tightly integrated RTL verification tool suite<br>including all simulations and formal tools need<br>complete the verification process           Transactional Modeling         2005         60 %         200K HW, 250K SW         SW development<br>verification         Tightly integrated RTL verification tool suite<br>including all simulations and formal tools need<br>consisting of behavioral (where the system<br>function has not been partitioned) and archite<br>(where HW and SW arcitectification<br>and verification           Very Large Block Reuse         2007         200 %         600K HW, 323K SW         Chipticruit/PD<br>verification         Blocks > 1M gates; intellectual-property cores<br>or und a main processor; enabling performan<br>power efficiency. and high reuse           Software Vintual Prototype         2011         300% SW         1200K HW, 2584K SW         SW development<br>verification         Virtualization tools used to allow development<br>to complete distion           Reusable Platform Blocks         2013         200% HW, 100% SW         4949K HW, 5168K SW         SW development<br>verification         Virtualization tools used to allow development<br>to completed silicon           Re                                                                                                                                                                                                                                                                                                                                                                                                                                              | Reuse—Small Blocks              | 1997 | 340 %               | 40K HW                                |                            | Blocks from 2,500–74,999 gates                                                                                                                                                                                                          |

| Image: Construction of the system is to GDSI through IC place and rout<br>EDA supportRTL Functional Verification Tool<br>Suite200337.50 %125K HW, 87K SWSW development<br>verificationTiplety integrated RTL verification of suite<br>including all simulators and formal tools need<br>completed the verification processTransactional Modeling200560 %200K HW, 250K SWSW development<br>verificationLevel above RTL including both HW and SW<br>and constring of behavioral (where the system<br>design and rubite<br>(where HW and SW are identified and handed<br>design teams) levelsVery Large Block Reuse2007200 %600K HW, 323K SWChipcircuit/PD<br>evelsBlocks >IM gates, intellectual-property cores<br>and verificationHomogeneous Parallel Processing2009100% HW, 100% SW1200K HW, 2584K SWChipcircuit/PD<br>evelsMany identical cores provide specialized proc<br>and verificationSoftware Virtual Prototype2011300% SW1200K HW, 2584K SWSW development<br>overificationVirtualization tools usite to allow development<br>overificationIntelligent Testbench201237.5% HW1650K HW, 2584K SWSystem design and<br>verificationLike RTL verification tool suite to allow development<br>overificationStilicon Virtual Prototype2015100% HW, 100% SW4949K HW, 5168K SWSystem design and<br>System design and<br>verificationFully functional platform store at a block in 1<br>platform design and<br>verificationHeterogeneous (AMP) Parallel<br>Processing2012100% HW, 100% SW19794K HW, 1036K SWSW development<br>system design and<br>verification <td>Reuse—Large Blocks</td> <td>1999</td> <td>38.90 %</td> <td>56K HW</td> <td>integration</td> <td>Blocks from 75,000–1M gates</td>                                                                                                                                                                                                                                                                                                                                                                                                            | Reuse—Large Blocks              | 1999 | 38.90 %             | 56K HW                                | integration                | Blocks from 75,000–1M gates                                                                                                                                                                                                             |

| Suiteverificationincluding alt simulators and formal tools needsTransactional Modeling200560 %200K HW, 250K SWSW development<br>verificationLevel above RTL, including both HW and SW<br>and consisting of behavioral (where the system<br>design taums) levelsVery Large Block Reuse2007200 %600K HW, 323K SWChip/circuit/PD<br>verificationBlocks >1M gates; intellectual-property coresHomogeneous Parallel Processing2009100% HW, 100% SW1200K HW, 646K SWChip/circuit/PD design<br>and verification<br>around a main processor, enabling performanc<br>power efficiency, and high reuseSoftware Virtual Prototype2011300% SW1200K HW, 2584K SWSW development<br>verificationImelligent Testbench201237.5% HW1650K HW, 2584K SWSystem design and<br>verification of the verification patrioning such as a block in 1Silicon Virtual Prototype2015100% HW, 100% SW4949K HW, 5168K SWSystem design and<br>verificationLike RTL verification patrioning such as a block in 1Silicon Virtual Prototype2015100% HW9897K HW, 5168K SWSystem design and<br>verificationA hardware virtualization tool such as a block in 1Silicon Virtual Prototype2011100% HW, 100% SW19794K HW, 10336K SWSystem design and<br>verificationA hardware virtualization apatrioning such as a block in 1Silicon Virtual Prototype2012100% SW19794K HW, 10336K SWSystem design and<br>verificationA hardware virtualization and SW development in<br>patriom basing con-xhith all mostor performance<br>verificationM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | IC Implementation Suite         | 2001 | 63.60 %             | 91K HW, 87K SW                        | integration                | Tightly integrated tool set that goes from RTL synthesis to GDSII through IC place and route                                                                                                                                            |

| Very Large Block Reuse2007200 %600K HW, 323K SWChip'circuit/PD design and profession of the system function has not been partitioned) and architect (where HW and SW are identified and handed design teams) levelsVery Large Block Reuse2007200 %600K HW, 323K SWChip'circuit/PD design and yerificationBlocks >1M gates, intellectual-property coresHomogeneous Parallel Processing2009100% HW, 100% SW1200K HW, 646K SWChip'circuit/PD design and yerificationMany identical cores provide specialized proc<br>around a main processor, enabling performance<br>power efficiency, and high reuseSoftware Virtual Prototype2011300% SW1200K HW, 2584K SWSW development<br>verificationVirtualization tools used to allow development<br>to completed siliconIntelligent Testbench201237.5% HW1650K HW, 2584K SWSystem design and<br>verificationLike RTL verification tool suite, but also with<br>automation tool suite of the verification<br>patrom sign (e.g., ARM in OMAP)Silicon Virtual Prototype2015100% HW9897K HW, 5168K SWSystem design and<br>verificationA hardware virtualization platform sued as a block in I<br>platform disgn (e.g., ARM in OMAP)Silicon Virtual Prototype2017100% HW19794K HW, 10537K SWSW development<br>verificationMany specifized or platform that enable<br>erificationMany-Core SW Development Tools201960% SW19794K HW, 10537K SWSW developmentEnables compilation and SW oevlopment in<br>main processing SOGsMany-Core SW Development Tools201960% HW, 37.5% SW31671K HW, 45476K SWSW development                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                 | 2003 | 37.50 %             |                                       |                            | including all simulators and formal tools needed to complete the verification process                                                                                                                                                   |

| IndextIndextIndextIndextIndextHomogeneous Parallel Processing2009100% HW, 100% SW1200K HW, 646K SWChip/circuit/PD design<br>and verificationMany identical cores provide specialized proc<br>around a main processor, enabling performanc<br>power efficiency, and high reuseSoftware Virtual Prototype2011300% SW1200K HW, 2584K SWSW development<br>verificationVirtualization tools used to allow development<br>to completed siliconIntelligent Testbench201237.5% HW1650K HW, 2584K SWSystem design and<br>verificationLike RTL verification tool suite, but also with<br>automation of the verification partitioning stepReusable Platform Blocks2013200% HW, 100% SW4949K HW, 5168K SWSystem design and<br>verificationLike RTL verification partitioning stepSilicon Virtual Prototype2015100% HW9897K HW, 5168K SWSystem design and<br>verificationA hardware virtualization platform that enable<br>RTL handoff of a SOCHeterogeneous (AMP) Parallel<br>Processing2017100% HW, 100% SW19794K HW, 10336K SWSW development<br>verificationMany specialized cores provide processing are<br>main processor, which allows for performance<br>efficiency, and high reuseMany-Core SW Development Tools201960% SW19794K HW, 30374K SWSW developmentEnables compilation and SW development in<br>parallel processing SOCsSystem-Level Design Automation<br>(SDA)202360% HW, 37.5% SW31671K HW, 45476K SWSystem design and<br>verificationAutomates true system design on-<br>and off-chij<br>first time, including electroni                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Transactional Modeling          | 2005 | 60 %                | 200K HW, 250K SW                      |                            | Level above RTL, including both HW and SW design<br>and consisting of behavioral (where the system<br>function has not been partitioned) and architectural<br>(where HW and SW are identified and handed off to<br>design teams) levels |

| and verificationand verificationaround a main processor, enabling performance<br>power efficiency, and high reuseSoftware Virtual Prototype2011300% SW1200K HW, 2584K SWSW developmentVirtualization tools used to allow development<br>to completed siliconIntelligent Testbench201237.5% HW1650K HW, 2584K SWSystem design and<br>verificationLike RTL verification tools used to allow development<br>automation of the verification partitioning stepReusable Platform Blocks2013200% HW, 100% SW4949K HW, 5168K SWChip/circuit/PD<br>verificationFully functional platforms used as a block in L<br>platform design and<br>verificationSilicon Virtual Prototype2015100% HW9897K HW, 5168K SWSystem design and<br>verificationA hardware virtualization platform that enable<br>RTL handoff of a SOCHeterogeneous (AMP) Parallel<br>Processing2017100% HW, 100% SW19794K HW, 10336K SWSW development<br>verificationMany specialized cores provide processing ard<br>main processor, which allows for performance<br>efficiency, and high reuseMany-Core SW Development Tools201960% SW19794K HW, 16537K SWSW development<br>sW developmentEnables compilation and SW development in<br>parallel processing SOC'sSystem-Level Design Automation<br>(SDA)2025200% HW, 200% SW95013K HW, 136429K SWSystem design and<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Very Large Block Reuse          | 2007 | 200 %               | 600K HW, 323K SW                      |                            | Blocks >1M gates; intellectual-property cores                                                                                                                                                                                           |

| Intelligent Testbench201237.5% HW1650K HW, 2584K SWSystem design and<br>verificationLike RTL verification tool suite, but also with<br>automation of the verification partitioning stepReusable Platform Blocks2013200% HW, 100% SW4949K HW, 5168K SWChip/circuit/PD<br>verificationFully functional platforms used as a block in Like RTL verification partitioning stepSilicon Virtual Prototype2015100% HW9897K HW, 5168K SWSystem design and<br>verificationAndrawer virtualization platform that enable<br>RTL handoff of a SOCHeterogeneous (AMP) Parallel<br>Processing2017100% HW, 100% SW19794K HW, 10336K SWSW development<br>verificationMany specialized cores provide processing arm<br>main processor, which allows for performance<br>efficiency, and high reuseMany-Core SW Development Tools201960% SW19794K HW, 16537K SWSW development<br>sW developmentEnables compilation and SW development in parallel processing SOCsSystem-Level Design Automation<br>(SDA)202360% HW, 37.5% SW31671K HW, 45476K SWSystem design and<br>verificationAutomates true system design on- and off-chip<br>first time, including electronic, mechanical and<br>heterogeneous technologiesExecutable Specification2025200% HW, 200% SW95013K HW, 136429K SWSystem design and<br>verificationDescribes the system specification in a manne<br>allows automated design and verification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Homogeneous Parallel Processing | 2009 | 100% HW, 100% SW    | 1200K HW, 646K SW                     |                            | around a main processor, enabling performance,                                                                                                                                                                                          |

| Reusable Platform Blocks2013200% HW, 100% SW4949K HW, 5168K SWChip/circuit/PD<br>verificationautomation of the verification partitioning stepReusable Platform Blocks2013200% HW, 100% SW4949K HW, 5168K SWChip/circuit/PD<br>verificationFully functional platforms used as a block in L<br>platform design (e.g., ARM in OMAP)Silicon Virtual Prototype2015100% HW9897K HW, 5168K SWSystem design and<br>verificationA hardware virtualization platform that enable<br>RTL handoff of a SOCHeterogeneous (AMP) Parallel<br>Processing2017100% HW, 100% SW19794K HW, 10336K SWSW development<br>verificationMany specialized cores provide processing are<br>man processor, which allows for performance<br>efficiency, and high reuseMany-Core SW Development Tools201960% SW19794K HW, 16537K SWSW developmentEnables compilation and SW development in parallel processing SOCsConcurrent Memory2021100% SW19794K HW, 33074K SWSW developmentMemories capable of on-chip memory manageSystem-Level Design Automation<br>(SDA)202360% HW, 37.5% SW31671K HW, 45476K SWSystem design and<br>verificationAutomates true system design on-<br>and off-chipExecutable Specification2025200% HW, 200% SW95013K HW, 136429K SWSystem design and<br>verificationDescribes the system specification in a manne<br>allows automated design and validation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Software Virtual Prototype      | 2011 | 300% SW             | 1200K HW, 2584K SW                    | SW development             | Virtualization tools used to allow development prior to completed silicon                                                                                                                                                               |

| Image: Construct of the construction of the constr | Intelligent Testbench           | 2012 | 37.5% HW            | 1650K HW, 2584K SW                    |                            | Like RTL verification tool suite, but also with<br>automation of the verification partitioning step                                                                                                                                     |

| Silicon Virtual Prototype       2015       100% HW       9897K HW, 5168K SW       System design and verification       A hardware virtualization platform that enable RTL handoff of a SOC         Heterogeneous (AMP) Parallel Processing       2017       100% HW, 100% SW       19794K HW, 10336K SW       SW development verification       Many specialized cores provide processing are main processor, which allows for performance efficiency, and high reuse         Many-Core SW Development Tools       2019       60% SW       19794K HW, 16537K SW       SW development       Enables compilation and SW development in parallel processing SOCs         Concurrent Memory       2021       100% SW       19794K HW, 33074K SW       SW development       Memories capable of on-chip memory manage         System-Level Design Automation (SDA)       2023       60% HW, 37.5% SW       31671K HW, 45476K SW       System design and verification       Automates true system design on- and off-chip first time, including electronic, mechanical and heterogeneous technologies         Executable Specification       2025       200% HW, 200% SW       95013K HW, 136429K SW       System design and verification       Describes the system specification in a manne allows automated design and validation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Reusable Platform Blocks        | 2013 | 200% HW, 100% SW    | 4949K HW, 5168K SW                    |                            | Fully functional platforms used as a block in larger platform design (e.g., ARM in OMAP)                                                                                                                                                |

| ProcessingImage: Construction of the cons          | Silicon Virtual Prototype       | 2015 | 100% HW             | 9897K HW, 5168K SW                    |                            | A hardware virtualization platform that enables an                                                                                                                                                                                      |

| Image: Concurrent Memory         2021         100% SW         19794K HW, 33074K SW         SW development         Memories capable of on-chip memory manage           System-Level Design Automation<br>(SDA)         2023         60% HW, 37.5% SW         31671K HW, 45476K SW         System design and<br>verification         Automates true system design on- and off-chip<br>first time, including electronic, mechanical and<br>heterogeneous technologies           Executable Specification         2025         200% HW, 200% SW         95013K HW, 136429K SW         System design and<br>verification         Describes the system specification in a manne<br>allows automated design and validation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                 | 2017 | 100% HW, 100% SW    | 19794K HW, 10336K SW                  |                            | Many specialized cores provide processing around a<br>main processor, which allows for performance, power<br>efficiency, and high reuse                                                                                                 |

| System-Level Design Automation<br>(SDA)       2023       60% HW, 37.5% SW       31671K HW, 45476K SW       System design and<br>verification       Automates true system design on- and off-chip<br>first time, including electronic, mechanical and<br>heterogeneous technologies         Executable Specification       2025       200% HW, 200% SW       95013K HW, 136429K SW       System design and<br>verification       Describes the system specification in a manne<br>allows automated design and validation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Many-Core SW Development Tools  | 2019 | 60% SW              | 19794K HW, 16537K SW                  | SW development             | Enables compilation and SW development in highly<br>parallel processing SOCs                                                                                                                                                            |

| (SDA)       werification       first time, including electronic, mechanical and heterogeneous technologies         Executable Specification       2025       200% HW, 200% SW       95013K HW, 136429K SW       System design and verification       Describes the system specification in a manne allows automated design and validation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Concurrent Memory               | 2021 | 100% SW             | 19794K HW, 33074K SW                  | SW development             | Memories capable of on-chip memory management                                                                                                                                                                                           |

| verification allows automated design and validation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                 | 2023 | 60% HW, 37.5% SW    | 31671K HW, 45476K SW                  |                            | Automates true system design on- and off-chip for the<br>first time, including electronic, mechanical and other<br>heterogeneous technologies                                                                                           |

| Total 7920% HW, 21119% SW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Executable Specification        | 2025 | 200% HW, 200% SW    | 95013K HW, 136429K SW                 |                            | Describes the system specification in a manner that allows automated design and validation                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Total                           |      | 7920% HW, 21119% SW |                                       |                            |                                                                                                                                                                                                                                         |

Table 2.1 Design technology improvements and their impact on productivity [13].

can be easily used in many different environments. Figure 2.4 represents an artistic view of the concept of building a chip out of several IP blocks.

It is a common practice nowadays to buy ready-made IPs from IP core vendors, and thus reduce the total design effort (see e.g. [8]). There are also open-source IPs available, especially if the functionality of the IP is needed frequently in many designs (see e.g. [31]). The IPs can be delivered in the form of *soft*, *firm* or *hard* IPs. The soft IPs are delivered as a RTL description that the user can modify to fit in their needs and synthesize to the target technology. The firm IPs are already

Figure 2.4 Artistic view of IP-based design [3].

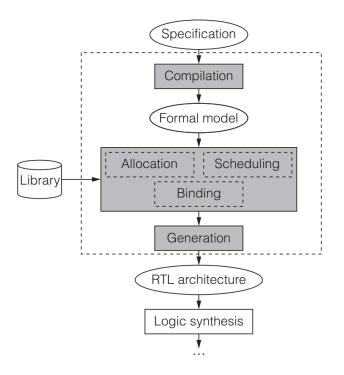

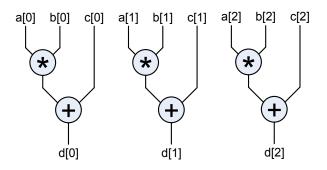

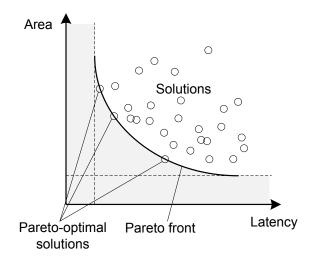

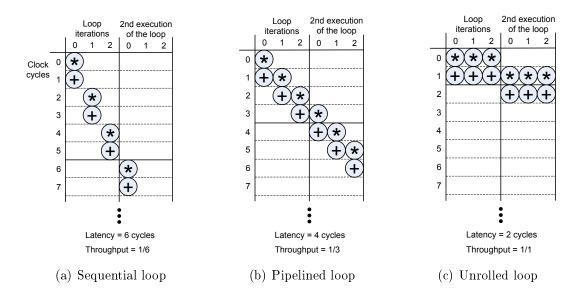

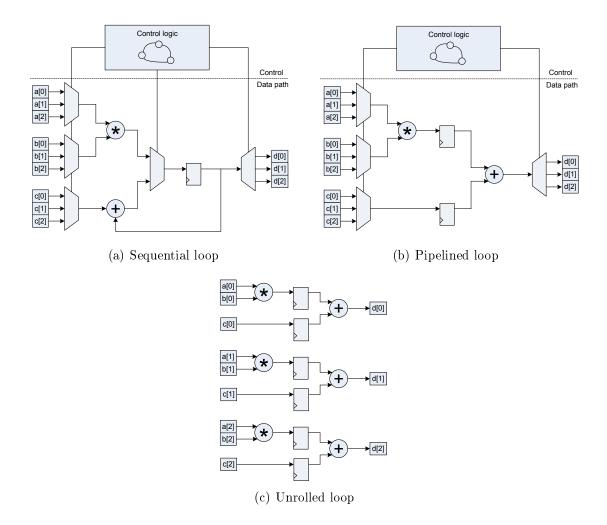

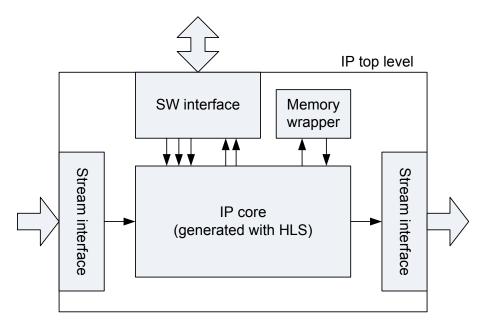

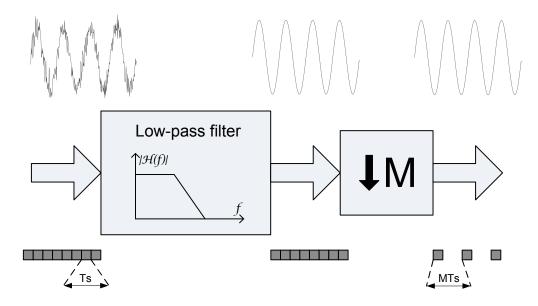

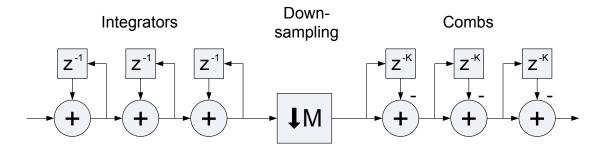

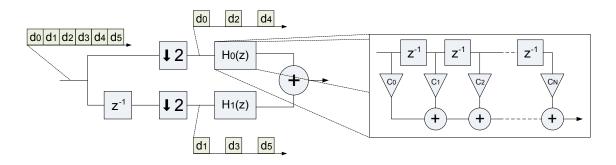

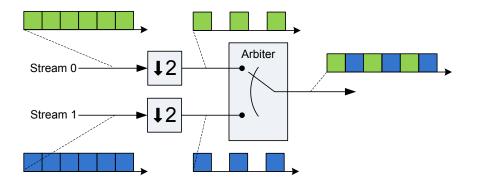

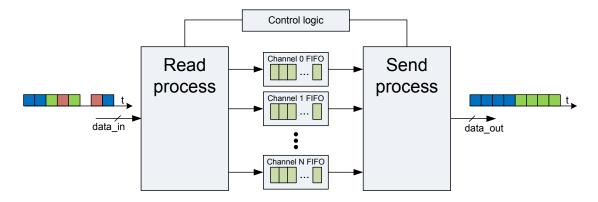

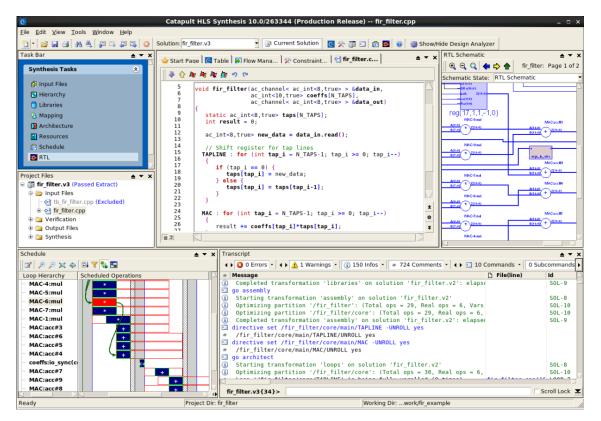

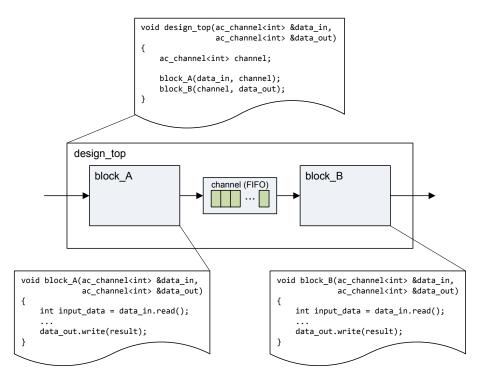

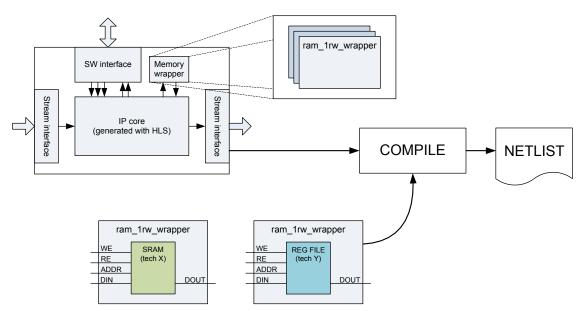

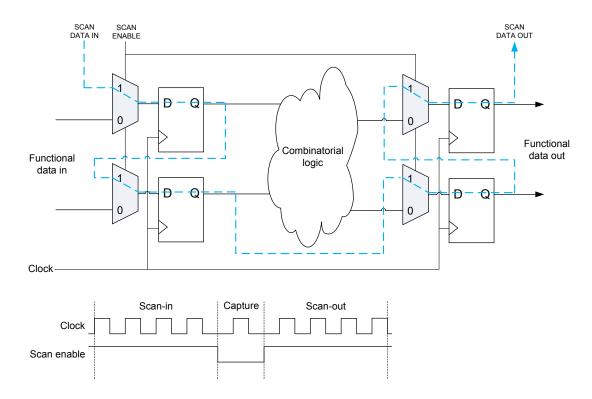

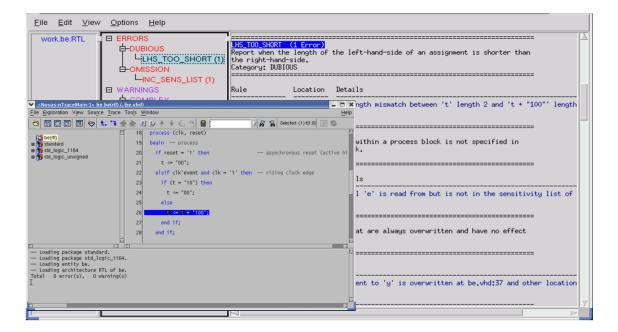

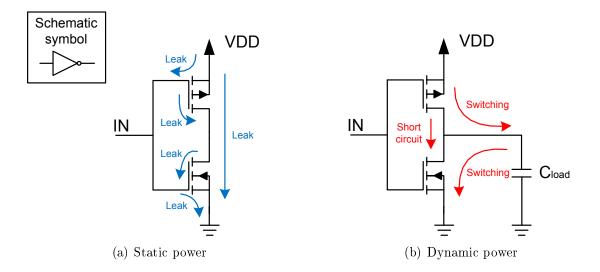

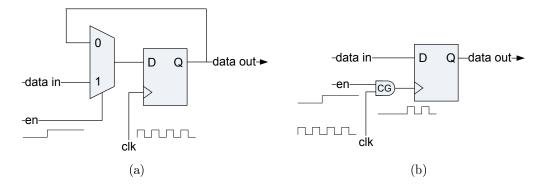

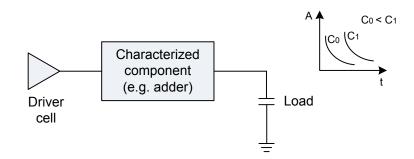

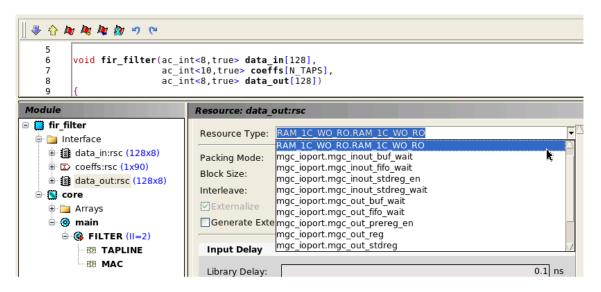

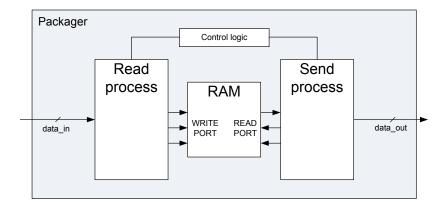

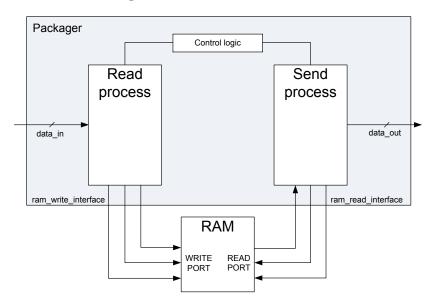

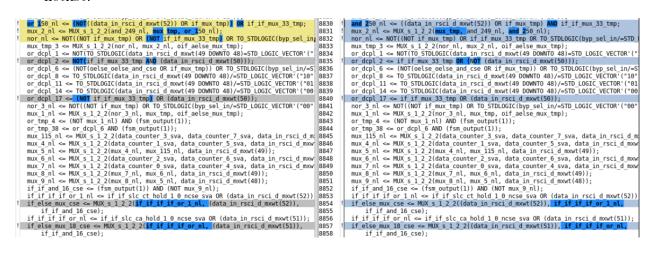

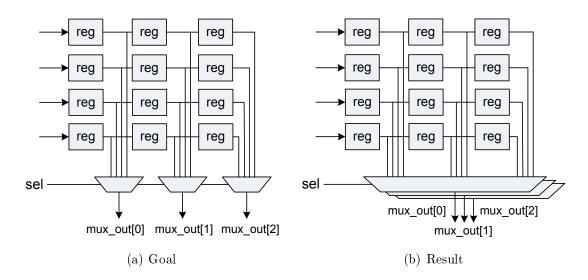

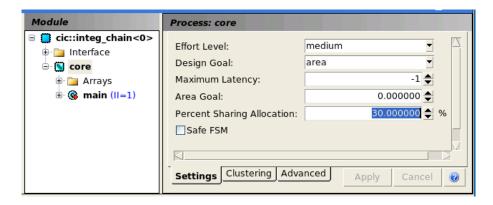

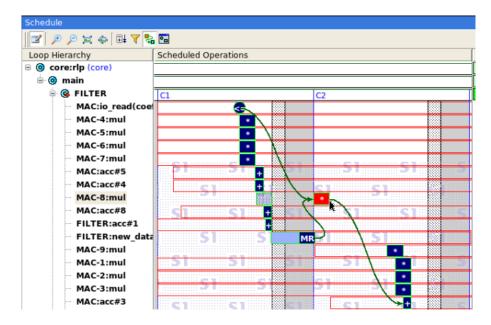

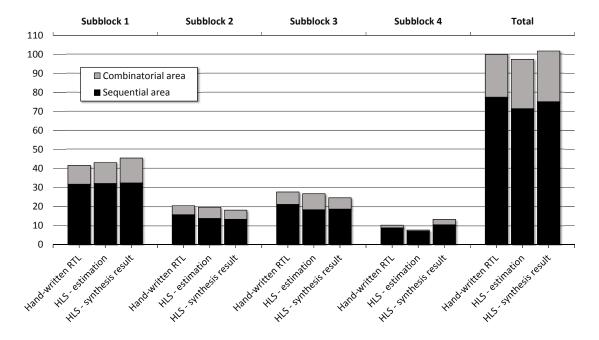

synthesized to a gate-level netlist, but still allow small modifications. Hard IPs, on the other hand, are already implemented as a physical layout and cannot thus be altered. Hard IPs are typically memories and analog components, such as analogto-digital converters or phase-locked loops that the silicon foundry provides to be used in a chip that they fabricate.