TAMPEREEN TEKNILLINEN YLIOPISTO TAMPERE UNIVERSITY OF TECHNOLOGY

## JANI HÄMÄLÄINEN COMPARISON OF OUTPUT HARMONICS BETWEEN TWO- AND THREE-LEVEL THREE-PHASE SPACE VECTOR PWM INVERT-ERS

Master of Science thesis

Examiner: prof. Teuvo Suntio Examiner and topic approved by the Faculty Council of the Faculty of Computing and Electrical Engineering on 6th May 2015

#### ABSTRACT

JANI HÄMÄLÄINEN: Comparison of Output Harmonics between Two- and Three-Level Three-Phase Space Vector PWM Inverters Tampere University of technology Master of Science Thesis, 53 pages, 16 Appendix pages October 2015 Master's Degree Programme in Electrical Engineering Major: Power Electronics of Electrical Drives Examiner: Professor Teuvo Suntio

Keywords: output harmonics, space vector modulation, three-level inverter

The usage of renewable energy sources is growing. These sources, such as photovoltaic devices and wind turbines, are connected to the power grids via inverters. Power electronic inverters produce non-sinusoidal voltages and increase the amount of unwanted distortion in the grids. Standards define the quality of the electricity in the power grids. Therefore, it is sensible to study the phenomena and methods to reduce the harmonic distortion in the outputs of different inverter topologies.

LCL filters are used to suppress the harmonic components in the output waveforms of the grid connected inverters. The filter is one of the most expensive component in drive systems. The amount of harmonics can also be decreased by adding voltage levels to the inverter's DC bus, optimizing the switching sequences and increasing the switching frequency. Therefore, better output harmonic performance can be achieved with the same LCL filter by using three-level inverter instead of two-level inverter. Three-level inverter also enables higher switching frequency. However, some additional costs are created, such as more semiconductor switches are needed, and the device requires more complex control system.

The main issue in this thesis is to compare output harmonics between two- and three-level inverters. The studied topologies are two-level voltage source inverter and three-level neutral-point-clamped inverter. A detailed space vector modulation method is explained for these inverters. Requirements for a well implemented space vector modulator are also discussed. Space vector pulse width modulators are created using MATLAB® and Simulink®. Output harmonic performance is compared by simulations with different switching frequencies and modulation indexes under linear modulation region.

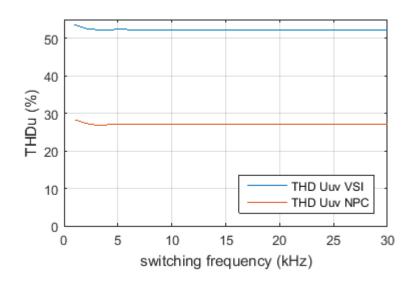

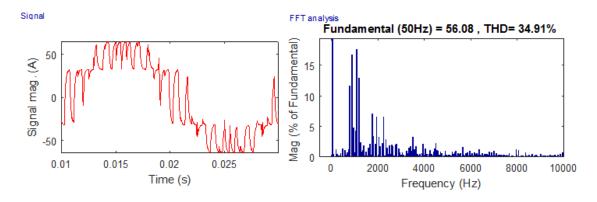

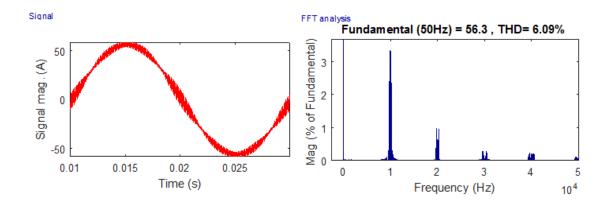

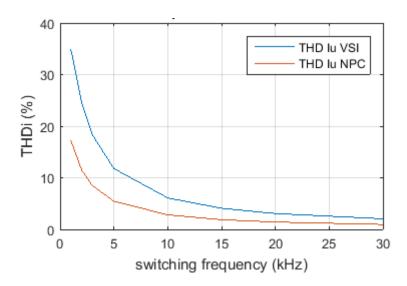

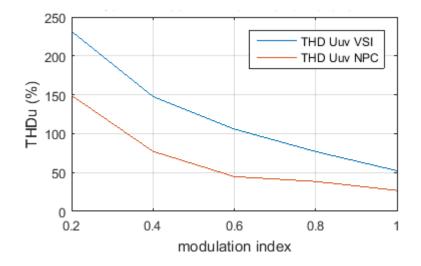

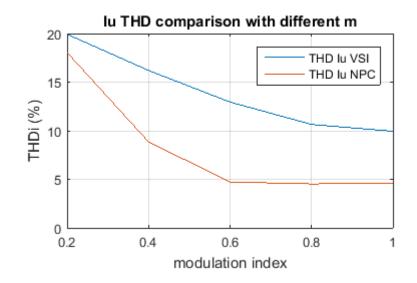

The simulations show that increasing the switching frequency reduces the phase current's harmonics. The switching frequency doesn't have similar effect on the line-to-line volt-age's total harmonic distortion value. It only increase the frequencies where the voltage's harmonic components occur. It's also shown, that the voltage's and current's THD values in the NPC inverter are half of the THD values in the VSI. The modulation index has an effect on both, the line-to-line voltage's and phase current's THD values. When the modulation index is reduced, the voltage's and current's THD values are increased. Small modulation index value reduces the difference between output performance of the VSI and NPC inverters.

#### TIIVISTELMÄ

JANI HÄMÄLÄINEN: Kaksi- ja kolmitasoisten kolmivaiheisten avaruusvektorimoduloitujen PWM vaihtosuuntaajien lähdön harmonisten vertailu Tampereen teknillinen yliopisto Diplomityö, 53 sivua, 16 liitesivua Lokakuu 2015 Sähkötekniikan diplomi-insinöörin tutkinto-ohjelma Pääaine: Sähkökäyttöjen tehoelektroniikka Tarkastaja: professori Teuvo Suntio

Avainsanat: lähdön harmoniset, avaruusvektorimodulointi, kolmitasoinen vaihtosuuntaaja

Uusiutuvien energianlähteiden käyttö on kasvussa. Vaihtosuuntaajia käytetään syöttämään tehoa sähköverkkoon aurinkopaneeli ja tuulivoimasovelluksissa. Tämä suuntaus lisää sähköverkkoon kytketyn tehoelektroniikan määrää. Standardeilla määritellään sähköverkkoon syötetyn sähkön laatua. Vaihtosuuntaajat tuottavat ei-sinimuotoisia lähtöjännitteitä ja lisäävät verkossa esiintyvien särökomponenttien määrää. Tämän vuoksi on tärkeä tutkia keinoja pienentää harmonisten komponenttien määrää eri suuntaajatopologioiden lähdöissä.

LCL suodattimia käytetään vähentämään verkkoon kytkettyjen vaihtosuuntaajien lähdöissä esiintyviä harmonisia komponentteja. Suodatin on kuitenkin yksi sähkökäyttöjen kalleimmista komponenteista. Harmonisten määrää voidaan vähentää myös lisäämällä vaihtosuuntaajan tasajännitetasoja, optimoimalla kytkentäjaksoja ja nostamalla kytkentätaajuutta. Samalla LCL suodattimella saavutetaan pienempi harmonisten määrä käyttämällä kolmitasoista vaihtosuuntaajaa kaksitasoisen sijaan. Kolmitasoinen vaihtosuuntaaja mahdollistaa myös korkeamman kytkentätaajuuden käytön. Useamman jännitetason käyttö aiheuttaa kuitenkin muita lisäkuluja, kuten pääpiirin puolijohdekomponenttien kasvaneen määrän ja laitteen monimutkaistuneen ohjauksen.

Tässä työssä vertaillaan kaksi- ja kolmitasoisten vaihtosuuntaajien lähdöissä esiintyviä harmonisia komponentteja. Tutkittavat topologiat ovat kaksitasoinen jännitesyöttöinen vaihtosuuntaaja ja kolmitasoinen nollapotentiaaliin kiinnitetty vaihtosuuntaaja. Työssä esitellään avaruusvektorimodulointimenetelmät näille suuntaajille. Lisäksi käsitellään vaatimuksia käytännön avaruusvektorimodulaattoritoteutukselle. Molemmille suuntaajille toteutetaan avaruusvektorimodulaattorit hyödyntäen MATLAB® ja Simulink® ohjelmistoja. Lähdön harmonisia vertaillaan tekemällä simulointeja eri kytkentätaajuuksilla ja modulointi-indekseillä. Simuloinnit toteutetaan lineaarisella modulointialueella.

Simuloinnit osoittavat, että kytkentätaajuuden nostaminen vähentää vaihevirran harmonisia. Kytkentätaajuuden nostolla ei ole samanlaista vaikutusta pääjännitteen THD arvoon. Sen kasvattaminen kuitenkin nostaa taajuusaluetta, missä jännitteen harmoniset esiintyvät. Tuloksista nähdään myös, että NPC vaihtosuuntaajaa käytettäessä jännitteen ja virran THD arvot puoliintuvat verrattuna VSI vaihtosuuntaajan arvoihin. Modulointiindeksillä todettiin olevan vaikutus jännitteen ja virran THD arvoihin molemmilla suuntaajilla. Jännitteen ja virran THD arvot kasvavat, kun modulointi-indeksiä pienennetään. Pienten modulointi-indeksien käyttö kaventaa eroa VSI ja NPC vaihtosuuntaajien lähdön harmonisten määrässä.

### PREFACE

I'd like to thank my family for support throughout studies. I also wish to name following fellow students: Antti Mansukoski, Jarno Naskali, Jori Lähteelä, Jukka Lehtinen, Tommi Koskinen and Toni Liimatainen. Their help was essential to make it through studies. Most importantly, I'd like to thank them for the past few years and all the shared experiences.

Vaasa, 4.10.2015

Jani Hämäläinen

### CONTENTS

| 1. | INTR  | ODUCTION                                                              | 1  |

|----|-------|-----------------------------------------------------------------------|----|

| 2. | TWO   | - AND THREE-LEVEL INVERTER SCHEMES                                    | 3  |

|    | 2.1   | Different inverter topologies                                         | 3  |

|    |       | 2.1.1 Current paths in different operational situations               | 4  |

|    | 2.2   | Output waveform comparison between different inverters                | 5  |

|    |       | 2.2.1 Harmonics and THD                                               |    |

|    |       | 2.2.2 Fourier analysis                                                | 8  |

| 3. | GEN   | ERAL SPACE VECTOR PWM METHOD                                          | 9  |

|    | 3.1   | Introduction                                                          | 9  |

|    | 3.2   | Space vector theorem                                                  | 9  |

|    | 3.3   | Space vector PWM for VSI                                              | 11 |

|    |       | 3.3.1 Switching times and sequence for VSI                            | 12 |

|    | 3.4   | Space vector PWM for NPC                                              |    |

|    |       | 3.4.1 Switching times and sequence for NPC                            | 16 |

| 4. | REQ   | UIREMENTS FOR ADVANCED SPACE VECTOR MODULATOR                         | 23 |

|    | 4.1   | Limit on amplitude of the reference voltage vector                    |    |

|    | 4.2   | Blanking time                                                         | 24 |

|    | 4.3   | Minimum pulse-width time                                              | 25 |

|    | 4.4   | Minimum time between successive pulses                                | 25 |

|    | 4.5   | DC-bus unbalance                                                      | 26 |

|    | 4.6   | Loss optimal modulation scheme                                        | 26 |

| 5. | SIMU  | JLATIONS                                                              | 27 |

|    | 5.1   | Simulation model of VSI                                               | 27 |

|    | 5.2   | Simulation model of NPC                                               | 28 |

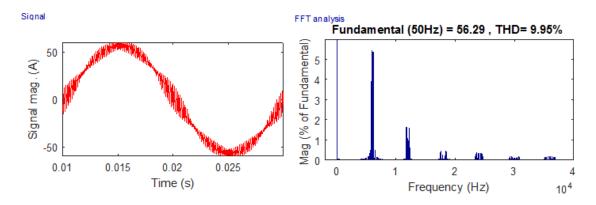

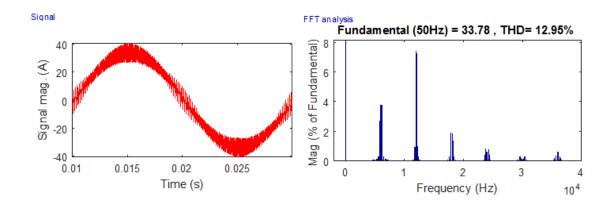

|    | 5.3   | Inverters' voltage and THD with different switching frequencies       | 30 |

|    | 5.4   | Inverters' phase current and THD with different switching frequencies | 35 |

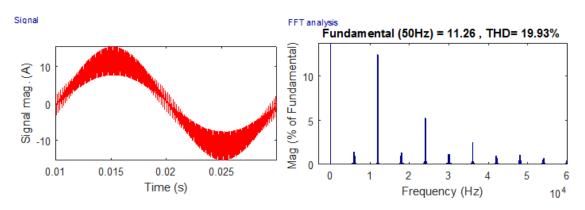

|    | 5.5   | Inverters' voltage and THD with different modulation indexes          | 39 |

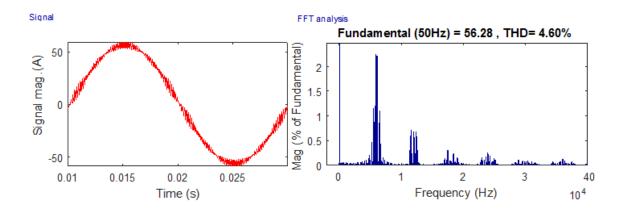

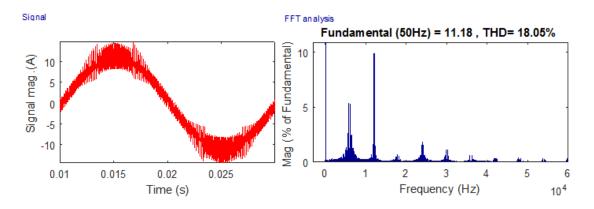

|    | 5.6   | Inverters' phase current and THD with different modulation indexes    |    |

| 6. | CON   | CLUSIONS                                                              | 50 |

| RE | FEREN | ICES                                                                  | 52 |

|    |       |                                                                       |    |

#### APPENDIX A: VSI SPACE VECTOR PWM MODULATOR CODE

APPENDIX B: NPC INVERTER SPACE VECTOR PWM MODULATOR CODE

## LIST OF FIGURES

| Figure 1. The main circuit topology of a grid connected 2L three-phase VSI with                    |    |

|----------------------------------------------------------------------------------------------------|----|

| LCL filter                                                                                         | 3  |

| Figure 2. The main circuit topology of a grid connected 3L three-phase NPC                         |    |

| inverter with LCL filter                                                                           | 4  |

| <i>Figure 3.</i> (a) <i>IGBTs</i> $S_1$ and $S_2$ are switched on with positive phase current. (b) |    |

| IGBTs $S_2$ and $S_3$ are switched on. (c) IGBTs $S_3$ and $S_4$ are switched                      |    |

| on with negative phase current                                                                     | 5  |

| Figure 4. VSI's phase and line-to-line voltages in square wave operation                           | 6  |

| Figure 5. NPC inverter's phase and line-to-line voltages with 45° trigger angle                    | 6  |

| Figure 6. Ideally sinusoidal three-phase voltages and three-phase voltages added                   |    |

| with third harmonic component                                                                      | 7  |

| Figure 7. Space vector presentation in a complex coordinates. Unity vectors used                   |    |

| in the space vector definition are also presented                                                  | 10 |

| Figure 8. Switching vectors for VSI in a complex coordinates.                                      | 12 |

| Figure 9. Switching vector presentation for VSI divided into six sectors (a).                      |    |

| Formation of the reference voltage vector is presented in (b)                                      | 13 |

| Figure 10. Upper IGBT switches' control signals and switching vectors applied                      |    |

| during one modulation period. The reference switching vector is                                    |    |

| located in the Sector 1 in this example                                                            | 14 |

| Figure 11. Switching vectors for NPC inverter in a complex coordinates                             | 16 |

| Figure 12. Switching vectors are divided into six main sectors. Each main sector                   |    |

| can be divided into six sub-sectors                                                                | 17 |

| Figure 13. Segment division for reference voltage vector location detection                        |    |

| purposes                                                                                           | 18 |

| Figure 14. (a) Definition of the new vector $sv_{ref2}$ . (b) New angles as switching              |    |

| vector sv <sub>onn/poo</sub> is taken as an origin                                                 | 18 |

| Figure 15. NPC inverter's switching vector numbering for on-time calculation                       |    |

| purposes                                                                                           | 19 |

| Figure 16. DC voltage utilization in different modulation methods                                  | 23 |

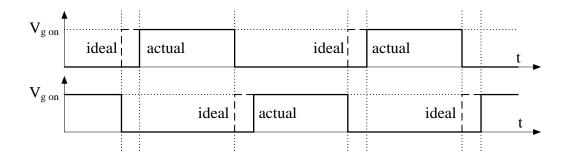

| Figure 17. Blanking time implementation to IGBTs' control signals. On-time                         |    |

| signals are delayed with blanking time                                                             | 24 |

| Figure 18. Implementation of the minimum pulse-width time in control pulse of an                   |    |

| individual IGBT switch                                                                             | 25 |

| Figure 19. Unbalance in the DC bus capacitors causes movement to the switching                     |    |

| vectors                                                                                            | 26 |

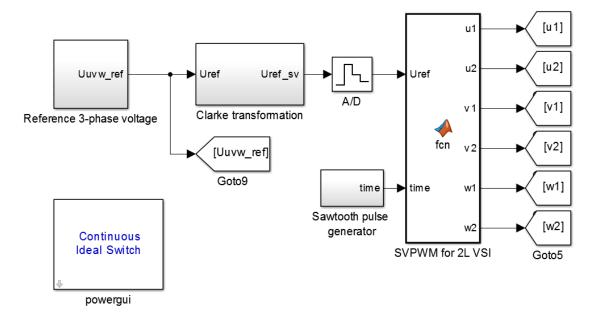

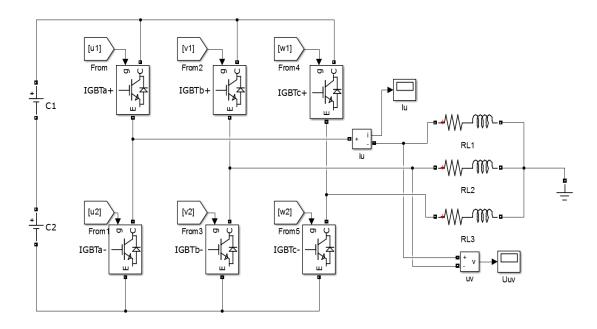

| Figure 20. The control signal generation model for the VSI                                         | 27 |

| Figure 21. VSI's main circuit model                                                                |    |

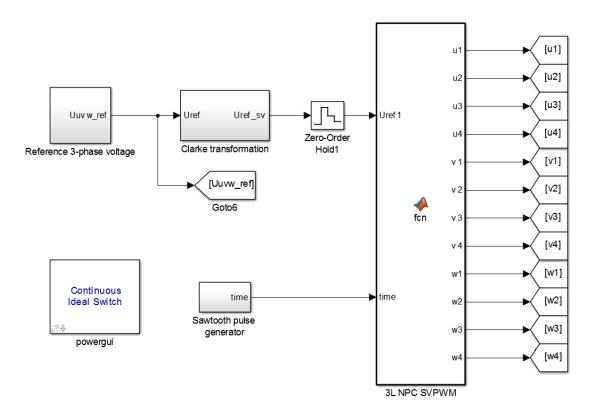

| Figure 22. The control signal generation model for the NPC inverter                                | 29 |

| Figure 23. NPC inverter's main circuit model                                                       | 30 |

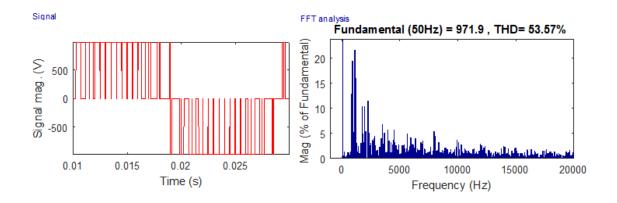

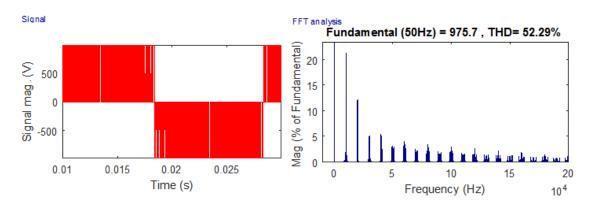

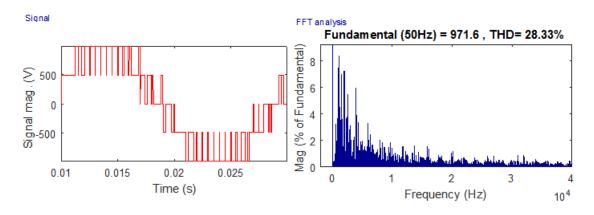

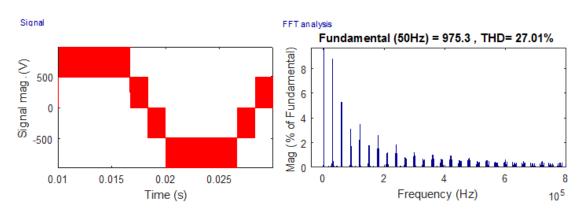

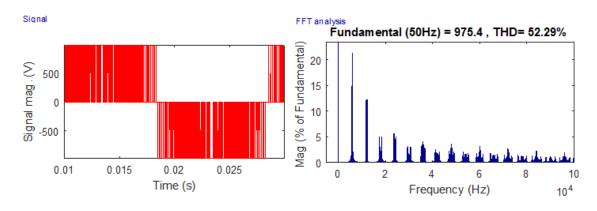

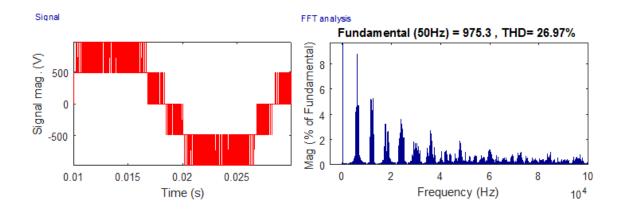

| <i>Figure 24. VSI's line-to-line voltage and FFT analysis with</i> $f_{sw}=1$ <i>kHz.</i>          | 31 |

| <i>Figure 25.</i> VSI's line-to-line voltage and FFT analysis with $f_{sw}=10$ kHz      |

|-----------------------------------------------------------------------------------------|

| <b>Figure 26.</b> VSI's line-to-line voltage and FFT analysis with $f_{sw}$ =30 kHz     |

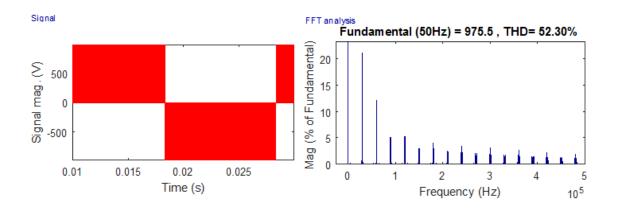

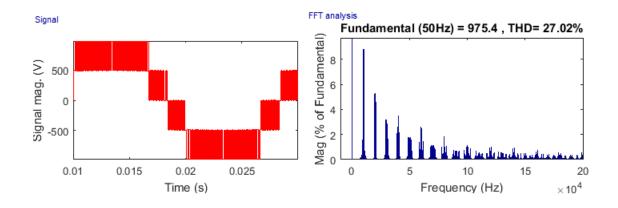

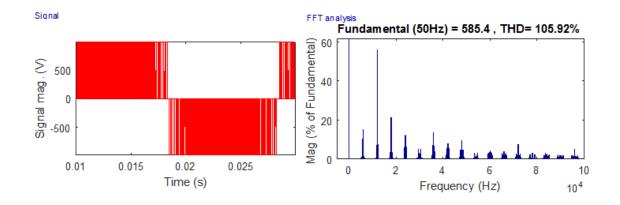

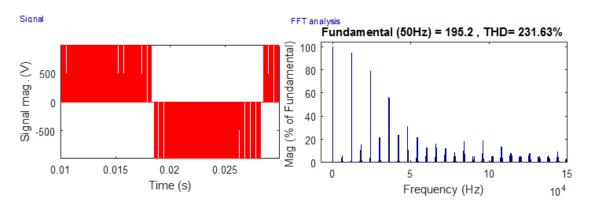

| <b>Figure 27.</b> NPC's line-to-line voltage and FFT analysis with $f_{sw}=1$ kHz       |

| <b>Figure 28.</b> NPC's line-to-line voltage and FFT analysis with $f_{sw}=10$ kHz      |

| <i>Figure 29.</i> NPC's line-to-line voltage and FFT analysis with $f_{sw}=30$ kHz      |

| Figure 30. Line-to-line voltage's THD comparison between VSI and NPC with               |

| different switching frequencies                                                         |

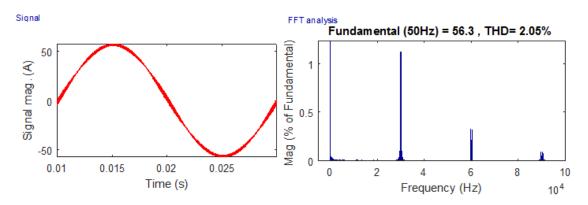

| <i>Figure 31.</i> VSI's phase current waveform and FFT analysis with $f_{sw}=1$ kHz     |

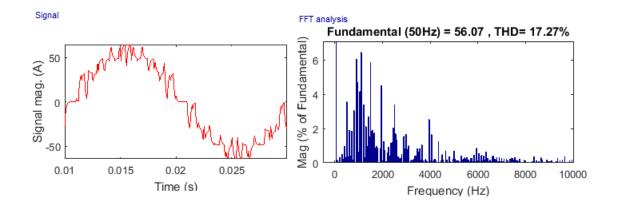

| Figure 32. VSI's phase current waveform and FFT analysis with $f_{sw}=10 \text{ kHz}$   |

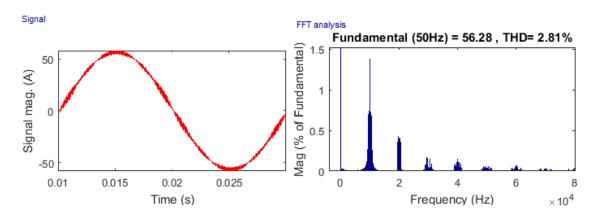

| <i>Figure 33.</i> VSI's phase current waveform and FFT analysis with $f_{sw}=30$ kHz    |

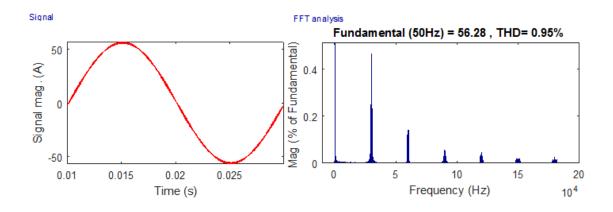

| <i>Figure 34.</i> NPC's phase current waveform and FFT analysis with $f_{sw}=1$ kHz37   |

| <i>Figure 35.</i> NPC's phase current waveform and FFT analysis with $f_{sw}=10$ kHz37  |

| <i>Figure 36.</i> NPC's phase current waveform and FFT analysis with $f_{sw}$ =30 kHz38 |

| Figure 37. Phase current's THD dependence on the switching frequency in VSI             |

| and NPC inverters                                                                       |

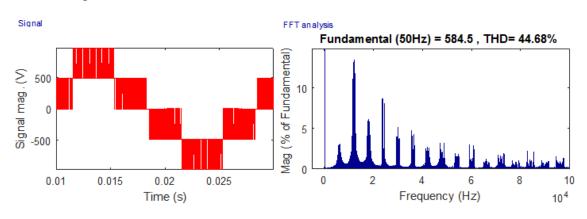

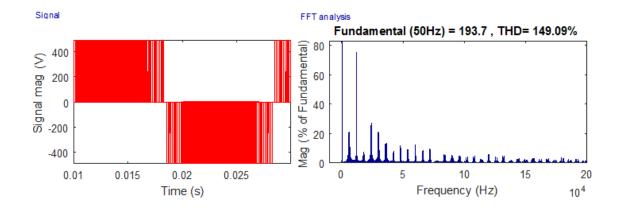

| <i>Figure 38. VSI's line-to-line voltage waveform and FFT analysis with m=140</i>       |

| <i>Figure 39. VSI's line-to-line voltage waveform and THD analysis with m=0.641</i>     |

| <i>Figure 40. VSI's line-to-line voltage waveform and THD analysis with m=0.241</i>     |

| <i>Figure 41.</i> NPC's line-to-line voltage waveform and THD analysis with m=142       |

| <i>Figure 42.</i> NPC's line-to-line voltage waveform and THD analysis with m=0.642     |

| <i>Figure 43.</i> NPC's line-to-line voltage waveform and THD analysis with m=0.243     |

| Figure 44. The effect of different modulation indexes on line-to-line voltage's         |

| THD values in VSI and NPC inverters                                                     |

| <i>Figure 45. VSI's phase current waveform and THD analysis with</i> $m=1$ <i>45</i>    |

| <i>Figure 46. VSI's phase current waveform and THD analysis with</i> $m=0.6$ <i></i> 46 |

| <i>Figure 47. VSI's phase current waveform and THD analysis with m=0.246</i>            |

| <i>Figure 48.</i> NPC's phase current waveform and THD analysis with $m=1$ 47           |

| <i>Figure 49.</i> NPC's phase current waveform and THD analysis with $m=0.6$            |

| <i>Figure 50.</i> NPC's phase current waveform and THD analysis with $m=0.2$            |

| Figure 51. Phase current's THD relationship to different modulation indexes             |

| between VSI and NPC inverters                                                           |

## LIST OF SYMBOLS AND ABBREVIATIONS

| 2L<br>3L<br>DC<br>ESR<br>IGBT<br>MTTF<br>NPC<br>PWM<br>RMS | two-level<br>three-level<br>direct current<br>equivalent series resistance<br>insulated-gate bipolar transistor<br>mean time to failure<br>neutral-point-clamped<br>pulse-width modulation<br>root mean square |

|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| THD                                                        | total harmonic distortion                                                                                                                                                                                      |

| VSI                                                        | voltage source inverter                                                                                                                                                                                        |

| $C_i \ D_{ik}$                                             | capacitor $i = \{1, 2, 3\}$<br>diode $i = \{1, 2, 3\} k = \{u, v, w\}$                                                                                                                                         |

| $f_{sw}$                                                   | switching frequency                                                                                                                                                                                            |

| h<br>\$                                                    | number of component                                                                                                                                                                                            |

| Î <sub>u</sub><br>K                                        | amplitude of phase voltage                                                                                                                                                                                     |

| K<br>L                                                     | constant<br>inductance                                                                                                                                                                                         |

| L<br>$L_i$                                                 | inductor $i = \{1, 2, 3\}$                                                                                                                                                                                     |

| $L_l$<br>Lload                                             | load inductance                                                                                                                                                                                                |

| m                                                          | modulation index                                                                                                                                                                                               |

| Ν                                                          | neutral point of grid voltages                                                                                                                                                                                 |

| n                                                          | negative DC bus                                                                                                                                                                                                |

| 0                                                          | midpoint of DC bus                                                                                                                                                                                             |

| p                                                          | positive DC bus                                                                                                                                                                                                |

| R                                                          | resistance                                                                                                                                                                                                     |

| $R_{load}$                                                 | load resistance<br>ICDT switch $i = (1, 2, 2,) k = (n, n, m)$                                                                                                                                                  |

| $S_{ik}$ $T_S$                                             | IGBT switch $i = \{1, 2, 3\}$ $k = \{u, v, w\}$<br>cycle time of modulation period                                                                                                                             |

| $t_i$                                                      | switching time of switching vector for two-level inverter $i = \{0, 1, 2\}$                                                                                                                                    |

| $t_k$                                                      | switching time of switching vector for three-level inverter $k = \{a, b, d\}$                                                                                                                                  |

| ν <sub>Λ</sub>                                             | c}                                                                                                                                                                                                             |

| и                                                          | inverter u-phase output                                                                                                                                                                                        |

| $u_h$                                                      | harmonic components of voltage u $h = \{1, 2, 3\}$                                                                                                                                                             |

| $U_{dc}$                                                   | DC bus voltage                                                                                                                                                                                                 |

| $u_k$                                                      | grid phase voltage $k = \{u, v, w\}$                                                                                                                                                                           |

| $\hat{U}_{uv}$                                             | amplitude of line-to-line voltage                                                                                                                                                                              |

| ν                                                          | inverter v-phase output                                                                                                                                                                                        |

| W<br>O                                                     | inverter w-phase output $(1, 2)$                                                                                                                                                                               |

| $	heta_{refn}$                                             | angle of reference vector $n = \{1, 2\}$                                                                                                                                                                       |

### 1. INTRODUCTION

Renewable energy sources are the topic of today's energy production. According to statistics provided by IEA, total power of installed photovoltaic energy worldwide is booming [5]. Unlike traditional electricity generation, renewable methods require inverters to feed the electricity to power grids. In addition, power electronics play an important role in several other applications with increasing prospects, such as electrical vehicles, elevators and escalators, wind power and cargo handling.

There are several different inverter topologies presented in the literature. The most common inverter type in industry is a two-level (2L) three-phase voltage source inverter (VSI). It has proven to be reliable, the control of the device is relatively easy to implement and the number of semiconductor components is low. However, the VSI has poor performance when it comes to output harmonics. The inverter's output harmonics can be decreased by increasing the number of voltage levels in a DC bus. The most common threelevel (3L) inverter topology is a neutral point clamped (NPC) inverter. Thus, these two inverters are studied in this thesis.

Lowering inverters output harmonics is important, since a grid connected inverter utilization requires an output LCL filter. The filter is a relatively high-cost component in drive systems. Reducing the harmonics allow the use of smaller filters and increase savings in the production costs. Voltage ratings of the insulated-gate bipolar transistor (IGBT) modules are also limited. Voltage stress over an individual IGBT module is split in multilevel inverters. Therefore, higher output voltage levels are obtained in the multilevel topologies using the same voltage rated IGBTs. Multilevel inverter drawbacks include an increased number of semiconductor components, more required driver and measurement circuits, and more complexity in controlling the device. These factors decrease the mean time to failure (MTTF) and make the multilevel inverters less attractive.

The main purpose of this thesis is to present a detailed operation of space vector pulsewidth modulation (PWM) methods for the VSI and NPC inverters. Simulation models of these two inverters are created using MATLAB® and Simulink®. The implemented models are used to investigate the relationship between different space vector modulation parameters and total harmonic distortion (THD) values in inverter's output voltage and current. The parameters of interest are the switching frequency and modulation index.

Chapter 1 introduces the subject considered in this thesis. Typical VSI and NPC inverters' main circuit topologies are given in Chapter 2. It also compares typical output waveforms of the inverters, provides a definition of harmonic components, and explains their analysis

method. General space vector PWM methods for the VSI and NPC inverters are presented in Chapter 3. More specific requirements for a well-implemented PWM method are covered in Chapter 4. Chapter 5 presents the simulation models of the VSI and NPC inverters. Simulation results are also provided in Chapter 5 before the conclusion is given in Chapter 6.

# 2. TWO- AND THREE-LEVEL INVERTER SCHEMES

This chapter gives an overview of three-phase implementations of the VSI and NPC inverters. These two inverter topologies are introduced in Section 2.1. A more detailed operation of the NPC inverter is showed by presenting current paths in different operational situations. Typical output voltage waveforms are presented along with a discussion about harmonics and an analyzation of the harmonic distortion in Section 2.2.

#### 2.1 Different inverter topologies

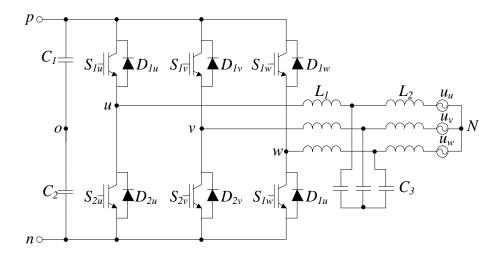

A typical main circuit topology of the grid connected VSI with an *LCL* filter is presented in the Figure 1. This is the most common type of an inverter in today's industry.

*Figure 1.* The main circuit topology of a grid connected 2L three-phase VSI with LCL filter.

The DC bus is implemented with two series connected capacitors-  $C_1$  and  $C_2$ . The positive DC bus is marked as 'p' and the negative as 'n'. The midpoint of the DC bus is referred to as 'o'. Inverter phase legs are made by using two IGBTs with inverse diodes, and they are denoted as  $S_1$ - $S_2$  and  $D_1$ - $D_2$ , respectively. The output LCL-filter is implemented with the  $L_1$  and  $L_2$  inductors and the  $C_3$  capacitor. Grid voltages are presented as  $u_u$ ,  $u_v$  and  $u_w$ . The grid's neutral point is marked 'N'. The inverter's phase outputs are denoted as 'u', 'v' and 'w'.

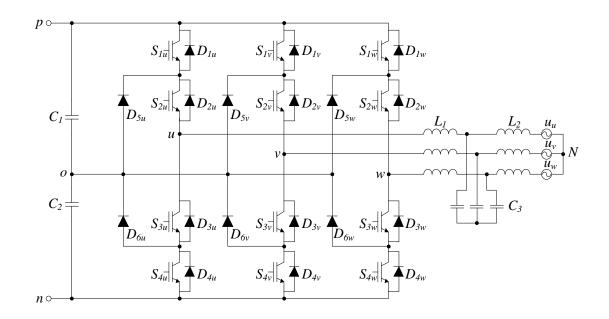

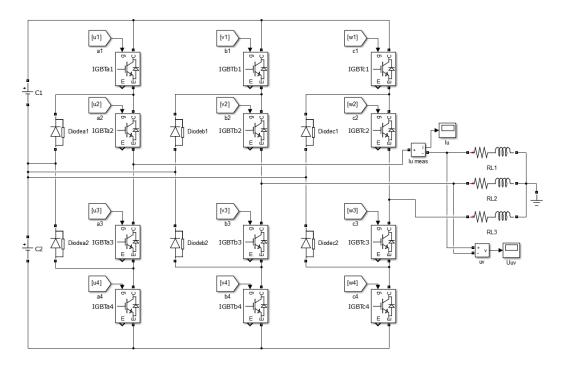

The main circuit topology found in the scientific publications of a grid connected NPC inverter with *LCL* filter is presented in the Figure 2.

*Figure 2.* The main circuit topology of a grid connected 3L three-phase NPC inverter with LCL filter.

Naming of the components and reference points is made with the same principles as the VSI in the Figure 1. The difference between the VSI and NPC is that the NPC inverter has a pair of neutral-point-clamp diodes ( $D_5$ - $D_6$ ) and twice as many IGBTs with inverse diodes in each phase leg. This allows the third DC bus voltage level, 'o', to be connected to the inverter's phase outputs.

#### 2.1.1 Current paths in different operational situations

More detailed operation of the NPC inverter is introduced in this section. Positive and negative current paths with all allowed IGBT state combinations are presented. Positive current denotes current from the DC bus capacitors to the phase output, and negative current flows from the phase output to the DC bus capacitors.

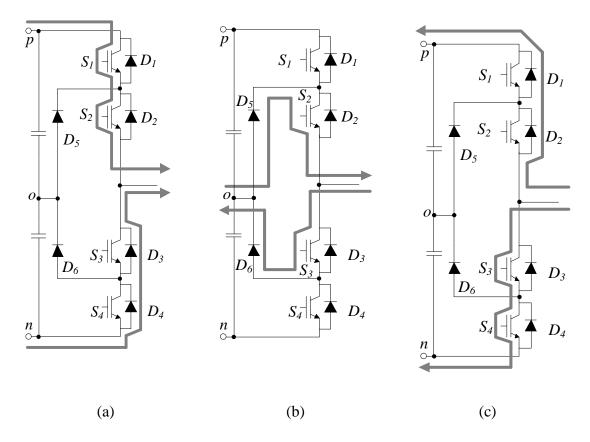

Current paths are presented in three different situations in Figure 3 depending on which IGBT pairs are in the on-state. Figure 3 (a) represents the combination of both upper IGBTs  $S_1$  and  $S_2$  when they are switched on and the phase current is positive. The positive DC bus is connected to the phase output when both of the upper IGBT switches are conducting. When both lower inverse diodes are conducting and current is positive, the phase output is connected to the negative DC bus. [13]

Figure 3 (b) demonstrates when IGBTs  $S_2$  and  $S_3$  are switched on. Upper neutral-pointclamp diode  $D_5$  and IGBT  $S_2$  are conducting so that the phase output and the DC bus midpoint are connected with positive phase current. The output is connected to the midpoint with negative phase current when the current flows through IGBT  $S_3$  and lower neutral-point-clamp diode  $D_6$ . [13] IGBTs  $S_3$  and  $S_4$  are switched on with negative phase current in Figure 3 (c). The negative phase current goes either through IGBT switches  $S_1$  and  $S_2$  or inverse diodes  $D_3$  and  $D_4$ . The phase is connected to positive or negative DC bus, respectively. [13]

*Figure 3.* (a) *IGBTs S*<sub>1</sub> and *S*<sub>2</sub> are switched on with positive phase current. (b) *IG-BTs S*<sub>2</sub> and *S*<sub>3</sub> are switched on. (c) *IGBTs S*<sub>3</sub> and *S*<sub>4</sub> are switched on with negative phase current.

#### 2.2 Output waveform comparison between different inverters

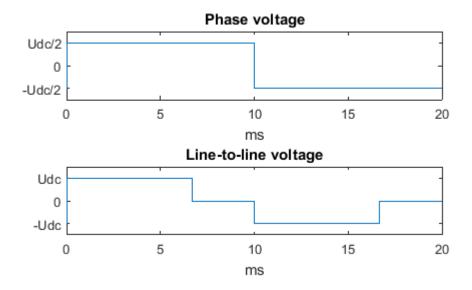

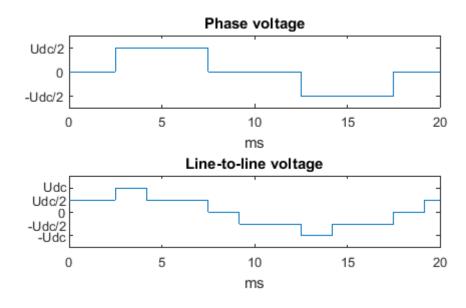

Output voltage waveforms for VSI and NPC inverters are compared in this section. VSI's phase and line-to-line voltages are demonstrated in the Figure 4. Phase voltage of the VSI is the voltage over points 'u' and 'o' as shown in Figure 1. Therefore, the DC voltage level is zero. Line-to-line voltage is the voltage over points 'u' and 'v'. The given output voltages are produced by square wave operation for simplicity. Each switch operates with 50% duty ratio in square wave operation [8]. Therefore, the output voltages have simple square wave-shape. Since all the three phases are equal, only one phase and line-to-line voltages are presented. The cycle time of the voltages used to demonstrate the operation is 20ms.

Figure 4. VSI's phase and line-to-line voltages in square wave operation.

Phase voltage is connected to the positive DC bus for half of the cycle. The amplitude of phase voltage is half that of the DC bus voltage (i.e.  $U_{dc}/2$ ). During the other half cycle, the phase output is connected to the negative DC bus. Therefore, the phase voltage is -  $U_{dc}/2$ . Line-to-line voltage is the difference between two phase voltages. Therefore, it is alternately connected to  $U_{dc}/2$ , 0 and  $-U_{dc}/2$  for one third of a cycle each.

Phase and line-to-line voltages produced with the NPC inverter with a 45° trigger angle are presented in Figure 5 [7]. Phase and line-to-line voltages equal the same potential differences as explained to VSI previously.

*Figure 5.* NPC inverter's phase and line-to-line voltages with 45° trigger angle.

The advantage gained using a three voltage level inverter can be seen by comparing Figure 4 and Figure 5. The phase voltage in the NPC inverter has one more voltage level than in the VSI. Therefore, the line-to-line voltage consists of five values:  $U_{dc}$ ,  $U_{dc}/2$ , 0,  $-U_{dc}/2$

or  $-U_{dc}$ . Thus, the resulting voltage is closer to the desired sinusoidal waveform and contains less harmonic components than VSI inverter.

#### 2.2.1 Harmonics and THD

The harmonic components existing in non-sinusoidal signals and the definition of THD are introduced in this section. Inverter output voltage waveforms are not ideally sinusoidal, as noted in the Chapter 2.2. It is important to understand the concept of harmonics occurring in signal waveforms for further analysis.

Assuming voltage *u* has no DC component, it can be presented as

$$u(t) = u_1(t) + \sum_{h \neq 1} u_h(t), \qquad (2.1)$$

where  $u_1$  is the fundamental component with nominal line frequency f and  $u_h$  is the harmonic component of u. The frequency of each harmonic components can be evaluated by

$$f_h = h f_1 \,[8]. \tag{2.2}$$

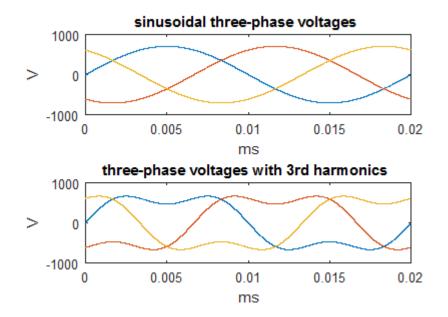

The effect of harmonic component on a fundamental signal is demonstrated in Figure 6. The upper curves present ideally sinusoidal three-phase voltages. The lower curves are the same sinusoidal three-phase voltages containing a third harmonic component.

*Figure 6. Ideally sinusoidal three-phase voltages and three-phase voltages added with third harmonic component.*

THD determines the amount of distortion in a signal. It can be calculated for any periodical signal. In order to define THD, distortion component needs to be defined with RMS values first. The total distortion can be defined with voltage u by the following equation:

$$u_h(t) = u(t) - u_1(t),$$

(2.3)

where  $u_h$  is the total distortion, u is the voltage signal, and  $u_1$  is the fundamental component of signal u. This can be presented in RMS terms of

$$U_h = \sqrt{U^2 - U_1^2},$$

(2.4)

where  $U_h$  is RMS value of distortion components, U is the RMS value of signal u, and  $U_1$  is the RMS value of fundamental component of u. THD percent of the voltage u can now be defined as

$$THD = 100\% \cdot \frac{U_h}{U_1} \ [8]. \tag{2.5}$$

#### 2.2.2 Fourier analysis

Harmonic components need to be solved to be able to calculate the THD value of a signal. These components can be calculated using Fourier analysis. A periodical signal can be presented as a sum of sinusoidal functions according to the Fourier analysis. The signal is a sum of its fundamental component and harmonic components. A repeating waveform can be presented as [8]

$$u(t) = U_0 + \sum_{h=1}^{\infty} [a_h \cos(h\omega t) + b_h \sin(h\omega t)], \qquad (2.6)$$

where  $U_0$  is the DC component of the signal u, h is the number of component,  $a_h$  is an amplitude of an even component,  $b_h$  is an amplitude of an odd component and  $\omega$  is the angular velocity of the signal. Amplitudes  $a_h$  and  $b_h$  can be expressed as [8]

$$a_h = \frac{1}{\pi} \int_0^{2\pi} u(t) \cos(h\omega t) d(\omega t)$$

(2.7)

and

$$b_{h} = \frac{1}{\pi} \int_{0}^{2\pi} u(t) \sin(h\omega t) \, d(\omega t), \tag{2.8}$$

where h = 0, 1, 2, ... Theoretically, if infinite amount of components are summed, the obtained signal is equivalent to the analyzed signal.

## 3. GENERAL SPACE VECTOR PWM METHOD

#### 3.1 Introduction

General space vector PWM methods for VSI and NPC inverters are presented in this chapter. The selection of active vectors and on-time calculations are explained in details for both inverters. Section 3.2 introduces a basic space vector theorem. The space vector PWM method for VSI is presented in Section 3.3, and Section 3.4 provides the space vector modulation method for NPC inverter.

Two common methods for inverter modulator signal generation are traditional sine-PWM and space vector PWM methods. Nowadays, every inverter's control system is implemented digitally. This favors the space vector PWM implementations, since it is based on mathematics. Therefore, it is easy to put into practice in microcontroller-based modulators. Space vector PWM method has also other pros compared to sine-PWM as discussed later. Consequently, it is widely studied in recent years.

In general, a good modulator should minimize the switching losses [6], maximize the DCbus voltage utilization [2] [12], and reduce the output harmonics [12]. In the space vector PWM, the switching losses and output harmonics can be minimized by optimally arranging the order of the applied switching vectors. The space vector PWM provides a better DC-bus voltage utilization than traditional sine-PWM method [9]. The DC-voltage utilization is discussed more thoroughly in the next chapter in Section 4.1.

There are basic steps in the space vector modulation schemes regardless of the number of the voltage levels in the inverter's DC bus. The first step is to locate the reference voltage vector and choose the switching vectors to be used in a modulation period. Next, the switching times are calculated. Finally, the switching cycle and control signals for switches are generated. The required volt-seconds are achieved in the inverter's output, i.e. the voltages in the modulation period equals the reference voltage vector in average [4].

Even though the basics of the space vector PWM schemes are similar for 2L and 3L inverters, the methods are studied separately, since the generation of the optimal modulation sequences varies.

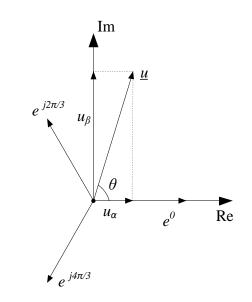

#### 3.2 Space vector theorem

General space vector theorem is presented in this section. The relationship between threephase variables and space vector will be presented. Three-phase systems can be calculated more effectively applying space vector theorem. Any time variant three-phase variables  $u_u$ ,  $u_v$  and  $u_w$  can be presented by a single vector. The name 'space vector' derives from that any point in space can be defined with three *xyz*- coordinates. Transformation from three-phase variables to complex space vector in  $\alpha\beta$  coordinates can be defined using Clarke transformation [3] as

$$\underline{u} = \frac{2}{3} \left( u_u e^0 + u_v e^{\frac{j2\pi}{3}} + u_w e^{\frac{j4\pi}{3}} \right) = u_\alpha + j u_\beta = |\underline{u}| e^{j\theta}, \tag{3.1}$$

where  $\underline{u}$  is the resulting space vector,  $u_u$ ,  $u_v$  and  $u_w$  are three-phase time domain variables,  $u_{\alpha}$  and  $u_{\beta}$  are real and imaginary components of the space vector  $\underline{u}$ , respectively, and  $\theta$  is the angle between space vector  $\underline{u}$  and real axis  $\alpha$ . Coefficient  $\frac{2}{3}$  is used to retain equal amplitudes between time domain and space vector presentations. Thus, it is used also in this thesis. Simple space vector presentation in complex coordinates is given in the Figure 7.

*Figure 7.* Space vector presentation in a complex coordinates. Unity vectors used in the space vector definition are also presented.

It should be noticed that the zero-sequence component is lost during the transformation. The zero-component can be calculated separately as

$$u_0 = \frac{1}{3}(u_u + u_v + u_w). \tag{3.2}$$

Zero-sequence component is canceled in a symmetrical three-phase system. It doesn't have to be taken into account when transforming sinusoidal three-phase variables into a space vector variable.

#### 3.3 Space vector PWM for VSI

Space vector modulation method for VSI used in the simulations of this thesis is presented in this section. It should be noted that the space vector PWM method provided in this section concentrates only in a linear modulation region. An overmodulation region is neglected in the space vector PWM implementation in this thesis, however it is discussed in the next chapter in Section 4.1

VSI has two alternatives where the output of an inverter phase can be connected to: positive or negative DC bus voltage. This approach generates eight different switching vectors. Table 1 presents all the possible switching vectors and corresponding switch states for each switches. The subscripts in the switching vector names denotes whether the phase outputs *u*, *v* and *w* are connected to the positive or negative DC bus voltages. The positive connected phase output is denoted as 'p' when the output voltage is half of the DC bus voltage, i.e.  $U_{dc}/2$ . The negative connected phase output is marked 'n' and the phase output voltage is -  $U_{dc}/2$  in this occasion. Individual IGBT switch states are presented as '1' and '0'. '1' means that the switch is in on-state and conducting, while '0' designates that the switch is in off-state and not conducting. Naming of the switches refers to Figure 1.

|               | S <sub>1u</sub> | S <sub>2u</sub> | S <sub>1v</sub> | <b>S</b> <sub>2v</sub> | S <sub>1w</sub> | S <sub>2w</sub> |

|---------------|-----------------|-----------------|-----------------|------------------------|-----------------|-----------------|

| <u>SV</u> pnn | 1               | 0               | 0               | 1                      | 0               | 1               |

| <u>SV</u> ppn | 1               | 0               | 1               | 0                      | 0               | 1               |

| <u>SV</u> npn | 0               | 1               | 1               | 0                      | 0               | 1               |

| <u>SV</u> npp | 0               | 1               | 1               | 0                      | 1               | 0               |

| <u>SV</u> nnp | 0               | 1               | 0               | 1                      | 1               | 0               |

| <u>SV</u> pnp | 1               | 0               | 0               | 1                      | 1               | 0               |

| <u>SV</u> ppp | 1               | 0               | 1               | 0                      | 1               | 0               |

| <u>SV</u> nnn | 0               | 1               | 0               | 1                      | 0               | 1               |

Table 1. Switching vectors and switch states for 2L VSI

Switches  $S_1$  and  $S_2$  of each phase leg work as a pair: Switch pairs are not allowed to have the same state in any occasion to avoid short circuiting in DC bus. More about blanking time is discussed in the next chapter in Section 4.2.

The available switching vectors are obtained by replacing the phase output values  $u_u$ ,  $u_v$  and  $u_w$  in the equation 3.1 with corresponding voltages  $U_{dc}/2$  or  $-U_{dc}/2$ . In order to clarify the presentation and space vector scheme, the switching vectors are presented in a complex coordinates in Figure 8.

Figure 8. Switching vectors for VSI in a complex coordinates.

The switching vectors can be divided in two categories: active vectors and zero vectors. The active vectors are vectors that enables current paths for inverter phase outputs. There are six active vectors and two zero vectors in Figure 8. The lengths of the active vectors are  $2/3U_{dc}$  for all the VSI's active vectors. Zero vectors are formed by clamping all the phase outputs to either positive or negative DC bus. Therefore, they don't provide current paths and the resulting switching vector lengths are zero.

#### 3.3.1 Switching times and sequence for VSI

As said, the reference voltage vector is formed by averaging the discrete switching vectors. In order to do this, we need to calculate the switching times. Switching time calculations along with modulation sequence generation are explained in this section.

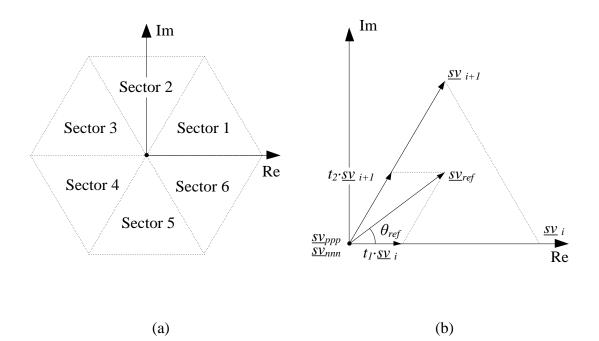

Switching vector presentation can be divided into six sectors (Figure 9 (a)). All the sectors are symmetric. Thus, the reference switching vector formation presented in the Figure 9 (b) is similar for all the sectors. Reference voltage vector is simply formed by using two nearest active switching vectors in VSI's space vector PWM scheme.

*Figure 9.* Switching vector presentation for VSI divided into six sectors (a). Formation of the reference voltage vector is presented in (b).

Switching times for reference switching vector located in any of the sectors can be solved using trigonometry by the following equations [15]

$$t_1 = \sqrt{3} T_s \frac{|\underline{sv}_{ref}|}{u_{dc}} \sin(\theta_{i+1} - \theta_{ref}) \text{ and}$$

(3.3)

$$t_2 = \sqrt{3} T_s \frac{\left|\underline{sv_{ref}}\right|}{u_{dc}} \sin(\theta_{ref} - \theta_i), \tag{3.4}$$

where  $t_1$  is the switching time for  $\underline{sv}_i$ ,  $t_2$  is the switching time for  $\underline{sv}_{i+1}$ ,  $T_s$  is the cycle time of modulation period,  $\underline{sv}_{ref}$  is the reference switching vector,  $U_{dc}$  is the DC bus voltage,  $\theta_{i+1}$  is the angle of the switching vector  $\underline{sv}_{i+1}$  respective to the real axis,  $\theta_{ref}$  is the angle of the reference switching vector respective to the real axis and  $\theta_i$  is the angle of switching vector  $\underline{sv}_i$  respective to real axis (Figure 9 (b)).

Application time of zero vectors is easy to compute after  $t_1$  and  $t_2$  have been calculated as

$$t_0 = T_s - t_1 - t_2, (3.5)$$

where  $t_0$  is the switching time for zero vectors. Now we how to select the active vectors and calculate the switching times. An example of a whole modulation period is given in Figure 10.

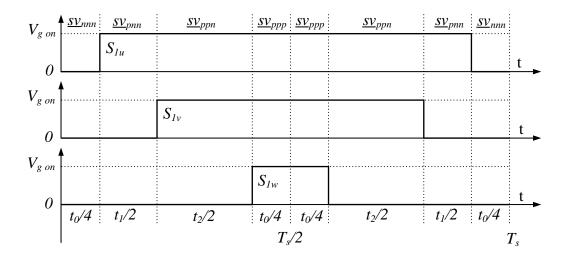

*Figure 10.* Upper IGBT switches' control signals and switching vectors applied during one modulation period. The reference switching vector is located in the Sector 1 in this example.

In this example, the reference vector is located in the Sector 1. The modulation period is divided into eight segments to split the applying time of each switching vector evenly. The modulation period always starts by applying the zero vector  $\underline{sv}_{nnn}$  in a space vector scheme for VSI. The  $\underline{sv}_{nnn}$  is applied for the time of  $t_0/2$ . The next applied switching vector is selected so that only one switch state is changed at a time. In this example, it means  $\underline{sv}_{pnn}$  is followed by  $\underline{sv}_{nnn}$ . It is applied for the time of  $t_1/2$ . The next active vector is  $\underline{sv}_{ppn}$  with the applying time of  $t_2/2$ . After the first and the second active switching time of  $t_0/4$ . After these steps, the sequence is repeated in a reverse order. The resulting switching vector can be stated as

$$\underline{sv}_{ref} = \frac{t_1}{T_s} \underline{sv}_i + \frac{t_2}{T_s} \underline{sv}_{i+1} + \frac{t_0/2}{T_s} \underline{sv}_{ppp} + \frac{t_0/2}{T_s} \underline{sv}_{nnn}.$$

(3.6)

As said, the modulation period is generated by carefully choosing the order of the switching vectors. The Table 2 presents the order of the switching vectors in which they should be applied to minimize the state changes during a modulation period.

|          | t₀/2          | <b>t</b> 1    | t <sub>2</sub> | t <sub>0</sub> /2 | t <sub>0</sub> /2 | t <sub>2</sub> | t <sub>1</sub> | t <sub>0</sub> /2 |

|----------|---------------|---------------|----------------|-------------------|-------------------|----------------|----------------|-------------------|

| Sector 1 | <u>SV</u> nnn | <u>SV</u> pnn | <u>SV</u> ppn  | <u>SV</u> ppp     | <u>SV</u> ppp     | <u>SV</u> ppn  | <u>SV</u> pnn  | <u>SV</u> nnn     |

| Sector 2 | <u>SV</u> nnn | <u>SV</u> npn | <u>SV</u> ppn  | <u>SV</u> ppp     | <u>SV</u> ppp     | <u>SV</u> ppn  | <u>SV</u> npn  | <u>SV</u> nnn     |

| Sector 3 | <u>SV</u> nnn | <u>SV</u> npn | <u>SV</u> npp  | <u>SV</u> ppp     | <u>SV</u> ppp     | <u>SV</u> npp  | <u>SV</u> npn  | <u>SV</u> nnn     |

| Sector 4 | <u>SV</u> nnn | <u>SV</u> nnp | <u>SV</u> npp  | <u>SV</u> ppp     | <u>SV</u> ppp     | <u>SV</u> npp  | <u>SV</u> nnp  | <u>SV</u> nnn     |

| Sector 5 | <u>SV</u> nnn | <u>SV</u> nnp | <u>SV</u> pnp  | <u>SV</u> ppp     | <u>SV</u> ppp     | <u>SV</u> pnp  | <u>SV</u> nnp  | <u>SV</u> nnn     |

| Sector 6 | <u>SV</u> nnn | <u>SV</u> pnn | <u>SV</u> pnp  | <u>SV</u> ppp     | <u>SV</u> ppp     | <u>SV</u> pnp  | <u>SV</u> pnn  | <u>SV</u> nnn     |

Table 2. Order of the switching vectors for VSI.

#### 3.4 Space vector PWM for NPC

This section presents how the space vector modulator is implemented in the simulation model of the NPC inverter in this thesis. The basic concept of the space vector modulation is the same for 2L and 3L inverters. 3L inverter has more switching vectors, since the phase output can be connected not only to 'p' positive or 'n' negative DC bus, but also to middle point 'o'. This results more switching vectors, some of which are redundant. This gives a degree of freedom to reference voltage vector generation. Therefore, there are several different space vector PWM methods for NPC inverter studied and introduced in the literature.

Switching vectors and corresponding switch states for 3L NPC inverter are presented in the Table 3.

|               | S <sub>1u</sub> | S <sub>2u</sub> | S <sub>3u</sub> | S <sub>4u</sub> | S <sub>1v</sub> | <b>S</b> <sub>2v</sub> | S <sub>3v</sub> | S <sub>4v</sub> | S <sub>1w</sub> | S <sub>2w</sub> | S <sub>3w</sub> | $S_{4w}$ |

|---------------|-----------------|-----------------|-----------------|-----------------|-----------------|------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|----------|

| <u>SV</u> onn | 0               | 1               | 1               | 0               | 0               | 0                      | 1               | 1               | 0               | 0               | 1               | 1        |

| <u>SV</u> poo | 1               | 1               | 0               | 0               | 0               | 1                      | 1               | 0               | 0               | 1               | 1               | 0        |

| <u>SV</u> oon | 0               | 1               | 1               | 0               | 0               | 1                      | 1               | 0               | 0               | 0               | 1               | 1        |

| <u>SV</u> ppo | 1               | 1               | 0               | 0               | 1               | 1                      | 0               | 0               | 0               | 1               | 1               | 0        |

| <u>SV</u> opo | 0               | 1               | 1               | 0               | 1               | 1                      | 0               | 0               | 0               | 1               | 1               | 0        |

| <u>SV</u> non | 0               | 0               | 1               | 1               | 0               | 1                      | 1               | 0               | 0               | 0               | 1               | 1        |

| <u>SV</u> opp | 0               | 1               | 1               | 0               | 1               | 1                      | 0               | 0               | 1               | 1               | 0               | 0        |

| <u>SV</u> noo | 0               | 0               | 1               | 1               | 0               | 1                      | 1               | 0               | 0               | 1               | 1               | 0        |

| <u>SV</u> nno | 0               | 0               | 1               | 1               | 0               | 0                      | 1               | 1               | 0               | 1               | 1               | 0        |

| <u>SV</u> oop | 0               | 1               | 1               | 0               | 0               | 1                      | 1               | 0               | 1               | 1               | 0               | 0        |

| <u>SV</u> ono | 0               | 1               | 1               | 0               | 0               | 0                      | 1               | 1               | 0               | 1               | 1               | 0        |

| <u>SV</u> pop | 1               | 1               | 0               | 0               | 0               | 1                      | 1               | 0               | 1               | 1               | 0               | 0        |

| <u>SV</u> pon | 1               | 1               | 0               | 0               | 0               | 1                      | 1               | 0               | 0               | 0               | 1               | 1        |

| <u>SV</u> opn | 0               | 1               | 1               | 0               | 1               | 1                      | 0               | 0               | 0               | 0               | 1               | 1        |

| <u>SV</u> npo | 0               | 0               | 1               | 1               | 1               | 1                      | 0               | 0               | 0               | 1               | 1               | 0        |

| <u>SV</u> nop | 0               | 0               | 1               | 1               | 0               | 1                      | 1               | 0               | 1               | 1               | 0               | 0        |

| <u>SV</u> onp | 0               | 1               | 1               | 0               | 0               | 0                      | 1               | 1               | 1               | 1               | 0               | 0        |

| <u>SV</u> pno | 1               | 1               | 0               | 0               | 0               | 0                      | 1               | 1               | 0               | 1               | 1               | 0        |

| <u>SV</u> pnn | 1               | 1               | 0               | 0               | 0               | 0                      | 1               | 1               | 0               | 0               | 1               | 1        |

| <u>SV</u> ppn | 1               | 1               | 0               | 0               | 1               | 1                      | 0               | 0               | 0               | 0               | 1               | 1        |

| <u>SV</u> npn | 0               | 0               | 1               | 1               | 1               | 1                      | 0               | 0               | 0               | 0               | 1               | 1        |

| <u>SV</u> npp | 0               | 0               | 1               | 1               | 1               | 1                      | 0               | 0               | 1               | 1               | 0               | 0        |

| <u>SV</u> nnp | 0               | 0               | 1               | 1               | 0               | 0                      | 1               | 1               | 1               | 1               | 0               | 0        |

| <u>SV</u> pnp | 1               | 1               | 0               | 0               | 0               | 0                      | 1               | 1               | 1               | 1               | 0               | 0        |

| <u>SV</u> ppp | 1               | 1               | 0               | 0               | 1               | 1                      | 0               | 0               | 1               | 1               | 0               | 0        |

| <u>SV</u> 000 | 0               | 1               | 1               | 0               | 0               | 1                      | 1               | 0               | 0               | 1               | 1               | 0        |

| <u>SV</u> nnn | 0               | 0               | 1               | 1               | 0               | 0                      | 1               | 1               | 0               | 0               | 1               | 1        |

Table 3. Switching vectors and switch states for 3L NPC inverter

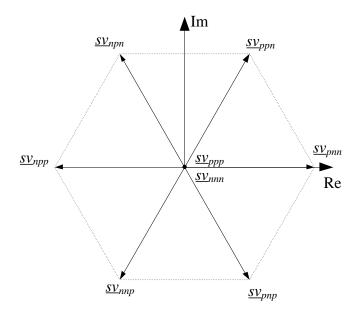

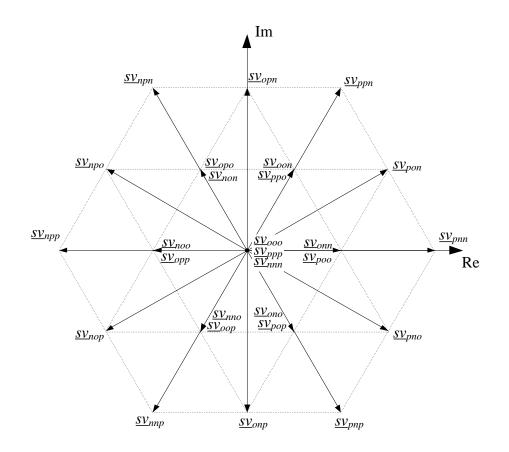

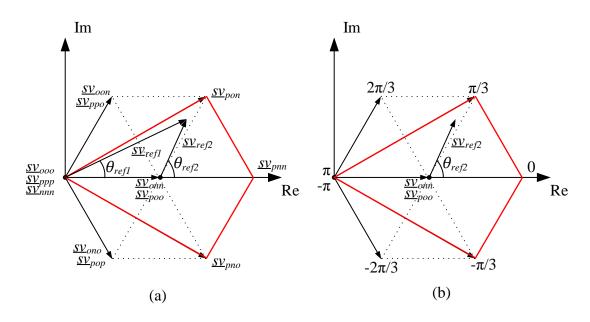

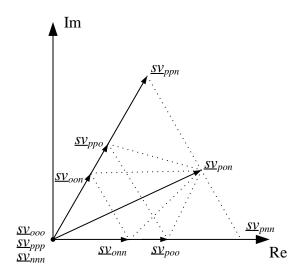

All the switching vectors are presented in a complex coordinates in the Figure 11. These vectors can be divided into four categories based on their length. The first 12 vectors in the Table 3 are short vectors with the length of Udc/3. Each short vector has one redundant short vector pair, as it can be seen in the Figure 11. The next six vectors are medium vectors. The length of the medium vectors is  $Udc/\sqrt{3}$ . The following six vectors are long vectors with the length of 2/3Udc. Neither medium nor long vectors have redundant switching vectors. The last three vectors are mutually redundant zero vectors.

Figure 11. Switching vectors for NPC inverter in a complex coordinates.

#### 3.4.1 Switching times and sequence for NPC

This section gives an explanation how the reference voltage vector is located, the switching times are calculated, and the switching sequence is generated.

Determination of the reference voltage vector location is a bit more complicated for NPC than it was for VSI. There are several reference voltage vector location defining methods for NPC inverter presented in the literature. The method implemented in this thesis is presented in the reference material [14] with slight differences. The implementation in this thesis is based on vector angles.

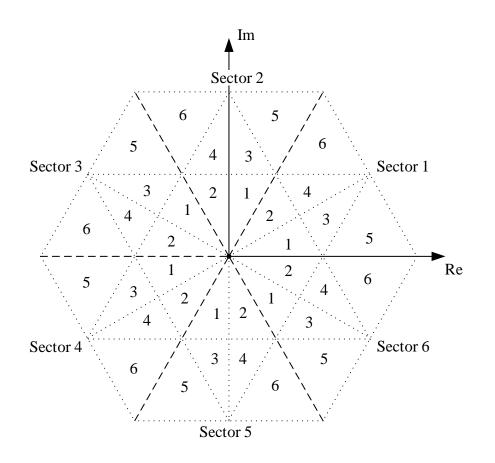

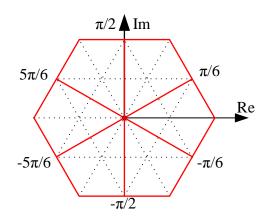

In order to explicitly locate the reference vector, we need to divide the previously introduced switching vector presentation. It is divided into six main sectors and 36 sub-sectors in the Figure 12.

*Figure 12.* Switching vectors are divided into six main sectors. Each main sector can be divided into six sub-sectors.

Main sectors are divided analogously to VSI inverter's switching vector presentation. In addition to VSI implementation, the main sectors are divided into six sub-sectors. The endpoints of the medium and short vectors are used to form the sub-sectors. For now on in this thesis, the sub-sector 2 in the main sector 1 will be referred to S12 etc.

Now we can start to define the location of the reference voltage vector. First, we split the switching vector presentation into six segments presented in Figure 13.

*Figure 13.* Segment division for reference voltage vector location detection purposes.

For example, if the angle of the reference vector respect to real axis is greater than  $-\pi/6$ , but smaller than  $\pi/6$ , we know that the reference vector must be located either in S11, S13, S15, S62, S64 or S66. This examination can be done similarly with all the reference vector angles. To figure out the precise main and sub-sector, we need to define a new vector <u>sv</u><sub>ref2</sub> as presented in the Figure 14 (a).

*Figure 14.* (a) Definition of the new vector  $\underline{sv_{ref2}}$ . (b) New angles as switching vector  $\underline{sv_{onn/poo}}$  is taken as an origin.

This method is clarified with an example. The reference voltage vector  $\underline{sv}_{refl}$  is located in the sector S13 in this example. Using a simple vector calculus, the  $\underline{sv}_{ref2}$  vector can be defined by the equation

$$\underline{sv}_{ref2} = \underline{sv}_{ref1} - \underline{sv}_{onn}.$$

(3.7)

Switching vector <u>sv</u><sub>onn</sub> can be considered as a new origin of this analysis. It is easy to define the angle of the vector <u>sv</u><sub>ref2</sub> respect to real axis after execution of equation 3.7. The angle of the <u>sv</u><sub>ref2</sub> is between  $\pi/3$  and  $2\pi/3$  in this example. Now we can be certain that the <u>sv</u><sub>ref2</sub> is located in S13. This method can be done similarly for all the reference vectors located in any main or sub-sectors.

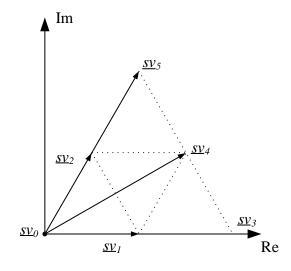

The reference vectors are modulated by using the vectors defining the sub-sector where the reference voltage vector is located. In order to define later calculated switching times for corresponding switching vectors, we need to define explicit numbering of the switching vectors as introduced in the Figure 15.

*Figure 15.* NPC inverter's switching vector numbering for on-time calculation purposes.

The modulated voltage vectors can be defined as [11]

$$\underline{sv}_{ref1} = \frac{t_a}{T_s} \underline{sv}_1 + \frac{t_b}{T_s} \underline{sv}_0 + \frac{t_c}{T_s} \underline{sv}_2$$

(3.8)

for sub-sectors 1 and 2,

$$\underline{sv}_{ref1} = \frac{t_a}{T_s} \underline{sv}_1 + \frac{t_b}{T_s} \underline{sv}_4 + \frac{t_c}{T_s} \underline{sv}_2$$

(3.9)

for sub-sectors 3 and 4,

$$\underline{sv}_{ref1} = \frac{t_a}{T_s} \underline{sv}_1 + \frac{t_b}{T_s} \underline{sv}_4 + \frac{t_c}{T_s} \underline{sv}_3$$

(3.10)

for sub-sector 5 and

$$\underline{sv}_{ref1} = \frac{t_a}{T_s} \underline{sv}_5 + \frac{t_b}{T_s} \underline{sv}_4 + \frac{t_c}{T_s} \underline{sv}_2$$

(3.11)

for subsector 6, where the  $t_a$ ,  $t_b$  and  $t_c$  are switching times of the switching vectors. These equations applies for all the main sectors. The reference voltage vector just have to be rotated to the first sector to check the corresponding applying times.

The actual switching times  $t_a$ ,  $t_b$  and  $t_c$  are calculated next. The calculated switching times applies for all the main sectors. The equations used to calculate the switching times depend on which of the sub-sectors the reference vector is located. The equations are defined in reference material [11] and can be written as

$$t_a = T_s 2K \sin(\frac{\pi}{3} - \theta_{ref1}) \tag{3.12}$$

$$t_b = T_s \left[ 1 - 2K \sin\left(\frac{\pi}{3} + \theta_{ref1}\right) \right]$$

(3.13)

$$t_c = T_s 2Ksin(\theta_{ref1}) \tag{3.14}$$

for sub-sectors 1 and 2,

$$t_a = T_s \left[ 1 - 2K \sin(\theta_{ref1}) \right] \tag{3.15}$$

$$t_b = T_s \left[ 2K \sin\left(\frac{\pi}{3} + \theta_{ref1}\right) - 1 \right]$$

(3.16)

$$t_c = T_s \left[ 1 - 2K \sin\left(\frac{\pi}{3} - \theta_{ref1}\right) \right]$$

(3.17)

for sub-sectors 3 and 4,

$$t_a = T_s \left[ 2 - 2K \sin\left(\frac{\pi}{3} + \theta_{ref1}\right) \right]$$

(3.18)

$$t_b = T_s 2K \sin(\theta_{ref1}) \tag{3.19}$$

$$t_c = T_s \left[ 2K \sin\left(\frac{\pi}{3} - \theta_{ref1}\right) - 1 \right]$$

(3.20)

for sub-sector 5 and

$$t_a = T_s [2K\sin(\theta_{ref1}) - 1]$$

(3.21)

$$t_b = T_s \left[ 2K \sin\left(\frac{\pi}{3} - \theta_{ref1}\right) \right] \tag{3.22}$$

$$t_c = T_s \left[ 2 - 2K \sin\left(\frac{\pi}{3} + \theta_{ref1}\right) \right]$$

(3.23)

for sub-sector 6, where  $K = \sqrt{3} \cdot \frac{|sv_{refl}|}{Udc}$  [1].

Redundant vectors make it complicated to form switching loss minimized modulation cycles for NPC inverter. The order of the switching vectors in which they should be applied to minimize the state changes is presented in the Table 4. Switching times in the first row of the table are not denoted as  $t_a$ ,  $t_b$  or  $t_c$  since the order of the applying times varies between sectors. The order needs to be checked sector sensitively using Figure 15 and equations 3.8-3.11.

|           | time/4        | time/2        | time/2        | time/4        | time/4        | time/2        | time/2        | time/4        |

|-----------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|

| Sector 11 | <u>SV</u> onn | <u>SV</u> oon | <u>SV</u> 000 | <u>SV</u> poo | <u>SV</u> poo | <u>SV</u> 000 | <u>SV</u> oon | <u>SV</u> onn |

| Sector 12 | <u>SV</u> oon | <u>SV</u> 000 | <u>SV</u> poo | <u>SV</u> ppo | <u>SV</u> ppo | <u>SV</u> poo | <u>SV</u> 000 | <u>SV</u> oon |

| Sector 13 | <u>SV</u> onn | <u>SV</u> oon | <u>SV</u> pon | <u>SV</u> poo | <u>SV</u> poo | <u>SV</u> pon | <u>SV</u> oon | <u>SV</u> onn |

| Sector 14 | <u>SV</u> oon | <u>SV</u> pon | <u>SV</u> poo | <u>SV</u> ppo | <u>SV</u> ppo | <u>SV</u> poo | <u>SV</u> pon | <u>SV</u> oon |

| Sector 15 | <u>SV</u> onn | <u>SV</u> pnn | <u>SV</u> pon | <u>SV</u> poo | <u>SV</u> poo | <u>SV</u> pon | <u>SV</u> pnn | <u>SV</u> onn |

| Sector 16 | <u>SV</u> oon | <u>SV</u> pon | <u>SV</u> ppn | <u>SV</u> ppo | <u>SV</u> ppo | <u>SV</u> ppn | <u>SV</u> pon | <u>SV</u> oon |

| Sector 21 | <u>SV</u> oon | <u>SV</u> 000 | <u>SV</u> opo | <u>SV</u> ppo | <u>SV</u> ppo | <u>SV</u> opo | <u>SV</u> 000 | <u>SV</u> oon |

| Sector 22 | <u>SV</u> non | <u>SV</u> oon | <u>SV</u> 000 | <u>SV</u> opo | <u>SV</u> opo | <u>SV</u> 000 | <u>SV</u> oon | <u>SV</u> non |

| Sector 23 | <u>SV</u> oon | <u>SV</u> opn | <u>SV</u> opo | <u>SV</u> ppo | <u>SV</u> ppo | <u>SV</u> opo | <u>SV</u> opn | <u>SV</u> oon |

| Sector 24 | <u>SV</u> non | <u>SV</u> oon | <u>SV</u> opn | <u>SV</u> opo | <u>SV</u> opo | <u>SV</u> opn | <u>SV</u> oon | <u>SV</u> non |

| Sector 25 | <u>SV</u> oon | <u>SV</u> opn | <u>SV</u> ppn | <u>SV</u> ppo | <u>SV</u> ppo | <u>SV</u> ppn | <u>SV</u> opn | <u>SV</u> oon |

| Sector 26 | <u>SV</u> non | <u>SV</u> npn | <u>SV</u> opn | <u>SV</u> opo | <u>SV</u> opo | <u>SV</u> opn | <u>SV</u> npn | <u>SV</u> non |

| Sector 31 | <u>SV</u> non | <u>SV</u> noo | <u>SV</u> 000 | <u>SV</u> opo | <u>SV</u> opo | <u>SV</u> 000 | <u>SV</u> noo | <u>SV</u> non |

| Sector 32 | <u>SV</u> noo | <u>SV</u> 000 | <u>SV</u> opo | <u>SV</u> opp | <u>SV</u> opp | <u>SV</u> opo | <u>SV</u> 000 | <u>SV</u> noo |

| Sector 33 | <u>SV</u> non | <u>SV</u> noo | <u>SV</u> npo | <u>SV</u> opo | <u>SV</u> opo | <u>SV</u> npo | <u>SV</u> noo | <u>SV</u> non |

| Sector 34 | <u>SV</u> noo | <u>SV</u> npo | <u>SV</u> opo | <u>SV</u> opp | <u>SV</u> opp | <u>SV</u> opo | <u>SV</u> npo | <u>SV</u> noo |

| Sector 35 | <u>SV</u> non | <u>SV</u> npn | <u>SV</u> npo | <u>SV</u> opo | <u>SV</u> opo | <u>SV</u> npo | <u>SV</u> npn | <u>SV</u> non |

| Sector 36 | <u>SV</u> noo | <u>SV</u> npo | <u>SV</u> npp | <u>SV</u> opp | <u>SV</u> opp | <u>SV</u> npp | <u>SV</u> npo | <u>SV</u> noo |

| Sector 41 | <u>SV</u> noo | <u>SV</u> 000 | <u>SV</u> oop | <u>SV</u> opp | <u>SV</u> opp | <u>SV</u> oop | <u>SV</u> 000 | <u>SV</u> noo |

| Sector 42 | <u>SV</u> nno | <u>SV</u> noo | <u>SV</u> 000 | <u>SV</u> oop | <u>SV</u> oop | <u>SV</u> 000 | <u>SV</u> noo | <u>SV</u> nno |

| Sector 43 | <u>SV</u> noo | <u>SV</u> nop | <u>SV</u> oop | <u>SV</u> opp | <u>SV</u> opp | <u>SV</u> oop | <u>SV</u> nop | <u>SV</u> noo |

| Sector 44 | <u>SV</u> nno | <u>SV</u> noo | <u>SV</u> nop | <u>SV</u> oop | <u>SV</u> oop | <u>SV</u> nop | <u>SV</u> noo | <u>SV</u> nno |

| Sector 45 | <u>SV</u> noo | <u>SV</u> nop | <u>SV</u> npp | <u>SV</u> opp | <u>SV</u> opp | <u>SV</u> npp | <u>SV</u> nop | <u>SV</u> noo |

| Sector 46 | <u>SV</u> nno | <u>SV</u> nnp | <u>SV</u> nop | <u>SV</u> oop | <u>SV</u> oop | <u>SV</u> nop | <u>SV</u> nnp | <u>SV</u> nno |

| Sector 51 | <u>SV</u> nno | <u>SV</u> ono | <u>SV</u> 000 | <u>SV</u> oop | <u>SV</u> oop | <u>SV</u> 000 | <u>SV</u> ono | <u>SV</u> nno |

| Sector 52 | <u>SV</u> ono | <u>SV</u> 000 | <u>SV</u> oop | <u>SV</u> pop | <u>SV</u> pop | <u>SV</u> oop | <u>SV</u> 000 | <u>SV</u> ono |

| Sector 53 | <u>SV</u> nno | <u>SV</u> ono | <u>SV</u> onp | <u>SV</u> oop | <u>SV</u> oop | <u>SV</u> onp | <u>SV</u> ono | <u>SV</u> nno |

| Sector 54 | <u>SV</u> ono | <u>SV</u> onp | <u>SV</u> oop | <u>SV</u> pop | <u>SV</u> pop | <u>SV</u> oop | <u>SV</u> onp | <u>SV</u> ono |

| Sector 55 | <u>SV</u> nno | <u>SV</u> nnp | <u>SV</u> onp | <u>SV</u> oop | <u>SV</u> oop | <u>SV</u> onp | <u>SV</u> nnp | <u>SV</u> nno |

| Sector 56 | <u>SV</u> ono | <u>SV</u> onp | <u>SV</u> pnp | <u>SV</u> pop | <u>SV</u> pop | <u>SV</u> pnp | <u>SV</u> onp | <u>SV</u> ono |

| Sector 61 | <u>SV</u> ono | <u>SV</u> 000 | <u>SV</u> poo | <u>SV</u> pop | <u>SV</u> pop | <u>SV</u> poo | <u>SV</u> 000 | <u>SV</u> ono |

| Sector 62 | <u>SV</u> onn | <u>SV</u> ono | <u>SV</u> 000 | <u>SV</u> poo | <u>SV</u> poo | <u>SV</u> 000 | <u>SV</u> ono | <u>SV</u> onn |

| Sector 63 | <u>SV</u> ono | <u>SV</u> pno | <u>SV</u> poo | <u>SV</u> pop | <u>SV</u> pop | <u>SV</u> poo | <u>SV</u> pno | <u>SV</u> ono |

| Sector 64 | <u>SV</u> onn | <u>SV</u> ono | <u>SV</u> pno | <u>SV</u> poo | <u>SV</u> poo | <u>SV</u> pno | <u>SV</u> ono | <u>SV</u> onn |

| Sector 65 | <u>SV</u> ono | <u>SV</u> pno | <u>SV</u> pnp | <u>SV</u> pop | <u>SV</u> pop | <u>SV</u> pnp | <u>SV</u> pno | <u>SV</u> ono |

| Sector 66 | <u>SV</u> onn | <u>SV</u> pnn | <u>SV</u> pno | <u>SV</u> poo | <u>SV</u> poo | <u>SV</u> pno | <u>SV</u> pnn | <u>SV</u> onn |

Table 4. Order of the switching vectors for NPC inverter

# 4. REQUIREMENTS FOR ADVANCED SPACE VECTOR MODULATOR

Chapter 3 introduced the basic space vector PWM schemes and explained how the modulation is implemented in the simulation models in this thesis. This chapter concentrates on special requirements a practical well-implemented space vector modulator needs to include. The requirements discussed in this chapter are modulator working in the overmodulation region, insertion and compensation of a blanking time, minimum times between the IGBT's control pulses, DC capacitors unbalance and loss optimal switching scheme. It should be noted that the methods explained in this chapter are not implemented in the simulation models presented in Chapter 5.

#### 4.1 Limit on amplitude of the reference voltage vector

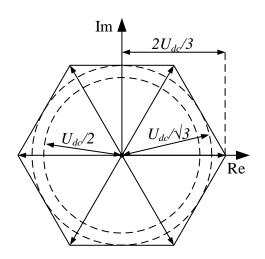

The operation of the modulator can be divided in two regions based on the length of the reference voltage vector. The sections are linear modulation and overmodulation regions. These regions are clarified in the Figure 16.

Figure 16. DC voltage utilization in different modulation methods.

The amplitude of the reference voltage vector needs to be limited to ensure that the operation will be in the linear modulation region. The maximum length of the reference vector is  $U_{dc}/\sqrt{3}$  when using space vector modulation method. That equals the length of the medium switching vectors of NPC inverter. It applies for both, VSI and NPC inverters. The outer circle in the Figure 16 illustrates the boundary between linear and overmodulation regions in space vector PWM. It can be seen that a vector with the length over  $U_{dc}/\sqrt{3}$  can exceed the sector defined by long switching vectors with the length of  $2U_{dc}/3$ . Thus, it would be require overmodulation operation. The inner circle with the length of  $U_{dc}/2$  demonstrates the maximum linearly modulated phase voltage amplitude when using a traditional sine-PWM method [8]. Therefore, the DC voltage utilization is roughly 15% better in space vector implementations. This is one of the reasons the space vector PWM has overtaken the traditional modulation scheme.

The term modulation index *m* is used in the simulations of this thesis. It refers to the length of the reference voltage vector compared to the DC voltage  $U_{dc}$  divided by  $\sqrt{3}$  and can be written as

$$m = \frac{|\underline{sv}_{ref}|}{U_{dc}/\sqrt{3}}.$$

(4.1)

#### 4.2 Blanking time

IGBTs are not ideal switches. Real life switches have turn-on and turn-off delay times, and finite rise and fall times. When it comes to a voltage source inverters, a well-implemented modulator needs to make sure that a short circuiting between DC busses are avoided. This phenomenon is prevented by adding delay to the on-switching instants. The time used to delay the on-switching instants is called a blanking time [8]. Unintentional short circuiting during IGBT switch state changes would cause undesired effects, such as additional losses, increased wear of the components and decreased MTTF. Long enough short circuiting can easily destroy the IGBT modules at once. The blanking time is typically few microseconds with today's IGBT technology. Blanking time effect on switching pulses is presented in the Figure 17.

*Figure 17.* Blanking time implementation to IGBTs' control signals. On-time signals are delayed with blanking time.

Dashed line represents the ideal switching instants. The actual switching pulse is provided after the blanking time. Blanking time is drawn relatively too long compared to the switching time to make the presentation clearer.

There is no voltage provided to the inverter's output phase during the blanking time. This cause changes to the output voltage. The change is either positive or negative, depending on the direction of the current [8].

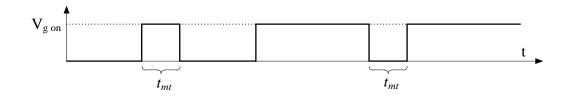

#### 4.3 Minimum pulse-width time

A minimum pulse-width time limitation is another requirement deriving from IGBT switch non-idealities. The minimum pulse-width time requirement relates to a small on-time control pulse durations [17]. It is desired to allow the IGBT module to fully change its state between changes in the control pulse. This manner is applied to avoid IGBT switch failures [17]. Pulses with a length less than the minimum allowed time can be either dropped, or applied for a specified time duration. Figure 18 presents the situation, when the pulses are applied for a minimum pulse-width time.

*Figure 18.* Implementation of the minimum pulse-width time in control pulse of an individual IGBT switch.

The minimum off-time is also controlled in the implementation presented. This is because the IGBTs work as a pairs as stated earlier. There is always another switch, which is in on-state during the off-state of the studied switch. Therefore, also the off-time cannot be shorter than the defined minimum pulse. The minimum pulse-width time has an effect on the resulted output voltages.

#### 4.4 Minimum time between successive pulses

Time between the state changes in different phase legs of an inverter should also be discussed [16]. A well implemented modulator should be safe and reliable to use in motor applications. Requirement of the minimum time between successive pulses relate to the motor utilizations. Modulator needs to prevent instantaneous state changes between two different phase outputs. The magnitudes of line-to-line voltage transients are doubled if this is not prevented. It is obvious that not preventing this kind of operation would cause a damage to the motor insulation.

It is also desired that the oscillation occurring in motor cables after state changes has enough time to settle. If consecutive pulse is applied too early, the previous oscillation seen in the cables hasn't necessarily settled. It is possible that the previous oscillation pulse adds up with the new state change. Usually, the implemented criterion of minimum time between successive pulses is few microseconds [16].

#### 4.5 DC-bus unbalance

The DC capacitors may be loaded differently during modulation periods. This is an issue with the multilevel inverters, such as NPC. DC-bus unbalance causes some movements to the switching vectors. It should be noted that the redundant short vectors move to different directions if the capacitors are unbalanced as shown in the Figure 19.

*Figure 19.* Unbalance in the DC bus capacitors causes movement to the switching vectors.

The situation presented in the Figure 19 is a consequence of the capacitor  $C_1$  having a greater voltage than the capacitor  $C_2$  (Figure 2). This kind of voltage drifting can be handled with an advanced modulation algorithm. More of it can be read from the reference material [10].

#### 4.6 Loss optimal modulation scheme

There are multiple modulation methods presented in the literature to minimize the switching losses. A method presented in reference material [6] is discussed in this section. The basic of the method is that there are sections in the inverter's phase outputs when the output state is not changed. It is said that the phase output is 'clamped' to a certain DC bus. The 'no-switching' period is located in the middle of the peak of the load current to minimize the switching losses. In order to locate the 'no-switching' instants, the load power factor must be known.