### THANG LUONG CAO Serial bus adapter design for FPGA Master of Science Thesis

Examiner: Prof. Timo D. Hämäläinen Examiner and topic approved by the Faculty Council of the Faculty of Computing and Electrical Engineering On May 6, 2015.

### ABSTRACT

TAMPERE UNIVERSITY OF TECHNOLOGY Master's Degree Programme in Electrical Engineering **THANG, LUONG CAO: Serial bus adapter design for FPGA** Master of Science Thesis, 63 pages April 2015 Major: Communication Circuits and Systems Examiner: Prof. Timo D. Hämäläinen Keywords: Serial bus, I<sup>2</sup>C, adapter, SoC, FPGA, HPS, simulation

In recent years, FPGAs (Field Programmable Gate Arrays) have become a popular platform for testing and implementing hardware designs by increasing their capacity and cost efficiency in the competition with Application Specific Integrated Circuits (ASICs). Processors can be used for any problem but they have not been optimized for specific problems. The design of ASIC is an extremely complex task, very time consuming and expensive; they are used for mass products. FPGA is an intermediate solution between general purpose processors and ASICs. Altera Cyclone V 28nm is a *System On Chip (SoC)*, which integrates a *Hard Processor Core (HPS)*, peripherals, and memory controller with the FPGA fabric. However, HPS consist of only one-directional serial data (SDA) buses and serial clock (SCL) buses and provides support for a communication link only between integrated circuits on a board. It is necessary to build an I<sup>2</sup>C serial bus adapter in order to communicate between HPS and other devices outside the board.

$I^2C$  serial bus adapter is implemented and tested in this thesis. It adapts the communication from one-directional serial data line of hard processor system to bidirectional data line. In order to test the  $I^2C$  adapter in both writing data operation and reading data operation, Signal Generator blocks to generate testing signals are implemented and  $I^2C$  Slave block from OpenCores to detect and display data to LEDs is used. All the blocks are implemented in *VHSIC Hardware Description Language* (*VHDL*).

The verifications for  $I^2C$  Adapter, Signal Generator and  $I^2C$  Slave are inspected by waveforms on Modelsim SE 10.2c simulator. The block implementations are compiled and programmed by Quartus II 13.1 to DE1-SoC FPGA development board. DE1-SoC board buttons and LEDs are used to test the  $I^2C$  adapter operation by a user. The results show that the adapter works as specified.

### PREFACE

The research through my Master's Thesis was conducted during academic year 2014-2015 at the Department of Pervasive Computing at Tampere University of Technology.

I would like to thank Prof. Timo D. Hämäläinen for the opportunity to work this project. I am especially grateful to Dr. Tech. Erno Salminen for his time and dedication provided to the completion of my thesis, because of his long design meetings, guidance and advices.

I also would like to thank to all of my friends in Finland who were being with me during time in this beautiful country, my good friend Stefanus Arinno for helping me a lot and Julio Cesar for his motivation pictures at my work station office forcing me to finish my thesis all the time.

Last but not the least; I am grateful for my family, my parents Long and Nguyen, my younger brother Loc for their support throughout my study and life.

Tampere, April 2015

Luong Cao Thang

# CONTENTS

| DEV   |                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.1   |                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|       | -                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|       |                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|       |                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2.3.3 |                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2.3.4 |                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2.3.5 | •                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2.3.6 | R/ <b>W</b> bit                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| IMPL  | EMENTATION ON FPGA                                                                                                                                                                                                                                                                     | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.1   | Block Diagrams                                                                                                                                                                                                                                                                         | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.1.1 | Writing data process                                                                                                                                                                                                                                                                   | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.1.2 | Reading data process                                                                                                                                                                                                                                                                   | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.2   | Signal generator                                                                                                                                                                                                                                                                       | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.2.1 | Signal generator to write                                                                                                                                                                                                                                                              | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.2.2 | Signal generator to read                                                                                                                                                                                                                                                               | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.3   | I <sup>2</sup> C Adapter                                                                                                                                                                                                                                                               | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.3.1 | I <sup>2</sup> C Adapter Block                                                                                                                                                                                                                                                         | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

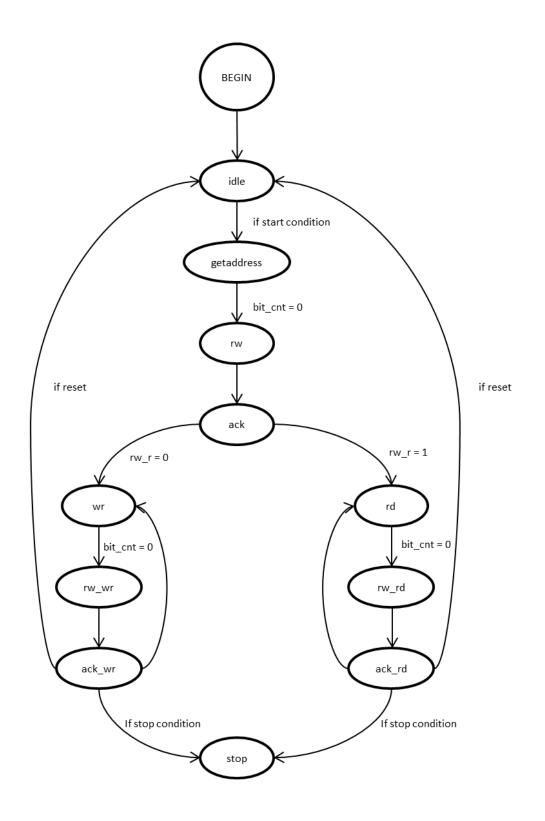

| 3.3.2 | Finite State Machine                                                                                                                                                                                                                                                                   | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.3.3 | How I <sup>2</sup> C Adapter work                                                                                                                                                                                                                                                      | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

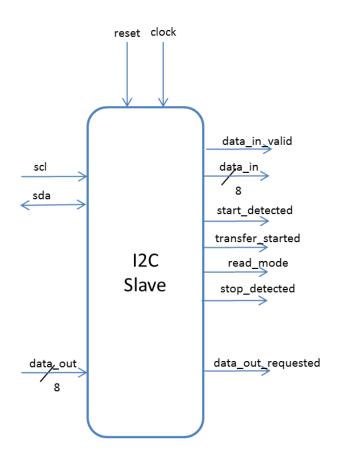

| 3.4   | I <sup>2</sup> C Slave                                                                                                                                                                                                                                                                 | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

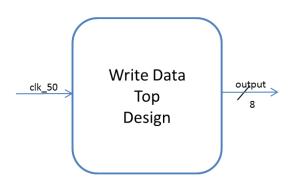

| 3.5   | Top Level Design                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|       |                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|       | -                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|       |                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|       |                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|       | -                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|       | 0                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|       |                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|       |                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4.3   |                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|       | DEV<br>2.1<br>2.2<br>2.3<br>2.3.1<br>2.3.2<br>2.3.3<br>2.3.4<br>2.3.5<br>2.3.6<br>IMPI<br>3.1<br>3.1.1<br>3.1.2<br>3.2<br>3.2.1<br>3.2.2<br>3.2.1<br>3.2.2<br>3.3<br>3.3.1<br>3.3.2<br>3.3.3<br>3.4<br>3.5<br>VERI<br>4.1<br>4.1.1<br>4.1.2<br>4.1.3<br>4.2<br>4.2.1<br>4.2.2<br>4.2.3 | 2.2       Utilized tools         2.3       I <sup>2</sup> C Protocol         2.3.1       Introduction         2.3.2       Protocol         2.3.3       Start and stop conditions         2.3.4       Byte format.         2.3.5       Acknowledge (ACK) and not acknowledge (NACK)         2.3.6       R/W bit.         IMPLEMENTATION ON FPGA.         3.1       Block Diagrams.         3.1.1       Writing data process.         3.1.2       Reading data process.         3.1.3       Signal generator         3.2.1       Signal generator to write         3.2.2       Signal generator to read         3.3.1       I <sup>2</sup> C Adapter         3.3.1       I <sup>2</sup> C Adapter Block         3.3.2       Finite State Machine         3.3.3       How I <sup>2</sup> C Adapter work         3.4       I <sup>2</sup> C Slave         3.5       Top Level Design         VERIFICATION AND RESULT         4.1       Writing Data Process Verification         4.1.1       Verification of Signal Generator To Write in Writing Data Process.         4.1.2       Verification of I <sup>2</sup> C Adapter in Writing Data Process.         4.1.3       Verification of I <sup>2</sup> C Slave in Writing Data Process.         4. |

|    | 4.3.1 | Register Transfer Level                   | 59 |

|----|-------|-------------------------------------------|----|

|    | 4.3.2 | Assign Pins and Display Result by DE1-SoC | 60 |

| 5. | CONC  | LUSIONS                                   | 62 |

## LIST OF FIGURES

| Figure 1.1 Altera SoC FPGA Device Block Diagram                                                                 | 2  |

|-----------------------------------------------------------------------------------------------------------------|----|

| Figure 1.2 Board Block Diagram                                                                                  | 2  |

| Figure 1.3 Block Diagram on DE1-SoC                                                                             | 4  |

| Figure 1.4 Block Diagram on DE1-SoC for Writing Data Operation                                                  | 5  |

| Figure 1.5 Block Diagram on DE1-SoC for Reading Data Operation                                                  | 5  |

| Figure 2.1 DE1-SoC Board                                                                                        | 6  |

| Figure 2.2 I <sup>2</sup> C bus configuration                                                                   | 8  |

| Figure 2.3 Start and Stop conditions                                                                            | 10 |

| Figure 2.4 Data transfer on the $I^2C$ bus                                                                      | 11 |

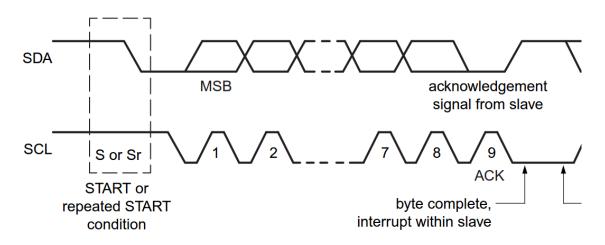

| Figure 2.5 Acknowledgement on $I^2C$ bus                                                                        | 11 |

| Figure 2.6 A complete data transfer                                                                             | 12 |

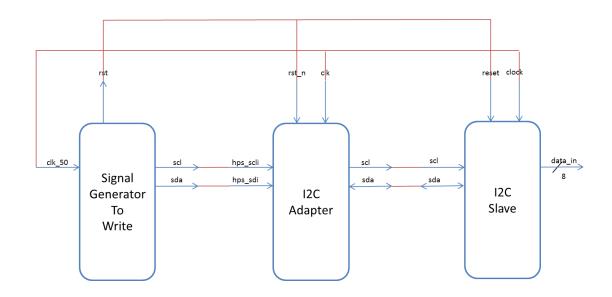

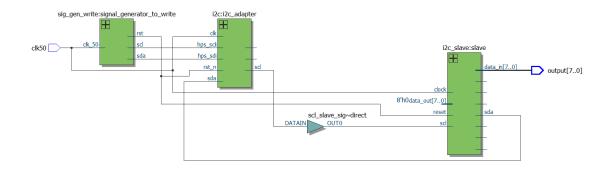

| Figure 3.1 Writing data process block diagram                                                                   | 13 |

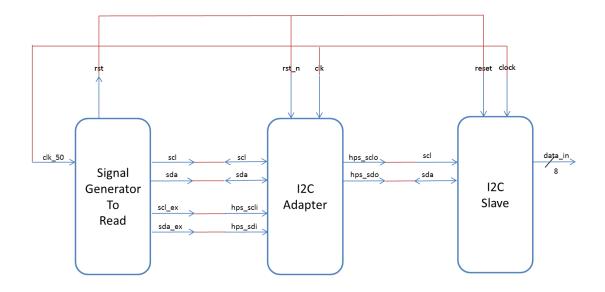

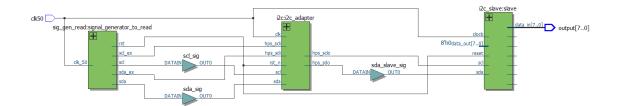

| Figure 3.2 Reading data process block diagram                                                                   | 14 |

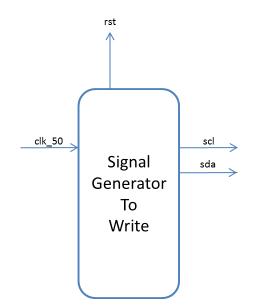

| Figure 3.3 Signal Generator To Write Block                                                                      | 15 |

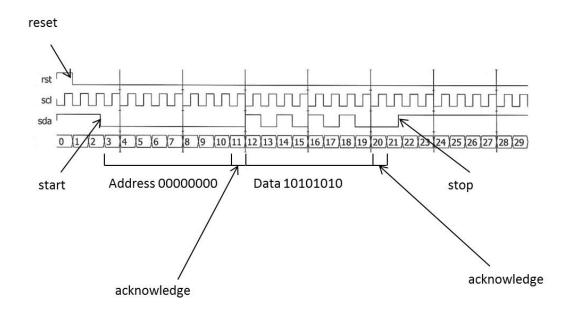

| Figure 3.4 Address and data signals waveform generated by Signal Generator To                                   |    |

| Write                                                                                                           | 16 |

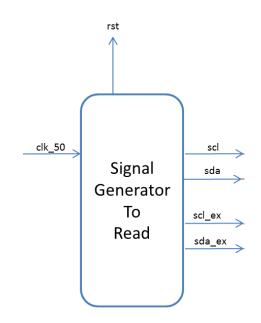

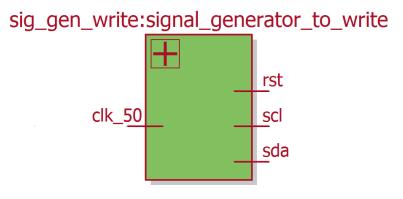

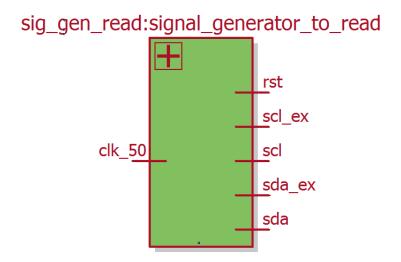

| Figure 3.5 Signal Generator To Read Block                                                                       | 17 |

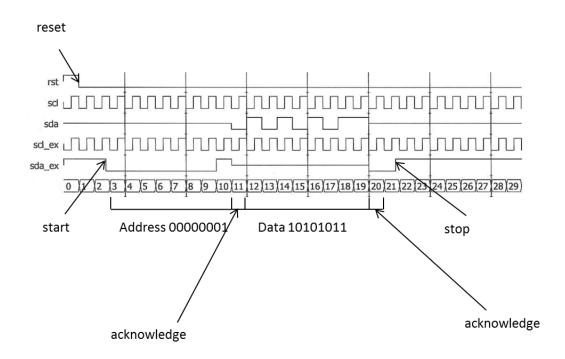

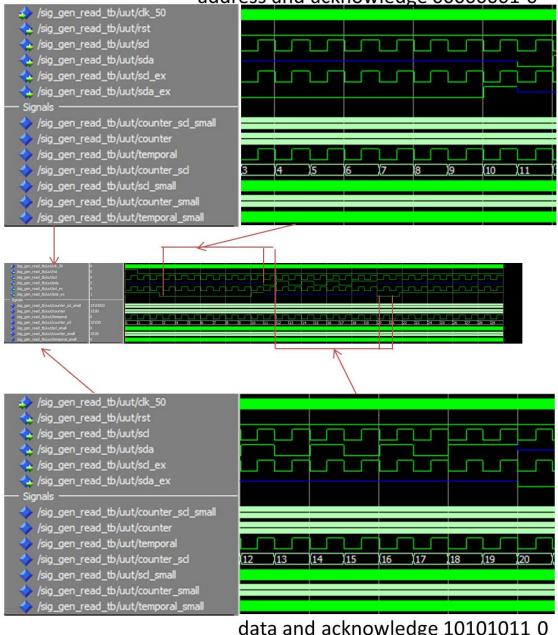

| Figure 3.6 Address and data signals waveform generated by Signal Generator To Read                              | 10 |

|                                                                                                                 |    |

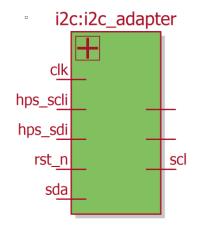

| Figure 3.7 I2C Adapter Block.                                                                                   |    |

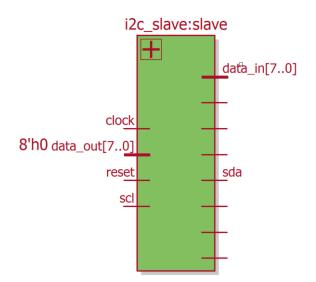

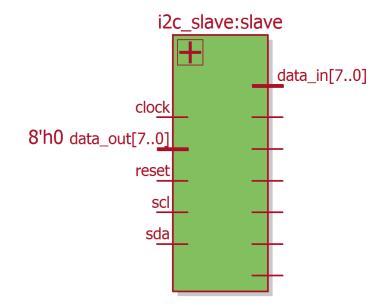

| Figure 3.8 Finite state machine of I2C Adapter block<br>Figure 3.9 I2C Slave Block                              |    |

| Figure 3.9 12C Stave Block<br>Figure 3.10 Write Data Top Design Block                                           |    |

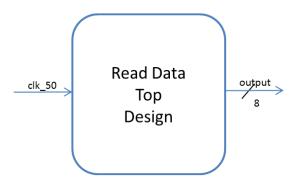

| Figure 3.11 Read Data Top Design block                                                                          |    |

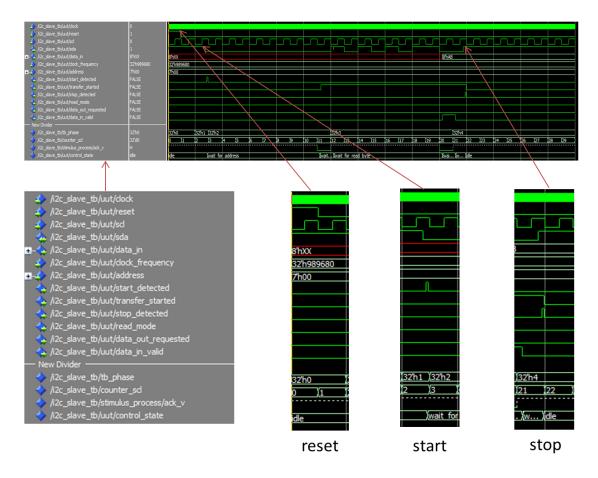

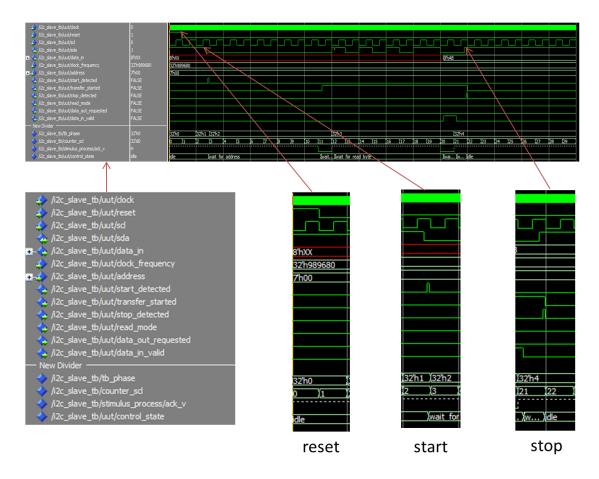

| Figure 4.1 Modelsim testbench for reset, start and stop of Signal Generator To<br>Write in Writing Data Process | 31 |

| Figure 4.2 Modelsim testbench for address and data transmission of Signal                                       |    |

| Generator To Write in Writing Data Process                                                                      | 32 |

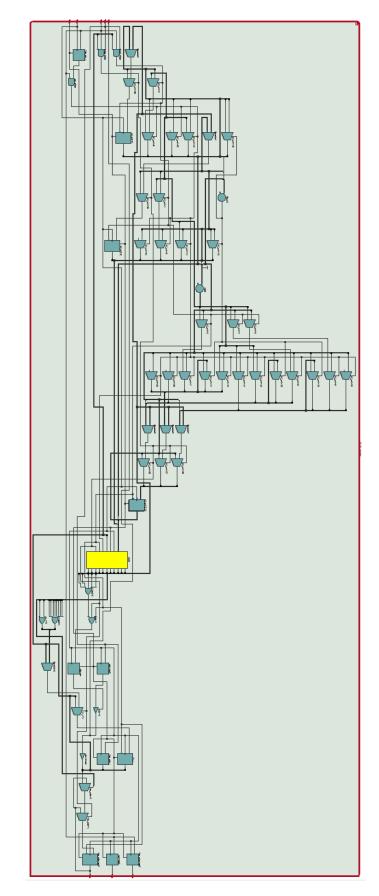

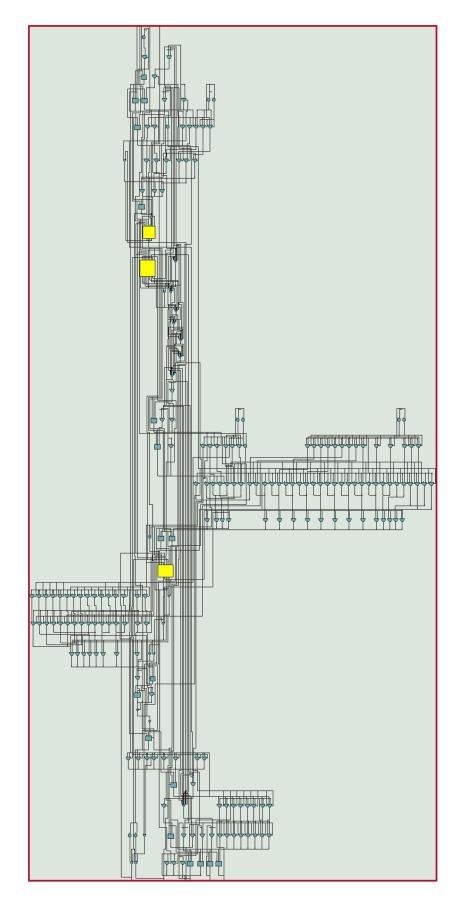

| Figure 4.3 Signal Generator To Write Block on RTL Viewer of Quartus II in<br>Writing Data Process               | 33 |

| Figure 4.4 Inside Signal Generator To Write Block on RTL Viewer of Quartus II                                   |    |

| in Writing Data Process                                                                                         | 34 |

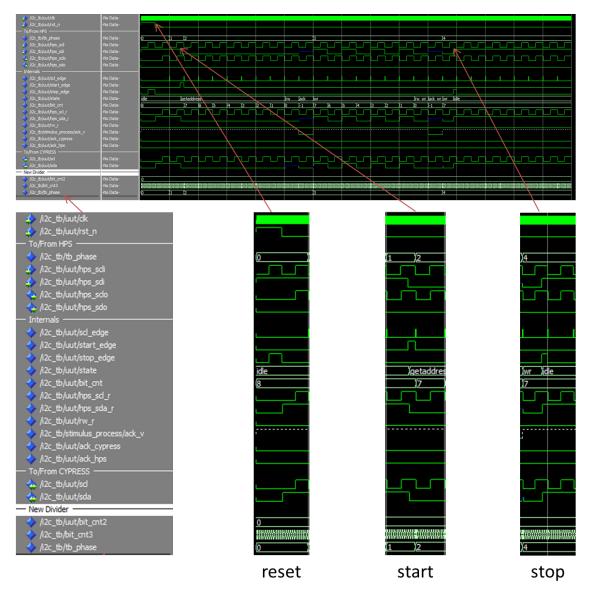

| Figure 4.5 Modelsim testbench for reset, start and stop of I2C Adapter in Writing                               |    |

| Data Process.                                                                                                   | 35 |

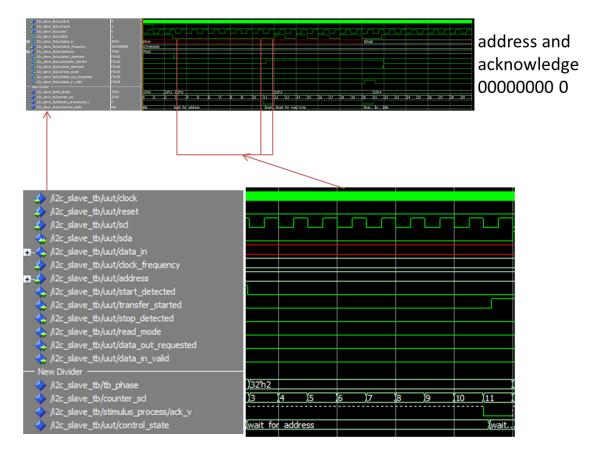

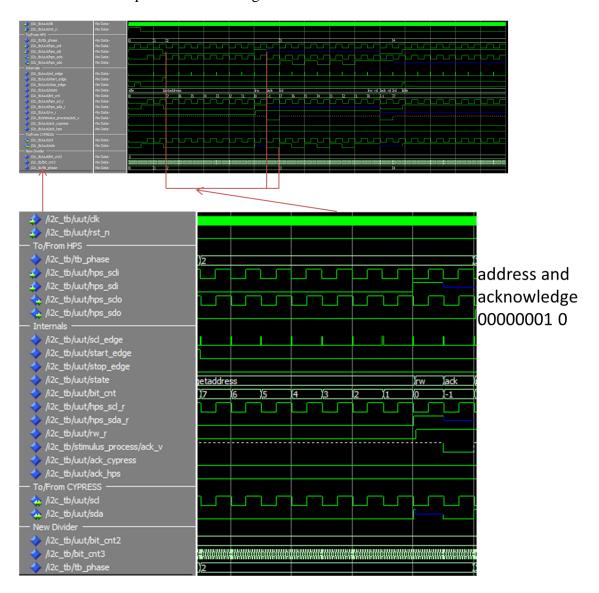

| Figure 4.6 Modelsim testbench for address transmission of I2C Adapter in         |      |

|----------------------------------------------------------------------------------|------|

| Writing Data Process                                                             | 36   |

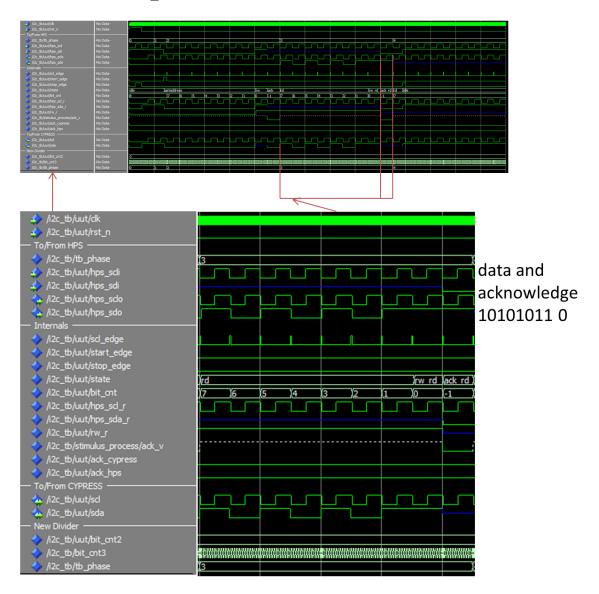

| Figure 4.7 Modelsim testbench for data transmission of I2C Adapter in Writing    |      |

| Data Process.                                                                    | 37   |

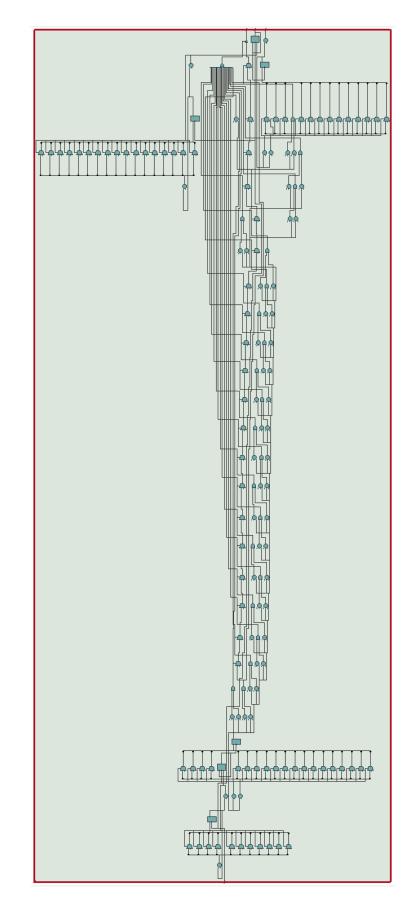

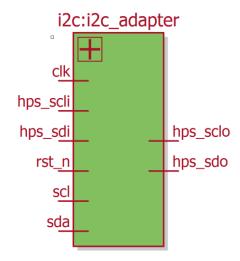

| Figure 4.8 I2C Adapter Block on RTL Viewer of Quartus II in Writing Data         |      |

| Process.                                                                         | 38   |

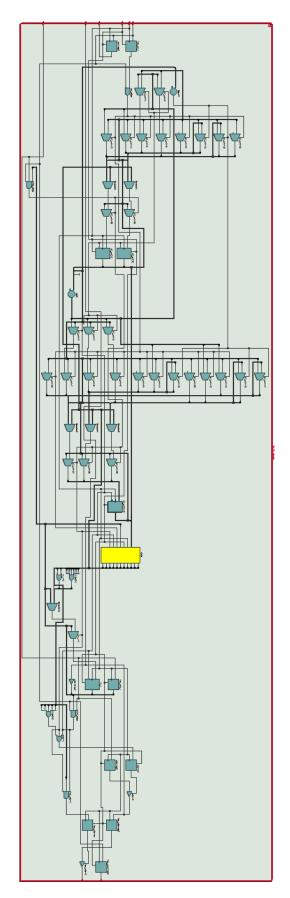

| Figure 4.9 Inside I2C Adapter Block on RTL Viewer of Quartus II in Writing Data  |      |

| Process.                                                                         | 39   |

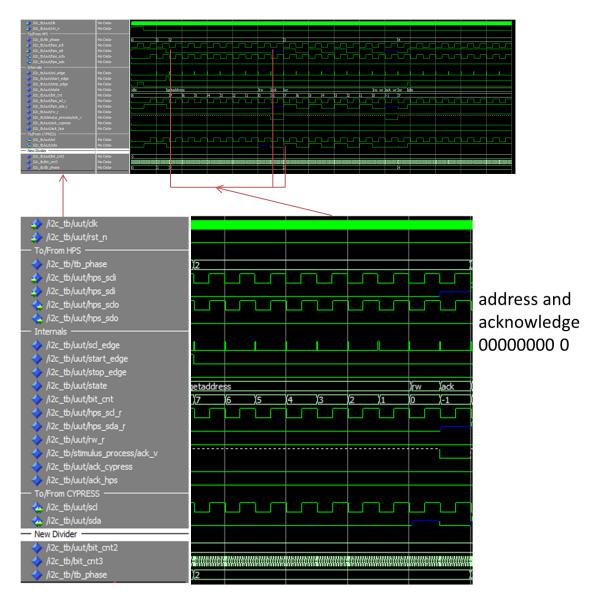

| Figure 4.10 Modelsim testbench for reset, start and stop of I2C Slave in Writing |      |

| Data Process.                                                                    | 40   |

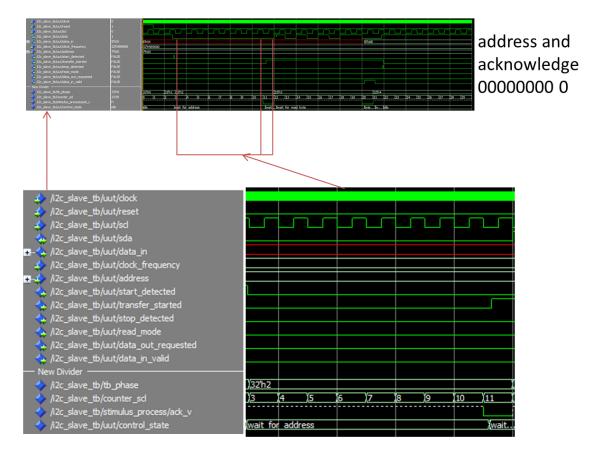

| Figure 4.11 Modelsim testbench for address transmission of I2C Slave in Writing  |      |

| Data Process.                                                                    | 41   |

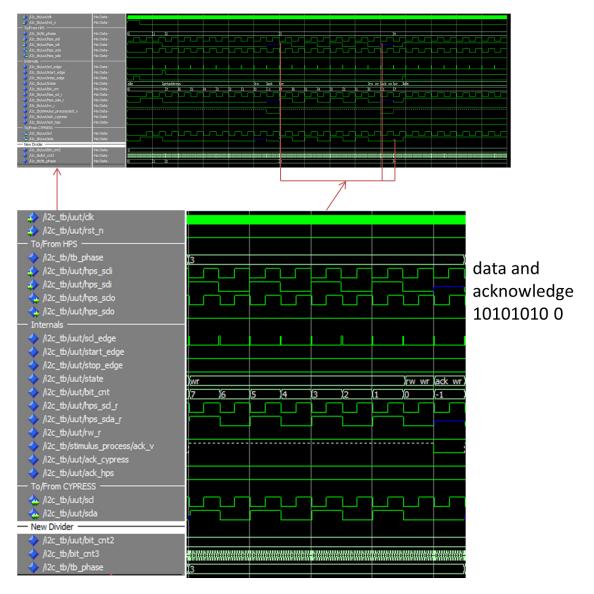

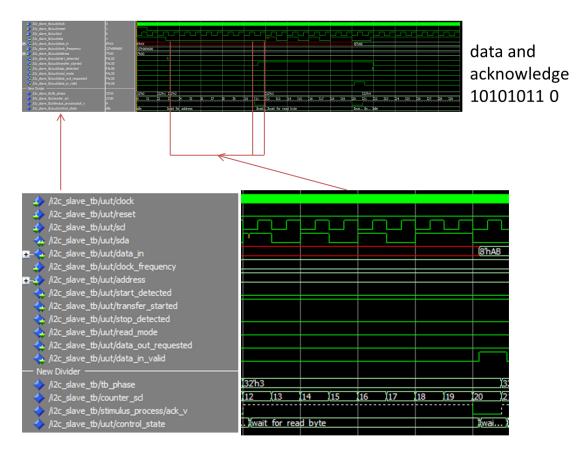

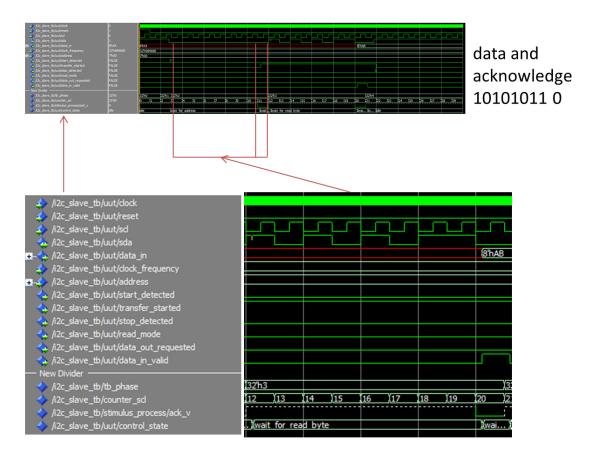

| Figure 4.12 Modelsim testbench for data transmission of I2C Slave in Writing     |      |

| Data Process.                                                                    | 42   |

| Figure 4.13 I2C Slave Block on RTL Viewer of Quartus II in Writing Data          | . 12 |

| Process.                                                                         | 13   |

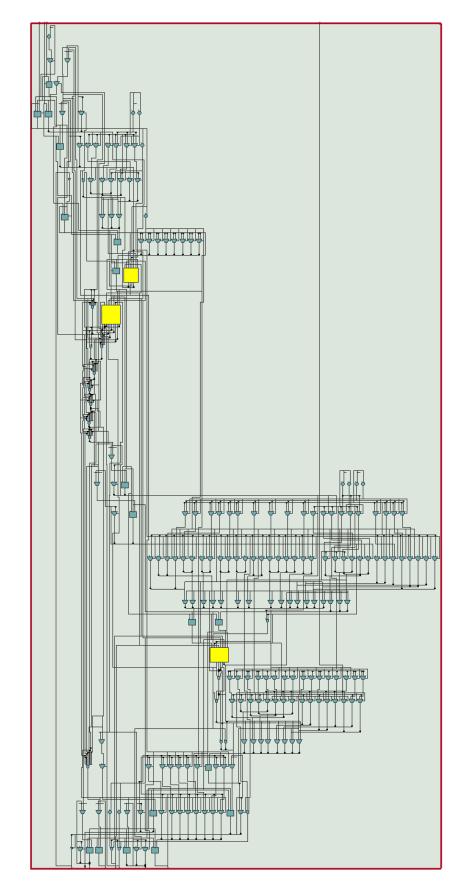

| Figure 4.14 Inside I2C Slave Block on RTL Viewer of Quartus II in Writing Data   | .45  |

|                                                                                  | 11   |

| Process.                                                                         |      |

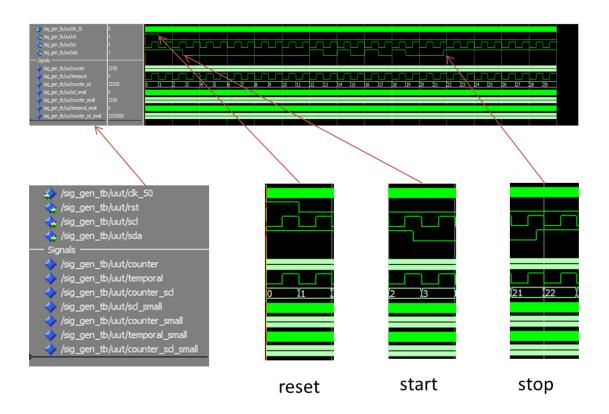

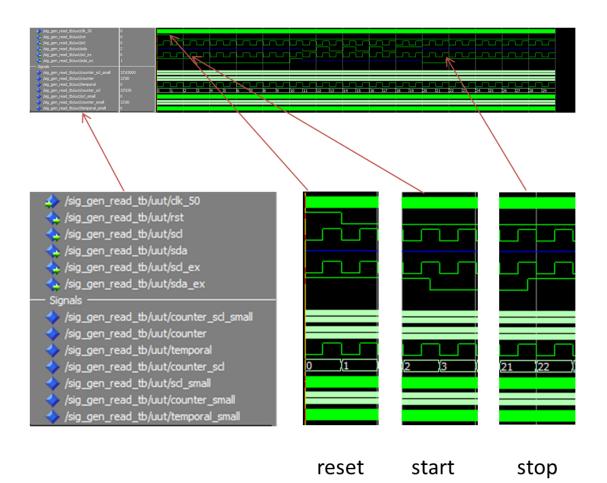

| Figure 4.15 Modelsim testbench for reset, start and stop of Signal Generator To  | 15   |

| Read in Reading Data Process.                                                    | 45   |

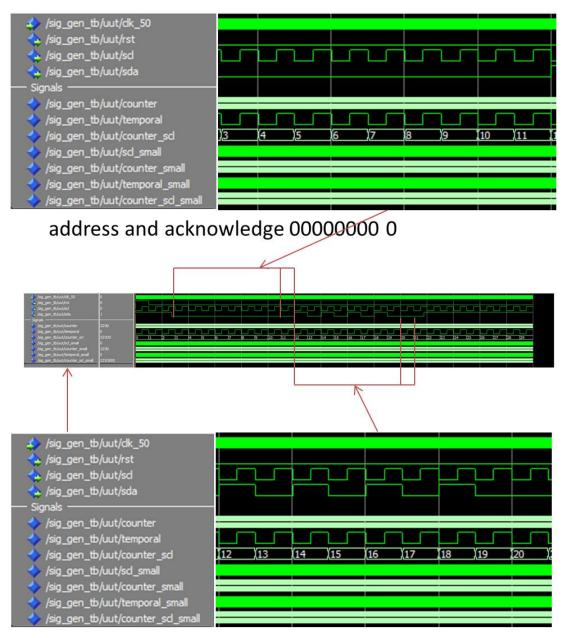

| Figure 4.16 Modelsim testbench for address and data transmission of Signal       | 16   |

| Generator To Read in Reading Data Process                                        | 40   |

| Figure 4.17 Signal Generator To Read Block on RTL Viewer of Quartus II in        |      |

| Reading Data Process                                                             | 47   |

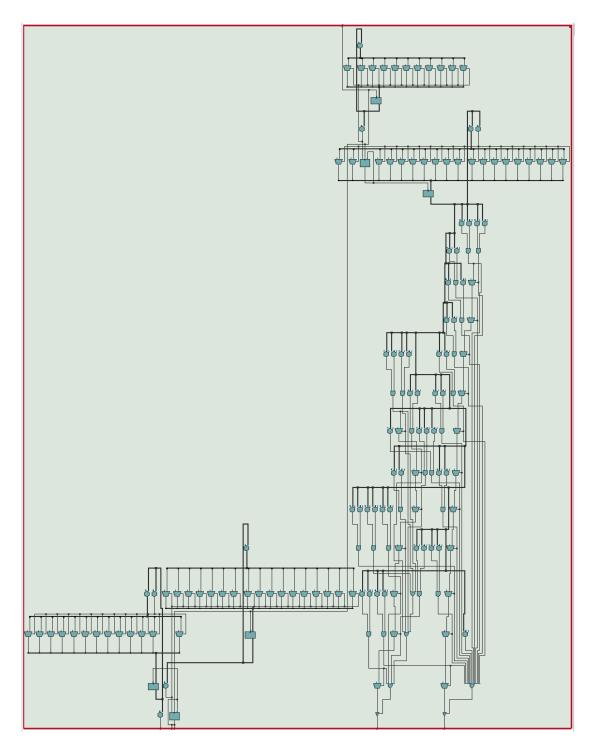

| Figure 4.18 Inside Signal Generator To Read Block on RTL Viewer of Quartus II    |      |

| in Reading Data Process                                                          | 48   |

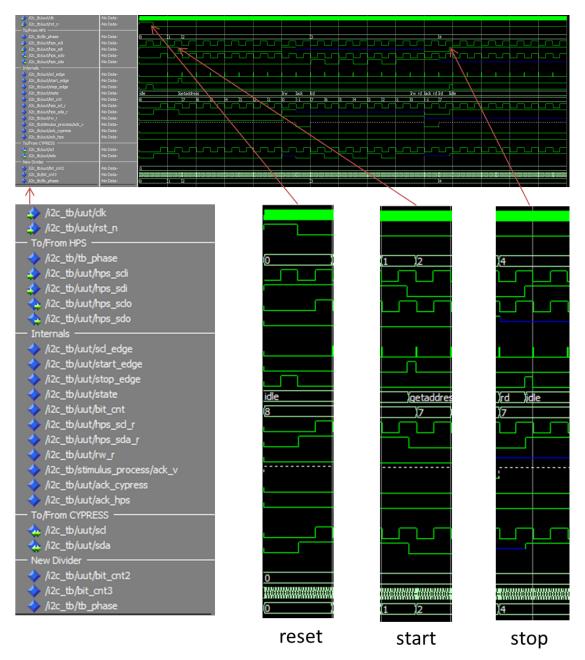

| Figure 4.19 Modelsim testbench for reset, start and stop of I2C Adapter in       |      |

| Reading Data Process                                                             | 49   |

| Figure 4.20 Modelsim testbench for address transmission of I2C Adapter in        |      |

| Reading Data Process                                                             | . 50 |

| Figure 4.21 Modelsim testbench for data transmission of I2C Adapter in Reading   |      |

| Data Process.                                                                    | 51   |

| Figure 4.22 I2C Adapter Block on RTL Viewer of Quartus II in Reading Data        |      |

| Process.                                                                         | 52   |

| Figure 4.23 Inside I2C Adapter Block on RTL Viewer of Quartus II in Writing      |      |

| Data Process.                                                                    | 53   |

| Figure 4.24 Modelsim testbench for reset, start and stop of I2C Slave in Reading |      |

| Data Process.                                                                    | 54   |

| Figure 4.25 Modelsim testbench for address transmission of I2C Slave in Reading  |      |

| Data Process.                                                                    | 55   |

| Figure 4.26 Modelsim testbench for data transmission of I2C Slave in Reading     |      |

| Data Process.                                                                    | 56   |

| Figure 4.27 I2C Slave Block on RTL Viewer of Quartus II in Reading Data        |    |

|--------------------------------------------------------------------------------|----|

| Process.                                                                       | 57 |

| Figure 4.28 Inside I2C Slave Block on RTL Viewer of Quartus II in Reading Data |    |

| Process.                                                                       | 58 |

| Figure 4.29 Top Level Design for Writing Data Process on RTL Viewer of         |    |

| Quartus II                                                                     | 59 |

| Figure 4.30 Top Level Design for Reading Data Process on RTL Viewer of         |    |

| Quartus II                                                                     | 59 |

| Figure 4.31 Assignment Editor for Top Level Design.                            | 60 |

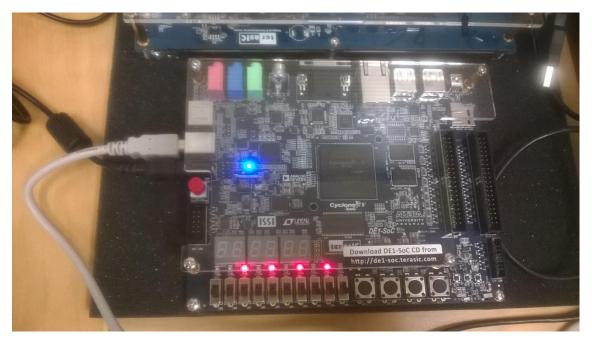

| Figure 4.32 Output of Top Level Design Block displaying on Leds of DE1-SoC in  |    |

| Writing Data Process                                                           | 61 |

| Figure 4.33 Output of Top Level Design Block displaying on Leds of DE1-SoC in  |    |

| Reading Data Process                                                           | 61 |

# LIST OF SYMBOLS AND ABBREVIATIONS

| FPGAs    | Field Programmable Gate Arrays                 |

|----------|------------------------------------------------|

| ASICs    | Application Specific Integrated Circuits       |

| SoC      | System on Chip                                 |

| HPS      | Hard Processor System                          |

| PCB      | Printed Circuit Board                          |

| SDRAM    | Synchronous dynamic random access memory       |

| DAC      | Digital to analog converter                    |

| ADC      | Analog to digital converter                    |

| I2C      | I squared C                                    |

| SDA      | Serial Data Line                               |

| SCL      | Serial Clock Line                              |

| ACK      | Acknowledge                                    |

| NACK     | Not Acknowledge                                |

| SPI      | Serial Peripheral Interface                    |

| UART     | Universal Asynchronous Receiver Transmitter    |

| CAN      | Control Area Network                           |

| USB      | Universal Serial Bus                           |

| Rst      | Reset                                          |

| Rst_n    | Negative Reset                                 |

| Clk      | Clock                                          |

| Clk_50   | Clock 50 MHz                                   |

| Scl_ex   | Serial clock line extra                        |

| Sda_ex   | Serial data line extra                         |

| Hps_scli | Hard processor system serial clock line input  |

| Hps_sdi  | Hard processor system serial data line input   |

| Hps_sclo | Hard processor system serial clock line output |

| Hps_sdo  | Hard processor system serial data line output  |

| Data_in  | Data input                                     |

| Wr       | Write state                                    |

| Rd       | Read state                                     |

| Rw_wr    | Read/Write of Write State                      |

| Rw_rd   | Read/Write of Read State                            |

|---------|-----------------------------------------------------|

| Ack_wr  | Acknowledge of Write State                          |

| Ack_rd  | Acknowledge of Read State                           |

| ICs     | Integrated Circuits                                 |

| MSB     | Most Significant Bit                                |

| LSB     | Least Significant Bit                               |

| I/O     | Input/output                                        |

| RTL     | Register Transfer Level                             |

| FSM     | Finite State Machine                                |

| SPD     | Serial Presence Detect                              |

| EEPROMs | Electrically Erasable Programmable Read-Only Memory |

| NVRAM   | Non-volatile Random Access Memory                   |

|         |                                                     |

# 1. INTRODUCTION

A Field Programmable Gate Array (FPGA) is an integrated circuit designed to be configured by a customer or designer after manufacturing. The basic blocks in an FPGA device are Logic Elements (LE) and the interconnections between them are programmable to communicate each other [1]. Reprogrammable logic device provides a fast and cost efficient way for testing and implementing custom digital designs. A variety of reusable Intellectual Property (IP) components allows the designer to create complex designs in reasonable time and synthesizable soft-core processors providing the possibility to implement functionality using software. It is often easier and faster to implement complex functionality using software rather than implementing the same functionality on hardware logic [2]. The *field programmable* can be understood as the ability to program it in the field or programming can be done by the end-user [3]. In compare to processors [4] and Application Specific Integrated Circuits (ASICs) [5], FPGAs are inexpensive and they can even outperform the others, since designers can develop application specific logic that take advantage of the inner parallelism of the given problem; FPGA are designed to provide good performance for any application, whereas ASIC are just designed for a given problem. Beside the advantages of FPGA over ASIC in terms of flexible reprogrammable ability, early testing stages, shorter time-to-market, it cannot get over ASIC by area, delay, power consumption and unit price in high volume products. There is a measurement done by Kuon and Rose in their research about the gap between FPGAs and ASICs [6].

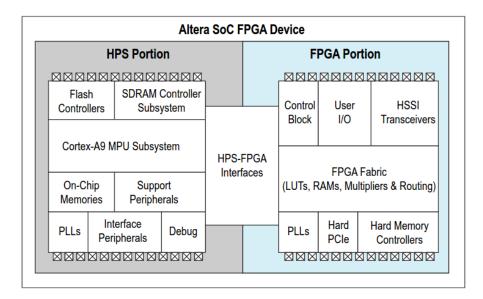

Figure 1.1 Altera SoC FPGA Device Block Diagram [8].

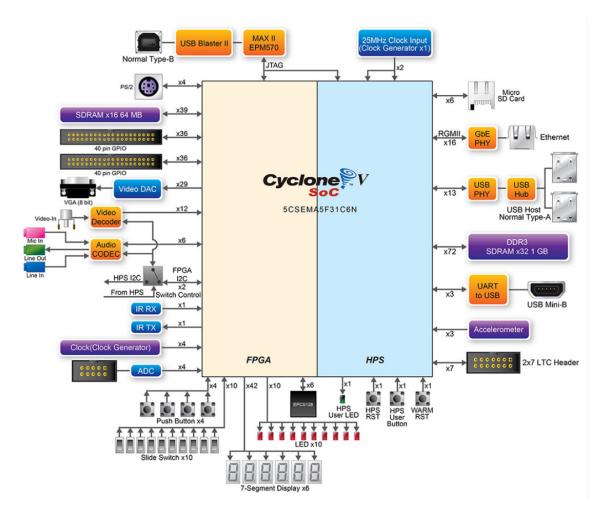

Figure 1.2 Board Block Diagram [9].

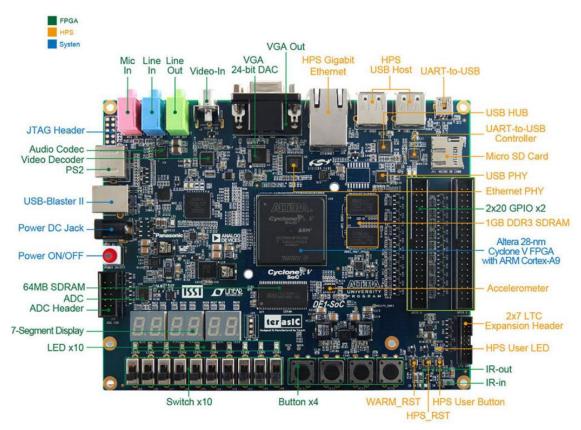

Altera Cyclone V 28nm is a *System On Chip (SoC)*, which integrates a *Hard Processor Core (HPS)*, peripherals, and memory controller with the FPGA fabric using a high-bandwidth interconnect backbone [7][8]. Cyclone V is available on DE1-SoC FPGA development board. The Altera SoC FPGA Device Block Diagram is shown in Figure 1.1 and Figure 1.2 illustrates the DE1-SoC board block diagram for Cyclone V in a FPGA development board.

Inter-Integrated Circuit, abbreviated as  $I^2C$  is a serial bus short distance protocol invented by Philips Semiconductor to transfer data among ICs. Because of advantages in simplicity and low manufacturing cost,  $I^2C$  is nowadays one of the most popular serial bus communication protocols in the market together with other serial bus communication protocols such as SPI [26], UART [27], CAN [28], USB [29], and so on. There are many devices, which have I/O I<sup>2</sup>C interface and communicate with other devices following the I<sup>2</sup>C protocol. Examples of I<sup>2</sup>C compatible devices are Analog to Digital Converter, Digital to Analog Converter, EEPROM, Real Time Clock [30],Real Time Calendar [31], Temperature Sensor [32], LCD multimedia color touch panel from TerasIC, and so on.

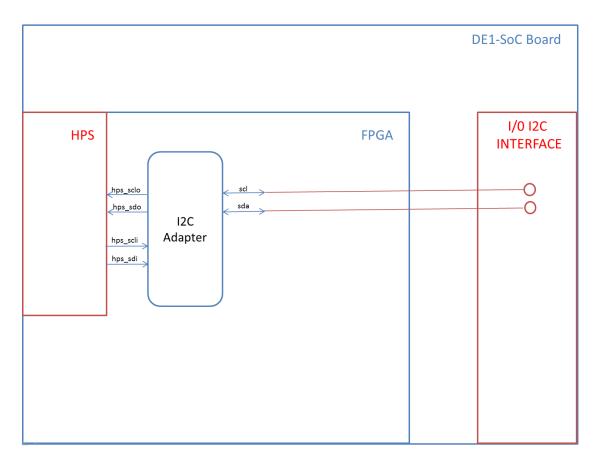

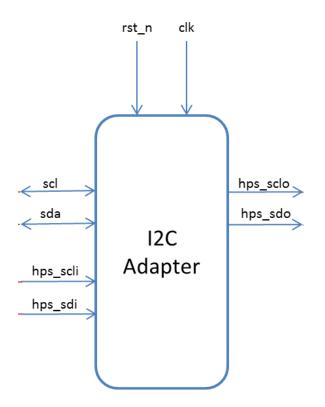

The I<sup>2</sup>C protocol is applied to I<sup>2</sup>C compatible devices which have bi-directional signals serial data (SDA) and serial clock (SCL). However, the Hard Processor System on Altera Cyclone V has only one-directional I<sup>2</sup>C buses, one serial clock and one serial data for signals coming in to HPS, and one serial clock and one serial data for signals coming out from HPS. In order to adapt the communication between one-directional serial data line of HPS and bi-directional serial data line following the I<sup>2</sup>C protocol, it is necessary to implement a serial bus adapter as illustrated in Figure 1.3.

Figure 1.3 Block Diagram on DE1-SoC.

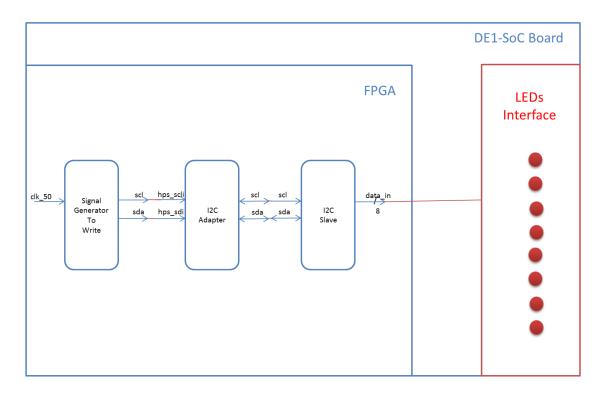

For this thesis, a serial bus Adapter to make communication between HPS Portion and FPGA Portion following I<sup>2</sup>C protocol in Altera SoC FPGA Device is created. In order to test the I<sup>2</sup>C Adapter, there is also Signal Generator to produce testing signals and an I<sup>2</sup>C Slave from OpenCores is involved. The data generated by the Signal Generator after going through I<sup>2</sup>C Adapter is detected at I<sup>2</sup>C Slave and displayed to the LEDs of the DE1-SoC Board for Writing Data Operation and Reading Data Operation as shown in Figure 1.4 and Figure 1.5 respectively. The thesis is divided into the following chapters. Chapter 2 introduces devices and tools used in the work. The implementation of blocks is presented in Chapter 3. Chapter 4 shows verification and results of block implementations by software as well as by compiling and programming the FPGA device. Chapter 5 is the conclusions for this thesis.

Figure 1.4 Block Diagram on DE1-SoC for Writing Data Operation.

Figure 1.5 Block Diagram on DE1-SoC for Reading Data Operation.

# 2. DEVICES AND I<sup>2</sup>C PROTOCOL

This Chapter presents an introduction to the  $I^2C$  protocol. Devices and utilized tools used in this work are described.

### 2.1 Platform

The platform used in this work is DE1-SoC FPGA development board. The DE1-SoC board has many features that allow users to implement a wide range of designed circuits, from simple circuits to various multimedia projects [10].

Figure 2.1 DE1-SoC Board [10].

An overview of the specification of DE1-SoC Board is following [10]:

FPGA Device:

- Cyclone V SoC 5CSEMA5F31C6 Device

- Duo-core ARM Cortex-A9 (HPS)

- 85K Programmable Logic Elements

- 44500 Kbits embedded memory

- 6 Fractional PLLs

- 2 Hard Memory Controllers

Configuration and Debug:

- Serial Configuration device EPCS128 on FPGA

- On-Board USB Blaster II (Normal Type B USB connector)

Connectors:

- Two 40-pin Expansion Headers (voltage levels: 3.3V)

- One 10-pin ADC Input Header

- One LTC connector (One Serial Peripheral Interface (SPI) Master, one I2C and one GPIO interface)

Switches, Button and Indicators:

- 4 User Keys (FPGA x4)

- 10 User switches (FPGA x10)

- 11 User LEDs (FPGA x10; HPS x1)

- 2 HPS Reset Buttons (HPS\_RST\_n and HPS\_WARM\_RST\_n)

- Six 7-segment displays

### 2.2 Utilized tools

The following tools were used in this work:

• Altera Quartus II [11]

Quartus II is used for analysis and synthesis of the HDL design of the project. Quartus II enables the developer to compile designs, perform timing analysis, examine RLT diagrams, simulate a design's response to stimulation, and configure the target device with the programmer. The version used in the project is Quartus II 13.1 (64-bit).

• Modelsim [13]

Modelsim is a hardware simulation and debug environment by Mentor Graphics, primarily targeted at smaller ASIC and FPGA designs. Modelsim is used to verify and simulate for VHDL design of project. The version used in the project is Modelsim SE 10.2 c.

### 2.3 I<sup>2</sup>C Protocol

#### 2.3.1 Introduction

From 1980s, Philips Semiconductors Company created the  $I^2C$  interface which is used for data transfer among ICs at the Printed Circuit Board (PCB) level. The concept is connecting all the  $I^2C$  bus compatible devices which have an  $I^2C$  interface. This concept allows devices communicate directly with each other devices via  $I^2C$  bus [14].

In I<sup>2</sup>C, designs proceed rapidly from block diagram to final schematic and interconnections are minimized that ICs have fewer pins. With simplicity and low manufacturing cost, I<sup>2</sup>C is common in many applications such as reading configuration data on SDRAM [15], supporting systems management for PCI cards [16], accessing low speed DACs [17] and ADCs [18], and display data channel. I<sup>2</sup>C is now implemented in over 1000 different ICs [19] and broadly adopted by many leading chip design companies like Intel, Texas Instrument, Analog Devices, *etc*.

#### 2.3.2 Protocol

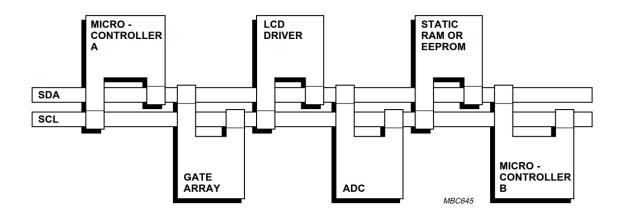

In  $I^2C$ , only two signal lines are required; a serial data line (SDA) and a serial clock line (SCL). Each device connected to the bus is software addressable by a unique address and simple master/slave relationships exist at all times; masters can operate as master-transmitters or as master-receivers. The device that initiates communication is called the Master, and at that time, all the other devices on the bus are considered Slaves.

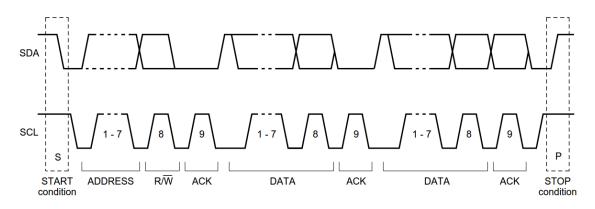

*Figure 2.2*  $I^2C$  bus configuration [20].

Figure 2.2 illustrates I2C bus configuration and Table 2.1 describe some basic I2C bus terminology. First, consider when microcontroller A wants to send information to microcontroller B, microcontroller A is master and addresses microcontroller B is the slave. Microcontroller A (master-transmitter) sends data to microcontroller B (slave-receiver) and microcontroller A terminates the transfer. When a Master wants to initiate a communication, it issues a "START" condition. At that time, Slave has to listen to the bus for incoming data. After the "START" is issued, the Master sends the "ADDRESS" of the Slave that it wishes to communicate with along with a bit to indicate the direction of the data transfer (either read or write). Slave will then compare its address with the address received on the bus. If the address matches, the Slave will send an "ACKNOWLEDGEMENT" (ACK) to the Master. Slave whose address does not match will not send an ACK. Once communication is established, the two lines are busy. No other device is allowed to control the lines except the Master and the Slave which was selected. When the Master wants to terminate communication, it will issue a "STOP" signal. After that, both SCL line and SDA line are released and free.

So far we have introduced the "START", "ADDRESS", "ACKNOWLEDGEMENT" and "STOP" signals. We will discuss these signals in more detail later. Terms used in  $I^2C$  bus are summarized in the Table 2.1.

| Term        | Description                                                                                   |

|-------------|-----------------------------------------------------------------------------------------------|

| Transmitter | the device which sends data to bus                                                            |

| Receiver    | the device which receives data from bus                                                       |

| Master      | the device which initiates a transfer,<br>generate clock signals and terminates a<br>transfer |

| Slave       | the device addressed by a master                                                              |

*Table 2.1* Definition of  $I^2C$  bus terminology [21].

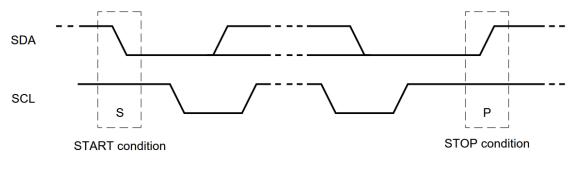

#### 2.3.3 Start and stop conditions

When a Master wants to initiate a data transfer, it issues a START condition and when it wants to terminate the transfer, a STOP condition will be initiated. There can be multiple STARTs during once transaction called a repeated START. The Master can then release the STOP condition whenever it wants to.

Figure 2.3 Start and Stop conditions [21].

As you can see in Figure 2.3, a START is issued by bringing the SDA line low while the SCL line is high. A STOP condition is implemented by transitioning the SDA line high while the SCL line is high. START and STOP conditions are always generated by the Master. The bus is considered to be busy after the START condition. The bus stays busy if a repeated START is generated instead of a STOP condition. In this respect, the STARTS and repeated START conditions are functionally identical. After that the Master controls the SCL line and can generate clock signals.

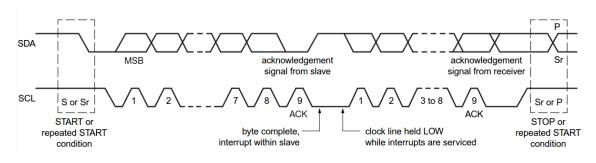

### 2.3.4 Byte format

The I<sup>2</sup>C bus is a byte-oriented protocol. After signaling Slave by the START condition, the Master sends "starting byte" to the Slave. There are two components that make us the "starting bytes": Slave address and data direction (Read or Write). The Master sends the MSB (Most Significant Bit) first and the LSB (Least Significant Bit) last. There are two addressing modes in the I<sup>2</sup>C protocol: the 7-bit and 10-bit address modes.

We will first consider the 7-bit addressing mode. Every byte put on the SDA line must be eight bits long. The number of bytes that can be transmitted per transfer is unrestricted. Each byte must be followed by an Acknowledge bit. If a Slave cannot receive or transmit another complete byte of data until it has performed some other function, for example servicing an internal interrupt, it can hold the clock line SCL LOW to force the master into a wait state. Data transfer then continues when the Slave is ready for another byte of data and releases clock line SCL. Data transfer on the I<sup>2</sup>C bus is illustrated in the Figure 2.4.

*Figure 2.4* Data transfer on the  $I^2C$  bus [21].

With the 10-bit addressing mode, when the  $I^2C$  bus became more popular, it was recognized that the number of available addresses in the 7-bit addressing mode is too small. Therefore, a new addressing mode (the 10-bit mode) was developed. The new addressing mode also supports the old one. Devices with 7-bit addresses can be connected with devices with 10-bit addresses on the same mode. In this mode, the first two bytes are dedicated for address and data direction. The format of the first byte is 11110xx; the last two bits of the first byte, combined with eight bits in the second byte form the 10-bit address.

#### 2.3.5 Acknowledge (ACK) and not acknowledge (NACK)