### MIKKO NIKU DESIGN OF A CASCADE CONTROLLED BOOST-POWER-STAGE CONVERTER FOR PHOTOVOLTAIC APPLICATION

Master of Science Thesis

Examiner: Teuvo Suntio Examiner and the topic were approved in the Faculty of Computing and Electrical Engineering Council meeting on 15.01.2014

## TIIVISTELMÄ

TAMPEREEN TEKNILLINEN YLIOPISTO Sähkötekniikan diplomi-insinöörin tutkinto **MIKKO NIKU: Aurinkosähkögeneraattorin syöttämän kaskadisäädetyn nostavan teholähteen suunnittelu** Diplomityö, 53 sivua, 6 liitesivua Syyskuu 2014 Pääaine: Teholähde-elektroniikka Tarkastajat: Prof. Teuvo Suntio Avainsanat: Kaskadisäätö, suunnittelu, dc-dc nostava teholähde, aurinkosähkö

Aurinkosähkögeneraattori muuttaa auringon sähkömagneettisen säteilyn sähköenergiaksi. Tehoelektroniikkalaitteet ovat tärkein väline tuotetun aurinkosähkögeneraattoriin hallinnoinnissa esimerkiksi lähteen ja verkon välillä. Aurinkosähkögeneraattoriin kytketyn tehoelektroniikkalaitteen suunnittelu perustuu generaattorin sähköisiin ominaisuuksiin, kuten maksimilähtötehoon, oikosulkuvirtaan ja avoimen piirin jännitteeseen, jotka ovat riippuvaisia säteilytehotiheydestä ja lämpötilasta. Myös aurinkosähkögeneraattorin lähtöimpedanssilla on merkittävä vaikutus esimerkiksi säädön suunnitteluun. Tietyissä olosuhteissa mitattua Raloss SR30-36 aurinkopaneelin mittausdataa käytettiin hyödyksi tässä työssä.

Tässä työssä suunniteltiin aurinkosähkögeneraattorin lähtöön kytketty kaskadisäädetty jännitettä nostava teholähde. Säätö toteutettiin siten, että sisempi säätösilmukka kontrolloi kelavirtaa ja ulompi säätösilmukka vastaavasti sisäänmenojännitettä. Tämän työn päätavoitteena oli oikean dynaamisen mallin löytäminen, sekä dynaamisen resistanssin vaikutuksen tutkiminen säädön suunnittelussa. Prototyyppiteholähde rakennettiin ja digitaalinen säätö toteutettiin työssä esitellyn suunnittelun pohjalta. Prototyyppilaitteen suljetun silmukan taajuusvasteet, sekä jännitereferenssin askelvasteet mitattiin teoreettisen mallin avulla saatujen tulosten vahvistamiseksi. Idea tällaisen säädön testaamiseen saatiin hiljattain julkaistuista tutkimuksista.

Mittaustulokset vahvistivat, että työssä luotu teoreettinen malli vastaa oikean laitteen toimintaa. Tosin, jos säätö toteutetaan digitaalisesti, tulee näytteenottoviive ottaa huomioon suunnittelussa. Kaksi PI-säädintä riitti stabiilin järjestelmän aikaansaamiseen. Dynaamisella resistanssilla oli huomattava vaikutus säädön suorituskykyyn. Säätö reagoi hitaammin referenssin muutokseen, kun toimintapiste oli aurinkosähkögeneraattorin vakiojännitealueella. Dynaamisella resistanssilla ei ollut vaikutusta järjestelmän lähtöimpedanssiin. Lisätutkimusta tarvitaan esitellyn säädön toteuttamiskelpoisuuden varmistamiseksi, johon tämä työ antaa hyvän pohjan.

## ABSTRACT

TAMPERE UNIVERSITY OF TECHNOLOGY Master's Degree Programme in Electrical Engineering **MIKKO NIKU: Design of a Cascade Controlled Boost-Power-Stage Converter for Photovoltaic Application** Master of Science Thesis, 53 pages, 6 Appendix pages September 2014 Major: Switched-mode converter design Examiner: Prof. Teuvo Suntio Keywords: Cascade control, design, dc-dc boost converter, photovoltaic generator

A photovoltaic generator converts solar radiation into electrical energy. Power electronic converters are of prime importance in managing the produced energy e.g. between source and grid. Design of a photovoltaic generator interfacing converter is based on the electrical characteristics of the generator. Characteristics such as: maximum output power, short circuit current and open circuit voltage, which are dependent on the amount of insolation and the value of ambient temperature, are important to know when the converter is designed. Also, the dynamic resistance of a photovoltaic generator has a significant effect especially on the control design. Measurement data of the electrical characteristics of a Raloss SR30-36 solar panel measured in certain climate conditions was used in the design in this thesis.

In this thesis, a boost-power-stage converter with a cascaded inner inductor-current and outer input-voltage control was designed for photovoltaic generator interfacing. The main focus of this work is in obtaining a correct dynamic model for such a system, as well as, to evaluate the effect of the dynamic resistance on control. A prototype converter was built based on the design, and the control was implemented digitally. Every closed-loop frequency response of the converter and the responses to a voltage reference step-change were measured in order to verify the theoretical findings. The idea for testing this type of control was obtained from recent publications.

The measurement results confirmed that the obtained system model was correct, however, if the control is implemented digitally, the sampling delay should be taken into account in the design. Two PI-controllers were sufficient for providing a stable system. Control performance was significantly affected by the dynamic resistance. The control was much slower when the operation point was in the constant voltage region. The dynamic resistance had no effect on the system output impedance. More research is needed in order to determine the feasibility of the proposed control, for which this thesis gives a good foundation.

## PREFACE

This Master of Science thesis was made for the Department of Electrical Engineering at Tampere University of Technology. The examiner of the thesis was Professor Teuvo Suntio.

I would like to thank Prof. Teuvo Suntio for providing me with an interesting research topic, and also for his effort in revising this work. I would also like to thank M.Sc. Juha Jokipii for his help with the converter model and especially M.Sc. Jukka Viinamäki, who operated as my mentor during this process and helped me in pretty much every step of the way. A special acknowledgement belongs to my parents for their support.

Tampere 16.09.2014

Mikko Niku

# CONTENTS

| 1. | Introducti                                           | on                                                                                                                       | 1 |  |

|----|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|---|--|

| 2. | Boost-Pov                                            | ver-Stage Converter                                                                                                      | 3 |  |

|    | 2.1 Basic                                            | c Operation $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                             | 4 |  |

|    | 2.2 Dyna                                             | amic Modelling                                                                                                           | 6 |  |

|    | 2.2.1                                                | Photovoltaic Generator Effect                                                                                            | 2 |  |

|    | 2.3 Simu                                             | lation Model of The Open-loop System 1'                                                                                  | 7 |  |

| 3. | Converter                                            | Design                                                                                                                   | 1 |  |

|    | 3.1 Max                                              | imum Input Current                                                                                                       | 1 |  |

|    | 3.2 Indu                                             | $ tor Design \ldots 22 $      | 2 |  |

|    | 3.3 Selec                                            | tion of Switching Component and Diode                                                                                    | 6 |  |

|    | 3.4 Selec                                            | tion of Input and Output Capacitors                                                                                      | 0 |  |

| 4. | Control D                                            | esign $\ldots \ldots 33$             | 3 |  |

|    | 4.1 Cont                                             | rol Theory                                                                                                               | 3 |  |

|    | 4.2 Indu                                             | ctor-Current Control                                                                                                     | 5 |  |

|    | 4.3 Case                                             | ade Control                                                                                                              | 0 |  |

| 5. | Measurem                                             | $ents \dots \dots$ | 4 |  |

|    | 5.1 Prote                                            | otype Converter $\ldots \ldots 44$                 | 4 |  |

|    | 5.2 Meas                                             | surement Results                                                                                                         | 4 |  |

| 6. | Conclusion                                           | ns $\ldots \ldots 43$         | 9 |  |

| Re | eferences .                                          |                                                                                                                          | 0 |  |

| А. | A. Appendix $\ldots$ $\ldots$ $\ldots$ $\ldots$ $54$ |                                                                                                                          |   |  |

| В. | Schematic                                            | s of The Prototype Converter                                                                                             | 7 |  |

# **TERMS AND SYMBOLS**

### NOTATION

| $\mathbf{A}$      | System matrix                                                       |

|-------------------|---------------------------------------------------------------------|

| $A_c$             | Cross-sectional area of the core                                    |

| $A_L$             | Inductance per turn                                                 |

| $A_w$             | Cross-sectional area of the wire                                    |

| $\alpha$          | Material constant of the core                                       |

| a                 | Diode ideality factor                                               |

| В                 | Input matrix                                                        |

| $B_{max}$         | Maximum flux density                                                |

| $B_{sat}$         | Saturation flux density of the core                                 |

| $\beta$           | Material constant of the core                                       |

| $\mathbf{C}$      | Output matrix                                                       |

| C                 | Capacitance                                                         |

| $\Delta$          | Characteristic polynomial                                           |

| $\Delta i_{L,pp}$ | Inductor current peak-to-peak ripple                                |

| D                 | Input-output matrix                                                 |

| d                 | Duty ratio                                                          |

| d'                | Complement of duty ratio                                            |

| D                 | Steady-state value of duty ratio                                    |

| $f_r$             | Resonant frequency                                                  |

| $f_s$             | Switching frequency                                                 |

| G                 | Solar irradiance                                                    |

| $\mathbf{G}$      | Converter transfer function matrix                                  |

| g                 | Core air gap length                                                 |

| $\gamma$          | Auxiliary variable                                                  |

| $G_a$             | Modulator gain                                                      |

| $G_{cc-L}$        | Inductor-current controller transfer function                       |

| $G_{ci-c}$        | Closed current-loop control-to-input transfer function              |

| $G^S_{ci-c}$      | Source-affected closed current-loop control-to-input transfer func- |

|                   | tion                                                                |

| $G_{ci-cc}$       | Closed voltage-loop control-to-input transfer function              |

| $G^S_{ci-cc}$     | Source-affected closed voltage-loop control-to-input transfer func- |

|                   | tion                                                                |

| $G_{ci-o}$        | Open-loop control-to-input transfer function                        |

| $G^S_{ci-o}$      | Source-affected open-loop control-to-input transfer function        |

| $G_{cL-o}$        | Control-to-inductor-current transfer function                       |

|                   |                                                                     |

| $G^S_{cL-o}$     | Source-affected control-to-inductor-current transfer function |

|------------------|---------------------------------------------------------------|

| $G_{co-c}$       | Closed current-loop control-to-output transfer function       |

| $G_{co-cc}$      | Closed voltage-loop control-to-output transfer function       |

| $G_{co-o}$       | Open-loop control-to-output transfer function                 |

| $G^S_{co-o}$     | Source-affected open-loop control-to-output transfer function |

| $G_{cv}$         | Input-voltage controller transfer function                    |

| $G_{iL-o}$       | Input-to-inductor-current transfer function                   |

| $G^S_{iL-o}$     | Source-affected input-to-inductor-current transfer function   |

| $G_{io-c}$       | Closed current-loop input-to-output transfer function         |

| $G_{io-cc}$      | Closed voltage-loop input-to-output transfer function         |

| $G_{io-o}$       | Open-loop input-to-output transfer function                   |

| $G^S_{io-o}$     | Source-affected open-loop input-to-output transfer function   |

| $G_n$            | Solar irradiance in standard test condition                   |

| $G_{oL-o}$       | Output-to-inductor-current transfer function                  |

| $G^S_{oL-o}$     | Source-affected output-to-inductor-current transfer function  |

| $G_{se-in}$      | Voltage sensing transfer function                             |

| $i_0$            | Saturation current                                            |

| $i_{0,n}$        | Nominal saturation current                                    |

| $I_{ m d,rms}$   | Root mean square of diode current                             |

| $I_e$            | Magnetic path length of the core                              |

| $i_{in}$         | Converter input current                                       |

| $I_L$            | Steady-state value of inductor-current                        |

| $I_{max}$        | Converter maximum peak input current                          |

| $i_o$            | Converter output current                                      |

| $i_{ph}$         | Photocurrent                                                  |

| $i_{ph,n}$       | Photocurrent in standard test condition                       |

| $i_{sc,n}$       | Short circuit current in standard test condition              |

| $I_{\rm SC,MAX}$ | Maximum short circuit current                                 |

| $I_{\rm sw,rms}$ | Root mean square of switch current                            |

| Ι                | Identity matrix                                               |

| K                | Current controller gain                                       |

| $K_v$            | Voltage controller gain                                       |

| $K_I$            | Temperature coefficient                                       |

| $K_g$            | Geometrical constant of the core                              |

| $K_u$            | Winding fill factor                                           |

| k                | Boltzmann constant                                            |

| $K_m$            | Material constant of the core                                 |

| $K_c$            | Auxiliary variable                                            |

| $K_{cv}$         | Auxiliary variable                                            |

|                  |                                                               |

| L                | Inductance                                               |

|------------------|----------------------------------------------------------|

| $L_c$            | Current loop gain                                        |

| $L_c^S$          | Source-affected current loop gain                        |

| $L_{cv}$         | Voltage loop gain                                        |

| $L_s$            | Equivalent series inductance                             |

| M                | Input to output modulo                                   |

| $\mu_e$          | Effective permeability of the core                       |

| $N_s$            | Number of series connected cells                         |

| N                | Number of turns                                          |

| $\omega_p$       | Angular frequency of current controller pole             |

| $\omega_{p1}$    | Angular frequency of voltage controller pole             |

| $\omega_z$       | Angular frequency of current controller zero             |

| $\omega_{z1}$    | Angular frequency of voltage controller zero             |

| $P_{\rm d,cond}$ | Conduction power loss of the diode                       |

| $P_{\rm d,rev}$  | Reverse leakage current power loss of the diode          |

| $P_{ m d,tot}$   | Total power loss of the diode                            |

| $P_{fe}$         | Time average core loss per unit volume                   |

| $P_{\rm sw}$     | Average switching power loss                             |

| $P_{\rm sw,c}$   | Switch conduction loss                                   |

| $P_{\rm sw,tot}$ | Total power loss of the switch                           |

| q                | Electron charge                                          |

| $r_{pv}$         | Dynamic resistance of a photovoltaic generator           |

| $R_{sL}$         | Current sensing transfer function                        |

| S                | Laplace variable                                         |

| $T_{amb}$        | Ambient temperature                                      |

| $T_{oi-c}$       | Closed current-loop reverse voltage transfer ratio       |

| $T_{oi-cc}$      | Closed voltage-loop reverse voltage transfer ratio       |

| $T_{oi-o}$       | Open-loop reverse voltage transfer ratio                 |

| $T^S_{oi-o}$     | Source-affected open-loop reverse voltage transfer ratio |

| $T_s$            | Switching period                                         |

| $u_{oc,n}$       | Open-circuit voltage in standard test condition          |

| $V_e$            | Effective magnetic volume of the core                    |

| $W_A$            | Window area of the core                                  |

| $W_{c(on)}$      | Switch turn-on energy loss                               |

| $\hat{x}$        | AC-perturbation around a steady-state operation point    |

| $Y_{o-c}$        | Closed current-loop output admittance                    |

| $Y_{o-cc}$       | Closed voltage-loop output admittance                    |

| $Y^S_{o-cc}$     | Source-affected closed voltage-loop output admittance    |

| $Y_{o-o}$        | Open-loop output admittance                              |

|                  |                                                          |

| $Y^S_{o-o}$     | Source-affected output admittance                    |

|-----------------|------------------------------------------------------|

| $Y_{o-\infty}$  | Ideal output admittance                              |

| $Y_s$           | Output admittance of a non-ideal source              |

| $Z_{in-c}$      | Closed current-loop input impedance                  |

| $Z_{in-cc}$     | Closed voltage-loop input impedance                  |

| $Z_{in-o}$      | Open-loop input impedance                            |

| $Z^S_{in-o}$    | Source-affected input impedance                      |

| $Z_{in-oco}$    | Open circuit input impedance                         |

| $Z_{in-\infty}$ | Ideal input impedance                                |

| $Z^S_{o-cc}$    | Source-affected closed voltage-loop output impedance |

| $Z_o$           | Open-loop output impedance                           |

| $Z_s$           | Output impedance of a non-ideal source               |

## ABBREVIATIONS

| AM     | Air mass                                |

|--------|-----------------------------------------|

| CC     | Constant current                        |

| CCM    | Continuous current conduction           |

| CF-CO  | Current-fed current output              |

| $CO_2$ | Carbon dioxide                          |

| CV     | Constant voltage                        |

| DC     | Direct current                          |

| DCM    | Discontinuous current conduction        |

| DDR    | Direct duty-ratio                       |

| DSP    | Digital signal processor                |

| ESL    | Equivalent series inductance            |

| ESR    | Equivalent series resistance            |

| I - V  | Current to voltage                      |

| LHP    | Left half-plane                         |

| MLT    | Mean length per turn                    |

| MPP    | Maximum power point                     |

| MPPT   | Maximum power point tracking or tracker |

| PV     | Photovoltaic                            |

| PVG    | Photovoltaic generator                  |

| PWM    | Pulse width modulation                  |

| RHP    | Right half-plane                        |

| RMS    | Root-mean-square                        |

| SAS    | Solar array simulator                   |

| SF     | Sizing factor                           |

| STC    | Standard test conditions                |

## 1. INTRODUCTION

The world's energy consumption has skyrocketed after the years of industrial revolution. The energy need has increased because of growing population and higher standard of living. The current trend is that the energy demand is only going up. Globally in 2010, around 87% of the consumed energy was produced with fossil fuels i.e. coal (28%), natural gas (21%) and oil (38%). 6% came from nuclear plants and the remaining 7% came from renewable energy sources, such as hydro, wind, solar, geothermal and biofuels. The problem is, however, that the burning of fossil fuels generates pollutant gases, notably  $CO_2$ , which is the main contributor to greenhouse effect i.e. global warming. Another problem is, that the reserve of fossil fuels is limited, and it is estimated that e.g. oil would run out in 50 to 100 years. The global warming has serious effect on the world's ecological structure in the long run, such as severe droughts near the equator and the rise in sea level, which would ultimately drive 100 million people away from their homes. The need for renewable and clean energy is real, which is why many governments have started to invest on them, and new laws are legislated in order to cut down emissions. [1]

Recent studies have shown that all of the world's energy demand could be produced with renewable energy sources, assuming that there is an adequate storage for it. One of the alternatives is the solar or photovoltaic (PV) energy. The pros of solar energy are that it is abundantly available and the cost of PV panels, which convert the solar insolation directly into electricity, is decreasing due to intense development of these devices. However, the availability of solar energy is intermittent in nature, and therefore it needs a back-up support. All of these energy management issues can be handled with power electronics, which means that the design of reliable and efficient power electronic systems are of prime importance in fullfilling the recognized needs and to secure the availability of energy in the future. [1]

In grid connected or energy storaging PV power systems, the PV generator (PVG) is usually interfaced with a dc-dc boost-power-stage converter with an added input-capacitor [2][3]. The converter is operated under input-voltage control, which changes the converter to be a current-fed converter [4]. The reference value for input-voltage control is obtained from a maximum power point (MPP) tracker to ensure maximum energy yield at all times. The operation of the converter and its control is affected by the operation point dependent output-impedance of the PVG,

#### 1. Introduction

which is referred to as a *dynamic resistance* in literature. The variance of dynamic resistance between operation points results in a variable damping factor in the boost converter duty cycle to input-voltage transfer function, but the system can be easily controlled with a simple I-controller. [5]

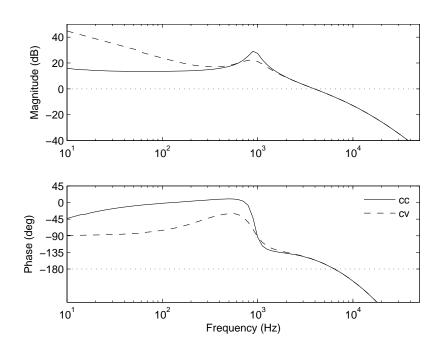

However, the performance of an input-voltage control is limited due to the resonance between the inductor and input-capacitor, thus resulting in a slow operation point tracking or ringing. Therefore, in order to improve the operation point tracking, reject the effect of abrupt irradiance variations, and eliminate the effect of dynamic resistance on control in a PVG interfacing converter, several new control methods have been proposed all based on a cascaded inner current and outer voltage control [6] [7] [8].

In this thesis, a simple cascade controlled boost-power-stage converter was designed for low power PVG application. The control consisted of an inner inductorcurrent control, which got its set-value from an outer input-voltage controller, thus forming a cascade. The objective of this thesis was to design a working device in its simplest form, obtain a correct method for modelling the dynamics associated with the system, as well as, to evaluate the effect of the dynamic resistance on closedloop dynamics. A prototype converter was built and measured in order to verify the theoretical model and to present the performance of the designed control.

The rest of the thesis is organized as follows: Chapter 2 presents how the dynamics of the converter are modelled, and how the effect of the dynamic resistance can be included into it. In Chapter 3 the converter components are selected and their corresponding dynamic model values are determined. In Chapter 4 the control system is designed, and in Chapter 5 the measurements of the prototype converter built for this thesis are presented. It should be noted, that the control was designed without taking the sampling delay into account. The effect of sampling delay has been discussed in Chapter 5 "Measurements". The final chapter summarizes the most important results of this study.

## 2. BOOST-POWER-STAGE CONVERTER

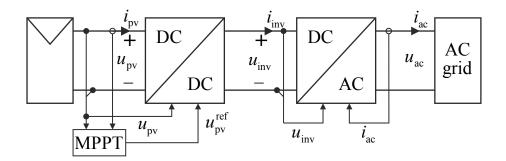

The interfacing of photovoltaic generators (PVGs) into a downstream power system is usually done by utilizing power electronic converters. The interfacing scheme depends on the nature of the load. If the load is a dc battery, a dc-dc converter is applied, and if the load is an ac grid a dc-ac converter i.e. *an inverter* is needed. The ac grid interfacing can be divided further into two schemes: a single-stage and a double-stage conversion schemes. In the single-stage conversion scheme, the inverter input is directly connected to the PVG, and the ac side is feeding the grid. In the double-stage conversion scheme, there is a dc-dc converter between the PVG and the inverter (see Fig. 2.1). [9] [10, p. 5-6]

Figure 2.1. The principle of a double-stage conversion scheme used in the gridconnected PV systems. [11]

Typically the converter topology used in a double-stage conversion scheme is a conventional boosting converter with an added input-capacitor [2][3]. Due to its voltage boosting property there can be less series connected photovoltaic (PV) cells or modules, which can be also beneficial in partial shading conditions [12]. The other advantages are that the topology includes an output-diode, which prevents current from flowing into the PVG at times of low irradiation, and the converter has continuous input-current, which reduces the size of the input-capacitor [2].

A PVG interfacing converter should control its input-current or input-voltage for setting the desired operation point. The desired operation point is usually the maximum power point (MPP) on the PVG's current to voltage (I-V) curve (see Fig. 2.7). A MPP-tracker (MPPT) is a general name to a piece of equipment that is allocated for tracking the MPP. The MPPT measures the PVG's output-current and output-

voltage, which are used to determine the MPP, and provides a duty-cycle or, as in Fig. 2.1, a set-value for the input-voltage controller of the dc-dc converter. The MPPT ensures that maximal power is transferred into the downstream system. [13]

Controlling the input-voltage of a PVG interfacing converter has advantages over the input-current control. The PV current is directly proportional to solar irradiation, which can change rapidly and in large scale. This means that the input-current control needs to be extremely fast in order to accurately follow the desired operation point, and if this is not the case, the control can easily saturate. The photovoltaic voltage on the other hand is only slightly affected by the insolation. The most significant factor affecting the photovoltaic voltage is the temperature, which has slow dynamics. This means that the preferred control variable is the PV voltage, and thus it has been conventionally used in a PVG interfacing converters. [2][13]

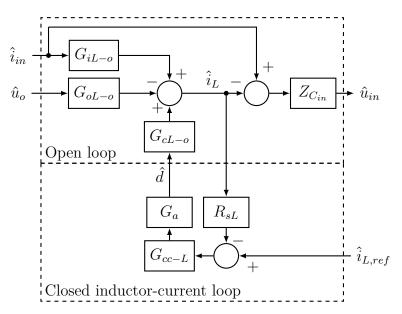

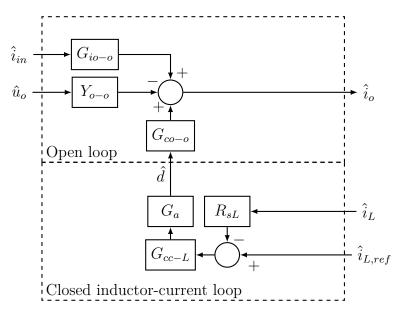

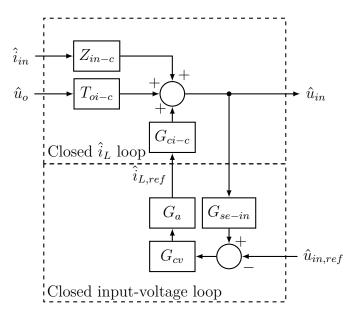

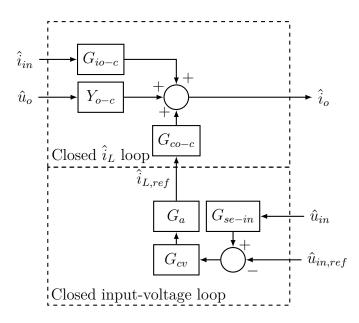

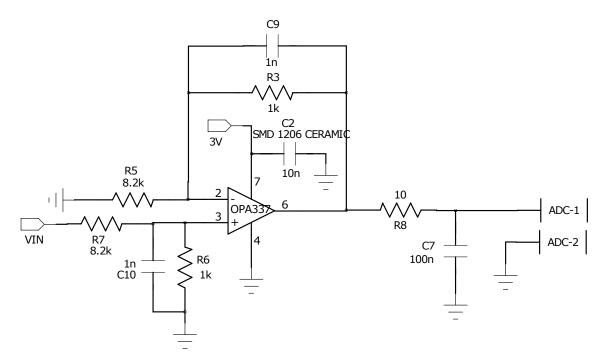

In this thesis, the control system designed for the boost converter is a cascaded inductor-current and input-voltage control. The current controller gets its set-value from the voltage controller, thus the current loop is inside the voltage loop. In this type of control, the outer control loop is the primary control loop, since the control is based on its reference value. This means that the input-voltage is effectively controlled.

According to general control engineering principles, the output variables are controllable and the input variables are uncontrollable. This means, that in order to control the input-voltage, which is usually adopted in the PVG interfacing converters, the input-voltage must be an output-variable i.e. a current-fed converter [3] [4]. Furthermore, the converter designed in this thesis is thought to be an a PVG interfacing converter feeding an input-voltage controlled inverter or a battery load. Dynamically these loads are seen approximately as a constant voltage loads. Based on the information presented in preceding paragraphs the converter designed here should be considered as a current-fed current output (CF-CO) converter.

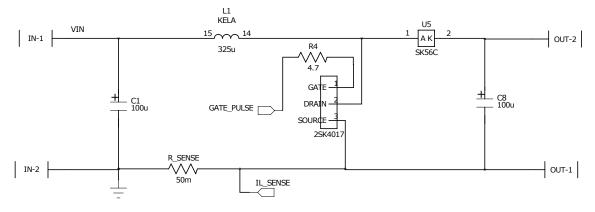

### 2.1 Basic Operation

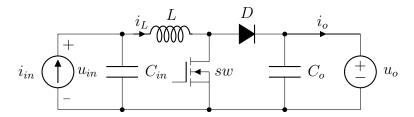

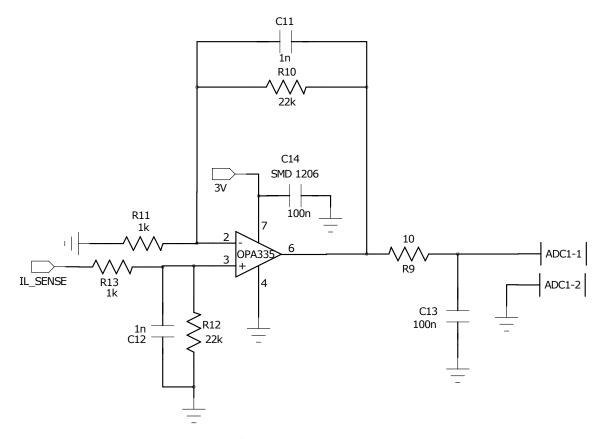

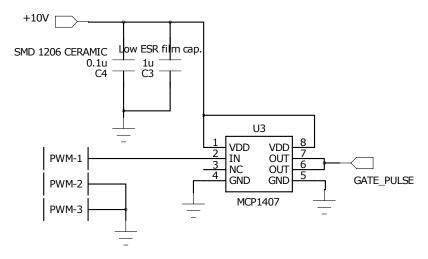

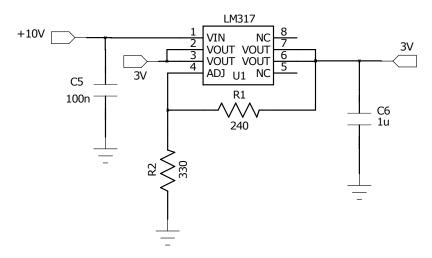

The main circuit of a boost-power-stage converter with an added input-capacitor is presented in Fig. 2.2, which is also the circuit configuration used for the boost converter designed in this thesis. It should be noted, that the load side inductorcurrent sensing resistor (see Fig. B.1) is omitted from this figure, since it does not affect the dynamics of the converter and introduces only more losses, at least in theory. The value of this resistor was added to the dc-resistance of the inductor in the converter model. A current-source at the input and a voltage-source load refer to a current-fed current out (CF-CO) type converter, which is discussed more closely in the next section.

A boost converter produces a dc output-voltage greater in magnitude than the

Figure 2.2. Main circuit of a boost-power-stage converter with an added inputcapacitor.

dc input-voltage. This is possible because of the inductor stored energy. When the switch "sw" is closed and conducting current (on-time), the input-voltage appears across the inductor, current through it raises and energy is stored in the magnetic field of the inductor. When the switch is open and not conducting (off-time), the inductor-voltage switches polarity and the output-diode becomes forward biased. Both the energy stored in the magnetic field of the inductor, and the energy from the input source flows through the diode to the output in the form of electrical current. During this period the inductor current falls. On-time and off-time periods form one switching cycle, and by changing the length of these periods (i.e. changing duty-cycle D), one can affect the magnitude of the output-voltage.

Mathematically this can be represented by using an inductor volt-second balance concept i.e. the average inductor-voltage over one time-period must be zero:

$$\int_{0}^{DT_{s}} u_{L_{on}} dt + \int_{DT_{s}}^{T_{s}} u_{L_{o}ff} dt = 0 \Leftrightarrow$$

$$\int_{0}^{DT_{s}} U_{in} dt + \int_{DT_{s}}^{T_{s}} U_{in} - U_{o} dt = 0 \Leftrightarrow$$

$$M(D) = \frac{U_{o}}{U_{in}} = \frac{1}{1 - D},$$

(2.1)

which applies when the voltage-ripples at the input and output are considered negligible, components are ideal, and the converter is at steady state. The input-tooutput modulo M(D) is always one or higher, meaning that the output-voltage is equal to the input-voltage or higher, respectively. Furthermore, assuming an ideal converter, the input power equals the output power. This means, that a dc-dc converter operates as a dc-dc transformer. [14, p. 22-27]

A steady-state condition is reached when the circuit waveforms repeat with a certain time period. In the case of switched-mode converters the time period is one switching cycle  $(T_s = \frac{1}{f_s})$ . After some time during start up, a switched-mode converter reaches a steady-state condition. When the inductor-current is flowing in positive direction (see Fig.2.2) changing around some average value as the on-time and off-time alternates, and never reaching zero, the converter is in continuous

current conduction mode (CCM).

The inductor-current peak-to-peak ripple in CCM can be calculated simply by using the inductor voltage-to-current relation:

$$u_L(t) = L \frac{di_L(t)}{dt} \approx L \frac{\Delta i_{L,pp}}{\Delta t} \Leftrightarrow \Delta i_{L,pp} = \frac{DT_s U_{in}}{L}, \qquad (2.2)$$

where  $\Delta i_{L,pp}$  is the inductor-current peak-to-peak ripple,  $\Delta t = DT_s$  is the on-time time interval and  $u_L = U_{in}$  is the inductor-voltage during on-time. In the same way, an analysis for the input- and output-voltage ripple could be done, and the results would show that the amount of ripple present depends on the capacitance of the respective capacitor. The input-voltage and inductor-current ripples need to be considered when designing the inductor-current and input-voltage measurement circuits, and their respective controllers. Moreover, the input-voltage ripple affects the operation point of the PV generator, which then again affects the energy yield.

It should be noted, that the dynamic analysis, which will be presented next, is valid only for CCM. In discontinuous current conduction mode (DCM), there is a third time-interval where the inductor-current is zero, which changes the dynamic behaviour of the converter substantially. [15]

### 2.2 Dynamic Modelling

The state-space averaging technique, first presented in [16], is the standard modelling technique for dc-dc converters. The same basic principles can be applied for modelling other power electronic converters also. The procedure yields in this case a linear small-signal model of a dc-dc converter, linearized around a steady-state operating point. Then the state-space model is Laplace-transformed to s-domain (i.e. frequency domain) yielding all transfer functions representing the system. At open-loop, a dc-dc converter operates as a dc-dc transformer having its dynamic properties determined by the source and the load.

In [5], the modelling of a CF-CO boost-power-stage converter with an inputcapacitor is done by using a structured approach. The main circuit of a converter (same as in Fig. 2.2) is divided into two different subunits, which are modelled separately and then unified. The first part is the LC input-filter circuit, and another is PWM switching shunt unit. This method was implemented in the study, because it clearly shows that the LC-circuit is the source of two RHP-zeros appearing in the output dynamics of the converter. In this thesis, the whole circuit is modelled as a one unit.

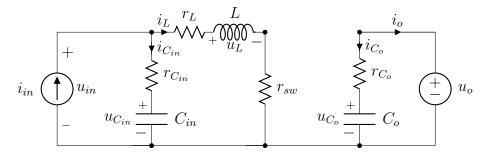

The basis of the state-space averaging technique is to define the different states in which the converter can be. In the case of a dc-dc converter in CCM there are two states: the on-time, and the off-time states. During on-time in steady-state the output circuit is isolated from the input, because the output-voltage is higher than the input-voltage. The on-time subcircuit of a boost-power-stage converter is presented in Fig. 2.3.

Figure 2.3. An on-time subcircuit of a boost-power-stage converter with an input capacitor.

In Fig. 2.3, the  $r_L$  represents both the equivalent series resistance (ESR) of the inductor and the value of the inductor-current sensing resistor. The inductor-current sensing resistor is discussed more in the converter design chapter.  $r_{sw}$  is the resistance of the switching component and  $r_{C_{in}}$ ,  $r_{C_o}$  are the ESRs of the input and output capacitors, respectively. These values are usually found in the component datasheets fairly easily. Depending on the components, and the amount of measurement data given in their datasheets, one can build a fairly accurate model by using this level of accuracy in the converter model. However, in practice the parameters change from component to component (tolerance), so for the best accuracy one should measure the specific components, which are used to build the actual device on a printed circuit board.

Applying Kirchhoff's laws to the circuit in Fig. 2.3 and rearranging yields:

$$u_{L,on} = i_{in} r_{C_{in}} + u_{C_{in}} - i_L (r_L + r_{C_{in}} + r_{sw})$$

$$i_{C_{in,on}} = i_{in} - i_L$$

$$i_{C_o,on} = \frac{u_o - u_{C_o}}{r_{C_o}}$$

$$u_{in,on} = r_{C_{in}} (i_{in} - i_L) + u_{C_{in}}$$

$$i_{o,on} = \frac{u_{C_o} - u_o}{r_{C_o}}.$$

(2.3)

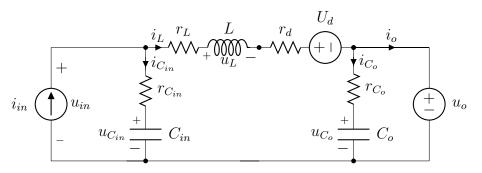

The off-time subcircuit is presented in Fig. 2.4. Inductor-voltage switches polarity at the same exact moment when the switch is turned off, and the sum of inputvoltage and inductor-voltage is momentarily higher than the output-voltage. Now, because the switching component does not conduct current, the current has to flow through the diode.

Applying Kirchhoff's laws to the circuit in Fig. 2.4 and rearranging yields:

Figure 2.4. An off-time subcircuit of a boost-power-stage converter with an input capacitor.

$$u_{L,off} = i_{in} r_{C_{in}} + u_{C_{in}} - i_L (r_L + r_{C_{in}} + r_d) - U_d - u_o$$

$$i_{C_{in,off}} = i_{in} - i_L$$

$$i_{C_o,off} = \frac{u_o - u_{C_o}}{r_{C_o}}$$

$$u_{in,off} = r_{C_{in}} (i_{in} - i_L) + u_{C_{in}}$$

$$i_{o,off} = i_L + \frac{u_{C_o} - u_o}{r_{C_o}},$$

(2.4)

where  $r_d$  is the parasitic resistance of the diode and  $U_d$  is the voltage drop across it.

The next step is to average the on-time equations in Eq. 2.3 and the off-time equations in Eq. 2.4 over one switching cycle using duty-ratio (d) and complementary duty-ratio (d'), and recognizing that d + d' = 1. This yields the averaged state-space representation:

$$\frac{d\langle i_L \rangle}{dt} = \frac{1}{L} (du_{L,on} + d'u_{L,off})

= -\frac{(r_{C_{in}} + r_L + dr_{sw} + d'r_d)}{L} \langle i_L \rangle + \frac{\langle u_{C_{in}} \rangle}{L} + \frac{r_{C_{in}}}{L} \langle i_{in} \rangle - \frac{d'(\langle u_o \rangle - U_d)}{L}

\frac{d\langle u_{C_{in}} \rangle}{dt} = \frac{1}{C_{in}} (di_{C_{in},on} + d'i_{C_{in},off})

= \frac{\langle i_{in} \rangle - \langle i_L \rangle}{C_{in}}

\frac{d\langle u_{C_o} \rangle}{dt} = \frac{1}{C_o} (di_{C_o,on} + d'i_{C_o,off})

= \frac{\langle u_o \rangle - \langle u_{C_o} \rangle}{C_o r_{C_o}}

\langle u_{in} \rangle = du_{in,on} + d'u_{in,off}

= r_{C_{in}} (\langle i_{in} \rangle - \langle i_L \rangle) + \langle u_{C_{in}} \rangle

\langle i_o \rangle = di_{o,on} + d'i_{o,off}

= \frac{\langle u_{C_o} \rangle - \langle u_o \rangle}{r_{C_o}} + d' \langle i_L \rangle.$$

(2.5)

The steady-state operating point can be solved from averaged state-space Eq. 2.5 by recognizing that the derivatives of the average values are zero in steady-state and replacing average values with the corresponding steady-state values. This procedure and rearranging gives:

$$U_{in} = D'U_{o} + (r_{L} + Dr_{sw} + D'r_{d})I_{in} + D'U_{d}$$

$$D' = \frac{U_{in} - (r_{L} + r_{sw})I_{in}}{U_{o} + U_{d} + (r_{d} + r_{sw})I_{in}}$$

$$I_{L} = I_{in}$$

$$U_{o} = U_{C_{o}}$$

$$U_{in} = U_{C_{in}}$$

$$I_{o} = D'I_{L}.$$

(2.6)

The final small-signal model for the converter can be found when the average state-space model in Eq. 2.5 is linearized at a desired operation point by developing partial derivatives for every variable (i.e. average value). Mathematically this can be presented e.g. for variable  $x_1$ :

$$\frac{\partial f(x_1, x_2 = X_2, \dots, x_n = X_n)}{\partial x_1} \bigg|_{x_1 = X_1} \cdot \hat{x}_1,$$

(2.7)

which means verbally that variable  $x_1$  is first differentiated with itself, and the other variables are replaced with their corresponding steady-state values. Then

variables of  $x_1$  are replaced with steady-state values, and finally the whole equation is multiplied with small signal variable  $\hat{x}_1$ .

Linearizing of the averaged state-space representation yields the following:

$$\frac{d\hat{i}_{L}}{dt} = -\frac{R_{eq}}{L}\hat{i}_{L} + \frac{1}{L}\hat{u}_{C_{in}} + \frac{r_{C_{in}}}{L}\hat{i}_{in} - \frac{D'}{L}\hat{u}_{o} + \frac{U_{eq}}{L}\hat{d}$$

$$\frac{d\hat{u}_{C_{in}}}{dt} = \frac{\hat{i}_{in} - \hat{i}_{L}}{C_{in}}$$

$$\frac{d\hat{u}_{C_{o}}}{dt} = \frac{\hat{u}_{o} - \hat{u}_{C_{o}}}{C_{o}r_{C_{o}}}$$

$$\hat{u}_{in} = r_{C_{in}}(\hat{i}_{in} - \hat{i}_{L}) + \hat{u}_{C_{in}}$$

$$\hat{i}_{o} = \frac{\hat{u}_{C_{o}} - \hat{u}_{o}}{r_{C_{o}}} + D'\hat{i}_{L} - I_{in}\hat{d},$$

(2.8)

where

$$R_{eq} = r_{C_{in}} + r_L + Dr_{sw} + D'r_d$$

$$U_{eq} = (r_d - r_{sw})I_{in} + U_o + U_d.$$

(2.9)

The linearized state-space representation in Eqs: 2.8 and 2.9 can also be presented in matrix form:

$$\begin{bmatrix} \frac{\hat{d}_{L}}{dt} \\ \frac{d\hat{u}_{C_{in}}}{dt} \\ \frac{d\hat{u}_{C_{o}}}{dt} \end{bmatrix} = \begin{bmatrix} -\frac{R_{eq}}{L} & \frac{1}{L} & 0 \\ -\frac{1}{C_{in}} & 0 & 0 \\ 0 & 0 & -\frac{1}{C_{o}r_{C_{o}}} \end{bmatrix} \begin{bmatrix} \hat{i}_{L} \\ \hat{u}_{C_{in}} \\ \hat{u}_{C_{o}} \end{bmatrix} + \begin{bmatrix} \frac{r_{C_{in}}}{L} & -\frac{D'}{L} & \frac{U_{eq}}{L} \\ \frac{1}{C_{in}} & 0 & 0 \\ 0 & \frac{1}{C_{o}r_{C_{o}}} & 0 \end{bmatrix} \begin{bmatrix} \hat{i}_{in} \\ \hat{u}_{o} \\ \hat{d} \end{bmatrix}$$

(2.10)

$$\begin{bmatrix} \hat{u}_{in} \\ \hat{i}_{o} \end{bmatrix} = \begin{bmatrix} -r_{C_{in}} & 1 & 0 \\ D' & 0 & \frac{1}{r_{C_o}} \end{bmatrix} \begin{bmatrix} \hat{i}_L \\ \hat{u}_{C_{in}} \\ \hat{u}_{C_o} \end{bmatrix} + \begin{bmatrix} r_{C_{in}} & 0 & 0 \\ 0 & -\frac{1}{r_{C_o}} & -I_{in} \end{bmatrix} \begin{bmatrix} \hat{i}_{in} \\ \hat{u}_o \\ \hat{d} \end{bmatrix},$$

(2.11)

which can be then again presented as follows:

$$\frac{d\hat{\mathbf{x}}(t)}{dt} = \mathbf{A}\hat{\mathbf{x}}(t) + \mathbf{B}\hat{\mathbf{u}}(t)$$

$$\hat{\mathbf{y}}(t) = \mathbf{C}\hat{\mathbf{x}}(t) + \mathbf{D}\hat{\mathbf{u}}(t).$$

(2.12)

One should now see that the column vectors:  $\hat{\mathbf{x}}(t) = \begin{bmatrix} \hat{i}_L & \hat{u}_{C_{in}} & \hat{u}_{C_o} \end{bmatrix}^\top$ ,  $\hat{\mathbf{u}}(t) = \begin{bmatrix} \hat{i}_{in} & \hat{u}_o & \hat{d} \end{bmatrix}^\top$  and  $\hat{\mathbf{y}}(t) = \begin{bmatrix} \hat{u}_{in} & \hat{i}_o \end{bmatrix}^\top$  consists of state variables, input variables, and output variables, respectively. The Laplace transformations of equations in (2.12) are:

$$\mathbf{sX}(s) = \mathbf{AX}(s) + \mathbf{BU}(s)$$

$$\mathbf{Y}(s) = \mathbf{CX}(s) + \mathbf{DU}(s).$$

(2.13)

Now by using common matrix manipulation techniques the input-to-output trans-

fer functions can be solved. First the upper equation in (2.13) is solved for  $\mathbf{X}(s)$ yielding transfer functions for input-to-state variables:  $\mathbf{X}(s) = [s\mathbf{I} - \mathbf{A}]^{-1}\mathbf{B}\mathbf{U}(s)$ , which is then substituted to the lower equation. The result is:

$$\mathbf{Y}(s) = [\mathbf{C}[s\mathbf{I} - \mathbf{A}]^{-1}\mathbf{B} + \mathbf{D}]\mathbf{U}(s) = \mathbf{G}(s)\mathbf{U}(s), \qquad (2.14)$$

where

$$\mathbf{G}(s) = \begin{bmatrix} Z_{in-o} & T_{oi-o} & G_{ci-o} \\ G_{io-o} & -Y_{o-o} & G_{co-o} \end{bmatrix}$$

(2.15)

contains every transfer function describing the system from input to output variables.

The final solution can be given in form:

$$\begin{bmatrix} \hat{u}_{in} \\ \hat{i}_{o} \end{bmatrix} = \begin{bmatrix} Z_{in-o} & T_{oi-o} & G_{ci-o} \\ G_{io-o} & -Y_{o-o} & G_{co-o} \end{bmatrix} \begin{bmatrix} \hat{i}_{in} \\ \hat{u}_{o} \\ \hat{d} \end{bmatrix}.$$

(2.16)

The symbolic solutions for the open-loop transfer functions are:

$$\Delta Z_{in-o} = \frac{1}{LC_{in}} (R_{eq} - r_{C_{in}} + sL)(1 + sr_{C_{in}}C_{in})$$

$$\Delta T_{oi-o} = \frac{D'}{LC_{in}} (1 + sr_{C_{in}}C_{in})$$

$$\Delta G_{ci-o} = \frac{-U_{eq}}{LC_{in}} (1 + sr_{C_{in}}C_{in})$$

$$\Delta G_{io-o} = \frac{D'}{LC_{in}} (1 + sr_{C_{in}}C_{in})$$

$$Y_{o-o} = \frac{D'}{L} \frac{s}{\Delta} + \frac{sC_o}{1 + sr_{C_o}C_o}$$

$$\Delta G_{co-o} = -I_{in} (s^2 - (\frac{D'U_{eq}}{LI_{in}} - \frac{R_{eq}}{L}) + \frac{1}{LC_{in}}),$$

(2.17)

where  $\Delta = s^2 + \frac{R_{eq}}{L}s + \frac{1}{LC_{in}}$  is the characteristic equation.

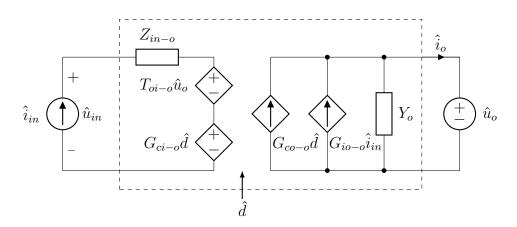

The dynamics of the converter can also be represented with a linear two-port model (Fig. 2.5) shown inside the dashed line. The linear model is another way of representing the Eq. 2.16, and gives physical insight of the operation of the converter. The minus sign in front of  $Y_{o-o}$  originates from the fact that the direction of the output-current is out of the converter.

As it was stated earlier, the converter uses a cascade controller, in which there is an inner inductor-current control loop. For designing the inductor-current controller, the transfer functions from input-variables to inductor-current are needed. These can be obtained by using the two uppermost equations in linearized state-space

Figure 2.5. Linear two-port model of a CF-CO dc-dc converter with ideal terminations.

representation (see 2.8). The equations are repeated here for convenience:

$$\frac{d\hat{i}_L}{dt} = -\frac{R_{eq}}{L}\hat{i}_L + \frac{1}{L}\hat{u}_{C_{in}} + \frac{r_{C_{in}}}{L}\hat{i}_{in} - \frac{D'}{L}\hat{u}_o + \frac{U_{eq}}{L}\hat{d}$$

$$\frac{d\hat{u}_{C_{in}}}{dt} = \frac{\hat{i}_{in} - \hat{i}_L}{C_{in}}.$$

Now by recognizing that the Laplace-transform for time-derivative is s, and substituting  $\hat{u}_{C_{in}}$  from the lower equation to the upper, the inductor current becomes:

$$\hat{i}_L = \underbrace{\frac{r_{C_{in}}s + \frac{1}{C_{in}}}{\Delta L}}_{G_{iL-o}} \hat{i}_{in} - \underbrace{\frac{D's}{\Delta L}}_{G_{oL-o}} \hat{u}_o + \underbrace{\frac{U_{eq}s}{\Delta L}}_{G_{cL-o}} \hat{d}, \qquad (2.18)$$

where  $\Delta = s^2 + \frac{R_{eq}}{L}s + \frac{1}{LC_{in}}$ , and the corresponding input-to-inductor-current transfer functions are underbraced and denoted. The most important transfer function considering the inductor-current controller design is the control-to-inductor-current transfer function  $G_{cL-o}$ , which shows how pulse-width affects the inductor-current.

### 2.2.1 Photovoltaic Generator Effect

A PV generator is a device, which directly converts sunlight into electricity. A basic unit in a PVG is a photovoltaic cell. A set of connected cells form a panel (or a PV module). Series connection of PV cells yield higher output voltage, and parallel connection yield larger output current. PV cells can be connected in any way inside a solar panel to achieve wanted electrical properties. Usually, however, there are mostly series connected cells since the voltage of a one cell is fairly small ( $\approx 0.7$ V). Series and/or parallel connection of solar cells and solar panels form solar arrays. PV generator is the general term used to describe these systems. [17]

A PV cell is basically a p-n junction exposed to sunlight. When there is no light, the p-n junction is in thermal equilibrium, where the currents of majority - and minority charge carries are equal. Irradiance of light (or insolation) on the cell disrupts this equilibrium, and if the cell is short-circuited an electrical current is produced. Depending on the loading of a PV generator i.e. the balance between accumulation and the flow of charge carries, the PV generator inflicts different electrical properties at its output. The accumulation of charge carries means a raise in voltage, and the flow of charge carries corresponds with a current increase, respectively. [18] [17]

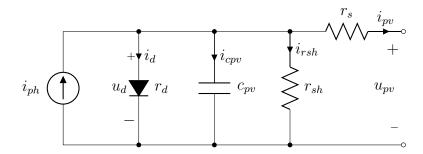

The electrical properties of a PV cell can be modelled with sufficient accuracy by using a one-diode model. This is presented in Fig. 2.6.

Figure 2.6. Simplified electrical equivalent circuit of a photovoltaic cell.

In Fig. 2.6  $i_{ph}$  is the photocurrent, which is directly proportional to irradiance,  $u_{pv}$ and  $i_{pv}$  are the output-terminal voltage and current respectively,  $i_{rsh}$  is the current through the shunt resistance  $r_{sh}$  and  $i_{cpv}$  is the current through shunt capacitance  $c_{pv}$ . The shunt resistance  $r_{sh}$  represents non-idealities in the p-n junction and impurities near the junction [18]. The series resistance  $r_s$  results from the bulk resistance of the semiconductor material, metallic contacts and their interconnections [18]. The diode symbol illustrates the electrical properties of a p-n junction. The one-diode model can be used for modelling PV modules i.e. series connection of PV cells, by scaling model parameters [17].

An equation, which mathematically describes the static I-V (current to voltage) characteristics of a PV module can be formulated as:

$$i_{pv} = i_{ph} - i_o \left[ \exp\left(\frac{u_{pv} + r_s}{N_s akT/q}\right) - 1 \right] - \frac{u_{pv} + r_s i_{pv}}{r_{sh}},$$

(2.19)

where  $N_s$  is the number of series connected cells, a is the diode ideality factor, k is the Bolzmann constant, T is the temperature of the p-n junction and q is the electron charge [17]. It should be noted, that this equation represents a static (DC) situation, so the capacitor in the one-diode model is an open circuit and does not contribute to this equation.

The saturation current  $i_0$  in Eq. 2.19 is:

$$i_0 = i_{0,n} \left(\frac{T_n}{T}\right)^3 \exp\left[\frac{qE_g}{ak} \left(\frac{1}{T_n} - \frac{1}{T}\right)\right],\tag{2.20}$$

where  $T_n$  is the temperature of the p-n junction in standard test conditions (STC), which is defined in next paragraph, T is the actual temperature,  $E_g$  is the bandgap energy of the semiconductor and  $i_{0,n}$  is the nominal saturation current, which can be expressed as:

$$i_{0,n} = \frac{i_{sc,n}}{\exp(u_{oc,n}q/N_s akT_n) - 1},$$

(2.21)

where  $i_{sc,n}$  is the short circuit current and  $u_{oc,n}$  is the open circuit voltage both in the STC.

The term "STC" refers to climate conditions, in which the solar irradiance G is  $1000\frac{W}{m^2}$ , the ambient temperature T is 298.15K, and Air mass is 1.5, which is usually abbreviated as AM1.5. The Air mass is the mass of air between a surface of the Earth and the Sun. The mass of air affects the spectral distribution of the light received by the PV device. The number after the abbreviation, as in AMx, indicates the length of the path the light travels through atmosphere. [19, p. 12]

The Eq. 2.19 can be enhanced by including the effect of the ambient temperature on photocurrent:

$$i_{ph} = (i_{ph,n} + K_I \Delta_T) \frac{G}{G_n}, \qquad (2.22)$$

where  $i_{ph,n}$  is the photovoltaic current at the STC,  $K_I$  is the temperature coefficient,  $\Delta_T$  is the difference between actual temperature and the temperature in STC, G is the actual irradiance on the surface of the PV module and  $G_n$  is the irradiance on the surface of the PV module in STC. Equations 2.19-2.22 form the basis, from which the PVG model used in this thesis was built.

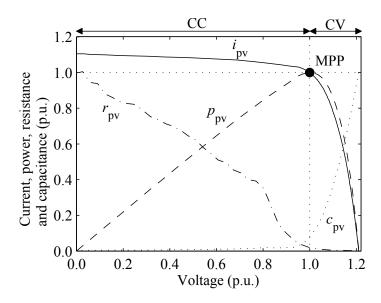

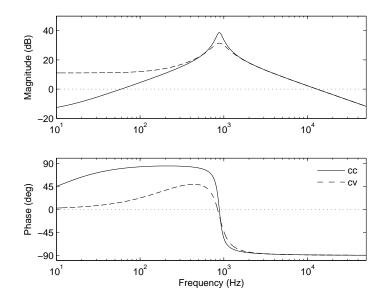

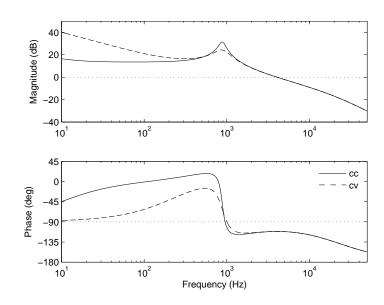

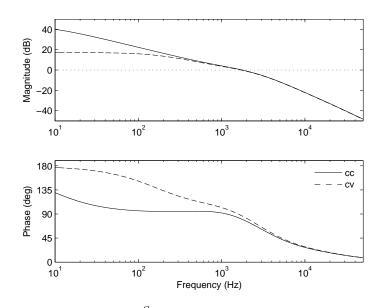

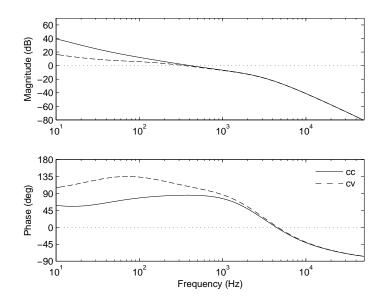

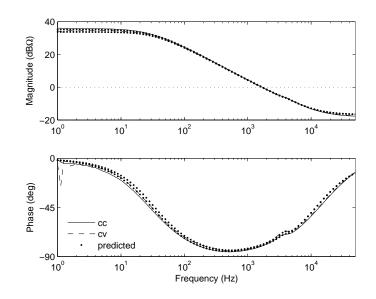

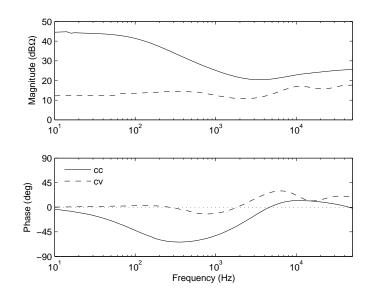

Typical static and dynamic characteristics of a PV module are shown in Fig. 2.7 as per unit values. The figure shows that a PV generator is internally a power limited non-linear current source having both constant current and constant voltage properties depending on the operation point. At MPP, the power produced by the PV module is at maximum value. The operating region from MPP to short circuit current i.e. maximum  $i_{pv}$ , is called a constant current (CC) region, and the operating region from MPP to open-circuit voltage i.e. maximum  $u_{pv}$  is called a constant voltage (CV) region, respectively.

The dynamic behaviour of a PV module is determined by its dynamic resistance  $r_{pv} = r_d ||r_{sh} + r_s|$  and the shunt capacitor  $c_{pv}$ , which are non-linear and dependent on the operation point. As it is shown in [11], the dynamic capacitance can be

Figure 2.7. Static and dynamic terminal characteristics of a PV module. [11]

approximated from the PVG impedance measured in the study as:

$$c_{pv} \approx \frac{1}{2\pi r_{pv} f_{-3dB}},\tag{2.23}$$

which is sufficiently accurate.

On the interfacing converter point of view the operating point dependent dynamic effect of a PVG can be taken into account by introducing a source admittance  $Y_S = \frac{1}{Z_S}$ . The source impedance is according to Fig. 2.6:

$$Z_S = r_s + r_d ||r_{sh}|| \frac{1}{sc_{pv}},$$

(2.24)

which can be approximated to

$$Z_S \approx r_d ||r_{sh}|| \frac{1}{sc_{pv}} \approx r_{pv} || \frac{1}{sc_{pv}}, \qquad (2.25)$$

under the assumption that  $r_s = 0$  and  $r_{pv} = r_d ||r_{sh} + r_s$ . Moreover at low frequencies:

$$Z_S \approx r_{pv},\tag{2.26}$$

which is the approximation used in this thesis. The use of Eq. 2.26 is justified if the input capacitance of an interfacing converter is larger than the dynamic capacitance i.e.  $C_{in} >> c_{pv}$ , which is typically the case. [11]

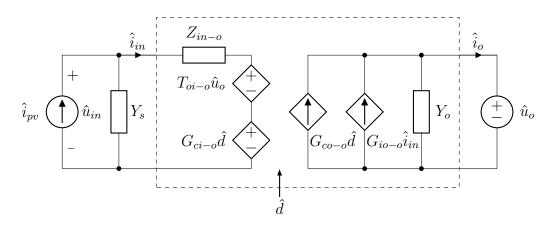

Now the source effect on the dynamics of a converter can be included in the dynamic model by using the source admittance  $Y_S$ . See Fig. 2.8.

Figure 2.8. Linear two-port model of a CF-CO dc-dc converter with non-ideal source.

By comparing the input sources in figures 2.8 and 2.5 it can be seen that

$$\hat{i}_{in} = \hat{i}_{pv} - \hat{u}_{in} Y_S,$$

(2.27)

and by solving the input-voltage from Eq. 2.16 one gets:

$$\hat{u}_{in} = Z_{in-o}\hat{i}_{in} + T_{oi-o}\hat{u}_o + G_{ci-o}\hat{d}.$$

(2.28)

Substituting Eq. 2.27 to Eq. 2.28 and rearranging yields the source-affected input-voltage:

$$\hat{u}_{in} = \frac{Z_{in-o}}{1+Z_{in-o}Y_S} \,\hat{i}_{pv} + \frac{T_{oi-o}}{1+Z_{in-o}Y_S} \,\hat{u}_o + \frac{G_{ci-o}}{1+Z_{in-o}Y_S} \,\hat{d}.$$

(2.29)

It should be noted, that the input-variable  $\hat{i}_{in}$  has now changed to  $\hat{i}_{pv}$  due to the source effect.

The source affected output-current can be solved in the same manner e.g. by substituting Eq. 2.29 into Eq. 2.27, and substituting the result into expression for output-current solved from Eq. 2.16. Rearraging gives:

$$\hat{i}_{o} = \frac{G_{io-o}}{1 + Z_{in-o}Y_{S}} \,\hat{i}_{pv} - Y_{o-o} \frac{1 + Y_{S}Z_{in-oco}}{1 + Z_{in-o}Y_{S}} \,\hat{u}_{o} + G_{co-o} \frac{1 + Y_{S}Z_{in-\infty}}{1 + Z_{in-o}Y_{S}} \,\hat{d}, \qquad (2.30)$$

where

$$Z_{in-oco} = Z_{in-o} + \frac{G_{io-o}T_{oi-o}}{Y_{o-o}} \quad \text{and} \quad Z_{in-\infty} = Z_{in-o} - \frac{G_{io-o}G_{ci-o}}{G_{co-o}}$$

(2.31)

are the open circuit input impedance and ideal input impedance, respectively. Equations: (2.29)-(2.31) give the symbolic solutions to source affected dynamic model of

the converter at open loop:

$$\begin{bmatrix} \hat{u}_{in} \\ \hat{i}_{o} \end{bmatrix} = \begin{bmatrix} Z_{in-o}^{S} & T_{oi-o}^{S} & G_{ci-o}^{S} \\ G_{io-o}^{S} & -Y_{o-o}^{S} & G_{co-o}^{S} \end{bmatrix} \begin{bmatrix} i_{pv} \\ \hat{u}_{o} \\ \hat{d} \end{bmatrix}.$$

(2.32)

Next the source affected input-to-inductor-current transfer functions are solved. From the linearized state-space representation in Eq. 2.8 one can solve the following:

$$\hat{u}_{in} = r_{C_{in}}(\hat{i}_{in} - \hat{i}_L) + \hat{u}_{C_{in}}$$

$\hat{u}_{C_{in}} = \frac{\hat{i}_{in} - \hat{i}_L}{sC_{in}},$

and by substituting the lower to the upper, and rearraging one gets:

$$\hat{u}_{in} = \left(\frac{1}{sC_{in}} + r_{C_{in}}\right)(\hat{i}_{in} - \hat{i}_L).$$

(2.33)

Substituting Eq. 2.33 into Eq. 2.27, solving it for  $\hat{i}_{in}$ , and substituting the result into 2.18 yields after rearranging:

$$\left(\frac{L\Delta}{s} - \frac{\gamma^2}{1+\gamma}\right)\hat{i}_L = \frac{\frac{1}{sC_{in}} + r_{C_{in}}}{1+\gamma}\hat{i}_{pv} - D'\hat{u}_o + U_{eq}\hat{d},$$

(2.34)

where  $\gamma = Y_S(\frac{1}{sC_{in}} + r_{C_{in}})$ , and  $\Delta = s^2 + \frac{R_{eq}}{L}s + \frac{1}{LC_{in}}$ . Solving equation 2.34 for  $\hat{i}_L$  yields the wanted source affected input-to-inductor-current transfer functions.

### 2.3 Simulation Model of The Open-loop System

In previous sections, a dynamic model of the CF-CO boost-power-stage converter, and how the effect of a PVG can be included into it, was presented. In this section, a simulation model of the converter and PVG is built for analyzing the time-domain behaviour of the system. The software used for modelling and simulation was MATLAB<sup>TM</sup>Simulink.

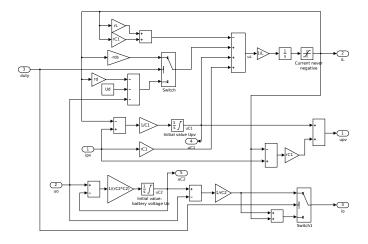

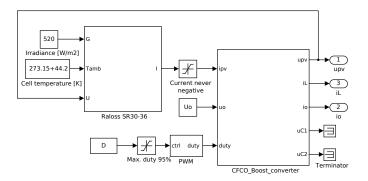

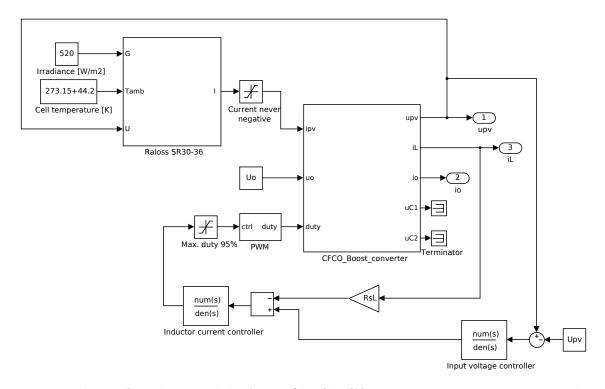

The simulation model of the converter can be built from the on -and off-time equations: 2.3 and 2.4. The resulting model is presented in Fig. A.1. It should be noted, that the notation is different in Fig. A.1 from the one used in previous sections. The converter variables: "C1, C2, rC1, rC2, uC1, uC2 and rds" in the simulation model correspond with variables: " $C_{in}$ ,  $C_o$ ,  $r_{C_{in}}$ ,  $r_{C_o}$ ,  $u_{C_{in}}$ ,  $u_{C_o}$ , and  $r_{sw}$ " used in the dynamic modelling section, respectively. The variables: "ipv, uo and duty" in the figure are the input-variables of the converter and correspondingly "upv and io" are the output-variables. The output "iL" is obviously the inductor-current output, and it is needed for connecting the inductor-current controller. Furthermore, the inductor-current can not be negative due to the inherent output-diode in a boost converter, so its minimum value is limited to zero.

The Simulink model of a PV generator used in this thesis was developed in [18, p. 47-56] according to principles presented in [17]. The basic equations for the modeling were introduced in this thesis earlier Eqs: 2.19-2.21. The input-variables for the model are G the intensity of solar irradiation,  $T_{amb}$  the ambient temperature in Kelvins and voltage U, which determines the operating point on the PVG I-V curve. The output of the block is the PVG current. The model also takes other parameters for defining a given PVG.

In this thesis a commercial Raloss SR30-36 solar panel was selected as an example PVG. The Raloss SR30-36 is composed of 36 series connected 2A monocrystalline silicon cells with no bypass diodes in parallel with any of the cells. The model parameters of Raloss SR30-36 were:

Table 2.1. PVG model parameters for Raloss SR30-36 in STC.

| Parameter                               | Value                                   |

|-----------------------------------------|-----------------------------------------|

| Nominal power                           | 30W                                     |

| Short-circuit current in STC $(I_{sc})$ | 1.91A                                   |

| Open-circuit voltage in STC $(U_{oc})$  | 21.81V                                  |

| Temperature in STC                      | 298.15K                                 |

| Irradiance in STC $(G)$                 | $1000 \frac{W}{m^2}$                    |

| Series resistance                       | $0.9201\Omega$                          |

| Shunt resistance                        | $346.3546\Omega$                        |

| Temperature coefficient of $I_{sc}$     | 0.0012                                  |

| Temperature coefficient of $U_{oc}$     | -0.0828                                 |

| Temperature increase due to $G$         | 0K                                      |

| Boltzmann constant                      | $1.3806503 \times 10^{-23} \frac{J}{K}$ |

| Elementary charge                       | $1.60217646 \times 10^{-19}C$           |

| Ideality factor                         | 1.0                                     |

| Number of cells                         | 36                                      |

The PVG model parameters were determined experimentally through an iterative process as presented in [17]. The whole idea of the process is to match the remarkable points  $I_{sc}$ ,  $U_{oc}$  and MPP of the model I-V curve to the ones presented on the datasheet.

The electrical and dynamic properties of a real Raloss SR30-36 solar panel were measured during earlier studies in Tampere University of Technology. The measurement setup can be found e.g. from [20]. The measurement data included outputvoltages and currents with short-circuit current ( $I_{sc}$ ) of 1A corresponding with an irradiance of  $G \approx 500 \frac{W}{m^2}$ . The average temperature during the measurements were  $T \approx 44.2 \text{C}^{\circ}$  according to the data. Also, the dynamic resistance  $r_{pv}$  was measured in several different operation points.

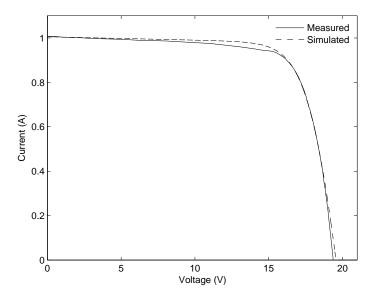

In Fig. 2.9, two I-V curves are presented. The measured I-V curve is based on the measured data of a Raloss SR30-36 panel, and another is simulated by using the PVG model and parameters presented in Table 2.1. The simulation was done in the same temperature as the average measurement temperature. The exact irradiance was not known, so it was selected to  $G = 520 \frac{W}{m^2}$ , since it matched the measured short circuit current.

Figure 2.9. Measured and simulated Raloss SR30-36 I-V curves.

As it can be seen from Fig. 2.9, the correspondence of the I-V curves is fairly high. There is a slight deviance in the open-circuit voltage and in the CC region curve, however.

From the measurement data and the simulated I-V curve, the PVG operation points and the corresponding dynamic resistances for simulations and drawing the system transfer functions were selected as:

Table 2.2.

The steady-state operation points of the system.

| Operation region             | Voltage $U_{in}$ | Current $I_{in}$ | Dynamic resistance $r_{pv}$ |

|------------------------------|------------------|------------------|-----------------------------|

| Constant current region (CC) | 12V              | 0.99A            | $157\Omega$                 |

| Maximum power point (MPP)    | 16V              | 0.92A            | $17.4\Omega$                |

| Constant voltage region (CV) | 17V              | 0.82A            | $7.2\Omega$                 |

The simulation model of the open-loop system is presented in Fig. A.2. The

simulation process advances as follows. At the beginning of a simulation, the operation point is selected from the table 2.2. Then the Duty-ratio D is calculated by using the second equation from top in 2.6 and the voltage and current values of the selected operation point.  $U_o$  is a constant. The switching pulse is generated in the PWM-block by comparing the calculated steady-state duty-ratio to a ramp signal having an amplitude of 1 and frequency of  $f_s$ . Some time after the simulation has been started, the converter reaches a steady-state point, and the output-values can be read. The converter is said to be at open-loop, and this type of control is called as the *direct duty-ratio control* (DDR-control).

## 3. CONVERTER DESIGN

In this chapter, a boost converter with an additional input capacitor in Fig. 2.2 is designed based on the maximum input-current of the source PVG. The principles used for selecting and designing the components are discussed, and their corresponding dynamic model parameter values are determined. The chapter is organized as follows: First, the properties of the source PVG are discussed, namely the maximum current it can provide. Next, based on the maximum input-current, an inductor is designed. Thirdly, the selection of the semiconductor components i.e. switch and diode is verified in terms of their loss power. Finally, the selection of the input and output-capacitors is discussed.

### 3.1 Maximum Input Current

There are several possible ways to determine the maximum input-current. In [21], the author designed two dc-dc converters using different design methods. In first of the methods, which was called as a conventional design method, the maximum input-current was determined by using a minimum input-voltage value of the PVG at MPP, and a sizing factor (SF). The sizing factor was presented as:

$$SF = \frac{P_{nom}}{P_{\text{PVG-STC}}},\tag{3.1}$$

where  $P_{nom}$  is the nominal power of a solar inverter, which consists of a dc-dc converter and an inverter, and  $P_{PVG-STC}$  is the maximum power of a given PVG at STC. Then a following equation was used:

$$I_{\rm IN,MAX} = \frac{P_{\rm PVG-STC}SF}{U_{\rm MPP,MIN}}.$$

(3.2)

$U_{\rm MPP,MIN}$  was calculated based on the fact that a rise in temperature decreases the open-circuit voltage of a PVG, which then again decreases the MPP voltage, and the fact that in partial shading conditions depending on the inner structure of a PVG, there might be some groups of series connected cells bypassed by diodes, which leads to lower output-voltage.

In the second method, which was referred as a new design method, the maximum input-current was determined by analyzing measurement data. The measured data was obtained from the solar energy system located on the roof of Tampere University of Technology. The PV module used in the study was NAPS NP190Gkg. It was found that the maximum output-current of the NAPS NP190Gkg in any climate conditions is about 1.4 times the short-circuit current in STC.

The results of the study in question were that by using the new design method, the inductor core becomes smaller, there is less capacitance at the input, and the switching component heat sink becomes smaller than by using the conventional design method. Based on these results, the new design method i.e. determining the maximum input-current according to peak solar irradiance, was selected for designing the converter in this thesis. For Raloss SR30-36, the short-circuit current in STC is 1.91A according to the datasheet [22], so the maximum short-circuit current  $I_{\rm SC,MAX}$  is  $1.91A * 1.4 \approx 2.67A$ , which is the converter maximum inputcurrent.

By using a current value this high in the design, eventhough the actual converter is simulated and measured with smaller currents ( $\leq 1.005$ A), it becomes certain that the converter could be supplied with a real Raloss SR30-36 solar panel, and the inductor core does not saturate in any condition.

### 3.2 Inductor Design

By solving duty-ratio from Eq. 2.1 and substituting the result into the Eq. 2.2, the equation for the inductor-current ripple can be formulated as:

$$\Delta i_{L,pp} = -\frac{T_s U_{in}^2}{U_o L} + \frac{T_s U_{in}}{L}.$$

(3.3)

Now by differentiating the Eq. 3.3 with respect to  $U_{in}$ , equating it to zero and solving it for  $U_{in}$  yields that the maximum inductor-current ripple can be found when  $U_{in} = \frac{U_o}{2}$ . Substituting this result back into Eq. 3.3, the minimum value of the inductance can be obtained as:

$$L = \frac{U_o}{4\Delta i_{L,pp} f_s}.$$

(3.4)

In this thesis, the value of the  $U_o$  was selected as 26V, because of the actual load configuration used in the measurements. The switching frequency was selected to 100kHz, since the control was coded on the digital signal processor (DSP) in such way, that the sampling frequency was the same, thus providing accurate enough transfer functions for the controllers. Furthermore, the maximum amount of inductor-current ripple was selected to be 20% of the input-current of 1A. With these values inserted into Eq. 3.4, the minimum value of the inductance becomes  $L \approx 325 \mu$ H.

A power inductor consists of a magnetic core and a copper wire wound around it. The electrical and magnetic characteristics of a power inductor depends on numerous factors, which are e.g. the size of the magnetic core, and the material from which it is made of. One way for evaluating the size of a magnetic core for a given application is the core geometrical constant  $K_g$ , which is the first step in the inductor design procedure presented in [14, p.544-545]. According to this procedure the selected magnetic core has to satisfy the inequality:

$$\frac{A_c^2 W_A}{\text{MLT}} \ge \frac{\rho L^2 I_{max}^2}{B_{max}^2 R K_u}, \quad (\text{cm}^5)$$

(3.5)

where the left side of the equation equals the  $K_g$ .  $A_c$  is the cross-sectional area of the core,  $W_A$  is the core window area, MLT is the mean length per turn,  $\rho$  is the resistivity of the coil winding wire (1.724  $\mu\Omega \cdot \text{cm}$  at 25C° for copper), L is the desired inductance,  $I_{max}$  is the maximum current inside the converter:  $I_{max} = I_{\text{SC,MAX}} + \frac{\Delta i_{L,pp}}{2}$ ,  $B_{max}$  is the selected maximum flux density (should be lower than the saturation flux density  $B_{sat}$ ), R is the resistance of the coil winding wire and  $K_u$ is the winding fill factor.

Epcos ETD29 core made of N87 (MnZn) ferrite was selected as the magnetic core of the inductor, since it was readily available. Ferrites in general are a popular choice for switched mode converter applications due to their low cost and low power loss. For the selected core, the geometrical parameters: saturation flux density, core window fill factor, size of an air gap,  $A_L$  value and effective permeability are presented in table 3.1. Values presented in the table can be found from the manufacturers datasheets: [23] and [24].

| Variable                        | Explanation               | Value                      |

|---------------------------------|---------------------------|----------------------------|

| $A_c$                           | Core cross-sectional area | $0.76 \mathrm{cm}^2$       |

| $W_A$                           | Core window area          | $0.97 \mathrm{cm}^2$       |

| MLT                             | Mean length per turn      | $5.28\mathrm{cm}$          |

| $B_{sat}$                       | Saturation flux density   | $0.49T~(25C^{\circ})$      |

| $B_{sat}$                       | Saturation flux density   | $0.39T (100C^{\circ})$     |

| $K_u$                           | Winding fill factor       | 0.4                        |

| g                               | Air gap                   | $0.5 \pm 0.05 \mathrm{mm}$ |

| $A_L$                           | Inductance per turn       | $\approx 201 \mathrm{nH}$  |

| $\mu_e$                         | Effective permeability    | 148                        |

| $I_e$                           | Magnetic path length      | 70.4mm                     |

| $V_e$ Effective magnetic volume |                           | $5350 \mathrm{mm}^3$       |

|                                 |                           |                            |

Table 3.1. Values for the ETD29 type core made of N87 material.

Using the values presented in table 3.1, the rest of the unknown variables in Eq. 3.5 can be determined. Peak current through the inductor can be calculated as:

$$I_{max} = I_{\rm SC,MAX} + \frac{\Delta i_{L,pp}}{2} = 2.67A + \frac{0.2A}{2} = 2.77A.$$

(3.6)

The maximum flux density can be selected to any value lower than the saturation flux density. This was selected to 0.3 T for some safety margin. The  $A_L$  value is related to inductance and number of turns (N) by:

$$L = A_L N^2 \Leftrightarrow N = \pm \sqrt{\frac{L}{A_L}} = \sqrt{\frac{325\mu H}{201nH}} \approx 40 \text{ turns.}$$

(3.7)

The final unknown variable is the winding resistance, which can be calculated with an equation:

$$R = \rho_{Cu} \frac{N(\text{MLT})}{A_w} = \frac{1.724\mu\Omega \cdot \text{cm} * 40 * 5.28\text{cm}}{0.00636\text{cm}^2} \approx 0.0572\Omega, \quad (3.8)$$

where wire cross-sectional area  $A_w$  is for a wire of 0.9mm in diameter.

Now by substituting the presented values into Eq. 3.5, the right-hand side becomes:

$$\frac{\rho L^2 I_{max}^2}{B_{max}^2 R K_u} = \frac{1.724 \frac{\mu\Omega}{\rm cm} (325 \mu H)^2 (2.77 A)^2}{(0.3T)^2 * 0.056 \Omega * 0.4} 10^8 \approx 0.07 \ {\rm cm}^5, \tag{3.9}$$

where the multiplication with  $10^8$  is made to match the units. The left-hand side i.e. the geometrical constant  $K_g$  becomes:

$$K_g = \frac{A_c^2 W_A}{\text{MLT}} = \frac{(0.76 \text{cm}^2)^2 * 0.97 \text{cm}^2}{5.28 \text{cm}} \approx 0.106 \text{ cm}^5,$$

(3.10)

so the inequality holds, and the selected core is large enough for the application.

During the previous analysis, the number of turns needed for obtaining the desired inductance was calculated. It should be verified that the selected number of turns does not saturate the core. This can be done with the following equation:

$$N_{max} = \frac{B_{sat}I_e}{\mu_o\mu_e I_{max}} = \frac{0.49T * 0.0704m}{4\pi * 10^{-7}\frac{H}{m} * 148 * 2.77A} \approx 67 \text{ turns.}$$

(3.11)

In fact, if the Eq. 3.11 was solved for B, when N is the selected number of turns i.e. 40, the result is 0.293T. Furthermore, when it is taken into account that the maximum current fed into the converter in measurements is 1A, the core should not saturate in any situation.

Power is lost in the inductor due to core losses and copper losses. The core losses are a sum of hysteresis, eddy current and residual losses. The copper losses are

mainly caused by the dc resistance of the winding, however, at high frequencies the losses are further increased due to skin and proximity effects.

For estimating the time average core loss per unit volume, the general Steinmetz equation in Eq. 3.12 for sinusoidal excitation can be used [25, p. 14].

$$P_{fe} = K_m f^{\alpha} (\frac{\Delta B}{2})^{\beta} \tag{3.12}$$

In Eq. 3.12,  $K_m$ ,  $\alpha$  and  $\beta$  are material constants, which can be usually found from manufacturers' datasheets. For N87 material these values are:  $K_m = 16.9$ ,  $\alpha = 1.25$  and  $\beta = 2.35$  [25, p. 20]. The  $\Delta B$  is the variance in flux density due to the inductor-current ripple. This can be calculated by applying the Eq. 3.11. With an inductor-current ripple of 0.2A, the  $\Delta B$  is 21.1mT. By substituting these values into Eq. 3.12, the approximated total core loss per unit volume is  $683 \frac{W}{m^3}$ , and by multiplying this result with effective magnetic volume  $V_e$  in Table 3.1 yields a total core power loss of 3.65mW.

The copper losses due to the average inductor-current can be calculated simply by Eq. 3.13.

$$P_{Cu,DC} = I_L^2 R \tag{3.13}$$

For  $I_{\rm SC,MAX}$  this yields approximately 0.408W of power loss and for 1A the result is 57.2mW. Copper losses due to the inductor-current ripple were omitted from the total loss calculations, because of their relatively small size. The results of power loss calculations are presented in Table 3.2.

Table 3.2. Calculated power losses in the designed inductor.

| Current          | $P_{\rm CORE} ({\rm mW})$ | $P_{\rm Cu,DC}$ (mW) | $P_{\rm TOTAL} (\rm mW)$ |

|------------------|---------------------------|----------------------|--------------------------|

| $I_{\rm SC,MAX}$ | 3.65                      | 408                  | 412                      |

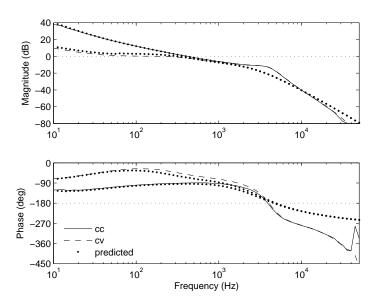

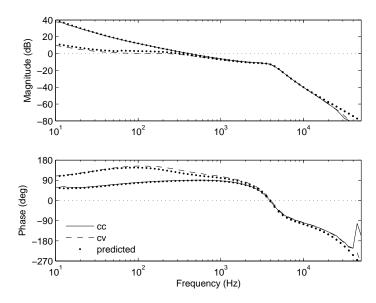

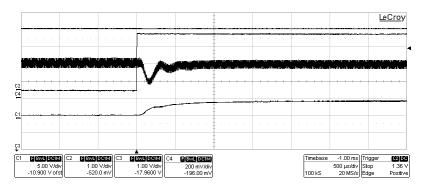

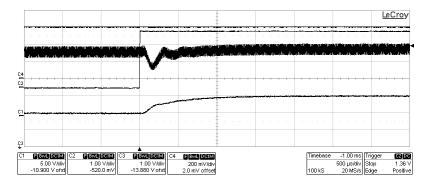

| 1A               | 3.65                      | 57.2                 | 60.9                     |