# JAVIER PÉREZ DE FRUTOS LOW-COST STANDALONE COMMUNICATION INTERFACE FOR DATA ACQUISITION SYSTEM IN MICROROBOTIC PLATFORM

Master of Science Thesis

Examiner: Prof. PASI J. KALLIO Supervisor: MATHIAS VON ESSEN Examiners and topic approved by the Council of the Faculty of Engineering Sciences on 9<sup>th</sup> of April 2014

# ABSTRACT

TAMPERE UNIVERSITY OF TECHNOLOGY JAVIER PÉREZ DE FRUTOS : Low-Cost Standalone Communication Interface For Data Acquisition System In Microrobotic Platform Master of Science Thesis, 73 pages, 12 appendix pages July, 2014 Major: Automation science and industrial electronics Examiner: Professor Pasi J. Kallio Supervisor: Mathias Von Essen Keywords: BeagleBone Black, interface, communication, data acquisition system, Inter-Integrated Circuit, analogue to digital covnersion

A development platform is an standalone electronic system, suited with open hardware and software, governed by a microprocessor or a microcontroller. The flexibility and adaptability encourages the spread of these systems in a wide range of applications, by different level designers. The platform is aimed to provide the enough software and hardware features for these projects. Though, additional circuitry and subsystems can be connected enhancing the capability of the electronic prototyping platform.

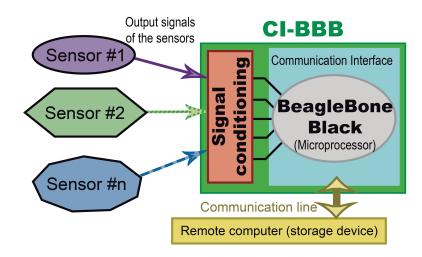

The core objective of this thesis work is the design and implementation of a communication interface over a BeagleBone Black (BBB) development platform, named as BeagleBone Black Communication Interface (CI-BBB). The scope of the resulted device, is the data acquisition system (DAQ) of the Microrobotic Platform (MP) of FIBAM project, developed by the Micro- and Nanosystems Research Group, of Tampere University of Technology. For that purpose the work is divided in two main areas. In first place, the necessary electronic circuits for signal adapting, which is built on a printed circuit board (PCB) and connected to the BBB. And the control software, which includes a function library and a remote control program. The final device results in an standalone system that comprises the hardware and software in a small area.

Performance measurements are made to characterize the features of the CI-BBB and the integration within the MP. The platform presents the capacity to acquire data, from analogue sources and I<sup>2</sup>C bus communication system, and provide the fetched samples in a file. The remote control provides a communication line with the system, ensuring the integration of the CI-BBB in the MP and avoiding the introduction of additional elements in the overall system.

### PREFACE

The present thesis has been handled at the Micro- and Nanosystems Research Group, at the Department of Automation Science and Engineering of Tampere University of Technology.

In first place, I would like to express my gratitude to Professor Pasi Kallio, for giving me the opportunity to work on this thesis within the Microrobotic Platform project, and learn how real engineering projects are carried out. To my supervisor, Mathias von Essen, for all the invaluable help, support and patience when programming the BeagleBone Black and designing the circuits. To Pooya Saketi, for lending me the tracker NSE 5310 to test the I<sup>2</sup>C program. To Kourosh Latifi, for assisting me make the tests with the microforce sensor. To Jarmo Verho, for his advices and guidelines to design the printed circuit board of the cape. Furthermore, thank you to my director of the thesis at my home university in Spain Jorge Portilla, for his help and advices despite the distance.

To my beloved family, with which I have an eternal debt of gratitude. I would have never reach this far without them. Their support and love, encouraged and will inspire me through all my life. Muchas gracias de todo corazón, sin vuestro apoyo y amor este día nunca habría sido posible.

Finally I want to thank all my friends, the family we chose to life with, formed by the special people we meet along the path. Thank you to the ones I left at home, with which I discover the life beyond textbooks and learned what is not taught in engineering schools. And thank you, to all the people I meet during my stay in Finland. They filled my days with joy, great experiences and memories I could hardly forget.

Javier Pérez de Frutos Tampere,  $21^{st}$  July 2014

# **TABLE OF CONTENTS**

| 1. | Introduc  | etion                                                                                                        | 1  |

|----|-----------|--------------------------------------------------------------------------------------------------------------|----|

|    | 1.1 Mo    | $\operatorname{tivation}$                                                                                    | 3  |

|    | 1.2 Ob    | jective and scope                                                                                            | 3  |

|    | 1.3 Ou    | tline                                                                                                        | 4  |

| 2. | Principle | es of Data Acquisition Systems                                                                               | 5  |

|    | 2.1 De    | finition of Data Acquisition Systems                                                                         | 5  |

|    | 2.2 Ele   | ements of the voltage adapter stage                                                                          | 6  |

|    | 2.2.1     | Voltage divider                                                                                              | 7  |

|    | 2.2.2     | Operational Amplifier                                                                                        | 8  |

|    | 2.3 Th    | eoretical framework for the communication channels $\ldots$ $\ldots$ $\ldots$                                | 19 |

|    | 2.3.1     | Analogue to digital conversion                                                                               | 19 |

|    | 2.3.2     | Inter-Integrated Circuit communication protocol                                                              | 23 |

| 3. | BeagleB   | one Black and Scope of the thesis                                                                            | 26 |

|    | 3.1 Mie   | crorobotic platform                                                                                          | 26 |

|    | 3.1.1     | Force sensor FT-S10000                                                                                       | 27 |

|    | 3.1.2     | Tracker NSE-5310                                                                                             | 29 |

|    | 3.2 Bea   | agleBone Black                                                                                               | 30 |

|    | 3.2.1     | Hardware description                                                                                         | 30 |

|    | 3.2.2     | Software support                                                                                             | 39 |

| 4. | Commu     | nication Interface                                                                                           | 43 |

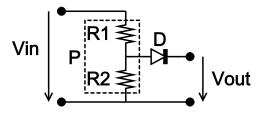

|    | 4.1 Vol   | ltage Attenuator circuit                                                                                     | 44 |

|    | 4.1.1     | Voltage Attenuator based on voltage divider circuit                                                          | 44 |

|    | 4.1.2     | Voltage Attenuator based on operational amplifiers $\ldots$ $\ldots$ $\ldots$                                | 45 |

|    | 4.1.3     | Measurements and circuit selection                                                                           | 47 |

|    | 4.1.4     | Components of the Voltage Attenuator prototypes $\ldots \ldots \ldots$                                       | 50 |

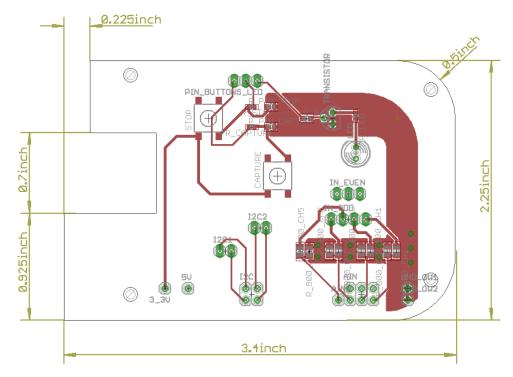

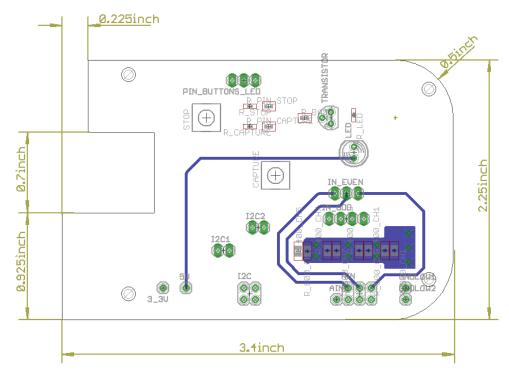

|    | 4.2 Th    | e cape implemented for the BeagleBone Black                                                                  | 52 |

|    | 4.3 Sof   | tware: library and remote control                                                                            | 55 |

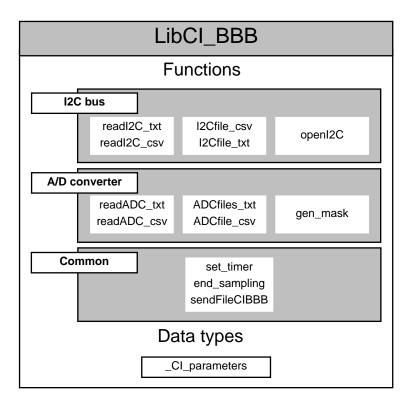

|    | 4.3.1     | The Communication Interface Library                                                                          | 56 |

|    | 4.3.2     | Remote Control software                                                                                      | 61 |

|    | 4.4 Per   | formance measurements                                                                                        | 62 |

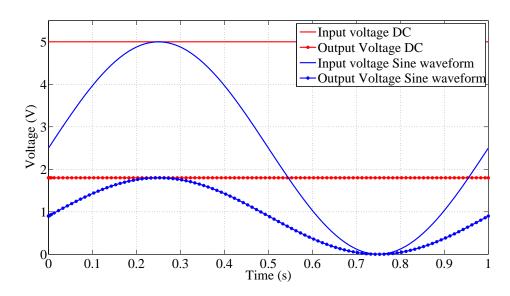

|    | 4.4.1     | A/D converter analysis $\ldots \ldots \ldots$ | 62 |

|    | 4.4.2     | Long-term test                                                                                               | 64 |

|    | 4.4.3     | Final implementation of the system                                                                           | 65 |

| 5. | Conclusi  | ons and future work                                                                                          | 67 |

| Re | ferences  |                                                                                                              | 70 |

| Appendices                                                                                                                           | <b>74</b> |

|--------------------------------------------------------------------------------------------------------------------------------------|-----------|

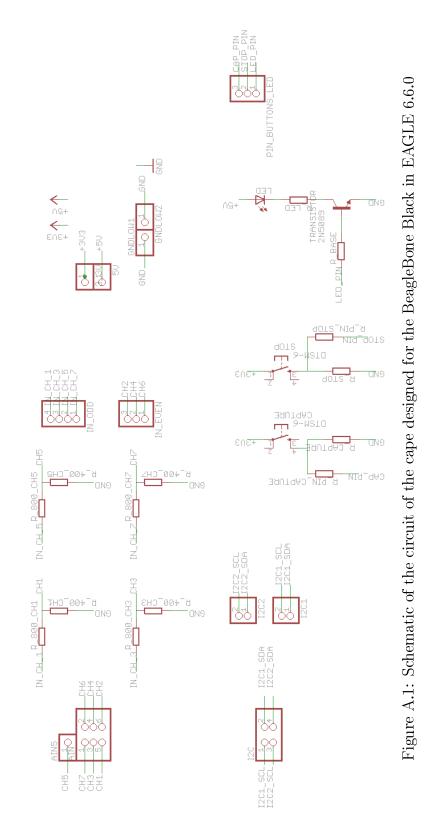

| Appendix A: Schematic of the cape for the BeagleBone Black in EAGLE 6.6.0                                                            | 74        |

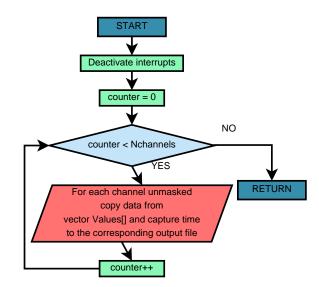

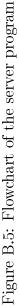

| Appendix B: Flowchart diagrams                                                                                                       | 76        |

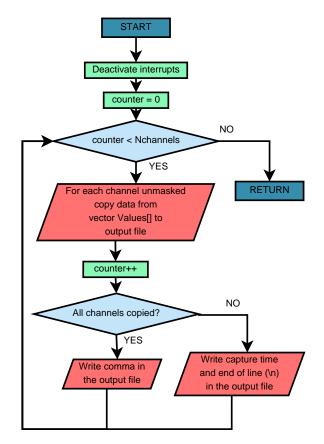

| A/D converter function flowchart - Final version                                                                                     | 76        |

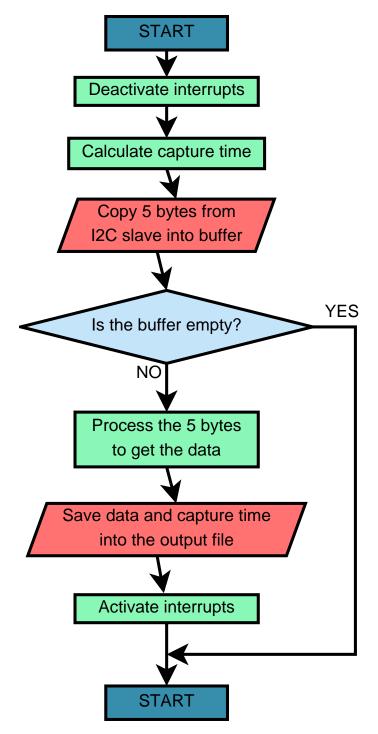

| $I^2C$ function flowchart                                                                                                            | 77        |

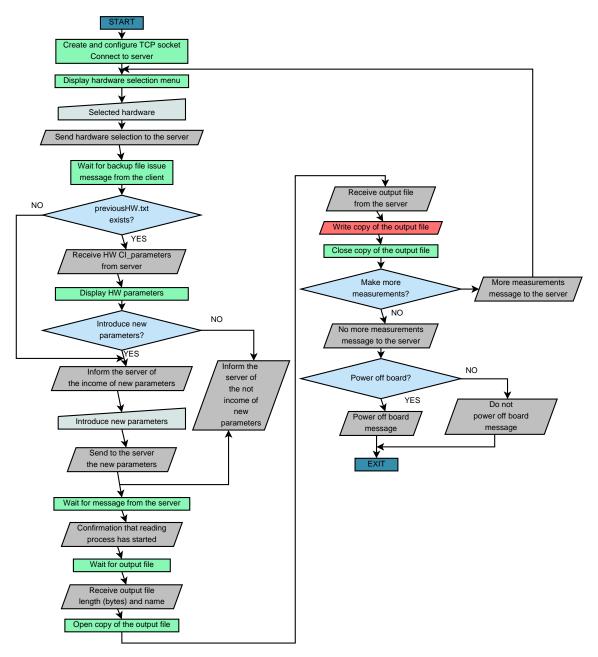

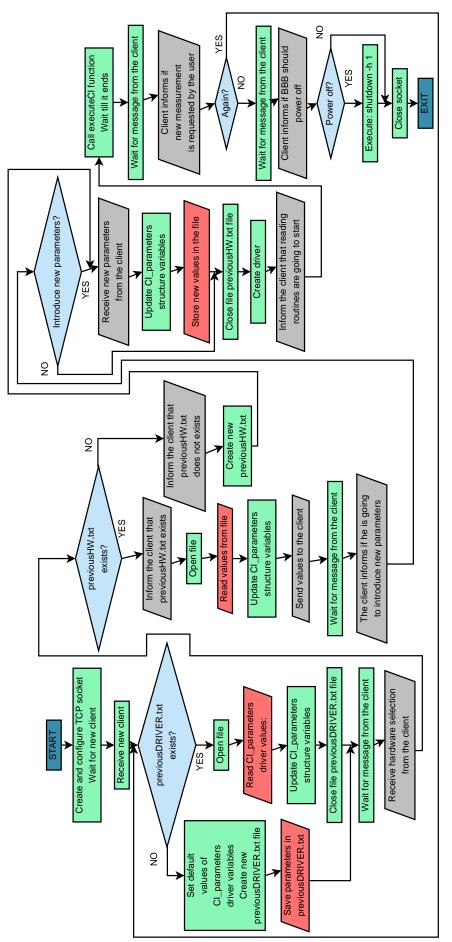

| Remote control program flowchart                                                                                                     | 78        |

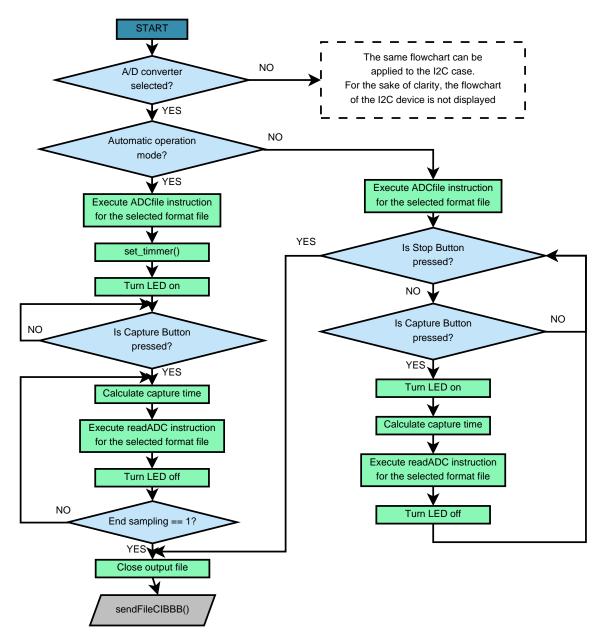

| Appendix C: User Manual for the Remote Control of CI-BBB                                                                             | 81        |

| Start up the CI-BBB                                                                                                                  | 81        |

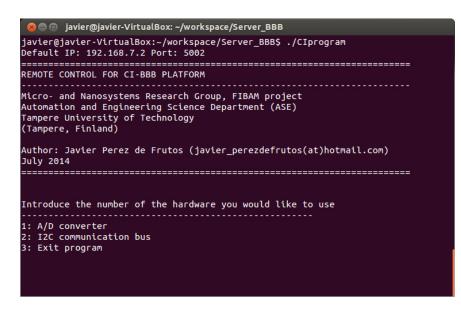

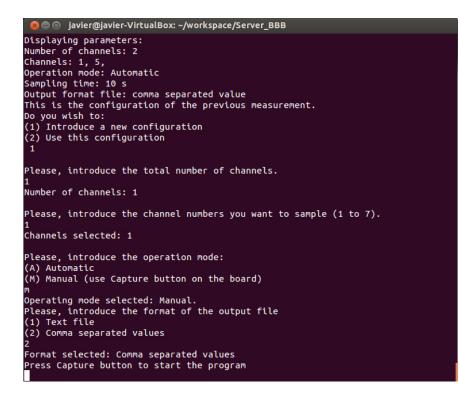

| ${ m A}/{ m D}$ conversion of analogue signals $\ \ldots \ $ | 82        |

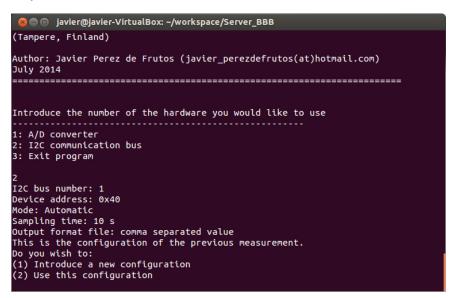

| $I^2C$ communication bus                                                                                                             | 84        |

| How to find the $I^2C$ device address $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                 | 85        |

# **LIST OF FIGURES**

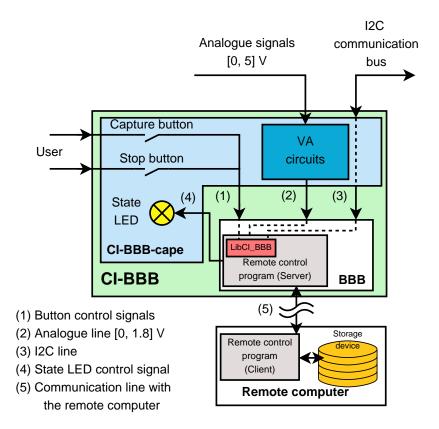

| 1.1  | Concept of the CI-BBB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4              |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

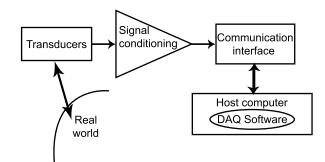

| 2.1  | Block diagram of a DAQ system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5              |

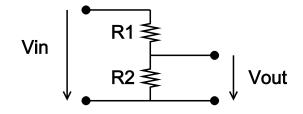

| 2.2  | Operation of a potentiometer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $\overline{7}$ |

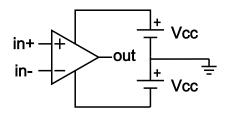

| 2.3  | Connection of energy sources to an OA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9              |

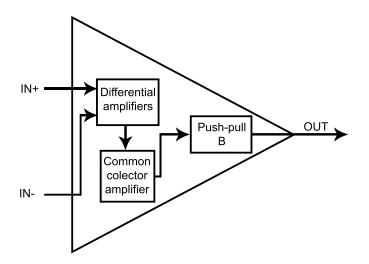

| 2.4  | Block diagram of an Operational Amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 9              |

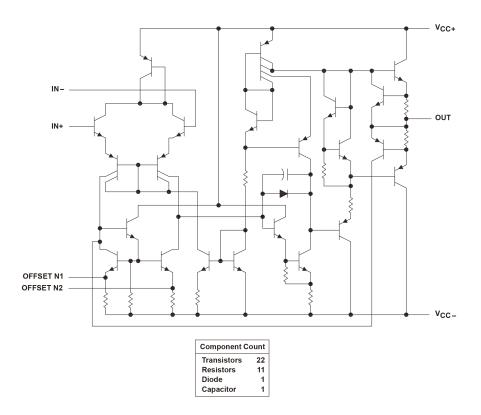

| 2.5  | Internal structure of the general-purpose OA $\mu$ A741 [19]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 10             |

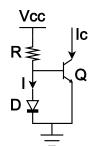

| 2.6  | Schematic of a current mirror                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 11             |

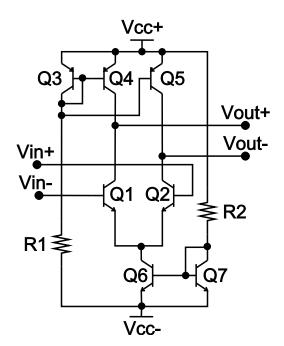

| 2.7  | Schematic of a differential amplifier implemented in an OA $\ldots$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 11             |

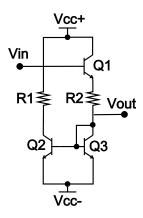

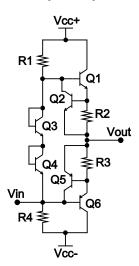

| 2.8  | Schematic of a common collector amplifier implemented in an OA $$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 12             |

| 2.9  | Schematic of the push-pull AB of the output stage of an OA $\ldots$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 13             |

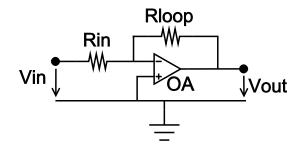

| 2.10 | Inverting amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 15             |

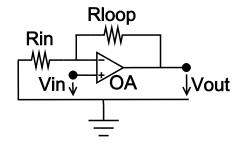

| 2.11 | Non-inverting amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 16             |

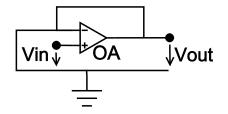

| 2.12 | Voltage follower                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 16             |

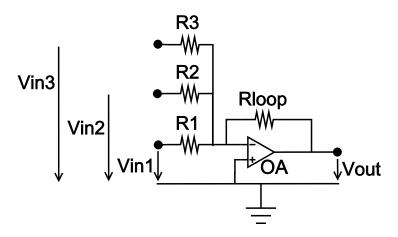

| 2.13 | Inverting adder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 17             |

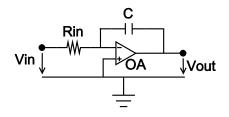

| 2.14 | Ideal integrator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 17             |

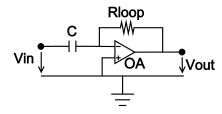

| 2.15 | Ideal differentiator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 18             |

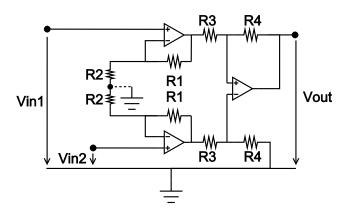

| 2.16 | Instrumentation amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 18             |

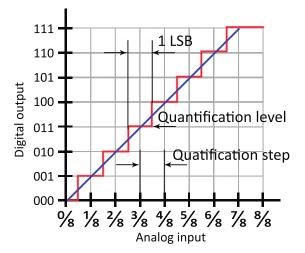

| 2.17 | Relation between the input and the output signals of a $A/D$ converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 20             |

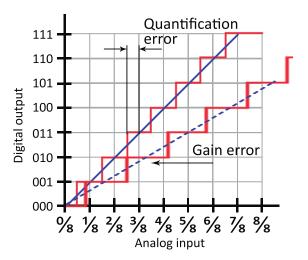

| 2.18 | Quantification and gain errors of a A/D converter $\ . \ . \ . \ . \ .$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 21             |

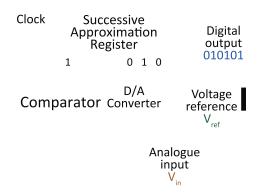

| 2.19 | Successive Approximation Register A/D converter block diagram [4; 24]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 23             |

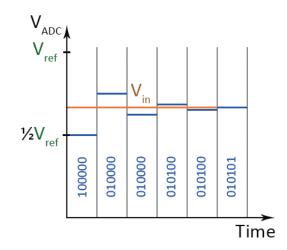

| 2.20 | Successive Approximation Register search process [4; 24]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 23             |

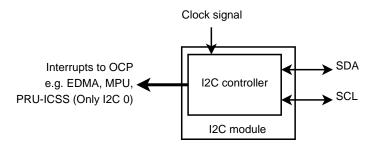

| 2.21 | Basic structure of a I <sup>2</sup> C bus communication system $\ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 24             |

| 2.22 | Data sequence of a basic $I^2 C$ communication process $\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hf$ | 25             |

| 3.1  | Microrobotic platform of the FIBAM project: (a) Old version, (b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                |

|      | New version                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 27             |

| 3.2  | Detail of the force sensor $[43]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 28             |

| 3.3  | Force sensor FT-S10000 of FemtoTools [43]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 28             |

| 3.4  | 3D model of the Tracker NSE-5310 [41] $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 29             |

| 3.5  | Tracker NSE-5310                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 29             |

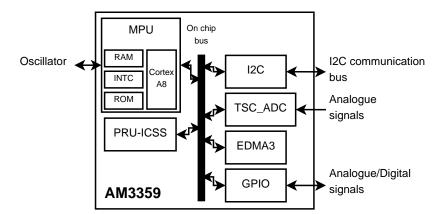

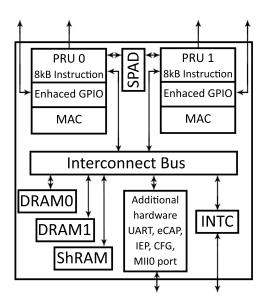

| 3.6  | Block diagram of the microprocessor with the most relevant OCP $$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 30             |

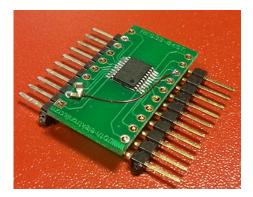

| 3.7  | BBB. Revision A5C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 31             |

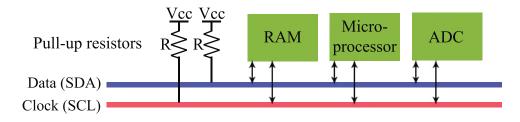

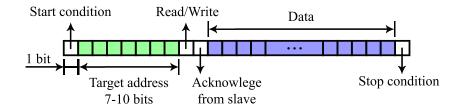

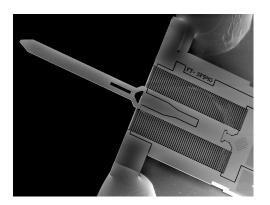

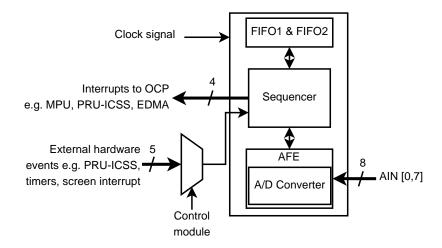

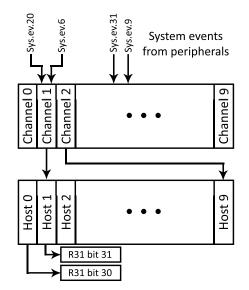

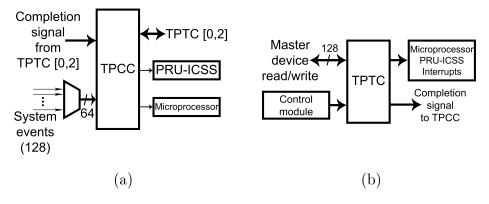

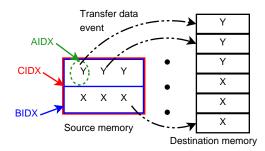

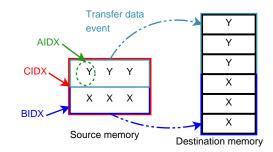

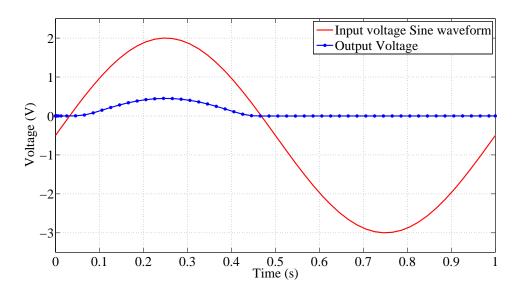

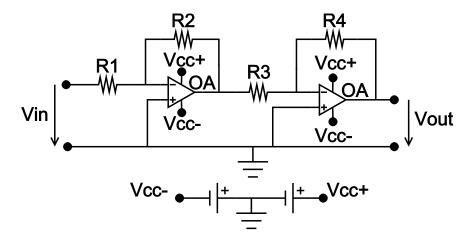

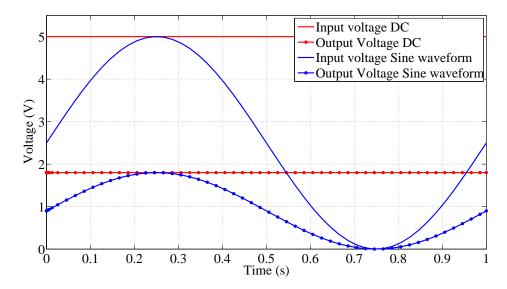

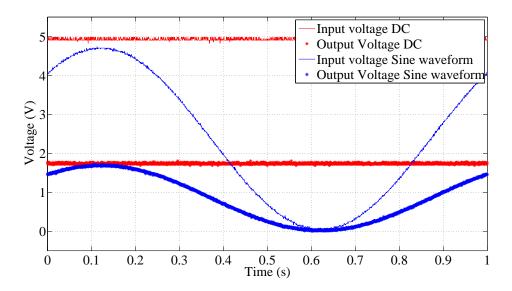

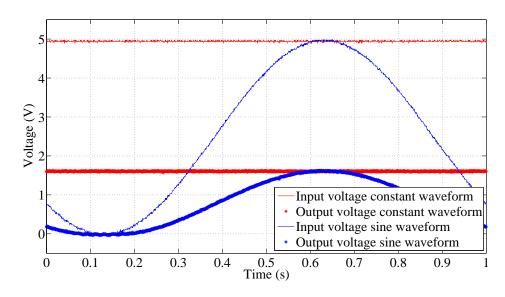

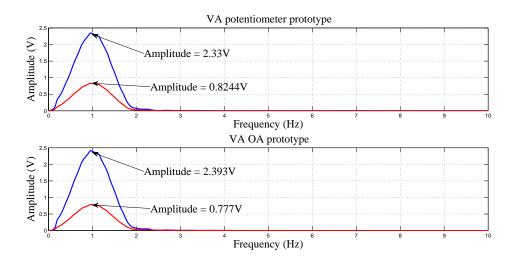

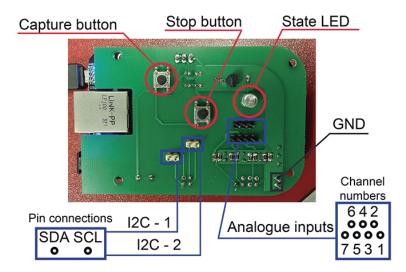

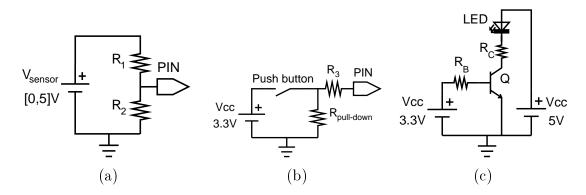

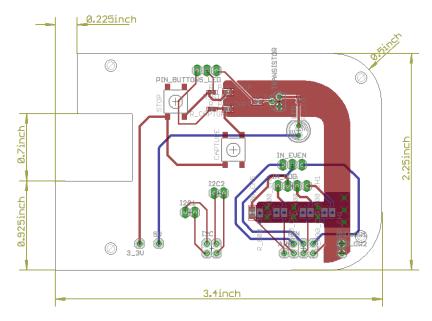

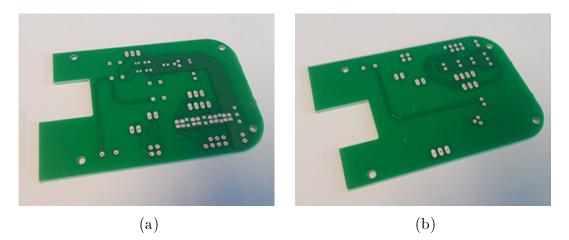

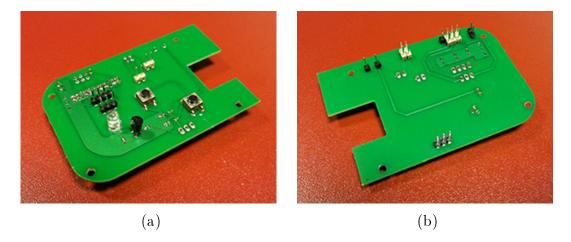

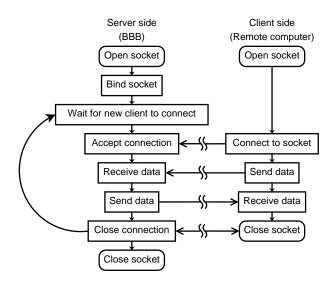

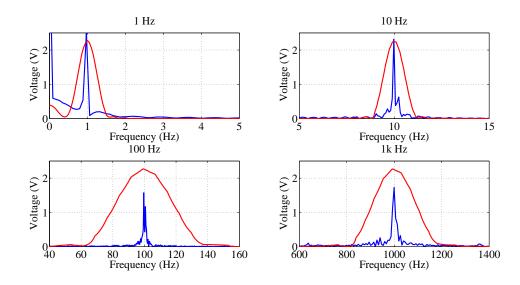

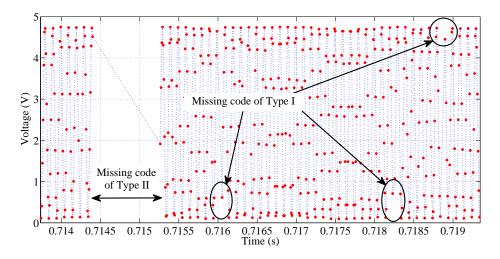

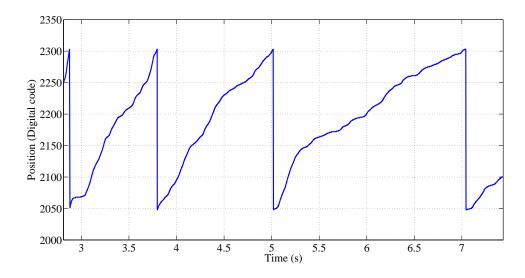

| 3.8  | Block diagram of the TSC_ADC subsystem [22]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 32             |