## Rehman Akbar HIGH SPEED FULLY MONOLITHIC SELF-TRIGGERED DC-DC BUCK CONVERTER Master of Science Thesis

Supervisor:Professor Nikolay T. Tchamov, Ph. D Examiner: Prof. Nikolay T. Tchamov, Jani Järvenhaara

Examiners and subjects were approved in the Faculty of Computing and Electrical Engineering Council meeting on 03-Apr-2013

# TIIVISTELMÄ

TAMPEREEN TEKNILLINEN YLIOPISTO

Sähkötekniikan koulutusohjelma

Rehman Akbar: Suurinopeuksinen monoliittinen itseliipaiseva DC-DC-muunnin

Diplomityö, 56 sivua, 9 liitesivua

Joulukuu 2013

Pääaine: Suurtaajuustekniikka

Ohjaaja: professori Nikolay T. Tchamov,

Tarkastaja: Prof. Nikolay T. Tchamov and Jani Järvenhaara

Avainsanat: DC-DC-muunnin, kuollut aika, CMOS, 45 nm

DC-DC-muuntimien sisällyttäminen CMOS-prosessiin sisältää useita haasteita, joista esimerkkeinä matalat transistoreiden läpilyöntijännitteet ja pienen Q-arvon suurikokoiset piille integroidut kondensaattorit ja kelat. Perinteisesti MOS-transistoreiden matalat läpilyöntijännitteet on ratkaistu kytkemällä useita transistoreita kaskadikytkentään pääteasteessa.

Jännitettä laskeva DC-DC-muunnin koostuu puolisillasta, jossa yläpuolen PMOS-kytkinelementtiä ja alapuolen NMOS-kytkinelementtiä ohjataan päälle ja pois signaaleilla, joiden käyttöjakso määrittää muuntimen ulostulojännitteen. Ohjaussignaalit eivät saa kytkeä transistoreita samaan aikaan päälle oikosulkutilanteiden välttämiseksi, joten ohjaussignaalien välillä tulee olla lyhyt kuollut aika. Puolisillan PMOS- tai NMOS-kytkinelementtien matalien läpilyöntijännitteiden ratkaisemiseksi voidaan kytkeä useita transistoreita kaskadikytkentään, joka lisää haasteita yksittäisten transistorien ohjaamiseen, sillä niiden ohjausjännitteet toimivat eri jännitealueilla. Tämä ongelma voidaan ratkaista tasomuuntimilla, jotka muuntavat ohjaussignaaleita jännitealueiden välillä. Tasomuuntimien käyttö voi kuitenkin huonontaa DC-DC-muuntimen kokonaishyötysuhdetta ajastusviiveiden ja tehonkulutuksen kautta.

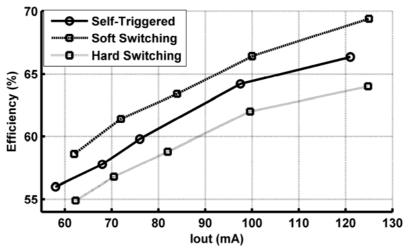

Tasomuuntimissa esiintyvien ongelmien ohittamiseksi tässä työssä esitellään itseliipaiseva laskeva DC-DC-muunnin. Tässä muuntimessa puolisillan yläpuolen kytkimen ohjaussignaali tuotetaan induktiivisella takaisinkytkennällä muuntimen ulostulosta. Induktiivisen takaisinkytkennän käyttö poistaa tasomuuntimien tarpeen yläpuolen kytkinelementin ohjauksessa, sekä on samanaikaisesti nopeavasteinen ja mahdollistaa muuttuvan kuolleen ajan ohjauksen ilman ylimääräisiä komponentteja. Ulostulojännitteen ohjaus toteutetaan muuttamalla alapuolen kytkinelementin ohjaussignaalin käyttöjaksoa. Ehdotetun DC-DC-muuntimen simulointi on tehty Cadencen 45 nanometrin CMOS General Process Design Kit (GPDK) -työkalulla, joka antaa itseliipaisevan DC-DC-muuntimen hyötysuhteeksi 64.25 %. Tätä tulosta verrataan ilman kuollutta aikaa käytettävän DC-DC-muuntimen simulaatiotuloksiin, jotka antavat hyötysuhteeksi sen 63.21 %, jossa ei ole mukana tasomuuntimissa esiintyvien viiveiden ja tehonkulutuksen vaikutuksia. Itseliipaiseva DC-DC-muunnin tuottaa  $1.5V \pm 20mV$

ulostulojännitteen 100mA  $\pm$  3mA kuormavirralla 3V-3.6V sisäänmenojännitteestä 360 MHz kytkentätaajuudella. Todellisen käyttäymisen mallintamiseksi työssä on totetuttu DC-DC-muuntimen piirileiska, josta lopulliset simulaatiot voidaan suorittaa piirin parasiittisten komponenttien kanssa. DC-DC-muunnin on rakennettu kokonaisuudessaan 1.73 x 1.62 mm piialueelle kytkinkomponenttien, muuntajan, ohituskondensaattorin sekä juotospisteiden kanssa.

## ABSTRACT

TAMPERE UNIVERSITY OF TECHNOLOGY

Master's Degree Programme in Electrical Engineering

Rehman Akbar: High Speed Fully Monolithic Self-Triggered DC-DC Converter

Masters of Science Thesis, 56 pages and 9 Appendix pages

December 2013

Major: Electrical Engineering

Supervisor: Prof. Nikolay T. Tchamov, Ph. D

Examiners: Prof. Nikolay T. Tchamov and Jani Järvenhaara

Keywords: DC-DC converter, dead time, CMOS, 45nm

The integration of DC-DC converter in standard CMOS process faces challenges from the low transistor breakdown voltages, poor quality factor and large size on-chip capacitors and inductors. The standard solution to deal with the problem of MOS transistor's low breakdown voltage is using cascode configuration in the output stage.

High-side PMOS and low-side NMOS power transistors in on-chip buck converter are switched ON and OFF with non-overlapping driving signals whose dutycycle regulate the output voltage of converter. The non-overlapping driving signals are required to avoid short-circuit losses through power transistors. By using the cascode configuration, driving signals for high-side PMOS and low-side NMOS power switching transistors operate in different voltage domains. To overcome this problem, the voltage level shifters are needed to transfer driving signals between two voltage domains. However, associated power losses and additional timing delays in conventional level shifters may deteriorate the overall efficiency of converter

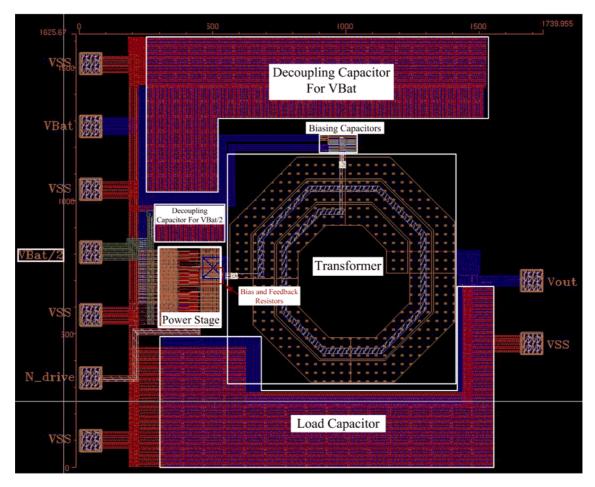

In order to avoid the losses and timing delays associated with the level shifters, a self-triggered buck converter is proposed in this work. The high-side driving signal is generated from the converter output via inductive feedback. The inductive feedback eliminates the required level shifters needed for transferring the driving signal to highside power transistor. The inductive feedback has fast response and provides adaptive dead-time that avoids short circuit losses with no additional hardware. Output voltage regulation is realized by controlling the duty-cycle of the signal switching the low-side NMOS transistor. Simulations are done on Cadence 45nm CMOS General Process Design Kit(GPDK) and show that the efficiency of self-triggered converter (64.25%) is better than the efficiency of a hard-switching buck converter(63.21%), even when the level shifter losses and delays are not taken into account. The converter generate output voltage  $\sim 1.5V \pm 20mV$  and average load current 100mA  $\pm$  3mA from 3V-3.6V input at a switching frequency of 360MHz. In order to closely match real circuit behavior, layout is made and final simulations are carried out with extracted layout and PCB Parasitics. The converter is fully integrated with 1.73×1.62[mm×mm] area on silicon including power stage, transformer, decoupling capacitors and pads.

## PREFACE

The research work presented in this thesis was done at the RFIC Laboratory, Department of Electronics and Communications Engineering, Tampere University of Technology (TUT). It is the continuation of a project with our industry partner Infineon Technology AG, who financially supported the research developments.

During the one-year period, I have received a lot of help from my supervisor and colleagues in our group. Foremost, I would like to thank Prof. Nikolay T. Tchamov for providing me the great opportunity to work in his research group. I also would like to thank my direct consultants Jani Järvenhaara and Faizan-Ul-Haq for his unconditional help. Meanwhile, I want to thank all other team members of RFIC Laboratory for the excellent work environment we have created together.

Finally yet importantly, I would like to thank my parents for their continuous support and inspiration, which have been the main source of motivation during my M.Sc. study.

Tampere, June 2013

Rehman Akbar Mekannikanpolku 6 A, 13 33720 Tampere FINLAND Tel. +358 44 970 8368

# LIST OF FIGURES

| Figure 1-1: Battery operated applications with DC-DC Converters.                                                | 1   |

|-----------------------------------------------------------------------------------------------------------------|-----|

| Figure 1-2: Off-chip standard buck converter                                                                    | 2   |

| Figure 1-3: implementation of buck converter with cascoded transistor structure                                 | 2   |

| Figure 2-1: Lumped model of the physical connection between battery and chip                                    |     |

| mounted on PCB.                                                                                                 | 5   |

| Figure 2-2: (a) Model of Linear voltage regulator. (b). A feedback varies the voltage a                         | at  |

| the gate of the series transistor (which is act as variable resistor) by comparing the                          |     |

| output voltage $V_{out}$ with the reference voltage $V_{Ref.}$                                                  | 7   |

| Figure 2-3: concept of capacitive conversion from charge point of view                                          | 8   |

| Figure 2-4: Charging of capacitor                                                                               |     |

| Figure 2-5: Schematic representation of Charge-Pump converter (Vout = $2 \times Vin$ )                          |     |

| Figure 2-6: (a) standard Buck Converter                                                                         |     |

| Figure 2-7: nominal steady-state waveforms of inductor current, output voltage and at                           |     |

| V <sub>x</sub> node                                                                                             |     |

| Figure 2-8: circuit model for parasitic impedances of buck converter.                                           |     |

| Figure 2-9: Short circuit Losses                                                                                |     |

| Figure 2-10: Body Diode Conduction                                                                              |     |

| Figure 2-11: ZVS (soft switching) waveforms                                                                     |     |

| Figure 2-12: standard buck converter with cascode connection.                                                   |     |

| Figure 3-1: Self-oscillating converter topology                                                                 |     |

| Figure 3-2: the proposed self-triggered converter                                                               |     |

| Figure 3-3: pulse forming block                                                                                 |     |

| Figure 3-4: (a) Close up of $V_{\text{Lsec}}$ at different $R_{fb}$ values (b) Effect of changing $R_{fb}$ on t |     |

|                                                                                                                 |     |

| Figure 3-5: simulated waveforms of self-triggered converter                                                     |     |

| Figure 3-6: Transformer Geometry from FastHenry                                                                 |     |

| Figure 3-7: $L_{pr}$ and $L_{sec}$ suspended in dielectric above substrate                                      |     |

| Figure 3-8: The Maxwell Capacitance Matrix                                                                      |     |

| Figure 3-9: Model of Transformer                                                                                |     |

| Figure 4-1: Self-triggered DC-DC converter                                                                      |     |

| Figure 4-2: PMOS power transistor width Vs. Efficiency ( $W_{\rm NMOS} = 1/2 W_{\rm PMOS}$ )                    |     |

| Figure 4-3 : Frquency vs. Efficiency.                                                                           | .28 |

| Figure 4-4: from (a)-(d) simulation setup for Quality factor of transformer. (e)                                |     |

| Simulation setup for coupling factor K.                                                                         | .29 |

| Figure 4-5: (a) Quality factor of primary and secondary winding, when other side                                |     |

| winding short-circuit respectively. (b) Quality factor of primary and secondary windin                          | ng. |

| when other side winding open-circuit respectively                                                               |     |

| Figure 4-6: K-factor Vs. Frequency.                                                                             |     |

| Figure 4-7: NMOS Cascaded gate driver.                                                                          |     |

| Figure 4-8: Pulse Forming Block                                                                                 |     |

| Figure 4-9: Test Bench of self-triggered converter                                                              |     |

| Figure 4-10: simulated waveforms with ideal components.                                                         |     |

| Figure 4-11: Fine adjustment of the $M_{1G}$ duty-cycle via the feedback resistance $R_{fb}$ (a)                |     |

| input voltage of the Pulse-Forming Block (b) M1G signal (c) effect on the VX node                               |     |

| voltage                                                                                                         | .34 |

| 6                                                                                                               |     |

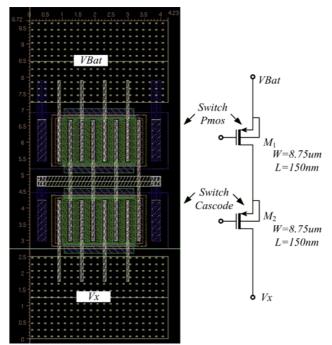

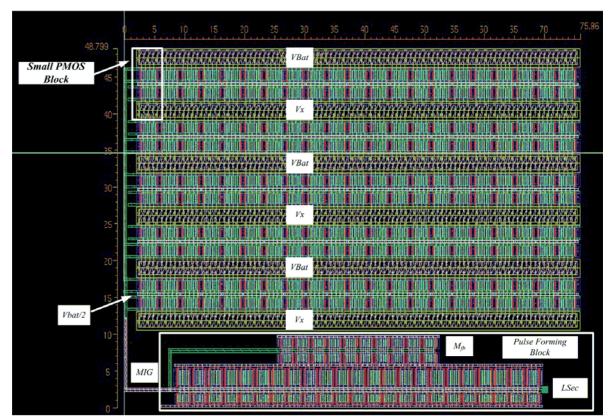

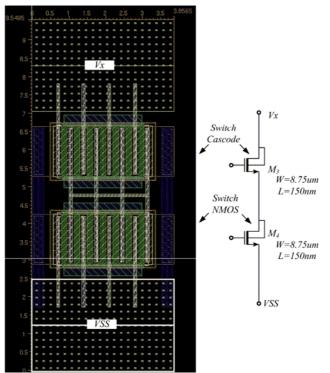

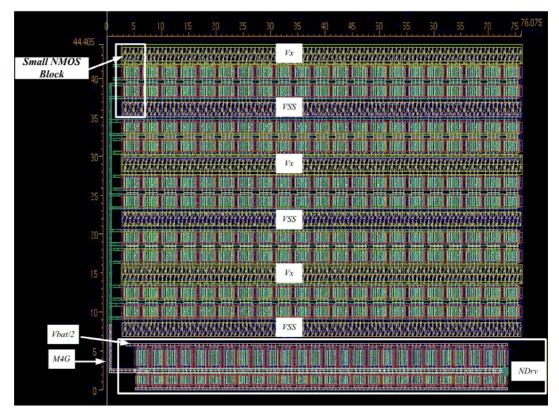

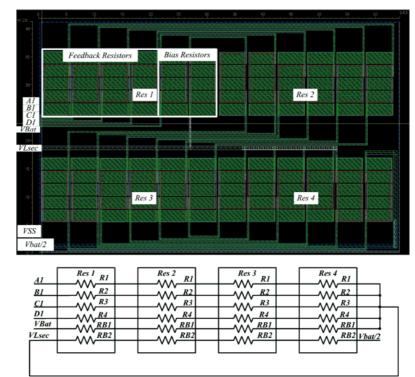

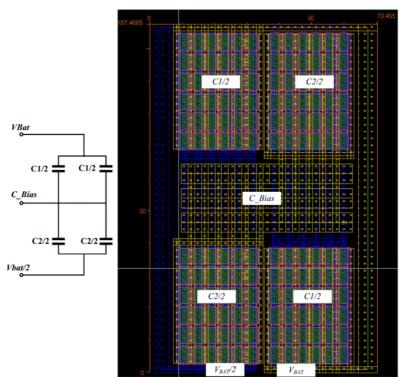

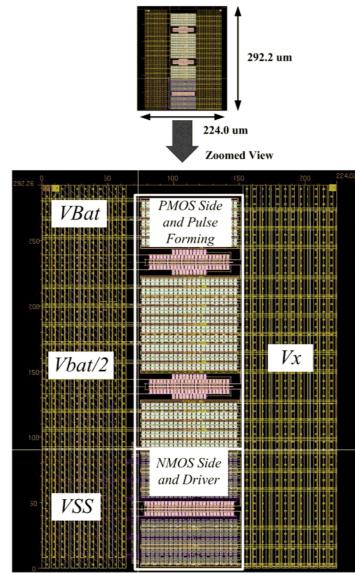

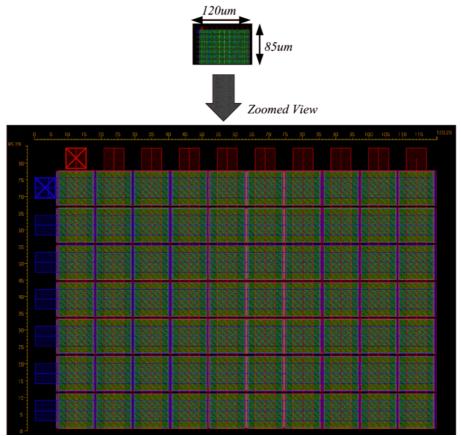

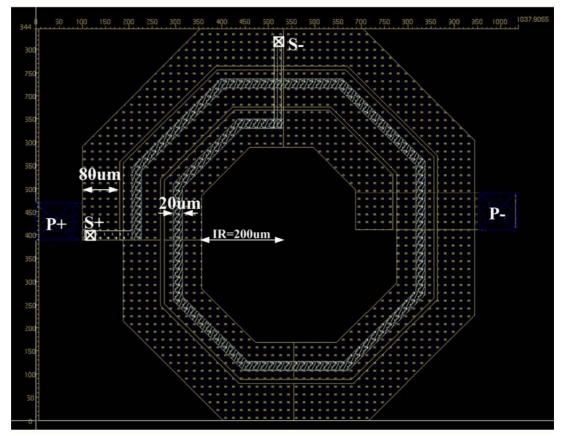

Figure 5-1: The floor plan of proposed converter. I/O pins are placed on both sides and power stage is surrounded by transformer and decoupling capacitors to minimize their Figure 5-2: A segment of cascaded Pmos transistors. The size is 4.23x9.7 [umxum].7 fingers with 1.25um width are used for each transistor to decrease the gate resistance. The interconnections between cascaded Pmos transistors are minimized by putting both Figure 5-3: A unit cell of cascoded PMOS transistor with enabled pulse forming buffer and feedback transistor  $M_{fb}$ . It consists of 21 identical PMOS segments, which makes an overall transistor width of 183.5µm. The overall size is 48×75 [µm×µm]. The pulseforming buffer is place under each transistor cell to minimize their interconnections...38 Figure 5-4: A segment of cascaded Pmos transistors. The size is 3.8x9.5 [umxum].7 fingers with 1.25um width are used for each transistor to decrease the gate resistance. The interconnections between cascaded Pmos transistors are minimized by putting both Figure 5-5: A unit cell of cascoded NMOS transistor with enabled gate driver. It consists of 21 identical PMOS segments, which makes an overall transistor width of 183.5 $\mu$ m. The overall size is 44×76 [ $\mu$ m× $\mu$ m]. The gate driver is place under each Figure 5-6: Feedback and Biasing Resistors of pulse forming circuit. It consists of 4 Figure 5-7: Biasing Capacitors of pulse forming circuit. Layout is formed in common Figure 5-8: Power stage of proposed self-triggered converter. The upper picture shows the size of the power stage in the floor plan and the lower picture shows its zoomed view. The PMOS transistor consists of 4 unit PMOS transistor cells, resulting in a total transistor width of 3.675mm. The NMOS transistor has 2 unit NMOS transistor cells, which makes a total transistor width of 1.8375mm The overall size of the power stage is Figure 5-9: A unit cell of PMOS capacitor. The upper picture shows the size of the unit capacitor cell in the floor plan and the lower picture shows its zoomed view. The unit cell consists of 100 PMOS transistor with 10µm gate width and 10µm gate length, which gives a total capacitance of 95pF. The overall size of the unit PMOS capacitor Figure 5-10: the transformer generated by Virtuoso Passive Component Designer. The metal width is 80µm with 10µm distance between adjacent turns. The number of turns is set to 2.5 so that its pins are shifted by 180 degrees, which minimizes the interconnections between the primary inductor and the output pin. The secondary winding has 20µm with 78µm sapacing between adjacent trace. The overall transformer Figure 5-11: Layout of proposed synchronous buck converter. It is designed according to the floor plan. Input, driving signals, and biasing voltage pins are placed on the left side. Output pin is placed on the right side to minimize the distance between the inductor and the load. The overall converter consumes a total silicon area of

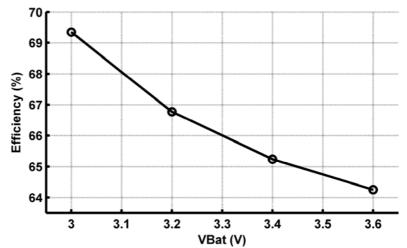

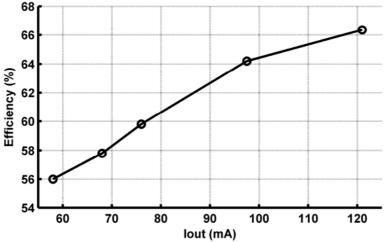

| Figure 6-5: Line regulation of Self-triggered DC-DC Converter. ( $V_{BAT} = 3-3.6V, f_s =$ |                |

|--------------------------------------------------------------------------------------------|----------------|

| $360 \text{MHz}, R_L = 15 \Omega$ )                                                        | 50             |

| Figure 6-6: Load Regulation of Self-triggered DC-DC Converter. ( $V_{BAT} = 3.6V, f_s =$   |                |

| $360 \text{MHz}, R_L = 15 \Omega$ )                                                        | 50             |

| Figure 6-7: Standard Buck Converter Schematic                                              | 51             |

| Figure 6-8: Efficiency comparison between hard-switching buck converter, Soft-             |                |

| switching buck converter, and Self-Triggered converter ( $V_{BAT} = 3.6V, f_s = 360MHz, R$ | $\mathbf{R}_L$ |

| $= 15\Omega$ )                                                                             | 51             |

# CONTENTS

| ABSTR    |                                                 | Ĭ  |

|----------|-------------------------------------------------|----|

| PREFA    |                                                 | IV |

| LIST O   | F FIGURES                                       | V  |

| ABBRE    | EVIATIONS                                       | IX |

| 1        | Introduction                                    | 1  |

| 2        | Background                                      | 4  |

| 2.1      | Static Characteristics                          | 4  |

| 2.2      | Dynamic Characteristics                         | 6  |

| 2.3      | DC-DC Converter Types                           | 6  |

| Lir      | near Voltage Converter                          | 7  |

| Ch       | arge-Pump DC-DC converter                       | 7  |

| Inc      | luctive Type DC-DC converters                   | 9  |

| 2.4      | Standard Buck Converter                         | 10 |

| 2.5      | Zero Voltage Switching                          | 15 |

| 2.6      | Cascode Structure                               | 16 |

| 2.7      | Voltage Level Shifter                           | 17 |

| 3        | Self-Triggered DC-DC Converter                  | 18 |

| 3.1      | Self- oscillating Converter                     | 18 |

| 3.2      | Self-Triggered Converter                        | 19 |

| 3.3      | Transformer Design for Self-Triggered Converter | 22 |

| 4        | Design and Simulations                          | 27 |

| 4.1      | Power Transistor Sizing                         | 27 |

| 4.2      | Switching Frequency                             | 28 |

| 4.3      | Transformer Design Simulations                  | 29 |

| 4.4      | NMOS gate driver design                         | 30 |

| 4.5      | Pulse Forming Block                             | 31 |

| 4.6      | Simulation Results                              | 32 |

|          | aveform analysis                                | 32 |

|          | nulated conversion efficiency                   | 34 |

| 5        | Layout Design                                   | 35 |

| 5.1      | Layout design guidelines                        | 35 |

| 5.2      | Floor plan                                      | 35 |

| 5.3      | Layout design                                   | 36 |

| 6        | Measurement Setup and Post-Layout Simulations   | 45 |

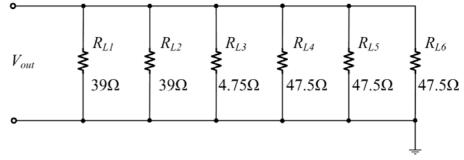

| 6.1      | Load resistor calculations                      | 45 |

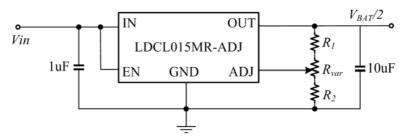

| 6.2      | LDCL015 voltage regulator for biasing           | 45 |

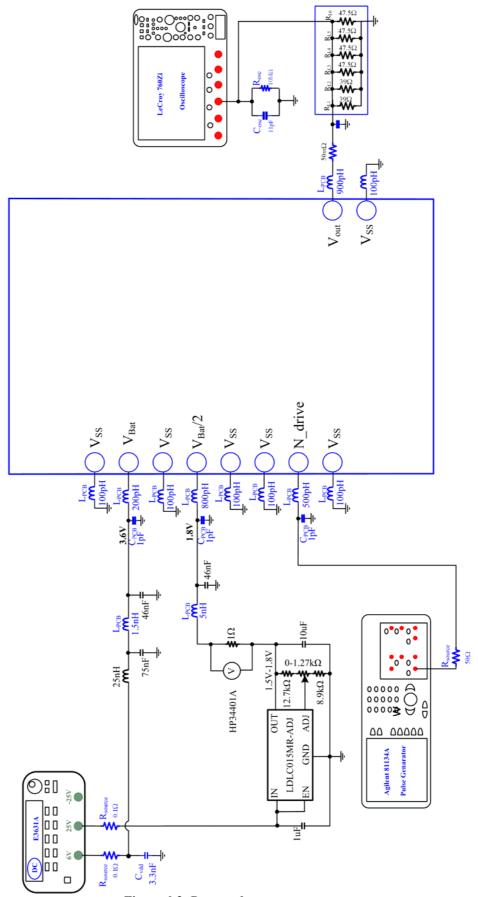

| 6.3      | Measurement setup                               | 46 |

| 6.4      | Post-Layout Simulations                         | 49 |

|          | ne Regulation                                   | 49 |

|          | ad Regulation                                   | 50 |

|          | mparison between Standard Buck Converter        | 50 |

| 7        | Conclusion and Discussion                       | 53 |

| Refrenc  |                                                 | 54 |

| Append   |                                                 | 57 |

| Append   |                                                 | 65 |

| - PP CHO |                                                 | 02 |

# ABBREVIATIONS

| DC-DC       | Direct-Current to Direct-Current        |

|-------------|-----------------------------------------|

| CMOS        | Complementary Metal Oxide Semiconductor |

| MOS         | Metal-Oxide-Semiconductor               |

| IC          | Integrated Circuit                      |

| PWM         | Pulse Width Modulation                  |

| $t_{ m LH}$ | Dead Time at Low-to-High transition     |

| $t_{ m HL}$ | Dead Time at High-to-Low transition     |

| ZVS         | Zero Voltage Switching                  |

| NMOS        | N-type Metal Oxide Semiconductor        |

| PMOS        | P-type Metal Oxide Semiconductor        |

| VPCD        | Virtuoso Passive Component Designer     |

| LVS         | Layout vs. Schematic                    |

| DRC         | Design Rule Check                       |

| PCB         | Printed Circuit Board                   |

| Esr         | Effective series resistance             |

## 1 Introduction

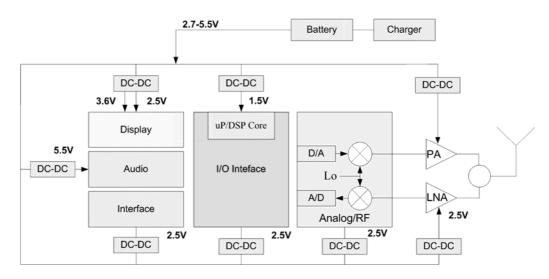

The possibility to integrate multiple electronic blocks in standard CMOS processes has resulted in battery powered portable electronic systems. However, batteries have an inherent problem of variable output voltages. As performance of electronic blocks in integrated circuits is dependent on fixed supply voltage, using a variable output voltage of batteries directly as power supply of these circuits can change the performance level of these blocks. Furthermore, different electronic block may require different power supply voltages for proper operation. Therefore, to generate these different supply voltages from single battery source, electronic circuits called as Direct-Current-to-Direct-Current (DC-DC) converters are required. See Figure 1-1.

Among the battery technologies, lithium batteries are widely used as energy source for portable devices due to compact in size, high energy storage density and low self-discharging. However, the lithium battery provides unregulated voltage varies from 2.8V-4.2V [13]. In Figure 1-1, shows system architecture where several voltage converters generate the regulated supply voltages required by different electronic application blocks from this unregulated lithium battery input voltage.

Figure 1-1: Battery operated applications with DC-DC Converters.

Standard CMOS Processes demands greater amounts of current at lower supply voltages from external battery source. For efficient delivery of power to advanced integrated circuits, board-level (PCB) voltages should be high. Distributing power at a higher voltage to the input pads of an integrated circuit reduces the supply current. At a reduced power supply current, resistive voltage drop and parasitic power dissipation of the off-chip power distribution network is reduced, thereby enhancing the energy efficiency and quality of the distributed voltage. Once the required energy reaches the

#### 1 Introduction

input pads of integrated circuit, a monolithic DC-DC converter can generate a lower supply voltage for particular application circuit.

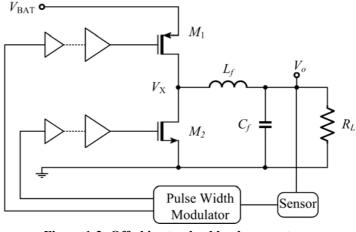

Figure 1-2: Off-chip standard buck converter

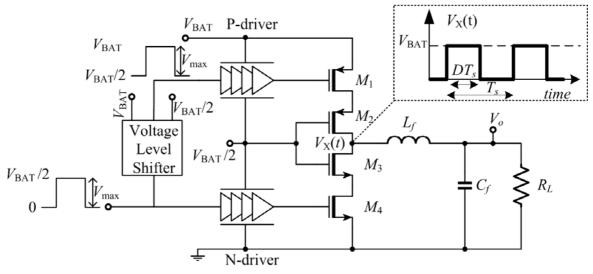

Due to advantages of high voltage power delivery on PCB and monolithic DC-DC conversion for standard CMOS process integrated circuits, leads to new challenges. The maximum battery voltage applies to the standard buck converter in Figure 1-2 is limited due to transistor's maximum gate-oxide breakdown voltage of standard CMOS processes. Therefore, standard switching DC–DC converter topology is not suitable for future high performance integrated circuits. To attain high voltage conversion ratio from monolithic DC-DC converter, cascoded transistor structure is appropriate [2]. Cascoded transistor structure shown in Figure 1-3(a) can operate at input voltage higher ( $V_{BAT}=2V_{max}$ ) than maximum transistor allowed gate-oxide breakdown voltage ( $V_{max}$ ).

Figure 1-3: implementaion of buck converter with cascoded transistor structure

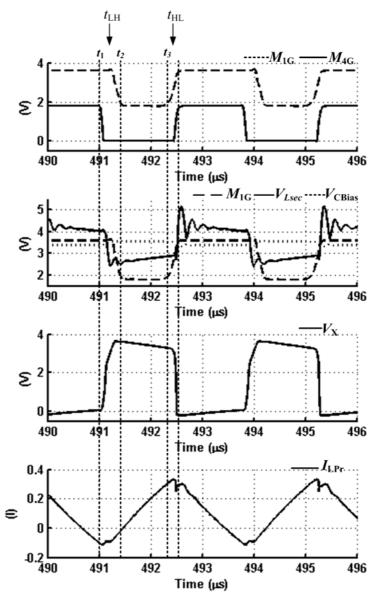

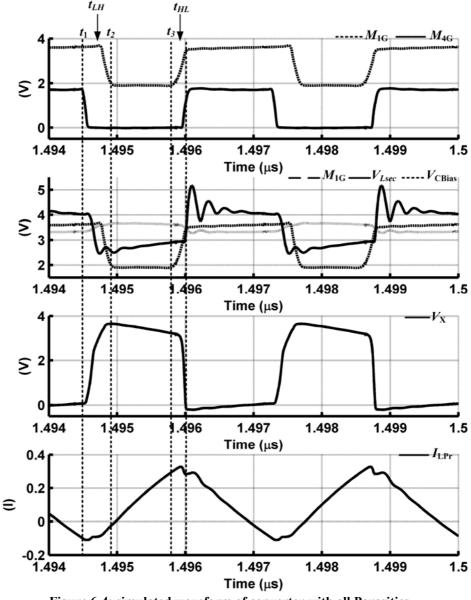

The P-driver and the N-driver form the switching signals  $M_{1G}$  and  $M_{4G}$  applied to the gates of  $M_1$  and  $M_4$  respectively. The waveforms of  $M_{1G}$  and  $M_{4G}$  are shown in Figure 1-3 (b), where  $t_{\text{HL}}$  and  $t_{\text{LH}}$  are intentionally introduced dead-times between the driving pulses, which assure no short-circuit currents through the transistor chain  $M_1-M_2-M_3-M_3$

#### 1 Introduction

$M_4$ . However, switching signals  $M_{1G}$  and  $M_{4G}$  are operating in two different voltage domains. The transfer of switching signals between different voltage domains requires level shifters. By adding level shifter, we introduce additional power losses and delays in the switching signal that affect the efficiency of buck DC-DC converter.

The integration of buck DC-DC converter, however, imposes a challenge On-chip integration of inductors and capacitors are required for energy storage and output signal filtering. These integrated capacitors/inductors become impractical above certain values due to the tight area constraints required by integrated circuits. Another significant issue with integrated inductors is the poor quality factor that can degrade the efficiency of a DC-DC converter. The physical size, value and parasitic impedances of inductors and capacitors can reduce by increasing switching frequency of DC-DC converter. By increasing switching frequency, the converter efficiency decreased dramatically[2]. A reduction the switching losses can be achieved by using fast MOS devices and implementing Zero-Voltage Switching (ZVS) techniques. The ZVS technique requires tight control of the dead-times  $t_{HL}$  and  $t_{LH}$ , which should be adaptive in order to provide appropriate switching instant under load and input voltage variations.

Recent researches have tried to overcome some of the above technical limitations. New innovative techniques in [14], [15], [16], [17] are reported for integration of DC-DC converters for low voltage applications at high switching frequencies.

This thesis proposes a new technique for integrated buck converter. Which describe the issues related to voltage level shifter in standard buck converter and gave solution, how self-triggered buck converter topology eliminates the need of voltage level shifter and their related issues. In addition, the self-triggered converter has better efficiency than standard buck converter even we do not include the voltage level shifter losses.

The background theory and characteristics of synchronous DC-DC buck is presented in Chapter 2. Chapter 3 is dedicated on the operation of the proposed self-triggered converter. The converter design procedure and pre-layout simulation results are depicted in Chapter 4. Chapter 5 gives the layout design procedure of the proposed converter. Chapter 6 gives an example of measurement setup for the designed buck converter as well as the post-layout simulation results and compare the Self-triggered converter results with standard buck converter in hard and soft switching mode. Chapter 7 concludes the thesis.

## 2 Background

As explained in chapter one, devices requiring certain degree of user mobility e.g. cell phones, laptops etc. are normally operated by batteries. Most of the devices used Li-ion batteries as a power source having nominal output voltages of 3.6V [1]. However, the electronics circuits inside the portable devices need different supply voltages e.g. 1.5V, 1.8V, 4.2V, 5V etc. these different voltages need to be generated from single battery. See Figure 1-1 [6]. Furthermore, variable battery output voltages under charged/discharged conditions can change the overall performance of electronic block. Therefore, portable electronic circuits must posses a circuit that converts variable battery voltage into constant voltages for different power domains inside the IC. Electronic circuits that perform this DC voltage conversion are known as DC-DC converters.

There are two major types of DC-DC converters, Linear and Switched-mode (Inductive and Capacitive) converter. Switching DC-DC converters are widely used among these topologies due to high efficiency, good voltage regulation and ability to provide high load currents. A switching DC–DC converter that generates a higher output supply voltage compared to the input supply voltage is knows as boost converter. Alternatively, a switching DC–DC converter that generates a smaller output supply voltage as compared to the input supply voltage is known as buck converter. Before going into details of converter types let us first analyze the requirements and characteristics of converter. The DC-DC converter characteristics are divided into two main categories: static and the dynamic characteristics [6].

### 2.1 Static Characteristics

Static characteristics are mainly describing the nature of converter in steady-state regime. This is related to the converter stage itself and to the control technique used by the converter [6]. The main characteristics are:

**Voltage Conversion Ratio:** is the ratio between output voltage and the input voltage of the converter stage.

$$VCR = \frac{Vout}{Vin}$$

(2-1)

For voltage conversion ratio *VCR* is greater than one, DC-DC converter is known as step-up converter. While for *VCR*, less than one, DC-DC converter is called as step-down converter.

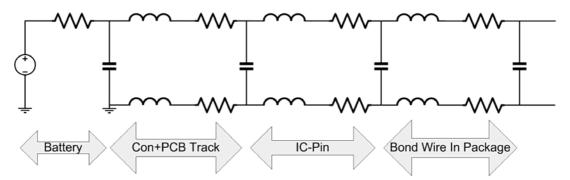

**Noise:** Ideally, voltage source has zero output impedance and provides the noise free constant DC supply regardless of output current. However, practically voltage source has some output impedance and parasitic components from source to load. These parasitic components also add to output impedance of voltage source as shown in Figure 2-1. When the varying current flows through the RLC lumped component model of interconnection between voltage source and load then voltage source turned into DC+AC source. The additional AC is known as input noise. Usually, decoupling capacitors are used to reduce the input noise.

Figure 2-1: Lumped model of the physical connection between battery and chip mounted on PCB.

Efficiency  $\eta$  A primary factor that determines the quality of a DC–DC converter is the output voltage regulation i.e. the stability of the output voltage over a wide range of input voltages and load currents. The output voltage drop and peak-to-peak output voltage ripple under changing conditions of the load current and input voltage characterizes the output stability of voltage regulator. Another important factor that determines the quality of a DC-DC converter is the energy efficiency of the voltage conversion process. The parasitic impedances of a DC–DC converter dissipate a specific amount of energy in order to generate a supply voltage. The choice of DC–DC conversion topology and related circuit techniques for a specific application is critical to the energy efficiency of the voltage conversion process. The energy efficiency of DC– DC converter is:

$$\eta = \frac{P_{out}}{P_{in}} \tag{2-2}$$

Where *Pout* is output power supplied to the load and *Pin* is total supplied power. The power consumed by parasitic components in the voltage Converter is:

$$P_{lost} = pin - pout = pout(\frac{1}{\eta} - 1)$$

(2-3)

### 2.2 Dynamic Characteristics

The dynamic characteristics are describing the nature of converter stage as by the control method of the DC-DC converter. The most fundamentals characteristics are as follow:

Line Regulation is a measure of the variation in the output voltage by changing the input voltage of converter. The variation is not necessarily linear over the whole input range [6] therefore line regulation can be calculated at two different input voltages (minimum and maximum input) and output voltages according to input and normalize this variation with respect to line variation describe as:

Line Regulation =

$$\frac{V_{out,in2} - V_{out,in1}}{V_{in2} - V_{in1}} \times 100\%$$

(2-4)

**Load Regulation** is a measure of the variation in output voltage at different output currents. The output voltage variation is not necessarily linear over the whole load range [6]. Therefore, output variation can be calculated for the maximum and minimum load current as follow:

Load Regulation =

$$\frac{V_{out, I_2} - V_{out, I_1}}{I_2 - I_1} \times 100\%$$

(2-5)

**Bandwidth:** of the DC-DC converter describes how fast is the transient response of the converter with changes in load, line and control-signal. This feature can be tested by changing load from minimum to maximum with a predefined rise/fall time [6].

**Overshoot and Undershoot:** is the deviation from the nominal output voltage due to transient in load-line or control. It should be exactly specified under which circumstances and operating points the overshoot and undershoot occurs.

## 2.3 DC-DC Converter Types

Several methods exist to achieve DC-DC voltage conversion from kilowatt range to few watts. Each topology having its own advantages and disadvantages. Main interest of this work is battery operated monolithic high speed switching buck DC-DC converter. The discussion on converter topologies limited to Integrated DC-DC converters in the following sections. The main two topologies are Linear and switched-mode converters.

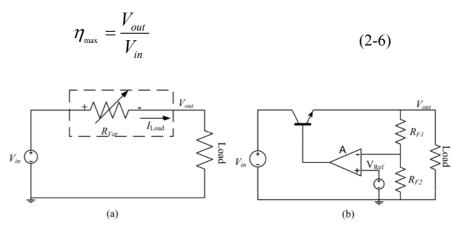

#### Linear Voltage Converter

Linear voltage converters are popular due to simple structure and well suited for monolithic integration due to simple in nature. Linear DC-DC converters operate on the principle of resistive voltage division. The operation of simple linear converter is illustrated in Figure 2-2(a). A variable resistor  $R_{var}$  lowering  $V_{in}$  to  $V_{out}$  and  $I_{Load}$  is equal to current drawn by the primary source  $V_{in}$ . The maximum efficiency  $\eta_{max}$  attained from Ideal linear voltage regulator is,

Figure 2-2: (a) Model of Linear voltage regulator. (b). A feedback varies the voltage at the gate of the series transistor (which is act as variable resistor) by comparing the output voltage  $V_{out}$  with the reference voltage  $V_{Ref}$ .

Therefore, the linear converter can offer high efficiency if voltage conversion ratio is small. For the high conversion ratio, the efficiency becomes small. Therefore, the switched-mode DC-DC converter topologies emerge, where high conversion ratio needed [1].

#### **Charge-Pump DC-DC converter**

Charge-Pump or switched-capacitor converter can generate different DC output voltage of different magnitude and/or opposite polarity compared to input voltage supply [11]. On-chip charge-pump converters are widely used in supply analog mixed signal circuits, non-volatile flash memories [11].

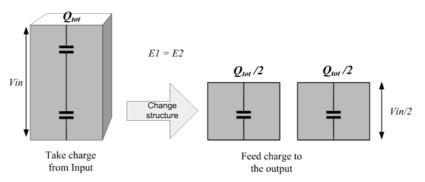

#### a) Charge Transfer

Charge-Pump converter utilizes capacitor to transfer charge from the input to the output of the converter. Figure 2-3 demonstrates the concept of charge-pump converter that divide the input voltage by two. Both structures contain equal amount of charge. The first state store charge is in series while second one in parallel connected capacitors.

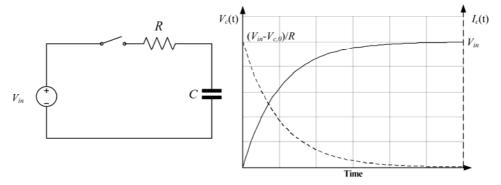

In charge-pump converter energy transfer from input to the load by means of single capacitor is modeled as charging capacitor by supply voltage through resistor in Figure 2-4. The process of charging the capacitor is described by the following equation:

#### 2 Background

$$V_{in} + RC\frac{dV_c}{dt} + V_c = 0$$

(2-7)

By solving the equation 2.6 for  $V_c(t)$  and current through capacitor  $I_c(t)$  the following expression are given:

Figure 2-3: concept of capacitive conversion from charge point of view.

$$V_{c}(t) = V_{in} - (V_{in} - V_{c,0})e^{-\frac{t}{RC}}$$

(2-8)

$$I_{c}(t) = \frac{I_{in} + I_{c,0}}{R} e^{-RC}$$

(2-9)

Figure 2-4: Charging of capacitor

Moreover, Energy added to the capacitor by means of this process:

$$E_c = \frac{(V_{dd}^2 - V_{c,0}^2)}{2}C$$

(2-10)

In addition, total energy delivered by the voltage supply source can be calculated as:

$$E_{tot} = V_{in} (V_{in} - V_{c,0})C$$

(2-11)

The part of the energy is loss due to resistor *R*,  $V_{c,0}$  is the voltage across Capacitor *C* at time zero. The charging efficiency  $\eta_{c,charge}$  can be quantified by [1]:

$$\eta_{c,Ch\,\mathrm{arg}\,e} = \frac{1}{2} \frac{V_{c,0} + V_{in}}{V_{in}} \tag{2-12}$$

The equation 2.11 demonstrates that efficiency of charging capacitor depends upon ratio of initial voltage and charging voltage. It is also clear that even when capacitor has no series resistance, the power loss will occur. To increase the charging efficiency the voltage difference between initial and final charging voltage should be small. Equation (2-9) demonstrates that if voltage difference is small the energy transfer is small. For high transfer of energy, result in large capacitors.

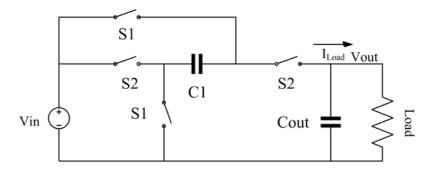

The operation of charge-pump converter circuit shown in Figure 2-5 works in the following manner. There are two switching networks S1 and S2 are controlled by two-phase control signals. Switches controlled by phase 1 control signal are labeled by S1 and phase 2 with S2. As phase 1 switches are activated while Phase 2 switches are in cutoff mode. C1 is charged to Vin, then output current is supplied by Cout. Once C1 is charged to Vin as a results phase 1 switches are in cut off state and Phase 2 switches are activated. Because of this connection, Cout is charged to 2xVin [6].

Figure 2-5: Schematic representation of Charge-Pump converter (Vout = 2 x Vin)

The disadvantage of charge-pump converter is the poor efficiency characteristics, discrete output voltages and low output current as compared to inductive type switchmode converter. However, have better efficiency than linear converters with large voltage conversion ratio. Easy to integrate on silicon, small in size compared to other switched-mode converters and provide opposite polarity output voltages are the main advantages [1].

#### Inductive Type DC-DC converters

Instead of using the capacitors as storing element, Inductive type DC-DC converters utilize inductor as energy storage element and capacitor for filtering/smoothing output voltage and act as energy reservoir for the load, when converter is not delivering any power to the load. The charging of capacitor through inductor is more efficient than charging through voltage source [1]. Such converters are widely used is both low power and low voltage applications because of high efficiency. Inductive type DC-DC buck

converters will be discussed in detail in the next section. The comparison of three converter types is summarized in Table 2-1.

| Type of DC-DC Conversion       | Linear     | Charge-Pump  | Inductive Type   |

|--------------------------------|------------|--------------|------------------|

| Low-to-high voltage conversion | No         | Yes          | Yes              |

| High-to-low voltage conversion | Yes        | Yes          | Yes              |

| Polarity reversal              | No         | Yes          | Yes              |

| Efficiency                     | Low        | Low          | High             |

| Voltage regulation             | Poor       | Poor         | Good             |

| Output voltage Ripple          | low        | high         | high             |

| Area                           | Small      | Medium       | Large            |

|                                | DRAM,      | DRAM, flash, | Microprocessors, |

| Typical applications           | Voltage    | EEPROM, and  | DSPs, SRAM       |

|                                | References | mixed-signal | and hard disks   |

Table 2-1: Comparison Table of Converter Types

## 2.4 Standard Buck Converter

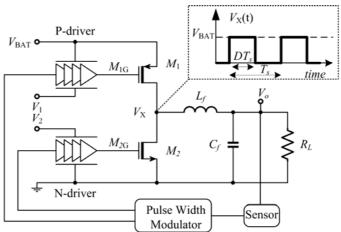

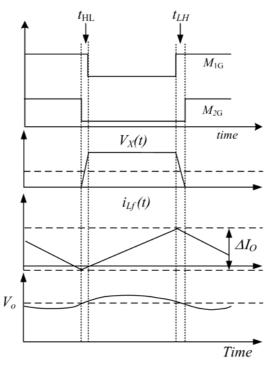

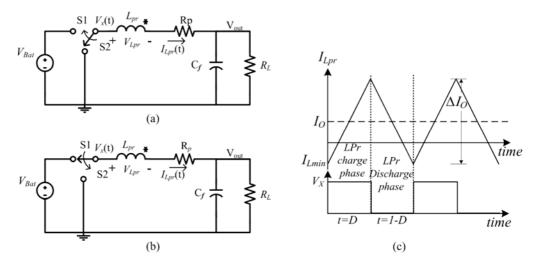

Buck converter is a standard switching DC-DC converter circuit topology with high efficiency and good output voltage regulation characteristics [15], [16], [21]. A buck converter circuit with the synchronous rectifier is shown in Figure 2-6. The operation of buck converter circuit is as follow. The power transistor  $M_1$  and  $M_2$  are switched ON and OFF with the feedback driving signal. This produce the rectangular wave of duty-cycle D and time period  $T_s$  at  $V_x$  node as shown in Figure 2-6. The rectangular pulses at  $V_x$  node is then applied to a second order filter composed of inductor and capacitor. Assuming the filter corner frequency is much smaller than the switching frequency  $f_s$  of the power transistors, the low pass filter passes DC component of the signal at  $V_x$  node and produce DC desired output voltage  $V_o$ .

Figure 2-6: (a) standard Buck Converter

Typically, power transistors have high input parasitic capacitances. To control the operation of power transistors, therefore,  $M_{1G}$  and  $M_{2G}$  are generated from series of gate drivers [5]. These gate driver buffers are typically tapered to drive these large capacitances. The gate drive buffers are controlled by PWM (pulse width modulated). Using feedback circuit, the PWM generates the necessary control signals for the power transistors  $M_1$  and  $M_2$  such that a rectangular pulses with an appropriate duty cycle is produced at  $V_X(t)$  as shown in Figure 2-7. During the operation of buck converter, duty-cycle may be modified in order to maintain the output voltage at desired value under variation of load current and input voltage.

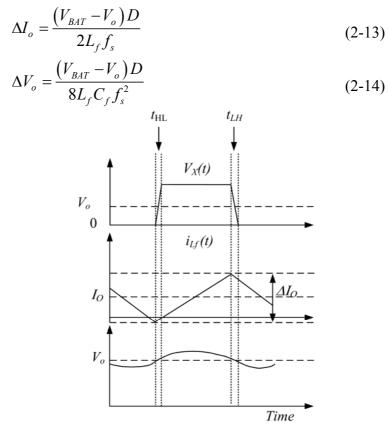

The inductor current  $I_{L_{J}}(t)$ , output voltage  $V_o$  and waveforms of buck converter are shown in Figure 2-7. The filter capacitance is chosen such that the series resistance of the capacitor is much smaller than load resistance. The AC component of the inductor current, therefore, passes through the filter capacitor while the DC component  $I_o$  passes through the load. The output voltage increases whenever the inductor current rises above  $I_o$ , as the filter capacitor is being charged. Similarly, the output voltage falls whenever the inductor current decreases below  $I_o$ , as the filter capacitor is being discharged. The expressions for the inductor ripple current  $\Delta I_o$  and amplitude of the output voltage ripple is [1]:

Figure 2-7: nominal steady-state waveforms of inductor current, output voltage and at V<sub>X</sub> node.

For a given battery, voltage  $V_{BAT}$ ,  $V_o$  is output voltage for duty-cycle *D* of switching frequency  $f_s$ .  $C_f$  and  $L_f$  are the output filter capacitor and inductor. Equation (2-12) and (2-13) illustrate the two principle means of miniaturizing a DC-DC converter. The physical size of filter components gets smaller as the switching frequency increases. Second, the requirement of good output voltage regulation with the small voltage ripple, which is possible with higher current ripple as a result of lowering the inductance of filter.

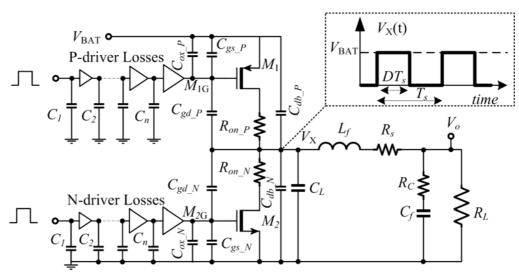

#### a) Main Losses in Buck Converter

The circuit model of buck converter in Figure 2-8 shows the main losses [22]. The power consumption of a buck converter is combination of the conduction losses caused by the parasitic resistive impedances while the switching losses due to the parasitic capacitive impedances of the circuit components.

**MOSFET Power Losses:** are due to series resistance while conduction and charging/discharging of parasitic capacitance related to transistors shown in Figure 2-8, in each switching cycle. The power loss due series resistance and parasitic capacitances are:

Figure 2-8: circuit model for parasitic impedances of buck converter.

$$P_{mos} = \frac{i_{rms}^2 R_{on}}{W} + E_g f_s W$$

(2-15)

$$E_{g} = \frac{\alpha}{1 - \alpha} \left( C_{OX} + C_{gs} + 2C_{gd} + C_{db} \right) V_{BAT}^{2}$$

(2-16)

Where W is width of transistor,  $\alpha$  is tapering factor of buffers,  $R_{on}$  is the equivalent series resistance of power transistors ( $R_{on}$ \_P or  $R_{on}$ \_N),  $i_{rms}$  is the *rms* current passing through the power transistors.  $C_{ox}$ ,  $C_{gs}$ ,  $C_{gd}$ , and  $C_{db}$  are the gate oxide, gate-to-source overlap, gate-to-drain overlap, and drain-to-body junction capacitances, respectively.

#### 2 Background

From equation (2-15), it is clear that W width of the transistor reduces the conduction losses but increases the switching losses. An optimum transistor width exists that minimize the total transistor power losses [22].

$$W_{opt} = \sqrt{\frac{R_{on}i_{rms}^2}{f_s E_g}}$$

(2-17)

$$P_{mos(\min)} = 2\sqrt{R_{on}i_{rms}^2 f_s E_g}$$

(2-18)

Filter Inductor Power Losses: are due to series resistance  $R_s$  and stray capacitance of filter inductor. Integrated planer spiral inductor losses are high due to poor quality factor [1]. But in recent years, novel low resistance inductors has been reported in [15]. The total power loss in filter inductor is [22]:

$$P_{ind} = b \left[ \frac{I_o^2}{\Delta I_o f_s} + \frac{\Delta I_o}{3f_s} + \frac{C_{Lf} V_{BAT}^2}{R_s \Delta I_o} \right]$$

(2-19)

$$b = \frac{(\Delta V_o) DR_s}{2}$$

(2-20)

Where  $C_{Lf}$  is stray capacitance and D is duty-cycle of switching signal.

**Filter Capacitor Power Losses:** Standard CMOS technology offers two options of onchip capacitors, MOM (metal-oxide-metal) and MOS capacitors. The MIM (metalinsulator-metal) capacitor requires additional processing steps [1]. Typically, MOM capacitance densities are in the range of 100 pF/mm<sup>2</sup> to1.5 nF/mm<sup>2</sup>. The benefits of MOM capacitors are their ability to withstand higher voltages than the nominal technology supply voltage, their potentially low parasitic series resistance and the possibility to place circuits underneath them. As a drawback, they have a low capacitance density. The second most used on-chip MOS capacitor have capacitance densities are in the range of 3 nF/mm<sup>2</sup> to 20 nF/mm<sup>2</sup> [1]. The main advantage of MOS capacitors is their high capacitance density. The draw back of MOS capacitor, they have high parasitic series resistance as compared to MOM capacitor. In General MOM capacitor offer parasitic series resistance of 200 m $\Omega$  to 300 m $\Omega$  (for area >1 mm<sup>2</sup>) and MOS capacitor offers 300 m $\Omega$  to 400 m $\Omega$ . However, high MOS capacitor densities save space on silicon. Which makes the MOS capacitor is optimum choice.

The losses in MOS capacitor are due to effective series resistance (esr)  $R_c$ . assuming the integrated capacitor is implemented with gate-oxide capacitance of transistor, the total power loss in filter capacitor is [22]:

#### 2 Background

$$P_{Cap} = df_s \Delta I_o \tag{2-21}$$

$$d = \frac{8R_c L_{Cap} C_o \Delta V_o}{3} \tag{2-22}$$

Where  $R_c$  is esr resistance of 1µm wide MOS transistor,  $L_{Cap}$  is channel length of transistor and  $C_0$  is gate–oxide capacitance of µm<sup>2</sup>.

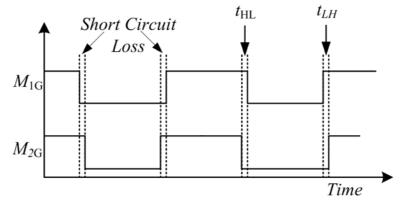

**Short Circuit Losses:** are related to simultaneous conduction of High-side PMOS and low-side NMOS. As in Figure 2-9 shows, if  $M_{1G}$  and  $M_{2G}$  driving signals switch ON power transistors without dead-time, the short-circuit path from VBAT to ground may exists temporarily. To avoid this condition, optimum dead-time introduce between driving signals.

Figure 2-9: Short circuit Losses

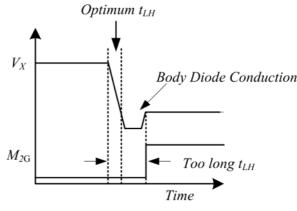

Figure 2-10: Body Diode Conduction

**Body Diode Reverse Recovery Losses:** are associated with the body diode conduction of switching transistors. To avoid short-circuit losses, we introduce dead-time between driving signal (both power transistors are OFF). If the dead-time is not optimum (too long) in Figure 2-10, the inductor reverse current will force the body diode of low-side NMOS (or High-side PMOS) to conduct. When transistor is turn ON, it removes the excess carrier charge from the body diode, dissipating an energy bounded by:

$$E_{rr} = Q_{rr} V_{BAT} \tag{2-23}$$

Where  $Q_{rr}$  is the charge stored in the body diode.

#### 2.5 Zero Voltage Switching

Typically, switching DC-DC converters have large inductive and capacitive storage components and power switches that occupy significant area and power. In order to achieve full integration of converter, the sizes of passive and active components of converter are reduced with higher switching frequency. Increasing switching frequency, also increase the power transistor switching losses given in equation (2-14). For reducing switching losses, ZVS (zero voltage switching) technique is often used.

Figure 2-11: ZVS (soft switching) waveforms

In ZVS scheme, filter inductor in Figure 2-8 used to charge/discharge the parasitic capacitances at  $V_X$  node in lossless manner, by providing the optimum dead-time between switching signal of  $M_1$  and  $M_2$ . If  $M_1$  or  $M_2$  are turned ON immediately after the  $V_X$  node charged or discharged by the filter inductor, the power transistor are switched to zero drain-to-source voltage difference (see Figure 2-11), thereby eliminating the switching power losses that would have, otherwise, been dissipated in the power transistor while charging or discharging  $V_X$  node.

## 2.6 Cascode Structure

As discussed earlier in chapter one, with the scaling of CMOS technology, limits the maximum allowed voltage that can be applied across the terminals of transistor for the specific technology. Due to this, the current demand of ICs increase at low voltages, further degrading the efficiency of the off-chip converter. If off-chip converter provides such low voltages at high currents, the losses on Printed circuit board are very high. Therefore, integrating the DC-DC converter on the same IC improves the efficiency, and enhances the quality of the output voltage regulation.

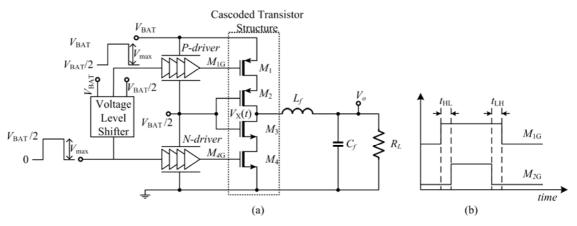

Integration of DC-DC converter on new CMOS technologies, high battery voltage is a problem. In order to solve this issue, cascade structure is appropriate for monolithic integration of converter. The cascade structure can operate at higher battery input voltages than the maximum allowed voltage  $V_{\text{max}}$  that can be applied across the terminals of transistor in low voltage CMOS technology. The circuit shown in Figure 2-6 is not suitable for monolithic integration of converter. If  $V_{\text{Bat}} = 2V_{\text{max}}$ , the buck converter configuration with cascode structure is shown in Figure 2-12.  $M_2$  and  $M_3$  are coscode transistors and  $M_1$  and  $M_4$  are switching transistors.

Figure 2-12: standard buck converter with cascode connection.

The cascode structure generates an output signal swinging between  $V_{BAT}$  and ground at  $V_X$  node from an input control signal swinging between ground and  $V_{max}$ , while guaranteeing that the voltages applied across the gate-to-source, gate-to-drain, and gate-to-body terminals of the transistors do not exceed the maximum voltage difference,  $V_{max}$ , to avoid gate oxide breakdown in a CMOS technology.

## 2.7 Voltage Level Shifter

Level shifters are important building blocks in power management systems. In DC-DC buck converters they are used to interface blocks operating at different supply domains. Figure 2-12 gives the general idea of voltage level shifters, which converts the low voltage control signal of the low-side N-driver to the high voltage control signal for high-side P-driver with the DC offset of  $V_{BAT}/2$ .

Level shift circuit topologies in low voltage technologies found in literature [31] suffer from large delays between input and output and are not able to drive large capacitive loads in an efficient way. This can lead to excess power dissipation in the following circuits. Due to non-idealities of level shifters, this thesis proposed to avoid level shifters and direct signal transfer between the high-side PMOS driver and the low-side NMOS driver. The low-side NMOS driver is driven with PWM signal to control the output voltage. The high-side driver is synchronized from the output via an inductive triggering scheme. The inductive feedback provides fast response, which is coherent with the high-frequency DC-DC converter. The inductive feedback is most suitable for fully integrated DC-DC converters, since the sensing winding can be placed beneath the main coil. Special means are provided to avoid short-circuit current by adjusting the ON-time of the PMOS power transistors.

## **3** Self-Triggered DC-DC Converter

The idea of self-triggered converter is to remove level shifter to improve power efficiency. In addition, synchronize the high-side driving signal from the output via inductive feedback and obtains automatic dead-time to avoid short circuit losses with no additional hardware. The output voltage regulation can be realized by feedback PWM signal controlling the low-side NMOS switching transistor. The idea of self-triggered is originated from self-oscillating PWM converter [19] which is similar to the proposed self-triggered converter utilize the information from the output and inductive feedback to create driving pulses. Before going into detail operation of proposed topology, let us first discuss the operation of self-oscillating converter, it will help to understand the operation of self-triggered converter.

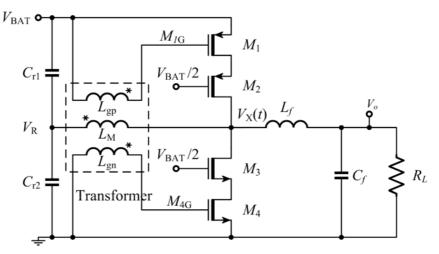

### 3.1 Self- oscillating Converter

The self-oscillating converter in Figure 3-1, the low-side NMOS and high-side PMOS drivers are replaced with the trifiliar transformer that provide positive feedback for switching ON and OFF  $M_1$  and  $M_4$  transistors. In trifiliar transformer, main winding  $L_M$  is inversely coupled  $L_{gp}$  and  $L_{gn}$  windng.  $M_1$  and  $M_4$  represent the switching transistors while  $M_2$  and  $M_3$  are cascoded transistors. The capacitive divider  $C_{r1}$  and  $C_{r2}$  are large enough to create the reference voltage  $V_R$  (or AC-ground) while charging and discharging current of main winding  $L_M$ .  $L_f$  and  $C_f$  are the output filtering components.

Figure 3-1: Self-oscillating converter topology

When  $V_{BAT}$  voltage is applied,  $V_{BAT}/2$  will appear at  $V_R$  node through capacitive divider. Initially the voltage at switching node  $V_X$  is zero. The main winding of the transformer  $L_M$  is placed between the switching node ( $V_X$ ) of the converter and  $V_R$  node. The voltage difference across main winding  $L_M$  become plus  $V_{BAT}/2$  transfer to  $L_{gp}$  and

$L_{\text{gnd}}$ , switch ON  $M_1$  and charge the  $V_X$  node to  $V_{\text{BAT}}$ . Afterwards, minus  $V_{\text{BAT}}/2$  voltage appear across the main winding and switch ON  $M_4$ . The oscillation frequency depends on the transformer inductances, on the transformer magnetic characteristic, and on the parasitic capacitance connected to the gates of the switching transistors. Thus, the oscillation frequency depends on the load current and battery voltage. The amplitude of the voltages supplied to the gates of  $M_1$  and  $M_4$  can be controlled by designing the transformer ratios ( $L_{\text{gp}} / L_{\text{M}} / L_{\text{gn}}$ ), but it cannot be used for electronic control. The amplitude of  $M_{4\text{G}}$  goes below zero, while  $M_{1\text{G}}$  goes above  $V_{\text{BAT}}$ , which guarantees secure switch OFF of the power switches, but it introduces extra losses. However, selfoscillating converter has no voltage and load regulation even the duty cycle is around 50%. They are difficult to implement on silicon because small saturable core inductors are used in [20] and no magnetic core available on standard silicon process. Selfoscillating converters are mostly used in high power applications some state-of-art selfoscillating DC-DC converters are reported in Table 3-1.

| Reference              | [26]   | [19] | [28]   | [25]   | [27]  |

|------------------------|--------|------|--------|--------|-------|

| Vin                    | 12V    | 600V | 48V    | 24V    | 1.1V  |

| Vout                   | 32V    | 300V | 12V    | 3-20V  | 7V    |

| Switching<br>Frequency | 110MHz | 9KHz | 100KHz | 200KHz | 1MHz  |

| Max.Efficiency         | 87%    | >90% | 86%    | 93%    | 25%   |

| Converter<br>Type      | Boost  | Buck | Buck   | Buck   | Boost |

| Power                  | 23W    | 3KW  | 100W   | 4W     | 1mW   |

| Integrated             | No     | No   | No     | No     | No    |

| Saturable<br>Cores     | No     | Yes  | Yes    | Yes    | Yes   |

| Year of<br>Publication | 2009   | 2002 | 2005   | 2012   | 2012  |

Table 3-1: Comparison of State-of-Art Self-Oscillating DC-DC converter

### 3.2 Self-Triggered Converter

A proposed self-triggered converter working principle is quite same as self-oscillating converter. In self-oscillating converter, the gate drivers are replaced with the trifilar transformer but the driving signal is more sinusoidal than square wave as well as it is not suitable for integrated circuits. In self-triggered converter, we replace the trilfilaar transformer with single winding (called secondary winding) for inductive feedback and pulse-forming circuit for signal shaping and creating dead-time. The primary winding of the transformer is used for both transferring the feedback signal to the secondary

winding, and for filtering the output voltage. The low-side NMOS is driven by external feedback PWM signal. Therefore, the self-triggered converter does not start oscillating by itself but it has driven by external PWM signal (or driven converter). The self-triggered title reflects the triggering scheme of high-side PMOS control signal that generates the dead-time between high-side and low-side control signals.

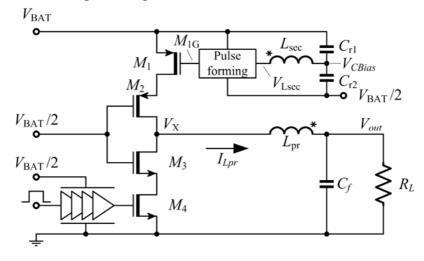

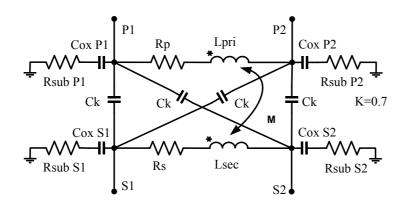

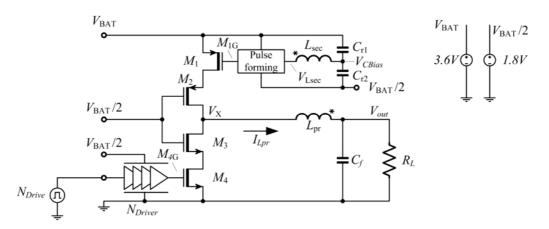

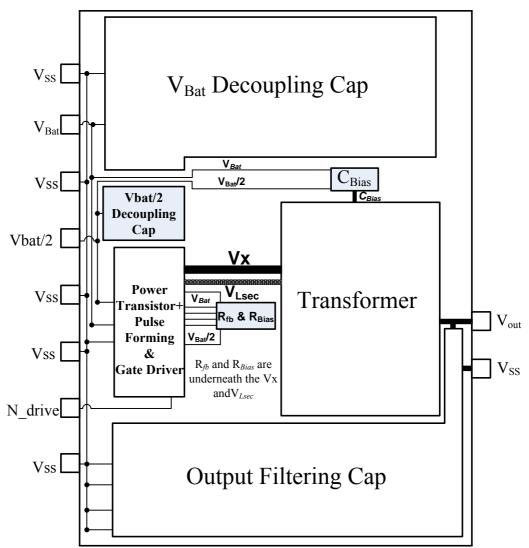

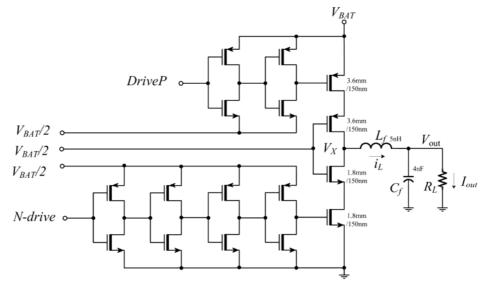

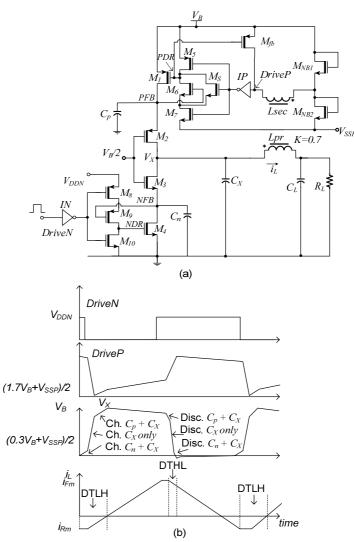

The proposed self-triggered DC-DC converter is depicted in Figure 3-2. Transistors  $M_1$  through  $M_4$  form the cascode switch-bridge and  $L_f$  and  $C_f$  are the filtering inductor and capacitor, respectively. The low-side NMOS transistor is controlled by PWM signal applied to the gate of  $M_4$  through the low-side driver. The output voltage is regulated for line or load variations by adjusting the duty-cycle of the PWM signal.

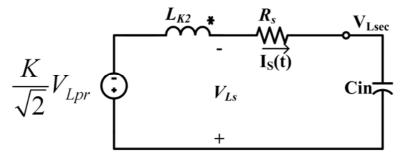

The high-side driver is replaced with the coupled inductor  $L_{sec}$  and pulse forming block, as shown in Figure 3-2, isolates the gate capacitance of the  $M_1$  from the secondary winding of the transformer and performs shaping of the gate voltage to obtain a squarewave signal at the gate of  $M_1$  rather than a sinusoidal one. Furthermore, since the input impedance of the pulse-forming block is substantially bigger than the impedance of  $M_1$ , the secondary winding carries very small current and the losses associated with  $L_{sec}$  are minor. The capacitors  $C_{r1}$  and  $C_{r2}$  are coupling capacitors and should be large enough so that their voltage remains nearly constant during the charging and discharging currents of  $L_{pr}$  and  $L_{sec}$ . The orientation of the  $L_{pr}$ - $L_{sec}$  windings is such that a decreasing voltage at  $V_X$  node causes voltage at the gate of  $M_1$  to increase and vice versa.

Figure 3-2: the proposed self-triggered converter

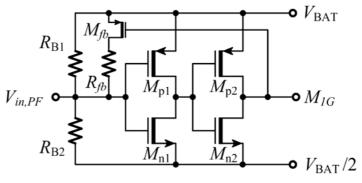

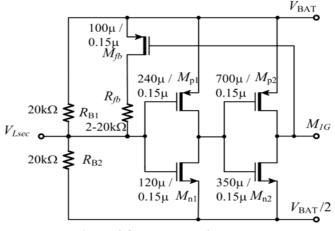

The implementation of the pulse-forming block is shown in Figure 3-3. The inverters,  $M_{p1}-M_{n1}$  and  $M_{p2}-M_{n2}$ , provide the delay time,  $t_{LH}$ , between the moments when  $V_X$  node voltage starts increasing and when  $M_1$  switch ON see Figure 3-5. The resistive combination of  $R_{B1}$ ,  $R_{B2}$ ,  $R_{fb}$  and transistor  $M_{fb}$  form a resistive divider, which create a certain dc-bias voltage at the input of inverters  $M_{p1}-M_{n1}$  and  $M_{p2}-M_{n2}$ .

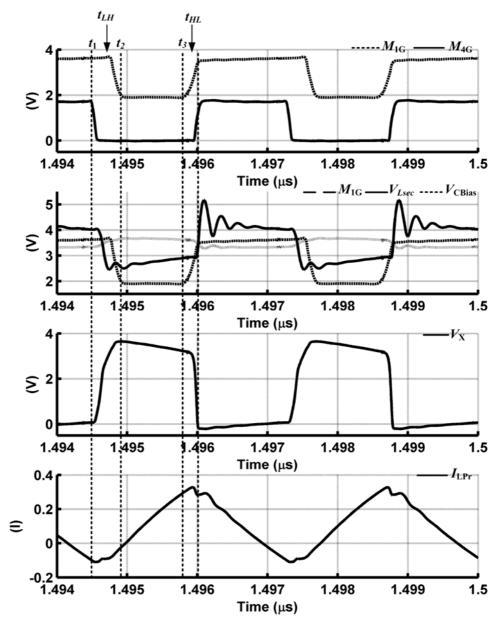

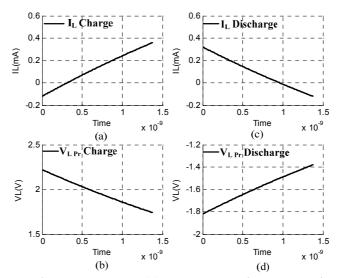

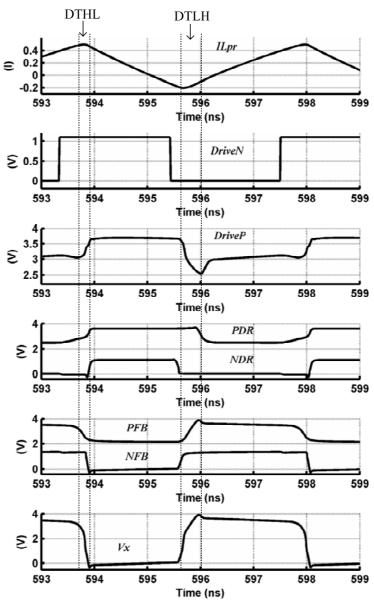

The working principle of proposed converter can be explained from Figure 3-5. At time  $t_1$ ,  $M_4$  is switched OFF, causes the  $V_X$  node starts rising to  $V_{BAT}$  (due to reverse inductor current operating in ZVS). Inverse transformer operation causes the rising edge at  $V_X$

node to transfer as falling edge at  $V_{\text{Lsec}}$  (Figure 3-5).  $V_{\text{Lsec}}$  is then applied at the input of pulse-forming block inverters. Here the inverters provide the delay time,  $t_{\text{LH}}$ , between the falling edge of  $V_{\text{Lsec}}$  and  $M_{1\text{G}}$ .

Figure 3-3: pulse forming block

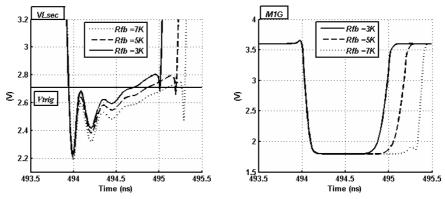

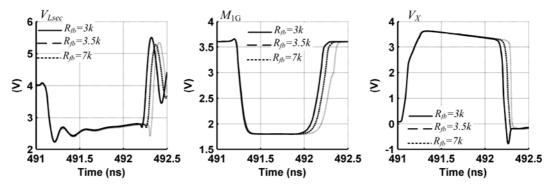

At time,  $t_2$  in Figure 3-5  $M_1$  is already switched ON and  $V_X$  node voltage has reached  $V_{Bat}$ . The primary side current  $I_{Lpr}$  is continuously increasing from time  $t_2$  to  $t_3$ , which causes the voltage decrease across  $L_{Pr}$  winding due to series resistance of  $L_{Pr}$ . As an effect of inversely coupled winding, the  $V_{Lsec}$  voltage starts increasing. At the same time  $t_2$ , the signal at  $M_{1G}$  also switch ON  $M_{fb}$ , pulling up the DC-Level at the input put of pulse forming block, the voltage crosses a triggering level, which terminates the ON pulse for  $M_1$ . The duration of the ON pulse is adjusted via feedback resistance  $R_{fb}$ . By changing value of  $R_{fb}$ ,  $V_{Lsec}$  voltage reaches the triggering level  $V_{trig}$  of pulse forming block inverters delay and switch OFF  $M_1$  and  $M_{fb}$ . Creating  $t_{HL}$  deadtime, which would not have been without the presence of  $M_{fb}$  and  $R_{fb}$ . In addition, if the duty cycle of  $M_{4G}$  pulse is changed, the time delay  $t_{HL}$  does not only remain dependent on  $R_{fb}$  value, it also becomes dependent on duty cycle of switching frequency.

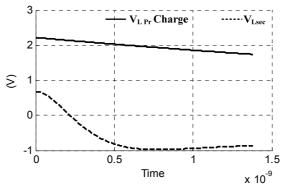

Figure 3-4: (a) Close up of  $V_{Lsec}$  at different  $R_{fb}$  values (b) Effect of changing  $R_{fb}$  on the turn-on time of  $M_{1.}$

This is because of the fact that changing duty cycle changes timing instant for rising edge of  $M_{4G}$  pulse. As a result, for changing duty cycle at  $M_{4G}$ ,  $R_{fb}$  value needs to be

changed electronically in order to generate optimum time delay  $t_{HL}$ . The automatic tuning of  $R_{fb}$  with respect to duty cycle has been left for future work of modified converter.

Figure 3-5: simulated waveforms of self-triggered converter

### 3.3 Transformer Design for Self-Triggered Converter

High-Quality factor inductors ( $\mu$ H Range) are needed to achieve high efficiency converters. Unfortunately, the inductance density of on-chip inductors yields small inductances (nH range) and high series resistance, which result in low-efficiency converters. To overcome these issues, there is need to decrease the size of on-chip inductors, which is possible by increasing the switching frequency of buck converter [1]. In self-triggered DC-DC Converter, the filtering inductor  $L_{pr}$  shown in Figure 3-2 is used as current source to charge and discharge the  $V_X$  node and magnetically couple with  $L_{sec}$ , which provides the driving signal for high-side transistor  $M_{1G}$ . The magnetic coupling between  $L_{pr} - L_{sec}$  can be realized by stacking the two inductors (transformer action) stacked on each other above the silicon substrate.

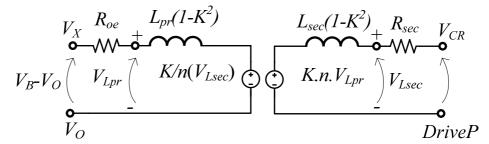

The design and modeling of monolithic planer transformer is a demanding task. In contrast to ideal transformer, monolithic transformers have parasitic effects and imperfect coupling between winding, which result is coupling factor less than one. Here, the goal is to model monolithic planer transformer at desired frequency range with minimum possible losses of primary winding  $L_{pr}$  and coupling factor k = 0.7 approximately. The modeling of monolithic planer transformer is done with 2.5D electromagnetic simulator FastModel (FastHenry and FastCap) [6]. The FastHenry and FastCap are based on Finite Element Method (FEM) core. FastHenry is used to calculate the inductances, and resistive losses of complex structures. FastCap is used to extract the capacity of complex geometries [7].

The modeling of a transformer in FastHenry starts with definition of its geometry. To define the geometry, subroutine is written in Ms-Excel, geometry is shown in Figure 3-6. The geometry of primary winding  $L_{pr}$  is constructed in such a way to get the minimum possible resistive losses. The distance between primary and secondary winding is adjusted to 3um to get coupling factor k = 0.7 approximately. The secondary winding is providing the scaled and inverted voltage of voltage across the  $L_{pr}$  for switching ON and OFF the  $M_1$  power transistor. The geometrical parameters of transformer are shown in Table 3-2.

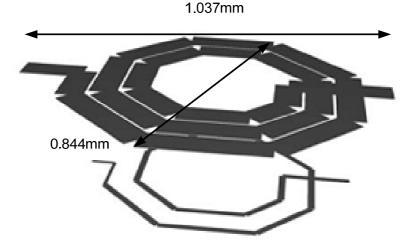

Figure 3-6: Transformer Geometry from FastHenry

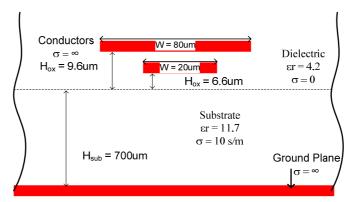

Next step is to find the substrate losses and capacitive coupling between  $L_{pr}-L_{sec}$  winding,  $L_{pr}$  to substrate and  $L_{sec}$  to substrate. The substrate material of silicon technologies has mixture of conductors and dielectric, which means substrate have finite

conductivity  $\sigma$  and permeability  $\varepsilon r \ge 1$ . Capacitive coupling from  $L_{pr}$  and  $L_{sec}$  winding to substrate and finite conductivity of substrate causes finite current flow from winding through the substrate down to ground plane. The current flow represents the additional losses, which are model by substrate resistance *Rsubp* and *Rsubs*. The geometry in Figure 3-7 shows how  $L_{pr}$  and  $L_{sec}$  winding are suspended over the substrate.

| Table 3-2: Transformer Geometrical Parameters |                   |  |

|-----------------------------------------------|-------------------|--|

| Parameters                                    | Values            |  |

| Inner Radius Lpr                              | 200um             |  |

| Outer Radius L <sub>pr</sub>                  | 416um             |  |

| Track Width Lpr                               | 80um              |  |

| Separation b/w L <sub>pr</sub> Track          | 10um              |  |

| Inner Radius L <sub>sec</sub>                 | 205um             |  |

| Outer Radius L <sub>sec</sub>                 | 293um             |  |

| Track Width L <sub>sec</sub>                  | 20um              |  |

| Separation b/w L <sub>sec</sub> Track         | 78um              |  |

| Size of Transformer                           | 1.037mm x 0.844mm |  |

The formula for the specific substrate resistance of an  $L_{pr}$  and  $L_{sec}$  winding placed on the substrate can be written as [10]:

$$Rsubp = \frac{\rho}{\pi lmp} \ln \left[ 2 \coth \left( \frac{\pi}{8} \frac{Wp + 6Hox + T}{Hsub} \right) \right]$$

(3-1)

$$Rsubs = \frac{\rho}{\pi lms} \ln \left[ 2 \coth \left( \frac{\pi}{8} \frac{Ws + 6Hox + T}{Hsub} \right) \right]$$

(3-2)

Where:

Wp = rop - rip: rop and rip are outer and inner radius of windingWs = ros - ris: rop and rip are outer and inner radius of windinglmp = 8(arop + arip): perimeter of octagonal windinglms = 8(aros + aris): perimeter of octagonal winding

The resistance *Rsubp1*, *Rsubp2* and *Rsubs1*, *Rsub2*of the model shown in Figure 3-9 can be determined as [10]:

$$Rsubp1 = RsubP2 = 2Rsubp$$

$$Rsubs1 = Rsubs2 = 2Rsubs$$

(3-3)

Figure 3-7: *L<sub>pr</sub>* and *L<sub>sec</sub>* suspended in dielectric above substrate

For capacity extraction between  $L_{pr}$ - $L_{sec}$  winding,  $L_{pr}$  to substrate and  $L_{sec}$  to substrate, FastCap is used. The input file for FastCap is different than FastHenry input file. To make input file for FastCap is very lengthy and time-consuming process to ovoid this ConvertHerny is used [7]. ConvertHenry is separate software utility, which converts the FastHenry input File into FastCap input file. FastCap calculate the capacitance of structure shown in Figure 3-7 in meters unit. Therefore to calculate the capacitance in  $\mu$ m, need to multiply results by 10<sup>-6</sup> [7]. The FastCap output is in Matrix form called Maxwell capacitance matrix shown in Figure 3-8.

$$\begin{bmatrix} C_{11} + C_{12} + C_{13} & -C_{12} & -C_{13} \\ -C_{21} & C_{21} + C_{22} + C_{23} & -C_{23} \\ -C_{31} & -C_{32} & C_{31} + C_{32} + C_{33} \end{bmatrix}$$

Figure 3-8: The Maxwell Capacitance Matrix

The C<sub>12</sub>, C<sub>13</sub>, C<sub>23</sub> are capacitances between  $L_{pr}$ - $L_{sec}$  winding,  $L_{pr}$  to substrate and  $L_{sec}$  to substrate respectively. The capacitance shown in Figure 3-9 can be determined as given in [10]. The complete model and parameter values of transformer are shown in Figure 3-9. The response of transformer model is given in Section 4.3

$$C_k = \frac{C_{12}}{4}$$

(3-4)

$$C_{OXP1} = C_{OXP2} = \frac{C_{13}}{2}$$

(3-5)

$$C_{OXS1} = C_{OXS2} = \frac{C_{23}}{2}$$

(3-6)

| Model Parameters Values |  |  |  |

|-------------------------|--|--|--|

| Values                  |  |  |  |

| 5nH                     |  |  |  |

| 2.36nH                  |  |  |  |

| 1.01 Ω                  |  |  |  |

| 12.18 Ω                 |  |  |  |

| 517fF                   |  |  |  |

| 86fF                    |  |  |  |

| 190fF                   |  |  |  |

| 145 Ω                   |  |  |  |

| 100 Ω                   |  |  |  |

|                         |  |  |  |

Figure 3-9: Model of Transformer

### 26

# 4 Design and Simulations

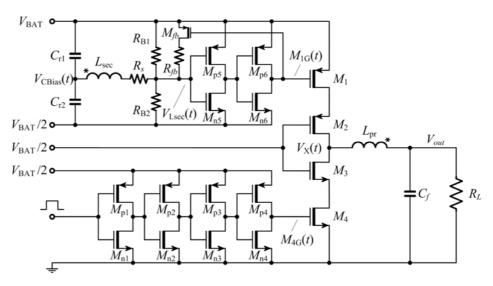

GPDK 45 nm CMOS process [29] was used to design and simulate the self-triggered converter as shown in Figure 4-1. The design was divided into following modules: Casocoded power transistors, which consists of high-side PMOS and low-side NMOS transistors, low-side NMOS driver, transformer for inductive feedback and pulse forming circuit for wave shaping.

Figure 4-1: Self-triggered DC-DC converter

All transistors in this design make use of 1.8 devices. The operating switching frequency of converter has to be high enough to achieve practical transformer size for on-chip integration and satisfy the requirement of ZVS. Large output capacitor can be used at the output, in order to achieve the small voltage ripple. The converter generates 1.5 V output voltage from 3.6 V input voltage, while providing 100mA current to the load. The converter is operating at switching frequency of 360 MHz. The specifications of proposed converter are shown in Table 4-1.

| Table 4-1. Specifications of proposed Sen-Triggered buck Converter |       |       |          |           |      |                  |             |

|--------------------------------------------------------------------|-------|-------|----------|-----------|------|------------------|-------------|

| Tashnalagu                                                         | Vin   | $f_s$ | Lpr-Lsec | Iout(TYP) | Vout | $\Delta V_{out}$ | $\eta(Max)$ |

| Technology                                                         | [V]   | [MHz] | [nH]     | [mA]      | [V]  | /Vout [%]        | [%]         |

| 45nm CMOS                                                          | 3-3.6 | 360   | 5-2.36   | 100       | 1.5  | <10              | >63         |

Table 4-1 : Specifications of proposed Self-Triggered buck Converter

# 4.1 Power Transistor Sizing

The sizing of transistor are mainly depends on conduction and switching losses of the power transistors as described in equation (2-4). The decrease in conduction losses

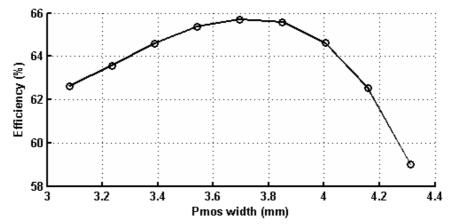

increases the switching losses. The optimum transistor sizes for 360MHz (transformer is designed for 360MHz switching frequency) are achieved when the conduction losses are equal to switching losses [2]. For the proposed converter, the minimum channels length is 150nm is used for power transistors. Figure 4-2 gives the simulated conversion efficiency as a function of PMOS power transistor widths. The NMOS size is half of PMOS size. The maximum conversion efficiency is achieved at 3.7mm PMOS power transistor width.

Figure 4-2: PMOS power transistor width Vs. Efficiency ( $W_{\text{NMOS}} = 1/2 W_{\text{PMOS}}$ )

# 4.2 Switching Frequency

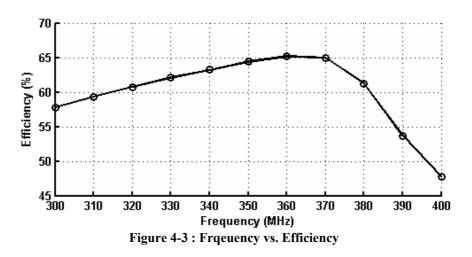

In practice, it is hard to determine the switching frequency of the converter. Switching frequency of converter should be high enough so that filtering inductor and capacitor sizes become small enough for on-chip integration. In addition, switching frequency should be far below 1GHz where the substrate effects become significant. As transformer is designed for 360MHz switching frequency converter, efficiency of converter were simulated at different frequencies. Figure 4-3 shows converter achieved maximum efficiency at switching frequency of 360MHz.

# 4.3 Transformer Design Simulations

In self-triggered converter, the primary winding is used as filtering inductor and for inductive feedback. The design procedure of transformer has been described in section 3.3 . The transformer's characteristics will discuss in this section.

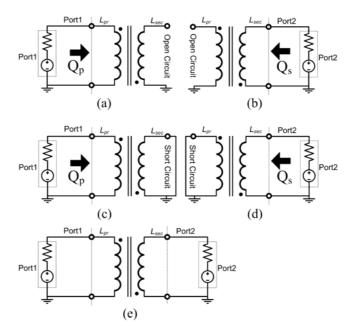

The S-parameter describes the electrical behavior of a monolithic planer transformer completely. However, not only the scattering parameters must be observed. The Z-parameters, Y-parameters, K-factor and Q-factor give a fundamental insight to the transformer's characteristics. These parameters can be derived directly from S-parameters. Figure 4-4 (a)-(d) and (e) shows simulation setup for quality factor of primary and secondary winding and K-factor respectively.

Figure 4-4: from (a)-(d) simulation setup for Quality factor of transformer. (e) Simulation setup for coupling factor K.

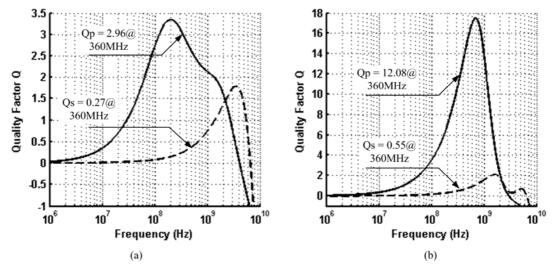

Figure 4-5 shows the characteristic Q-factor of the primary and secondary winding. Therefore, the output is left open (see Figure 4-4(a) (b) and Figure 4-5(b)). Q-factor value at 360MHz of primary winding is 12 and secondary winding is 0.55. Figure 4-5(a) shows the quality factor of the transformer with shorted output. The quality factor is analyzed using the following expression [10].

$$Q = \frac{\text{Im}(Z_{11})}{\text{Re}(Z_{11})}$$

(4-1)

Analyzing the coupling coefficient as a function of frequency the relation is useful

$$M = \sqrt{\left(Y_{11}^{-1} - Z_{11}\right)\frac{Z_{22}}{\omega^2}}$$

(4-2)

Figure 4-5: (a) Quality factor of primary and secondary winding, when other side winding shortcircuit respectively. (b) Quality factor of primary and secondary winding, when other side winding open-circuit respectively.

Then the coupling coefficient can be written as [10]:

$$k(L_{pr}, L_{sec}) = \frac{M}{\sqrt{L_{pr}L_{sec}}} = \sqrt{\frac{\left(Y_{11}^{-1} - Z_{11}\right)Z_{22}}{\operatorname{Im}(Z_{11})\operatorname{Im}(Z_{22})}}$$

(4-3)

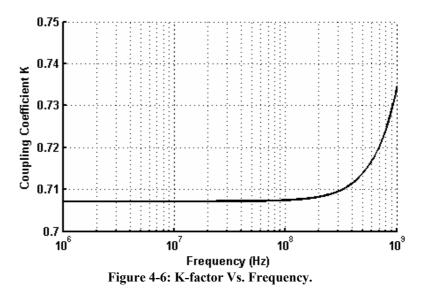

Figure 4-6 shows the K-factor is  $\sim$ 0.7 at 360MHz is good value for monolithic planer transformer.

4.4 NMOS gate driver design

Other than switching and conduction losses of DC-DC converter (given in section 2.4), timing delays and driving losses of gate driver are also major power dissipation contributors in DC-DC converter. The driving loss is represented in the following equation [5]:

$$P_{driving} = f_s V_{Supply} Q_g \tag{4-4}$$

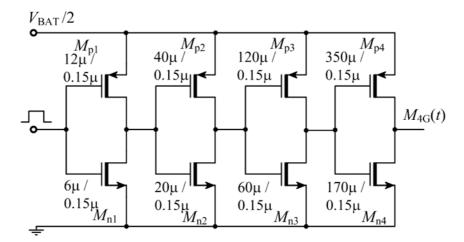

Where  $V_{Supply}$  is supply voltage,  $f_s$  is switching frequency and  $Q_g$  is gate charge capacitance of the output stage power transistor. The driving losses can be reduced by lowering the gate charge capacitance; however, reducing the gate charge increases the  $R_{on}$  series resistance of Power transistor. Another possibility of reducing gate drive loss by decreasing the supply voltage of the gate driver, it enable the fast switching and reduce the delays of driver. While designing the NMOS gate driver cascaded tapered inverters configuration is used, this increases the current capability to minimize the delay. Figure 4-7 shows the four tapered cascaded inverter stages with the tapering factor of ~3. The sizes of transistors are adjusted with electrical simulation to get minimum time delay of the driver.

Figure 4-7: NMOS Cascaded gate driver.

In proposed self-triggered converter, the timing delay of NMOS gate driver is important. Because, high-side PMOS driving signal is depend on  $M_{1G}$  and automatically obtain dead-times that avoid short-circuit losses with no additional hardware or driving signal adjustment (improvement in comparison to the standard buck converter, which requires special arrangement of driving signals).

## 4.5 Pulse Forming Block

The pulse forming block contain a tapered buffer stage, feedback transistor  $M_{fb}$ , resistor  $R_{fb}$  and biasing resistors  $R_{B1}$  and  $R_{B2}$ . The biasing resistors set the DC-level of signal coming from secondary winding. Buffer stage isolates the potentially big input capacitance of the  $M_1$  transistor from the secondary winding and makes a square-wave  $M_{1G}$  signal from distorted signal (more like sinusoidal shape) coming secondary winding.  $M_{fb}$  and  $R_{fb}$  define the ON pulse width of  $M_1$  transistor.

The buffer delay determines  $t_{LH}$  dead-time and  $R_{fb}$  determines  $t_{HL}$  dead-time by changing the DC-level of pulse. The size of buffer is adjusted according to dead-time in which

ZVS satisfy ( $V_X$  node charge to  $V_{BAT}$ ) and capable to drive big input capacitance of  $M_1$  and  $M_{fb}$ . The size of feedback transistor  $M_{fb}$  is adjusted so that  $R_{on}$  resistance of transistor does not affects the DC-level at the input of pulse forming block when it switch ON.

Figure 4-8: Pulse Forming Block

## 4.6 Simulation Results

Initially, circuit was designed with ideal components. The principle of operation and the performance of the Self-Triggered Converter are demonstrated by using the proposed topology shown in Figure 4-1 and test bench used for simulations is shown in Figure 4-9.

Figure 4-9: Test Bench of self-triggered converter

#### Waveform analysis

Simulated waveforms of the self-triggered converter in Figure 4-1 are shown in Figure 4-10. The driving signals applied to the gates of transistors  $M_1$  and  $M_4$  have square-wave shape (Figure 4-10), which help to achieve good converter efficiency. The dead-times between  $M_{1G}$  and  $M_{4G}$  are automatically created, as described in the section 3.2 , to achieve ZVS operation. The duty-cycle of the input signal controls only the duty-cycle of  $M_{4G}$ . When  $M_{4G}$  goes to zero, the inductor current is negative (Figure 4-10),