## **JUSSI HANNULA**

MICROPHONE LINE USED FOR DATA TRANSFER Master of Science Thesis

Examiner: Professor Karri Palovuori The subject approved by the department council 08.06.2011

### **ABSTRACT**

TAMPERE UNIVERSITY OF TECHNOLOGY

Master's Degree Programme in Electrical Engineering **HANNULA, JUSSI**: Microphone Line Used for Data Transfer

Master of Science Thesis, 91 pages, 2 Appendix pages

August 2011 Major: Electronics

Examiner: Professor Karri Palovuori

Keywords: ECI, I<sup>2</sup>C, microcontroller, accessory, design, measurement,

processor

The accessory microphone line of Nokia mobile phones can be utilized to provide a channel for data transmission in addition to the traditional microphone use. The transferred data can be, e.g. button press information in an accessory, such as a headset. The connection between the phone terminal and the outside device is implemented using a standard 3.5 mm jack receptacle, which includes left and right audio channels, a microphone line and a ground connection.

The switching of the microphone line to the data transmission purposes and the integration of the actual data transmission interface is a product-specific variable. The goal of this thesis is to design an electrical circuitry, which allows the microphone line to be separated from the phone terminal's microphone input and to be used to relay data between the phone and the connected accessory. The implementation of the electrical circuitry is designed so that it is suitable for mass production.

The most important tasks for implementation outside of the microphone line, are the ability to convert the data protocol used by the accessories to the data protocol supported by the phone terminal and vice versa, and also to store the received data in case the phone terminal is busy doing other tasks.

The used data protocols and electronics behind them are covered in order to create a sufficient level of understanding to the matters at hand. The design process of the electrical circuitry will be covered from the beginning; starting from the introduction of the interface under design, advancing to the selection of the base components and finally, designing of the schematic.

The process differs to some extent from the usual design flow where everything can be started from scratch. Some of the already placed components and functionalities of the interface under design are parallel or common with other interfaces inside the phone terminal and therefore, cannot be altered. The requirements and limitations set by the specification documents and the parallel functionalities concerning the design are fully covered and explained.

The functionality of the designed interface was verified and the operation of the electrical circuitry was tested in order to find possible errors from the design and provide the information for making the necessary corrections or modifications. Signal integrity and timing measurements were carried out with the help of an oscilloscope.

## TIIVISTELMÄ

TAMPEREEN TEKNILLINEN YLIOPISTO

Sähkötekniikan koulutusohjelma

HANNULA, JUSSI: Mikrofonilinjan hyödyntäminen tiedonsiirtoon

Diplomityö, 91 sivua, 2 liitesivua

Elokuu 2011

Pääaine: Elektroniikka

Tarkastaja: professori Karri Palovuori

Avainsanat: ECI, rajapinta, I<sup>2</sup>C, mikrokontrolleri, lisälaite, suunnittelu, mittaus

Nokian matkapuhelimien mikrofonilinjaa on mahdollista hyödyntää tavallisen mikrofonikäytön lisäksi datan siirtoon. Välikappaleena puhelimen mikrofonilinjan ja ulkoisen laitteen välillä toimii tavallinen 3,5 mm audioliitin, joka sisältää mikrofonisisääntulon lisäksi vasemman ja oikean audioulostulon ja maakytkennän.

Mikrofonilinjan erottaminen datansiirtoon ja itse datan välittäminen puhelimen käsiteltäväksi vaatii tuotekohtaista suunnittelua. Tämän diplomityön päällimäisenä tarkoituksena oli suunnitella elektroninen piiri, joka mahdollistaa mikrofonilinjan erottamisen puhelimen sisäisestä mikrofonisisääntulosta ja linjan käyttämisen tiedonsiirtoon puhelimen ja kytketyn lisälaitteen välillä. Piiri tuli suunnitella siten että sitä on mahdollista hyödyntää massatuotannossa sellaisenaan.

Suunnitellun piirin tulee pystyä dataväylän erottamisen lisäksi muuntamaan lisälaitteen käyttämä tiedonsiirtoprotokolla puhelimen käyttämän tiedonsiirtoprotokollan mukaiseksi. Muunto täytyy pystyä suorittamaan myös toiseen suuntaan. Piirin täytyy myös kyetä säilyttämään lisälaitteen lähettämää tietoa kunnes pääprosessori lukee tiedon, mikäli prosessori juuri kyseisellä hetkellä on kiireinen tehdessään muita toimenpiteitä.

Käytettyihin tiedonsiirtoprotokolliin liittyvä, teoria etenkin elektroniikan kannalta katsottuna, on käsitelty teoriaosuudessa, jotta suunnitellun piirin toiminta voitaisiin ymmärtää syvällisesti. Elektronisen piirin suunnitteluprosessi on käsitelty alusta saakka; aloittaen rajapinnan esittelystä edeten komponenttien valintaan ja aina piirin kytkentäkaavion suunnitteluun saakka.

Suunnitteluprosessi eroaa jonkin verran tavanomaisesta. Piirin suunnittelussa ei voida lähteä liikkeelle tyhjältä pöydältä, sillä suuri osa tärkeimmistä komponenteista ja mikropiireistä on jo asetettuina suunniteltuun piirin ja ne asettavat tiettyjä ehtoja ja rajoituksia suunnittelulle. Ympäröivistä piireistä ja olemassa olevista lisälaitteista johtuvat vaatimukset on käsitelty ainoastaan oleellisilta ja vaadituilta osin riittävän taustatiedon tarjoamiseksi.

Suunnitellun rajapinnan ja elektronisen piirin toiminnallisuus testattiin ja todennettiin, jotta mahdolliset suunnitteluvirheet ja piirin toiminnassa mahdollisesti esiintyvät virheet löydettäisiin ja voitaisiin korjata. Sähköisten signaalien laatu ja ajoitukset mitattiin oskilloskooppia hyödyntäen.

### **PREFACE**

This Master of Science thesis, **Microphone Line Used for Data Transfer**, was written for Nokia Corporation in Tampere, Finland.

I want to express my greatest gratitude to my supervisor and mentor M.Sc. Jarmo Kangasaho, who made this project possible in the first place. Also a huge word of thanks for reading through my thesis and for being so excited about it all the time.

I also want to thank my colleagues at Nokia, especially M.Sc. Ville Rantala, for the excellent working environment, all their support and encouraging comments.

I also would like to thank Prof. Karri Palovuori for examining my thesis.

Finally, big thanks to all the colleagues, who had anything to do with my thesis work and to my family and friends for supporting me during my studies.

# **TABLE OF CONTENTS**

| TEI | RMS                              | AND SYMBOLS                                     | vii |  |  |  |

|-----|----------------------------------|-------------------------------------------------|-----|--|--|--|

| 1   | INT                              | TRODUCTION                                      | 1   |  |  |  |

|     | 1.1                              | 1 The purpose of this thesis                    |     |  |  |  |

|     | 1.2 The structure of this thesis |                                                 |     |  |  |  |

| 2   | NOKIA AV INTERFACE               |                                                 |     |  |  |  |

|     | 2.1                              | AV connector                                    | 5   |  |  |  |

|     |                                  | 2.1.1 AHJ                                       | 7   |  |  |  |

|     | 2.2                              | ECI                                             | 8   |  |  |  |

|     |                                  | 2.3 ECI-accessory                               |     |  |  |  |

| 3   | DA                               | 13                                              |     |  |  |  |

|     | 3.1                              | 3.1 I <sup>2</sup> C-bus specification          |     |  |  |  |

|     |                                  | 3.1.1 I <sup>2</sup> C-bus features             |     |  |  |  |

|     |                                  | 3.1.2 I <sup>2</sup> C-communication procedure  |     |  |  |  |

|     |                                  | 16                                              |     |  |  |  |

| 4   |                                  | 18                                              |     |  |  |  |

|     | 4.1                              | Open-drain output                               |     |  |  |  |

|     |                                  | 4.1.1 Defining the pull-up resistor             |     |  |  |  |

|     |                                  | 4.1.2 Current consumption                       |     |  |  |  |

|     |                                  | 4.2 Schmitt-trigger input                       |     |  |  |  |

|     | 4.3                              | T T                                             |     |  |  |  |

| 5   |                                  | 27                                              |     |  |  |  |

|     | 5.1                              | ECI-controller selection                        |     |  |  |  |

|     |                                  | 5.1.1 ATtiny20 microcontroller                  |     |  |  |  |

|     |                                  | ECI requirements                                |     |  |  |  |

|     |                                  | EMC problems                                    |     |  |  |  |

| 6   |                                  | COMMUNICATION CIRCUITRY                         |     |  |  |  |

|     | 6.1                              | Common parts of the ECI and the audio interface |     |  |  |  |

|     |                                  | 6.1.1 EMC & ESD filtering                       |     |  |  |  |

|     |                                  | 6.1.2 HSMIC-line switched to data transfer      |     |  |  |  |

|     |                                  | 6.1.3 Powering the accessory                    |     |  |  |  |

|     |                                  | 6.1.4 Accessory detection & identification      |     |  |  |  |

|     | 6.2                              | 8 1                                             |     |  |  |  |

|     | 6.3                              | C                                               |     |  |  |  |

|     | 6.4                              | 6                                               |     |  |  |  |

|     | 6.5                              | 11                                              |     |  |  |  |

| 7   | TESTING AND VERIFICATION         |                                                 |     |  |  |  |

|     | 7.1                              |                                                 |     |  |  |  |

|     | 7.2                              |                                                 |     |  |  |  |

|     | 7.3                              |                                                 |     |  |  |  |

|     |                                  | 7.3.1 Probe selection                           | 65  |  |  |  |

|     | <ul><li>7.4 Functional testing</li><li>7.5 Electrical measurements</li></ul> |        |                        |    |  |

|-----|------------------------------------------------------------------------------|--------|------------------------|----|--|

|     |                                                                              |        |                        |    |  |

|     |                                                                              | 7.5.1  | Signal Integrity Tests | 68 |  |

|     |                                                                              | 7.5.2  | Timing Tests           | 79 |  |

| 8   | CO                                                                           | NCLUS: | IONS                   | 86 |  |

| REI | FERE                                                                         | ENCES  |                        | 88 |  |

| API | PENI                                                                         | DICES  |                        | 91 |  |

### **TERMS AND SYMBOLS**

ADC Analog-to-digital converter AHJ American Headset Jack

ASIC Application-specific Integrated Circuit

AV Audio-video

BJT Bipolar Junction Transistor

CMOS Complementary Metal–Oxide–Semiconductor

CPU Central Processing Unit

DC Direct Current

DCS Digital Cellular Service

ECI Enhancement Control Interface

EMC Electromagnetic Compatibility

EMI Electromagnetic Interference

ESD Electrostatic Discharge

GPS Global Positioning System

GND Ground

GSM Global System for Mobile Communications

IC Integrated Circuit

I<sup>2</sup>C Inter-Integrated Circuit

I/O Input/Output

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

MSIC Mixed Signal Integrated Circuit NFC Near Field Communication

NMOS N-channel MOSFET

PCS Personal Communications Service

PWB Printed Wiring Board

RF Radio Frequency

SCL Serial Clock Line

SDA Serial Data Line

TPI Tiny Programming Interface

TVS Transient Voltage Suppression Diode

TWI Two Wire Interface

Vcc Supply voltage

Vdd Supply voltage

C Capacitance

$\tau$  RC time constant

R Resistance

V Voltage

t Time

e Euler's numberT Signal rise time

## 1 INTRODUCTION

By just browsing the Nokia on-line store, one would notice that the product range includes not only mobile phones, but many other products as well. Accessories are a wide group of products designed to be used with Nokia mobile phones in order to add additional features, while providing more extensive user experience. Later in this thesis Nokia mobile phone is often referred to as phone terminal. [1]

Accessories are generally devices which are not possible or practical to integrate to the phone itself, e.g. memory cards, headsets, cables, chargers. A battery is also considered an accessory as it is actually not part of the mobile phone itself and in most cases can be replaced by the user. The word accessory also covers items which have nothing to do with the functionality of the phone or electricity. Such items include carrying cases or phone holders for example. An accessory in general is an item designed for use with a base item. [1]

When speaking of accessories, the meaning of the word in the context of this paper is limited. It is used as a common name for all the accessories that can be connected to the phone terminal's 3.5 mm jack receptacle. An accessory supported by the phone terminal could be for instance, a video cable, basic headphones, a car kit, headset with a microphone and so on. When such an accessory is being connected to the receptacle, it gets connected to the Nokia AV interface.

Nokia AV interface is a specific analog/digital communication system between an accessory and the phone. The interface is used to create an electrical audio and video interface between phone terminal and wired accessories. AV interface consists of the audio/video interface and the Enhancement Control Interface (ECI). The focus of this thesis is mainly on the ECI, but understanding some parts of the audio interface is a necessity in order to understand the activities within the ECI.

Some advanced accessories developed by Nokia may have added value features such as headphones with a volume control. Such an accessory is called an ECI-accessory. An example of an ECI-accessory is presented in Figure 1.1. In order to enable the volume controlling, the information of volume button presses must be somehow delivered to the phone terminal. The actual function of controlling the volume is done in the phone terminal. Only the command to lower the volume level is being sent from an ECI-accessory in this instance. [1]

Figure 1.1. An ECI-accessory [1]

The processing of the data generated by the button press utilizing the ECI is done by the main processor of the phone terminal. The data protocols used by an accessory and the main processor are different and therefore a block where the data conversion is done must be included. ECI is a data transmission interface with the purpose of making data transmissions between the phone and the accessory possible.

Without the ECI, the AV interface through the 3.5 mm jack receptacle is only capable of providing an audio and a video output and a microphone input. Video output and microphone input cannot be utilized simultaneously because both are using the same microphone line for transferring the data. ECI-protocol is a confidential Nokia proprietary data communication protocol, and therefore the ECI-accessory functionalities work only on a device having an ECI implemented, i.e. most of the Nokia mobile phones. An ECI-accessory works normally when connected, for example, to an mp3 player. In this case, only the ECI-functionalities are inoperative.

## 1.1 The purpose of this thesis

Nokia mobile phones have usually had a designated ASIC to handle all the data communications through the Nokia AV connector. The design has usually been implemented as a part of some greater functionality ASIC, normally mixed signal IC that includes most of the powering and analog audio circuitries. In this case however, the implementation with a mixed-signal ASIC was not possible, because the basic design is implemented with a commercial chipset and Nokia has very little room for affecting the specifications of the chipset.

The task was to design and test the electrical circuitry for the needed data communication paths between the Nokia AV connector and the phone. The main problem is the fact that the AV connector does not have a designated data line. The audio channels are solely reserved for audio use and the microphone line is mainly, as the name suggests, meant to use with a microphone. However, it is possible to utilize

the microphone line for other purposes by muting it. The ECI takes advantage of this opportunity and uses the line for ECI-communication.

The users expect full time functionality from the control buttons, which means that the volume controlling, for example, must work even when the microphone is in use. A button press automatically mutes the microphone and the phone terminal switches the microphone line to ECI-use for as long as the data communication lasts. A button press causes only a little pause to the microphone audio. The break should not be longer than a few milliseconds.

The functionality of the ECI-protocol and the basic principles of the ECI are always the same, but the implementation is a product-specific variable. The design, however, is intended to be used with other chipsets in the future as well. The future aspect must be taken into consideration during the selection of the supply voltages, signal logic levels and so on.

The design of the ECI must follow the predetermined specifications to be compatible with the accessories already in the field. Also the understanding of the different protocols is important not just in designing of the electrical circuitry, but also in order to understand the functionality of the entire AV interface. The understanding provides knowledge for testing and measuring the functionality of the interface. It is easy to do the measurements with minimal information regarding the electrical circuitry, but deep understanding provides the tools to make corrections if something does not go according to the plan.

### 1.2 The structure of this thesis

Most of the theory required for understanding the functionality of the ECI is discussed in chapters 2 and 3. In these chapters, a foundation for understanding the functionality of the ECI and the designed circuit is created. Chapter 2 introduces the parts of the Nokia AV interface, which are important from the ECI point of view. The chapter is an introduction to the point and the interface is not discussed in its entirety. This is because many things are context-specific and therefore complemented on the following chapters.

Chapter 3 concentrates on offering an extensive overview of the data communication protocols used. Chapter 4 concentrates on the electronics concerning the protocols discussed in chapter 3. All the used electrical output stages for data transmissions are covered.

The entire design process is covered in detail from beginning to end in chapters 5 and 6. All the electrical and other specifications needed for designing the electrical circuitry are presented and the decisions are rationalized. The process of detecting an accessory and the functionality of the ECI are explained.

The measurement methods used in this thesis are described in Chapter 7. The measurement results are analyzed and the root causes for the possible functional failures or abnormities in measurement results are explained. Chapter 8 includes all the conclusions of the thesis. Possible future recommendations, proposals for improvement,

evaluation of the work done, usefulness of the design and measurement results are discussed.

## 2 NOKIA AV INTERFACE

This chapter provides an introduction on the Nokia AV interface. The Nokia AV connector and related failure situations are reviewed. ECI is introduced and the basics of the accessory detection and powering of the accessory are also discussed. Items concerning the ECI will be specified in the following chapters. Thorough description of the accessory detection and the powering of the accessory will be given when the final structure of the designed ECI-block is known.

The Nokia AV interface is a wired mixed signal interface based on a 3.5 mm, or 2.5 mm in some cases, 4-pole miniature concentric audio plugs and jacks, which is used to connect a master device to a slave device. The master device is the phone terminal and the slave device is the accessory connected to the phone terminal. Connecting the two devices using the AV connector will enable transmission of power, stereo audio out and enhancement control data from master to slave, and transmission of microphone audio and accessory identification, configuration and status data from slave to master. In addition to this, the AV connector may also be used for transmission of a composite video signal from master to a display device.

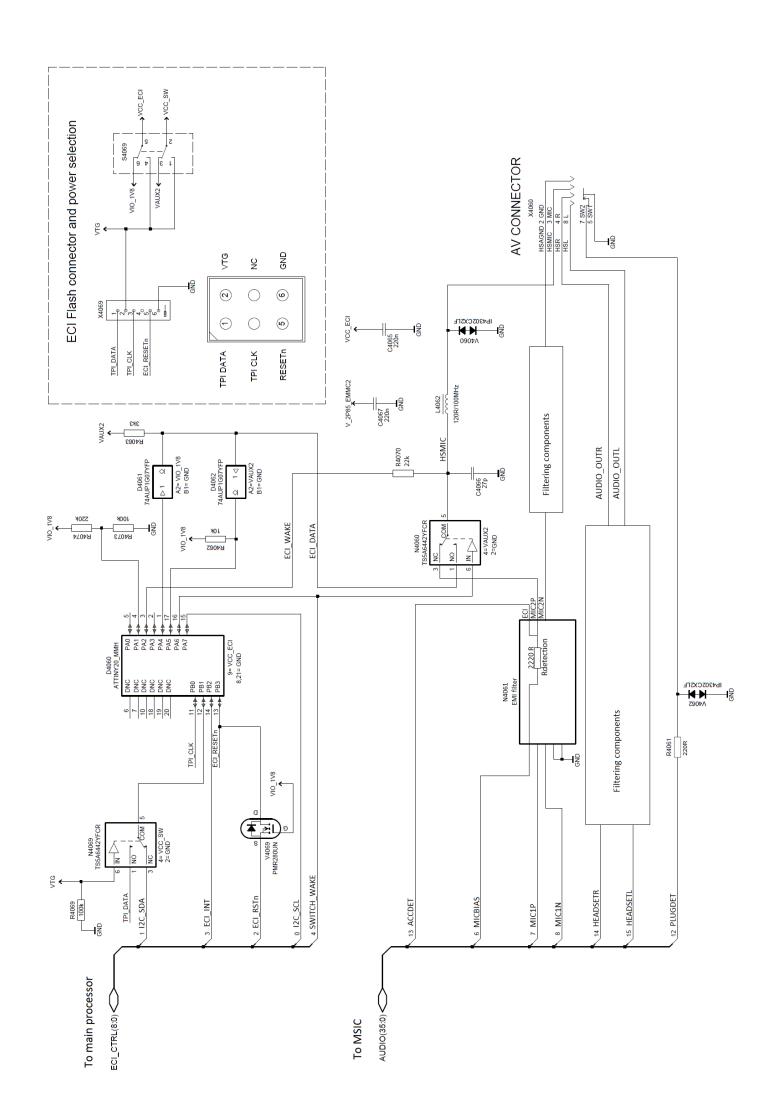

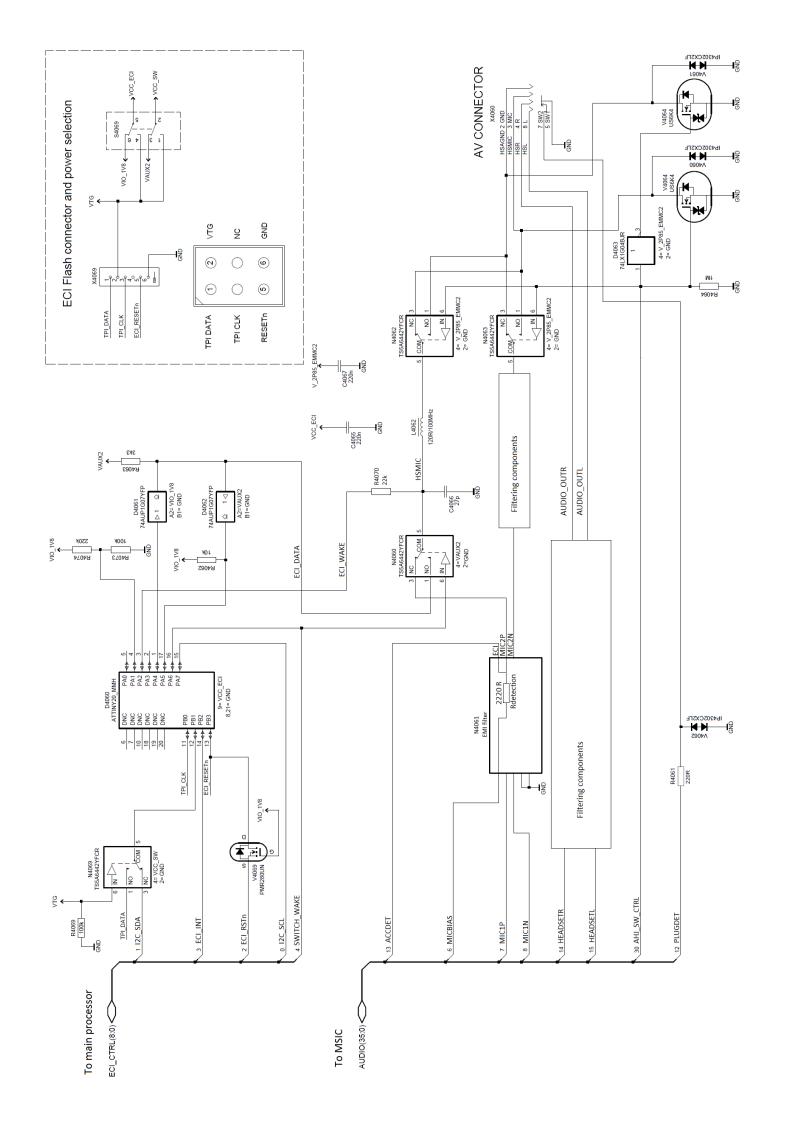

The AV interface consists of the audio interface and the ECI. The interfaces are connected to the outside world via the AV connector presented in Figure 2.1. Nokia has specified the electrical interface between the master and the slave using the AV connector. The specification document concerning the ECI is confidential and only given to manufacturers under a non-disclosure agreement. All the electrical or other needed specifications concerning the ECI are given in the following chapters.

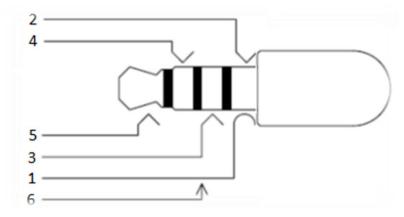

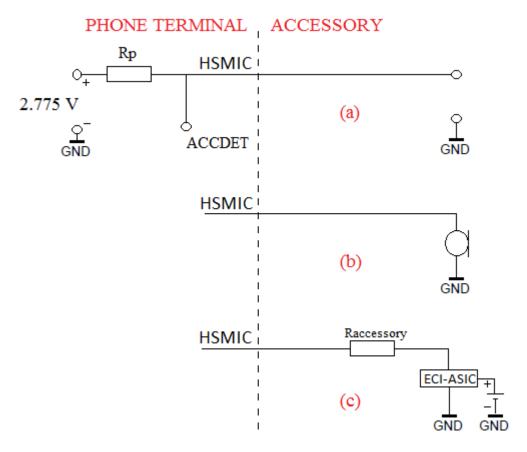

#### 2.1 AV connector

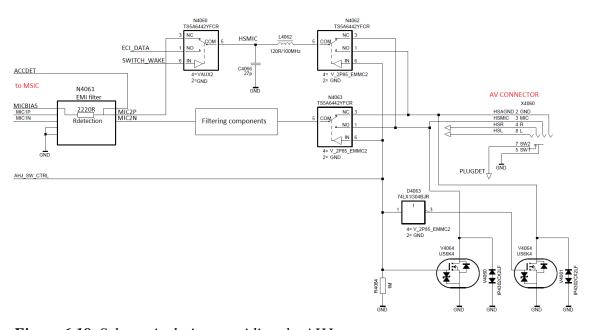

The Nokia AV connector is the electrical and physical interface used to connect the phone and an accessory. The pin order of the AV connector is presented in Figure 2.1. The connector plug has four lines. The PLUGDET-functionality connects pins one and six when the lug is inserted to the counterpart, indicating to the phone terminal that a plug has been connected. HSEARL is the left audio channel and HSEARR is the right audio channel. HSMIC is the microphone line and according to its name it is normally used to connect a microphone or alternatively used as a composite video output, but the line can also be switched by the phone terminal to be used as a data path for the ECI-accessories. In addition to data transfer properties, the line is also used to provide microphone bias voltage and a supply voltage to accessories. Signals of the Nokia AV interface are presented in Table 2.1.

Figure 2.1. Nokia AV connector pin layout

Table 2.1. Signals of the Nokia AV interface

| Pin<br>Number | Signal Name | Direction | Description                                                                                          |

|---------------|-------------|-----------|------------------------------------------------------------------------------------------------------|

| 6             | PLUGDET     | In        | Host internal connection, plug detection                                                             |

| 5             | HSEARL      | In / out  | Audio output                                                                                         |

| 4             | HSEARR      | In / out  | Audio output                                                                                         |

| 3             | HSMIC       | In / out  | Multiplexed microphone audio and control data, C-video out, microphone bias supply voltage (MICBIAS) |

| 1, 2          | GND         | -         | Ground contacts (or other reference level)                                                           |

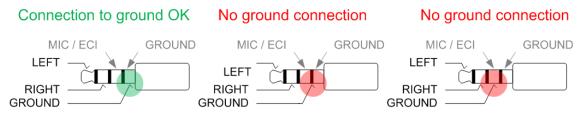

Some compatibility issues may occur, if a Nokia accessory with the Nokia AV connector is used in normal, meaning not a Nokia specified, 3.5 mm receptacle. There is a possibility that the ground connection of the receptacle does not get connected to the plug's ground connection. The reason for the bad or wrong connection is usually an undersized receptacle or accordingly can be said, that the plug is oversized. As a result, the plug does not fit in its entirety inside the receptacle and the grounds do not have a proper connection. Clarifying pictures are presented in Figure 2.2.

Figure 2.2. Nokia AV interface compatibility

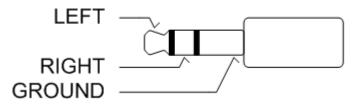

According to Nokia's specification, the pin order of an AV connector should follow the pin order presented in Figure 2.1 and Table 2.1, although that is not always the case on the connected accessory. For example, headphones do not have support for a microphone, nor for ECI-communication. The HSMIC-contact surface is usually grounded in headphone plugs. A Basic headphone plug is presented in Figure 2.3.

Figure 2.3. A basic headphone connector

The AV connector as well as the AV interface is fully compliant with the OMTP (Open Mobile Terminal Platform) specification. OMTP is an operator-sponsored non-profit forum serving the needs of each and every link in the mobile phone value chain by gathering and driving phone terminal requirements. This means that all accessories manufactured following the OMTP specification function with Nokia mobile phones. Accordingly, all Nokia-manufactured accessories, except the ECI-functionalities, function if connected to any mobile phone manufactured following the OMTP specification. [1], [2], [4]

#### 2.1.1 AHJ

Headphones do not cause problems when connected to Nokia AV connector as the missing HSMIC-connection is taken into account in specification. Much more problematic is a plug where HSMIC- and GND-connections have been reversed. Such a plug is called American Headset Jack (AHJ) and it is used by some American companies. If an AHJ plug is being connected to a Nokia specified receptacle, HSMIC-line gets connected to GND and vice versa.

In case of an AHJ plug and a grounded HSMIC-connection, the accessory gets detected as headphones. The audio output channels would work as usual, but only in theory because the audio channels would not have a proper ground connection. The microphone line would be grounded and the possible microphone would not work at all.

To provide support for AHJ-plugs, some extra switching components can be placed on the circuit board in order to switch the HSMIC- and GND-lines. The drawback is that it causes additional resistance to ground. Good ground at the phone terminal side is extremely important for achieving a good EMC performance. Low common ground resistance is important to avoid an electrical echo via common ground from the audio outputs to microphone input. The bigger the ground resistance, the poorer the EMC protection will be because of the unwanted extra series resistance relative to ground. The common ground between the audio output and the microphone line needs to be designed the way that the path resistance is minimized. [29]

Undesired capacitive, inductive and conductive coupling, i.e. crosstalk is caused by two channels using the same shared electrical lead to ground. The common ground impedance defines the crosstalk performance of the system including crosstalk from ECI communication to the earpieces. Therefore, the microphone line and the audio outputs must have separate ground lines on the phone terminal side. The separation of

the grounds would cause some extra switches alongside some alternative signal routing to be placed on host side implementation. [29], [11]

### 2.2 ECI

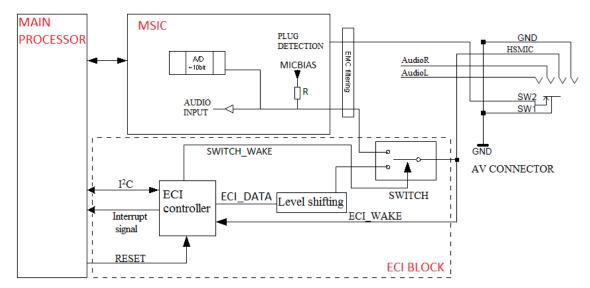

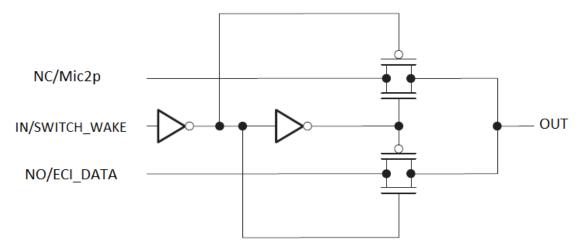

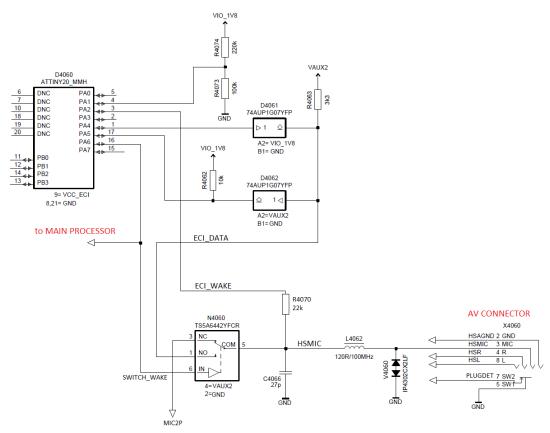

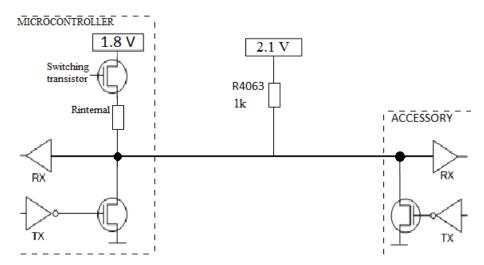

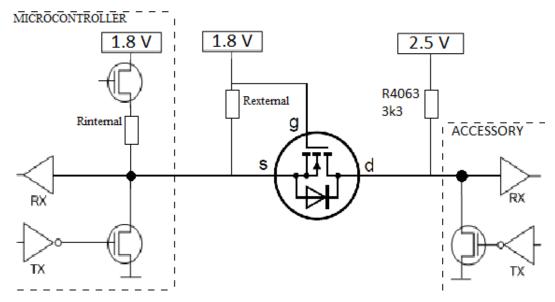

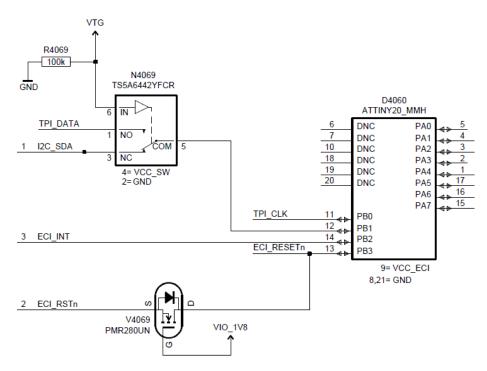

The ECI controls the data traffic between the phone and the accessory through a bidirectional data line. It is a slow digital interface decoupled from a microphone line. The ECI-block communicates to the accessory using the AV connector's HSMIC I/O-port.

The ECI-accessory supports only the Nokia proprietary ECI-data transfer protocol and the main processor does not have support for it, therefore, two different data transfer protocols have to be used to transfer information. The ECI-block must also be able to handle the data conversion between the used protocols.

The communication between accessories and the main processor via the ECI occurs using the I<sup>2</sup>C-protocol. Communication between the interface and the accessory occurs using the Nokia proprietary ECI-protocol. Both protocols are bi-directional, but I<sup>2</sup>C uses two lines for communication, and ECI uses only one. There are several different data transfer protocols available for use with the main processor, but the I<sup>2</sup>C-protocol is the most adequate solution, because it is simple to implement and faster transfer protocol is not needed.

Generally speaking, the logic high voltage level on both protocols is not fixed. The main processor used in this design, however, uses fixed internal pull-up voltage of 1.8 V to power the line. ECI-protocol uses bit higher logic high voltage level. For that reason, a voltage level adaptation must be done at some point along the electrical circuitry.

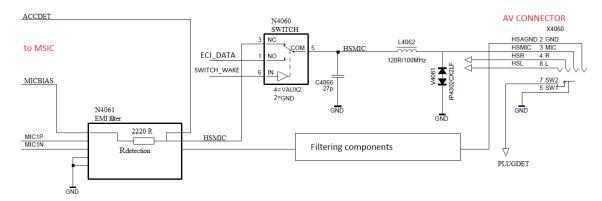

The system block diagram illustrating the functionality of the intended solution for the ECI is presented in Figure 2.4. The audio interface and the ECI have a strong mutual dependence and have some overlapping functionalities. It is not possible to determine exactly which part of the AV interface or the block diagram belongs to the audio interface and which parts to the ECI. The dash line in the figure is there to outline the part of the overall block diagram where the actual ECI-communication and the data conversion occur.

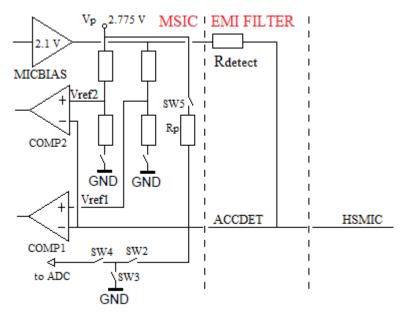

The MSIC is a circuit, which includes most of the powering and analog audio circuitries of the phone terminal. It includes the electronics to detect plug insertion and removal. After insertion, the MSIC starts an accessory detection to differentiate between possible accessories. If the HSMIC-line is needed for the ECI-communication during the detection phase, the ECI-controller must be woken up. The wake up command is sent by the main processor. Before the main processor can wake up the ECI-controller, the MSIC must inform the main processor about the need for the ECI-communication.

Figure 2.4. The intended block diagram of the ECI

The ECI-controller takes care of the data transfer to accessory, be it data reading or writing. For reading cases, the ECI-controller will activate the interrupt signal to the main processor when the ECI-data is ready to be read. For writing, the main processor must activate the ECI-controller using I<sup>2</sup>C to transfer the data to the ECI-controller. The activation occurs only during the detection phase, because at all other times, the need for communication comes from the accessory.

To enable the communication between the ECI-controller and the accessory, the ECI-controller must activate the SWITCH\_WAKE-signal to switch the HSMIC-line to ECI-communication use allowing the ECI-controller to start data transfer with the accessory. Immediately after the ECI-communication, the ECI-controller switches the line back to audio use.

After the detection phase the ECI-controller may be in idle mode for a long time, until the user presses a button. The ECI-controller must be woken up from the idle mode before it can handle the ECI-communication. The ECI\_WAKE-line is routed directly from the HSMIC-line to the ECI-controller. A button press pulls the HSMIC-line and the ECI\_WAKE-line to the ground and the falling edge of the HSMIC-signal immediately wakes up the ECI-controller, which activates the SWITCH\_WAKE-signal and the line is once again ready to transfer ECI-data.

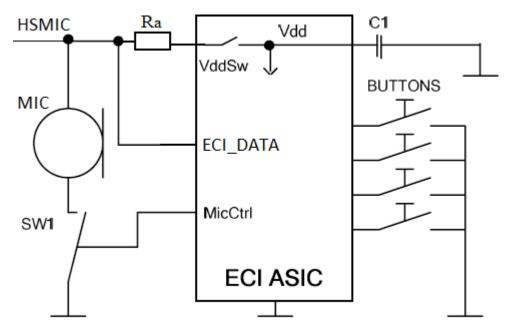

# 2.3 ECI-accessory

ECI-accessories are usually powered by the microphone bias supply provided by the MSIC. Later in this thesis the microphone bias supply is often referred to as MICBIAS. The HSMIC-line is used to provide enough power to charge a capacitor inside the ECI-accessory presented in Figure 6.4. As the MICBIAS-line must be switched off from the ECI-data path during the ECI-communication, the charged capacitor as well as the pull-up voltage of the ECI\_DATA-line is used for powering the accessory. The HSMIC-line can be switched to the ECI-communication use only when the communication is needed

in order to be able to charge the powering capacitor effectively and so that the microphone audio could be utilized, i.e. the HSMIC-line can be switched to the ECI-communication use only when the ECI-data is actually being transferred.

An ECI-accessory may also have its own internal power supply. In these devices, the bias supply from the phone terminal is usually used only for microphone biasing. The detection mechanism for these devices is exactly the same as for accessories powered by the phone terminal. Although, it is also possible to use the phone terminal's bias supply to power the ECI-accessory's control logic even if a local supply is available. A car kit accessory is a prime example of an application which uses its own supply; a car battery. Also some home stereo products such as external speakers may have their own supply.

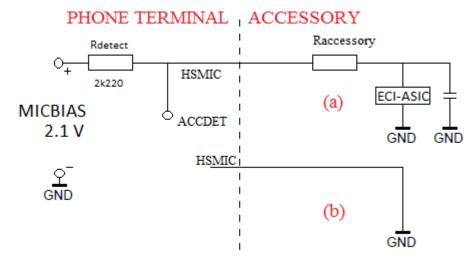

The detection between different kinds of accessories is based on the voltage measurement in HSMIC-line. The same microphone bias supply voltage, which is used to power accessories, is also used during the detection phase. In addition to the microphone bias voltage, the detection phase also uses a pull-up voltage mainly for separating an open cable from other accessories.

Based on the measured voltage level, accessories are basically being divided into ECI-accessories and non-ECI-accessories, the latter of which are being sorted out individually depending on the measured voltage level. If the measured voltage suggests that the accessory is an ECI-accessory, the phone terminal tries to start the ECI-communication with the accessory.

A non-ECI-accessory is an accessory having audio inputs, a microphone output or both. A non ECI-accessory could also be a video cable presented in Figure 2.5. An example of a non-ECI accessory could be basic headphones, presented in Figure 2.5, which consist merely of one or two earpieces. It does not include any active parts, and the phone terminal cannot differentiate them from each other. For example, the phone terminal cannot detect whether the headset is mono or stereo.

**Figure 2.5.** Examples of non-ECI-accessories; basic headphones and a video cable [1]

Some phone terminals which do not have the ECI at all, may have a support for long and short button press detection. Such a feature could be used, for example, when answering and ending a call. The button is connected in parallel with the microphone. A button press draws the microphone line to ground, which is detected and handled by the MSIC. An example of such an accessory having an answer/end call button could be a basic headset, presented in Figure 2.6, which consists of a microphone and an earpiece.

Figure 2.6. Two headsets with a microphone, an earpiece and an answer/end call button [1]

ECI is needed for some advanced accessories that enable added value features, which are implemented by using an internal ECI-ASIC. The ECI provides the data communication channel between the ECI-ASIC and the phone terminal. Figure 2.7 presents two examples of ECI-accessories. Examples of the ECI-accessories already in the field include:

- headset with earpiece and microphone with multiple buttons (e.g. volume +/-, play, stop, rewind, skip)

- induction loop for hearing impaired people

- speaker phone for car environment

- loudspeaker accessory without a microphone

- a car kit.

Figure 2.7. Two headsets with some integrated basic audio control functions [1]

An ECI-accessory with an electret microphone, such as an ECI-headset, typically contains an ECI-compliant ASIC or a microcontroller, which includes memory and I/O-ports for identification and control purposes. Accessory detection by the master device is made by reading accessory information from the memory of the accessory. Every ECI-accessory has its own parameters and these are stored in ECI-accessory memory. The stored parameters include the needed configuration and identification data.

## 3 DATA COMMUNICATION PROTOCOLS

In order to make the data communication possible, there must be a common set of rules and instructions that each device follows. A specific set of communication rules is called a protocol. The purpose of this chapter is to introduce the data communication protocols used to relay information between the concerning interfaces. [30]

All data communications concerning the main processor occur using the I<sup>2</sup>C-protocol. Its integrated addressing and data-transfer protocol allow systems to be almost completely software-defined. All things concerning the I<sup>2</sup>C-protocol are covered only on the basis of making the electronics design and measurements concerning this thesis possible, i.e. many features concerning the I<sup>2</sup>C-protocol are deliberately left out of the content. For example, only the used speed-mode, i.e. data transfer rate, is being covered while the other possibilities are deliberately being left out of the content. [3]

Data communications concerning externally connected accessories are being handled using the ECI-protocol. Theory behind the I<sup>2</sup>C-protocol is covered in more detail than the theory concerning the ECI-protocol as the ECI-protocol is currently determined to be classified by Nokia. In this thesis the ECI-protocol is defined on a need-to-know basis. Only a brief introduction concerning the communication protocol is given, but the things affecting the electronics design and the required measurements are being defined in detail.

# 3.1 I<sup>2</sup>C-bus specification

I<sup>2</sup>C-bus is an invention developed by Philips Semiconductors over 20 years ago. It is mainly used to attach low-speed peripherals to a motherboard, embedded systems or, like in this case, to a mobile phone main processor. For example, Nokia uses I<sup>2</sup>C-protocol in its phones to attach sensors and other peripherals such as touch control, camera control, backlight control, GPS, NFC, ECI and many others. [2]

Several competitors such as Atmel have brought their own I<sup>2</sup>C-products on the market or even developed their own I<sup>2</sup>C-compatible communication interfaces. Atmel's version of I<sup>2</sup>C Interface is called the Two Wire Interface (TWI) and is fully I<sup>2</sup>C-compatible except for some particularities. As far as this thesis is concerned, both interfaces are identical, and all items referring to the I<sup>2</sup>C interface are equally valid for the TWI. [5], [6]

### 3.1.1 I<sup>2</sup>C-bus features

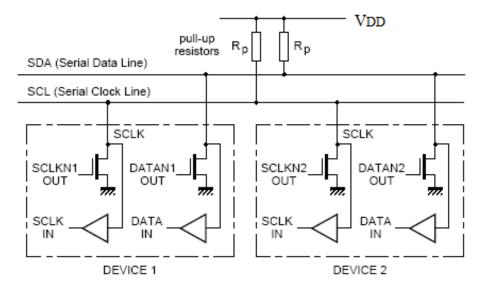

The I<sup>2</sup>C-bus is a bi-directional, bus communication interface, which uses only two signal lines for communication. The two I<sup>2</sup>C-lines are called serial data line (SDA) and serial clock line (SCL). Virtually any number of slaves and any number of masters can be connected onto these 2 signal lines. The number is limited only by a maximum bus capacitance. I<sup>2</sup>C-devices can be added or removed from a system without affecting the functionality of any other circuits on the bus. This makes the debugging relatively easy and may be the biggest benefit compared to many other bus protocols as the source of the problem is easy to locate and malfunctions can be quickly traced. [2]

The master device initiates and terminates the data transfer on the bus and generates the clock signals to permit the transfer. The addressed device is considered to be the slave. Devices are distinguished from each other by unique software configurable addresses. [3]

The master is always the device driving the SCL-line. The slaves are devices that respond to the master and cannot initiate a transfer over the I<sup>2</sup>C-bus; only a master can do that. I<sup>2</sup>C is a multi-master bus, i.e. it is possible to connect more than one master to the bus. More than one master could try to initiate a data transfer at the same time. Therefore, the bus includes data collision detection and arbitration to prevent data corruption if masters simultaneously initiate data transfer. Such features are not necessary in case of this design. The main processor is the master and all other I<sup>2</sup>C-devices sharing the same bus are slaves, including the ECI-controller. [3], [2]

Data on the I<sup>2</sup>C-bus can be transferred at rates of up to 100 kbit/s in the Standard-mode, up to 400 kbit/s in the Fast-mode and up to 3,4 Mbit/s in the High-speed mode. ECI-implementation uses the Fast-mode; therefore the maximum clock frequency is 400 kHz. [2]

Due to the variety of different transistor technologies, such as CMOS, NMOS and BJT which can be connected to the  $I^2C$ -bus, the levels of the logical '0' (low) and '1' (high) are not fixed and depend on the associated level of the supply voltage. Devices with a variety of supply voltages can share the same bus. According to the  $I^2C$  specification, the logical high and low levels are set as 70% and 30% of the pull-up voltage. By keeping any waveform distortions below 30% of  $V_{CC}$ , that portion of the rising edge will not be counted as part of the formal rise time. [2]

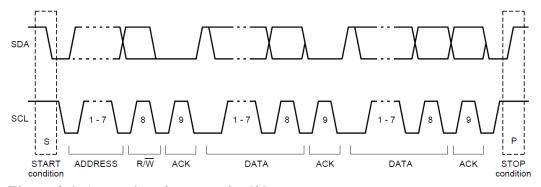

## 3.1.2 I<sup>2</sup>C-communication procedure

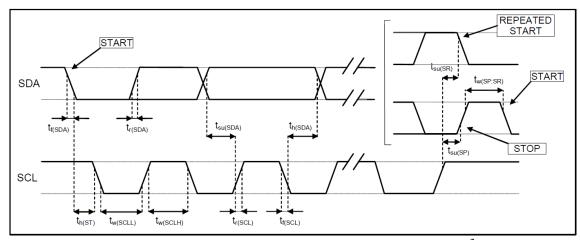

Figure 3.1 presents the different conditions related to a complete data transfer on the I<sup>2</sup>C-bus. All data transfers follow the format presented in the Figure 3.1. The basic ground rules for the I<sup>2</sup>C-communication procedure are:

- the data on the SDA line must be stable during the HIGH period of the clock

- the HIGH or LOW state of the data line can only change when the clock signal on the SCL line is LOW

- one clock pulse is generated for each data bit transferred

- all transactions begin with a START (S) condition

- all transactions are terminated by a STOP (P) condition

- every byte put on the SDA line must be 8-bits long

- each byte must be followed by an acknowledge bit

- data is transferred with the most significant bit first. [2], [3]

Figure 3.1. A complete data transfer [2]

A START condition (S) marks the beginning of a data transaction. The master issues the START condition by indicating a high to low transition on the SDA line while the SCL line is kept high. After the start condition a 7-bit long slave address is being sent by the master. The 8<sup>th</sup> bit is a data direction bit – LOW state indicates a transmission (WRITE), HIGH state indicates a request for data (READ). The 9<sup>th</sup> bit is the Acknowledge (ACK) bit or the Not Acknowledge (NACK) bit. At that moment, the master-transmitter becomes a master-receiver and the slave-receiver becomes a slave-transmitter. The first acknowledge is generated by the slave. Subsequent acknowledges are generated by the master. [2], [5]

The acknowledge takes place after every byte and data direction bit. The acknowledge bit allows the receiver to report the transmitter that the byte was successfully received and another byte may be sent. The number of bytes that can be transmitted per transfer is unrestricted. If the NACK is received, the data transfer is immediately terminated by a STOP condition, always generated by the master. STOP condition is indicated by a low to high transition on the SDA line while SCL line is kept high. There are five conditions that lead to the generation of a NACK:

- No receiver is present on the bus with the transmitted address

- The receiver is unable to receive or transmit because it's performing some other tasks and is not ready to start the communication with the master

- During the transfer the receiver gets data or commands that it does not understand

- During the transfer the receiver cannot receive any more data bytes

- The master signals the slave of the end of the transfer. [2], [5]

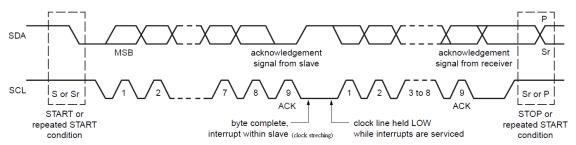

However, instead of a STOP condition, if the master still wants to communicate on the bus, it can generate a repeated START (Sr) condition to speed up the communication process. The START and repeated START conditions are functionally identical. By generating the repeated START, the master can address another slave faster as it does not have to generate the START and STOP conditions separately. The bus also needs to be free for a period of time between the START and STOP conditions. Figure 3.2 presents the data transfer on the I<sup>2</sup>C-bus. Repeated START condition is illustrated in the figure. [2]

**Figure 3.2.** Data transfer on the  $I^2C$ -bus [2]

Slave devices are not always fast enough in processing the data, so if a slave cannot receive or transmit another complete byte of data until it has performed some other function, it can pause a transaction and hold the clock line SCL low, in which case the master goes into a wait state. The master generates the clock, monitors the voltage on the SCL bus, immediately knows if there is a problem, and then waits until the slave releases the SCL line. The transaction cannot continue until the line is released HIGH again. Data transfers then continue when the slave is ready for another byte of data and release clock line SCL. [3]

For example, a device may be able to receive the data fast enough but needs more time to store the received byte or prepare another byte to be transmitted. Such a feature is illustrated in Figure 3.2 and is called clock stretching. As an exception to a normal slave device behavior, the slave device having the clock stretching capability must be able to drive the clock line in order to be able to control the clock. For I<sup>2</sup>C-buses shared by multiple devices, it is important to estimate the impacts of clock stretching as the total bandwidth of the shared bus might be decreased. Causing the clock to stretch, the slowest I<sup>2</sup>C device dominates the bus performance. Clock stretching also causes some extra current consumption. [2], [3], [5]

# 3.2 ECI-bus protocol

From the electronics point of view, the ECI-bus is very much like the  $I^2C$ -bus protocol. Both protocols use the same output stage technique for communication. Basically, a single  $I^2C$ -bus protocol's signal line is excluded from the design.

High and low levels of the ECI-bus protocol are not fixed, as they are not in the  $I^2C$ -bus protocol either. The biggest difference between the  $I^2C$ -protocol and the ECI-

protocol is the fact that the  $I^2C$  is a synchronous communication protocol having a separate clock line, and the ECI is an asynchronous communication protocol without a separate clock line. [3]

The ECI controller must be able to tolerate large clock tolerances, therefore the ECI controller must be able to adapt to the current speed of the slave. The master adapts to the speed on the basis of the learning sequence sent by the slave. After the learning sequence, the data bit width is T. The sampling at the receiving end is done at T/2, i.e. in the middle of the bit, regarding to the starting rising edge of the START-pulse.

# 4 INPUT/OUTPUT STAGE ELECTRONICS

The goal of this chapter is to introduce the electronics concerning the implementation of the data buses, as well as provide the information needed for understanding the electrical measurements. Many items concerning the electronics are deliberately left out of the content and only the relevant items concerning the ECI implementation are being covered.

The open-drain output circuit technique, used by I<sup>2</sup>C-protocol and the ECI-protocol, is covered in depth as it plays a major role in designing the circuit. Whereas the input part just scratches the surface as its significance towards the designed circuit is relatively small, because the input stages are already implemented inside the ICs. In addition, the basics of the push-pull output circuits are covered. [3]

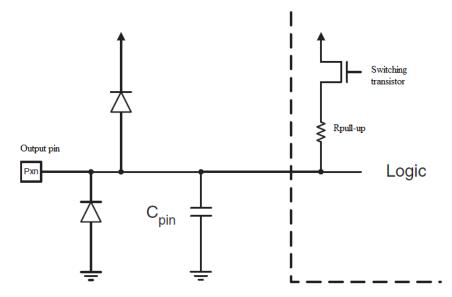

## 4.1 Open-drain output

An open-drain output is a driver stage that can transmit data by pulling the bus low. An input stage, meant for receiving the data sent by the open-drain output, consists of high impedance sense amplifiers that monitor the bus voltage. The circuit technique allows multiple devices to communicate bi-directionally on a single wire. I<sup>2</sup>C-protocol requires two wires to work. It consists of two active wires and a ground connection, while the ECI has only one active wire used for communication. Electronic designs behind both bus protocols are basically the same. The only physical difference is the number of wires. [2], [7, p. 487-489]

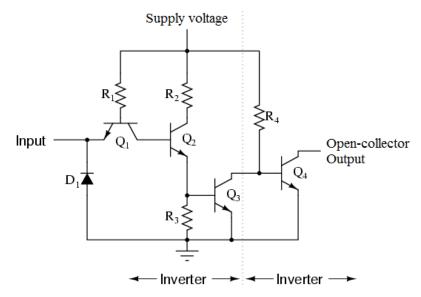

All I<sup>2</sup>C-bus outputs are implemented using the open-drain or the open-collector circuit design presented in Figure 4.1. The output is called open-collector when using bipolar transistor and open-drain, if the used device is implemented using FET-technology. [2]

Instead of outputting a signal of a specific voltage or current, the output is not capable of supplying current to the signal line. The needed current is drawn from a positive supply voltage, named as  $V_{DD}$  in Figure 4.1, via pull-up resistor, i.e. a resistor tied to  $V_{DD}$ . A pull-up resistor provides the simplest means of tying off unused inputs. A great number of inputs can be connected with a pull-up resistor without violating minimum high or low input level requirements, since input currents are very low, usually as low as  $1...10~\mu A$  for most CMOS devices. [12, p. 205]

*Figure 4.1.*  $I^2C$  *Hardware architecture* [2]

It is generally not wise or practical to connect too many devices together. The longer the line is, the greater the chance for coupled noise and bigger the bus capacitance will be. Also, the troubleshooting of a short-circuited line tied to a great number of points can be very difficult because the exact cause for a problem may be hard to find. One device not working as the way it should, may cause the whole bus to malfunction. [12, p. 205]

The operation of the open-drain output is simple. When the bus is free and the transistors are closed, the signal is on high state. The pull-up voltage determines the value of the high state. The output signal of an I<sup>2</sup>C-device is basically applied to the base/gate of an internal transistor. To initiate communication, an I<sup>2</sup>C-device pulls the SDA line low by turning on the output stage transistor. Generation of clock signals on the I<sup>2</sup>C-bus is always the responsibility of the master, so it is not necessary for the slave device to have an output stage on the SCL bus line. Only the master can enable its pull-up circuit. In order for the slave device to obtain permission for pulling down the SDA line, the master must first send the READ command to the slave device. In other words, the master is controlling the on-time of the slave device's output transistor. [2]

A series resistor is sometimes needed for protection against high-voltage spikes, or in some cases against overcurrent on the SDA and SCL lines. If series resistors are used, the additional resistance must be taken into consideration when calculating the value of the pull-up resistor and allowable bus capacitance. A series resistor slows down the output fall time and together with the pull-up resistor affects the static low level of the I<sup>2</sup>C-lines. The use of a series resistor leads to different voltage levels at master's and slave's input during the LOW phase, depending on which device currently pulls SDA or SCL low. Thus, it is possible to recognize which I<sup>2</sup>C device is currently active by analyzing the low level on the I<sup>2</sup>C lines. [2], [5]

### 4.1.1 Defining the pull-up resistor

Defining the pull-up resistor is a compromise between the current consumption and the rise time of the signal. Rise time is determined to be the time period between the logical low and logical high levels of the rising edge of the CLK/SDA-signal. [3], [2]

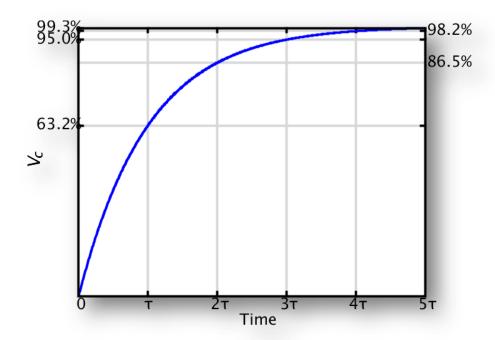

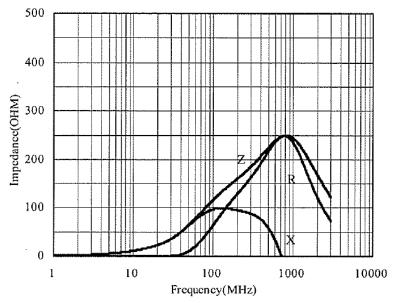

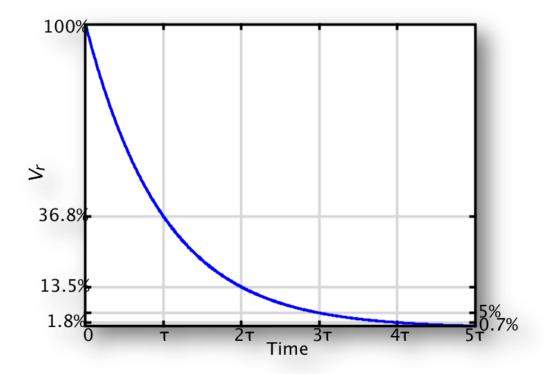

The bus capacitance caused by the parasitic capacitances and the pull-up resistor together form an RC-circuit. According to the Equation 4.1, RC time constant  $\tau$  is equal to the product of the circuit resistance and the circuit capacitance. It is determined as the time required to charge the capacitor through the resistor to about 63 percent of full charge. Calculating the time constant is not usable as such for defining the resistor, but taking the used logical high and low levels into consideration the equation becomes much more useful. [3], [2]

Capacitor's charging curve is presented in Figure 4.2. The used time unit, presented in the horizontal axis, is the time constant  $\tau$ . The pull-up voltage with percentages of its final value is presented in the vertical axis. After a period equivalent to five time constants, the capacitor in this RC charging circuit is virtually fully charged and the voltage across the capacitor is now approximately 99% of its maximum value. [3], [2]

*Figure 4.2.* Capacitor's charging curve with percentages of final value [15]

General arithmetic operation for determining the voltage Vc(t) across the bus capacitance is presented in Equation 4.2, where t is the time since the charging started. The voltage Vc(t) is also the voltage that the input stage of the data bus sees. The voltage  $V_{pull-up}$  is the supply voltage or the pull-up voltage of the bus line presented in Figure 4.1. Equations 4.3 and 4.5 are the same as Equation 4.2, except that they take the related input thresholds into consideration. The time  $t_1$  spent in charging the capacitor to

logic low level is presented in Equation 4.4 and the time  $t_2$  spent in charging the capacitor to logic high level is presented in Equation 4.6. Rise time of the signal is the time spent between the logic low and high levels. Calculating the value for the signal rise time T is presented in Equation 4.7. [2], [7, p. 23-24]

According to the I<sup>2</sup>C-specification the maximum rise time for a signal working in Fast-mode is 300 ns. The minimum value is determined to be 20 ns and a sum of the actual rise time, which can be calculated using Equation 4.7, multiplied by 0.1. For bus loads up to 200 pF, the pull-up device for each bus line can be a resistor and for bus loads between 200 pF and 400 pF, the pull-up device can be a current source or a switched resistor circuit. [2]

The discharge of an RC circuit occurs following the same principles as the charging of the circuit. According to Equation 4.1 the time constant  $\tau$  is determined as the time required to discharge the capacitor, through the total resistance of the discharge path, to about 37% percent of full charge. As the charging turns into discharging, Equation 4.2 is adjusted to form presented in Equation 4.8. [2], [7, p. 23-24]

$$\tau = RC \tag{4.1}$$

$$Vc(t) = V_{pull-up} \times (1 - e^{-\frac{t}{RC}})$$

(4.2)

$$Vc(t1) = 0.3 \times V_{pull-up} = V_{pull-up} \times (1 - e^{-\frac{t1}{RC}})$$

(4.3)

$$t_1 = 0.3566749 \times RC \tag{4.4}$$

$$Vc(t2) = 0.7 \times V_{pull-up} = V_{pull-up} \times (1 - e^{-\frac{t2}{RC}})$$

(4.5)

$$t_2 = 1,2039729 \times RC \tag{4.6}$$

$$T = t_2 - t_1 = 0.8473 \times RC \tag{4.7}$$

$$Vc(t) = V_{pull-up} \times e^{-\frac{t}{RC}}$$

(4.8)

The bus capacitance is always an estimate during the schematic design phase as the most significant part of the formation of the total bus capacitance is a sum of many different components, e.g. traces of the PWB, connections and pins. This capacitance limits the maximum value of the pull-up resistor due to the specified maximum rise time. A high bus capacitance can be compensated with a low pull-up resistor and vice versa. [2], [3]

Maximum value for the pull-up resistor can be determined using the Equation 4.9. The size of the final bus capacitance is impossible to know before the final layout

design. The value can be simulated with reasonable accuracy, but usually the best resort is to use previously proven estimates and just estimate a suitable resistor value. If the operational performance of the bus does not meet the specifications, the value of the pull-up resistor can always be fine-tuned afterwards. [2]

$$R_{pull-up,max} = \frac{T}{0.8473 \times C} \tag{4.9}$$

The bus capacitance in this design must be as low as possible, because more capacitance means bigger value for time constant, which means more reduction to signal rise times. The signal rise times and the current consumption go hand in hand, so the bigger the bus capacitance, the smaller the pull-up resistor and higher the current consumption will be. An educated guess for the bus capacitance in this case is no more than 50 pF at maximum. The main reason for such a low value is the very short wires. Maximum and minimum values for the pull-up resistor in a bus having a bus capacitance of 50 pF are calculated based on Equation 4.9 in Equations 4.10 and 4.11.

$$R_{pull-up,max} = \frac{300 \, ns}{0.8473 \times 50 \, pF} \approx 7 \, k\Omega \tag{4.10}$$

$$R_{pull-up,min} = \frac{20 \, ns}{0.8473 \times 50 \, pF} \times 1.1 \approx 519 \,\Omega$$

(4.11)

When the signal is pulled down, the bus capacitance is slowing down the falling edge just the way it is affecting the rising edge of the signal. The value of the time constant  $\tau$  can be determined using the Equation 4.1. The only difference during the discharge period is that the capacitor is not discharging through the pull-up resistor, but instead it discharges through the transistor straight to ground. The path to ground is almost non-resistive and the value of the time constant is very small and the effect of the bus time constant can be completely ignored, unless a serial resistor is placed to the data path. [2], [5]

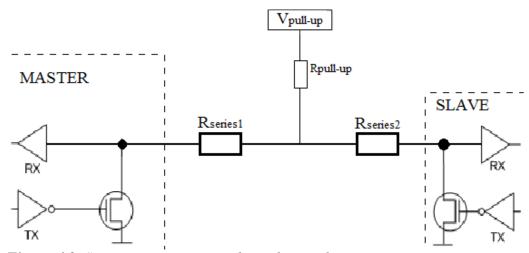

The two possible placements for  $R_{series1}$  and  $R_{series2}$  are presented in Figure 4.3. If the placed resistor is  $R_{series1}$ , the voltage low level  $V_{low}$  at slave's input when the master-transistor is in a conducting state could be calculated using the Equation 4.12. When the slave-transistor is in conducting state, the master's input voltage low level  $V_{low}$  is hardly rising at all, because the pull-up resistor  $R_{pull-up}$  is not affecting the formation of the voltage level. [2]

Correspondingly, if the placed resistor is  $R_{\text{series2}}$ , the low voltage level at master's input when slave-transistor is pulling the line to ground could be calculated using the same equation. When the master-transistor is in a conducting state, the slave's input voltage low level is hardly rising at all, because the pull-up resistor is also not affecting the formation of the voltage level. [2]

$$V_{low} = \frac{R_{series}}{R_{pull-up} + R_{series}} \times V_{pull-up}$$

(4.12)

Figure 4.3. Series resistor in open-drain data path

The maximum values for the fall time of the signal are determined to be the same as the limits for the signal rise time. According to I<sup>2</sup>C specification, the maximum fall time for a signal working in Fast-mode is 300 nanoseconds. The limit for the minimum fall time is slightly smaller than the limit for the minimum rise time, because the value of the time constant is smaller during the capacitor discharge than during capacitor charge period. [2]

If a series resistor is inserted, it slows down the falling edges of the signal. The fall time cannot be calculated using the normal RC circuit fall time determining Equations 3.1-3.7 because another determinant factor in the formation of the fall time is the switching speed of the transistor. The maximum value of the series resistor is generally limited by the maximum input voltage low level at one input. Which one, depends of the placement of the series resistor. This all is of course dependent on the switching speed of the transistor. If the switching speed is already near the maximum fall time limit of 300 ns, even a small series resistor would cause the fall time to be too slow and rule out the placement of the resistor completely. [3], [12, p.181-182]

Sometimes a series resistor could also be useful. If a transistor has a switching speed under the minimum fall time limit, a small series resistor could slow down the falling edges enough and also decrease the voltage-spikes for the line to fulfill the I<sup>2</sup>C specifications and ensure the correct operation of the devices connected to I<sup>2</sup>C-bus. [3], [12, p.181-182]

### 4.1.2 Current consumption

Current is required to establish a voltage potential across the capacitor. If a small resistance causing large current, is in series with the capacitor, the charge time will be

short. If a large resistor causing small current is in series, the charge time will be long. Longer rise time means lower current consumption. Therefore, the bigger the pull-up resistor, the lower the current consumption. [2]

Input current and off-state output current are extremely small for the used CMOS type I/O-devices. Basically, the bus is drawing current only when a transistor is in a conducting state, but because of the current needed to charge the parasitic capacitances the current consumption slightly increases. The transient current flowing through the selected pull-up resistor when one of the output transistors is open can be determined using the Equation 4.13. The current is also the maximum current possible in the circuit. The small bus capacitance does not have any meaningful significance to the current consumption, except for the slight increase in time needed for the charging of the capacitor after the transistor switch has been closed. The current decreases exponentially during the short charging event, therefore the extra current drawn during the charging period is relatively small. [2]

$$I_{pull-up} = \frac{V_{pull-up}}{R_{pull-up}} \tag{4.13}$$

When the pull-up resistor selections in the electrical design in Appendix A are not predetermined, they are selected to be as big as possible within the limits of the I<sup>2</sup>C- or any other specification in question in order to achieve as low current consumption as possible.

Two circuit elements placed nearby will always interact capacitively. The faster the rising edge, the bigger the chance of formation of crosstalk due to the mutual capacitance. Sudden changes in current cause greater problems with inductive coupling. Thus, fast edges are also more probable in causing EMC-problems and have to be avoided as well as possible. [10, p. 60-61]

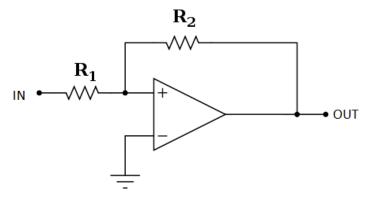

# 4.2 Schmitt-trigger input

I<sup>2</sup>C-bus inputs are implemented using high impedance sense amplifiers like Schmitt-triggers. The Schmitt-trigger is a comparator application which switches the output HIGH when the input passes upward through a positive reference voltage. Parallel positive feedback creates the needed hysteresis that is controlled by the proportion between the resistances of R1 and R2 and prevents switching back to the other state until the input passes through a lower threshold voltage. [5], [7, p. 231-232], [9, p. 679-682]

When the circuit input voltage is above the high threshold or below the low threshold, the output follows the input value, i.e. the output voltage has the same sign as the circuit input voltage. Figure 4.4 presents a schematic of a basic non-inverting Schmitt-trigger. [5], [7, p. 231-232], [9, p. 679-682]

Figure 4.4. A non-inverting Schmitt-trigger

Schmitt-trigger has a built-in hysteresis effect, which is very effective in switching against rapid triggering and makes it very effective in noise reduction. Schmitt-trigger action at all inputs also makes the circuit tolerant for slower input rise and fall times. [5]

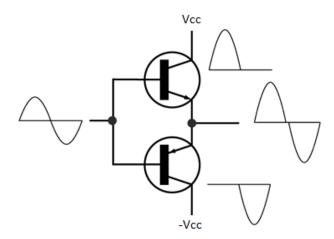

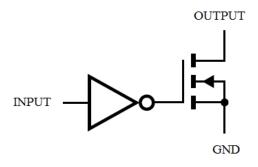

### 4.3 Push-pull output

The most common used digital logic output circuit is called push-pull or active pull-up. The output is held either HIGH or LOW through a conducting transistor or MOSFET. Output is generally realized as a complementary pair of transistors or MOSFETs, one sinking current from the load to ground or a negative power supply, and the other supplying or sourcing current to the load from a positive power supply. A basic push-pull output circuit is presented in Figure 4.5 [7, p. 487-488]

Figure 4.5. Push-pull output circuit

Push-pull output provides low output impedance in both states, giving faster switching time and better noise immunity, as compared with an open-drain output with passive drain resistor. In the case of CMOS, it also results in lower power dissipation. Significant power is only drawn when the transistors in the CMOS device are switching between on and off states, i.e. when the gate capacitance is being charged or discharged. Possibly the greatest disadvantage of the push-pull output is the fact that it cannot be

used to drive a bus, since the output cannot be disconnected from the shared data lines. The output holds the data line either HIGH or LOW at all times. [7, p. 487-488], [15, p. 25]

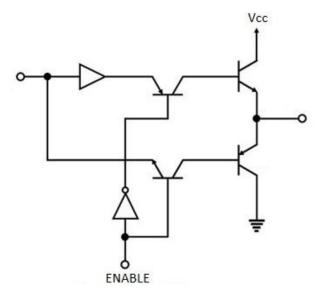

Another output stage type is a gate whose output can be floating, i.e. an output port with a high impedance state in addition to the 0 and 1 logic levels. The high impedance state effectively removes the influence of the output from the circuit. Such devices come in two varieties; three-state devices and open-drain devices. Open-drain devices are mainly used in situations, where the speed is negligible or there are no high speed requirements. Figure 6.4 presents a realization of a three-state push-pull output with BJTs. Logic HIGH at the ENABLE-pin enables the output and logic LOW disables the output by putting the output pin in high-impedance mode, i.e. both output transistors in a non-conducting state. [7, p. 487-488]

Figure 4.6. Three-state output circuit [8]

A separate enable-input determines whether the three-state output behaves like an ordinary push-pull output or goes into the high impedance state, regardless of the logic levels present at the other inputs. A device with three-state output behaves exactly like ordinary push-pull logic when enabled, always driving its output either HIGH or LOW. If the output is disabled, it effectively disconnects its output, so another logic device can drive the same line. So, basically it is a push-pull with a disable feature. [7, p. 487-488]

## 5 ECI IMPLEMENTATION

This chapter includes the justifications for the selection of the ECI-controller and introduces the ground rules and general requirements concerning the ECI implementation, focusing on the design of the electrical circuitry. Individual component characteristics and the requirements set by them will be introduced in later chapters, although most of the requirements set by the ECI-controller are covered in this chapter.

Unlike many other design issues, EMC is not an area where it is possible to list a set of rules that work with certainty or the rules are considered more as guidelines. EMC must always be considered as a system-level issue. EMC compliance cannot be guaranteed by design; it must be tested. [17], [11]

A good EMC design requires more knowledge than what can put into this thesis and the EMC design itself is not a subject of this thesis, any in-depth review of the subject is left out. Yet, the problems caused by the EMC are essential on the design point of view. Therefore, the problems caused by the EMC and the effects it has on the design of the electrical circuitry are covered as well as the most crucial EMC components, but only on a need-to-know basis. All the capacitor values and the final selections of the components affecting to the certain frequency bandwidths are determined based on the EMC testing.

The first step in the design was to choose the method of ECI-to-I<sup>2</sup>C implementation. Many functionalities and electrical parameters were mandatory. ECI must be able to handle the data conversion from I<sup>2</sup>C-protocol to ECI-protocol and the other way round, so a block where the data conversion is done must be included. This block is called ECI-controller.

### 5.1 ECI-controller selection

The first and the least demanding option from the electronics point of view, is to use the main processor to handle the tasks demanded by an ECI-controller. That could be possible in theory, but there is one decisive limitation to be taken into consideration. An ECI-ASIC inside an accessory does not have a buffer memory for button presses, so the button data must be read during the button is pressed. That means there is only limited time to read the data. The main processor might be busy with other tasks and will be unable to carry out the data processing in time. Therefore, the use of the main processor as an ECI-controller is not a feasible option. The controller must be able to act as a time buffer and store the data for the main processor. All in all, the ECI-controller is needed mainly for two reasons:

- to convert the ECI-protocol data into I<sup>2</sup>C-protocol

- to act as a time buffer.

At the beginning of the actual decision making process there are three viable options from which to choose. The first is to implement the entire ECI-block using an FPGA. The second option is to use an ASIC for implementation. The last option is a microcontroller accompanied by some discrete components. The decision between the implementation possibilities is principally made on the basis of:

- cost

- size versus available space

- schedule.

The cheapest of the three is an ASIC when considering mass production. If the manufacturing lot is small, the cost per ASIC is relatively high. On the other hand, the bigger the amount of manufactured ASICs, the cheaper would the price be per individual ASIC. The expected size of the production lot is substantial, so the expected price is relatively low. [31]

The implementation using a microcontroller as a base of the ECI-block is the considerably more expensive implementation option. The cost of an FPGA based implementation would probably be even higher than the cost of a microcontroller based implementation and the manufacturing costs are not as production-lot-size-dependent as they are on the case of an ASIC. FPGA was basically rejected because it loses the price comparison to ASIC-option and Nokia has much more experience in using ASICs than FPGAs. Both would be made by vendors on the grounds of Nokia's requirements. [31]

An ASIC takes the smallest amount of space. This is true even when compared to an FPGA, which takes significantly more space from the circuit board. The size of a microcontroller is roughly the size of an FPGA, but it needs some discrete components in addition to the actual controller circuit. The spacing and routing would also take extra space if discrete components are used. [31]

A huge advantage of the microcontroller is the maturity of the technology. Microcontrollers in general are widely used and Nokia has much experience using them. If a microcontroller is selected, an off-the-shelf device could be used and the in-house-development could be started right away.

ASIC is a common technology, but its greatest disadvantage is the lack of flexibility and the schedule in general, i.e. the difficulty of making changes to the silicon. If the designed circuit inside the ASIC contains any errors, the fixing process takes a lot of time and money because an ASIC can no longer be altered after production. That is why the design must be perfect, especially when making large quantities of the same ASIC. [31]

The biggest advantage of an FPGA over an ASIC is the flexibility and speed of changes. This is partially because it is not as hardware dependent as the ASIC, and

changes do not require as much money. An FPGA is basically a reprogrammable integrated circuit. Because of its programmable nature, it is possible to correct mistakes and to send out patches or updates after the manufacturing. [31]

In case of a microcontroller, the biggest advantage is its superior flexibility to changes. Minor changes or even addition of new features are possible even during the manufacturing due to the re-programming possibility of the microcontroller. There are also several other factors besides the cost, size and timetable issues to be taken into consideration during the decision making process.

A microcontroller is the best solution from the software point of view because the development could be started right away, the development cost would be the smallest and the development could be done in the same location as the hardware designing and testing, which allows face to face communication between the software and hardware personnel. The information between the two parties would travel in real-time, which is a huge advantage if any unexpected errors occur during the overall development process.

Requirements for the ECI were not 100% clear and they tend to change during the development process. It could also be possible that the ECI-controller must be able to handle some additional features, which were still speculations during the planning process. A microcontroller was chosen to be the base of the design, because the overall flexibility is considered to be more important than a few cents of extra cost per unit. Minor additions or changes at a later date would also be possible to implement with a tight schedule, without major effort or resources.

### 5.1.1 ATtiny20 microcontroller

The decision of which microcontroller to use is a pre-determined decision. Nokia has certain reference components and preferred suppliers from which to choose. Atmel's ATtiny20 has been proven to be a strong performer and was chosen to be the base of the ECI. The simplified block diagram of the ECI after the decision of using a microcontroller looks the same as the block diagram in Figure 2.4.

ATtiny20 is a low-power CMOS 8-bit microcontroller. It can run either on internal oscillator or external clock. It includes two kilobytes of in-system programmable flash memory, and 128 bytes of internal SRAM, which should be more than enough for the task at hand. [6]

The communication bus to the main processor is I<sup>2</sup>C-compliant TWI, which uses two dedicated serial ports with open-drain outputs; SDA and SCL. The microcontroller also has twelve general purpose I/O-ports with all port pins having individually selectable pull-up resistors with a supply-voltage invariant resistance, i.e. open-drain outputs with internal pull-up resistors, which can be used or alternatively, external pull-up resistors can be used. All of those general I/O-ports also have push-pull output stages and the system designer can determine which option to use. [6]

Most port pins have alternate functions in addition to being general digital I/O-ports. Port A pin PA1 has an alternate function of being a positive input of an analog comparator and Port A pin PA2 has an alternate function of being a negative input of

the same analog comparator. The comparator can be used to provide an external level triggered interrupt to the microcontroller. [6]

ATtiny20 also provides various sleep modes to tailor the power consumption to the application's requirements; power-down, standby, ADC noise reduction and idle. The utilized modes are standby and idle. [6]

Idle mode stops the CPU while allowing the SRAM, timer/counter, ADC, analog comparator and interrupt system to continue functioning. In Standby mode, the oscillator is running while the rest of the device is sleeping, allowing very fast start-up combined with low power consumption. [6]

A low level on the reset pin for longer than the minimum pulse length will generate a reset, even if the clock is not running. An external reset pulse will wake-up the microcontroller from any of the sleep modes. [6]

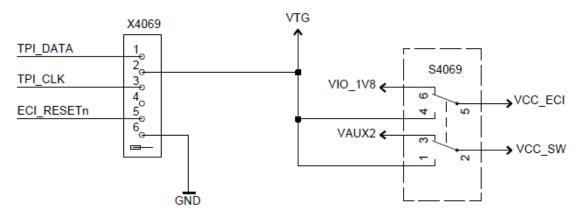

There must be a reprogramming possibility available during the development phase, i.e. after the microcontroller has been placed to the circuit board. The voltage during the programming is 5 V, which is much more than its normal operating voltage. The microcontroller supports operating voltages between 1.8...5.5 V, but the needed and also available supply voltage is 2.5 V at maximum. Thus, the high programming voltage sets some demands to the electrical circuit around the controller. [6]

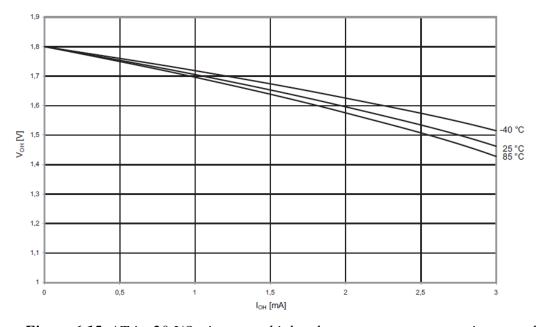

The electrical characteristics, or more precisely, the I/O-voltage levels, are determined according to the used supply voltage. I<sup>2</sup>C voltage high level at the main processor end is fixed to 1.8 volts. The ECI-data voltage high level is 2.1 V at minimum, so the supply voltage for the microcontroller must be 1.8 V, 2.1 V or more, depending on the used ECI-data high voltage level. On the electrical circuitry point of view, it does not matter which one of the possible supply voltage values gets chosen, because a voltage level shifting must be done either way.

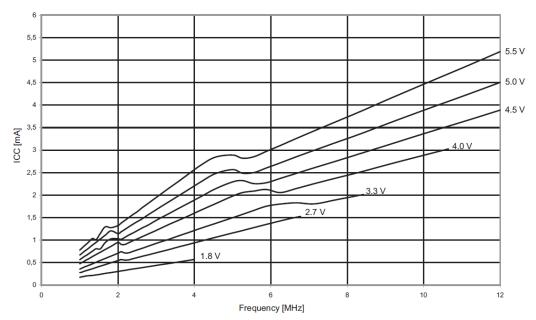

The lower the supply voltage is, the lower the current consumption will also be. Current consumption is a function of several factors such as operating voltage, operating frequency, loading of I/O-pins, switching rate of I/O-pins, code executed and ambient temperature. The dominating factors are operating voltage and frequency. Current consumption for the ATtiny20 in relation to the used frequency in active mode is presented in Figure 5.1. The figure also presents the dependency between the current consumption and processing speed. If the fastest processing speed is not needed, the system designer is allowed to optimize the system by lowering the processing speed. On the basis of the current consumption and the needed voltage levels, the supply voltage of the microcontroller was decided to be 1.8 volts. [6], [18]

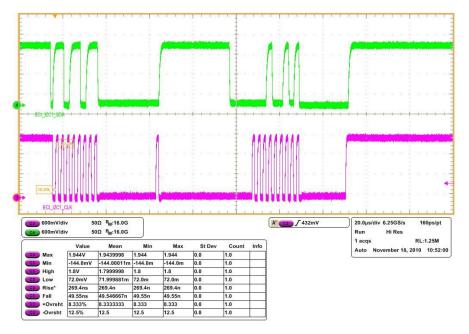

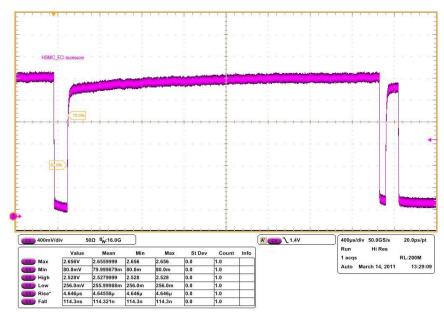

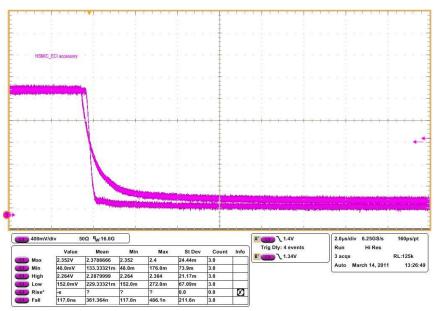

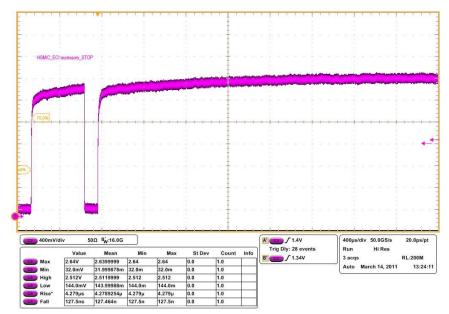

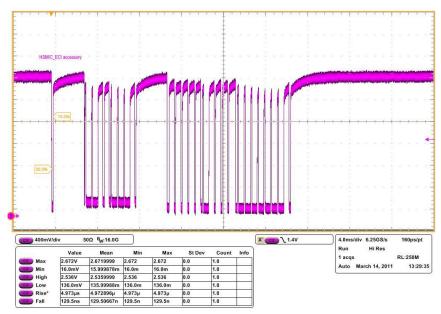

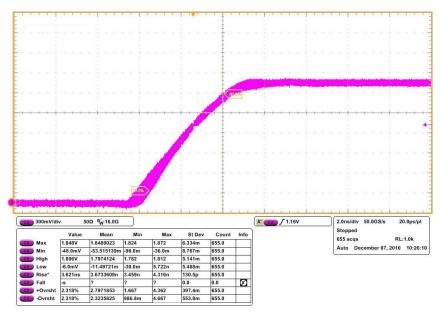

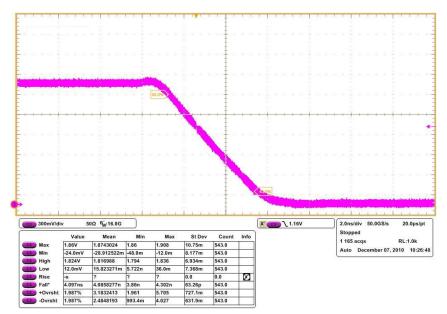

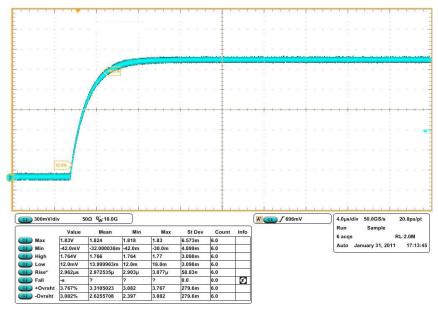

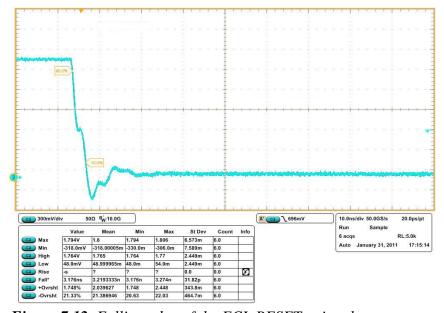

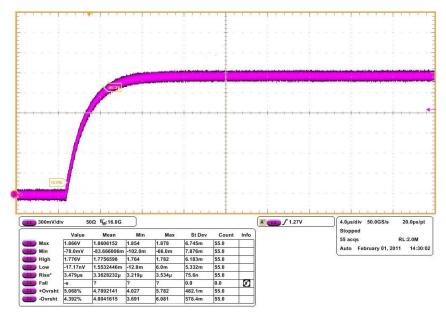

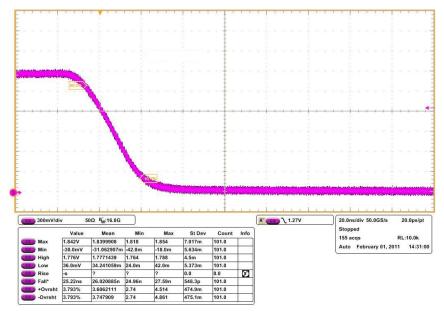

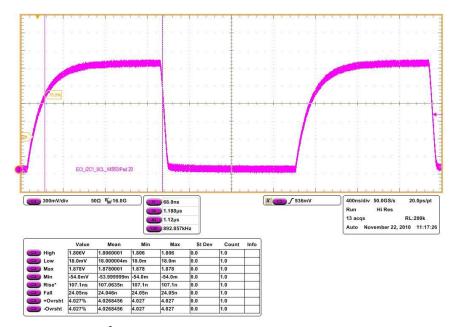

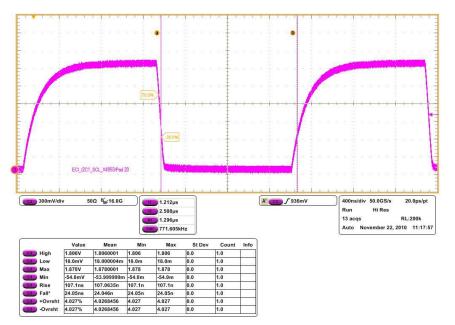

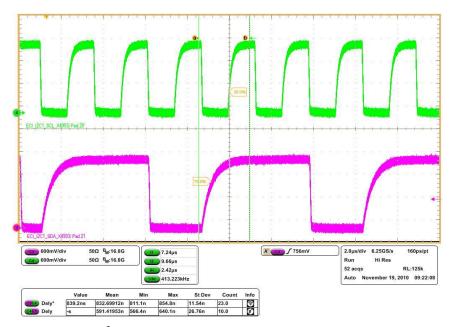

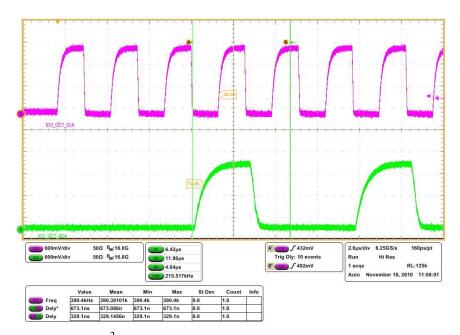

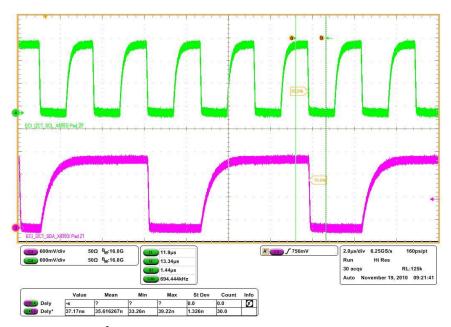

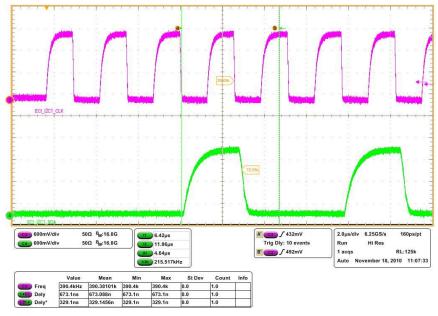

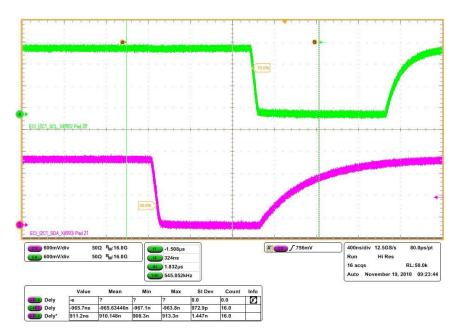

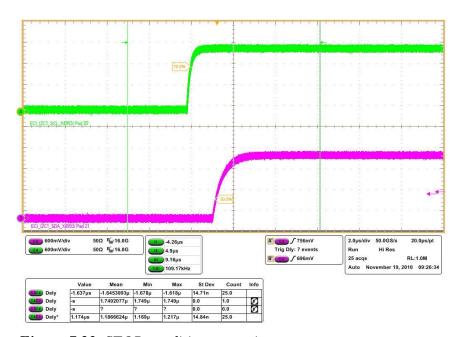

Figure 5.1. ATtiny20 active supply current versus Frequency (1-12 MHz)[6]