Thomas Szymkowiak

# FPGA-BASED PROTOTYPING OF A MODERN MPSOC

Master of Science Thesis Faculty of Information Technology and Communication Sciences Examiners: Prof. Timo Hämäläinen Arto Oinonen, M.Sc. December 2023

# ABSTRACT

Thomas Szymkowiak: FPGA-Based Prototyping of a Modern MPSoC Master of Science Thesis Tampere University Information Technology - Embedded Systems December 2023

The complexity of computing systems has been increasing exponentially since the invention of the integrated circuit in the 1950s. This increase in complexity has led to the creation of modern computer architectures such as the Multi-Processor System-on-Chip (MPSoC). The development of MPSoCs is a highly complex and resource-intensive process, with verification forming a significant portion of the activities required to produce a viable design. FPGA-based prototyping is a crucial verification activity used to create an accurate, highly performant hardware model of the system or component subsystems.

This thesis presents an overview of FPGA-based prototyping within the context of modern MPSoC development and an analysis of the application of FPGA-based prototyping within an actual MPSoC development project. The benefits and limitations of FPGA-based prototyping in developing complex ASICs are described in detail.

Keywords: Verification, FPGA, SoC, MPSoC, ASIC, SoC-Hub, RISC-V

The originality of this thesis has been checked using the Turnitin OriginalityCheck service.

# PREFACE

Coming to Finland and working as a part of SoCHub while studying Embedded Systems at Tampere University has been the realisation of a dream. I cannot possibly put into words how thankful I am for the experience. First and foremost, I would like to sincerely thank my family for the endless support that they have provided throughout this process. Additionally, the SoCHub team at Tampere University have been key in making the past 3 years so enjoyable. In no particular order, I would like to personally thank Jarkko Passi, Antti Nurmi, Aisha Ahmed, Arto Oinonen, Matti Käyrä, Antti Rautakoura, Timo Hämäläinen and Sakari Lahti.

Tampere, 31st December 2023

Thomas Szymkowiak

# CONTENTS

| 1. | Intro | oductio | on                                    |  | 1  |

|----|-------|---------|---------------------------------------|--|----|

| 2. | SoC   | C Deve  | elopment                              |  | 2  |

|    | 2.1   | Overv   | view                                  |  | 2  |

|    | 2.2   | Verific | cation Challenges                     |  | 2  |

| 3. | FPC   | GA-bas  | sed Prototyping                       |  | 4  |

|    |       |         | vation for Logic Emulation            |  |    |

|    | 3.2   | FPGA    | A-based Emulation                     |  | 4  |

|    |       | 3.2.1   | Single-FPGA Emulation Platform        |  | 5  |

|    |       | 3.2.2   | Multiple-FPGA Emulation Platform      |  | 6  |

|    |       | 3.2.3   | Standalone FPGA Emulation Platform    |  | 7  |

|    |       | 3.2.4   | In-circuit FPGA Emulation Platform    |  | 7  |

|    |       | 3.2.5   | Co-simulation FPGA Emulation Platform |  | 8  |

|    | 3.3   | FPGA    | A Technology Overview                 |  | 8  |

|    |       | 3.3.1   | Logic Blocks                          |  | 10 |

|    |       | 3.3.2   | IO Blocks                             |  | 10 |

|    |       | 3.3.3   | Memory Blocks                         |  | 10 |

|    |       | 3.3.4   | Routing Networks                      |  | 11 |

|    |       | 3.3.5   | DSP Blocks                            |  | 11 |

|    |       | 3.3.6   | High-speed Transceivers               |  | 11 |

|    |       | 3.3.7   | Embedded Processor Cores              |  | 12 |

|    |       | 3.3.8   | Other Components                      |  | 12 |

|    | 3.4   | FPGA    | A and ASIC Comparison                 |  | 12 |

|    |       | 3.4.1   | Technologies                          |  | 12 |

|    |       | 3.4.2   | Development Flows                     |  | 13 |

|    | 3.5   | Relate  | ed Work                               |  | 13 |

| 4. | Ball  | ast De  | evelopment and Architecture           |  | 17 |

|    | 4.1   | SoC F   | Hub                                   |  | 17 |

|    | 4.2   | Ballas  | st Architecture                       |  | 17 |

|    | 4.3   | Devel   | lopment Methodology                   |  | 17 |

|    | 4.4   | Verific | cation Strategy.                      |  | 18 |

|    |       | 4.4.1   | Functional Coverage.                  |  | 19 |

|    |       | 4.4.2   | FPGA Prototyping.                     |  | 19 |

|    | 4.5   | Subsy   | ystems of Interest                    |  | 20 |

|    |       | 4.5.1   | SysCtrl                               |  | 20 |

|    |     | 4.5.2  | MPC                                                   | 21 |

|----|-----|--------|-------------------------------------------------------|----|

|    |     | 4.5.3  | HPC                                                   | 22 |

|    |     | 4.5.4  | C2C                                                   | 23 |

|    | 4.6 | Debug  | gging Architecture                                    | 24 |

|    |     | 4.6.1  | JTAG                                                  | 24 |

|    |     | 4.6.2  | Debug and Trace                                       | 24 |

|    |     | 4.6.3  | OpenOCD                                               | 25 |

|    |     | 4.6.4  | Ballast Debugging                                     | 26 |

| 5. | FPC | A Pro  | totype Implementation                                 | 28 |

|    | 5.1 | Protot | ype Configurations                                    | 28 |

|    | 5.2 | Platfo | rm Hardware Selection                                 | 29 |

|    |     | 5.2.1  | Digilent PYNQ-Z1                                      | 30 |

|    |     | 5.2.2  | AMD Zynq UltraScale+ MPSoC ZCU104                     | 30 |

|    |     | 5.2.3  | AMD Virtex UltraScale+ FPGA VCU118                    | 30 |

|    |     | 5.2.4  | Prototype Configuration to Platform Mapping           | 31 |

|    | 5.3 | Protot | ype Build Flow Development                            | 32 |

|    |     | 5.3.1  | GNU Make                                              | 32 |

|    |     | 5.3.2  | TCL                                                   | 32 |

|    |     | 5.3.3  | Vivado IDE                                            | 32 |

|    |     | 5.3.4  | Synthesis Flow                                        | 32 |

|    | 5.4 | Gener  | al FPGA Prototype Implementation Strategies           | 35 |

|    |     | 5.4.1  | RTL Partitioning                                      | 35 |

|    |     | 5.4.2  | Input Clock Architecture                              | 36 |

|    |     | 5.4.3  | Memory Interfaces                                     | 37 |

|    |     | 5.4.4  | Clock Gating                                          | 37 |

|    |     | 5.4.5  | IO Pads                                               | 39 |

|    | 5.5 | SysCt  | rl and MPC Specific FPGA Prototyping Implementation 3 | 39 |

|    |     | 5.5.1  | SysCtrl BootROM                                       | 39 |

|    |     | 5.5.2  | SysCtrl SDIO Clock Gating                             | ł0 |

|    |     | 5.5.3  | Slow Clock Generator                                  | 11 |

|    |     | 5.5.4  | Peripheral Clocks                                     | 12 |

|    |     | 5.5.5  | Memory Capacity                                       | 12 |

|    | 5.6 | HPC S  | Specific FPGA Prototyping Implementation 4            | ł3 |

|    |     | 5.6.1  | L2 Cache Controller                                   | ł3 |

|    |     | 5.6.2  | Memory Capacity                                       | 14 |

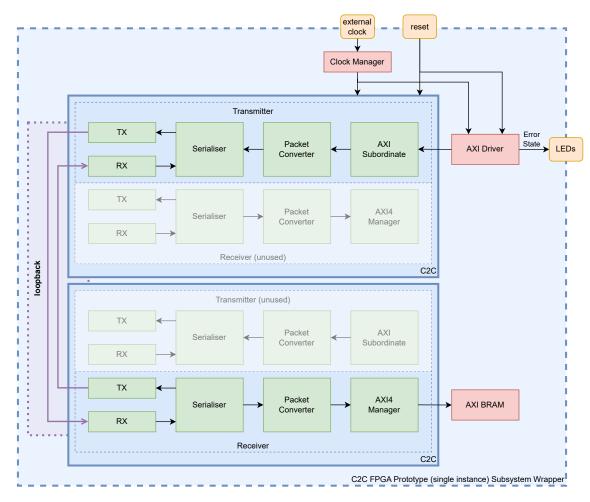

|    | 5.7 | C2C S  | Specific FPGA Prototyping Implementation 4            | 14 |

|    |     | 5.7.1  | AXI Driver and AXI Memory modules                     | 15 |

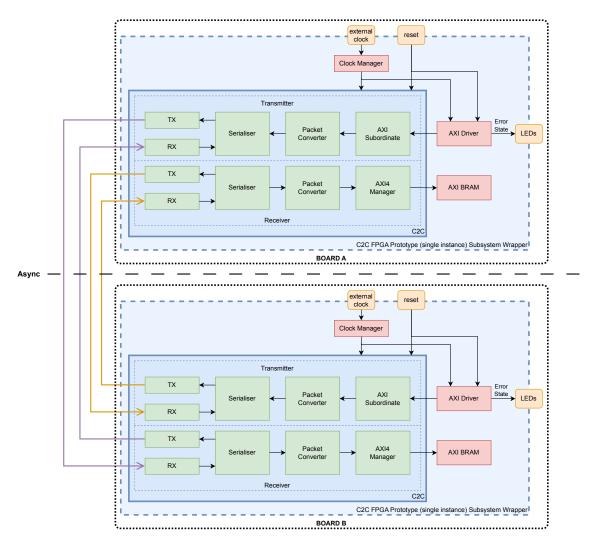

|    |     | 5.7.2  | Two Board Prototype Configuration                     | 16 |

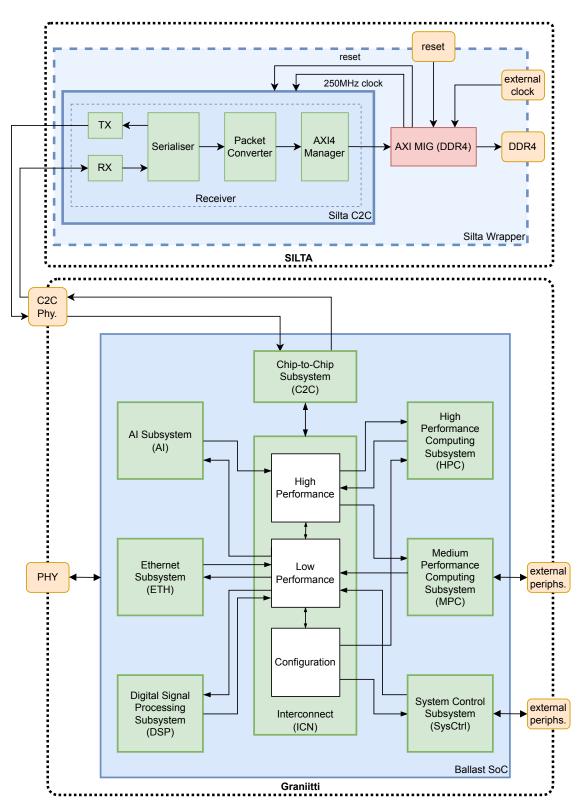

|    |     | 5.7.3  | Ballast Peripheral bridge - "Silta"                   | 16 |

iv

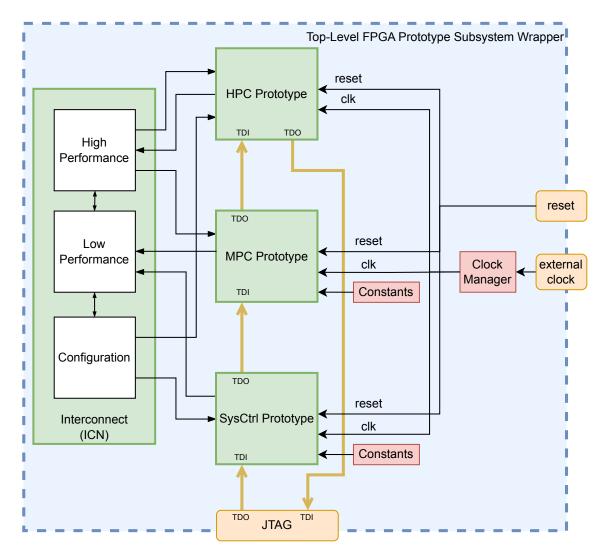

|     | 5.8    | Top-Le  | evel Specific FPGA Prototyping Implementation 47 |

|-----|--------|---------|--------------------------------------------------|

|     |        | 5.8.1   | Synthesis Flow                                   |

|     | 5.9    | Verific | ation of Implementation                          |

|     |        | 5.9.1   | RTL Simulation                                   |

|     |        | 5.9.2   | Hardware Validation                              |

|     | 5.10   | Debug   | gging the Hardware Design                        |

|     |        | 5.10.1  | AMD-Xilinx Integrated Logic Analyser             |

|     |        | 5.10.2  | 2 AMD-Xilinx Virtual Input/Output                |

| 6.  | Res    | ults .  |                                                  |

|     | 6.1    | Review  | w of Objectives                                  |

|     |        | 6.1.1   | Prototype Build Flow Development                 |

|     |        | 6.1.2   | Validation of SoC Boot Design                    |

|     |        | 6.1.3   | Validation of Debug Architecture                 |

|     |        | 6.1.4   | Validation of C2C Interface                      |

|     |        | 6.1.5   | Validation of SoC Peripheral Interfaces          |

|     |        | 6.1.6   | Provision of Platform for BSP Development        |

|     | 6.2    | Identif | fication of SDIO Hardware Design Issues          |

|     | 6.3    | Limita  | tions of FPGA Prototyping                        |

|     |        | 6.3.1   | Development Complexity                           |

|     |        | 6.3.2   | Prototype Performance                            |

|     |        | 6.3.3   | Technology Differences                           |

|     |        | 6.3.4   | Verification Coverage                            |

| 7.  | Con    | clusior | n and Future Work                                |

|     | 7.1    | Future  | e Work                                           |

| Ref | erenc  | es      |                                                  |

| Арр | pendix | k A: Ap | opendix A                                        |

# GLOSSARY

| AI    | Artificial Intelligence                   |

|-------|-------------------------------------------|

| AIC   | And-Inverted Cone                         |

| ALU   | Arithmetic Logic Unit                     |

| AMBA  | Advanced Microcontroller Bus Architecture |

| APU   | Application Processing Unit               |

| ASIC  | Application Specific Integrated Circuit   |

| ATPG  | Automatic Test Pattern Generation         |

| AXI   | Advanced eXtensible Interface             |

| BRAM  | Block RAM                                 |

| BSP   | Board Support Package                     |

| C2C   | Chip-to-Chip                              |

| CDC   | Clock Domain Crossing                     |

| cJTAG | Compact JTAG                              |

| CMOS  | Complimentary Metal Oxide Semiconductor   |

| CPI   | Camera Parallel Interface                 |

| CPU   | Central Processing Unit                   |

| CTS   | Clock Tree Synthesis                      |

| CVA   | Core-V APU                                |

| DDR   | Double Data Rate                          |

| DDR3  | Double Data Rate Generation 3             |

| DDR4  | Double Data Rate Generation 4             |

| DFT   | Design For Test                           |

| DMA   | Direct Memory Access                      |

| DPRAM | Dual Port RAM                             |

| DRV   | Design Rule Violation                     |

| DSP   | Digital Signal Processing                 |

| DUT   | Design Under Test                         |

|       |                                           |

| Electronic Design Automation              |

|-------------------------------------------|

| Ethernet                                  |

| Frequency Locked Loop                     |

| FPGA Mezzanine Card                       |

| Field Programmable Gate Array             |

| Globally Asynchronous Locally Synchronous |

| Gigabit per Second                        |

| Graphical Convolutional Network           |

| GNU Debugger                              |

| Graphic Design System                     |

| Gate Level Simulation                     |

| GNU's Not Unix                            |

| Graphics Processing Unit                  |

| Hardware Abstraction Layer                |

| Hardware Thread                           |

| High Performance CPU                      |

| High Pin Count FPGA Mezzanine Card        |

| High-Speed Transceiver Logic              |

| Hardware                                  |

| Input/Output                              |

| Inter-Integrated Circuit                  |

| Inter-IC Sound                            |

| Integrated Circuit                        |

| Integrated Development Environment        |

| Integrated Logic Analyser                 |

| Intellectual Property                     |

| Inter-Processor Communication             |

| Instruction Set Architecture              |

| Joint Test Action Group                   |

| Logic Equivalence Checking                |

| Low Pin Count FPGA Mezzanine Card         |

| Low Power Double Data Rate                |

|                                           |

| LTSSM   | Link Training and Status State Machine    |

|---------|-------------------------------------------|

| LUT     | LookUp Table                              |

| LVCMOS  | Low-Voltage CMOS                          |

| LVDS    | Low-Voltage Differential Signalling       |

| LVS     | Layout Versus Schematic                   |

| LVTTL   | Low-Voltage TTL                           |

| MMCM    | Multi-Mode Clock Manager                  |

| MMU     | Memory Management Unit                    |

| MPC     | Medium Performance CPU                    |

| MPSoC   | Multiprocessor System on Chip             |

| NRE     | Non-Reoccurring Expense                   |

| openOCD | Open On Chip Debugger                     |

| PCle    | Peripheral Component Interconnect Express |

| PLL     | Phase-locked Loop                         |

| PMOD    | Peripheral Module                         |

| PPA     | Power, Performance and Area               |

| PULP    | Parallel Ultra-Low power Processor        |

| QSPI    | Quad-Serial Peripheral Interface          |

| RAM     | Random Access Memory                      |

| RISC    | Reduced Instruction Set Computer          |

| ROM     | Read Only Memory                          |

| RTL     | Register Transfer Level                   |

| SD Card | Secure Digital Card                       |

| SDF     | Standard Delay Format                     |

| SDIO    | Secure Digital Input Output               |

| SerDes  | Serializer Deserializer                   |

| SMD     | Surface Mount Device                      |

| SoC     | System on Chip                            |

| SPI     | Serial Peripheral Interface               |

| SPRAM   | Single Port RAM                           |

| SRAM    | Static RAM                                |

| STA     | Static Timing Analysis                    |

|         |                                           |

| SV      | System Verilog                              |

|---------|---------------------------------------------|

| SW      | Software                                    |

| SWD     | Serial Wire Debug                           |

| SysCtrl | System Control                              |

| ТАР     | Test Access Port                            |

| TAU     | Tampere University                          |

| TCL     | Tool Command Language                       |

| TTL     | Transitor-Transistor Logic                  |

| TUNI    | Tampere Universities                        |

| UART    | Universal Asynchronous Receiver Transmitter |

| uDMA    | Micro-Direct Memory Access                  |

| URL     | Uniform Resource Locator                    |

| USB     | Universal Serial Bus                        |

| UVM     | Universal Verification Methodology          |

| VHDL    | VLSI Hardware Description Language          |

| VIO     | Virtual Input/Output                        |

| VIP     | Verification IP                             |

| VLSI    | Very Large Scale Integration                |

# 1. INTRODUCTION

The complexity of modern MPSoCs can result in complex development life cycles, with multiple streams of coupled development tasks being performed in parallel. Verification activities require a high percentage (40% - 50% [37]) of total engineering resources within projects and contain multiple complimentary activities. One of the commonly used but rarely analysed activities is FPGA-based prototyping. FPGA-based prototyping is typically used to provide an accurate, highly performant hardware model, which can interface to real components within a lab without incurring high material costs. This thesis documents an overview of FPGA-based prototyping methodologies, a review of the current related technologies and an analysis of a real-life application within the SoCHub project. Measuring the effectiveness of FPGA prototyping is a challenging task, as it is an activity which is mainly used to complement adjacent, metric-driven verification activities. This thesis attempts to evaluate the strengths and weaknesses of FPGA prototyping by establishing high-level objectives, which guide the implementation and testing scope, and a qualitative analysis of the activity is performed.

This thesis is composed of six sections. Section 2 provides an overview of modern SoC development and the related verification challenges. Section 3 delivers an overview of FPGA prototyping methodologies, current technologies and related work. The context of the FPGA prototyping analysis is given within Section 4, in which the Ballast SoC project, architecture and prototyping objectives are detailed. Section 5 follows this by presenting the detailed implementation of the FPGA prototyping configurations used as a part of the Ballast SoC verification activities. A review of the results and identified limitations of the prototyping activities are provided within Section 6. Section 7 contains the conclusion and suggestions for future work items that could build upon this thesis's content.

# 2. SOC DEVELOPMENT

#### 2.1 Overview

Following Moore's Law, the component density of an IC has approximately doubled every two years and historically the complexity of computing systems has increased at an equivalent rate. Computing architectures have evolved to satisfy the functional and performance requirements placed upon computing systems to manage this complexity [26]. A major milestone in the evolution of computer architecture design was the introduction of the SoC concept in the 1980's. An SoC can be summarised as a heterogeneous VLSI system that utilises a traditional processor core in combination with ASICs contained within a single IC. This combination leverages the optimised performance that a custom hardware solution provides and the operational flexibility that a general-purpose CPU running software offers [25].

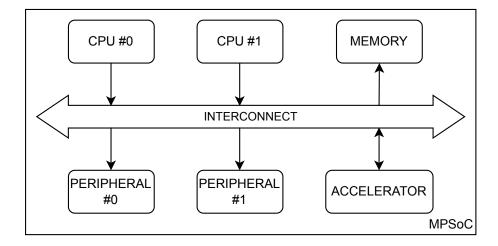

Another significant evolution of architecture, conceived in the early 2000s, was the MP-SoC. An MPSoC builds upon the traditional SoC concept by introducing multiple, independent, programmable processors connected to memories and other system components via a dedicated interconnect. The addition of multiple CPU instances within an MPSoC increases the achievable performance and flexibility of the software running on the system. This combination makes MPSoCs suitable for use in embedded multimedia and highspeed data communications applications, where there is a need for high performance that can be implemented to meet strict quantitative goals [55]. Figure 2.1 represents a basic MPSoC architecture.

#### 2.2 Verification Challenges

During the development of hardware for ICs, the design must be sufficiently tested to ensure that all bugs are removed before tape-out, as the time/cost impact of fabricating another chip iteration is significant and often unacceptable. Verification is the most demanding task in terms of engineering effort, with typically 40-50% of project resources allocated to functional verification on a hardware development project [36].

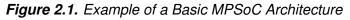

For a modern MPSoC, the typical development life-cycle is highly complex. Due to the demands of project schedules and multiple activities being coupled, several activities are

Figure 2.2. MPSoC Design Life-cycle, processes and artefacts [44]

often executed in parallel. These include RTL design, SW development, Physical Design and Verification [44]. Figure 2.2 illustrates the complex and parallel nature of modern MPSoC project execution. It is imperative to use design and verification techniques to accelerate the de-risking of hardware and software as early as possible in the life-cycle to minimise the penalties associated with refactoring software/RTL and reduce the time to market.

# 3. FPGA-BASED PROTOTYPING

#### 3.1 Motivation for Logic Emulation

Simulating RTL is the most widely used method for performing functional verification of modern ASIC designs. As the size of the simulated designs grows, the time it takes to complete the simulation and the amount of host storage/processing required increases. It becomes impractical to run simulations of designs containing multiple processing cores or accelerator blocks for a long enough time to perform realistic use cases.

Hardware emulation (or prototyping) is a design-phase verification technique that integrates a hardware design into a reconfigurable prototyping platform to enable functional testing of the Design Under Test (DUT). It allows the hardware and the low-level software to be evaluated in a realistic performance setting [35]. Hardware emulation platforms are applied within ASIC development to satisfy the following typical requirements [18]:

- Providing a platform which can be used to run the designs at emulation speeds higher than what can be achieved through the use of RTL simulation.

- Being able to emulate the entire system on a single platform.

- Maintaining similarity between the design artefacts used on the delivered solution and the artefacts used in emulation.

- Supplying a high degree of visibility in the emulation for debug purposes.

- Enabling the ability to offer low-cost copies of the prototype for use in hardwaresoftware co-design and field testing.

#### 3.2 FPGA-based Emulation

FPGAs are an example of an effective hardware emulation technology that can execute the design at speeds that would not be possible in RTL simulators [46]. FPGAs have been used in this way for over 30 years. However, until recently, several weaknesses associated with the platforms limited their applicability for prototyping (e.g. low compile time and low area) to small and simple designs. The larger sizes and improved tool performance of the more recent generations of commercial FPGAs have made them more suitable for the task [15][35].

FPGA logic emulation is typically used to replace or augment traditional CPU-based logic or gate-level simulation. The logic circuits within an FPGA are implemented and run in parallel. The parallel performance of CPU-based simulators is limited by the number of ALUs available to execute instructions. In contrast, the performance of FPGA-based emulation is only limited by the amount of resources available on the FPGA. The result is that FPGA-based emulators run logic circuits faster than the equivalent logic executed using a CPU-based simulator. The execution performance of FPGA-based emulators is good. However, there are a number of limitations that exist when emulating a design using FPGA [51]:

- FPGA-based emulators can only support cycle-accurate logic evaluation that is synchronised to the clock of the FPGA design.

- The technology used to implement a design on FPGA differs significantly from the technology used for implementing the ASIC. Therefore, reliable post-synthesis/post-routing timing information cannot be retrieved by running the design on FPGA.

- Debugging designs on an FPGA during runtime is significantly more complex than debugging a design in simulation. Typically, dedicated resources must be reserved within the design to allow in-circuit analysis of the signals within the FPGA.

Depending on the application's requirements, FPGA emulators can be implemented on a single FPGA or across multiple FPGAs. Furthermore, using the FPGA emulator in a standalone, in-circuit or co-simulation configuration is possible. The following subsections provide a summary of each configuration.

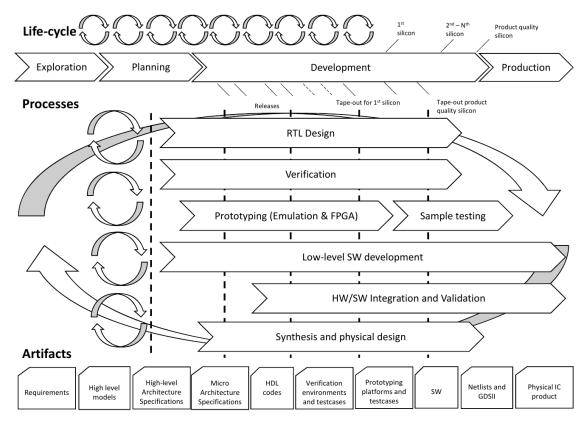

# 3.2.1 Single-FPGA Emulation Platform

The basic form of emulator is a design running on a single FPGA. The design is translated to remove/replace any design structures that cannot be synthesised on FPGA. Additionally, architectural features in modern ASIC design, such as multiple asynchronous clock domains, complex reset trees, test/debug interfaces and multi-port memories complicate the FPGA compilation process. Therefore, modifications are made to the design to simplify these aspects and simplify implementation without compromising the RTL functionality of the DUT [27].

Once this is complete, the RTL of the design is synthesised using the FPGA-specific tooling and mapped to the platform. This approach is the simplest for logic emulation, but the size of the available FPGA platform limits it. Figure 3.1 (left) illustrates a single-FPGA emulation platform.

#### 3.2.2 Multiple-FPGA Emulation Platform

For larger ASIC designs which cannot be prototyped using a single FPGA platform, it is possible to partition the design and implement each partition onto single FPGAs which are connected to each other. Modern multi-FPGA emulation systems are complex systems containing, in some instances, hundreds of FPGAs/memory chips, high-speed interfaces and logic analysers. Typical systems contain multiple boards, each of which contains multiple interconnected FPGAs. The boards are connected together using fixed connections or across a back-plane bus. The design flow for such a configuration is significantly more complex than the single FPGA as in addition to the logic implementation required on each FPGA locally, the implementation also need to be analysed locally across multiple FPGAs. This analysis includes the following steps [51]:

- 1. Translation of ASIC design into the FPGA circuit representation.

- 2. Partitioning and global placement of design such that each design partition is able to fit onto a single FPGA.

- 3. Global routing of signals between partitions.

- 4. Assignment of interconnected signals to pins on each FPGA. It is common that there is not a sufficient number of pins available to support dedicated connections between the partitioned design, thus time-based multiplexing of signals on each pin is used to enable the design to function correctly.

- 5. Local synthesis, place and route and bitstream generation for each FPGA on the system.

Figure 3.1 (right) illustrates a multi-FPGA emulation platform connected using a mesh topology.

**Figure 3.1.** A Single-FPGA Emulation Platform (left) and a Multi-FPGA Emulation Platform Connected in a Mesh Topology (right)

# 3.2.3 Standalone FPGA Emulation Platform

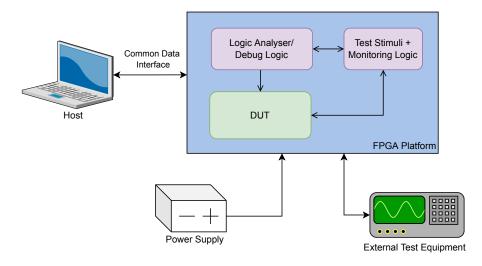

As a standalone platform, the design is implemented onto a single or multi-FPGA platform and driven by sources independent of the target system within which the design will be integrated. Figure 3.2 illustrates a typical setup when using a standalone FPGA-based emulation platform. The design can be monitored using integrated debug components or external test equipment. Similarly, stimuli can be sent to the DUT using test logic which has been included within the FPGA design, external dedicated hardware to assist with testing or using test vectors from a host machine, which is usually connected to the FPGA platform using a standard data interface e.g. USB or PCIe. Depending on the testing requirements, a selection or all monitoring/stimulus sources can be used during emulation.

# 3.2.4 In-circuit FPGA Emulation Platform

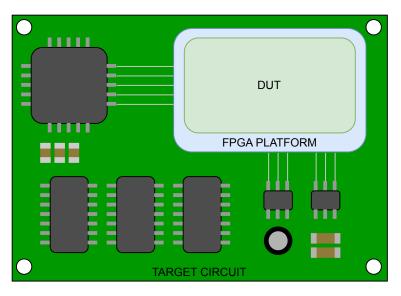

For in-circuit emulation, the DUT is implemented on an FPGA-based emulation platform and connected to the target system within which the final design is intended to reside. The stimuli to the emulation platform can then come from the surrounding system components [51] as is shown within Figure 3.3.

Figure 3.2. Typical Setup of a Standalone FPGA Emulation Platform

Figure 3.3. Illustration of an In-circuit Emulation Platform

# 3.2.5 Co-simulation FPGA Emulation Platform

It is possible to use an FPGA-based emulation platform as a simulation accelerator. In this configuration (FPGA co-simulation/co-verification), the emulator is connected to a host computer using a common data interface. The host computer simulates the components connected to the design running on the emulator, transferring stimuli between the simulation and the emulator over the data interface [51].

# 3.3 FPGA Technology Overview

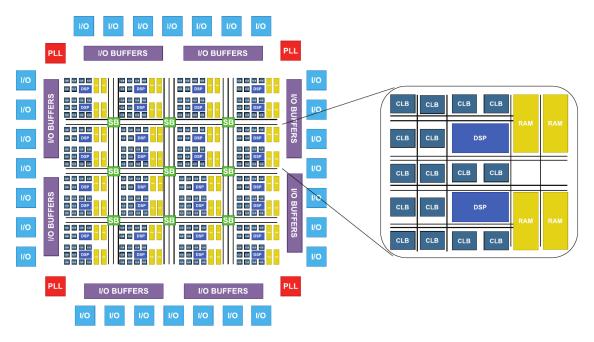

Following the creation of FPGAs in the 1980s, due to the technological limitations of the time, the initial applications of FPGAs were mainly limited to implementing custom 'glue' logic that could be used to connect components. The programmability of FPGAs meant

Figure 3.4. Generic Example of a Modern FPGA's Internal Structure [14]

that any design errors recognised at a late stage in the development lifecycle could be quickly resolved with minimal impact on schedule or cost. Over time as digital technology advanced and the cost of the technologies reduced, the capabilities of FPGAs and the range of problem domains they can be applied to has increased [56].

The typical architecture of a modern FPGA can consist of a mixture of monolithically embedded components:

- · Logic blocks,

- I/O blocks,

- · Embedded memories,

- DSP blocks,

- · High-speed data transceivers,

- · Clock management blocks,

- · Signal and clock routing networks,

- Processor cores.

A generic example of the internal structure of a modern FPGA can be seen in 3.4.

The following section provides an overview of the most common components and features of modern FPGAs, focusing on AMD-Xilinx FPGAs.

#### 3.3.1 Logic Blocks

FPGA logic blocks contain a combination of n-bit LUTs, interconnecting logic components and D-type storage elements. The LUTs are composed of n-bit input, 1-bit output SRAM blocks that are used to perform arbitrary combinatorial operations. The interconnecting logic enables routing between the logic blocks and to the I/O components on the FPGA [57]. The storage elements enable sequential operations and, in modern FPGAs, can be configured as latches or flip-flops. In addition to the basic functions some FPGA vendors use logic blocks to implement additional functionality such as shift registers, distributed RAM, LUT-based ROM, arithmetic operations and multiplexing [30]. The terminology used to reference logic blocks varies between vendors. For example, AMD-Xilinx refers to logic blocks using the term "configurable logic block (CLB)", while Intel uses the term "adaptive logic module (ALM)". The exact contents of these blocks vary between vendors and architectures.

#### 3.3.2 IO Blocks

FPGAs use I/O interfaces to route signals in and out of the chip. Modern FPGAs support several different I/O standards and the specific standard assigned to an FPGA pin is typically statically configurable. CMOS, LVCMOS, LVTLL HSTL and LVDS are examples of some of the I/O standards supported by modern FPGAs [9]. In addition to the standard, the FPGA pins can be configured as input, output or bidirectional. The FPGA I/O interfaces and configuration logic are contained within a block referred to as the IO Block on AMD-Xilinx FPGAs. In addition to the configurable aspects already mentioned, the IO Blocks also include additional resources, such as voltage translators, buffers, registers and resistors [48]. The aforementioned configurable I/O properties allow an FPGA to communicate with external components using various interfaces.

#### 3.3.3 Memory Blocks

A memory block, or "Block RAM" (BRAM), is a discrete, fixed-sized block of SRAM memory within an FPGA. It can often be configured to operate in various modes depending on the user requirements, e.g. FIFO, SPRAM, DPRAM. These blocks are typically provided to enable fast and local memory access. BRAMs can be combined to provide the capability of a larger memory without the need for a larger dedicated memory component. There are often many instances of BRAM available within the FPGA. However, the number of blocks and the capacity of each block vary between platforms, and they are typically welldistributed across the FPGA to aid with signal routing. To demonstrate the variable BRAM usage within FPGAs, at the time of writing this thesis, the Xilinx Vitex Ultrascale+ series advertises a rather large BRAM capacity of 94.5Mb [29], while the Lattice iCE40 LP640 offers a relatively modest 64kb [47].

In addition to 'traditional BRAMs', some modern FPGAs now include multiple embedded memory options to help address the increasing need for fast local memory access in FPGA designs. An example is the availability of 'UltraRAM' within the Xilinx Ultrascale range of FPGAs. These are larger (288kb) but less well-distributed blocks of memory to provide an intermediate between the fast/small BRAMs and large/slow off-chip memories such as DDR [31].

# 3.3.4 Routing Networks

A programmable interconnect is used to flexibly connect all of the components mentioned above and create a complete circuit. A typical routing interconnect comprises an array of wires and switch matrices, the layout of which is architecture-dependent.

One of the challenges EDA vendors face is to ensure that the signal routing distances between the elements within a circuit are as small as possible to minimise propagation delays. Arrangements of logic and routing resources are selected in an attempt to address this. For example, a typical routing style used within modern FPGAs is the "Island style", in which horizontal and vertical channels connect the FPGA functional elements [57] (see Figure 3.4). Furthermore, it is typical for an FPGA to use dedicated routing for wires for the clock pins of synchronous elements. These are specially designed to minimise propagation delay, clock skew and jitter. In modern FPGAs using small technology nodes, routing is the factor which limits the FPGA performance. As a result, some modern devices have started to include register pipelines within routing paths to guarantee better data throughput [23].

# 3.3.5 DSP Blocks

To perform high-speed arithmetic operations on values with large word lengths, hard DSP blocks are implemented within the FPGA fabric. These blocks typically contain pipelined configurable arithmetic units that allow users to efficiently perform complex arithmetic which is standard in applications such as digital signal processing [16].

# 3.3.6 High-speed Transceivers

Modern FPGAs also include high-speed data transceivers to provide a SerDes capability. The operation and performance of the transceiver is platform specific. For example, AMD-Xilinx Virtex Ultrascale devices contain GTY-transceivers to provide 400G networking capabilities which would otherwise be not be possible [8].

#### 3.3.7 Embedded Processor Cores

If there is a requirement to have a high degree of configurable control within a design, it is common to implement one or more "soft" processor cores within an FPGA design. The operating frequency and performance achieved by such soft processor cores on an FPGA is lower than can be achieved by an equivalent CPU core implemented as an ASIC due to the reasons outlined within section 3.4. To try and address the continuous need for improved efficiency and performance, some vendors offer hybrid solutions within which a "hard" CPU core is embedded within the FPGA chip alongside the traditional FPGA fabric. For example, the AMD-Xilinx Zynq-7000 SoC contains a dual-core Arm Cortex-A9 processor block that can be interfaced to the FPGA fabric using AXI connections [23].

#### 3.3.8 Other Components

In addition to the main components listed above, modern FPGAs can contain other hardware peripherals such as media codecs, network controllers, external memory controllers (e.g. DDR4 and HBM), high-performance ADCs and DACs. However, the existence of these components is highly variable, depending on the FPGA platform. A detailed description of these components is beyond the scope of this thesis and therefore they will not be covered in detail.

# 3.4 FPGA and ASIC Comparison

# 3.4.1 Technologies

The mainstream approach that is used to perform the physical design of SoCs is called semi-custom design. Within this approach, the cells of a standard cell library are used to construct the logic of the design. The cells within the library are composed of logic gates, flip-flops, latches, IO pads, clocking components, SRAM memory cells and other components [23]. During the physical design stages of an ASIC, the cells which make up the design can be freely placed and connected. This freedom can be used to optimise the design implementation in a way that isn't possible within the fixed programmable logic contained within an FPGA (see Section 3.3). Furthermore, the semi-custom approach enables the construction of complex clock and reset tree structures, fine-grained power management logic and memory customisations within ASICs which are not feasible within modern FPGAs due to the fixed nature of the underlying hardware. The result of this is that a typical semi-custom ASIC can achieve a clock frequency which 3-15 times faster, with a 50% reduction in area when comparing to an equivalent FPGA implementation [23].

While the achievable performance of an ASIC is higher than that of an FPGA, the devel-

opment costs and time associated with an ASIC solution are significantly higher than an FPGA implementation. This can be mainly attributed to the high NRE cost that must be paid to develop the mask set which is used to fabricate the ASIC. In contrast, the NRE cost for FPGA development is essentially zero as the programming of the design onto the platform is a straightforward activity [23].

# 3.4.2 Development Flows

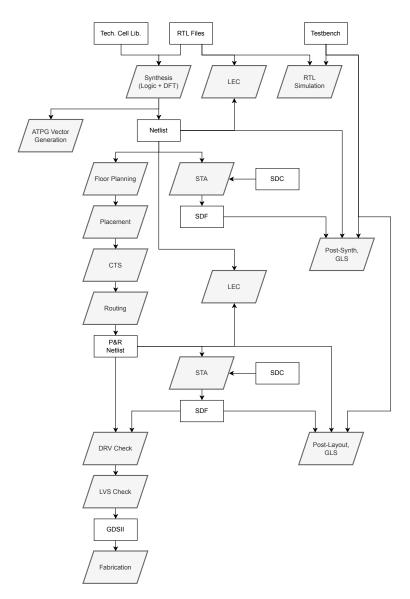

The development flow is a term used to describe the progressive stages of development which must be completed to progress from an FPGA or ASIC design specification to a fully functioning and tested end-product. ASICs and FPGAs share the same high-level steps to create a design from RTL, but significant practical differences need to be considered in the development of each.

The general development flow for an FPGA can be seen in Figure 3.5. Most of the tasks in the flow are completed using the same tool, typically provided by the same vendor that produces the FPGA.

In contrast, the equivalent flow for a modern ASIC can be seen in Figure 3.6. The main difference can be seen in the number of discrete steps required for verification and physical design, mainly because the FPGA is already fabricated and therefore does not need to be verified to such a high standard before the design is released. Additionally, it can be seen that the ASIC flow is separated into front-end and back-end stages. The transition between the front-end and back-end stages occurs over the logic synthesis stage, with the front-end only containing activities independent of the selected fabrication technology or ASIC chip instance [23].

# 3.5 Related Work

Within [33], the implementation of a single-board FPGA prototype (described within 3.2.1) for the LEON3 SoC is presented. In the final prototype, the entire SoC is implemented using a single Xilinx XC3S1500 FPGA that is mounted on a PCB. The PCB is shared with several peripherals connected to the FPGA pins, enabling the testing of the prototype SoC peripherals using representative hardware. The prototype verification methodology of the SoC is presented and shows that the individual prototype subsystem IPs from the SoC were initially verified as standalone designs. Once this was complete, the IPs were integrated, and the entire SoC prototype verification was performed. The details of how the ASIC-specific components, such as IO pads, PLLs and SRAMs, were modified to allow FPGA synthesis are provided. Once the SoC prototype was available, it was possible to perform HW/SW co-design with ease, as the platform was able to run a Linux-based operating system.

Figure 3.5. Typical FPGA Development Flow

An example of a large SoC implemented using multiple FPGAs (described within 3.2.2) can be found in [21]. The focus of the work is the creation of a high-bandwidth, lowlatency, scalable interconnect which can be easily re-purposed for other designs requiring multi-FPGAs prototyping platforms. The SoC design is logically partitioned, and each partition is placed onto physically separated FPGAs. In addition to the DUT, logic is added that performs the routing and switching of data flowing in and out of the local FPGA design via a custom bridge. The routing and switching logic is designed to allow the FPGAs to communicate in direct link or routed mode, resulting in a topology-agnostic architecture. Furthermore, transparent error checking and an error correcting protocol are implemented to remove the bit-errors expected when utilising high-speed interfaces. The additional logic connects the DUT and the high-speed transceivers on the selected FPGA platforms. The external pins of the transceivers are connected using SATA cables. The work claims that using this generic interconnect, adapting a single vector processing system design from a single FPGA configuration to a 16 FPGA configuration took only a

Figure 3.6. Typical ASIC Development Flow

single day of effort [21].

As described within 3.2.2, the partitioning of designs onto multiple FPGA prototyping configurations can be highly complex. This complexity can lead to delays and uncertainty in project schedules and create the need for experienced engineers to perform the task. [52] looks at solving the complexity associated with partitioning and mapping a single SoC onto a multi-FPGA configuration by applying deep learning methods to reduce the time to market. The work redefines the process of partitioning and mapping as a high-level task: group the SoC IPs into clusters that do not require more resources than are available on each FPGA and then ensure that the number of signals between the IP clusters is minimised. A graph convolutional network (GCN) is used to generate the FPGA-level clusters as they are proven effective for learning rich representations of nodes and edges in a graph [52]. The SoC IPs can be represented as nodes, and the connections between them can be described as edges of a graph, making a GCN suited for this task. Addi-

tionally, the FPGA logic resource constraints are fed into the constraining of the clusters. Once this is complete, a constrained greedy approach is used to map the DUT to a multi-FPGA platform and the clusters with the most connections between them are placed close together. This approach was applied to map three different SoCs containing 100-150 IPs. In parallel, the same mapping task was also completed manually to act as a control. The results show that the automated partitioning and mapping process performed the mapping more efficiently than the manual attempt for each SoC, with an estimated saving of one month of engineering effort [52].

Compared to simulation-based functional verification of hardware, measuring the functional coverage achieved when using FPGA prototyping to verify a design is complex. [38] looks at implementing a synthesisable active agent and coverage collecting component, which can be integrated into an FPGA prototype to improve input stimuli quality and perform test coverage calculations.

The work focuses on the hardware implementation of a USB3.0 IP core, which is to be verified using an FPGA prototype. The prototyped IP core is driven using an external USB3.0 host device and the output of the IP core is captured using a CPU core, which is embedded within the FPGA prototyping platform and connected via an AXI interface. In this configuration, it is impossible to gain functionality coverage within the USB3.0 link layer, such as the Link Training and Status State Machine (LTSSM), as properties such as signal timing cannot be configured on the driving external USB3.0 host. This work implements an active agent component between the DUT and the external USB3.0 host, which can be configured to set the signal timing of the link layer and therefore, freely control the stimuli. The embedded CPU which collects the DUT output data is also connected to the active agent to configure the timing parameters. A coverage collector application is executed on the CPU, creating a closed-loop system that can then be used to thoroughly test the time-sensitive aspects of the link layer and report on the coverage achieved. The active agent is designed to minimise resource consumption on the FPGA and the resulting design utilised 13% of LUTs and 6% of the registers when compared to the DUT [38].

# 4. BALLAST DEVELOPMENT AND ARCHITECTURE

#### 4.1 SoC Hub

SoC-Hub is a research ecosystem created by Tampere University to bring together stakeholders from academia and industry in Finland to boost research and education in the field of SoC design. One of the targets of SoC-Hub is to produce SoCs at a cadence of one each year. Ballast is the name of the first SoC that was developed as a part of this initiative [43].

# 4.2 Ballast Architecture

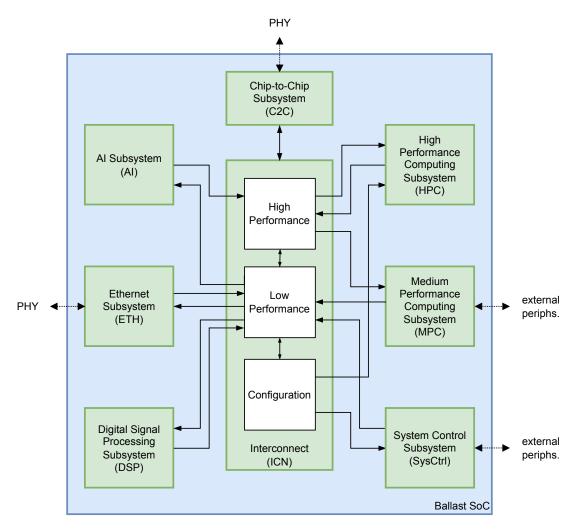

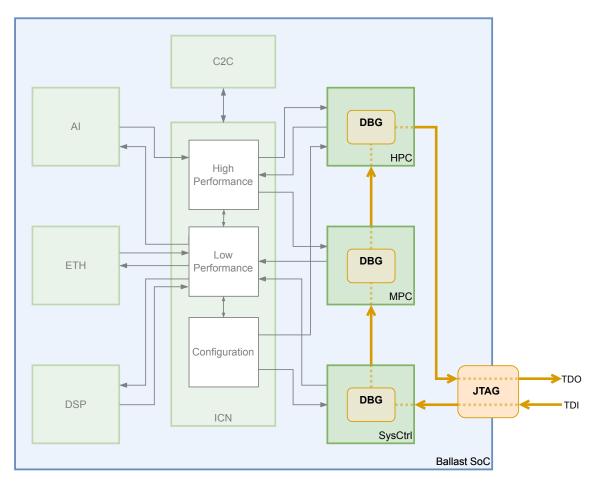

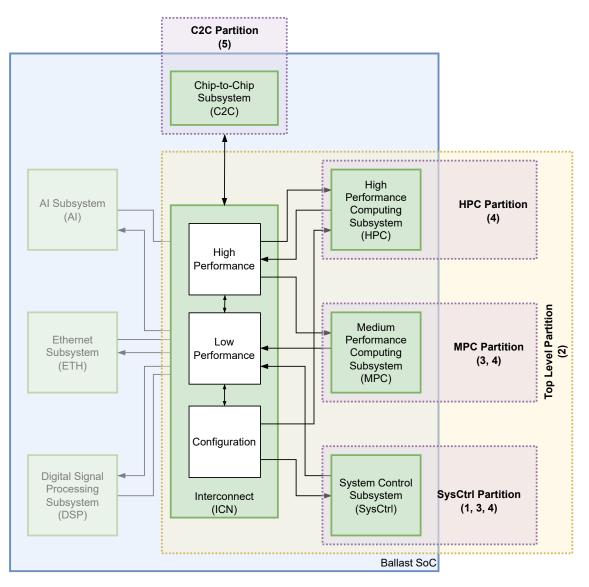

Ballast is an edge-capable, heterogeneous MPSoC which has been taped out on 22nm technology and has a maximum frequency of 1.2GHz. There are seven subsystems contained within the SoC, namely:

- System Control (SysCtrl) subsystem,

- High Performance CPU (HPC) subsystem,

- Medium Performance CPU (MPC) subsystem,

- Chip-to-Chip (C2C) subsystem,

- Artificial Intelligence (AI) subsystem,

- Ethernet (ETH) subsystem,

- Digital Signal Processing (DSP) subsystem [43].

There is also a top-level interconnect which consists of three AMBA AXI4 [34] crossbar components, connected in a cascaded bus matrix topology [22], as shown within Figure 4.1.

# 4.3 Development Methodology

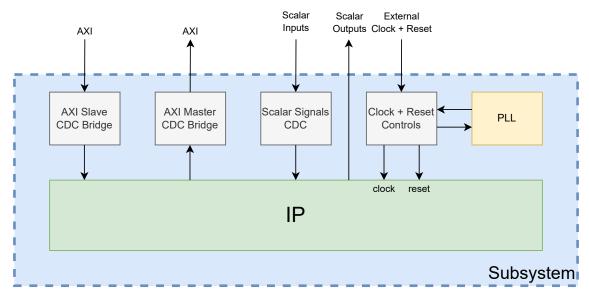

The SoC is designed using a GALS architecture so that each subsystem was intended to operate within its own clock domain. To help ensure that the development of the SoC was as efficient as possible, each subsystem (and the interconnect) used the same top-

Figure 4.1. Ballast High-Level Architecture

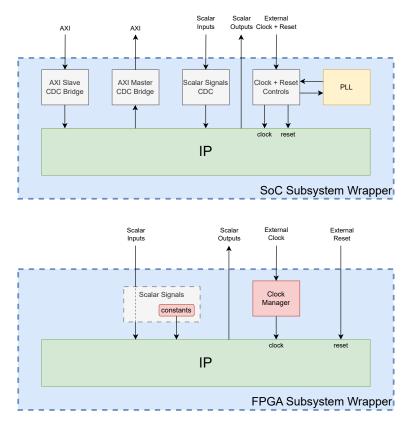

level architecture template. This template contained generic definitions for the AXI CDC interface(s), control/status signal synchronisers and clock/reset controls (see Figure 4.2. It enabled the use of a hierarchical ASIC design flow, allowing for concurrent development of subsystems and reduced complexity of the design environment [43].

In addition, the use of this template provided a functional partition between subsystems and allowed each subsystem to be developed/tested in isolation from the other subsystems on the chip.

# 4.4 Verification Strategy

Hierarchical verification was the primary strategy employed during the development of Ballast. Each subsystem was independently verified as a separate entity using the most appropriate verification methodologies. Once verified as a standalone, the subsystem was then integrated into the top-level design and integration testing was performed [43].

The verification methodologies applied at the subsystem level included basic functional

Figure 4.2. Ballast Subsystem Template

testbenches, UVM, HW/SW co-simulation and FPGA prototyping. This work focuses on FPGA prototyping; therefore, only this will be covered in detail.

#### 4.4.1 Functional Coverage

When performing functional verification of a design, one must have access to a metric which has a direct relationship to the functionality of the design to determine at which point the design has been sufficiently tested. To define such a metric, a fault model of the design is created that is described at the functional level and is independent of the implementation details [37]. A fault analysis was performed during the planning stages of the Ballast SoC and was used as an input during the generation of the verification planning artefacts. The details of the verification plan creation and its contents outside of the FPGA prototyping testing objectives are beyond the scope of this thesis.

# 4.4.2 FPGA Prototyping

The Ballast FPGA prototyping objectives were dictated by the Ballast verification planning activities as follows:

- 1. Create an extensible and re-usable build flow which can be applied across the FPGA prototyping configurations required by Ballast,

- 2. Validate the SoC boot design,

- 3. Validate the SoC debugging architecture,

- 4. Validate SoC peripheral functionality through the use of real components,

- 5. Provide a platform for development of the SoC BSP and tools used for the SoC wake-up

activities.

6. Validate the functionality of the asynchronous C2C interface.

#### 4.5 Subsystems of Interest

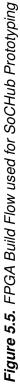

Ideally, creating an FPGA prototype of the entire Ballast SoC would be possible. However, this is not feasible due to hardware resource constraints on modern FPGAs. Different approaches can be taken to partition the SoC into smaller modules, which can then be individually prototyped on separate platforms. For example, [46] outlines an approach that uses the resources required to implement each module of the SoC on an FPGA and implements an algorithm that partitions the design into sections that can be implemented on a pre-defined FPGA platform. Due to project constraints, a more conservative approach was taken in the design partitioning of Ballast. Rather than aiming to prototype the entire SoC, it was found that to meet the FPGA prototyping objectives, only a subset of the subsystems and functionality of Ballast needed to be implemented on the same FPGA. Each subset (a prototype configuration) is described in more detail in Section 5.1.

As the selected prototype configurations only contain a fraction of the total subsystems on Ballast, only the subsystems relevant to the Ballast SoC prototyping configurations are described in detail here. It is possible that for some subsystems, FPGA prototyping was completed when developing the subsystem IPs. However, a prototype was not created as a part of the Ballast SoC development and integration activities. For example, the DSP subsystem was an IP developed independently of the SoCHub project and subsequently integrated into the Ballast SoC. It is known that FPGA prototyping of this subsystem was performed, but this was independent of the development of the Ballast SoC and is therefore not covered within this thesis.

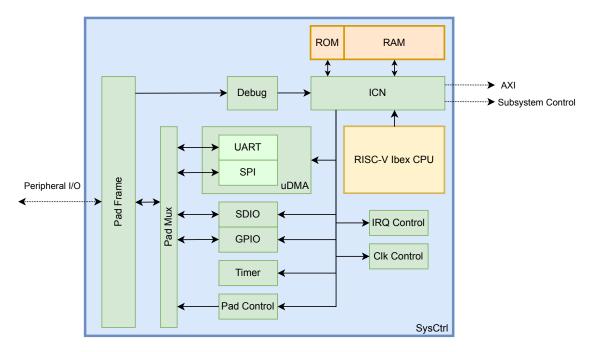

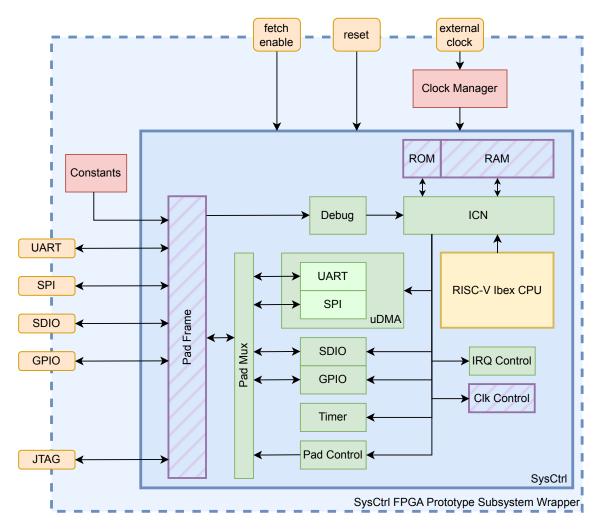

#### 4.5.1 SysCtrl

The System Control (SysCtrl) subsystem is adapted from the Pulpissimo SoC [45], initially developed by the University of Bologna. The SoC contains a collection of peripherals which are standard in contemporary microcontrollers (e.g. UART, SPI, timers, etc.), accessed using a low-power uDMA [42]. SysCtrl utilises the zero-RISCY variant of the RISC-V core, which is a minimal, 32-bit, 2-stage, in-order core; it implements the 'I', 'M' and 'C' extensions of the RISC-V ISA [53][17].

The primary purposes of the SysCtrl subsystem are to manage the boot sequence of the Ballast SoC, to control the clock/reset inputs to the other subsystems and to configure the SoC. Full details of the boot control can be found within [39]. The subsystem is not designed to be computationally powerful and, therefore, is not a main target for running application code. However, it contains several peripherals, which make it suitable to per-

Figure 4.3. High-level View of SysCtrl Architecture

form supporting tasks such as acting as a system monitor for waking up from a low power state.

The following modifications were made to the Pulpissimo IP to create the SysCtrl subsystem:

- To enable a resilient boot process, the SDIO peripheral was removed from the uDMA subsystem and refactored to be accessed via the main system bus.

- Removal of unnecessary peripherals such as I2C, I2S and the parallel camera interface.

- Removal of the internal FLL and associated internal clock generators, as the clock signals of SysCtrl are generated by an external reference clock.

- Addition of external interrupt sources to enable IPC.

- Modifications to memory layout and reduction of ROM/RAM memory size.

A high-level view of the SysCtrl subsystem architecture can be seen in Figure 4.3.

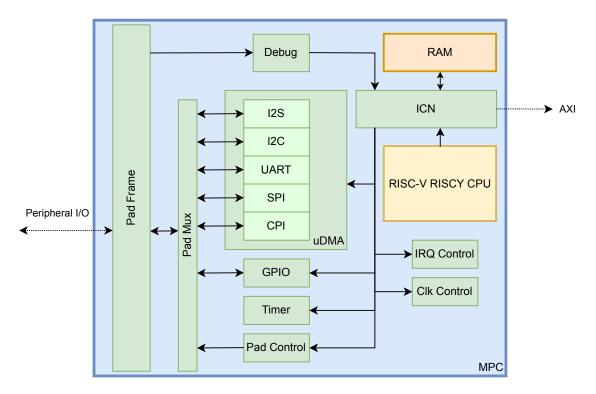

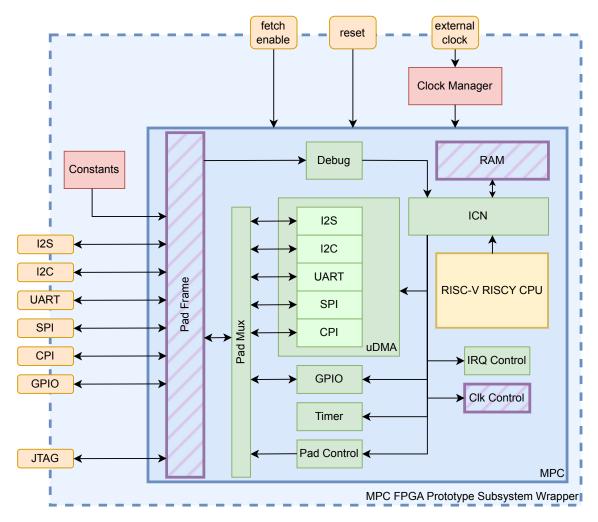

#### 4.5.2 MPC

Similar to SysCtrl, the MPC subsystem of Ballast is also created from a modified version of the Pulpissimo SoC. However, rather than using the low-power zero-RISCY variant, MPC utilises the RISCY core. The RISCY core is a 32-bit, in-order, 4-stage RISC-V core with the 'l' and 'M' extensions implemented. It has been further extended to increase performance and can be used within DSP and edge applications.

Figure 4.4. High-level View of MPC Architecture

The following modifications were made to the Pulpissimo IP to create the MPC subsystem:

- Removal of unnecessary peripherals such as SDIO as this is provided by SysCtrl.

- Removal of the internal FLL and associated internal clock generators, as the clock signals of SysCtrl are generated by an external reference clock.

- Addition of external interrupt sources to enable IPC.

- Removal of ROM.

A high-level view of the MPC subsystem architecture can be seen in Figure 4.4.

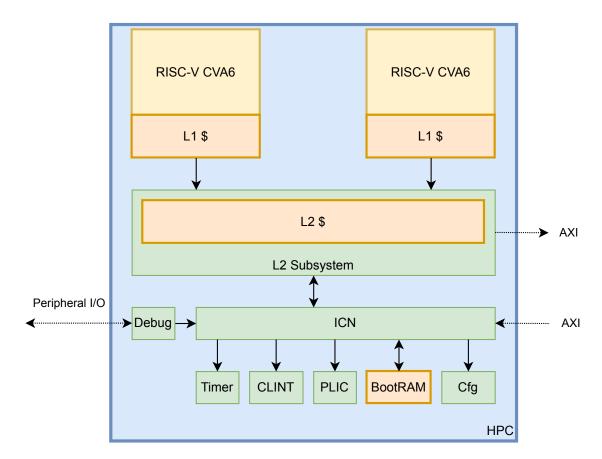

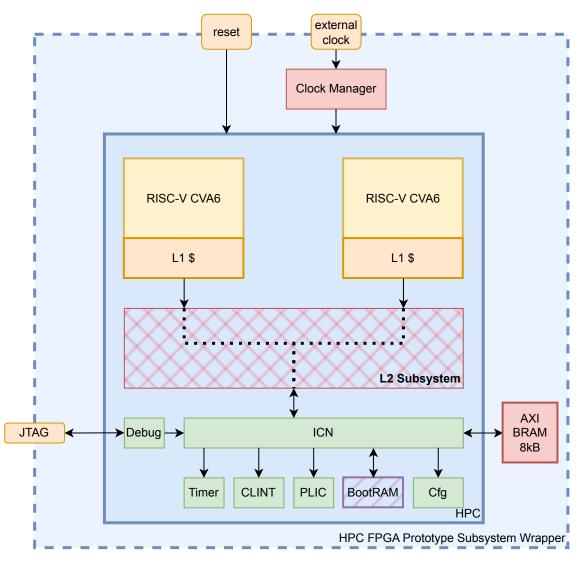

#### 4.5.3 HPC

The HPC subsystem is designed for to handle computationally intensive applications on Ballast. It is implemented using two CVA6 RISC-V cores. The CVA6 is a 64-bit, singleissue, in-order RISC-V core which implements the 'I', 'M', 'A' and 'C' extensions. Additionally, it has Machine, User and Supervisor privilege levels implemented [54]. Furthermore, the CVA6 provides complete hardware support for MMU translation. These features enable the CVA6 to operate as an application class core and provide the infrastructure required to run popular operating systems such as Linux [58].

As well as two CVA6 cores, the HPC subsystem implements a 32kB 8-way L1 cache per core and a 256kB 8-way L2 cache, which is coherently shared between the cores.

Figure 4.5. High-level View of HPC Architecture

Moreover, HPC includes an interrupt controller and timer peripherals.

A high-level view of the HPC subsystem architecture can be seen in Figure 4.5.

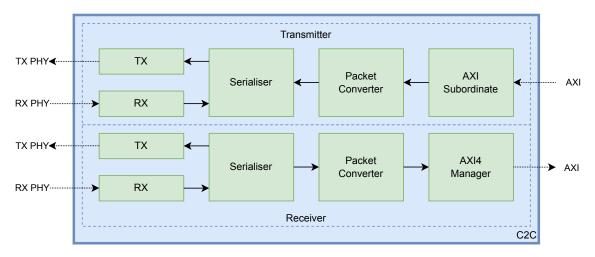

#### 4.5.4 C2C

The C2C subsystem allows Ballast to be functionally extended by exposing a bidirectional physical interface. The interface implementation performs data transfer at a higher frequency than conventional serial communications protocols (e.g. SPI or I2C) without significantly increasing the pin count of the chip as would happen when using a parallel interface. The C2C interface enables efficient communications between Ballast and off-chip memories, sensors or another instance of Ballast.

The subsystem is connected to the Ballast interconnect via an AXI interface. It takes AXI transactions from the interconnect, converts them to an asynchronous serial protocol and then transmits them off-chip. Similarly, it receives serial data asynchronously over the external interface and converts it to an AXI transaction, which is then sent over the Ballast interconnect. Data synchronisation between the external interface and the interconnect is performed using asynchronous FIFOs and handshaking over the physical interface. With a clock frequency of 200MHz, a uni-directional bandwidth of 3.2Gbps can be achieved

Figure 4.6. High-level View of C2C Architecture

[43]. A high-level view of the HPC subsystem architecture can be seen in Figure 4.6.

# 4.6 Debugging Architecture

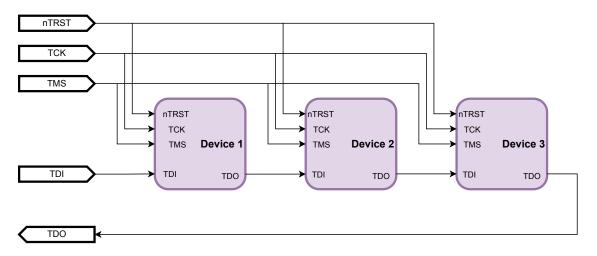

# 4.6.1 JTAG

As integrated circuits became more complex and SMD components became more prevalent in solutions, it became more challenging for engineers to test the ICs by directly probing pins: JTAG was developed in 1985 as a solution to this problem. JTAG defines that a small number of pins and testing infrastructure are to be added to the design of each IC in a solution (see Figure 4.7. The pins of each IC can then be connected and presented to the user as a single JTAG port [14].

The JTAG standard defines a protocol which can be used to control the testing infrastructure (JTAG TAP) on each IC. The protocol controls a state machine that can store/load data to/from the IC [49]. With a few basic instructions, it is possible to control/monitor the IC functionality or perform boundary scan tests to verify the integrity of the circuits implemented on the chip. Additionally, the scope of how JTAG can be used has expanded to include more advanced functions, such as programming FPGA bitstreams into devices and integrating with external logic analysers to present the internal operations of an IC onto a display [14].

Alternatives to JTAG have been developed such as cJTAG and SWD with the goal of reducing the pin-count and area of the testing/debugging infrastructure.

# 4.6.2 Debug and Trace

With the complexity of modern SoCs, it is of utmost importance that mechanisms are provided to allow engineers to understand software behaviour and quickly identify software

Figure 4.7. Example of Daisy-Chained JTAG Bus for Test/Debug of Three Devices

issues. Exactly how this is achieved can vary from chip to chip. However, the implementations generally aim to provide either debug capabilities, trace capabilities or some combination of both.

Debug capabilities typically include:

- Controlling execution of a core to enable the pausing of execution and stepping through the instruction execution.

- Accessing core registers.

- Performing reads/writes either directly from the debug infrastructure or using a selected core to perform the operation.

- Setting/clearing watchpoints/breakpoints within the code such that system events can be generated when particular conditions are met.

When debugging some code of interest on an SoC, manipulating the execution state can cause undesired secondary effects in the system's state. Therefore, it can become difficult to replicate an issue using debug capabilities alone. Trace capabilities complement this by allowing the user to stream configurable data or events to a dedicated memory or IO port. This data can be extracted and reviewed externally to allow the user to analyse the core or system behaviour without interfering with the execution [23].

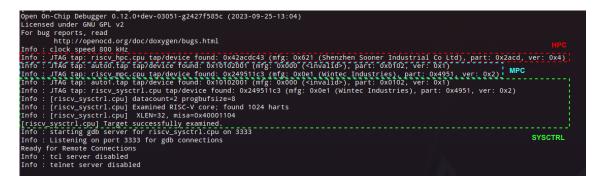

# 4.6.3 OpenOCD

OpenOCD is an open-source software project which can be used to debug an application on a remote device. OpenOCD runs as a server and can be targeted by the GDB and can then communicate to a hardware debugging interface to send commands to a remote chip using a protocol such as JTAG or SWD. It supports the debugging of multiple platforms and can be configured to allow the debugging of multiple cores within a heterogeneous

| Subsystem | Debug Module        | Specification Version |

|-----------|---------------------|-----------------------|

| SysCtrl   | PULP Debug Module   | Not Compliant         |

|           | RISC-V Debug Module | v0.13.1               |

| MPC       | PULP Debug Module   | Not Compliant         |

|           | RISC-V Debug Module | v0.13.1               |

| HPC       | RISC-V Debug Module | v0.13.1               |

|           | •                   |                       |

*Table 4.1.* Debug modules contained within Ballast and their compliance with the RISC-V Debug Specification.

SoC [41].

#### 4.6.4 Ballast Debugging

The Ballast SoC is designed with the capability to debug the subsystems containing CPU cores and use these cores to debug the remaining systems on the chip indirectly. No trace capability is included to minimise the design complexity. Each of the HPC, MPC and SysCtrl subsystems is implemented with a RISC-V debug module and JTAG TAP. In addition, the SysCtrl and MPC subsystem also contain a custom implementation of a debug module, which was used by the PULP project for internal testing.

The RISC-V debug module specification has not yet been formally ratified and is in a draft state. As a result, the specification is updated frequently. Each of the HPC, MPC and SysCtrl IPs were initially forked from separate existing project repositories. The repositories for each subsystem used implementations of the RISC-V debug module, which are aligned to version v0.13.1 of the draft specification. The versions used by each subsystem can be found in Table 4.1.

Version 0.13.1 of the RISC-V Debug Specification the RISC-V module can be found in [20]. A sample of the most relevant supported features are:

- RISC-V hart registers can be read/written.

- Ability to debug all harts in the hardware platform.

- Each hart can be debugged from first instruction execution.

- Memory access from the system bus or hart.

- Breakpoint support.

- Hardware single-step can execute one instruction at a time.

The Ballast SoC has a single set of JTAG ports on the top level. As is typical in modern SoC architectures, these ports for the JTAG bus and the JTAG TAP of each subsystem with debug capabilities are connected to this bus, as can be seen in Figure 4.8.

Figure 4.8. Ballast JTAG Bus Connections

# 5. FPGA PROTOTYPE IMPLEMENTATION

### 5.1 Prototype Configurations

The objectives for the Ballast FPGA prototyping were outlined within Section 4.4.2. The list below re-states the objectives as requirements and describes the FPGA prototype configurations that were suitable to satisfy them.

1. Validate the SoC boot design:

Ballast boot is controlled by the SysCtrl subsystem. It utilises the JTAG, SDIO and QSPI peripherals. An FPGA prototype containing at least the SysCtrl subsystem with those interfaces exposed externally is required to verify the boot design.

2. Validate the debugging architecture:

As Section 4.6.4 mentions, the Ballast debugging infrastructure is connected to the SysCtrl, MPC and HPC subsystems. An FPGA prototype containing these subsystems and the debugging infrastructure is required to test the chip debugging capabilities.

3. Validate peripheral functionality through the use of real components:

Both SysCtrl and MPC are the designated subsystems to perform operations with peripherals. An FPGA prototype of at least the SysCtrl and MPC subsystems (together or standalone) with exposed peripheral IO pins is required to achieve this objective.

4. Provide a platform for development of the SoC BSP and tools used for the SoC wake-up activities:

The main focus of the software development plan for Ballast was using the RISC-V cores to develop a Rust-based HAL. Therefore, FPGA prototypes of the HPC, MPC and SysCtrl subsystems were a priority for this. These could be in a standalone or combined platform.

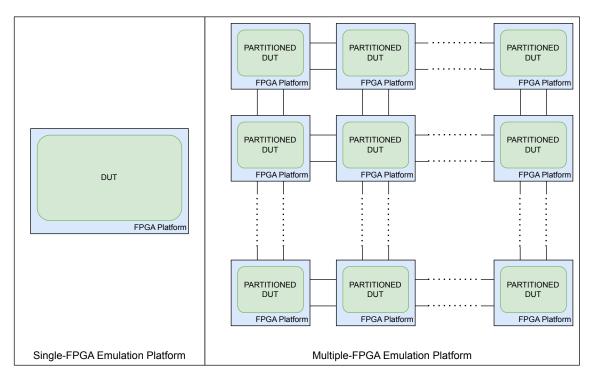

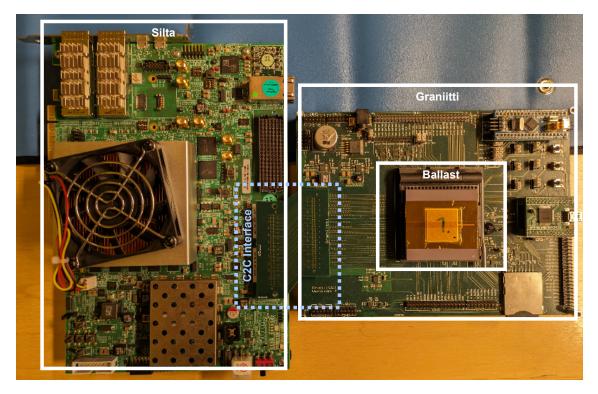

5. Validate the functionality of the asynchronous C2C interface:

As mentioned in Section 4.5.4, the C2C subsystem is designed to be used as an asynchronous interface. Therefore, to fully validate this aspect of the design, a prototype configuration of two connected C2C subsystems would need to be created. Each subsystem would use a clock which is asynchronous to each other. The image in Figure 5.1 illustrates how the Ballast architecture was partitioned for prototyping. Each partition is labelled with the ID of the requirement it aimed to satisfy. Some requirements are partially satisfied by multiple partitions. The remaining subsystems were not included within the scope of SoCHub FPGA prototyping due to them already being prototyped independently of the SoCHub project.

Figure 5.1. Partitioning of Ballast Architecture for Prototyping

### 5.2 Platform Hardware Selection

The primary characteristics that were considered when selecting a platform for prototyping were the size of the FPGA fabric, functional features offered by the FPGA and number of available IO pins. This led to the selection of three platforms which are described in the following sections.

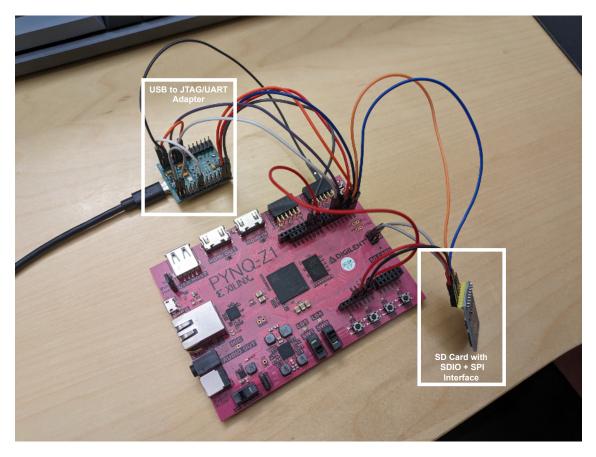

Figure 5.2. Digilent Pynq-Z1 Development Board [19]

# 5.2.1 Digilent PYNQ-Z1

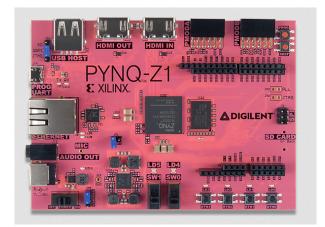

The PYNQ-Z1 (Figure 5.2) is an FPGA development board supplied by Digilent, which is designed to be used with the PYNQ project, an open-source project from AMD, to make it easier to develop adaptive computing platforms by using Python to develop programmable logic for selected AMD platforms [1].

The board itself houses an AMD Zynq (XC7Z020-1CLG400C) SoC, which contains a dual-core Arm Cortex-A9 processor, a DDR3 memory controller, high-bandwidth peripheral controllers, low-bandwidth peripheral controllers, with Artix-7 programmable logic having the resources shown in Table 5.1[19]. The PYNQ-Z1 board exposes 49 external IOs, making it an appropriate choice for implementing smaller designs with many external peripherals.

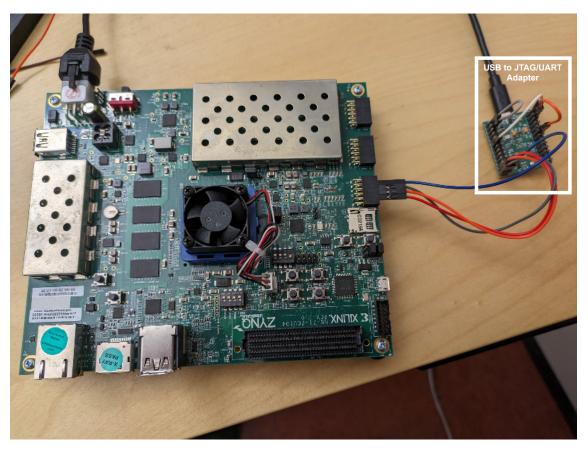

# 5.2.2 AMD Zynq UltraScale+ MPSoC ZCU104

The ZCU104 (Figure 5.3) is an evaluation kit supplied by AMD-Xilinx targeted for use in embedded vision applications. It houses a Zynq Ultrascale+ (XCZU7EV-2FFVC1156) MPSoC, which contains a quad-core Arm Cortex-A53 APU, a dual-core Cortex-R5 real-time processor, GPU, video codec, DDR4 memory controller, a rich set of both high-bandwidth peripheral controllers and low-bandwidth peripheral controllers, with Ultrascale programmable logic containing the resources shown in Table 5.1[3]. The ZCU104 board exposes three PMOD interfaces and an LPC FMC socket, making it an appropriate choice to implement medium-sized designs with a small number of external peripherals.

# 5.2.3 AMD Virtex UltraScale+ FPGA VCU118

The VCU118 (Figure 5.4) is an evaluation kit supplied by AMD-Xilinx targeted for high-performance FPGA designs. It houses a VCU118 XCVU9P-L2FLGA2104E FPGA, which

Figure 5.3. AMD-Xilinx ZCU104 Development Board [3]

Figure 5.4. AMD-Xilinx VCU118 Development Board [2]

contains a DDR4 memory controller, a selection of high-bandwidth peripheral controllers, with a Virtex Ultrascale programmable logic having resources shown within 5.1[2]. The VCU118 board exposes 2 PMOD connectors and 2 HPC FMC sockets, making it an appropriate choice for large, high-performance designs with few external peripherals.

| Resources   | PYNQ-Z1 [19] | ZCU104 [3] | VCU118 [2] |

|-------------|--------------|------------|------------|

| Logic Cells | 13.3k        | 504.0k     | 2,586.0k   |

| Memory (Mb) | 5.04         | 38.0       | 345.9      |

| DSP Slices  | 220          | 1,728      | 6,840      |

Table 5.1. Comparison of Programmable Logic Resources In Selected Platforms

### 5.2.4 Prototype Configuration to Platform Mapping

Using the platform information and configuration requirements detailed within the previous sections, Table 5.2 indicates a suitable mapping between the prototype configurations and the selected hardware platforms.

| Configuration | Design Size | IO Count | Platform      |

|---------------|-------------|----------|---------------|

| SysCtrl       | Small       | High     | PYNQ-Z1       |

| MPC           | Small       | High     | PYNQ-Z1       |

| HPC           | Medium      | Low      | ZCU104/VCU118 |

| C2C           | Medium      | Low      | ZCU104/VCU118 |

| Top Level     | Large       | Low      | VCU118        |

**Table 5.2.** Mapping of Prototype Configuration Against the Most Suitable Hardware Platforms

#### 5.3 **Prototype Build Flow Development**

#### 5.3.1 GNU Make

GNU Make is an easy to use, but powerful build tool which allows Users to define commands (referred to as Make targets), which can then be used to perform complex command sequences and generate output artefacts [32]. It is traditionally used to construct C/C++ software projects but can also be used in hardware to drive tools.

#### 5.3.2 TCL

TCL is a general-purpose interpreted scripting language which is commonly used to drive the operation of modern IC development tools. It was developed in the late 1980s to attempt to unify the various command line tools used to drive the various IC development tools that existed at the time. It was designed to be easily extensible so that on top of the base language, each vendor could extend and add custom functions which could be used to drive their tool efficiently [40].

#### 5.3.3 Vivado IDE

As AMD-Xilinx FPGA platforms were selected for prototyping, the AMD-Xilinx Vivado IDE was used to develop the prototypes. The Vivado IDE can be operated using a GUI or driven using TCL [11]. Version 2019.2 was chosen to maintain compatibility with the example FPGA flows by the open-source IP used within Ballast.

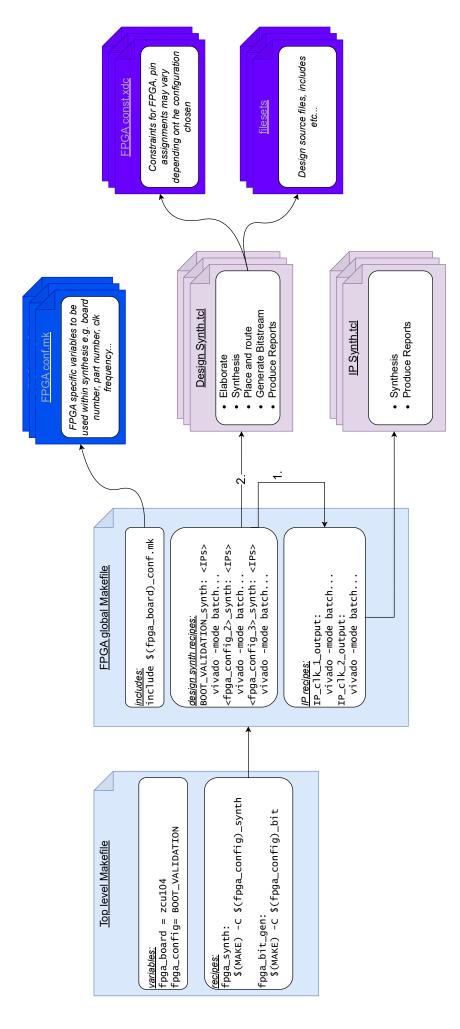

#### 5.3.4 Synthesis Flow

As described in Section 3.4.2, the synthesis flow for FPGA designs contains multiple artefacts and stages. There was a desire to develop a flow for the Ballast prototyping aligned with the ASIC RTL simulation flow. An aligned flow would ensure that users

who are familiar with the existing RTL simulation flow, but might be unfamiliar with FPGA development would be able to quickly generate a bitstream for running tests on FPGA without any need to modify their environment or use unfamiliar tools.

The entry point for building and simulating the Ballast RTL was a top-level Makefile containing multiple targets. The general approach to align the FPGA build process with the existing RTL simulation process was to create a top-level Makefile within a sub-directory dedicated to the FPGA build. The Makefile contained targets to fully build a prototype configuration, build selected IPs for a specific prototype configuration, or clean the environment of all files generated during the build process. Once the main build target is called, the build completes the FPGA build efficiently and returns to the entry point. The specific prototype configuration and target platform are selected through variables assigned when calling the target (FPGA\_CONF and FPGA\_BRD, respectively). The static configuration data for each FPGA prototype is stored within separate files, which are included depending on the value of the FPGA\_CONF and FPGA\_BRD variables. Listing 5.1 shows an example of how the build process for the HPC prototype configuration on the ZCU104 platform could be initiated:

#### Listing 5.1. Example call of FPGA build

make all FPGA\_CONF=HPC FPGA\_BRD=ZCU104

An abstract illustration of how the FPGA build flow operates can be seen in Figure 5.5.

#### 5.4 General FPGA Prototype Implementation Strategies

Modifications to the ASIC design were required to implement the FPGA prototype configurations. As described within [24], the focus of this exercise was not to completely rewrite the design as this would contradict the aim of using the same sources for ASIC and FPGA prototype, but to optimise critical design parts either for performance or resource utilisation. The scope of this section is limited to prototype implementation modifications applied to all of the prototyping configurations in Ballast. Subsystem-specific considerations can be found in Sections 5.5 to 5.8.

### 5.4.1 RTL Partitioning

When prototyping a portion of a complex SoC, it is necessary to ensure a suitable partition is drawn between the parts of the design required for functional testing of the target design and the rest of the SoC design. The process of functionally partitioning the SoC into prototyping configurations is outlined in Section 4.5. This section describes the common low-level approach to partition each prototyping configuration from the rest of the SoC.

Each subsystem of Ballast was initially developed as a standalone IP. The IP was then integrated into a wrapper component, which contained components and interfaces common to each subsystem on the SoC. This wrapper component was then instantiated on the SoC top level and connected to the other subsystems on the SoC. For the FPGA prototyping of the individual subsystems, the wrapper component is replaced with an FPGA wrapper equivalent, which removes the unwanted ports to the rest of the SoC and contains required FPGA-specific components (see Figure 5.6).

For example, the SysCtrl wrapper module port definition includes ports for the AXI4 interface, clock controls, PLL configuration and peripheral IO signals. The SysCtrl FPGA wrapper module removed the AXI4 interface, clock controls and PLL configuration. It should be noted that some of the external signals removed from the original wrapper are inputs to the SysCtrl IP. These signals were driven by constant values within the wrapper to prevent build issues or bugs in the FPGA design. In addition to the port modifications, the SysCtrl wrapper module contained CDC logic for the signals travelling between clock domains on the SoC. As described within Section 5.4.2, to simplify the prototyping design, each design was implemented within a single clock domain. Therefore, the CDC components within the wrapper were removed. Furthermore, to control the clock generation in the FPGA design, a clock management IP was instantiated in the FPGA wrapper, which replaced the PLL component contained within the original wrapper.

Figure 5.6. Comparison of Top-Level Wrapper Used for ASIC and FPGA Prototyping

#### 5.4.2 Input Clock Architecture

The Ballast SoC was designed to allow most IPs to operate at configurable clock frequencies by including a PLL IP and clock selection logic components within the wrapper of each subsystem. It is impossible to synthesise the PLL IP used within each wrapper for FPGA, as it is implemented using mixed-signal components not present in the FPGA platforms. Additionally, as the FPGA platform uses different technologies to implement the logic compared to the ASIC, there is no way to gain useful timing information from the prototype. Therefore, a decision was made to make the clock tree in the prototype as simple as possible. As a result, clock selection logic was not included within the FPGA wrapper, leaving the design to be fed from a single clock.

While the clocking inputs to the design were simplified for prototyping, having control over the clock configuration is still valuable. As mentioned previously, the technology used to implement the design on FPGA significantly differs from the technology used to implement the ASIC design. As a result, achieving the targeted high clock frequencies of the ASIC design is often impossible. Therefore, clock management components need to be inserted into the FPGA design to reduce the frequency of the design. The AMD-Xilinx Clocking Wizard is an IP provided within Vivado, which enables the possibility of synthesising one or more clock signals with an output frequency independent of the IP's input clock frequency [4]. The frequency of the clock manager IP was defined within the

static configuration data described in Section 5.3.4 and could be changed at compile time if desired. Note that the IP can also perform dynamic clock configuration via an AXI-Lite slave interface; whilst this was not used for prototyping Ballast subsytems, it is clear that this could provide value when prototyping future designs.

### 5.4.3 Memory Interfaces

A common component found within modern SoCs is on-chip memory. Depending on the requirements and process selected to implement the ASIC, on-chip memory can be implemented using different technologies. The functionality of on-chip memory modules can also vary depending on the needs of the design. This difference in functionality is typically reflected in the ports on the interface to the memory module. For example, memory interfaces can use a single port or dual port configuration and contain additional control signals, such as a byte-enable signal, to mask the contents of the read memory.

As described in Section 3.3.3, FPGAs contain limited on-chip memory in the form of BRAMs. It is desirable to utilise FPGA BRAM to implement the ASIC on-chip memories within the FPGA prototype, as otherwise, the memories are implemented using registers (known as register RAM) or LUTs (known as distributed RAM). For larger memory sizes, register RAM or LUT RAM can become expensive in terms of logic resources and increase the complexity of the routing task performed by the FPGA design tools.

The memory configurations created using BRAMs on FPGA vary between FPGA platforms. Vivado offers the ability to either infer memories through specific RTL constructs (an example of a module which infers a single port memory can be seen in Listing A.1 ) or via instantiating BRAM IPs within the design. Each on-chip memory instance within Ballast included within the prototype was refactored to ensure that the RTL used to instantiate the memory was compatible with the pattern required by Vivado to infer the appropriate BRAM. Furthermore, due to the resource constraints of the FPGA platform, reducing the size of the memories used by the prototype configuration may be necessary. The specific modifications for each configuration are described in detail within the appropriate subsection below.

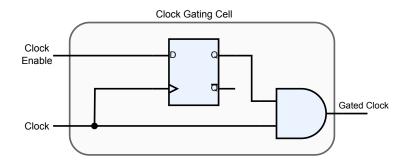

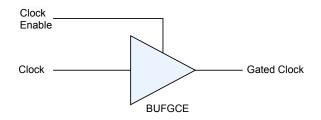

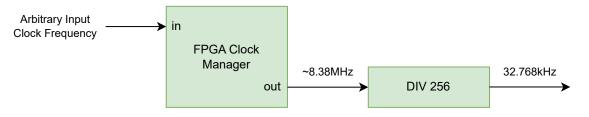

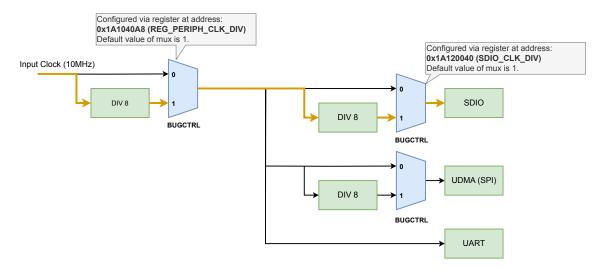

### 5.4.4 Clock Gating