# PANU SJÖVALL

# Feasibility Study of High-Level Synthesis

Implementation of a Real-Time HEVC Intra Encoder on FPGA

# PANU SJÖVALL

# Feasibility Study of High-Level Synthesis Implementation of a Real-Time HEVC Intra Encoder on FPGA

#### ACADEMIC DISSERTATION

To be presented, with the permission of the Faculty of Information Technology and Communication Sciences of Tampere University,

for public discussion in the auditorium TB109

of Tietotalo, Korkeakoulunkatu 1, Tampere,

on 17 March 2023, at 12 o'clock.

#### ACADEMIC DISSERTATION

Tampere University, Faculty of Information Technology and Communication Sciences

Responsible Associate Professor

supervisor Jarno Vanne

and Custos Tampere University

Finland

Supervisor Professor

Timo Hämäläinen Tampere University

Finland

Pre-examiners Associate Professor Dr. Ercan Kalali

Maxime Pelcat Eindhoven University of Technology

INSA Rennes, IETR Netherlands

France

Opponents Associate Professor Dr.-Ing. Christian Herglotz

Maxime Pelcat Friedrich-Alexander University

INSA Rennes, IETR Erlangen-Nürnberg

France Germany

The originality of this thesis has been checked using the Turnitin OriginalityCheck service.

Copyright ©2023 author

Cover design: Roihu Inc.

ISBN 978-952-03-2775-0 (print) ISBN 978-952-03-2776-7 (pdf)

ISSN 2489-9860 (print) ISSN 2490-0028 (pdf)

http://urn.fi/URN:ISBN:978-952-03-2776-7

Carbon dioxide emissions from printing Tampere University dissertations have been compensated.

PunaMusta Oy – Yliopistopaino Joensuu 2023

#### **PREFACE**

The research for this thesis was conducted in *Tampere University of Technology* (*TUT*) Department of Pervasive Computing and Laboratory of Pervasive Computing during 2014-2018 and in *Tampere University* (*TAU*) Computing Sciences during 2019-2021. Although the name of the university and the unit has changed during this journey, I have had the pleasure to be a part of the *Ultra Video Group* (*UVG*), led by Assoc. Prof. Jarno Vanne, the whole time. I received my M.Sc, degree in December 2015 and started pursuing for a PhD in August 2016. I was lucky enough that I could continue the same research during my doctoral studies that I started with my M.Sc. The research was thus a direct continuation of my master's thesis titled "High-Level Synthesis of HEVC Intra Prediction on FPG". This thesis describes the fully HLS implemented HEVC intra video encoder on FPGA.

I would like to express my deepest gratitude to Assoc. Prof. Jarno Vanne and Prof. Timo D. Hämäläinen for giving me the opportunity to work at the university, and for the guidance and collaboration with practically all of the publications. Also, a big thanks to all other co-authors collaborating to the research and publications, including Vili Viitamäki, Arto Oinonen, Mikko Teuho, Ari Lemmetti, Sakari Lahti, Janne Virtanen, and Ari Kulmala. A special thanks goes to my supervisor Assoc. Prof. Jarno Vanne for the supervision of my thesis and for all the help during my doctoral studies.

I would also like to thank my colleagues working in the same office room as I did, Esko Pekkarinen, Mikko Teuho, and Vili Viitamäki. Thank you for all the discussions (random and work related), for the company during lunchtime and coffee breaks, and for the occasional game of chess. These have been an essential part of work happiness and provided a small break from work when needed. It helped keeping the motivation high and reaching this final goal.

Finally, I would like to thank my family for all the support during this process.

I would have never gotten this far with my academic career without you. It is a privilege to come home from work to a loving family. Even though I had some doubts about working remotely from home during the COVID-19 situation at first, it proved to be very easy and pleasant. Even the writing of this thesis was done fully at home. Working from home has also made it possible to spend even more time with you.

Panu Sjövall 11.11.2022 Ylöjärvi

#### **ABSTRACT**

High-Level Synthesis (HLS) is an automated design process that seeks to improve productivity over traditional design methods by increasing design abstraction from register transfer level (RTL) to behavioural level. Various commercial HLS tools have been available on the market since the 1990s, but only recently they have started to gain adoption across industry and academia. The slow adoption rate has mainly stemmed from lower quality of results (QoR) than obtained with conventional hardware description languages (HDLs). However, the latest HLS tool generations have substantially narrowed the QoR gap.

This thesis studies the feasibility of HLS in video codec development. It introduces several HLS implementations for *High Efficiency Video Coding (HEVC)*, that is the key enabling technology for numerous modern media applications. HEVC doubles the coding efficiency over its predecessor *Advanced Video Coding (AVC)* standard for the same subjective visual quality, but typically at the cost of considerably higher computational complexity. Therefore, real-time HEVC calls for automated design methodologies that can be used to minimize the HW implementation and verification effort.

This thesis proposes to use HLS throughout the whole encoder design process. From data-intensive coding tools, like intra prediction and discrete transforms, to more control-oriented tools, such as entropy coding. The C source code of the open-source Kvazaar HEVC encoder serves as a design entry point for the HLS flow, and it is also utilized in design verification. The performance results are gathered with and reported for *field programmable gate array* (*FPGA*).

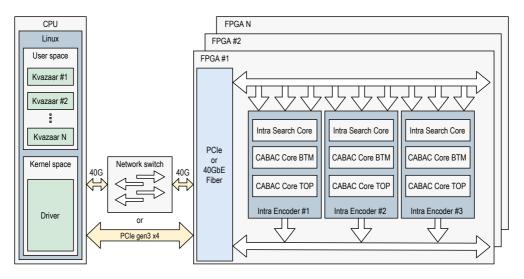

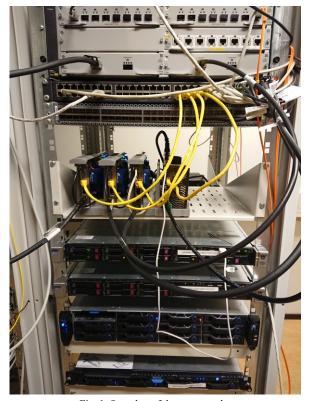

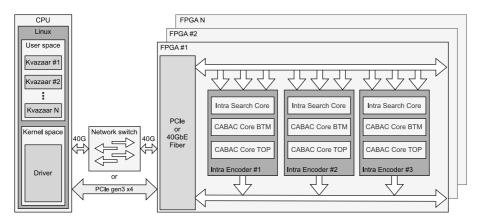

The main contribution of this thesis is an HEVC intra encoder prototype that is built on a Nokia AirFrame Cloud Server equipped with 2.4 GHz dual 14-core Intel Xeon processors and two Intel Arria 10 GX FPGA Development Kits, that can be connected to the server via *peripheral component interconnect express* (*PCIe*) generation 3 or 40 Gigabit Ethernet. The proof-of-concept system achieves real-time

4K coding speed up to 120 fps, which can be further scaled up by adding practically any number of network-connected FPGA cards.

Overcoming the complexity of HEVC and customizing its rich features for a real-time HEVC encoder implementation on hardware is not a trivial task, as hardware development has traditionally turned out to be very time-consuming. This thesis shows that HLS is able to boost the development time, provide previously unseen design scalability, and still result in competitive performance and QoR over state-of-the-art hardware implementations.

# TIIVISTELMÄ

High-Level Synthesis (HLS) on automatisoitu suunnitteluprosessi, joka pyrkii parantamaan tuottavuutta perinteisiin suunnittelumenetelmiin verrattuna, rekisterisiirtotasolta nostamalla abstraktiota (RTL)suunnittelun käyttäytymistasolle. Erilaisia kaupallisia HLS-työkaluja on ollut markkinoilla aina 1990-luvulta lähtien, mutta vasta äskettäin ne ovat alkaneet saada hyväksyntää teollisuudessa sekä akateemisessa maailmassa. Hidas käyttöönottoaste on johtunut pääasiassa huonommasta tulosten laadusta (QoR) kuin mitä on ollut mahdollista tavanomaisilla laitteistokuvauskielillä (HDL). Uusimmat HLS-työkalusukupolvet ovat kuitenkin kaventaneet QoR-aukkoa huomattavasti.

Tämä väitöskirja tutkii HLS:n soveltuvuutta videokoodekkien kehittämiseen. Se esittelee useita HLS-toteutuksia *High Efficiency Video Coding (HEVC)*-koodaukselle, joka on keskeinen mahdollistava tekniikka lukuisille nykyaikaisille mediasovelluksille. HEVC kaksinkertaistaa koodaustehokkuuden edeltäjäänsä *Advanced Video Coding (AVC)* -standardiin verrattuna, saavuttaen silti saman subjektiivisen visuaalisen laadun. Tämä tyypillisesti saavutetaan huomattavalla laskennallisella lisäkustannuksella. Siksi reaaliaikainen HEVC vaatii automatisoituja suunnittelumenetelmiä, joita voidaan käyttää *rautatoteutus- (HW)* ja varmennustyön minimoimiseen.

Tässä väitöskirjassa ehdotetaan HLS:n käyttöä koko enkooderin suunnitteluprosessissa. Dataintensiivisistä koodaustyökaluista, kuten intra-ennustus ja diskreetit muunnokset, myös enemmän kontrollia vaativiin kokonaisuuksiin, kuten entropiakoodaukseen. Avoimen lähdekoodin Kvazaar HEVC -enkooderin C-lähdekoodia hyödynnetään tässä työssä referenssinä HLS-suunnittelulle sekä toteutuksen varmentamisessa. Suorituskykytulokset saadaan ja raportoidaan ohjelmoitavalla porttimatriisilla (FPGA).

Tämän väitöskirjan tärkein tuotos on HEVC intra enkooderin prototyyppi. Prototyyppi koostuu Nokia AirFrame Cloud Server palvelimesta, varustettuna

kahdella 2.4 GHz:n 14-ytiminen Intel Xeon prosessorilla, sekä kahdesta Intel Arria 10 GX FPGA kiihdytinkortista, jotka voidaan kytkeä serveriin käyttäen joko peripheral component interconnect express (PCIe) liitäntää tai 40 gigabitin Prototyyppijärjestelmä 4K Ethernettiä. reaaliaikaisen saavuttaa järjestelmän enkoodausnopeuden, jopa 120 kuvaa sekunnissa. Lisäksi suorituskykyä on helppo skaalata paremmaksi lisäämällä järjestelmään käytännössä minkä tahansa määrän verkkoon kytkettäviä FPGA-kortteja.

Monimutkaisen HEVC:n tehokas mallinnus ja sen monipuolisten ominaisuuksien mukauttaminen reaaliaikaiselle HW HEVC enkooderille ei ole triviaali tehtävä, koska HW-toteutukset ovat perinteisesti erittäin aikaa vieviä. Tämä väitöskirja osoittaa, että HLS:n avulla pystytään nopeuttamaan kehitysaikaa, tarjoamaan ennen näkemätöntä suunnittelun skaalautuvuutta, ja silti osoittamaan kilpailukykyisiä QoR-arvoja ja absoluuttista suorituskykyä verrattuna olemassa oleviin toteutuksiin.

# **CONTENTS**

| Pre | face .   |           |                                                             |

|-----|----------|-----------|-------------------------------------------------------------|

| Ab  | stract.  |           |                                                             |

| Ab  | breviati | ions      |                                                             |

| Ori | iginal p | ublicatio | nsxix                                                       |

| 1   | Intro    | duction.  |                                                             |

|     | 1.1      | The mo    | otivation and objectives of the research                    |

|     | 1.2      | Researc   | ch questions and methods                                    |

|     | 1.3      | Summa     | ry of publications                                          |

|     | 1.4      | Outline   | e of the thesis                                             |

|     | 1.5      | Acknow    | wledgments                                                  |

| 2   | Backg    | ground .  |                                                             |

|     | 2.1      | Autom     | ated design process: High-level synthesis (HLS) 11          |

|     |          | 2.1.1     | HLS flow                                                    |

|     |          | 2.1.2     | Advantages of HLS over traditional hardware design          |

|     |          |           | methods                                                     |

|     |          | 2.1.3     | Catapult HLS tool                                           |

|     |          | 2.1.4     | HLS design example                                          |

|     | 2.2      | Applica   | ation of Interest: High Efficiency Video Coding (HEVC) . 18 |

|     |          | 2.2.1     | Block partitioning structure                                |

|     |          | 2.2.2     | Intra prediction                                            |

|     |          | 2.2.3     | Inter prediction                                            |

|     |          | 2.2.4     | Transform coding                                            |

|     |          | 2.2.5     | Entropy coding                                              |

|     |          | 2.2.6     | Techniques for HEVC encoder parallelization 21              |

|   |       | 2.2.7       | Open-source implementations for HEVC encoding        | . 22 |

|---|-------|-------------|------------------------------------------------------|------|

|   |       | 2.2.8       | Kvazaar HEVC encoder                                 | . 23 |

|   | 2.3   | Target o    | device: Field-programmable gate array (FPGA)         | . 23 |

| 3 | Relat | ed work     |                                                      | . 27 |

|   | 3.1   | Existing    | g HLS implementations for HEVC                       | . 27 |

|   |       | 3.1.1       | Intra prediction                                     | . 27 |

|   |       | 3.1.2       | DCT and IDCT                                         | . 29 |

|   |       | 3.1.3       | Interpolation                                        | . 29 |

|   |       | 3.1.4       | Hadamard SATD                                        | . 30 |

|   |       | 3.1.5       | Decoding tools                                       | . 30 |

|   | 3.2   | Existing    | g hardware implementations for HEVC entropy coding   | . 30 |

|   |       | 3.2.1       | Whole entropy encoder                                | . 31 |

|   |       | 3.2.2       | Separate implementations for arithmetic encoding or  |      |

|   |       |             | binarization                                         | . 31 |

|   | 3.3   | Existing    | g hardware implementations for complete HEVC         |      |

|   |       | encoder     | ·s                                                   | . 32 |

|   |       | 3.3.1       | Academic HEVC encoders on FPGA                       | . 32 |

|   |       | 3.3.2       | Academic HEVC encoders on FPGA/ASIC                  | . 33 |

|   |       | 3.3.3       | Academic HEVC encoders on ASIC                       | . 34 |

|   | 3.4   | How to      | improve upon prior art                               | . 34 |

| 4 | Resul | ts of the r | research                                             | . 37 |

|   | 4.1   | HLS im      | plementations of single HEVC intra encoding tools    | . 37 |

|   |       | 4.1.1       | Intra prediction                                     | . 37 |

|   |       | 4.1.2       | Transform coding                                     | . 38 |

|   |       | 4.1.3       | User study: HLS vs. manual RTL                       | . 39 |

|   | 4.2   | FPGA-       | accelerated HEVC intra search on a compute server    | . 40 |

|   |       | 4.2.1       | 1st generation Intra Search Core                     | . 41 |

|   |       | 4.2.2       | 2nd generation Intra Search Core                     | . 42 |

|   |       | 4.2.3       | Live demonstration of the Intra Search Core          | . 44 |

|   | 4.3   | FPGA-       | accelerated HEVC intra search in a cloud environment | . 44 |

|   | 4.4   | Comple      | ete HEVC intra encoder on FPGA                       | . 45 |

| 5 | Conc  | lusion .    |                                                      | . 49 |

|   | 5.1   | Discussi    | ion about lessons learned                            | 49   |

| 3.      | HEVC encoder                                                             |

|---------|--------------------------------------------------------------------------|

| 5.      |                                                                          |

|         | implementations against existing work 51                                 |

| 5.      |                                                                          |

| Referen | nces                                                                     |

| Publica | ation I                                                                  |

| Publica | ation II                                                                 |

| Publica | ation III                                                                |

| Publica | ation IV                                                                 |

| Publica | ation V                                                                  |

| Publica | ation VI                                                                 |

| Publica | ation VII                                                                |

| Publica | ation VIII                                                               |

| Publica | ation IX                                                                 |

| Publica | ation X                                                                  |

| List of | Figures                                                                  |

| 1.1     | Summary and connection of publications 6                                 |

| 1.2     | Author's main scientific contributions                                   |

| 2.1     | HLS design flow [Publication X]                                          |

| 2.2     | HEVC encoder model [6]                                                   |

| 2.3     | Parallelization approaches supported by HEVC: (a) slices, (b) tiles, (c) |

| 2.4     | wavefront parallel processing, and (d) overlapped wavefront              |

| 2.4     | Simplified example of an FPGA                                            |

| 2.5     | Programming                                                                    | 24 |

|---------|--------------------------------------------------------------------------------|----|

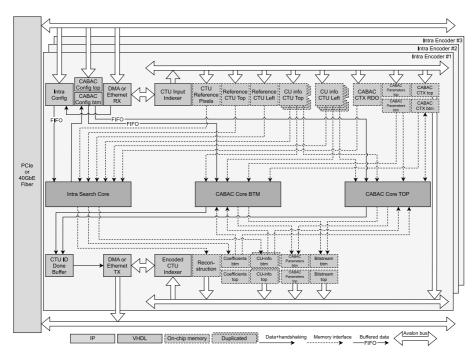

| 4.1     | System architecture of the proposed HEVC intra encoder on FPGA [Publication X] | 46 |

|         |                                                                                |    |

| List of | Tables                                                                         |    |

| 3.1     | Existing HLS approaches for HEVC encoding                                      | 28 |

| 3.2     | Existing HLS approaches for HEVC decoding                                      | 28 |

| 3.3     | Existing CABAC implementations for HEVC                                        | 33 |

| 3.4     | Existing commercial HEVC encoders on HW                                        | 33 |

| 3.5     | Existing academic HEVC encoders on HW                                          | 33 |

| 4.1     | HLS implemented HEVC intra prediction units with area and                      |    |

|         | performance figures                                                            | 38 |

| 4.2     | HLS-implemented HEVC DCT/DST units with area and performance figures           | 39 |

| 4.3     | HLS-implemented HEVC IDCT/IDST units with area and                             | 37 |

|         | performance figures                                                            | 40 |

| 4.4     | Area and performance figures from the test group study for HLS and             |    |

|         | RTL designs, with quality and productivity comparison                          | 40 |

| 4.5     | Supported base configuration for the proposed HW HEVC intra                    |    |

|         | encoder                                                                        | 42 |

| 4.6     | Corresponding intra depth ranges and luma PU and TU sizes                      | 42 |

| 4.7     | The resource consumption of the proposed 1st and 2nd generation                |    |

|         | Intra Search Cores                                                             | 43 |

| 4.8     | The performance of the proposed 1st and 2nd generation Intra Search            |    |

|         | Cores                                                                          | 43 |

| 4.9     | The performance of proposed Intra Search Cores using PCIe and                  |    |

|         | 40GbE                                                                          | 45 |

| 4.10    | The area figures of the proposed fully HLS implemented HEVC intra              |    |

|         | encoder on FPGA                                                                | 46 |

| 4.11 Performance comparison of the proposed standalone CABAC C |                                                                      |    |

|----------------------------------------------------------------|----------------------------------------------------------------------|----|

|                                                                | [Publication X] to related work $\ldots \ldots \ldots \ldots \ldots$ | 46 |

| 4.12                                                           | The 2160p performance of the proposed prototype HEVC intra           |    |

|                                                                | encoding system [Publication X]                                      | 47 |

| 4.13                                                           | Performance comparison with related work [Publication $X$ ]          | 47 |

| List of                                                        | Programs and Algorithms                                              |    |

| 2.1                                                            | HLS example                                                          | 17 |

### **ABBREVIATIONS**

AI All-Intra

ALM Adaptive logic module

ALUT Adaptive look-up table

AMP Asymmetric motion partition

ASIC Application-specific integrated circuit

AVC Advanced Video Coding

AVX2 Advanced vector extensions 2

BD-rate Bjøntegaard delta bitrate

CABAC Context-adaptive binary arithmetic coding

CB Coding block

CPB Current picture buffer

CPU Central processing unit

CTB Coding tree block

CTU Coding tree unit

CU Coding unit

D Residual

D' Inversed residual

D<sub>rec</sub> Reconstructed picture

D<sub>ref</sub> Reference picture

DCT Discrete cosine transform

DF Deblocking filter

DMA Direct memory access

DPB Decoded picture buffer

DSE Design space exploration

DSP Digital signal processing

DST Discrete sine transform

EC Entropy coding

EDA Electronic design automation

FIFO First in, first out

FME Fractional motion estimation

FPGA Field-programmable gate array

GbE Gigabit Ethernet

HDL Hardware description language

HDMI High-definition multimedia interface

HEVC High Efficiency Video Coding

HLS High-level synthesis

HM HEVC Test Model

HW Hardware

IDCT Inverse discrete cosine transform

IDST Inverse discrete sine transform

idx Reference picture index

IME Integer motion estimation

IP Internet protocol

IP Intra prediction

IPOL Interpolation

IQ Inverse quantization

IT Inverse transform

LE Logic element

LUT Loop filtering

LUT Look-up table

MC Motion compensation

MD Mode decision

ME Motion estimation

MV Motion vector

OWF Overlapped wavefront

$P_{inter}$  Inter prediction  $P_{intra}$  Intra prediction

PB Prediction block

PC Personal computer

PCIe Peripheral component interconnect express

PMI Prediction mode interlaced

PSNR Peak signal-to-noise ratio

PU Prediction unit

Q Quantization

QoR Quality of Results

QP Quantization parameter

QTCOEFF Quantized transform coefficient

RA Random access

RD Rate-distortion

RDO Rate-distortion optimization

RMD Rough mode decision

RTL Register transfer level

RTP Real-time transport protocol

SAD Sum of absolute differences

SAO Sample-adaptive offset

SATD Sum of absolute transformed differences

SDN Software defined networking

SoC System on Chip

SW Software

T Transform

TB Transform block

TCOEFF Transform coefficient

TCOEFF' Inversed transform coefficient

TU Transform unit

USB Universal serial bus

VHDL Very high-speed integrated circuit hardware description

language

WPP Wavefront parallel processing

#### ORIGINAL PUBLICATIONS

Publication I P. Sjövall, J. Virtanen, J. Vanne, and T. D. Hämäläinen, "Highlevel synthesis design flow for HEVC intra encoder on SoC-FPGA," in *Proceedings of Euromicro Conference on Digital System Design*,

Funchal, Madeira, Portugal, Aug. 2015. doi: 10.1109/DSD.2015.

67.

Publication II P. Sjövall, V. Viitamäki, J. Vanne, and T. D. Hämäläinen, "High-level

synthesis implementation of HEVC 2-D DCT/DST on FPGA," in *Proceedings of IEEE International Conference on Acoustics, Speech and Signal Processing*, New Orleans, Louisiana, USA, Mar. 2017. DOI:

10.1109/ICASSP.2017.7952416.

Publication III V. Viitamäki, P. Sjövall, J. Vanne, and T. D. Hämäläinen, "High-level

synthesized 2-D IDCT/IDST implementation for HEVC codecs on FPGA," in *Proceedings of IEEE International Symposium on Circuits and Systems*, Baltimore, Maryland, USA, May 2017. DOI: 10.1109/

ISCAS.2017.8050323.

Publication IV S. Lahti, P. Sjövall, J. Vanne, and T. D. Hämäläinen, "Are we

there yet? A study on the state of high-level synthesis," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 38, no. 5, pp. 898–911, May 2019. DOI: 10.1109/

TCAD.2018.2834439.

Publication V P. Sjövall, V. Viitamäki, A. Oinonen, J. Vanne, T. D. Hämäläinen,

and A. Kulmala, "Kvazaar 4K HEVC intra encoder on FPGA

accelerated air-frame server," in *Proceedings of IEEE International Workshop on Signal Processing Systems*, Lorient, France, Oct. 2017. DOI: 10.1109/

SiPS.2017.8109999.

- Publication VI P. Sjövall, V. Viitamäki, J. Vanne, T. D. Hämäläinen, and A. Kulmala, "FPGA-powered 4K120p HEVC intra encoder," in *Proceedings* of *IEEE International Symposium on Circuits and Systems*, Florence, Italy, May 2018. DOI: 10.1109/ISCAS.2018.8351873.

- Publication VII V. Viitamäki, P. Sjövall, J. Vanne, and T. D. Hämäläinen, "Live demonstration: 4K100p HEVC intra encoder," in *Proceedings of International Symposium on Circuits and Systems*, Florence, Italy, May 2018. DOI: 10.1109/ISCAS.2018.8351770.

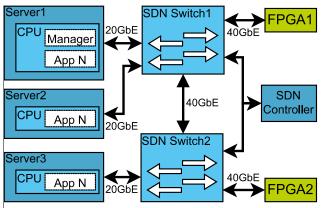

- Publication VIII P. Sjövall, A. Oinonen, M. Teuho, J. Vanne, and T. D. Hämäläinen, "Dynamic resource allocation for HEVC encoding in FPGA-accelerated SDN cloud," in *Proceedings of IEEE Nordic Circuits and Systems Conference*, Helsinki, Finland, Oct. 2019. DOI: 10.1109/NORCHIP. 2019.8906940.

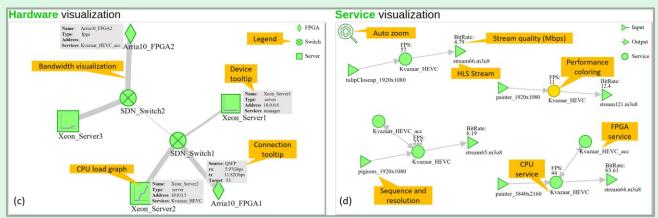

- Publication IX P. Sjövall, M. Teuho, A. Oinonen, J. Vanne, and T. D. Hämäläinen, "Visualization of dynamic resource allocation for HEVC encoding in FPGA-accelerated SDN cloud," in *Proceedings of IEEE Visual Communications and Image Processing*, Sydney, New South Wales, Australia, Dec. 2019. DOI: 10.1109/VCIP47243.2019.8966042.

- Publication X P. Sjövall, A. Lemmetti, J. Vanne, S. Lahti, and T. D. Hämäläinen, "High-level synthesis implementation of an embedded real-time HEVC intra encoder on FPGA for media applications," ACM Transactions on Design Automation of Electronic Systems, vol. 27, no. 7, May 2022. DOI: 10.1145/3491215.

## 1 INTRODUCTION

High-level synthesis (HLS) is an intriguing subject in the field of hardware (HW) design. Even though various commercial HLS tools have been available on the market since the 1990s, they have only recently started to gain adoption across industry and academia [1]. One can argue that the slow adoption rate has mainly stemmed from lower quality of results (QoR) than obtained with conventional hardware description language (HDL) approaches. However, the latest HLS tool generations have substantially narrowed the QoR gap. HLS has also traditionally worked well with data-intensive designs, whereas implementing clock accurate control structures has been more challenging due to the lack of explicit time information in behavioural source code [2], [3].

Using HLS to fully implement a complex *High Efficiency Video Coding (HEVC)* [4], [5] video encoder on HW should give good insight on how HLS performs over traditional HDLs. HEVC is the key enabling technology for numerous modern media applications. HEVC doubles the coding efficiency over its predecessor *Advanced Video Coding (AVC)* standard for the same subjective visual quality, but typically at the cost of considerable computational complexity. Overcoming the complexity of HEVC and customizing its rich features for a real-time HEVC encoder implementation on HW is not a trivial task, as HW designs are traditionally very time-consuming. Thus, the development of modern video encoders can make use of automated design methodologies that can be used to minimize the HW implementation and verification effort.

This chapter gives the introduction for the thesis, including the motivation, research questions and methods, and the summary of publications with author's main scientific contribution in them.

#### 1.1 The motivation and objectives of the research

The main motivation for this thesis is to evaluate whether HLS is a feasible implementation approach for computation-intensive multimedia processing. In practise, the analysis is carried out by implementing HLS solutions for HEVC encoding and evaluating their QoR, performance, and development time on field-programmable gate array (FPGA). The motivation is also to see if HLS is suitable for implementing designs that require more accurate control structures. This would enable the use of HLS for the whole system, and not just for traditionally suitable data-intensive algorithms. HEVC [4], [5] video encoder is an ideal application for the following reasons:

- 1. HEVC has gained a lot of traction in academia, so the obtained results can be compared with many other scientific works;

- 2. it is a very complex application, which will minimize the effect of normal variance in results (difference between HLS tools, synthesis results, etc.);

- 3. the complexity of HEVC is still reasonable for the scope this thesis;

- 4. HEVC has several independent units (coding tools, entropy coding, control structures) making it possible to showcase potential productivity increase and comparable QoR with HLS for single units and the whole system;

- 5. it also has characteristics that can be considered both strengths and weaknesses of HLS, i.e., functionality that can be considered data-intensive or something that needs of an accurate control structure; and finally,

- 6. HEVC is suitable for FPGA implementation, in order to enable performance measurements outside of simulations.

HEVC is a widely deployed and researched topic in industry and academia. The complexity of the HEVC [6] is very high, but HLS holds promise for better design management over traditional design methods. HEVC adopts the conventional hybrid video coding scheme (intra/inter prediction, transform coding, and entropy coding) [5] from the prior MPEG/ITU-T video coding standards. It offers a great variety of functionality, ranging from data-intensive algorithms, like intra prediction and discrete sine/cosine transform, to more control-intensive tools, such as intra search control and context-adaptive binary

arithmetic coding (CABAC). The latest FPGAs are able to meet the capacity and performance need for HEVC intra encoding, so they can be used as a real-life proof-of-concept test platforms, in addition to simulation.

The objectives of the thesis are the following:

- 1. To implement single algorithms/coding tools of HEVC on FPGA, by using Catapult HLS tool [7];

- to integrate the implemented coding tools together and to add the associated control logic, to enable a fully-fledged real-time 4K HEVC intra encoder on FPGA; and

- to make the encoder easily customizable for different media applications, scalable for different performance requirements, and portable to different platforms, from embedded devices to cloud environments.

The results of all these objectives are compared with prior art in existing scientific publications.

The entire implementation process relies on the open-source HEVC encoder called Kvazaar [8]–[10], that is used as a design entry point and as the reference software (SW) encoder. Although the implementation needs additional work to be fully optimized for HW, the original source code can still be used as is for testing purposes. Utilizing the existing Kvazaar C-code and C/C++ for the HW implementations, removes the need for re-implementing the reference algorithm. The automatic generation of register transfer level (RTL)-code with an HLS tool also removes the need for manual writing of traditional HDL, like very high-speed integrated circuit hardware description language (VHDL) and Verilog. This way, the focus can be directed more on the behavioural code.

Even though this work focuses on the *All-Intra* (*AI*) [11] coding configuration of HEVC Main Profile, the proposed design approach can be applied to other HEVC profiles or video codecs as well.

#### 1.2 Research questions and methods

This thesis aims to answer the following research questions:

1. Is HLS feasible for the implementation of a complex multimedia application, like HEVC, that consists of multiple parallel units, and both control and data

intensive algorithms?

- 2. Do the developed HLS implementations for HEVC intra coding show comparable area and performance results with existing HW designs?

- 3. By combining and generalizing the first two questions, does HLS offer overall improvement over traditional design methodologies in terms of development time and QoR?

To answer these questions, the research in this thesis follows the principles of the design science methodology [12], [13] that has established well-known guidelines and evaluation methods for an iterative design process. The implementation of the whole encoding system is constructed of individual HEVC coding tools and control structures that are finally integrated together. The iterative design process for each coding tool starts from the reference algorithm, which is used for the first HW implementation and test bench. The design process then continues with *design space exploration* (*DSE*) and code restructuring, in order to optimize the area and performance of the HW design.

During the development, the individual units and the encoding system are iterated, improved, and compared with prior art according to the following criteria:

- 1. Area. The area figures reported for proposed implementations include the number of logic elements (LE), look-up table (LUT), adaptive look-up table (ALUT), or adaptive logic module (ALM) [14], the amount of on-chip memory, and the number of digital signal processing (DSP) units used for the specified FPGA. For fair comparison, effort has been made to unify the area figures with previous work, e.g., by using coefficients between the LEs according to the functionality of the used LE, or by re-generating the results for the same device using HLS and an appropriate synthesis tool.

- 2. Performance. The performance is measured for the developed individual coding tools by applying the worst-case scenario. For a complete encoder, several open-source 4K sequences [15] were used to obtain reliable and consistent results. Again, effort has been made to calculate or estimate missing values of the related work by extrapolating them from the published information.

- 3. Coding quality. For proposed individual coding tools where the implementation is one-to-one to Kvazaar [8]-[10], the need for such

measurements can be omitted. If the Kvazaar reference code had to be optimized in a way that it changed the original algorithm, this modification was also implemented in the HEVC reference encoder, HEVC Test Model (HM) [16], in order to report coding quality changes. Bjøntegaard delta bitrate (BD-rate) [17] can be used as direct value for comparing the coding quality between two codecs. It allows the measurement of bitrate reduction by a codec or a codec feature while maintaining the same quality as measured by objective metrics. In practise, the average peak signal-to-noise ratio (PSNR) is measured for the anchor and the one being evaluated using same four quantizers. BD-rate is then calculated for both curves [17]. Furthermore, HM, using AI configuration [18], is used as an anchor for the proposed full encoding system. The BD-rate gain, or loss, is reported for the test sequences from [15]. Coding quality is also considered when comparisons are made to related work.

4. Supported HEVC features. The supported features of individual coding tools and the supported encoding configuration of the full encoding system is always specified. The support or absence of features is listed for the related work. Supporting all features will always produce the best coding quality, but by removing some features, it can have a more positive affect on the area and performance when compared to the negative effect on coding quality.

This thesis contributes to the debate for the feasibility of HLS and the promise of overall improvement over traditional design methods by implementing a complete HEVC intra encoder on FPGA, using solely HLS. The individual publications included in this thesis illustrate the steps taken to achieve the goal and give a detailed description of how HLS was used to implement individual units and the final encoder.

#### 1.3 Summary of publications

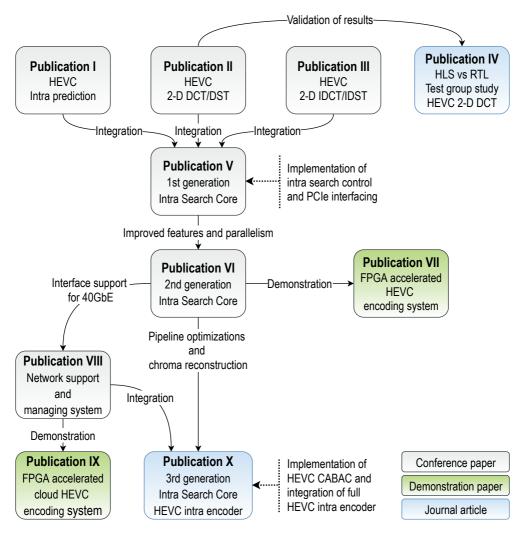

This section introduces all the publications included in this thesis. Figure 1.1 summarizes the main outcomes of these publications and the interconnections. The figure is drawn from the perspective of the developed HEVC encoder.

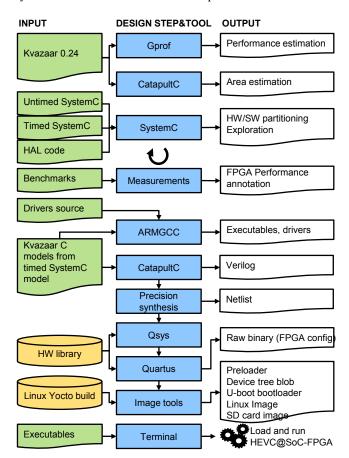

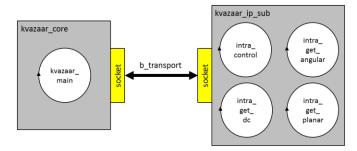

**Publication I** describe the developed HLS flow and how it can be used to develop HW- accelerated functions. The introduced HLS design flow is applied for

Figure 1.1 Summary and connection of publications.

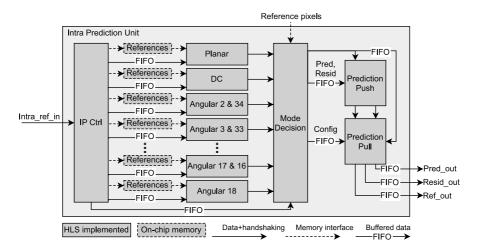

HEVC intra prediction to produce a HW implementation for FPGA. The publication also presents a complete design of a real-time HEVC intra encoder on system on chip (SoC)-FPGA, utilizing the implemented HW intra prediction for encoding acceleration.

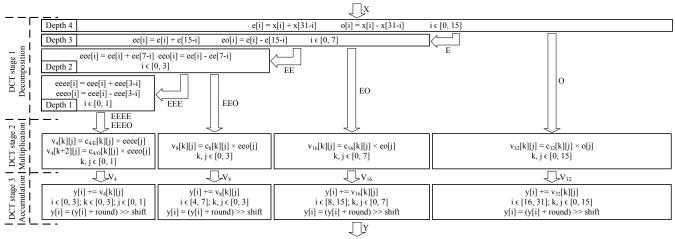

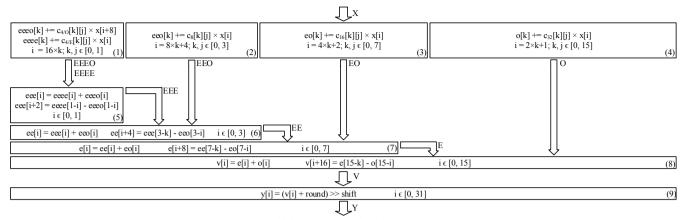

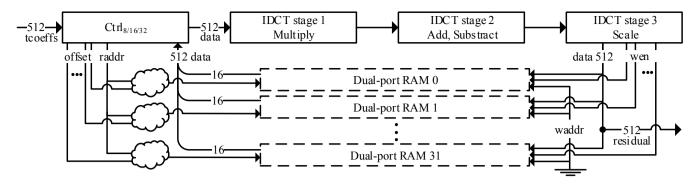

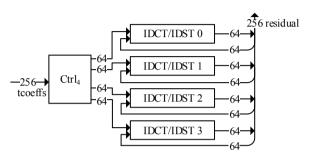

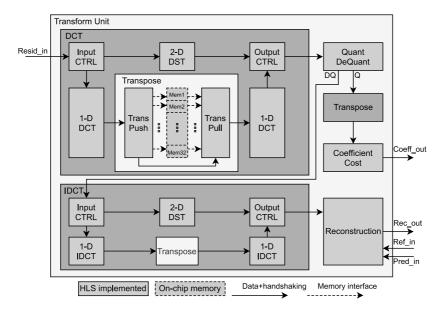

**Publication II** describes an HLS implementation of HEVC 2-D discrete cosine transform (DCT)/discrete sine transform (DST) on FPGA. The work reported in **Publication III** stems from that of Publication II, as it describes the inverse version of the same algorithm, 2-D inverse discrete cosine transform (IDCT)/inverse discrete sine transform (IDST). Both approaches implement the 2-D transforms by two

successive 1-D transforms using a well-known row-column and even-odd decomposition techniques. These two publications showed that the benefits of HLS do not come at the cost of implementation overhead, as the HLS solutions outperformed existing works in terms of performance and cost.

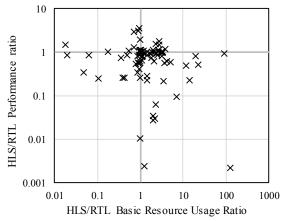

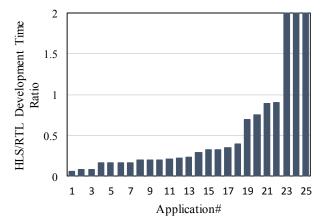

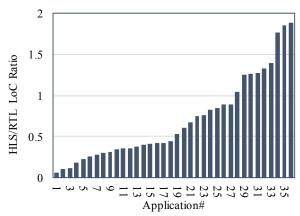

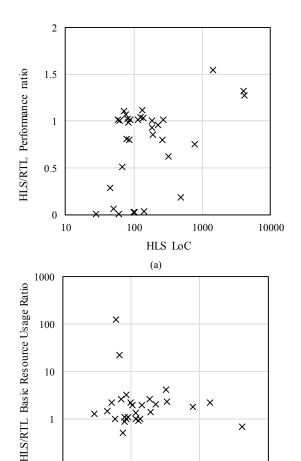

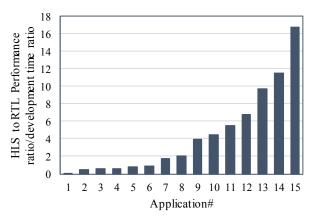

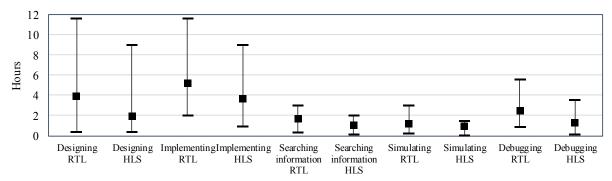

**Publication IV** is a survey of the state of HLS, based on the scientific literature published since 2010. The literature survey was conducted by Sakari Lahti. Sakari Lahti also wrote the majority of the text. The author contributed to this publication with the planning, organization, analysis, and text for the case study, in which a test group was given an assignment to implement HEVC 2-D DCT algorithm for  $8 \times 8$  residual blocks with both HLS and traditional HDLs.

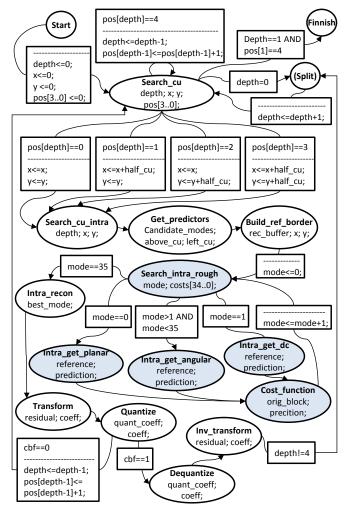

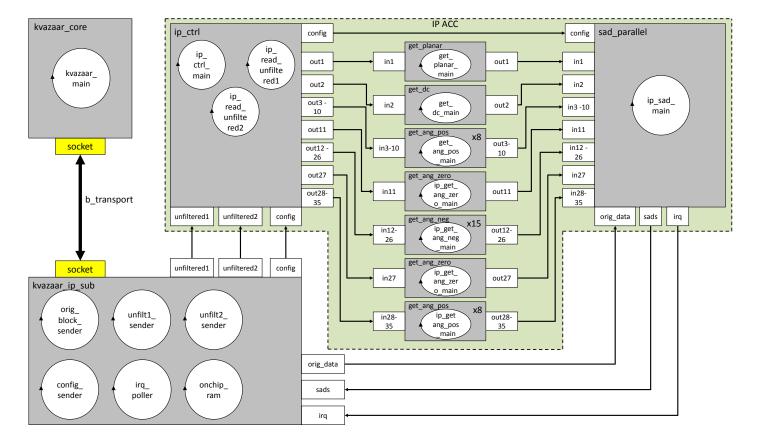

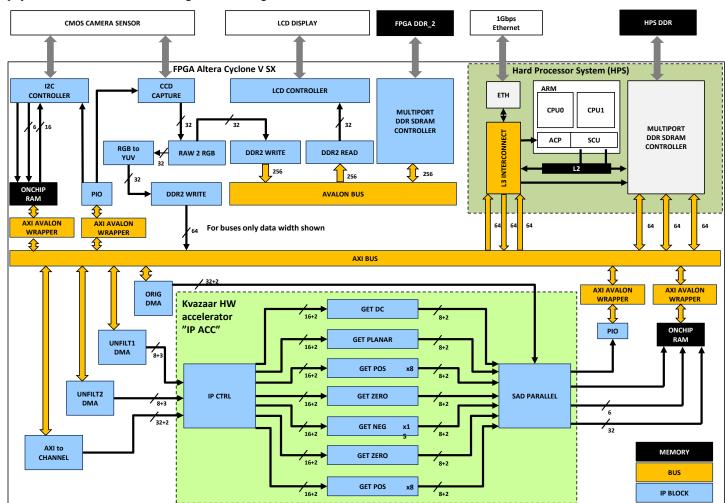

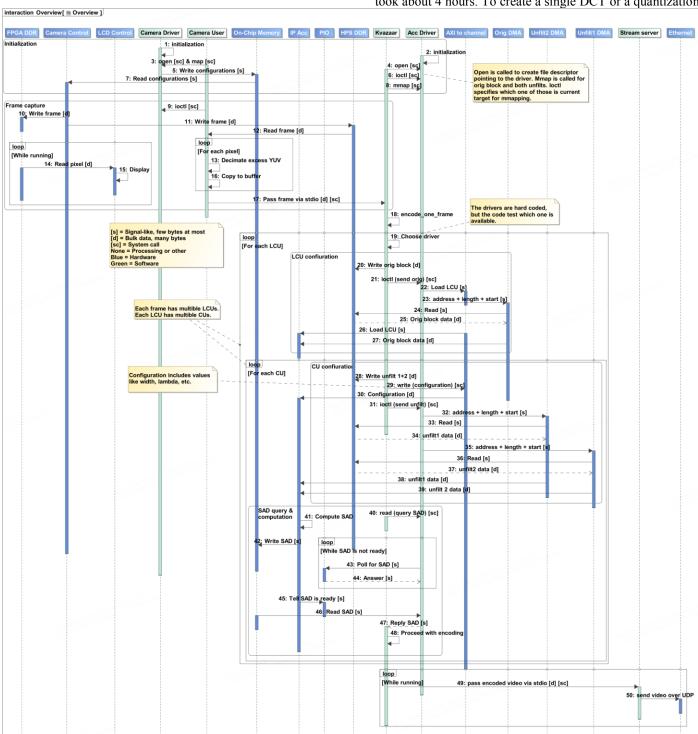

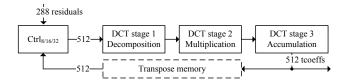

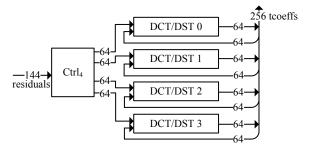

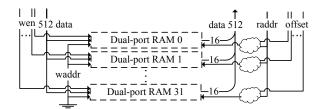

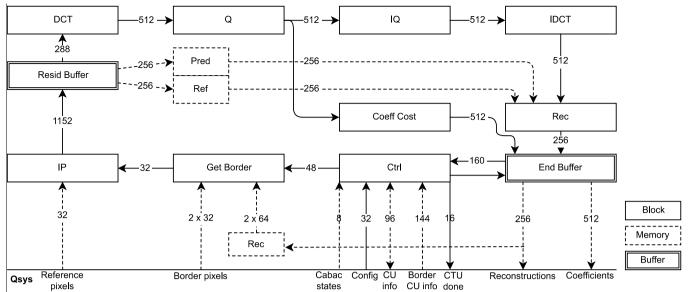

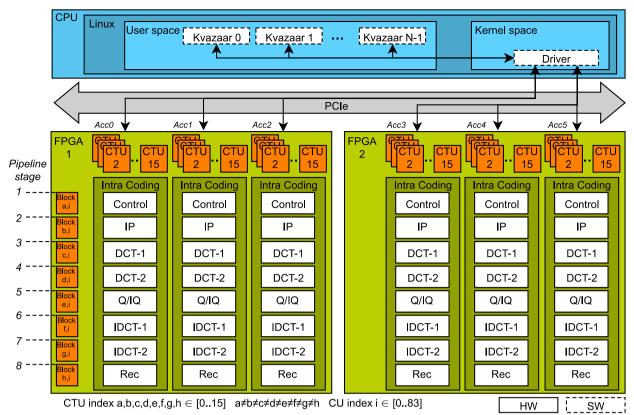

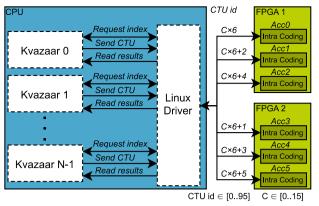

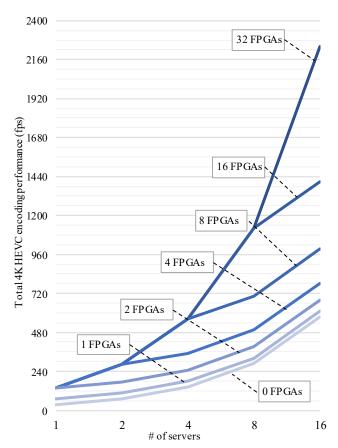

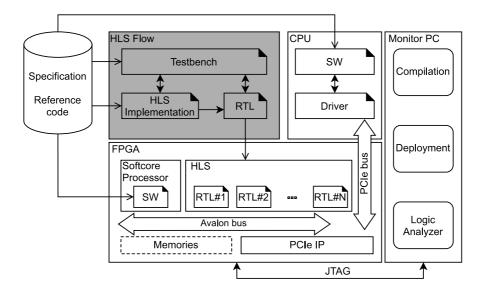

Publication V describes a 4K HEVC intra encoder partitioned between a processor and a peripheral component interconnect express (PCIe)—connected FPGA. It introduces the implementation and integration of the following data-intensive Kvazaar coding tools: intra prediction, DCT, IDCT, quantization, and inverse quantization. It also describes the HW implementation of the control-oriented intra search process using HLS. CABAC and other control-intensive coding tools are executed on SW. The publication also describes the implementation of the HW/SW partitioning scheme between a central processing unit (CPU) and an FPGA.

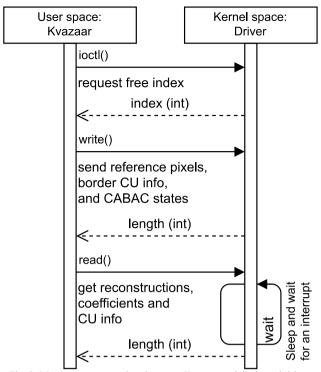

**Publication VI** describes the  $2^{\rm nd}$  version of the Intra Search Core that has been improved upon the  $1^{\rm st}$  version presented in Publication V. The proposed speedup techniques include optimizing the use of DSP-units, increasing the support of parallel *coding tree units* (CTU) on HW, and duplicating time-sensitive resources. Furthermore, the Linux kernel driver is upgraded to maximize the utilization of both HW and SW and to support multiple PCIe-FPGA cards.

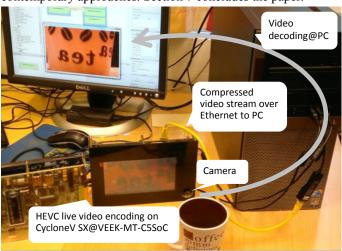

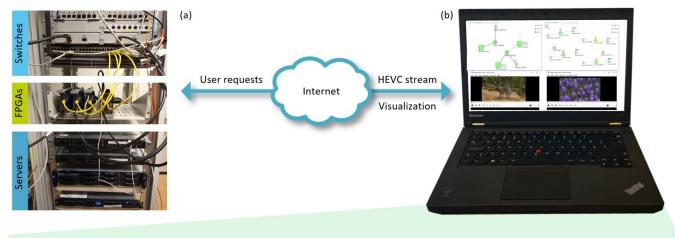

Publication VII is a demonstration publication. It showcases how the encoding system presented in Publication VI can be utilized for real-life purposes. The presented demonstration setup enables real-time HEVC encoding of three 4K cameras simultaneously. The cameras send the RAW video data through high-definition multimedia interface (HDMI) and the HDMI-capture cards transmit the data to the encoder via universal serial bus (USB). Finally, the encoded video is sent via Ethernet for live view on three laptops.

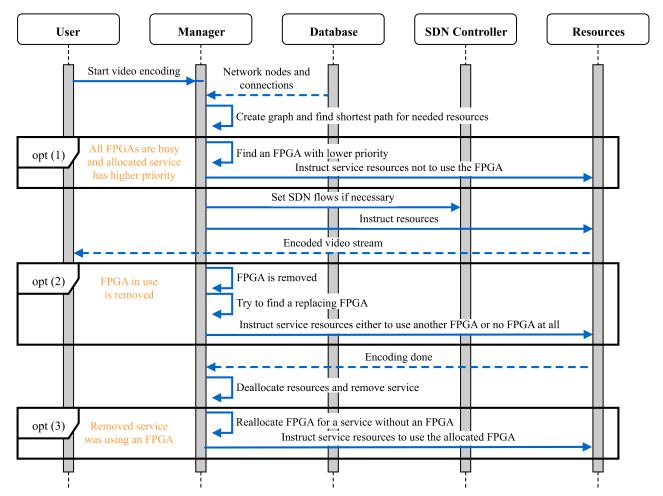

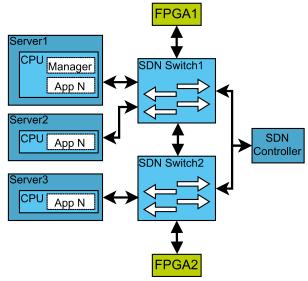

Publication VIII describes an approach to accelerate, distribute, and manage video encoding services in large-scale cloud systems. The Intra Search Core

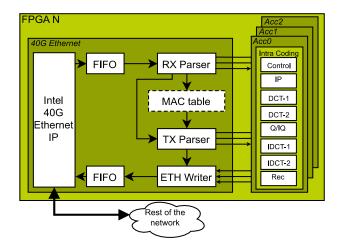

presented in Publication VI is used as a proof-of-concept application. In the case of cloud encoding, the usage of PCIe-FPGAs from the previous publications would have limited the flexibility of the encoding system, as the FPGAs are bound to servers and only 1-2 boards could be attached per cloud server. The given solution is an advanced partitioning scheme for sharing execution between servers, FPGAs, and software defined networking (SDN) switches. This combination allows the deployment of practically any number of heterogeneous FPGAs and servers. The implemented resource manager, which controls the SDN switches, is responsible for allocation, deallocation, and load balancing of software and hardware resources upon service requests, or changes in network infrastructure. The research also includes HLS implementations for the Ethernet packet parsing and generation, which was integrated to the HEVC accelerator logic presented in Publication VI.

Publication IX is another demonstration publication. It showcases how the system presented in Publication VIII works in practice. The demonstration setup includes a laptop that is connected to the cloud system. Through this connection, several encoding services can be invoked with requests to the resource manager. A run-time visualizer on the laptop illustrates in real-time the data provided by the resource manager, such as the physical network structure, running services, and performance of the network elements. The live encoded video stream can also be viewed on the laptop screen.

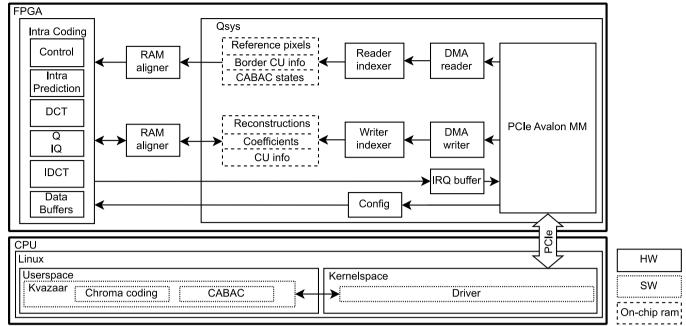

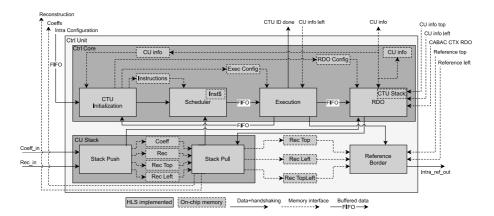

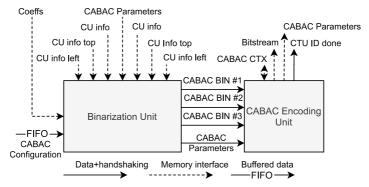

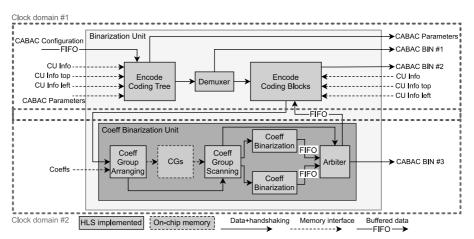

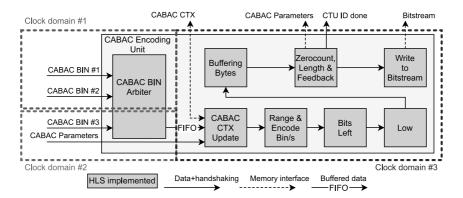

Finally, **Publication X** describes the HLS development framework improved upon Publication I, the 3<sup>rd</sup> version of Intra Search Core optimized from the version described in Publication VI, and the HLS implementation of the CABAC Core. The integration of intra search and CABAC cores is also presented, and the needed changes in the kernel driver. This finally creates a complete HEVC intra encoder on FPGA. This is the key publication of the thesis, and it shows that the HLS proposal not only boosts development time, but also provides previously unseen design scalability with competitive performance over the existing encoder implementations.

The author served as the  $1^{st}$  author in publications Publication I, Publication II, Publication IV, Publication V, Publication VIII, Publication IX, and Publication X, and as the  $2^{nd}$  author in Publication III, Publication VI, Publication VII. The author's contribution in each publication is listed in Table 1.2. The table also lists the work done in collaboration with co-authors.

| Pub. | Author's own work                                                                                                                                                                                                                                                                                                                                                | Work done in collaboration or by co-authors                                                                                                                                    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I    | <ul> <li>Presented HLS design flow</li> <li>HEVC intra prediction (IP) HW implementation with HLS</li> <li>Implementation of DMAs on FPGA</li> <li>Integration of the IP accelerator into the SoC CPU</li> <li>Linux kernel driver for interfacing the IP accelerator</li> <li>Supporting HW IP acceleration in Kvazaar</li> <li>Performance analysis</li> </ul> | HW components related to camera and display     FPGA – CPU interfacing related to camera and display                                                                           |

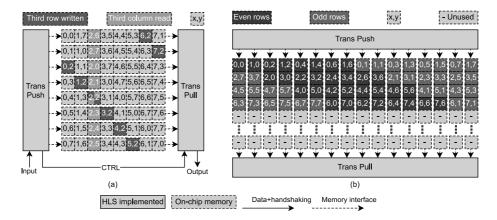

| II   | <ul> <li>Initial versions of 2-D DCT and 2-D DST</li> <li>Implementation of the low-cost 2-D DCT variant</li> <li>Implementation of the transpose memory</li> <li>Performance analysis</li> </ul>                                                                                                                                                                | <ul> <li>Implementation of the high-speed 2-D DCT variant</li> <li>Implementation of the 4×4 2-D DCT/DST variant</li> </ul>                                                    |

| Ш    | <ul> <li>Initial versions of 2-D IDCT and 2-D IDST</li> <li>Implementation of the transpose memory</li> <li>Performance analysis</li> </ul>                                                                                                                                                                                                                      | Implementation of the final 2-D IDCT/IDST unit                                                                                                                                 |

| IV   | <ul> <li>Planning, development, organization, analysis, and text for the test group study</li> <li>Idea and design of the CTU based</li> </ul>                                                                                                                                                                                                                   | <ul> <li>The conducted survey and the writing of rest of the publication was done fully by the co-author Sakari Lahti</li> <li>Design of the CTU based intra coding</li> </ul> |

| V    | intra coding accelerator  • FPGA – CPU interfacing using PCle  • Implementation of DMAs on FPGA  • CTU-based memory indexing on FPGA  • Linux kernel driver for interfacing the Intra Search Core on the PCle FPGA from a server CPU  • Supporting HW intra coding acceleration in Kvazaar  • Performance analysis                                               | accelerator • Implementation of Intra Coding Control, Get Reference, Border, Coefficient Cost, and Reconstruction for the Intra Search Core                                    |

| VI   | <ul> <li>Linux kernel driver support for multiple PCle FPGAs</li> <li>Improved CTU load balancing</li> <li>Interrupt support on FPGA and Linux kernel driver for signalling the finished coding of a CTU</li> </ul>                                                                                                                                              | Optimization of HW units in the Intra Search Core                                                                                                                              |

| VIII | Setup and demonstration     Implementation of the Resource Manager application     HLS implementations of Ethernet packet parsing and generation on FPGA     FPGA – CPU interfacing using Ethernet     Supporting cloud HW intra coding acceleration in Kvazaar                                                                                                  | <ul> <li>Initial idea of using FPGAs together with SDN</li> <li>Initial network – FPGA tests</li> <li>Orchestration of the prototype cloud system</li> </ul>                   |

| IX   | <ul> <li>Gathering data in the Resource Manager application<br/>and providing it to the run-time visualizer</li> <li>Setup and demonstration</li> </ul>                                                                                                                                                                                                          | Implementation of the run-time visualizer                                                                                                                                      |

| X    | Improved HLS development framework from Pub. I     Optimized version of Intra Search Core from Pub. V     Full HW implementation of the CABAC Core using HLS     Integration of CABAC Core into Intra Search Core     Support for HW CABAC in the Linux kernel driver and Kvazaar     Performance analysis                                                       |                                                                                                                                                                                |

Figure 1.2 Author's main scientific contributions.

#### 1.4 Outline of the thesis

The introductory part of this thesis is organized as follows. Chapter 2 describes the background of the thesis. It introduces the HLS design flow, the basics of HEVC encoding, and the basic concept of an FPGA. Chapter 3 considers the related work that is limited to HW HEVC approaches in academia. The related work consists of HLS implementations for single HEVC coding tools, as well as dedicated CABAC and entire encoder implementations done with handwritten HDLs. Chapter 4 summarizes the main results of the publications and gives the rationale for design choices and implementation process. Finally, Chapter 5 concludes the thesis.

#### 1.5 Acknowledgments

This work is supported in part by Nokia, the European Celtic-Plus projects 4KREPROSYS and VIRTUOSE, the European ECSEL project ADACORSA (under the grant agreement 876019), the Tuula and Yrjö Neuvo Fund, Nokia Foundation, and the Finnish Foundation for Technology Promotion.

#### 2 BACKGROUND

This chapter introduces the automated design process, HLS design flow, and their advantages over traditional design methods. Secondly, the basics of HEVC encoding are presented with common terminology used in the introductory part and publications. Finally, the use of FPGA as the target technology is rationalized and the basic concept of an FPGA is explained.

#### 2.1 Automated design process: High-level synthesis (HLS)

HLS is an automated design process, where an HLS tool is used to automatically generate the RTL HDL-code from a high-level program code. The higher abstraction level offers technology-independent implementations, as the HLS tool can be used to configure and optimize the design for different target technologies, e.g., *application-specific integrated circuits* (ASIC) or FPGAs, without the need to rewrite the code. The RTL-code generation is based on the behavioural code and constraints specified by an HLS tool. Furthermore, to minimize the verification effort, HLS tools can be used to verify both the high-level code and the generated RTL-code with a shared high-level testbench.

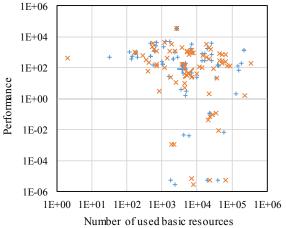

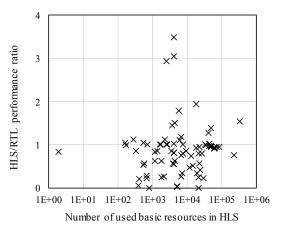

There are numerous commercial and academic HLS tools [19] that support the HLS design flow. According to the survey done in Publication IV, the most popular HLS tool in academia was the Xilinx Vitis HLS [20] (previously Vivado HLS/Autopilot). However, the range of different HLS tools used in the scientific literature is wide, which argues that no single HLS tool is the best choice for every situation.

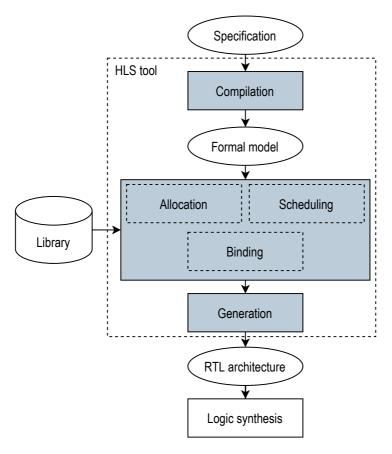

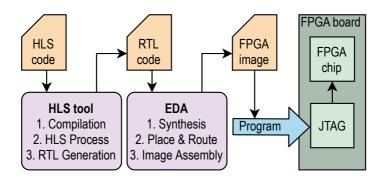

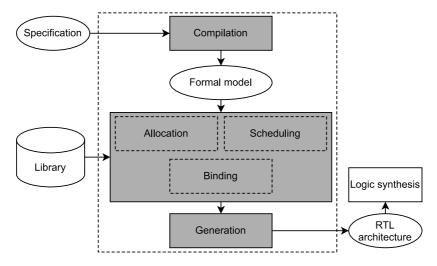

#### 2.1.1 HLS flow

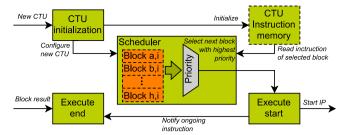

Figure 2.1 depicts the conceptual block diagram of the HLS design flow. The HLS tool is used for compiling the algorithmic specification of the system, most often

Figure 2.1 HLS design flow [Publication X].

written in C, C++, or SystemC. The user can specify the target technology and provide micro-architectural constraints, such as directives for loop pipelining/unrolling, desired clock frequency, number of clocks, clock-crossing, the usage and depth of *first in*, *first out* (*FIFO*) memory components, and mapping of arrays to registers or memories. The HLS tool then automatically allocates the HW resources required by the specification, creates state machines, schedules the operations, and binds the operations to physical resources specified in the target technology library. The clock(s) and reset(s) in the generated RTL code are completely inserted by the HLS tool, according to the architectural constraints. The generated RTL HDL-code can then be used in the downstream logic synthesis SW, for both FPGA and ASIC designs.

#### 2.1.2 Advantages of HLS over traditional hardware design methods

The main strength of HLS comes from the productivity increase, when compared to traditional HW design methods. This is achieved by increasing design abstraction from RTL to behavioural level [2], [3], [21]. HLS has been reported to provide 4-6 times increase in productivity [Publication IV], mainly because the behavioral code is more readable, design and verification times are shorter, and the design reusability is far better than that of handwritten HDL.

In particular, HLS offers advantages over manual RTL coding in the following cases:

- 1. Data-intensive designs. HLS has traditionally worked well with data-intensive designs, whereas implementing clock accurate control structures has been more challenging due to the lack of explicit time information in behavioural source code [3], [21]. However, a recent work [22] has showed that even more demanding control structures could be described with the latest HLS tools.

- 2. Algorithm and system architecture optimizations outperform micro-architectural optimizations. Adopting HLS and high-level coding techniques allows the designer to shift focus from fine-tuning single algorithms to the whole system architecture, which tends to provide higher performance gains than optimizing micro-architectures.

- 3. DSE. Although the system architecture optimizations can also be considered as part of DSE, HLS tools also enable DSE for single units in the form of architectural constraints. These can be applied via configuration scripts or by embedded pragmas, like loop unrolling/pipelining options, in the code. The process of finding the optimal trade-off between performance and area is significantly faster with HLS than with hand-written RTL. In practice, a comprehensive DSE cannot be conducted with conventional HDL approaches, as each solution would require extensive rewriting of the code.

- 4. Reduced verification effort. Reducing the verification effort is an important aspect of any design. Especially for digital system projects, it has become one of the most time-consuming phase [23]. The verification process can be significantly faster with HLS than verifying manually written RTL, as the functional correctness of the high-level code and the automatically generated

RTL code can be done using the same high-level testbench. The output of the generated RTL can also be validated automatically against the behavioural code. Most often, only the algorithm level verification is needed. In addition, some corner cases, e.g., type casting or vector overflows, may require additional effort. The testbench also synchronizes with the input and output of the design under verification, which makes it tolerant of architectural changes and removes the need for any code rewriting during the DSE.

- 5. Technology independency. HLS can offer better design reusability over traditional design approaches. A technology-independent behavioral code releases the designers from addressing the implementation details of the target technology, such as timing, interfaces, and memory elements. In principle, the same holds for the handwritten RTL code, but the design is usually implemented with a specific technology and performance in mind. In practise, when a new platform is selected with an HLS tool, a platform-optimized RTL code is generated using the same existing source code. In contrast, with manual RTL, time-consuming code restructuring is typically needed because of new clock constraints or additional resource sharing, caused by limited capacity of the new platform. Full technology independency might not be achieved with every HLS tool, as different HLS tools support a different range of target technologies.

- 6. Increased productivity. All previous advantages of HLS add to the compelling productivity increase over traditional RTL design flows. Even though custom RTL approaches tend to achieve better performance with less resources, the literature survey in Publication IV indicates that the average development time of an HLS project is only a third of that of the manual HDL project. The average productivity of HLS is also reported to be more than 4× as high in terms of the system performance with respect to the development time.

#### 2.1.3 Catapult HLS tool

In this work, Catapult HLS [7] from Siemens (previously owned by Calypto and Mentor) was used for its availability at the university where the research was carried out. In addition, Catapult HLS was preferred over another available tool, Xilinx Vitis, because Catapult HLS supports Intel FPGAs that were found

appropriate for this work. Several versions of the Catapult HLS tool were used during the research and the version was updated upon availability of newer version. Before the version 10.3 was released, the university only had access to a university license (some limitations in features), after that a full license was available.

Catapult HLS provides a wide support for the features described in Section 2.1.2. These features include:

- language support for C/C++/SystemC;

- support for both algorithmic and control logic synthesis;

- configuration scripts and embedded pragmas for architectural constraints;

- support for a unified testbench for the verification of both algorithmic code and RTL, with automated verification of the generated RTL against the algorithmic code;

- variety of target technologies ranging from ASIC technologies to different FPGA vendors, including automated synthesis tool integration;

- possibility to have multiple clock domains in a hierarchical designs and automatically generated clock crossing components;

- initial area and performance results without actual RTL synthesis; and

- a cycle accurate Gantt Chart of the scheduled operations for a visual representation of the generated RTL.

## 2.1.4 HLS design example

Listing 2.1 exemplifies the basic HLS coding features supported by the Catapult HLS tool. It shows how hierarchical designs, arrays, loops, pragmas, functions, channels, look-up-tables, type definitions, bit accurate types, macros, and compilation time calculated bit widths (*nbits*) can be used in HLS code. In this producer-consumer implementation, the *producer* (chef) is hierarchically connected to the *consumer* (tables) on the top-level function *restaurant*. These functions are marked with pragmas *hls\_design* and *hls\_design top*. The top-level interface consists of two parameters, orders and income. Both of these are defined as algorithmic C (*ac*), datatypes, and more specifically channels. In Catapult, the channels can be used to implement data transfers without, or with one or two handshake signals, buffered input/output for a more pipelined behaviour, FIFOs with automatic or

manually adjusted depth, and even clock crossing support between hierarchical blocks. Bit accurate types (ac\_int) are also used and defined with type definitions.

The implementation of the *producer* has three separate parts. First, a *Tables* structure is read from the channel *orders*. The helper structure is necessary for reading an array of data with one call. Secondly, a separate function called *calculate\_number\_of\_orders()* is used for calculating the number of non-zero orders in a loop that is fully unrolled with pragma *hlr\_unroll*. Thirdly, the chef starts preparing the food in a loop for each table that has a non-zero *recipe* and writes the correct price from a look-up-table *price\_of\_food* to the correct index in the array of channels. This array will result in separate data paths for each index in the generated RTL. The for loop is pipelined with pragma *hls\_pipeline\_init\_interval 1*, stating that a new iteration of the loop is started after one cycle. The possible interval depends on the implementation and data dependencies. The implementation of the for loop also shows how a *break* statement is used for an optimized loop control, as a known number of loops is always better than an unknown one. Breaking the loop when remaining iterations have no effect improves the responsiveness. It also shows the usage of *continue*.

The implementation of the *consumer* has to parts. First part is the loop, which is fully unrolled. All tables that get food, eat and pay for it. As the *food* parameter of the function is an array of channels and all indexes need to be iterated, the loop utilizes *size()* function of the channel to implement non-blocking reading. The other alternative would be using *nb\_read()*, but size() is used here for a more optimized implementation. If the table is getting food (*size()* is not zero), the price for the food is read from the channel and stored to *cash*. The *cash* is incremented to the *cash\_register* as zero or the read value. This loop shows the importance of data dependency in a fully unrolled loop, as incrementing *cash\_register* inside the if statement would have resulted in a lower maximum frequency due to the dependency to *cash\_register* between iterations. After the loop the *cash\_register* is given to the owner.

On top of the code, the compilation can be affected with a set of directives (Tcl script), that can be modified directly in the directives file or via GUI. These directives affect the outcome, i.e., area, latency, and slack. Pragmas are also interpreted from the HLS code automatically as directives. Other important directives include design goal latency/area, clocks, clock overhead, resource binding (channels, wires, memories, registers), FIFO depths, and DSP extraction options.

```

#include "ac int.h"

#include "ac channel.h"

// Macro for amount of tables in the restaurant

#define TABLES 16

// Typedefs for bit accurate types

8

typedef ac int<1, false> uint 1;

typedef ac_int<2, false> uint_2;

typedef ac_int<4, false> uint_4;

// Just enough bits (nbits<>) for iterating tables

typedef ac int<ac::nbits<TABLES>::val, false> loop t;

// Just enough bits (nbits<>) for maximum amount of money

typedef ac_int<ac::nbits<3 * TABLES>::val, false> money_t;

struct Tables{ // Helper struct for an array of orders

uint 2 order[TABLES];

18

3:

static uint 2 price of food[4] = \{0,1,2,3\}; // Look-up-table for prices

static loop t calculate number of orders (Tables &cook) { // Inlined function

loop_t num_of_orders = 0;

#pragma hls_unroll // Calculate number of orders

for(loop_t \bar{i} = 0; i < TABLES; i++) {

num of orders += cook.order[i] != 0 ? 1 : 0; // Increment if order is non zero

return num of orders;

29

#pragma hls_design // Pragma for hierarchical design

void producer(ac_channel<Tables> &orders, ac_channel<uint_2> food[TABLES]) {

Tables cook = orders.read();

loop t num of orders = calculate number of orders(cook);

// The chef can pipeline the making of food and start next iterations every cycle

#pragma hls_pipeline_init_interval 1

for(loop_t i = 0; i < TABLES; i++) {</pre>

uint 2 recipe = cook.order[i];

40

if (recipe == 0) continue; // No order? Continue to next table

food[i].write(price_of_food[recipe]); // Send food with price

41

42

if(num of orders-1 == 0) break;

43

num of orders--;

44

4.5

1

1

47

#pragma hls design // Pragma for hierarchical design

49

void consumer(ac_channel<uint_2> food[16], ac_channel<money_t> &owner) {

money_t cash_register = 0; // No money yet

#pragma hls_unroll // One waiter per table, everyone eats/pays at the same time

for(loop_t \bar{i} = 0; i < TABLES; i++) {

uint 1 available = food[i].size(); // Check if food is serverd to table

uint^{-}2 cash = 0;

if(food[i].size()) cash = food[i].read(); // Get the cash from the table

cash_register += cash;

58

owner.write(cash register); // Deposit all money

-}

#pragma hls design top // Pragma for top level

void restaurant(ac channel<Tables> &orders, ac channel<money t> &income) {

static ac_channel<uint_2> waiter[TABLES]; // Waiters serve food from chef to tables

producer(orders, waiter); // Producer, chef

consumer(waiter, income); // Consumer, customer at the table

```

Listing 2.1 HLS example

# 2.2 Application of Interest: High Efficiency Video Coding (HEVC)

Due to the increased usage of numerous modern media applications, i.e., Internet video, video-streamed gaming, and video conferencing, video traffic has been estimated to account for 82% of all global *internet protocol* (*IP*) traffic by 2022 [24]. HEVC [4], [5] is the latest widespread MPEG/ITU-T video coding standard. It doubles the coding efficiency over its predecessor AVC [25] standard for the same subjective visual quality, but typically at the cost of considerable computational complexity overhead in the reference encoder HM [6] and practical encoders.

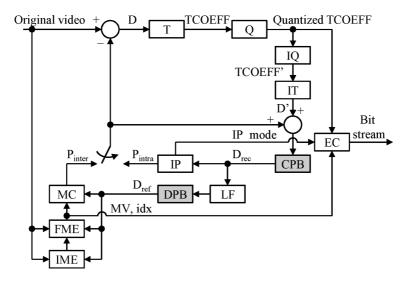

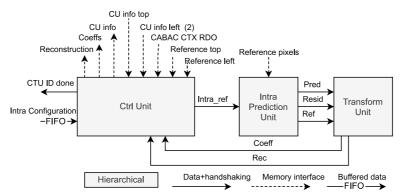

HEVC adopts the conventional hybrid video coding scheme [5] from the prior MPEG/ITU-T video coding standards. The encoding model of HEVC is shown in Figure 2.2. It can be divided into intra/inter prediction, transform coding, and entropy coding. They are covered in the following sections. Although the focus of this thesis is in HEVC intra encoding [11], inter encoding is also briefly covered.

### 2.2.1 Block partitioning structure

The coding structure of HEVC has been extended from the traditional macroblock structure. It is an analogous block partitioning scheme with four different logical units: CTU, coding unit (CU), prediction unit (PU), and transform unit (TU). For 4:2:0 color format, each of these consists of one luma and two chroma blocks that cover the corresponding block areas: coding tree block (CTB), coding block (CB), prediction block (PB), and transform block (TB). This new HEVC coding structure is the primary factor for the improved coding gain over AVC. As a downside, it also introduces majority of the computational overhead for both intra and inter encoding.

In HEVC, each raw input video frame is partitioned into CTU [26] quadtree structures. The size of the CTU can be defined as  $2N_{MAX} \times 2N_{MAX}$ , where  $N_{MAX} \in \{8, 16, 32\}$ . The CTU can be recursively split into four smaller square CUs until the min CU size of  $8\times 8$  is reached. The size of the CU can be defined as  $2N\times 2N$ , where  $N \in \{4, 8, 16, 32\}$ . Each CU in the CTU is predicted and transformed individually.

## 2.2.2 Intra prediction

Intra prediction utilizes spatial redundancy in compression. HEVC intra prediction supports CBs from  $32 \times 32$  pixels down to  $8 \times 8$  pixels. In intra prediction, the PBs

Figure 2.2 HEVC encoder model [6].

can be of the same size as the processed CB. In addition, HEVC supports partitioning the CB into four equal sized PBs when the CB size equals the smallest allowed CB size.

The *intra prediction* (*IP*) algorithm utilizes predefined prediction methods [5] to estimate the current CU. HEVC supports 35 different IP modes (DC, planar, and 33 angular modes) for each PB size. The *intra prediction* ( $P_{intra}$ ) refers to the *reconstructed picture* ( $D_{rec}$ ) from the *current picture buffer* (*CPB*), which is a storage for the previously reconstructed CBs. In intra mode, the *residual* (D) is calculated by subtracting  $P_{intra}$  from the original CB.

### 2.2.3 Inter prediction

Inter prediction utilizes temporal redundancy between different video frames. HEVC inter prediction supports CBs of 64 × 64 pixels down to 8 × 8 pixels. In addition to PBs of the same size as the processed CB, HEVC supports horizontal and vertical partitioning of CBs into two equal size PBs, or into four equal sized PBs when the CB size equals the smallest allowed CB size. Furthermore, by utilizing asymmetric motion partitions (AMP), HEVC supports partitioning of CBs into two asymmetric PBs [4], [5].

Inter prediction consists of motion compensation (MC), integer motion estimation (IME), and fractional motion estimation (FME). MC produces inter

predictions ( $P_{inter}$ ) for PBs based on the result of motion estimation (ME) (IME, FME). First, IME is used to search the best candidate for the PB of interest from the decoded picture buffer (DPB), which is a storage for previously reconstructed reference pictures ( $D_{ref}$ ). The motion vector (MV) and reference picture index (idx) produced by the IME is then forwarded to FME, which uses an 8-tap/4-tap separable interpolation (IPOL) filter to produce 1/4-pixel luma samples and 1/8-pixel chroma samples. The initial MV generated by the IME can then be refined to a sub-pixel accuracy.

When the encoder operates in inter mode, the  $P_{inter}$  produced by the MC is used to compute the D, by subtracting  $P_{inter}$  from the original CB. If the CU is encoded as skip mode, no D is computed, only PBs of size  $2N \times 2N$  are allowed, and motion parameters are derived with merge mode [5]. The merge mode is used to derive the motion parameters, including MV and one or two *reference picture indices* (idx), from spatially or temporally neighboring blocks.

### 2.2.4 Transform coding

In HEVC, the *transform* (T) stage utilizes 2-D DCT (TB sizes from 32 × 32 to 8 × 8) and 2-D DST (4 × 4 TBs) to transform D from spatial domain into frequency domain *transform coefficients* (TCOEFF) [27]. The transform coding supports CB sizes of 32 × 32 to 8 × 8 and further partitioning of square CBs into square sized TBs until the size of 4 × 4 is reached. In frequency domain, high-frequency components of the video can be removed in the *quantization* (Q) stage to produce *quantized transform coefficients* (QTCOEFF) without significant quality loss, since human eye is less sensitive to the high-frequency components.

The encoding loop also includes decoder-side functionality such as *inverse* quantization (IQ) and inverse transform (IT) stages, where QTCOEFFs are dequantized into inversed transform coefficients (TCOEFF) and then transformed back into inversed residuals (D), i.e., back from frequency domain to spatial domain. The IT stage uses the corresponding inverse functions of the T stage, i.e., 2-D IDCT and 2-D IDST [27]. The reconstructed D is then added to the  $P_{intra}/P_{inter}$  to generate the final D', which is stored in CPB. For example, in intra mode, reconstructed CBs are needed in the intra prediction phase, where spatially adjacent pixels are used as a reference for generating predictions for neighbouring CBs. Furthermore, as the reconstructed pictures correspond to the images

generated and displayed by the decoder, they can also be used to measure the error introduced by compression.

In addition, HEVC supports sequential in-loop filters, sample-adaptive offset (SAO) and deblocking filter (DF), in the loop filtering (LF) stage. This stage is used for filtering distortions and visible borders of blocks. Unlike intra mode, which utilizes the  $D_{rec}$  directly, inter mode utilizes the filtered  $D_{rec}$  from DPB to find the best temporal candidate for the processed PU and to generate the interprediction.

### 2.2.5 Entropy coding

In the last encoding phase, the QTCOEFFs, IP mode, and MV are processed by the *entropy coding* (EC) stage to generate the final encoded bitstream. In this step, the video signal is reduced to a series of syntax elements that contain properties of the blocks, including prediction modes, quantization parameters, transform coefficients, filter modes, and all other parameters required to describe how the video signal should be reconstructed by the decoder.

These elements are ordered and compressed to generate an encoded video bitstream. Entropy coding method in HEVC is called CABAC [28], which is a lossless compression technique based on arithmetic coding. The compression is achieved by utilizing statistical properties of symbols, i.e., more frequent symbols are coded with less bits and less frequent symbols with more bits.

### 2.2.6 Techniques for HEVC encoder parallelization

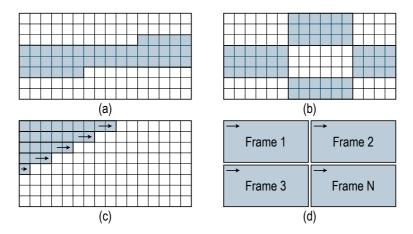

HEVC supports parallel processing of multiple CTUs [29] in a single frame, as well as parallelism between frames. As shown in Figure 2.3, the specified strategies include (a) slices, (b) tiles [30], (c) wavefront parallel processing (WPP) [30], [31], and (d) overlapped wavefront (OWF) [30], [32].

In its simplest, a slice in HEVC can contain the whole frame. For added parallelism, a single frame can be encoded using several independent slices. The minimum size of a slice is a single CTU. Each slice can consist of varying number of CTUs per frame, and each frame can consist of varying number of slices.

With tiles, the frame can be divided into independently encoded rectangular regions. This increases the capability of parallel processing of CTUs in a single

**Figure 2.3** Parallelization approaches supported by HEVC: (a) slices, (b) tiles, (c) wavefront parallel processing, and (d) overlapped wavefront.

frame without the need for complex synchronizations.

When WPP is enabled, processing of adjacent CTU rows can always be started when two CTUs from the preceding row have been encoded. Thus, the level of parallelism with WPP increases row by row. Furthermore, WPP may provide higher coding performance than tiles by utilizing CABAC better, i.e., the CABAC state of the previous row is always propagated to the next row with a delay of two CTUs. This dependency does require better synchronization methods than with tiles.

OWF is the process of encoding multiple frames in parallel. This is straightforward in all-intra mode, as the frames have no temporal dependencies, but when using inter mode, additional synchronization is required for reference pictures.

## 2.2.7 Open-source implementations for HEVC encoding

The most notable open-source HEVC encoder is the HEVC reference software called HM [16]. The main purpose of HM is to implement and provide a reference for all coding tools in the standard. On the other hand, HM has not been optimized for speed, e.g., with multithreading, and thus it has a considerable computational complexity, which severely limits its practical usage outside research.

There are also two notable open-source HEVC encoder implementations addressing practical encoding, namely x265 [33] and Kvazaar [8]–[10]. Both of them are highly optimized and support HEVC specified parallelism to achieve

real-time SW encoding. The x265 encoder has primarily been written in C++, just like HM. The development of x265 is coordinated by MulticoreWare. Kvazaar encoder is presented in more detail in Section 2.2.8.

### 2.2.8 Kvazaar HEVC encoder

Kvazaar [8]–[10] is an academic open-source SW HEVC encoder developed by Ultra Video Group at Tampere University. The open development of the encoder was started in January 2014 and still continues actively. The encoder has completely been implemented from scratch using C with additional advanced vector extensions 2 (AVX2) optimizations. Kvazaar supports HEVC Main profile [18] with ten presets from ultrafast to placebo [10]. Kvazaar architecture offers multi-threaded coding scheme with rate-distortion optimized (RDO) mode decision and HEVC parallelization strategies to achieve high rate-distortion (RD) performance with reasonable coding time.

In almost all publications included in this thesis, Kvazaar is used as a reference software for HEVC, i.e., as a design entry point for HLS implementations, for testing purposes, and as the SW application running on CPU where applicable. The wide usage of Kvazaar in this thesis is not only because Kvazaar has been developed in the same research group as this thesis is being carried out, but also because Kvazaar is a fully-fledged open-source HEVC encoder, which is implemented completely in a hardware-friendly C-code, and has shown promising results when compared with HM [16] or x265 [33].

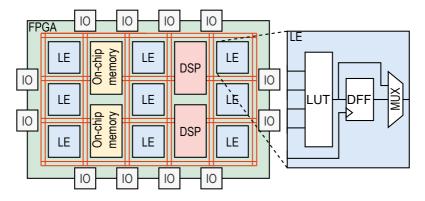

# 2.3 Target device: Field-programmable gate array (FPGA)

FPGAs are re-programmable logic circuits that enable fast development and real-time emulations for HW implementations. A simplified example of an FPGA is illustrated in Figure 2.4. In the basic case, an FPGA is made up of an array of programmable LEs, consisting of a classic 4-input LUT, carry logic, and a single register. The FPGA also has programmable interconnections for connecting the LEs. These interconnected LEs can be used to form designs from simple gates to highly complex functions. In reality, the basic building block [14] of an FPGA device depends highly on the FPGA vendor. These building blocks can consist of several classic LEs, larger LUTs, multiple registers, or additional hard-coded

Figure 2.4 Simplified example of an FPGA.

Figure 2.5 High-level overview of the design flow from HLS code to FPGA programming.

functionality such as adders. The FPGA chips also usually contain on-chip memory blocks and DSPs. The memory blocks are typically allocated for FIFOs and single or dual-port memories. DSPs are mostly used for performing complex mathematical functions. They can be used together with LEs and minimize the LE usage in memory-intensive or arithmetic applications.