# Modeling of an Interleaved DC-DC Boost Converter for a Direct Model Predictive Control Strategy

Thomas Effenberger<sup>\*</sup>, Hannes Börngen<sup>\*</sup>, Eyke Liegmann<sup>\*</sup>, Michael Hoerner<sup>\*†</sup>, Petros Karamanakos<sup>‡</sup>, and Ralph Kennel<sup>\*</sup> \*Chair of High-Power Converter Systems, Technical University of Munich Arcisstr. 21, 80333 Munich, Germany <sup>†</sup>Institute ELSYS, Technische Hochschule Nuremberg Kesslerplatz 12, 90489 Nuremberg, Germany <sup>‡</sup>Faculty of Information Technology and Communication Sciences, Tampere University FI-33101 Tampere, Finland

Email: eyke.liegmann@tum.de

## Keywords

«Interleaved converters», «Modelling», «MPC (Model-based Predictive Control)».

## Abstract

This paper presents a model predictive control (MPC) algorithm for interleaved dc-dc boost converters with coupled inductors. The prediction model covers the switching nature of the converter and all possible operating states. The MPC algorithm is realized in MATLAB and designed such to facilitate its real-time implementation on a field programmable gate array (FPGA) using the MATLAB HDL Coder. Open-loop measurement results demonstrate the accuracy of the system model, while the effectiveness of the controller is validated in simulation.

### Introduction

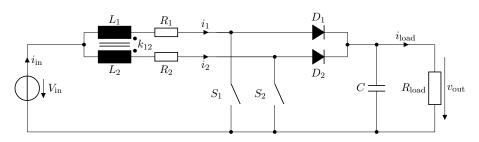

The interleaved dc-dc boost converter is a multi-branch converter topology consisting of multiple parallel boost stages, as depicted in Fig. 1. The branches share the input voltage, the output capacitance and in the case of coupled inductors—the magnetic core, resulting in a compact design. This enables the reduction of the input current ripple and an increase of the output current, as shown in [1], [2]. However, as there is no inherent mechanism to guarantee proper current sharing among the parallel paths a suitable controller is required to address this challenging issue.

Another challenge that a controller needs to deal with is that the output voltage of the boost converter has a non-minimum-phase behavior with respect to the control input, i.e., the switching action. To mask this,

Fig. 1: Interleaved dc-dc boost converter with coupled inductors.

the standard control approach is to design the controller as a current controller, average the continuoustime dynamics associated with the different modes of operation, and to linearize them at the operating point [3], [4]. This, however, complicates the controller design and can potentially deteriorate the dynamic performance.

Direct model predictive control (MPC) with reference tracking—also referred to as finite control set MPC (FCS-MPC)—is a control alternative that can effectively deal with the aforementioned challenges as it allows one to directly include constraints in the design phase and to account for the switching or hybrid nature of dc-dc converters [5]. According to this method, the control inputs are modeled as integers that directly relate to the switch positions of the converter, thus bypassing any modulation stage. Examples of FCS-MPC for dc-dc converters can be found in [6]–[9]. In [6] and [7], FCS-MPC for a dc-dc boost converter is proposed for the direct control of the inductor current and output voltage, respectively. In a similar direction, [8] focuses on FCS-MPC of a single-phase boost converter feeding a constant power load. Finally, an FCS-MPC strategy for an interleaved buck converter with four phases, but without magnetically coupled inductors is presented in [9].

These works clearly demonstrate the advantages of FCS-MPC, such as the great design flexibility and fast dynamic response. Nevertheless, direct manipulation of the converter switches also implies that the optimization problem underlying FCS-MPC is an integer program. A straightforward approach to solve such problems is to use exhaustive enumeration, i.e., to test all candidate solutions before concluding to the optimal one. As integer problems are typically computationally demanding, such a brute-force solution method may not be a realistic option when the number of candidate solutions is not small. To reduce the computational complexity of the associated optimization problem, some methods have been proposed that limit the feasible set [10] or propose nontrivial horizons [11]. Alas, they have been mostly tested on a simulation level [10], [12].

Moreover, considering that the computing time is limited to values smaller than  $10 \,\mu\text{s}$  to achieve a high sampling frequency, and thus enable a high switching granularity [13], a central processing unit (CPU) based control hardware would not be fast enough to test all options in real time within that time interval. A solution is to implement the algorithm on an FPGA, which not only allows for a computationally efficient implementation of the FCS-MPC algorithm, but also facilitates the utilization of a complex model for the interleaved boost converter that fully describes its dynamics.

The above motivates the design of a long-horizon FCS-MPC for the interleaved dc-dc boost converter with coupled inductors that will fully exploit the advantages of FCS-MPC, while facilitating its real-time implementation with a system model covering all physically feasible operating states. To this aim, a detailed model of the converter of interest is first derived that is suitable for all physically feasible operating states. Specifically, the discrete-time model of the converter is designed such that it accurately predicts the plant behavior when operating both in continuous (CCM) and discontinuous conduction mode (DCM). Subsequently, an FCS-MPC strategy is designed as a voltage-mode controller with the main control objectives of regulating the output voltage, balancing the phase leg utilization and limiting the phase currents. Such a control method offers design simplicity as it directly addresses the voltage control loops, while simultaneously meeting additional control objectives. The presented experimental results based on a low-voltage test bench demonstrate the validity of the proposed model, while simulation results highlight the advantages of the presented control strategy.

# System Model

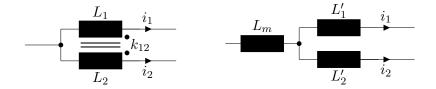

The interleaved boost converter with coupled inductors, shown in Fig. 1, is a dc-dc converter that boosts the input voltage to a higher output voltage. Each converter branch  $n \in \{1,2\}$  consists of a diode  $D_n$ and an active switch  $S_n$ . Each switch  $S_n$  can be controlled actively, whereas diode  $D_n$  conducts current depending on the applied voltage. In doing so, the current can be stored in the coupled inductors and, subsequently, deliver energy to the output, thus boosting its voltage value. These coupled inductors  $L_1$ and  $L_2$  and their mutual coupling  $k_{12}$  can be modeled by utilizing the equivalent Y-model with mutual

Fig. 2: Coupled inductors and equivalent Y-model.

inductance  $L_m$  and uncoupled inductances  $L'_1 = L'_2 = L'$ , as shown in Fig. 2. In doing so, the inductances can be mathematically described as follows

$$L_m = k_{12}\sqrt{L_1 L_2},$$

(1a)

$$L_1' = L_1 - L_m \,, \tag{1b}$$

$$L_2' = L_2 - L_m \,. \tag{1c}$$

The system model of the interleaved boost converter with coupled inductors differs from the system model of a standard boost converter in two major ways. Firstly, by interleaving, the system state should account for the branch currents, e.g., in the case of two branches, the state vector is chosen to be  $x = [i_1 \ i_2 \ v_{out}]^T$ , with  $v_{out}$  being the output voltage. Secondly, by coupling the inductors, a change of the inductor current  $i_1$  induces a voltage in the second winding, thus affecting branch current  $i_2$ , and vice versa.

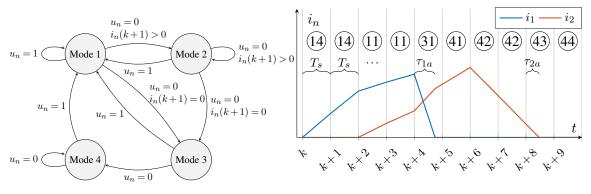

The switch positions of  $S_1$  and  $S_2$  are modeled by the binary variables  $u_1, u_2 \in \mathcal{U} = \{0, 1\}$ , respectively, together forming the input vector  $\boldsymbol{u} = [u_1 u_2]$ . In total, four distinct operating modes can be identified for each branch individually. The state machine in Fig. 3 visualizes the system states and the transitions for a single branch.

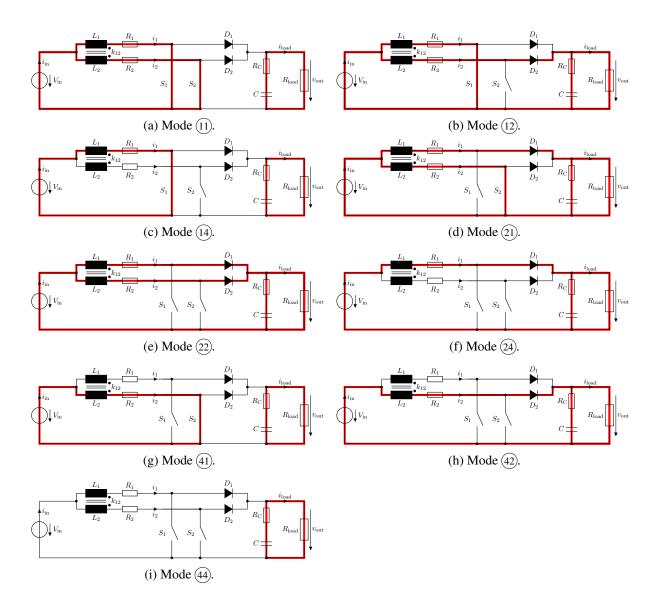

Within every discrete time interval  $T_s$  each converter branch is in one of the four modes, resulting in a total of 16 possible operating modes. In the following, the operating modes are denoted with a symbolic  $\langle w \rangle$ , where X and Y indicate the operating mode of the first and second converter branch, respectively. With switch  $S_n$  on, i.e.,  $u_n = 1$ , the respective branch operates in mode (1) with current  $i_n$  increasing and always being larger than 0. For all remaining modes it holds that  $u_n = 0$ . In mode (2) the corresponding current is decreasing, still being larger than zero, i.e.,  $i_n (k+1) > 0$ . Mode (3) is an intermediate state of modes (2) and (4), in which the branch current falls to 0 A, i.e.,  $i_n (k+1) = 0$ . Finally, in mode (4) the current remains 0. An illustrative example of combined modes for the two-branched system is shown in Fig. 4. In addition, all modes (except mode (3)) with the corresponding current paths (---) are depicted in detail in Fig. 5.

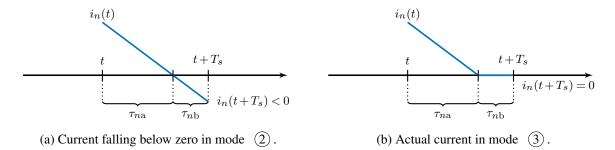

The system matrices for mode (3) are calculated by linearly averaging modes (2) and (4), weighted with

Fig. 3: State machine of branch n [7].

Fig. 4: Illustrative subset of modes of interleaved boost converter.

Fig. 5: Active current paths (----) of the interleaved boost converter in different operating modes.

Fig. 6: Current in mode (3).

(a) Submodes when  $i_1$  reaches 0 A first.

(b) Submodes when  $i_2$  reaches 0 A first.

Fig. 7: Submodes of mode (33).

the duration  $\tau_{na}$  given by

$$\tau_{na} = \frac{i_n(k)}{i_n(k) - i_n(k+1)} T_s.$$

(2)

This interval is the time in which the respective branch current is greater than 0 A, as shown in Fig. 6. Based on that,  $\tau_{nb}$  can be obtained as  $\tau_{nb} = T_s - \tau_{na}$ . This is calculated online, assuming operation in mode (2). If a zero-crossing of the branch current is detected, the operation mode is changed to mode (3).

To further clarify this point, consider as an example mode (3Y). For this mode it holds that

$$\boldsymbol{A}_{(3Y)} = \left(\boldsymbol{A}_{(4Y)} + \tau_{1a}/T_s \left(\boldsymbol{A}_{(2Y)} - \boldsymbol{A}_{(4Y)}\right)\right).$$

(3)

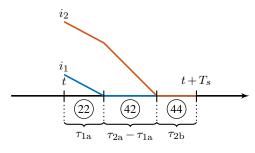

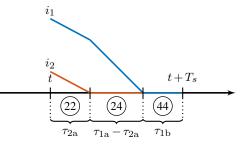

In mode (33), both currents fall to 0 A within the same interval. This leads to three distinct intervals within one sampling period, as illustrated in Fig. 7. It can be seen that there are two variants of mode (33), depending on which branch current falls to 0 A first. For example, for the case depicted in Fig. 7a, it holds that

$$\boldsymbol{A}_{(33)} = \frac{1}{T_s} \left( \tau_{1a} \boldsymbol{A}_{(2)} + (\tau_{2a} - \tau_{1a}) \boldsymbol{A}_{(42)} + \tau_{2b} \boldsymbol{A}_{(44)} \right).$$

(4)

Given all the above, the system model is derived as a bi-linear state space model of the form

$$\frac{\mathrm{d}\boldsymbol{x}}{\mathrm{d}t} = \boldsymbol{A}\left(\boldsymbol{x}, \boldsymbol{u}\right) \boldsymbol{x}(t) + \boldsymbol{B}\left(\boldsymbol{u}\right).$$

(5)

The state matrix A is given in (6). The individual entries, which depend on the switching state  $u_n$  and the branch current  $i_n$  are provided in Table I.

$$\boldsymbol{A} = \begin{bmatrix} A_{11} & A_{12} & A_{13} \\ A_{21} & A_{22} & A_{23} \\ A_{31} & A_{32} & A_{33} \end{bmatrix}$$

(6)

As for the entries of the input matrix  $\boldsymbol{B}$ , these are

$$\boldsymbol{B}_{(1)(22)(2)(2)} = \begin{bmatrix} \frac{L'}{D} \\ \frac{L'}{D} \\ 0 \end{bmatrix} V_{\text{in}}, \quad \boldsymbol{B}_{(14)(24)} = \begin{bmatrix} \frac{1}{L_m + L'_1} \\ 0 \\ 0 \end{bmatrix} V_{\text{in}}, \quad \boldsymbol{B}_{(42)(41)} = \begin{bmatrix} 0 \\ \frac{1}{L_m + L'_1} \\ 0 \end{bmatrix} V_{\text{in}}, \quad \boldsymbol{B}_{(44)} = \boldsymbol{0} \quad (7)$$

Finally, as the controller is designed in the discrete-time domain, in a subsequent step, the continuous-

| Mode | A <sub>11</sub>        | $A_{12}$          | $A_{13}$            | $A_{21}$          | $A_{22}$               | $A_{23}$            | $A_{31}$      | $A_{32}$      | $A_{33}$                      |

|------|------------------------|-------------------|---------------------|-------------------|------------------------|---------------------|---------------|---------------|-------------------------------|

| (11) | $-\frac{(L_m+L')R}{D}$ | $\frac{L_m R}{D}$ | 0                   | $\frac{L_m R}{D}$ | $-\frac{(L_m+L')R}{D}$ | 0                   | 0             | 0             | $-\frac{1}{CR_{\text{load}}}$ |

| (22) | :                      | ÷                 | $-\frac{L'}{D}$     | ÷                 | •                      | $-\frac{L'}{D}$     | $\frac{1}{C}$ | $\frac{1}{C}$ | ÷                             |

| (12) | :                      | ÷                 | $\frac{L_m}{D}$     | ÷                 | •                      | $-\frac{L_m+L'}{D}$ | 0             | $\frac{1}{C}$ | ÷                             |

| (21) | $-\frac{(L_m+L')R}{D}$ | $\frac{L_m R}{D}$ | $-\frac{L_m+L'}{D}$ | $\frac{L_m R}{D}$ | $-\frac{(L_m+L')R}{D}$ | $\frac{L_m}{D}$     | $\frac{1}{C}$ | 0             | ÷                             |

| (14) | $-\frac{R}{L_m+L'}$    | 0                 | 0                   | 0                 | 0                      | 0                   | 0             | 0             | ÷                             |

| (41) | 0                      | 0                 | 0                   | 0                 | $-\frac{R}{L_m+L'}$    | 0                   | 0             | 0             | ÷                             |

| (24) | $-\frac{R}{L_m+L'}$    | 0                 | $-\frac{1}{L_m+L'}$ | 0                 | 0                      | 0                   | $\frac{1}{C}$ | 0             | ÷                             |

| (42) | 0                      | 0                 | 0                   | 0                 | $-\frac{R}{L_m+L'}$    | $-\frac{1}{L_m+L'}$ | 0             | $\frac{1}{C}$ | ÷                             |

| (44) | 0                      | 0                 | 0                   | 0                 | 0                      | 0                   | 0             | 0             | $-\frac{1}{CR_{\text{load}}}$ |

Table I: Entries of matrix A depending on operating mode, with  $D = L'(2L_m + L') = (L' + L_m)^2 - L_m^2$ .

time system matrices are discretized using forward Euler method. This yields

$$\boldsymbol{x}(k+1) = (\boldsymbol{I} + \boldsymbol{A}T_s)\boldsymbol{x}(k) + \boldsymbol{B}T_s$$

(8)

with  $T_s$  being the sampling interval.

In the next section, the proposed converter model is verified experimentally.

### **Model Verification**

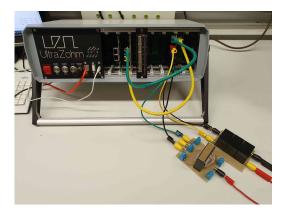

The proposed model is tested using the FPGA-based open-source control platform UltraZohm [14], [15], which is depicted in Fig. 8. The platform enables rapid control prototyping of power electronic systems. The calculation unit is a Xilinx Zynq UltraScale+ 9EG MPSoC that consists of several ARM processors and an FPGA on the same silicon chip. The platform is expandable with adapter cards that offer digital and analog interfaces to the converter and sensor. For FPGA hardware development Xilinx Vivado Design Suite is used. The software for the generated hardware processor is programmed with Xilinx Vitis.

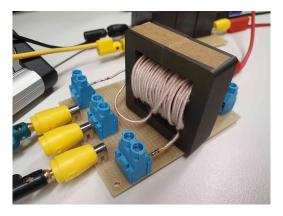

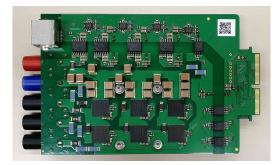

Fig. 9 shows the prototype of the coupled inductors, while Table II presents the parameters of the interleaved boost converter. A power inverter board equipped with gallium nitride (GaN) transistors, shown in Figs. 10 and 11, provides the switching cells. The GaN inverter adapter card offers three half-bridges

Fig. 8: Experimental setup with UltraZohm.

Fig. 9: Coupled inductors prototype.

Fig. 10: GaN adapter card top side.

Fig. 11: GaN adapter card bottom side.

with a shared dc-link, originally designed for drive applications. It is compatible with the digital adapter slots of the UltraZohm system, easing the initial setup effort. The power switches are fully integrated with logic level input drivers and protection against over-current. The availability of phase current, phase voltage, and dc-link voltage measurements allows for use with various control schemes.

In the preliminary experimental setup, push-pull stages are used, i.e.,  $D_1$  and  $D_2$  are replaced with active switches, limiting the set of operating modes to only (1), (12), (21), and (22), leading to a forced CCM type of operation. Here, a more reasonable approach to not drive the top-side switches in each half-bridge, and thus yield a diode-like behavior, was not recommended by the manufacturer of the power switches [16]. As such, the top-side switches are driven with the inverse signal of the respective bottom-side switches, leading to the aforementioned forced CCM.

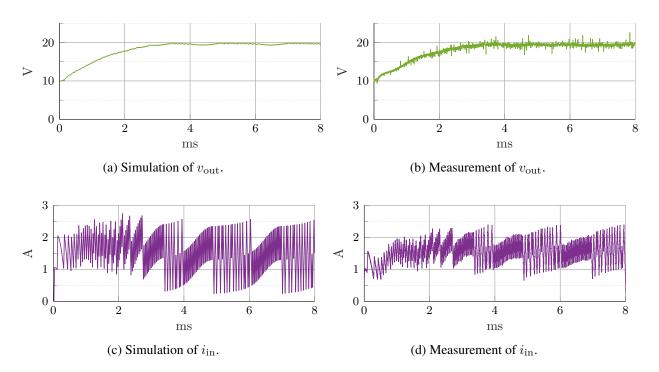

With this setup, the presented mathematical model is verified by applying a pre-calculated switching sequence directly to the switches, resulting in an open-loop start-up operation. The parameters of the open-loop experiment are provided in Table III. The sampling frequency is chosen to be 50 kHz, resulting in an average switching frequency of 18.625 kHz. A comparison of the simulated start-up with the corresponding measurements is depicted in Fig. 12. As can be seen, there is a close matching between the simulated and experimental output voltage  $v_{\text{out}}$ , shown in Figs. 12a and 12b, respectively. Moreover, the simulated and experimental input current  $i_{\text{in}}$  depicted in Figs. 12c and 12d, respectively, shows a comparable pattern that corroborates the validity of the derived model.

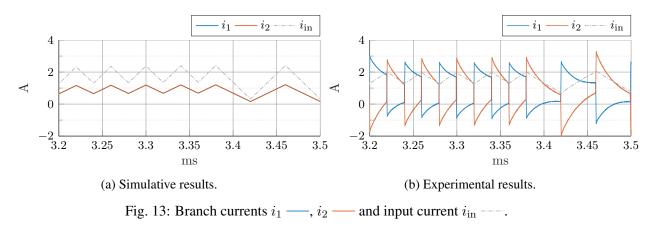

The differences in the branch currents  $i_1$  and  $i_2$ , predicted by the simulation compared to the actual current in the test setup is briefly explained in the following. For this, the branch currents, in addition to the input current, are presented over a shorter time interval to allow for insightful observations, see Fig. 13. In simulation (see Fig. 13a) both branch currents match exactly, whereas Fig. 13b depicts drastically different waveforms. This is an effect caused by the peculiarities of the push-pull topology, in which the timing of the "rectifying" switches becomes critical—in comparison to a topology using conventional diodes. Here, even a small delay of one half-bridge—with respect to the other—will cause a steep change in the currents through both inductances  $L'_1$  and  $L'_2$ , which are, with the coupling factor chosen, in the one-digit  $\mu$ H range. For example, at time 3.22 ms, the sequence of commanded modes is  $(1) \rightarrow (2)$ , where an additional intermediate mode, i.e., mode (2), can be identified that stems from an unwanted delay in the gate driving. During the short time mode (21) is active, the output voltage is directly applied to  $L'_1$  and  $L'_2$ , in the negative and in the positive direction respectively, forcing a change of the

Table II: Parameters of interleaved boost prototype. Table III: Parameters for open-loop measurements.

| Parameter  | Value                 | Parameter      | Value          |

|------------|-----------------------|----------------|----------------|

| $L_1, L_2$ | 190 µH                | $V_{ m in}$    | $10\mathrm{V}$ |

| $k_{12}$   | 0.993                 | $v^*_{ m out}$ | $20\mathrm{V}$ |

| $R_1, R_2$ | $150\mathrm{m}\Omega$ | $R_{ m load}$  | $20\Omega$     |

| C          | $146\mu\mathrm{F}$    |                |                |

Fig. 12: Comparison between simulation and experimental measurements.

branch currents according to the voltages applied.

Despite the aforementioned shortcomings of the setup, it can be concluded that the presented results from the *feasible* subset of operating modes clearly demonstrate the validity of the developed model of the converter.

# **Optimal Control Algorithm**

In this section, the previously derived discrete-time model of the converter is leveraged in a direct MPC scheme. In MPC, the control action is obtained online by solving the underlying optimization problem. At each time step, the switching commands are optimized for N time steps ahead in the future, i.e., the prediction horizon, with respect to a given objective function. The formulated optimization problem, besides accounting for the discrete-time model of the system, can account for explicit constraints. The optimal sequence of control inputs is the one that minimizes the objective function. To introduce feedback, and thus deal with model uncertainties and disturbances, only the first element of the optimal sequence of control actions is applied to the converter. The described approach is known in literature as *receding horizon policy* [17]. At the next time step, the optimization problem is solved again with updated measurements.

The objectives of the proposed MPC strategy are the minimization of the difference between the predicted

and the reference output voltage  $v_{out}^*$ , i.e., the tracking error, and the minimization of excess branch currents, i.e., currents larger than an upper current bound  $i_{bnd}$ . These objectives are mapped into a scalar with the following objective function

$$J(k) = \sum_{\ell=k}^{k+N-1} (v_{\text{out}}^*(\ell) - v_{\text{out}}(\ell))^2 + \lambda_i J_i(\ell) + \lambda_b \left| \sum_{m=1}^{k+N-1} i_1(m) - i_2(m) \right| \quad \text{with}$$

(9a)

$$J_i(\ell) = \sum_{n=1}^2 \begin{cases} 0 & i_n(\ell) < i_{\text{bnd}} \\ (i_n(\ell) - i_{\text{bnd}})^2 & \text{otherwise.} \end{cases}$$

(9b)

It is worth mentioning that in (9a) a third term is added to achieve a balanced utilization of the two converter branches. This term minimizes the difference of the branch currents,  $i_1 - i_2$  over the whole operation of the converter, starting from the first time step m = 1. Moreover, the weighting factors  $\lambda_i, \lambda_b > 0$  are introduced to prioritize among the control goals.

To find the optimal switching sequence that results in the smallest cost  $J_{opt}(k)$  of (9), an exhaustive search is performed at every time step. Algorithm 1 shows the basic structure of the proposed controller with an outer for-loop iterating over all possible switching combinations. An inner loop, that iterates over N, performs the prediction and the cost calculation for each candidate solution. In a final step, the calculated cost is compared with the tentative minimal cost value. If a candidate with a lower associated cost is found, the upper bound of  $J_{opt}$  is updated accordingly. Once all candidates have been explored, the switching pattern resulting in  $J_{opt}$  is identified as the optimal solution.

Algorithm 1 Pseudocode of proposed MPC algorithm.

1: for each  $U(k) = \begin{bmatrix} u(k) & u(k+1) & \dots & u(k+N-1) \end{bmatrix}^T \in \mathcal{U}^{2N}$  do 2: for each step  $\ell \in \{1, \dots, N\}$  do 3: Predict next state based on the operating mode of the converter. 4: Calculate intermediate cost. 5: end for 6: if cost of candidate  $\leq J_{opt}$  then 7: Update  $J_{opt}$ 8: end if 9: end for 10: return  $u^*(k)$

#### **Simulation Results**

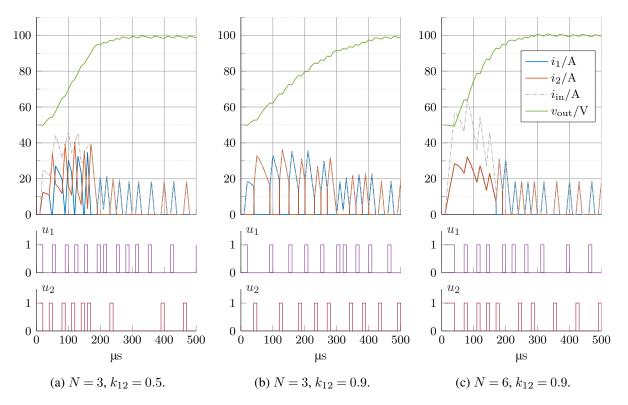

In this section, the proposed control scheme is scrutinized in a simulation environment. The input voltage of 50 V is boosted to a reference output voltage of 100 V at a load of 20  $\Omega$ . The sampling and control frequency is 100 kHz, while the switching frequency is variable due to the direct nature of the control scheme. The weighting factors are  $\lambda_i = 0.05$ ,  $\lambda_b = 0.01$ , with the soft constraint on the branch current being activated above  $i_{\text{bnd}} = 5$ . Fig. 14 displays simulation results for a prediction horizon of N = 3 and N = 6, as well as for two different coupling factors  $k_{12}$ . For three exemplary parameter sets, the input current  $i_{\text{in}}$ , the branch currents  $i_1$  and  $i_2$ , and the output voltage  $v_{\text{out}}$  are plotted. Below, the gate signals  $u_1$  and  $u_2$  are depicted.

It is apparent that the reference output voltage can be tracked accurately in all depicted cases. For N = 3, (Figs. 14a and 14b) the algorithm exhibits similar behavior for both coupling factors in steady-state operation. Nevertheless, significant differences can be found when focusing on the output voltage rampup section. For  $k_{12} = 0.5$ , the algorithm chooses operating points that are in CCM, particularly for  $i_2$ . This enables a higher input current (with comparable branch currents) and thus speeds up the initial ramp up. For  $k_{12} = 0.9$ , however, the uncoupled inductances are significantly smaller. As a result, the changes

Fig. 14: Start-up behavior of the interleaved dc-dc boost converter for different N and  $k_{12}$ .

in the current, and thus its ripple, are bigger, leading to a DCM operation. This gives rise to a slower start-up scenario with a slower transient time by a factor of 2. It is noteworthy that the shorter prediction horizon hinders the algorithm to fully align the cost of branch current balancing while achieving output tracking error minimization.

Comparing this behavior with the case where the same coupling factor of 0.9 is used along with a longer prediction horizon of N = 6 steps, it can be seen that the proposed direct MPC strategy is able to provide a faster dynamic response. Specifically, the algorithm outputs a symmetric start-up pattern to minimize the cumulative tracking error by means of a faster initial ramp-up, while maintaining perfectly balanced branch currents.

Finally, it is noteworthy that the non-minimum-phase nature of the boost converter is visible in the first simulation steps in Fig.14, where the output voltage drops while the coupled inductors are being magnetized. In simulation, a minimum prediction horizon length of N = 2 steps is required to achieve a stable system behavior for the specific problem setting. One possible explanation is that the controller needs to be able to predict past the initial voltage dip caused by the non-minimum-phase behavior [7].

#### Conclusion

This paper presented a switched model of an interleaved boost converter with coupled inductors that covers all possible operating modes of the two-branched system. To derive an as accurate model as possible, the influence of the coupling of the inductors was included in the model. Based on this model, an FCS-MPC scheme was developed and its effectiveness was validated in a MATLAB simulation. The presented results demonstrate that a favorable operation can be achieved as the horizon length increases, even when the magnetic coupling of the inductors is strong.

In a next step, the experimental setup will be changed with respect to the power switches used to avoid operating limitations and thus enable operation in DCM. Additionally, the controller will be implemented on the FPGA of the open-source control platform UltraZohm. In doing so, the whole control scheme, consisting of the derived model and the presented control algorithm, will be validated in real time.

#### References

- [1] P.-W. Lee, Y.-S. Lee, D. Cheng, and X.-C. Liu, "Steady-state analysis of an interleaved boost converter with coupled inductors," *IEEE Trans. Ind. Electron.*, vol. 47, no. 4, pp. 787–795, Aug. 2000.

- [2] H. Kosai, S. McNeal, B. Jordan, *et al.*, "Coupled inductor characterization for a high performance interleaved boost converter," *IEEE Trans. Magn.*, vol. 45, no. 10, pp. 4812–4815, Oct. 2009.

- [3] P. Athalye, R. W. Erickson, and D. Maksimović, "Variable-frequency predictive digital current mode control," *IEEE Power Electron. Lett.*, vol. 2, no. 2, pp. 113–116, Dec. 2004.

- [4] T. Gomez, W. Hernández, W. Martínez, and C. A. Cortes, "Control techniques for interleaved dc/dc converters with magnetic coupling," in *IEEE Works. on Power Electr. and Power Qual. Appl.*, Bogota, Colombia, May 2017, pp. 1–6.

- [5] P. Karamanakos, E. Liegmann, T. Geyer, and R. Kennel, "Model predictive control of power electronic systems: Methods, results, and challenges," *IEEE Open J. Ind. Appl.*, vol. 1, pp. 95–114, 2020.

- [6] P. Karamanakos, T. Geyer, and S. Manias, "Direct model predictive current control strategy of dc-dc boost converters," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 1, no. 4, pp. 337–346, Dec. 2013.

- [7] P. Karamanakos, T. Geyer, and S. Manias, "Direct voltage control of dc-dc boost converters using enumerationbased model predictive control," *IEEE Trans. Power Electron.*, vol. 29, no. 2, pp. 968–978, Feb. 2014.

- [8] Z. Karami, Q. Shafiee, S. Sahoo, *et al.*, "Hybrid model predictive control of dc–dc boost converters with constant power load," *IEEE Trans. Energy Convers.*, vol. 36, no. 2, pp. 1347–1356, Jun. 2021.

- [9] T. Hausberger, A. Kugi, A. Eder, and W. Kemmetmüller, "High-speed nonlinear model predictive control of an interleaved switching dc/dc-converter," *Control Eng. Pract.*, vol. 103, pp. 1–13, Oct. 2020.

- [10] P. Karamanakos, T. Geyer, and S. Manias, "Model predictive control of the interleaved dc-dc boost converter with coupled inductors," in *Proc. Eur. Power Electron. Conf.*, Lille, France, Sep. 2013, pp. 1–10.

- [11] P. Karamanakos, T. Geyer, N. Oikonomou, F. D. Kieferndorf, and S. Manias, "Direct model predictive control: A review of strategies that achieve long prediction intervals for power electronics," *IEEE Ind. Electron. Mag.*, vol. 8, no. 1, pp. 32–43, Mar. 2014.

- [12] Y. Liang, Z. Liang, D. Zhao, Y. Huangfu, and L. Guo, "Model predictive control for interleaved dc-dc boost converter based on Kalman compensation," in *Int. Power Electr. and Appl. Conf. and Expo.*, Shenzhen, China, Nov. 2018, pp. 1–5.

- [13] P. Karamanakos and T. Geyer, "Guidelines for the design of finite control set model predictive controllers," *IEEE Trans. Power Electron.*, vol. 35, no. 7, pp. 7434–7450, Jul. 2020.

- [14] S. Wendel, A. Geiger, E. Liegmann, et al., "UltraZohm—A powerful real-time computation platform for MPC and multi-level inverters," in Proc. IEEE Int. Symp. Pred. Control of Elect. Drives and Power Electron., Quanzhou, China, May 2019, pp. 1–6.

- [15] E. Liegmann, T. Schindler, P. Karamanakos, A. Dietz, and R. Kennel, "UltraZohm—An open-source rapid control prototyping platform for power electronic systems," in *Int. Aegean Conf. on Elect. Mach. and Power Electron. and Int. Conf. on Optim. of Elect. and Electron. Equip.*, Brasov, Romania, Sep. 2021, pp. 1544– 1551.

- [16] LMG342xR030 600-V 30-mOhm GaN FET with integrated driver, protection, and temperature reporting, SNOSDA7D, Revised March 2022, Texas Instruments, Sep. 2020. [Online]. Available: https://www.ti. com/lit/gpn/LMG3425R030.

- [17] T. Geyer, *Model predictive control of high power converters and industrial drives*. Hoboken, NJ: Wiley, 2016.