SAMAN PAYVAR

# GPU-based Architecture Modeling and Instruction Set Extension for Signal Processing Applications

#### SAMAN PAYVAR

GPU-based Architecture Modeling and Instruction Set Extension for Signal Processing Applications

#### **ACADEMIC DISSERTATION**

To be presented, with the permission of the Faculty of Information Technology and Communication Sciences of Tampere University, for public discussion in the auditorium TB109 of the Tietotalo, Korkeakoulunkatu 1, Tampere, on 20 January 2023, at 12 o'clock.

#### ACADEMIC DISSERTATION

Tampere University, Faculty of Information Technology and Communication Sciences

Finland

Responsible Professor Timo D. Hämäläinen

supervisor Tampere University

and Custos Finland

Pre-examiners Professor Juha Plosila Docent Sebastien Lafond

University of Turku Åbo Akademi University

Finland Finland

Opponent Professor Shuvra Bhattacharyya

University of Maryland

**United States**

The originality of this thesis has been checked using the Turnitin OriginalityCheck service.

Copyright ©2022 author

Cover design: Roihu Inc.

ISBN 978-952-03-2722-4 (print) ISBN 978-952-03-2723-1 (pdf) ISSN 2489-9860 (print) ISSN 2490-0028 (pdf)

http://urn.fi/URN:ISBN:978-952-03-2723-1

Carbon dioxide emissions from printing Tampere University dissertations have been compensated.

PunaMusta Oy – Yliopistopaino Joensuu 2022

#### **PREFACE**

This work has been carried out in the Faculty of Information Technology and Communication Sciences at Tampere University during 2017-2022.

I would like to express my appreciation to my supervisor Professor *Timo D. Hämäläinen* for his guidance. Grateful acknowledgments go also to the reviewers of my thesis, Professor *Juha Plosila* and Docent *Sebastien Lafond* for their comments and the opponent Professor *Shuvra S. Bhattacharyya*. In addition, I would like to thank Professor *Jani Boutellier* and Professor *Maxime Pelcat* for their advice. I am very grateful for the opportunity of working at the Unit of Computing Sciences and I want to thank all my colleagues and supervisors.

I am grateful to my family for supporting me throughout my education.

Tampere, December 2022 Saman Payvar

#### **ABSTRACT**

The modeling of embedded systems attempts to estimate the performance and costs prior to the implementation. The early stage predictions for performance and power dissipation reduces the more costly late stage design modifications. Workload modeling is an approach where an abstract application is evaluated against an abstract architecture. The challenge in modeling is the balance between fidelity and simplicity, where fidelity refers to the correctness of the predictions and the simplicity relates to the simulation time of the model and its ease of comprehension for the developer. A model named GSLA for performance and power modeling is presented, which extends existing architecture modeling by including GPUs as parallel processing elements. The performance model showed an average fidelity of 93% and the power model demonstrated an average fidelity of 84% between the models and several application measurements. The GSLA model is very simple: only 2 parameters that can be obtained by automated scripts.

Besides the modeling, this thesis addresses lower level signal processing system improvements by proposing Instruction Set Architecture (ISA) extensions for RISC-V processors. A vehicle classifier neural network model was used as a case study, in which the benefit of Bit Manipulation Instructions (BMI) is shown. The result is a new PopCount instruction extension that is verified in ETISS simulator. The PopCount extension of RISC-V ISA showed a performance improvement of more than double for the vehicle classifier application. In addition, the design flow for adding a new instruction extension for a re-configurable platform is presented.

The GPU modeling and the RISC-V ISA extension added new features to the state of the art. They improve the modeling features as well as reduce the execution costs in signal processing platforms.

# **CONTENTS**

| 1 | Intro | oduction                                      | 17 |

|---|-------|-----------------------------------------------|----|

|   | 1.1   | Objectives and scope of research              | 18 |

|   | 1.2   | Research problems                             | 19 |

|   | 1.3   | Summary of contributions                      | 19 |

|   |       | 1.3.1 Author's contribution to published work | 20 |

|   | 1.4   | Outline of the thesis                         | 20 |

| 2 | Rela  | ted work                                      | 21 |

|   | 2.1   | Workload modeling                             | 21 |

|   |       | 2.1.1 Fidelity work                           | 21 |

|   |       | 2.1.2 Optimization work                       | 23 |

|   | 2.2   | Instruction Set Architecture extensions       | 29 |

|   | 2.3   | Literature review comparison                  | 35 |

| 3 | Met   | hodology                                      | 37 |

|   | 3.1   | Workload modeling                             | 37 |

|   | 3.2   | RISC-V ISA extension methods                  | 38 |

|   |       | 3.2.1 ETISS simulator                         | 39 |

|   | 3.3   | Use case applications                         | 39 |

| 4 | Wor   | kload modeling of heterogeneous platforms     | 41 |

|   | 4.1   | Performance modeling                          | 42 |

|   | 4.2   | Power modeling                                | 43 |

|   | 4.3   | Proposed models                               | 44 |

|   | 4.4   | Population count analysis                     | 47 |

|     |         | 4.4.1     | ropCount instruction                         | 4/  |

|-----|---------|-----------|----------------------------------------------|-----|

|     |         | 4.4.2     | PopCount modeling                            | 52  |

|     |         | 4.4.3     | Modeling conclusion                          | 55  |

| 5   | RISC    | C-V non   | -standard instruction extensions             | 57  |

|     | 5.1     | RISC-V    | V BMI extension                              | 57  |

|     | 5.2     | RISC-V    | V extension design flow                      | 58  |

|     |         | 5.2.1     | Compiler modification                        | 58  |

|     |         | 5.2.2     | Simulator modification                       | 59  |

|     |         | 5.2.3     | ISA extension conclusions                    | 59  |

| 6   | Con     | clusions  | 8                                            | 61  |

|     | 6.1     | Addres    | ssing the research problem                   | 61  |

|     | 6.2     | Future    | work                                         | 62  |

| Re  | ferenc  | ces       |                                              | 63  |

| Pu  | blicat  | ion I     |                                              | 71  |

| Pu  | blicat  | ion II .  |                                              | 79  |

| Pu  | blicat  | ion III . |                                              | 103 |

| Pu  | blicat  | ion IV .  |                                              | 111 |

| Lis | st of I | Figures   |                                              |     |

|     | 1.1     | Overv     | iew of the research conducted in this thesis | 18  |

|     | 3.1     | Workl     | oad modeling method                          | 38  |

|     | 4.1     | Model     | of Architecture                              | 41  |

|     | 4.2     | Model     | of Computation.                              | 42  |

|     | 4.3     | Mappi     | ng of MoC on MoA                             | 42  |

|     | 4 4     | An exa    | ample of the $S$ and $\gamma$ variables.     | 43  |

| 4.5     | Trading off between different aspects of the modeling | 44 |

|---------|-------------------------------------------------------|----|

| 4.6     | Development and utilization workflow                  | 46 |

| 4.7     | PopCount LLVM Logical Operations                      | 51 |

| 4.8     | Population count graph                                | 54 |

| 5.1     | Compiler modification design flow                     | 59 |

| 5.2     | Simulator modification design flow                    | 60 |

| List of |                                                       |    |

| 2.1     | Summary of workload reviews                           | 27 |

| 2.2     | Summary of RISC-V reviews                             | 34 |

| 4.1     | Parameters of functions                               | 53 |

| 4.2     | Fidelity values                                       | 54 |

# **ABBREVIATIONS**

API Application Programming Interface

BMI Bit Manipulation Instruction

CNN Convolutional Neural Network

DSP Digital Signal Processor

ETISS Extendable Translating Instruction Set Simulator

GCC GNU Compiler Collection

GNU GNU's Not Unix

GPU Graphics Processing Unit

I/O Input Output

ISA Instruction Set Architecture

LSLA Linear System Level Architecture

MoA Model of Architecture

MoC Model of Computation

OpenCL Open Computing Language

PULP Parallel Ultra Low Power

RISC-V Reduced Instruction Set Computer Five

# **ORIGINAL PUBLICATIONS**

Publication I

S. Payvar, J. Boutellier, A. Morvan, C. Rubattu and M. Pelcat. Extending Architecture Modeling for Signal Processing towards GPUs. 2019 27th European Signal Processing Conference (EU-SIPCO). 2019, 1–5. DOI: 10.23919/EUSIPCO.2019.8903094.

Publication II

S. Payvar, M. Pelcat and T. D. Hämäläinen. A model of architecture for estimating GPU processing performance and power. *Design Automation for Embedded Systems*. 2021, 43–63. DOI: 10.1007/s10617-020-09244-4.

Publication III

S. Payvar, M. Khan, R. Stahl, D. Mueller-Gritschneder and J. Boutellier. Neural Network-based Vehicle Image Classification for IoT Devices. 2019 IEEE International Workshop on Signal Processing Systems (SiPS). 2019, 148–153. DOI: 10.1109/SiPS47522. 2019.9020464.

Publication IV

S. Payvar, E. Pekkarinen, R. Stahl, D. Mueller-Gritschneder and T. D. Hämäläinen. Instruction Extension of a RISC-V Processor Modeled with IP-XACT. 2019 IEEE Nordic Circuits and Systems Conference (NORCAS): NORCHIP and International Symposium of System-on-Chip (SoC). 2019, 1–5. DOI: 10.1109/NORCHIP. 2019.8906975.

# 1 INTRODUCTION

Computer systems are composed of software, middleware, and hardware. The software can be abstracted as a collection of commands to be executed on the hardware. Typically, hardware platforms have multiple Processing Units (PUs). The middleware provides abstraction between software and hardware, and can regard the workload scheduling where the SW commands are mapped to the PUs of the hardware.

Machine learning algorithms require high computing performance and there is a need to execute them in a wide range of platforms from Internet of Things (IoT) devices to cloud servers. Quite often there is a limited execution time budget. The challenge is that energy consumption should be minimized while the output quality and performance requirements have to be satisfied. Traditionally, the optimization process starts by modifying the application and then further system level optimizations are considered by changing the mapping or the platform. In these cases, the application workload mapping on the platform variations must be evaluated.

A model-based approach is often used to speed up the development time rather than trying out real implementations. There are multiple feasible system modeling methods. This thesis uses a modular approach, which considers the application and platform models separately. This system modeling concept was originally introduced by Pelcat et al. [34] and named Linear System Level Architecture (LSLA) and provides an obvious division and reusability for application and platform models. In LSLA, the Model of Computation (MoC) presents the application and the Model of Architecture (MoA) represents the platform. The original LSLA supports only multi-core CPU platforms, and performance modeling. To better support machine learning applications, this thesis presents an extension to cover Graphical Processing Unit (GPU) units and power modeling also.

In this way the goal of this thesis is to improve system level modeling features at a high abstraction level. The second goal is to improve real platform performance at a lower abstraction level study. Machine learning applications are often written

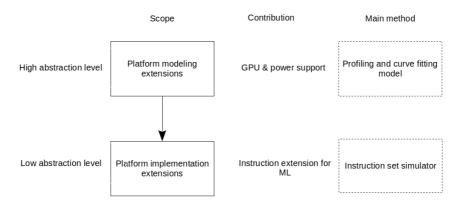

Figure 1.1 Overview of the research conducted in this thesis

in OpenCL which motivates the GPU extension for the LSLA. For platform optimization, the way that extra instructions are added is studied. It is expected that the Instruction Set Architecture (ISA) extensions will reduce the number of compiled assembly instructions, resulting in faster execution time. Reduced Instruction Set Computer Five (RISC-V) ISA is open source and a widely adopted ISA which makes it a suitable selection for this research. Common classification applications like the Convolutional Neural Network (CNN) benefit greatly from Bit Manipulation Instructions (BMI) extensions which at the beginning of this study were not standardized in RISC-V. Implementation of a non-standard RISC-V extension is another aspect of the research problem for system optimizations in this thesis.

Figure 1.1 presents an overview of the research conducted in this thesis: the abstraction levels according to the scope, novel contributions, and main methods applied in the research.

# 1.1 Objectives and scope of research

The objective of this thesis is to improve implementations of machine learning type applications. The focus is on the modeling of the workload mapping on the platform and ISA extensions. The target is to present performance and power models with as high fidelity as possible for the platform, i.e., at least 80 percent to be useful for early state architecture exploration. The modeling of the applications and their platform independent optimizations are beyond the scope of this thesis. The second goal is

to achieve at least double the performance improvement with ISA extensions for a neural network application on an IoT device.

## 1.2 Research problems

The research problems investigated in this thesis are platform modeling and ISA extensions. The modeling questions include the following:

- What is the simplest system model that achieves a reasonable fidelity value for useful modeling accuracy?

- Could the performance model also be used for power modeling to keep the model as simple as possible?

- How to expand the LSLA so that OpenCL applications running on GPUs can be modeled?

The ISA extension questions consist of the following:

- What is the performance gain and effort of adding instruction extensions to machine learning algorithms?

- What kind of custom instruction helps neural network execution on RISC-V?

# 1.3 Summary of contributions

*Publication* [26] describes the performance model for an OpenCL application on GPU equipped platforms. The model is linear and it is named GSLA. It introduces minimal computation for fast workload analysis resulting in reasonable workload balancing between processing elements. The performance studies show an average fidelity value of 93%.

*Publication* [31] depicts the power model for the OpenCL applications and provides a power dissipation analysis. Utilizing this model facilitates workload spreading between processing elements for optimal power dissipation. The power dissipation inspections reveal an average fidelity value of 84%.

Publication [27] introduces the Population Count(PopCount) extension for RISC-VISA, which improves the performance of a vehicle classifier CNN application more

than double. This work includes the total instruction count and type analysis as well as their impact on performance.

Publication [29] presents a design flow for including the new instructions in the compiler and simulator of the RISC-V ISA. The effort analysis estimates around two hours for a new instruction inclusion.

#### 1.3.1 Author's contribution to published work

The author is the main author and the main contributor in all included publications. The main tasks were performed by the author including the literature reviews, software development work, measurements, analysis of the results, and typing of the articles.

Assistant Professor Jani Boutellier helped to develop the ideas in *Publication* Payvar et al., [31] and [27], assisted with the writing, and gave valuable comments.

Prof. *Maxime Pelcat* helped to develop the ideas in *Publication*[26] and *Publication* [31] and gave instructive comments.

Dr. Antoine Morvan and Claudio Rubattu, M.Sc., helped to develop the idea in *Publication*[26] and [31].

Mir Khan, M.Sc., provided the binarized version of the vehicle classifier application and helped with the writing of *Publication* [27].

Rafael Stahl, M.Sc., and Dr. Daniel Mueller-Gritschneder helped with *Publication* [27] and *Publication* [29], and provided valuable comments.

Esko Pekkarinen, M.Sc., helped to develop the idea in Publication [29] and with the writing of the article.

Prof. Timo D. Hämäläinen helped to develop the idea in *Publication* [29] and [31] and with the writing of the articles.

#### 1.4 Outline of the thesis

This thesis consists of four publications and an introductory part. Chapter 2 briefly presents the related work. Chapter 3 introduces the performance and power models for workload distribution. Chapter 4 explains the non-standard RISC-V ISA extensions. Chapter 5 considers the execution cost improvements of the implementations. Chapter 6 presents the main results and conclusions of the thesis.

#### 2 RELATED WORK

System optimizations for a specific application are considered by two approaches utilized simultaneously or separately. The first approach is by efficient workload balancing between the processing elements of heterogeneous platforms. The second approach is architecture modifications, in this thesis the system's processing elements with ISA extensions. In this section, the related work for both approaches is presented.

## 2.1 Workload modeling

In platforms with multiple processing units, the optimal platform utilization requires balanced work allocation between them. This is achievable by many methodologies, and Table 2.1 summarizes the major works related to them.

The related work is divided into two subgroups which focus on fidelity evaluation or optimization. This thesis concentrates on fidelity evaluation while the optimization works are presented here to provide a broader view. The studies use different metrics to evaluate their proposed estimation models, i.e., the fidelity of their work. The suitability of their selected metric is beyond the scope of this thesis but could be further investigated, e.g., in [13].

## 2.1.1 Fidelity work

The main related work is the Linear System-Level Architecture (LSLA) [34]. LSLA presents the hardware as a model of architecture (MoA) and describes the application with a mode of computation (MoC). System optimization iteration is shown as the mapping of the MoC activity on the MoA. An LSLA MoA is composed of the processing elements and the communication nodes, and each component has a cost function where the targeted cost could differ such as the execution time or the

energy consumption. The total execution cost of the system is calculated as the sum of the execution costs of the processing elements and the communication nodes. The authors present experiments with C applications running on a multi-core CPU platform using the PREESM tool [33]. They used the *kendall tau* as the fidelity measurement to evaluate their experiments and reported a fidelity of 86% for the energy consumption modeling.

The period graph study [3] estimates the system throughput from the system simulation data and the maximum cycle mean. They experimented with a nested genetic and a simulated annealing algorithm for voltage scaling optimization. Their graph consists of four main elements including named nodes, striped nodes, directed edges, and solid small black circles on the edges. For period graph construction, first the simulation data is used to identify the period. Then, the tasks of the period are considered as the nodes and the idle time of the period is demonstrated with striped nodes. Later, the nodes connections as the edges are assigned according to their order in the period from the last node to the first node. They use the send and receive nodes for Inter Processor Communication (IPC) to show the data transmission. They are connected by the edges of the send node to the receive node. Also, a delay is applied to an edge by adding a black circle to visualize the inter-iteration dependencies. They reported a fidelity value of more than 0.65 for a system with six processors.

The ARM's big.LITTLE model [41] facilitates the core selection of heterogeneous architecture. Their model is based on a correlation between last-level data cache (LLC) misses and cycles per instruction (CPI) for efficient core selection. They use two linear equations for presenting the model where one equation is for the small cores and the other equation is for the big cores. Their model provides a soft threshold setting where the larger number of LLC misses are scheduled on little cores. They use a linear equation with two parameters for CPI calculations where MPI is multiplied by the first parameter and added to the second parameter. They experimented with HEVC and LDPC decoder applications and observed the effectiveness of application division into multi-phases. They reported a negligible error of 9.71% for A15 and 21.67% for A7, and error reduction as the LLC misses increased.

The Runtime system for User Preferences-defined Schedules (RUPS) [7] is a runtime scheduling tool for multi-core architectures, which provides a trade-off between three variables named PE, i.e., performance, E, i.e., energy consumption, and FT, i.e., fault tolerance. Their methodology depicts the best scheduling trade-off deci-

sion from the user preferences. They considered task duplication for fault tolerance where a copy of a task named duplicate was assigned to another processing element which was replaced by the initial task in case of failure. RUPS consists of four parts including system check, user preferences, schedule creation, and runtime system. First, the system check gets the system data and then the user preferences are collected. Later, the schedule is optimized according to the user requests and the system data and then the runtime system receives the schedule. They experimented using real machines supporting DVFS with four scenarios of only PE, PE and FT, only FT, and only E. They reported an average maximum deviation of 7.14% and 1.64% for energy prediction.

The thermally aware energy efficiency model of [38] utilizes environmental temperature variations and eliminates the power sensor requirement of the multiprocessor platform. Their model includes a variable for the temperature which is used for application reconfiguration. They considered the platform configuration points for energy modeling of the heterogeneous platforms with Hardware Program Counters (HPC). They experimented with the ODROID XU3 platform in three different environments where the board fan condition and temperatures were different in order to provide a cold, middle, and hot case. They observed large energy level variations with temperature changes from cold to hot and their results show 33% energy improvements for modeling with temperature awareness.

The ANNETTE [46] shows a performance estimation model for Deep Neural Network (DNN) applications. They focus on mapping of the layers according to their stacked model. Their framework has mapping and mixed layer models and generates models according to the kernel and benchmark data. They use two separate platforms, i.e., ZCU102 SoC board and Intel Neural Compute Stick 2 (NCS2) and two network applications for execution time evaluations. They used the Spearman metric to evaluate their model on 34 random models of the NASBench dataset and reported 0.988 as the fidelity value of their model.

#### 2.1.2 Optimization work

The parallel dataflow study by [12] uses the PREESM tool to explore the energy efficient mapping of a parallel application on a platform with a quad-core CPU. Their work depicts the effect of the static power domination of contemporary platforms on

the energy consumption of parallel applications. They showed that limiting the execution speed of the application for controlling the clock frequency of the processor core by meta data input to the power management system resulted in energy-efficient mapping. They used Levenberg-Marquardt's algorithm for calculating a third degree polynomial as their power model. They experimented with three different mappings of the Sobel filter application including completely sequential, completely parallel, and mix-parallel mappings. They reported energy savings of over 50% compared to the reference.

The runtime mapping optimization research in [47] considers the energy efficiency of several parallel applications running on a multi-core platform. They utilized a hybrid approach of both mapping and frequency adjustment. Their management strategy has three steps. First, for each application some mapping options and their minimum frequencies are calculated at design time. Later, at runtime, the minimum common frequency is selected according to the design time data, which shows the relevant mappings. Finally, the mappings are combined. In the case of violation of the timing constraints, the second and third steps are redone. Their design time data consists of the execution trace which is the start time and the end time of the mapping options at the defined frequencies. Also, the Minimum Allowed Frequency (MAF) based on [12] is determined. Their results depict 2x reduction in energy consumption.

The workload type study by [11] investigates the effect of the instructions type on the big.LITTLE platform. They showed the impact of the type of the executed instruction and the stress on the micro architecture. The execution operation of different machine instructions utilizes diverse transistors, thus the power dissipation on the processor varies. Their experiments with six benchmarks depict around 40% workload type impact on power dissipation. Their workload type aware scheduling includes a power and a performance model for each workload type where the energy consumption of a schedule is calculated according to the relevant models. Their scheduler has four variations for power and performance, both including and ignoring them. The best case studies showed 31.3% energy savings.

The passive-active flow graphs (PAFGs) of [20] proposes a computation model for the signal processing systems. A PAFG is developed as an application graph based on core functional dataflow (CFDF). The PAFG expands the dataflow graphs to cover several inputs and outputs with a different presentation where the vertices

show both buffers and computational models and the edges depict their connections. The PAFG blocks are passive or active, where an active block shows both computational blocks and buffers but a passive block depicts only buffers. In addition, they introduce the passivization transformation which is the conversion of active blocks to passive ones. Their experiments with the error vector magnitude and jitter measurement applications show improvements in throughput and buffer memory requirement (BMR).

The intermediate directed acyclic graph (DAG) representation work by [2] shows an improved model for resource allocation. Its implementation in the SPIDER tool utilizes single-rate directed acyclic graph (SR-DAG) data. They use dependency equations for the numerical modeling of the SR-DAG and define additional equations for hierarchy inclusion from the  $\pi$ SDF MoC. Their relaxed execution model on interface-based synchronous dataflow (IBSDF) maximizes the throughput of the hierarchical application. The proposed method eliminates the SR-DAG building and storing stage but increases the complexity of the resource allocation algorithm. They experimented with the greedy scheduling of four applications including SqueezeNet, Reinforcement Learning, Stabilization, and Sobel-Morpho. They report an overhead reduction in computation time and memory footprint besides performance improvement. Their results show an average memory reduction of 97.34% for scheduling and mapping. Also, a minimum decrease of 47.11% in total execution time for the resource allocation stage is reported.

The Data flow Method for Hardware/Software Exploration (DAMHSE) [42] represents a fast hardware-software prototyping method. A compilable/synthesizable code is provided by performing a design space exploration (DSE). Their experiments with the parallel edge detection of an image processing system shows performance elevation by 21.6x. They used hardware accelerators and an edited PREESM tool for optimized tasks for actor scheduling and mapping in addition to code generation. They described a complementary application management system which dynamically distributes tasks between processing elements. Their manager has a low penalty of maximum 20% of the execution time which makes it suitable for low power systems. They report high computational performance with reasonable overhead for dynamic application mapping.

The OpenCL as abstract hardware research [36] shows a system modeling framework with multiple MoCs. They implemented a portable heterogeneous architec-

ture for system modeling. Their model-based design framework arranges a system into different directors where each one shows a semantic model. The models are based on a MoC which executes according to implemented semantics. An application scenario contains multiple directors, which is a heterogeneous combination of MoCs. They evaluated the utilization of OpenCL by mapping an application modeled by Synchronous Data Flow (SDF) on different platforms. They experimented with a palatalized 2-D image processing application for face detection. The face detection has three modules for skin detection, skin quantization, and image contouring. They conclude that OpenCL eases the targeted automatic synthesis.

The Distributed Operation Layer (DOL) by [44] is a framework for the efficient execution of parallel applications on heterogeneous platforms with multiple processors. DOL provides automation for optimized algorithm mapping on the architecture according to the targeted goal. In addition, DOL facilitates system level performance analyzing with two static and dynamic models. The static model does not consider resource sharing and assumes smooth patterns of operation and communication, whereas the dynamic model considers bursts, blocking, and synchronization. The DOL framework has four parts including application specification, architecture specification, functional simulation, mapping optimization and performance evaluation while it outputs the mapping specification. They experimented with MPEG-2 decoder mapping using a static model for performance analysis. Their experimental architecture has two identical tiles communicating through a NoC while each tile consists of a RISC and a DSP. They presented three optimal mappings and selected one of them as the best choice because of the workload variations.

ArchC [39] is an open-source processor architecture description language (ADL) based on SystemC. It aids architecture design in the early stages by providing a SystemC executable and automatically generating verification tools like a simulator. ArchC compares the model editions against the functional description by inspecting the memory hierarchy and other integration of IPs in a design. Also, it supplies multiple simulator options, i.e., interpreted or compiled and several memory selections like memory levels or cache. ArchC has two inputs for describing the targeted architecture. One is the explanation of the resources like a pipeline structure or memory hierarchy, and the other is a statement of the instruction set architecture, such as the format of the instructions or the opcodes. They simulated multiple processor architectures using ArchC. They have MIPS and Intel 8051 with both cycle-accurate and

functional models and several architectures, such as PowerPC with only functional models.

The energy model work in [37] describes the utilization of core level techniques for heterogeneous platform modeling. They experimented with variable platform configurations with the same performance levels where the platform configuration was considered as the number of application parallel instances, number and type of cores, DVFS levels, and utilization rate. Their experiments were based on the ODROID XU4 platform which has two types of core clusters of ARM Cortex A7 and ARM Cortex A15, while four distinct voltage and frequency levels for both core types are involved. They implemented two energy models: one for big cores and the other for small cores and reported different energy and performance values in a table. Their results show better energy efficiency in terms of the utilization rate factor.

The present work focuses on improving modeling features and accuracy while the majority of the reviewed related research targets the optimization of some applications. Table 2.1 summarizes the workload reviews. The summary tables present the similarities, case study and the results with respect to this work. These studies are selected based on the goal of the study, the utilized methodology, experimentation approaches, design tools, and evaluation metrics. In addition to relevance, the publication date of the paper is considered to provide an up-to-date literature review as the majority of the reviewed papers have been published during the last four years. For example, the LSLA uses the same evaluation metric to show the suitability of the model and report a high fidelity value, as in this work. The table includes five columns. From left to right the first column shows the reference, the second describes the scope of the reviewed work, the third lists the similarity score to this work within a range of one to five where five is the highest and only used for the publications of this research, and the fourth and fifth columns show the purpose and the reported results.

Table 2.1 Summary of workload reviews

| Ref. | Scope                      | Similarity | Purpose                                           | Results      |

|------|----------------------------|------------|---------------------------------------------------|--------------|

| LSLA | Methodology and evaluation | 4          | Modeling C applications running on multi-core CPU | 86% fidelity |

| [12] | Polynomial utilization     | 3 | Parallel applications energy efficient mapping                   | 50% energy saving                          |

|------|----------------------------|---|------------------------------------------------------------------|--------------------------------------------|

| [47] | Mapping optimization       | 2 | Dynamic energy optimization by mapping and frequency adjustment  | 206% energy saving                         |

| [11] | Workload scheduling        | 2 | Energy optimiza-<br>tion by type<br>aware workload<br>scheduling | 31.3% energy saving                        |

| [20] | Graph presenta-            | 2 | Modeling signal processing systems                               | 31.88% throughput<br>25% BMR               |

| [2]  | MoC of application         | 2 | Resource allocation modeling                                     | 97.34% mem.,<br>47.11% exe. reduc-<br>tion |

| [3]  | Fidelity evaluation        | 3 | Systems through-<br>put estimation                               | Fidelity of mini-<br>mum 65%               |

| [42] | Task mapping               | 2 | Hardware-software prototyping                                    | 21.6x performance increase                 |

| [36] | OpenCL mapping             | 2 | System modeling with portable architecture                       | Design flow                                |

| [44] | Architecture modeling      | 2 | Automatic algorithm mapping                                      | Optimal mapping                            |

| [39] | Architecture<br>design     | 2 | Early stage architecture design and verification                 | MIPS-I 550.91<br>KIPS                      |

| [41] | Multi-core model-<br>ing   | 2 | Modeling ARM's big.LITTLE architecture                           | System model                               |

| [7]  | Multi-core schedul-<br>ing | 2 | Runtime scheduling of multi-core architectures                   | Max deviation of 7.14% and 1.64%           |

| [37] | Multi-core model-<br>ing   | 2 | Modeling heterogeneous platform                                  | Energy model                               |

| [38] | Multi-core model-<br>ing   | 2 | Energy-efficient<br>modeling without<br>power sensors            | 33% energy saving                          |

| [46]                 | Fidelity evaluation | 3 | Modeling DNN applications           | 0.988 performance fidelity                   |

|----------------------|---------------------|---|-------------------------------------|----------------------------------------------|

| This work [26] & [31 | Architecture mod-   | 5 | Modeling OpenCL applications on GPU | 93% performance<br>and 84% power<br>fidelity |

#### 2.2 Instruction Set Architecture extensions

The RISC-V ISA extension work in [16] depicts the inclusion of Bit Manipulation Instructions (BMI) into the RISC-V ISA. They explored system performance and power improvements through hardware optimization. They considered the instructions of the ARMv8 and x86 and used them as a reference for introducing ten BMIs to the RISC-V ISA. They mentioned 13.5% less bytes encoding requirement in comparison to x86. They implemented the introduced BMIs with Berkeley's Rocket CPU and reported no overhead on the critical path. Their experiments included 13 benchmarks where instructions were manually replaced for the GNU assembler and the results show a speed-up of between 1.09x and 96.87x.

The RISC-V verification environment study by [23] presents a framework for the early stage evaluation of RISC-V cores. The demonstrated framework has a reconfigurable, portable, and user-friendly design for the easy addition of user-defined ISA extensions. Their environment communicates with the DUT through the AXI4 lite protocol, which facilitates core switching. Their implementation, based on Universal Verification Methodology (UVM), utilizes the object-oriented facilities of the UVM to provide bottom-up stimuli generation. They used internal binded signals for designing their predictor model, which provides a reconfigurable architecture.

The multi-core generation work by [40] presents an automated solution for architecture customization. It is based on the RISC-V ISA and outputs the Verilog code of the architecture for an input application described as a dataflow. They used an open source rocket chip generator with added accelerators and a NoC. The utilized tools allow architecture configuration such as memory size or number of cores. They used the CAL actor language for the application development, which includes actors as operations. They experimented with two applications including auto focus criterion calculation and convolution. Their results show decreased design time, reduced hardware resources, and improved performance.

The customized core paper in [48] demonstrates the analysis of a taped-out implementation of an in-order, single-issue, 64-bit RISC-V ISA core named Ariane. It has Global Foundries 22-nm FDX technology and runs up to 1.7 GHz. The core covers multiplication or division, atomic memory operations, floating point, and compressed instructions. It has six pipeline stages and a branch predictor. Its cache memories are single-port static SRAM by INVECAS while the cache size of the instructions is 16kB and the cache size of the data is 32kB. Their implementation includes ISA extensions, reducing the number of instructions by a factor of 4.6 when compared to the baseline 32-bit RISC-V. Their evaluations with a 2-D convolution show that the number of instructions decreases to 110k with the DSP ISA extensions, whereas without the extension the number of instructions is 129k for 64-bit ISA and 135k for 32-bit ISA.

The near-threshold (NT) RISC-V core work by [9] shows the implementation of an architecturally optimized in-order core which supports ISA extensions. It covers compressed instructions and has a L0 buffer which causes less cache access. Their implementation has four pipeline stages and Harvard memory architecture. For power efficiency, they considered clock gating so that each unit has separate input operand registers, resulting in a 50% decrease in power dissipation. Their evaluations of sensor processing workloads demonstrate 3.5-fold performance gain and 3.2-fold energy efficiency. They implemented several ISA extensions such as post-increment instructions, hardware loop, vector instructions, and fixed point. They compare their architecture to baseline RISC-V and OpenRISC cores and reported 10-fold speedup as a result of the implemented ISA extensions.

The vector extension study by [5] describes a 64-bit RISC-V coprocessor called Ara coupled with a RV64GC core named Ariane. Their architecture has uniform lanes of functional units and vector register files communicating through a vector load/store unit (VLSU) and slide unit (SLDU) which makes it scalable. They experimented with AXPY, convolution, and matrix multiplication and reported 97% floating point unit (FPU) usage for 256x256 matrix multiplication. Ara is implemented with GlobalFoundries 22FDX FD-SOI technology and runs at more than 1 GHz in the typical corner. They compared Ara plus Ariane with solo Ariane and noted 2.5x energy efficiency for the Ara and Ariane pair. They observed two challenges, one with a scalability bottleneck introduced by VLSU and SLDU, and the other with performance reduction of smaller size problems caused by pairing Ara

plus Ariane with the vector instruction issue rate problem.

The RISC-V soft-core process work by [15] shows a scalable vector extension for the performance optimization of parallel applications. Their vector extension eliminates the vectorized code adaptation requirement upon adjusting the number of computing units for the SIMD soft-core. They targeted ARM SVE compatibility so they used ARM's automatic vectorization compiler. First, they compiled the program to ARM SVE assembly code. Second, they translated the assembly to a RISC-V assembly. Finally, they assembled the RISC-V assembly to RISC-V machine code using the edited GNU assembler. They used 32 vector registers and 16 predicate registers with eight of them for vector-mask control and the other eight for logical operation between them. Their vector instructions have three types including control, load/store, and vector operations. They performed a functional simulation of their implementation in a gem5 simulator.

The RISC-V ISA small float SIMD extension paper by [43] presents a 32-bit RISC-V core for scalar and floating point operations with a data type width of 8-bit and 16-bit. They implemented relevant C/C++ types and GNU compiler editions. Their edition covers the real type extension of the GNU compiler, which is an internal format for floating point types. They included call back functions to convert the internal format to the small floats and tuned the machine modes and rules as well as adding new keywords and conversion rules and adjusting the GCC auto-vectorizer. Their experiments with mixed precision computing shows no accuracy degradation and the results for 8-bit demonstrate execution time improvements of 2.18x and an energy reduction of 50%, whereas for 16-bit the execution time reduction is 1.64x and the energy decrease 30%.

ASSIST [19] is a synthesis framework for a RISC-V core which receives instruction specifications and provides multiple RISC-V processors register transfer level (RTL) implementations. The multi RTL outputs balance the quality-of-result (QoR) metrics with a facilitating custom instruction set and architectural feature analyses. Also, they describe automatic optimization for specific technology and performance. ASSIST has three main parts including an instruction specification interface, architectural synthesis engine, and pipeline schedule autotuner. The instruction interface uses an architecture description language (ADL) in Python for collecting the functional behavior of the instructions. The synthesis engine uses the DAL data and pipeline schedule for architecture generation as Chisel RTL, which is later sim-

ulated. The schedule autotuner receives the measured metrics and optimizes the pipeline schedule. They evaluated more than 60 variations of RTL implementations of in-order RISC-V 32I with different features such as pipeline structures. Their experiments were with machine learning and cryptograph applications and their 32-bit cryptographic ISA extension showed 9.3X faster task execution.

SMURF by [4] is a RISC-V high precision floating point accelerator used for Variable Precision (VP) calculations and covers up to 512 bits of mantissa. They present a RISC-V ISA extension and its design as a 64-bit word-size with pipelined architecture. SMURF is generated with Rocket chip as a RISC-V coprocessor and has two floating point (FP) formats for the internal computations and the main memory, while the format conversion is performed by a load and store unit. Their FPGA implementation has a 50 MHz clock frequency and their ASIC implementation with a 28 nm FDSOI has a 600 MHz clock frequency. They compared their design with a RISC-V 64-bit FP and reported 9 times more area and 12 times more power dissipation and stated that the essential internal memories and the mantissa buffers were the main reason.

The compressed RISC-V ISA work by [25] describes a 32-bit core with a coexisting 16-bit ISA extension which includes a low overhead dual-issue hardware support. Their architecture has six pipeline stages, while the execution stage has substages with variable latency for different instructions. For example, the addition instruction takes one clock cycle but division needs 16 cycles. They observed that RISC-V ISA mainly uses 8 registers with instruction compression which increases the hazards. Thus, they reduced stalls by selective register renaming for instruction compression registers. Also, they implemented a partitioned register file and clock gating. They experimented with a cycle-accurate simulator and analyzed the hardware, reporting similar performance with area and power efficiency in comparison to a super-scalar processor.

The multi precision RISC-V ISA floating point extension study by [17] presents an architecture for IEEE 754-2008 SP numbers which provides a trade-off between accuracy and precision. Their implementation covers eight-core Pulp architecture with their proposed shared unit for the floating point square root or division operation, which supports different precision in 5 to 8 clock cycles. They divide the architecture into three stages consisting of pre-processing, iteration, and post-processing. The pre-processing and post-processing each take one clock cycle while the iteration

stage includes four parallel iteration units which output one mantissa bit. They experimented with DIV/SQRT-intensive algorithms and concluded that there was a possibility for effectiveness and energy saving through precision reduction. Their report shows 36% energy saving and 43.65% performance improvement.

The RISC-V virtual prototype (VP) research by [10] presents an instruction set simulator (ISS) with software debugging, which facilitates functional verification and design space validations. Their design covers the IMAC instruction set with interrupt controllers and peripherals for 32-bit and 64-bit single and multi-cores. In addition, it is possible to add ISA extensions by modifying the decode and execute functions. Their VP design is based on systemC and it has about 12000 lines of C++ code. It is extendable with a generic bus system and TLM 2.0 communication, and covers the GCOV and GDB of the GNU tool chain. Their VP simulation is fast as it has two performance optimizations including a direct memory interface and local time quantums. They provide a HiFive1 board configuration example and experimented with embedded applications, reporting an average of 46 MIPS.

The resource sharing multi processor system on chip (MPSoC) study by [18] describes a RISC-V ISA extension where the instructions execute on shared coprocessing units outside of the processor's data path. They implemented a NoC-based MPSoC with 3x3 mesh topology, i.e., nine tiles where each tile contains a network interface (NI), a router, and a PE. In their design the center tile is the memory surrounded by four processors and four coprocessors. The coprocessors execute the multiplication and division instructions and are accessible by the processors as needed, where the processor uses the NoC for sending the operation packet to the coprocessor and receiving the result packet. They used four scenarios for area, power and performance evaluations and reported negligible hardware and execution time overheads to trade off area and leakage power.

XpulpNN [8] is a RISC-V ISA extension designed for quantized neural network (QNN) applications. It provides SIMD instructions for low-bit-width data types of nibble, i.e., 4-bit and crumb, i.e., 2-bit, which removes the instructions required for data packing and unpacking of QNN as well as an instruction for quantization. They implemented the extension in the RISC-V RI5CY where the quantization unit was added to the execution stage of the pipeline on the PULPissimo platform with 22nm FDX technology. Their report shows insignificant overhead with around 5-fold performance improvement for 4-bit and about 8-fold improvement for 2-bit in

comparison to 8-bit SIMD. They report 2-fold energy efficiency in comparison to commercial ARM architectures and up to 9-fold when compared to the baseline.

Table 2.2 summarizes the reviews. The RISC-V BMI study has the same goal of extending the RISC-V ISA and shows a high speed-up value like the high value obtained in this work. The table has five columns for referencing, stating the scope, depicting the similarity point, presenting the purpose, and the reported results of the reviewed work.

Table 2.2 Summary of RISC-V reviews

| Ref. | Scope                                          | Similarity | Purpose                                  | Results                      |

|------|------------------------------------------------|------------|------------------------------------------|------------------------------|

| [16] | RISC-V BMI extension                           | 4          | RISC-V ISA customization                 | Up to 96.87x speedup         |

| [23] | Non-standard ex-<br>tension simulation         | 2          | Early stage RISC-V core evaluation       | Development time reduction   |

| [40] | Application<br>specific ISA cus-<br>tomization | 2          | Customized HDL generation                | 3 to 4 times speedup         |

| [48] | RISC-V ISA extension analysis                  | 2          | Taped-out RISC-V core                    | Reduction by a factor of 4.6 |

| [9]  | RISC-V ISA extension investigation             | 2          | Implemented<br>RISC-V core               | 10 times speedup             |

| [5]  | RISC-V ISA extension implementation            | 2          | Implemented RISC-V co- processor         | 2.5x energy effi-<br>ciency  |

| [15] | Architecture extension                         | 2          | Implemented RISC-V soft-core process     | Programming method           |

| [43] | RISC-V ISA extension                           | 2          | Implemented RISC-V SIMD extension        | 2.18x and 1.64x speedup      |

| [19] | RISC-V ISA extension simulation                | 2          | RISC-V core syn-<br>thesis framework     | Up to 9x speedup             |

| [4]  | RISC-V ISA extension implementation            | 2          | Variable Precision<br>RISC-V accelerator | 12x power increase           |

| [25] | RISC-V ISA extension                           | 2          | Dual-issue RISC-V core                   | Performance<br>improvement   |

| [17]                  | RISC-V ISA extension        | 2 | Multi-precision<br>RISC-V architec-<br>ture | 36% energy saving          |

|-----------------------|-----------------------------|---|---------------------------------------------|----------------------------|

| [10]                  | RISC-V ISA simulation       | 2 | RISC-V instruction set simulator            | 46 average MIPS            |

| [18]                  | RISC-V ISA extension        | 2 | RISC-V co-<br>processing                    | Area and power reduction   |

| [8]                   | RISC-V ISA extension for NN | 2 | RISC-V QNN customization                    | 9x energy effi-<br>ciency  |

| This work [27] & [29] | RISC-V ISA extension        | 5 | Extending Pop-<br>Count instruction         | 2x performance improvement |

## 2.3 Literature review comparison

The workload modeling studies include similar work such as LSLA [34] and parallel dataflow [12] with similar methodology. Also, the period graph study [3] has related evaluation metric as this work. On the other hand, the difference between the studies lies in the application parallelization, i.e., OpenCL or the platform selection, i.e., the GPU. The ISA extension studies have similarities in the selection of RISC-V ISA although they selected different types of instructions or have different implementations. In this work, the Instruction Set Simulator (ISS) is used where a GNU RISC-V compiler is edited to cover the PopCount instruction with no physical implementation.

## 3 METHODOLOGY

This work targets improvements from two different aspects: improving platform modeling by the means of workload modeling, as well as implementing an RISC-V ISA extension. The applications, tools, input data, platforms, and measurement methods as well as the techniques and platforms utilized are described for each of these aspects.

## 3.1 Workload modeling

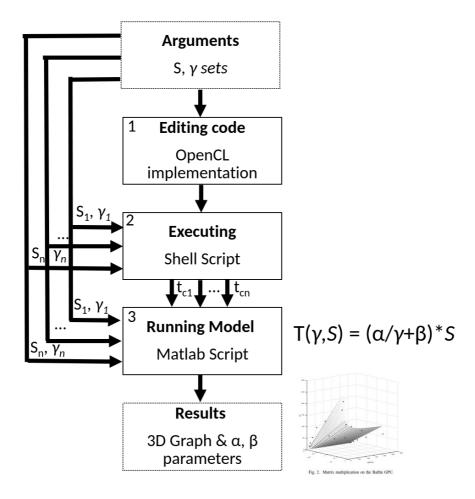

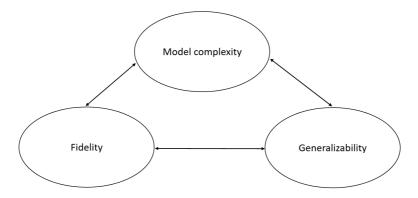

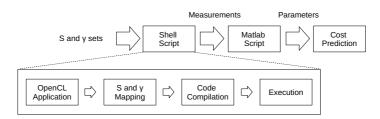

Four representative OpenCL applications were considered including Matrix multiplication, predistortion, Gaussian filtering, and PopCount, which are executed with random data inputs. Two different GPUs which are known as Mali on Odroid XU3 [24] and AMD RX 460, i.e., Baffin [1] on a desktop computer were selected. Two different shell scripts were used for profiling the applications on each of the platforms. One of the shell scripts was used for collecting the execution time data only on the Baffin GPU while the other was used for collecting both the execution time and power dissipation data through a wire connection on the Odroid XU3 platform, as it has built-in power sensors. The collected profiling data was used for studying the workload optimization and proposing the performance and power models presented in this work with a Matlab script. For example, Figure 3.1 shows the stages of the proposed model's utilization on an unknown platform. In this figure, the OpenCL implementation, Shell script, and Matlab script usages are demonstrated in order from stage 1 to 3.

Figure 3.1 Workload modeling method.

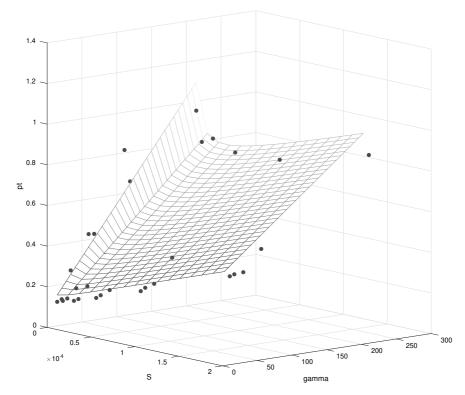

S is the input data quantity,  $\gamma$  is the parallelism factor,  $\alpha$  shows the reciprocal of the slope, and  $\beta$  depicts the intercept.

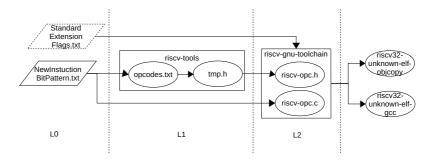

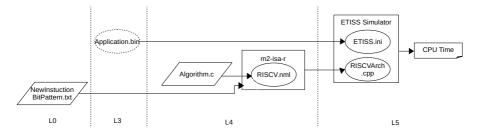

## 3.2 RISC-V ISA extension methods

The RISC-V ISA extension was studied with the PopCount [27] instruction addition to the open source GNU RISC-V compiler. One C implementation of a binarized neural network application known as the vehicle classifier [14] was selected, which is run with camera images of four vehicle types. The modified compiler was used for compiling the C code for the RISC-V ISA assembly that included the PopCount instruction. No commercial RISC-V processor with a hardware implementation of

the PopCount instruction was available thus the Extendable Translating Instruction Set Simulator (ETISS) by [22] was used for exploring the effect of the addition of PopCount, and the ETISS simulator was modified to cover the PopCount instruction.

#### 3.2.1 ETISS simulator

ETISS has multiple ISA support, including RISC-V. It provides semi-automated instruction additions and has a straightforward procedure. Its successful execution results in a simulation and performance data display which could be edited to show more details such as the printing of all of the executed assembly instructions. In addition, as the targeted platform is PULPino [35], the relevant library files are used. The PULPino is an open source RISC-V microcontroller. It is reconfigurable for covering RISCY or the zero-riscy core. The ETISS simulator has the advantage of being open source while its codes can be edited to cover extra functionalities.

## 3.3 Use case applications

The selected applications for the experiments have wide usage areas such as signal processing, wireless communication, or machine learning. They have been selected by their use in other research studies. Verification of the use case is beyond the scope, but it is stated that they are sufficient for the methodology development purposes.

In this study four applications were selected: matrix multiplication, predistortion, Gaussian filtering, and the vehicle classifier. The matrix multiplication, predistortion, Gaussian filtering applications were used in the modeling studies as they are common embedded system applications. Also, the vehicle classifier was used in the ISA extension as it includes a population count instruction. It is a neural network image processing application which detects vehicle types according to pictures of them.

# 4 WORKLOAD MODELING OF HETEROGENEOUS PLATFORMS

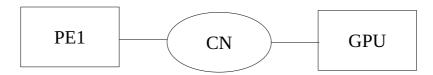

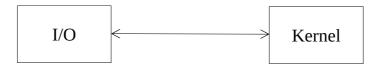

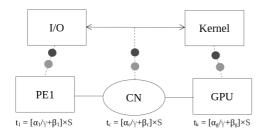

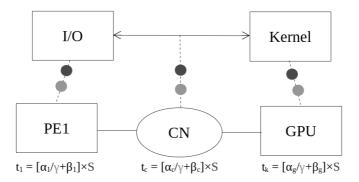

The LSLA [34] concept covers multi-core CPU platforms while many current platforms also include a GPU. Such heterogeneous platforms require an extension to the LSLA in order to cover the GPU. The proposed model is named GSLA which adds a new parameter for parallelism and support to OpenCL applications. OpenCL applications use the CPU as the host for the GPU. Thus, a simple MoA was designed for the investigations. Figure 4.1 depicts the MoA, which consists of two processing elements called PE1 and GPU and one communication node named CN. The PE1 is the host device of the OpenCL applications, which communicates with the GPU through CN.

OpenCL applications include the kernel code which runs in the GPU and the main code in the CPU, including OpenCL API calls and I/O management. Figure 4.2 illustrates two computations named I/O and Kernel and presents their communication as a two-sided arrow. The execution of the application shown by MoC on the platform presented by MoA is depicted by mapping the MoC to the MoA where the dash lines show the mapped computations on the relevant processing element or communication node. The execution costs such as execution time or power dissipation are shown as tokens in the arcs on the dash lines. Figure 4.3 shows the mapping of the model of the computation on the model of the architecture.

The total execution cost is presented in Equation 4.1, which is the sum of the

Figure 4.1 Model of Architecture.

Figure 4.2 Model of Computation.

Figure 4.3 Mapping of MoC on MoA.

costs of the processing elements and the costs of the communication nodes.  $\lambda$  shows the scaling coefficient between the processing units and the communication cost.  $T_p$  depicts the collection of processing element tokens while  $T_c$  represents the collection of the communication node tokens. Also, t represents any token.

$$cost(A,P) = \sum_{t \in T_p} cost(t, map(t)) + \lambda \sum_{t \in T_c} cost(t, map(t))$$

(4.1)

In this study, the execution costs of the OpenCL applications are examined and two models are presented: one for performance and the other for the power dissipation of the system.

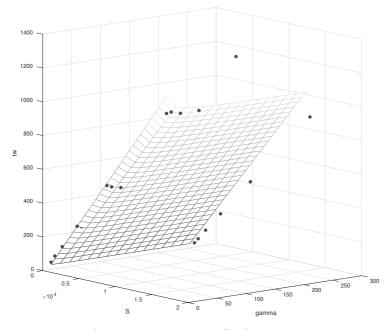

# 4.1 Performance modeling

The execution time of the OpenCL applications can be modeled with GSLA [32] as a simple linear model as the sum of the costs of the three elements of the MoA, i.e., the cost functions of PE1, CN, and GPU. The total execution time is presented as  $(t_w)$  in Equation 4.2 as the sum of the execution costs of the kernel, i.e.,  $(t_k)$  plus the execution cost of the processing elements, i.e.,  $(t_k)$  plus the execution costs of the

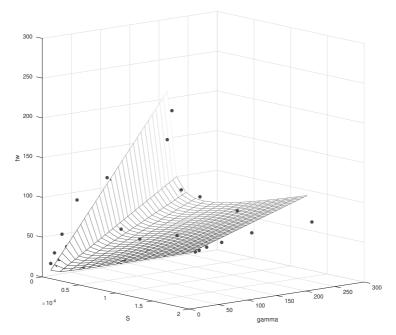

**Figure 4.4** An example of the S and  $\gamma$  variables.

communication node, i.e.,  $(t_c)$ .

$$t_w = t_k + t_1 + t_c (4.2)$$

The cost functions are presented in Equations 4.3, 4.4, and 4.5 where they all have two variables named S and  $\gamma$  and two parameters named  $\alpha$  and  $\beta$ . Here, S is the input data quantity and  $\gamma$  is the parallelism factor. Figure 4.4 shows an example of S and  $\gamma$  variables with values of 512 and 8. Also, in the models the  $\alpha$  shows the reciprocal of the slope, and  $\beta$  depicts the intercept.  $\alpha$  and  $\beta$  are coefficients of the equations and they are calculated for each specific system.

$$t_k(\gamma, S) = (\alpha_g/\gamma + \beta_g) \times S \tag{4.3}$$

$$t_1(\gamma, S) = (\alpha_1/\gamma + \beta_1) \times S \tag{4.4}$$

$$t_c(\gamma, S) = (\alpha_c/\gamma + \beta_c) \times S \tag{4.5}$$

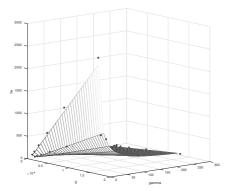

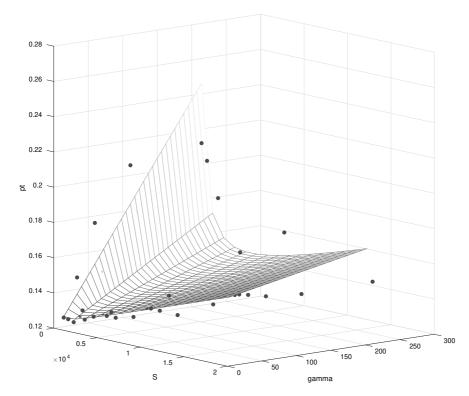

## 4.2 Power modeling

The power dissipation of the OpenCL applications are representable by our proposed power model, as shown in Equation 4.6. The total power dissipation of the

Figure 4.5 Trading off between different aspects of the modeling.

OpenCL application is denoted by  $P_t$  and has two variables named S and  $\gamma$  and three parameters named  $a_{gpu}$ ,  $b_{gpu}$ , and  $c_{gpu}$ .  $a_{gpu}$ ,  $b_{gpu}$ , and  $c_{gpu}$  are coefficients of the equations similar to the  $\alpha$  and the  $\beta$  coefficients of the 4.3, 4.4, and 4.5 equations. In the experiments, the  $a_{gpu}$  parameter was a fixed constant value for all the tested applications, which suggests it is static power dissipation. On the other hand, when the  $a_{gpu}$  parameter is removed, i.e., having the same equation for both performance and power, the R-squared value decreases. The R-squared value is a metric for correlation calculation and here it is used for evaluating the proposed model. It is a value between 0 and 1 and shows a better correlation as its value gets closer to 1.

$$p_t(\gamma, S) = a_{gpu} + b_{gpu}S + c_{gpu}S/\gamma \tag{4.6}$$

# 4.3 Proposed models

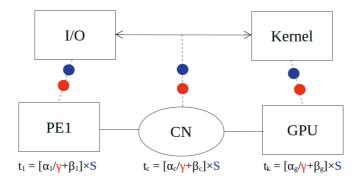

This modeling approach has practical benefits. The simplicity of the model and its generalizability together with its evaluation with a fidelity metric provide a useful modeling approach. The concept is illustrated in Figure 4.5.

Equations 4.1-4.6 show the results of the workload modeling of this work. Here two workload models are proposed for the execution of OpenCL applications on GPUs. The selection criteria of these models is based on the complexity and fidelity trade-off, i.e., introducing powerful but simple models with the lowest possible complexity.

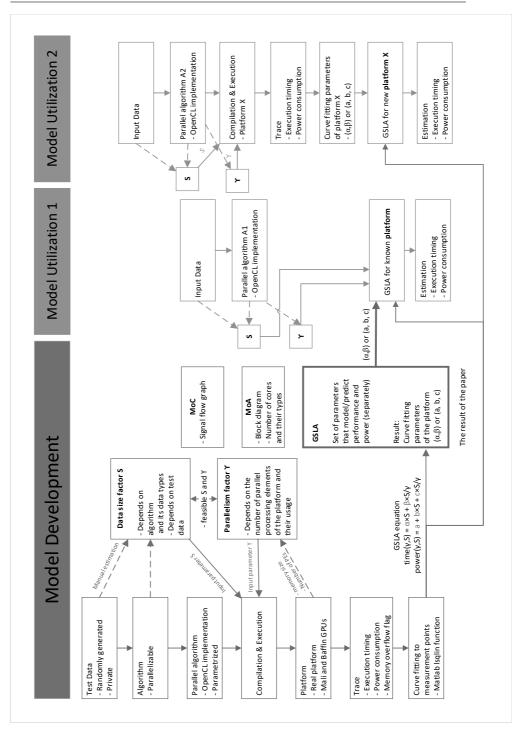

Figure 4.6 presents the development and the utilization of the models. The model

development section in blue shows the model creation phases step by step, whereas the model usages in green depict the two utilization approaches of the presented time and power models.

In model development, first the test data and a parallelizable application are selected, taking the data size into consideration. Also, a MoC for the application and a MoA for the platform are designed as schematics. Then, the OpenCL implementation of the parallel application is made. Later, the application is edited to receive the S and  $\gamma$  parameters as command line inputs that are affected by the input data size of the application, the parallelization capacity of the platform, and the relation of S to  $\gamma$ . The compiled application is executed and the correctness of the outputs is checked. Then, the application with considered S and  $\gamma$  values is run on the selected platform and the profiling data is collected. The data includes the execution time and power dissipation without any runtime error. Later, the Lsqlin function in Matlab is used to fit the average of the collected data points. After multiple use case modeling, GSLA models for time and power as well as curve fitting parameters are proposed.

In the model utilization for a known platform, first the input data is considered and the OpenCL implementation of a parallelizable application is carried out. Then, the application is edited to receive the S and the  $\gamma$  parameters as inputs. Later, the application is run on the known platform, thus profiling is not required and the same  $\alpha$  and  $\beta$  parameters for the time equation and the same a, b, and c parameters for the power equation are used. The models show the estimated execution time and power dissipation values for the selected input data size and the parallelization factor.

In the model utilization for an unknown platform, first the OpenCL implementation of the selected parallelizable application is implemented, taking the input data size of the application and the parallelization factor into consideration. Then, the application is run on a reference platform and the profiling data is collected. The collected data about the execution time and the power dissipation is used in the Matlab script to provide the new platform specific parameters. Later, the equations with the calculated parameters are used to estimate the execution time and power dissipation values of the application. In addition, these parameters could be reused for similar applications or platforms. If only the MoC of the application is available, i.e., no physical platform or MoA to execute the code on, the previously collected data of similar platforms could provide initial guesses, e.g., expecting similar cost function

Figure 4.6 Development and utilization workflow.

parameters and similar graphs. In this case, the model utilization would be for the known platform but it would be an initial estimation rather than the actual usage of the proposed model, i.e., the S and the  $\gamma$  parameters and the arguments to calculate the execution time or power dissipation from the cost function formula are required.

# 4.4 Population count analysis

Further analysis of the proposed performance and power models is investigated from the aspect of neural network applications. The popularity of the neural network applications and suggested performance improvements in recent studies, e.g., [14] motivated the selection of the PopCount algorithm in this study. The PopCount instruction has high utilization in the binary convolution of neural network applications.

#### 4.4.1 PopCount instruction

The PopCount algorithm receives a string of zeros and ones and outputs a number showing the number of ones in that string. There are multiple implementations for the PopCount calculation. Here three of them have been selected for further investigations with OpenCL kernel code. The selected algorithms include a native OpenCL function call 1, LLVM implementation 2, and the adder tree method 3. These kernel codes are disassembled by editing the 4th parameter of the *clBuildProgram* call in the OpenCL code which resulted in five files outputs. One of the files, i.e., *.isa* contains the assembly code equivalent of the kernel code.

```

Algorithm 1 OpenCL Kernel Native Instruction

```

```

__kernel void

PopC (

__global int * C,

__global int * A,

{

C[get_global_id(0)] = popcount(A[get_global_id(0)]);

}

```

The experiments were performed on the AMD Baffin GPU and the disassembling

#### Algorithm 2 OpenCL Kernel LLVM Implementation [21]

```

__kernel void

PopC_2(

__global int * C,

__global int * A,

{

int x = A[get_global_id(0)];

x = x - ((x >> 1) & 0x5555555);

x = ((x >> 2) & 0x33333333) + (x & 0x33333333);

x = (x + (x >> 4)) & 0x0f0f0f0f;

x = (x + (x >> 16));

C[get_global_id(0)] = (x + (x >> 8)) & 0x0000003F;

}

```

#### Algorithm 3 OpenCL Kernel Adder Tree Method

```

__kernel void

PopC_3 (

__global int * C,

__global int * A,

{

int x = A[get_global_id(0)];

ushortx_l = x;

ushortx_h = (x >> 16);

int res_l = popcount(x_l);

int res_h = popcount(x_h);

C[get_global_id(0)] = res_l + res_h

}

```

results showed 23 assembly instructions 4 for the native OpenCL function call, 36 assembly instructions 5 for the LLVM implementation, and 27 assembly instructions 6 for the adder tree method. All disassembly codes have the same first 16 and 2 last instructions which are grayed out for easier comparison.

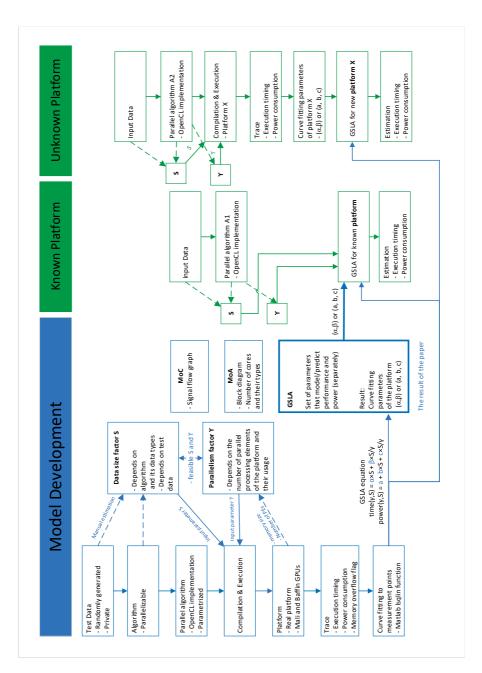

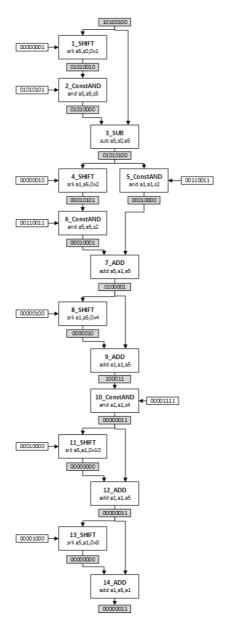

The compiler converts the C code to the assembly according to the platform. For example, Figure 4.7 shows the 14 logical operations of the LLVM implementation of the PopCount algorithm and Algorithm 5 shows its equivalent assembly on an AMD Baffin GPU. Instruction number 18 in the algorithm is the first instruction, i.e., 1 SHIFT in the graph. The instructions are the same up to number 10 in the

graph, i.e., 10\_ConstAND which is the number 27 in the assembly. Then, there is an extra  $v\_add\_u32$  instruction in the assembly. Later, it continues the same up to number 12 in the graph, i.e., 12\_ADD which is followed by an extra  $v\_add\_u32$  instruction again. The last two instructions in the graph, i.e., 13\_SHIFT and 14\_ADD are converted into the three instructions of  $v\_mov\_b32$ ,  $v\_addc\_u32$ , and  $v\_and\_b32$  in the assembly. Consequently, the 14 logical operations are converted into 18 assembly instructions for the real platform.

### Algorithm 4 OpenCL Kernel Native Instruction Disassembly

```

1: s load dword s0, s[4:5], 0x04

2: s waitent lgkment(0)

3: s and b32 s0, s0, 0x0000ffff

4: s mul i32 s0, s0, s8

5: v add u32 v0, vcc, s0, v0

6: s load dwordx2 s[0:1], s[6:7], 0x00

7: s load dwordx4 s[4:7], s[6:7], 0x30

8: s waitent lgkment(0)

9: v add u32 v0, vcc, v0, s0

10: v mov b32 v1, s1

11: v addc u32 v1, vcc, 0, v1, vcc

12: v lshlrev b64 v[0:1], 2, v[0:1]

13: v add u32 v2, vcc, s6, v0

14: v mov b32 v3, s7

15: v addc u32 v3, vcc, v3, v1, vcc

16: flat load dword v2, v[2:3]

17: v add u32 v0, vcc, s4, v0

18: v mov b32 v3, s5

19: v addc u32 v1, vcc, v3, v1, vcc

20: s waitent vment(0) & lgkment(0)

21: v bcnt u32 b32 v2, v2, 0

22: flat store dwordv[0:1], v2

23: s endpgm

```

#### Algorithm 5 OpenCL Kernel LLVM Implementation Disassembly

```

1: s load dword s0, s[4:5], 0x04

2: s waitent lgkment(0)

3: s and b32 s0, s0, 0x0000ffff

4: s mul i32 s0, s0, s8

5: v add u32 v0, vcc, s0, v0

6: s load dwordx2 s[0:1], s[6:7], 0x00

7: s load dwordx4 s[4:7], s[6:7], 0x30

8: s waitent lgkment(0)

9: v add u32 v0, vcc, v0, s0

10: v mov b32 v1, s1

11: v addc u32 v1, vcc, 0, v1, vcc

12: v lshlrev b64 v[0:1], 2, v[0:1]

13: v add u32 v2, vcc, s6, v0

14: v mov b32 v3, s7

15: v addc u32 v3, vcc, v3, v1, vcc

16: flat load dword v2, v[2:3]

17: s waitcnt vmcnt(0) & lgkmcnt(0)

18: v lshrrev b32 v3, 1, v2

19: v and b32 v3, 0x55555555, v3

20: v sub u32 v2, vcc, v2, v3

21: v lshrrev b32 v3, 2, v2

22: v and b32 v2, 0x33333333, v2

23: v and b32 v3, 0x333333333, v3

24: v add u32 v2, vcc, v3, v2

25 : v lshrrev b32 v3, 4, v2

26: v add u32 v2, vcc, v3, v2

27: v and b32 v2, 0x0f0f0f0f, v2

28: v add u32 v2, vcc, v2, v2 src0 sel: WORD 1

29: v lshrrev b32 v3, 8, v2

30: v add u32 v2, vcc, v3, v2

31: v add u32 v0, vcc, s4, v0

32: v mov b32 v3, s5

33: v addc u32 v1, vcc, v3, v1, vcc

34: v and b32 v2, 63, v2

35: flat store dword v[0:1], v2

36: s endpgm

}

```

Figure 4.7 PopCount LLVM Logical Operations.

#### Algorithm 6 OpenCL Kernel Adder Tree Method Disassembly

```

1: s_load_dword s0, s[4:5], 0x04

2: s waitent lgkment(0)

3: s and b32 s0, s0, 0x0000ffff

4: s mul i32 s0, s0, s8

5: v add u32 v0, vcc, s0, v0

6: s load dwordx2 s[0:1], s[6:7], 0x00

7: s load dwordx4 s[4:7], s[6:7], 0x30

8: s waitent lgkment(0)

9: v add u32 v0, vcc, v0, s0

10: v mov b32 v1, s1

11: v addc u32 v1, vcc, 0, v1, vcc

12: v lshlrev_b64 v[0:1], 2, v[0:1]

13: v add u32 v2, vcc, s6, v0

14: v mov b32 v3, s7

15: v addc u32 v3, vcc, v3, v1, vcc

16: flat load dword v2, v[2:3]

17: s waitcnt vmcnt(0) & lgkmcnt(0)

18: v bfe u32 v3, v2, 0, 16

19: v lshrrev b32 v2, 16, v2

20: v bcnt u32 b32 v3, v3, 0

21: v bcnt u32 b32 v2, v2, 0

22: v_add_u32 v2, vcc, v2, v3 src0 sel: WORD 0src1 sel: WORD 0

23: v add u32 v0, vcc, s4, v0

24: v mov b32 v3, s5

25: v addc u32 v1, vcc, v3, v1, vcc

26: flat store dword v[0:1], v2

27: s endpgm

}

```

## 4.4.2 PopCount modeling

The *OpenCL* implementation of the PopCount algorithm is coded where the kernel receives an array of integer numbers and returns the PopCount results of each number. The kernel is designed as a two dimensional indexing space where the first dimension is a fixed value of 16, meaning that the kernel works on arrays which have 16 elements. The second dimension value is a variable presenting the  $\gamma$ , i.e., the

parallelization factor showing the number of vectors that the kernel performs the computations on. Also, S, i.e., work size is implemented as the iterations of a *for* loop calculated as S divided by  $\gamma$ . For example, when  $\gamma$  is 8 and S is 512, the kernel receives 8 arrays each with 16 values, which in total becomes 128 numbers when repeating the calculations 64 times. See Figure 4.4.

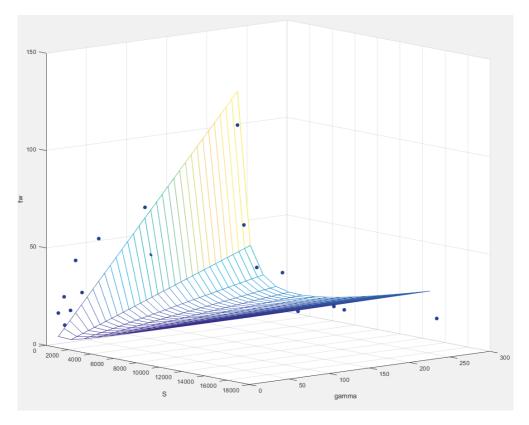

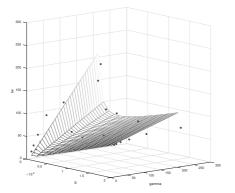

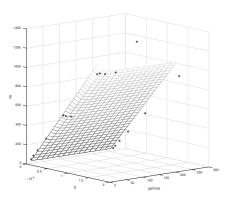

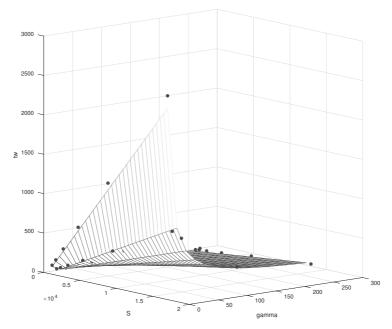

The shell scripts are used for benchmarking on the Baffin GPU and have nested loops with the program execute command with two command line arguments values for S and  $\gamma$ . The argument sets in the scripts have the same values as the previous experiments in order to provide comparable results. For benchmarking, the same S and  $\gamma$  sets were used for all applications.  $S \in \{512, 1024, 2048, 4096, 8192, 16384\}$  and  $\gamma \in \{8, 16, 32, 64, 128, 256\}$ . The measured values are read by the *Matlab* script of the proposed performance model which prints the parameters, the fidelity value, and the graph. See Figure 4.8. The blue dots in the figure are the average of 10 iterations for each relevant S and  $\gamma$  value.

Table 4.1 presents the PopCount parameters in addition to the algorithms of the three previous studies on the Baffin GPU. Table 4.2 shows the Kendall tau coefficient of the studied algorithms on the Baffin GPU. It is an association evaluation metric which shows the strength of the association with a value between -1 and 1. The zero value would show independence between the model and its measurements. As the value gets closer to 1 it shows better correlation, i.e., is more desirable. In these tables B1 is the matrix multiplication, B2 is the predistortion, B3 is the Gaussian filtering, and B4 is the PopCount algorithm.

Table 4.1 Parameters of functions.

| Application | $\alpha_g$ | $\beta_g$ | $\alpha_1$ | $\beta_1$ | $\alpha_c$ | $\beta_c$ |

|-------------|------------|-----------|------------|-----------|------------|-----------|

| B1          | 0.001      | 0.008     | 0.000      | 0.004     | 0.005      | 0.068     |

| B2          | 0.005      | 0.049     | 0.002      | 0.003     | 0.060      | 0.000     |

| В3          | 0.000      | 0.051     | 0.002      | 0.000     | 0.004      | 1.074     |

| B4          | 0.000      | 0.004     | 0.000      | 0.000     | 0.002      | 0.054     |

Table 4.2 Fidelity values.

| Application | Fidelity GSLA | Fidelity LSLA |

|-------------|---------------|---------------|

| B1          | 0.88          | 0.75          |

| В2          | 0.90          | 0.92          |

| В3          | 0.91          | 0.62          |

| В4          | 0.79          | 0.55          |

Figure 4.8 Population count graph.

$\gamma$  is the parallelization factor, S is the work size, and  $t\,w$  is the time in milliseconds.

#### 4.4.3 Modeling conclusion

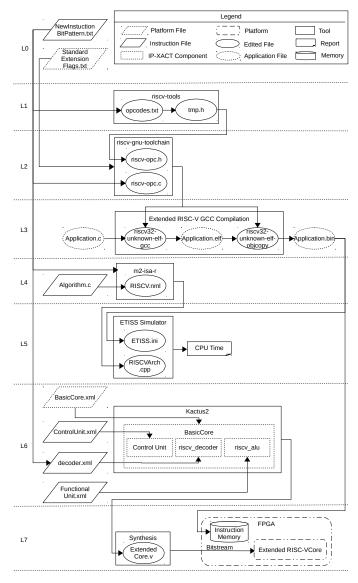

In this study, four applications were considered in terms of performance and power dissipation. The proposed GSLA model was examined for its correctness and feasibility with the fidelity metric. The results of the experiments showed a value between 0.79 and 0.91 for performance modeling on the Baffin platform. Thus, these observations suggest that the utilization of the model is feasible. In case of parallelizable applications like matrix multiplication, predistortion, and Gaussian filtering, the fidelity results are good while in case of the worst case, i.e., PopCount, it shows an expected reduction.