Tuukka Haapakumpu

# **X-PROPAGATION IN RTL SIMULATION**

Faculty of Information Technology and Communication Sciences Masters thesis November 2022

### ABSTRACT

Tuukka Haapakumpu: X-Propagation in RTL Simulation Masters thesis Tampere University Electrical engineering November 2022

RTL simulations are a major part of hardware development and verification. RTL simulation is the most commonly used method of verifying the correct operation of hardware designs. Verification is often run parallel to the hardware design and verification is a major part of SoC projects even before any physical releases.

RTL simulators depict and read logical values usually with '1' and '0'. In some situations the simulators cannot always tell what value is going into a component, then it will assign it an 'X'. Problems arise from the fact that there is no state 'X' for a signal in physical devices. If the simulator just assigns a '1' or a '0' to an X-value there is a significant chance of it being wrong which will cause errors later down the line.

X-propagation in a RTL simulator is a way of making the X-value run through the design to see where it ends up. This is done while configuring the simulator to make the 'X' end up in the least amount of places while trying to cover all places where there might be ambiguity. Simulations can be run in an X-pessimistic or X-optimistic way, where a pessimistic simulation will produce more X-values

In this thesis simulator A and its X-propagation plugins were tested. The aim was to assess the simulators ability to catch X-related errors and find any issues or restrictions that would hinder its use. The testing was done by running basic tests to see the finer details of the X-propagation plugin of each simulator and a larger test done on a design provided by the company. The basic tests were six different basic design simulations: an if-else statement, a case statement, a random number generator, a state machine, a RAM circuit and a shift register. The environment used in the simulations was provided by the company which restricted the choice of simulators.

The basic tests were run with and without X-propagation modules enabled on simulator A. The basic simulations went mostly as expected with a few surprises. Overall the simulator performed mostly as expected and without issues.

The larger simulations were run using simulator A. The X-value tracing function of simulator A was used to find sources of X-values and the testcases were run first without any X-propagation enabled and then with the X-propagation plugin enabled in relevant modes. Unfortunately there was no big difference in simulation results between modes.

In the simulator analysis some differences were found between simulation and the user guide. A notable bug was found in simulator A which the simulation vendor was informed about. While testing it was found that the simulator could be used in X-propagation simulations especially with larger designs.

Keywords: RTL simulation, X-propagation, Simulator, Verification

The originality of this thesis has been checked using the Turnitin OriginalityCheck service.

# TIIVISTELMÄ

Tuukka Haapakumpu: X-Propagaatio RTL Simulaatiossa Diplomityö Tampereen yliopisto Sähkötekniikka Marraskuu 2022

RTL-simuloinnit ovat tärkeä osa laitteistokehitystä ja verifiointia. RTL-simulointi on yleisimmin käytetty menetelmä laitteistosuunnitelmien oikean toiminnan todentamiseen. Verifiointi suoritetaan usein rinnakkain laitteistosuunnittelun kanssa, ja verifiointi on tärkeä osa SoC-projekteja jo ennen fyysisiä julkaisuja.

RTL-simulaattorit käsittelevät loogisia arvoja, jotka ovat yleensä '1' ja '0'. Joissakin tilanteissa simulaattorit eivät kuitenkaan pysty kertomaan, mikä arvo komponenttiin on menossa. Tällöin simulaattori antaa sille arvon 'X'. Fyysisissä laiteissa ei ole tilaa 'X' signaalille, mistä syntyy ongelmia. Jos simulaattori muuttaa arvon 'X' arvoon '1' tai '0', on suuri mahdollisuus että se on väärässä, mikä aiheuttaa myöhemmin virheitä.

X-propagointi RTL-simulaattorissa on tapa saada arvo 'X' kulkemaan suunnittellun laitteen läpi simulaatiossa, ja selvittää mihin se päätyy. Tämä toteutetaan konfiguroimalla simulaattori siten, että arvo 'X' päätyy mahdollisimman harvoihin paikkoihin. Samalla pyritään kattamaan kaikki paikat, joissa voi olla mahdollisia epäselvyyksiä. X-propagoinnilla simulaatiot voidaan suorittaa joko X-pessimistisesti tai X-optimistisesti. Pessimistinen simulaatio tuottaa simulaatioon enemmän arvoja 'X' kuin optimistinen.

Tässä työssä testattiin simulaattoria A ja sen X-propagointiliitännäisiä. Tavoitteena oli arvioida simulaattorin kykyä havaita X-arvoja ja löytää niiden käyttöä haittaavia virheitä tai rajoitteita.

Testaus suoritettiin ajamalla perustestejä simulaattorin X-propagointi -liitännäisen hienompien yksityiskohtien selvittämiseksi. Tämän lisäksi suoritettiin laajempi testi, joka tehtiin yrityksen toimittamalla alustalla. Perustesteissä simuloitiin kuutta erilaista peruskomponenttia: if-else -lause, case-lause, satunnaislukugeneraattori, tilakone, RAM-piiri ja siirtorekisteri. Yritys tarjosi simulaatioissa käytettävän ympäristön, mikä rajoitti simulaattoreiden valintaa.

Perustestit ajettiin ensin ilman X-propagointimoduuleja ja tämän jälkeen niiden ollessa käytössä. Perustesteissä keskityttiin simulaattorin A X-propagointitiloihin. Perussimuloinnit sujuivat enimmäkseen odotetusti lukuun ottamatta muutamia yllätyksiä. Kokonaisuudessaan simulaattori A suoriutui perussimuloinneista lähes odotetusti ja ilman ongelmia.

Suuremmissa simulaatioissa simulaattori A tarjosi mahdollisen X-arvon jäljittämiseen sopivan toiminnon. Tämä X-arvo aiheuttaa simulaation epäonnistumisen, tai on muulla tavoin mielenkiintoinen aiheuttamatta epäonnistumista. Testitapaukset ajettiin ensin ilman, että X-propagointitila oli käytössä. Tämän jälkeen ne ajettiin käyttäen X-propagointitilaa. Valitettavasti simulointituloksissa ei ollut suurta eroa tilojen välillä.

Simulaattorin ominaisuuksien analysoinnissa havaittiin joitakin eroja oppaassa esitetyssä ja odotetussa toiminnassa. Simulaattorissa A havaittiin virhe, joista ilmoitettiin simulaattorin toimittajalle. Testauksen aikana todettiin, että simulaattoria voidaan käyttää X-propgointisimulaatioissa, erityisesti suurissa simulaatioissa.

Avainsanat: RTL simulaatio, X-propagointi, Simulaattori, Verifiointi

Tämän julkaisun alkuperäisyys on tarkastettu Turnitin OriginalityCheck -ohjelmalla.

### PREFACE

The writing of this thesis was a major undertaking but at the same time a good learning experience. Working on this thesis has shown me the importance of tenacity and cooperation, more than any other project I have embarked upon. For the subject I would like to thank Risto Sterling and my supervisor on the company side Petri Kukkala. On the vendor side I would like to thank Juho Järvinen for the technical support throughout this project.

I would like to thank my supervisors Sakari Lahti and Timo Hämäläinen for the patience and support which made this project possible. I would also like to thank my family for the support and motivation they gave me and for this undertaking. Without you this thesis would never have been finished. A special thanks to all my friends without whom these years would have been unbearable, who I have been able to vent my frustrations regarding this project and especially for the unforgettable experiences we have shared. Hope there are still many to come.

In Tampere, 22nd November 2022

Tuukka Haapakumpu

# CONTENTS

| 1  | Intro | oduction                                         | 1  |

|----|-------|--------------------------------------------------|----|

| 2  | X-Pi  | ropagation                                       | 3  |

|    | 2.1   | Verification and RTL simulation                  | 3  |

|    | 2.2   | Basics of X-propagation                          | 5  |

|    | 2.3   | Formal X-propagation verification                | 7  |

|    | 2.4   | RTL X-propagation simulation                     | 8  |

|    | 2.5   | Code and simulation examples                     | 0  |

|    | 2.6   | Problems in X-Propagation Simulations            | 2  |

|    |       | 2.6.1 X-Optimism                                 | 2  |

|    |       | 2.6.2 X-Pessimism                                | 3  |

|    |       | 2.6.3 Solutions                                  | 4  |

| 3  | Basi  | ic Design Simulations                            | 5  |

|    | 3.1   | Simulation setup 1 - If-else and Case statements | 5  |

|    |       | 3.1.1 X-propagation with simulator A             | 6  |

|    | 3.2   | Simulation setup 2 - Random number generator     | 0  |

|    |       | 3.2.1 X-propagation with simulator A             | 2  |

|    | 3.3   | Simulation setup 3 - State machine               | 4  |

|    |       | 3.3.1 X-propagation with simulator A             | 6  |

|    | 3.4   | Simulation setup 4 - Random Access Memory        | 9  |

|    |       | 3.4.1 X-propagation with simulator A             | 1  |

|    | 3.5   | Simulation setup 5 - Shift register              | 3  |

|    |       | 3.5.1 X-propagation with simulator A             | 5  |

| 4  | Larg  | ge Design Simulations                            | 8  |

|    | 4.1   | X-propagation for larger designs                 | 8  |

|    | 4.2   | Simulation setup                                 |    |

|    |       | 4.2.1 X-propagation with simulator A             | 9  |

| 5  | Ana   | lysis of Results                                 | 8  |

|    | 5.1   | Small design simulations                         | .8 |

|    | 5.2   | Large design simulations                         | 0  |

| 6  | Con   | clusion                                          | 2  |

| Re |       | nces                                             | 4  |

# **LIST OF FIGURES**

| 2.1  | Simple testbench and DUT                                                 | 4     |

|------|--------------------------------------------------------------------------|-------|

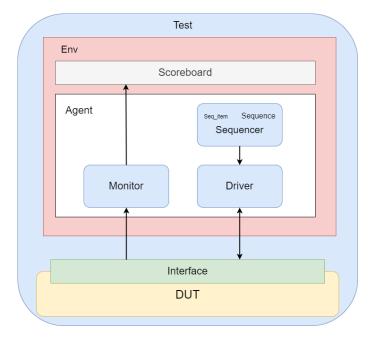

| 2.2  | Simple UVM testbench [6]                                                 | 5     |

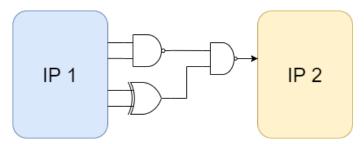

| 2.3  | Logic between IP blocks                                                  | 8     |

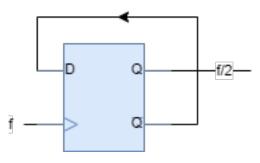

| 2.4  | Clock divider                                                            | 13    |

|      |                                                                          |       |

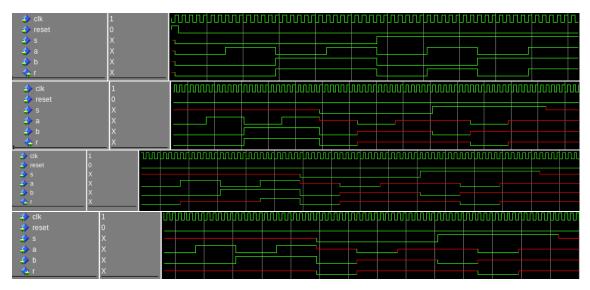

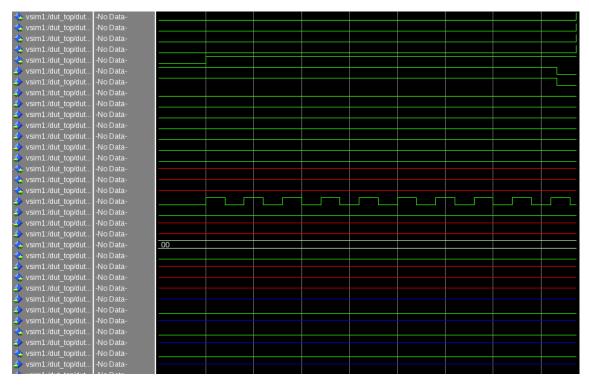

| 3.1  | If-else statement waveform in normal and X-propagation plugin operation. | 17    |

| 3.2  | Case statement waveform in normal and X-propagation plugin operation.    | 19    |

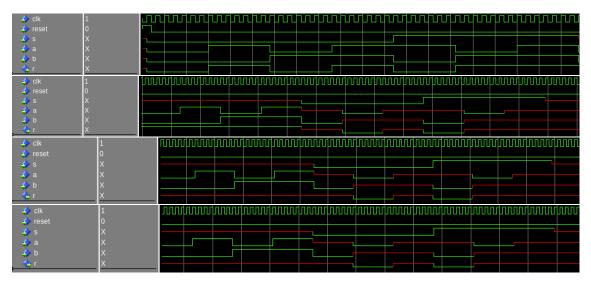

| 3.3  | Random number generator in normal and X-value operation without the      |       |

|      | X-propagation plugin.                                                    | 23    |

| 3.4  | Random number generator in resolve and pass mode X-propagation plugin    |       |

|      | simulation.                                                              | 24    |

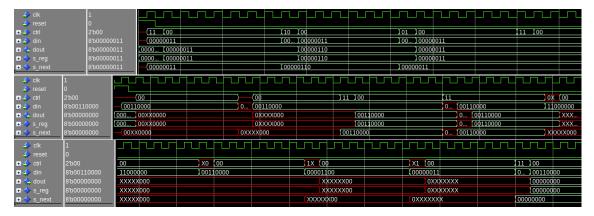

| 3.5  | State machine simulation without X-propagation plugins                   | 27    |

| 3.6  | State machine in resolve mode X-propagation simulation.                  | 28    |

| 3.7  | State machine in pass mode X-propagation simulation                      | 28    |

| 3.8  | State machine simulation waveform with variable input.                   | 29    |

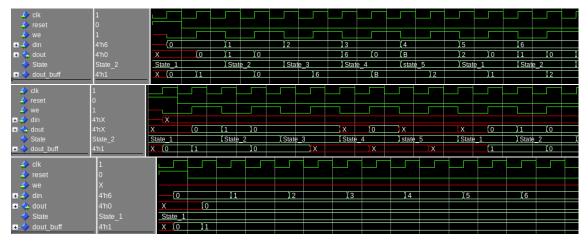

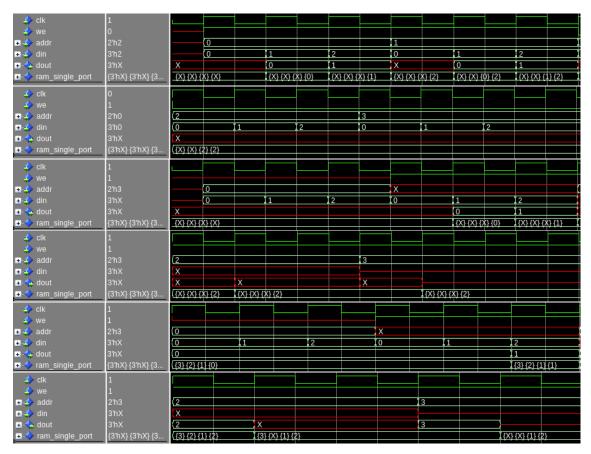

| 3.9  | RAM simulation without X-propagation plugins.                            | 32    |

| 3.10 | RAM simulation in resolve mode X-propagation.                            | 33    |

| 3.11 | RAM simulation in pass mode X-propagation.                               | 33    |

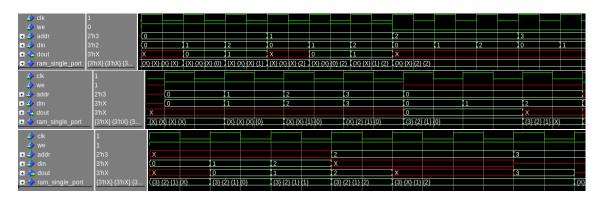

| 3.12 | Shift register simulation without X-propagation plugins                  | 35    |

| 3.13 | Shift register simulation in resolve mode simulation.                    | 36    |

| 3.14 | Shift register simulation in pass mode simulation.                       | 37    |

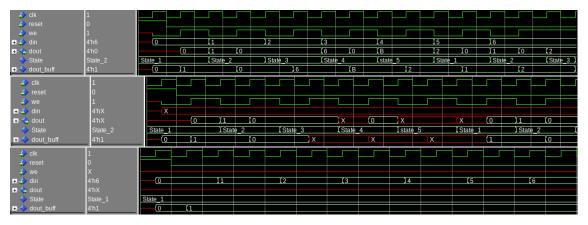

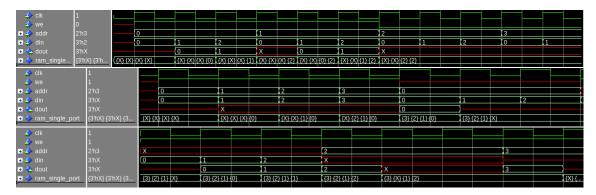

| 4.1  | Sanity check waveform in normal simulation                               | 40    |

| 4.2  | Sanity check waveform for resolve mode simulation                        | 41    |

| 4.3  | Sanity check waveform for pass mode simulation                           | 42    |

| 4.4  | Sanity check schematic for X tracing                                     | 42    |

| 4.5  | Sanity check schematic for X tracing                                     | 43    |

| 4.6  | Normal testfeature simulation waveform                                   | 45    |

| 4.7  | Testfeature resolve mode simulation waveform                             | 46    |

| 4.8  | Testfeature resolve mode simulation waveform                             | 47    |

|      |                                                                          | • • • |

# LIST OF TABLES

| 2.1 | X-value propagation through a multiplexer (edited from [11])                     | 6  |

|-----|----------------------------------------------------------------------------------|----|

| 2.2 | X-value operations in Verilog (edited from[12])                                  | 7  |

| 2.3 | If-else simulations for simulator A X-propagation plugin modes (edited from[14]) | 11 |

| 2.4 | Case simulations for simulator A X-propagation plugin modes (edited from[14])    | 12 |

| 3.1 | If-else statement simulation results, s=X                                        | 17 |

| 3.2 | If-else statement simulation results, s=0                                        | 8  |

| 3.3 | If-else statement simulation results, s=1                                        | 18 |

| 3.4 | Case statement simulation results, s=X                                           | 19 |

| 3.5 | Case statement simulation results, s=0                                           | 20 |

| 3.6 | Case statement simulation results, s=1                                           | 20 |

| 3.7 | State machine operators                                                          | 26 |

| 3.8 | Shift register commands without the X-propagation plugin                         | 35 |

# LIST OF PROGRAMS AND ALGORITHMS

| 2.1 | If-else statement in Verilog. [14]          |

|-----|---------------------------------------------|

| 2.2 | Case statement in Verilog. [14]             |

| 3.1 | If-else statement                           |

| 3.2 | Case statement                              |

| 3.3 | Random number generator. [21]               |

| 3.4 | State machine                               |

| 3.5 | Single port RAM. [21]                       |

| 3.6 | Shift register implementation in VHDL. [21] |

| 4.1 | If statement                                |

| 4.2 | First fixes                                 |

| 4.3 | Elsif statement                             |

| 4.4 | New elsif statement                         |

# LIST OF SYMBOLS AND ABBREVIATIONS

- ASIC Application Specific Integrated Circuit

- FPGA Field Programmable Gate Array

- GUI Graphical User Interface

- HDL Hardware Design Language

- IP Intellectual Property

- LSB Least Significant Bit

- MSB Most Significant Bit

- RAM Random Access Memory

- RTL Register Transfer Level

- SoC System on Chip

- UVM Universal Verification Methodology

- VHDL Very High Speed Integrated Circuit Hardware Design Language

### **1 INTRODUCTION**

Verification is an integral part of developing new System on Chip (SoC) devices such as Application Specific Integrated Circuits (ASIC) and Field Programmable Gate Arrays (FPGA) [1]. Especially, as the size and performance of designs are increasing, the importance of finding possible errors in the design rises [2]. Simulating and using formal verification methods when done properly will increase the amount of errors that are caught before moving forward in the design [1]. Unfortunately all errors cannot be uncovered only by simulating due to the limitations of the verification tools used.

There are many ways that errors might unintentionally be introduced into the design and a single tool might not take all of them into account. This makes it exceptionally important to have a more diverse set of tools for the project design verification. One part of design verification is the evaluation of ambiguity in the design which causes X-values. X-values propagate through designs when the simulator cannot decide the output value from the input values given, which is common when one or more input values are X-values.

Simulator vendors are aware of the problems caused by X-propagation, so many of them offer tools to tackle it. Different tools made by different vendors will ultimately have some differences on how they operate and those differences will lead to some differences in results and performance between them.

The purpose of this thesis is to research and evaluate a simulation tool for the propagation and its ability to catch unknown X-values through different SoC hardware designs. The simulator in use is referred to as simulator A. The simulation modes include operation in X-optimistic and X-pessimistic modes. Additionally the purpose of this thesis is to help develop a methodology or methodologies for X-propagation simulation to be used at the company.

Different modes were compared by simulating basic hardware designs and complex Intellectual Property (IP) block designs. Smaller design units included designs like a random number generator (RNG) and a shift register. For the larger IP block case a design with known problems with X-propagation will be used.

The thesis is structured as follows: Chapter 2 covers the basic concepts of X-propagation in Register Transfer Level (RTL) design simulation and sheds a light on some problems with X-propagation simulations. Chapter 3 gathers simulation setups and results for basic designs using different simulation settings. Chapter 4 covers the simulations for a larger IP. Chapter 5 is focused on the analysis of the simulation results and in Chapter 6 are the

conclusions.

### 2 X-PROPAGATION

As SoC designs grow ever larger verification remains an important part of SoC project flow. The goal of verification is to find and rule out possible errors early in the design lest they hamper the design later during the project. Verification flow runs in parallel with the project design flow and ought to be run at various levels of the design. Already in 2008 70 % to 80 % of design effort was taken up by verification, so a large portion of project labour costs are made up of finding errors in the design [3].

#### 2.1 Verification and RTL simulation

Verification is the umbrella term for multiple types of testing and analysis, such as formal methods and simulation. The goal of verification is to ensure the design works as planned. Due to large project sizes, SoC verification requires many different verification tools and methodologies. [2] For small designs, verification can be just an afterthought without many problems. For larger and more complex projects, the design team always has to know how it will be tested and verified [4].

Verification methodologies include simulation, timing analysis, formal verification and hardware emulation. Simulation is one of the most, if not the most, used type of verification but does not verify the lack of errors and is very time consuming. Timing analysis checks the timing of the design. Meaning checking for delays. Formal verification is another commonly used verification method. It uses mathematical models to verify designs. Formal methods are covered more thoroughly in section 2.3. [4]

SoC Verification operates in many different levels of abstraction. Since modern hardware designs have become more complex, including millions upon millions of transistors, no human or computer can realistically analyze the design directly. Different abstraction levels are used to balance between simulation time dictated by the complexity of the design and its accurate representation. In digital system design, four abstraction levels are considered. Going up this starts at the transistor level continuing into gate-level, register transfer level, and finally the processor level. Higher-level abstractions omit much of the data whereas low-level abstractions add more detail to it. [4]

Register transfer level is the digital design abstraction level that models digital circuits in terms of data flowing between hardware registers. This is an abstraction level higher from gate-level design. RTL design includes three primary parts, registers, combinatorial logic components like adders and lastly clocks all of which are written usually in Hardware Design Languages (HDL) like Very High Speed Integrated Circuit Hardware Design Language (VHDL) or Verilog. [4] In large designs, where parts of the design are produced by an outside vendor or a part of the design is reused, a black-box model of the part may be used to speed up design and simulation time. Additionally, the testbenches used in RTL simulation can be reused in top-level simulation increasing verification throughput. [2]

In RTL simulations the Design Under Test (DUT) is checked to comply with the goals of the project. As an input to the DUT, a vector of inputs is fed by a testbench, and the output of the DUT is then compared to the expected output by a testbench or a testcase.[5] Nowadays especially in larger designs, testbenches are usually written in some verification language like SystemVerilog using Universal Verification Methodology (UVM). To ensure better verification results, it is common practice for different teams of engineers to design the DUT and the testbench since the DUT designer might be blind to some mistakes.

Figure 2.1. Simple testbench and DUT

In Figure 2.1 we can see a simple representation of a DUT and its testbench. In the figure from the left, an example subset is fed to the DUT inputs and the corresponding outputs are coming out on the right. It is important to note that not all inputs can be seen directly affecting the output, or it might take more time to see the effect. The basic working principle of a UVM test is essentially the same as in a VHDL or Verilog testbench.

Figure 2.2. Simple UVM testbench [6]

In Figure 2.2 we can see that a simple UVM testbench architecture. The testbench consists of a top class for the test responsible for testbench configuration and stimulus instantiating, among others. The env or environment is a container for high-level components like the agent and scoreboard, an agent that handles UVM component grouping. The monitor monitors interface signals which are made into a packet and sent to for example the scoreboard. The scoreboard receives data and compares it to the expected output, the sequencer routes data packets to and from the UVM sequence, and a driver drives packet data from the sequence to the DUT, the interface for the DUT.

In verification, coverage is a metric for measuring when the verification is ready [7]. The coverage of verification is mostly determined by the quality of the testbench. For wider coverage, the testbench must check the DUT with a large number of random input values according to design constraints to cover a wide array of inputs. Random data vectors might not cover all possible input combinations. This means that some input data combinations are run as directed tests. Directed tests are run, by feeding the design known input values that might cause errors. Such cases are the edge, corner, and boundary cases. In the edge case, input data on the extreme limits of operation, is fed into the DUT, in the corner case the DUT operates outside normal operating parameters, and in the boundary case one or more input is outside the operating limits. When errors are found in the DUT by the verification team, the hardware designers modify the design, and the cycle continues.[5]

### 2.2 Basics of X-propagation

HDLs represent unknown logic values using X-values. When the simulator used to test the design can't decide if the logic value is '1', '0' or high impedance 'Z'; it will assign an

X. On the other hand X can be specifically assigned to depict a don't-care states, which can be confusing at times and therefore should not be used interchangeably. X logic values are often caused by system or component level resets, gated clock systems or other events that introduce uncertainty. [8]

Depending on the simulation setup, there can be one of two problems. Firstly the simulator might convert an X into an exact value like '1' or '0' by executing code that is too optimistic, this is called X-optimism. Secondly the simulator might generate too many X-values by executing code that is too pessimistic, this is called X-pessimism. [9] Xoptimism and X-pessimism will be covered more in depth in the next chapter.

As design sizes have continued to increase, energy saving designs have become more commonplace. When a part of the chip is powered down, its output can be initialized into an X-state. These X-states can propagate through the design and create more uncertainty through some coding methods or excessive X-pessimism in powered-up circuits. [10]

Large reset trees are not viable for large designs, and implementing them would, in most cases, prove expensive. Especially with FPGA designs where the usable area is restricted by the chip size and resets would take space from the functional design. This will cause some of the registers in a design not to be connected to a reset and may cause unknown values to be generated during startup as they are uninitialized, for example. In addition, uninitialized latches can be a major source of X-values. X-value sources are covered in section 2.4 [11]

Understanding how X-values move through the simulated logic helps designers and verification engineers find and debug possible problems. Basic knowledge of X-value sources helps the designers and verification engineers dig deeper and find the sources of the problems caused by ambiguity.

It is helpful to look at simple hardware components prone to X-value problems. One component often mentioned is a multiplexer declared with an if-else statement. Table 2.1 shows how a simple multiplexer propagates and X-value through itself.

| ENA | A | В | OUT |

|-----|---|---|-----|

| Х   | 0 | 0 | 0   |

| Х   | 0 | 1 | Х   |

| Х   | 1 | 0 | Х   |

| Х   | 1 | 1 | Х   |

Table 2.1. X-value propagation through a multiplexer (edited from [11])

The table shows that the first three cases resolve as expected, but when the A and B inputs are both '1', by any logic, the output should be '1', as it is in silicon, but the language semantics turn it to an X.

Looking at gate level operation can shed light on operation in the RTL level. Table 2.2 shows how some simple Verilog operators handle X-values in a standard simulation.

| NOT |   | AND       | OR |          | XOR |           | XNOR |            |   |

|-----|---|-----------|----|----------|-----|-----------|------|------------|---|

| ~X  | Х | (X AND X) | Х  | (X OR X) | Х   | (X XOR X) | Х    | (X XNOR X) | Х |

|     |   | (0 AND X) | 0  | (0 OR X) | Х   | (0 XOR X) | Х    | (0 XNOR X) | Х |

|     |   | (1 AND X) | Х  | (1 OR X) | 1   | (1 XOR X) | Х    | (1 XNOR X) | Х |

Table 2.2. X-value operations in Verilog (edited from[12])

The tables 2.1 and 2.2 show that in many cases, the X-values might propagate through simple logic elements, which might lead to a significant amount of lost information down the line. This information can be otherwise normal function of the logic or erroneous data, which would lead to the logic working improperly. The tendency of X-values to propagate is affected by X-optimism and pessimism and if an X-propagation simulation is running. [13] The simulation in question seems to be running somewhat pessimistically.

X-propagation simulations are more time consuming since the propagating X-values need to be calculated for the proceeding steps of the simulation and can mask critical fault data and information. The loss of faulty data caused by this, would lead to a decrease in verification coverage as fewer faults are caught. This in turn, means that X-propagation should not be enabled in all simulations, especially if simulation time is of concern. X-values are very useful for finding problems, but the downside is that it may hinder other functions and, as a result, should be used sparingly.

Masking correct data and possible bugs with X-values will complicate debugging processes as more simulation and code/error review time is needed to catch problems. As other valid values than '1' or '0' don't exist in hardware, their functionality will differ from Xpropagation simulations that have effectively 4 states: '1', '0', high impedance 'Z' and 'X'. This will cause difficulties in comparing simulation results with lab measurement results. Analyzing the X-propagation simulation waveform is labour-intensive manual inspection that can't be automated yet. This requires a level of understanding of the design, so simulation and analysis can't be done by everyone. [9]

The handling of X-values might be different between simulators. A simulator may calculate all possible outputs when an X is encountered at the input, or it may change the HDL semantics in a specific way. [14] This is the main reason simulation times are longer on X-propagation simulations. On rarer occasions the X-values cause the simulation to enter an endless loop which is not a problem caused by the simulator but the design itself.

### 2.3 Formal X-propagation verification

As verification is a significant bottleneck in design flows, different options to verify the designs have been proposed as an alternative to classical simulations. One alternative

group of methods are formal verification methods. In formal verification rigorous mathematical models are used to verify the correctness of algorithms behind the design under test. [15]

Formal methods are used in several areas like symbolic checking and symbolic simulation. Formal methods may increase the coverage of the design resulting in more bugs uncovered that may have been left undiscovered by just simulating. In many applications formal verification is cheaper than simulation since there is no need to write a separate testbench. [15]

Formal methods are used for checking designs for X-propagation errors. Validation of X-states is one of the top applications for formal methods used by the industry. In the case of X-propagation, formal analysis has some distinct advantages. They can pinpoint sources for the X-states that could have been masked due to X-optimism in RTL simulation. Additionally, formal methods can thoroughly evaluate the DUT behaviour for X-states propagating and possibly corrupting critical values. [16]

Using formal methods for X-propagation in large designs at the scale of the top-performing FPGA chips is not viable at the moment. On smaller IPs, formal methods are still viable, but due to the high demand for computing power, top-level verification requires a different solution. [17]

Additionally, if there is combinatorial logic between IP modules, the top-level design cannot be represented by chaining the IP modules. This implies that a formal model of the top-level design would not be the sum of all IP-level models. The logic between the blocks might be so complex that it warrants its own model, or it might be as simple as a few gates, so a universal solution to this problem is not easy.

Figure 2.3. Logic between IP blocks

In Figure 2.3 we can see a representation of logic between IP-blocks. This logic should be accounted for when testing the overall functionality of the larger design. Since it is located between IP blocks, it might not be taken into account when formally verifying a design unless it is added to the model.

#### 2.4 RTL X-propagation simulation

X-values in RTL simulation are very useful for representing the uncertainty of some values, although they introduce some challenges to be considered. The propagation of X- values through RTL and logic-gate level designs requires considerations lest they cause significant problems later. These problems might arise during simulation or in hardware as the difference in results compared to the simulations. [10]

RTL simulation often cannot indicate the problems related to the lack of X-propagation. Xvalues can cause differences between gate-level, and RTL simulation and X-propagation tools can save time in debugging those differences and the design problems behind them. [18]

In most situations, simulators don't propagate X through the design but handle these cases optimistically, resulting in possible errors being missed. To find these errors in RTL simulations, many vendors offer X-propagation plugins to their simulators. With these tools, the verification engineer can set the level of X-pessimism and X-optimism to represent the physical implementation of the design. This system is not flawless or instant, for that matter but will require iterations of tweaks to the X-optimism or X-pessimism and possibly modifying the underlying HDL.

As stated in the last section, formal methods are more effective at catching errors for most applications, for example, verifying a single IP block. Although not perfect, RTL simulation is still a viable tool for top-level X-propagation simulation in large designs. Although Formal methods might come out on top concerning single IP-block verification, RTL simulation will do well to complement formal methods to increase verification coverage even more. RTL simulation considers the possible logic between separate IP blocks and thus increases the coverage.

There are multiple ways the simulator can generate and propagate an X. Although all X-sources cannot be completely removed e.g. because of restrictions on reset trees, one can simplify the work required down the line to correct errors created by X-values. This can be done by using coding principles that focus on avoiding X-states to begin with or by focusing on writing the code in a way that does not propagate the generated X.

The best way to handle possible X-state problems and limit the propagation of X-values is to avoid X-value generation in the first place. To better understand how to avoid X-values, the engineer needs to understand the mechanics causing them. The sources might be intentional or a byproduct of the decision made due to, for example, size or timing constraints. Some sources of X include:

- · Uninitialized variables and registers

- · Operations resulting in unknown results

- Forced X-values

- · Some timing violations

- · Undriven and floating wires and wires with multiple drivers

These are only a few examples on how a simulator might generate an X. [10]

Assuming the designer or verification engineer is using the proper simulators and X-

propagation plugins while running RTL simulations, they can find and address issues originating from initialized parts of the design or other X-sources. The issue posed by standard simulation X-optimism is addressed by propagating the X-values forward in time. [19]

With regards to the propagation of X forward through time three pathways are most prominent. These are if and case statements and conditional assignments. This means that, for example if a conditional statement gets an input of X, it will be propagated to the output by the simulator X-propagation plugin by changing the language semantics. The X will affect the following logic similarly and can be seen in the simulator waveform. If these X-values continue to be unaddressed, they may cause the simulation to fail. A few of these failures are presented in chapter 5. [19]

Simulators used by the SoC industry are highly advanced and their basic functions will be comparable. In complex designs, the major functional difference will be the overall performance, not the simulation results.

There are multiple HDL simulators to choose from, and even covering all or most of them would make the scope of this thesis too large. This thesis will focus on one simulator to keep the length of this text reasonable.

Since the underlying algorithms are not available to the designers the major differences seen by them are the price, the look, platform support on some simulators and the look and feel of the simulator GUI. With this in mind, the primary criteria from the engineers' standpoint are the simulator's usability and the supported platforms. On a company level, the main criteria would be the price and the simulator's performance.

Looking at how the simulator handles X-propagation is important for understanding the usability of it. Vendors do not release the underlying algorithms for simulator X-value handling, although the working principles are listed in their user guides.

For smaller designs gate-level simulations and pseudo-exhaustive 2-state methods are used to find problems regarding X-propagation. These simulation methods become too slow and processing power consuming to be used in larger designs, as they cover only a portion of the verification flow. [18]

### 2.5 Code and simulation examples

If-else and case statements are often mentioned as sources of X-propagation problems. Looking deeper into how the simulator handles X-values in different simulation modes is useful for understanding how the simulation is actually working.

In this section the X-propagation simulation modes for the simulator is examined. The modes range from very X-optimistic to pessimistic. The possibility of changing the severity of optimism and pessimism enables the design to be studied more thoroughly.

Simulator A user guide does not give separate code examples between VHDL and Ver-

ilog, so it can be assumed that the simulation outcome will be the same regardless of the HDL used. Simulator A provides options to modify the simulation behaviour with X-propagation plugin options to match silicon as close as possible.

Simulator A has different X-propagation plugin modes of operation. Simulator A Xpropagation plugin modes are none, trap, resolve and pass. With these modes, the designer can set the wanted level of X-optimism and pessimism to fit the situation.

X-propagation plugin mode 'none' doesn't modify the simulation of the design instance, even though the X-propagation plugin is enabled. This will make the simulation run as if the X-propagation plugin was not enabled.

Mode 'resolve' is the simulator A X-propagation plugin mode that more closely resembles the silicon behaviour. 'Resolve' mode is not as optimistic as standard simulation and not as pessimistic as 'pass' mode. This will uncover problems with ambiguity but doesn't mask unrelated bugs in the design as much.

Mode 'pass' is the X-pessimistic approach to simulation. This will propagate the X-values through and will more likely cause X-related errors and hide design bugs. 'Pass' mode will turn some non-ambiguous values into unknown values.

The vendor does not provide enough information on how the 'trap' mode functions, so it will be omitted from this comparison. The only table provided in the user's manual 'trap' mode seems to result in an output similar to 'none' mode and basic RTL simulation, with no explanation provided [14].

A simple if-else statement is as follows. This would result in a multiplexer component.

```

if (ENA)

OUT = B;

else

OUT = A;

```

```

Listing 2.1. If-else statement in Verilog. [14]

```

In table 2.3, the truth table for simulator A X-propagation plugin modes is represented when running an X-propagation simulation for the if-else statement.

**Table 2.3.** If-else simulations for simulator A X-propagation plugin modes (edited from[14])

| ENA | А | В | pass | resolve | RTL sim | silicon |

|-----|---|---|------|---------|---------|---------|

| X   | 0 | 0 | Х    | 0       | 0       | 0       |

| X   | 0 | 1 | Х    | Х       | 0       | ?       |

| Х   | 1 | 0 | Х    | Х       | 1       | ?       |

| Х   | 1 | 1 | Х    | 1       | 1       | 1       |

From table 2.3, it can be seen that the resolve mode represents the silicon behaviour the closest. When the control signal is X and other inputs are the same, the output takes the value of the inputs. When the input values don't match, the X is propagated to the output.

A simple case statement written in Verilog is as follows. This will result in a simple multiplexer when instantiated.

Case (ENA) 1 'b0 : OUT = A; 1 'b1 : OUT = B; *Listing 2.2.* Case statement in Verilog. [14]

Table 2.4 is the truth table for simulator A X-propagation plugin modes for simulating the case statement simulation.

| Table 2.4. | Case simulations for simulator A X-propagation plugin modes (edited |

|------------|---------------------------------------------------------------------|

| from[14])  |                                                                     |

| ENA | Α | В | pass | resolve | RTL sim | silicon |

|-----|---|---|------|---------|---------|---------|

| Х   | 0 | 0 | Х    | 0       | 0       | 0       |

| Х   | 0 | 1 | Х    | Х       | 0       | ?       |

| Х   | 1 | 0 | Х    | Х       | 1       | ?       |

| Х   | 1 | 1 | Х    | 1       | 1       | 1       |

As seen from table 2.4, when the control signal is X, the behaviour of pass mode and standard RTL simulation is too pessimistic and optimistic respectively, while resolve mode represents silicon operation the closest. Additionally, when looking at other cases like latch and flip-flop statements, resolve mode seems to represent silicon behaviour the closest [14].

### 2.6 Problems in X-Propagation Simulations

All simulators are running models of the actual silicon behaviour. This means that no simulation is an exact match to the design when tested in the lab. The difference between X-propagation simulation and silicon is that in silicon, there is no such thing as an X. In this section some of the major problems in X-propagation simulations are reviewed. Knowing about the shortcomings of simulators will make verification easier and faster.

### 2.6.1 X-Optimism

X-optimism means the simulator handles X-values too optimistically, resulting in 'known' two-state values of '1' or '0' being assigned when the simulation result should be un-known. This would inadvertently hide X-value-related bugs in the design. Standard RTL

simulation operations are intrinsically X-optimistic. X-optimism can be hard to detect and debug since the X-values 'disappear' as they are changed into 'known' values. Finding the bugs in the design caused by overly optimistic simulation can be extremely difficult, and forcing X-values into known values means the cause of the X-value is hidden [20]. These design bugs can be caught with secondary tools, or at a later stage of the design and verification process. In a worst-case the bugs would go unnoticed until the design is tested in actual silicon.

A simple example of X-optimism in standard simulation done in SystemVerilog is an AND gate with inputs of '0' and an X that will result in an output of '0' [10]. When either '0' or '1' ANDed with an X, the output must be 'X'. The same applies in the case of an OR gate.

X-optimism is not always a bad thing. In cases when the operation of the silicon is ambiguous, an optimistic approach is the one closest to the operation of the silicon. The worst thing an optimistic approach can do is mask the ambiguity of silicon behaviour as if no problem exists.

#### 2.6.2 X-Pessimism

X-pessimism means the simulator handles X-values too pessimistically, resulting in an excessive amount of X-values being assigned and propagated. X-pessimism happens when the simulation is driving an output of X when, in actuality there is no uncertainty in the simulation or the physical silicon. This, in turn can hide bugs in the design and result in data loss. Some examples of this were covered in the previous chapter.

X-pessimism allows X-values to propagate through the design, allowing them to be more easily detected, debugged and corrected. The downside is that the X-values mask data, which makes the debugging of data harder. As the X-values propagate downstream, their source might be far away. Finding the output X-value source in an X-pessimistic simulation might take much work and time.

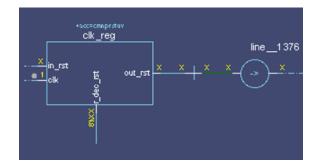

X-pessimism can cause problems with simulation by itself. A simulation might lock up because of X-values where possibly ambiguous values in silicon wouldn't cause this problem. One example of this is a simple clock divider seen in Figure 2.4.

Figure 2.4. Clock divider

At device startup, the clock dividers flip-flop will get either the value '1' or '0'. When

simulating, this will be interpreted as an X. The X will be fed back to the input of the inverter, which will pessimistically propagate an X into the input of the flip-flop. This means, the divider will be stuck in a loop of X output. As the output of this circuit will be stuck as an X, the registers downstream controlled by the circuit in Figure 2.4 will be locked in an X-state in a pessimistic simulation. Physical design does not have this problem. [10]

#### 2.6.3 Solutions

Some have suggested getting rid of X-values in simulation completely to remove the problem of dealing with X optimism and X-pessimism [10]. This would most probably lead to differences in simulation results and silicon behaviour since X-values tell the verification engineer that the simulator doesn't know if the value in silicon will become a '1' or a '0'. The appearance of an X indicates that something is wrong with the design with respect to ambiguity during simulation or silicon operation.

Omitting just some X-values in simulations would help in situations such as the circuit lockup discussed previously. Using SystemVerilog offers the possibility of mixing 2-state values and 4-state variables. The default value for uninitialized 2-state variables is '0', which doesn't represent the behaviour in silicon accurately. Powering up with all variables in the same value is extremely unlikely. Mixing 2- and 4-state values makes it possible to set the values that would otherwise erroneously lock up in 2-state values while keeping other values ambiguous. This is a more accurate representation the silicon behaviour. [10]

Some simulators offer a possibility of separating from the simulation standards of Verilog, VHDL, and SystemVerilog by using X-propagation rules specific to the simulator used. This is not offered by every simulator. These are the modes discussed in the previous chapter.

In some cases, it is possible to modify the design in a way that fewer X-values appear due to X-pessimism. One solution is to add resets to registers that don't need it, but as discussed before, that is not a very realistic choice due to size constraints in large designs, especially when using FPGAs. In some cases changing from synchronous to asynchronous reset will reduce X-pessimistic propagation-related problems. [19]

The testbench can be set to feed non-X-values into the design. As a universal solution this is not very realistic. For example, if the designer wants to simulate the design behaviour at device power up. This can be used to force values known to stay unambiguous to match the silicon behaviour.

The best solution would be to find the proper balance of pessimism and optimism that matches silicon behaviour. At the moment, it seems to demand too much computing resources to implement an exact model into RTL simulations. Alternatives for this are X-propagation tools which mimic the behaviour of silicon.

# **3 BASIC DESIGN SIMULATIONS**

In this chapter, simple designs are simulated for X-propagation in different modes. The simulations are run with a UVM top level, using SystemVerilog, and DUTs written using VHDL. The purpose of the simple designs is to test behaviour of X-values in low-level cases.

Understanding how X-propagation occurs in simple designs helps the verification engineer tackle larger designs. Larger and more complex designs most likely include at least some if not most or all of the simpler designs. Minor differences in simple design simulations can cause major differences in large scale simulations.

Some special emphasis is given to state machines and different data types since they have been non-functioning in previous iterations of X-propagation simulation plugins. The state machine used in this thesis has logic within. These include: logic ports, such as AND, OR and XOR gates.

The random number generator, singe port RAM and shift register VHDL codes are based on the designs made by Meher Krishna Patel. [21] The designs themselves are not under evaluation.

#### 3.1 Simulation setup 1 - If-else and Case statements

In the first simulation setup a multiplexer circuit is simulated. The simulation setup is the same as the examples in chapter 1. The if-else and case statements will be simulated to check if there are any discrepancies or unexpected differences compared to the results given in the user guides.

The circuit is fed data from the UVM testcase. The data set is very simple, hence the operation can be verified easily. Since the circuit is a multiplexer, the interesting signal considering uncertainty is the control signal. This is due to the fact that the control signal is the only signal used in all possible signal combinations.

A notable distinction between the if-else and case statement simulations compared to the other simulations in this chapter is that they are not synchronous simulations and include no registers. This means the focus is on the selection of input signals.

The different X-propagation simulation modes will be differentiated in the results of the simulations, similarly as in chapter 2. As the results of the simulations will most likely

follow along the lines of the user guide, the analysis will be lighter than the following simulations.

For the if-else statement the VHDL code is as follows.

```

entity if_else is

Port (s : IN std_logic;

a : IN std_logic;

b : IN std_logic;

r : OUT std_logic);

end if_else;

architecture BEHAVIORAL of if_else is

begin process (s, a, b)

begin if (s = '1') then

r <= a;

else

r <= b;

end if;

end process;

end;</pre>

```

#### Listing 3.1. If-else statement.

For the case statement the VHDL code is as follows.

```

entity X_CASE is

Port (s : IN std_logic;

a : IN std_logic;

b : IN std_logic;

r : OUT std_logic);

end X_CASE;

architecture BEHAVIORAL of X_CASE is

begin process (s, a, b)

begin case s is

when '0' => r <= a;

when '1' => r <= b;

when others => null;

end case;

end process;

end;

```

Listing 3.2. Case statement.

#### 3.1.1 X-propagation with simulator A

Simulator A simulator is used to simulate the above circuits for X-propagation. For both statements, the most important signal is 's'. As this signal controls the output directly, an X-value here will affect the output the most. First, the designs will be simulated using known values in different sequences. After this has been done, the designs can be

simulated with X-values in different signals to see how the values affect the regular RTL simulation.

First, the if-else statement is tested with a sequence of known values to check that the design works properly and to get baseline results to which the X-value simulations can be compared. The effect of the input X-values on the output is examined separately and combined.

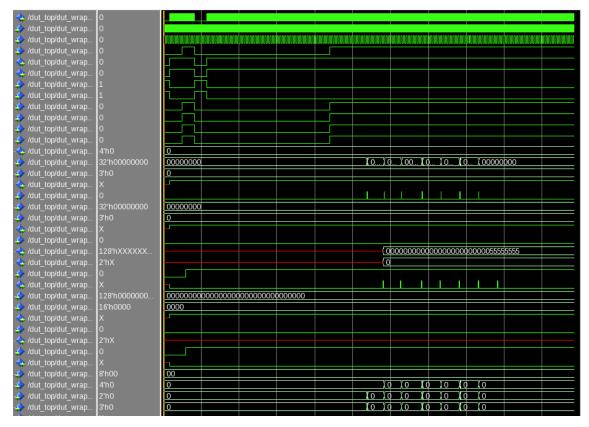

The normal operation simulation is done by feeding different combinations of signals into the DUT in sequence. The if-else statement simulation is done by feeding signal combinations into the DUT, where at least one of the signals is ambiguous. The input and output waveforms for the known-value simulation and X-value simulations without the X-propagation plugin, in resolve mode, and in pass mode for the if-else statement are represented in figure 3.1. The first part of the figure is the normal operation simulation, the second part is the X-value simulation, the third is the resolve mode simulation, and the last is the pass mode simulation. In the waveform, picture 's' is the control signal, 'a' and 'b' are the input signals, and 'r' is the output signal.

Figure 3.1. If-else statement waveform in normal and X-propagation plugin operation.

The simulation results are combined in tables 3.1, 3.2 and 3.3 separated by the value of the 's' signal.

|   | Nor | mal |   |   | Resolve |   |   |   | Pass |   |   |  |  |

|---|-----|-----|---|---|---------|---|---|---|------|---|---|--|--|

| s | а   | b   | r | s | а       | b | r | S | a    | b | r |  |  |

| X | 0   | 0   | 0 | Х | 0       | 0 | 0 | Х | 0    | 0 | Х |  |  |

| X | 1   | 0   | 0 | x | 1       | 0 | Х | X | 1    | 0 | Х |  |  |

| X | 0   | 1   | 1 | X | 0       | 1 | Х | X | 0    | 1 | Х |  |  |

| X | 1   | 1   | 1 | Х | 1       | 1 | 1 | X | 1    | 1 | Х |  |  |

Table 3.1. If-else statement simulation results, s=X

|   | Nor | mal |   |   | Res | olve | ) | Pass |   |   |   |

|---|-----|-----|---|---|-----|------|---|------|---|---|---|

| S | а   | b   | r | s | а   | b    | r | s    | а | b | r |

| 0 | Х   | 0   | 0 | 0 | X   | 0    | 0 | 0    | X | 0 | 0 |

| 0 | 0   | Х   | Х | 0 | 0   | Х    | Х | 0    | 0 | Х | Х |

| 0 | Х   | Х   | Х | 0 | X   | Х    | Х | 0    | Х | Х | Х |

**Table 3.2.** If else statement simulation results, s=0

Table 3.3. If-else statement simulation results, s=1

|   | Nor | mal |   |   | Res | olve |   | Pass |   |   |   |

|---|-----|-----|---|---|-----|------|---|------|---|---|---|

| s | а   | b   | r | s | а   | b    | r | s    | а | b | r |

| 1 | Х   | 0   | Х | 1 | Х   | 0    | Х | 1    | Х | 0 | Х |

| 1 | 0   | Х   | 0 | 1 | 0   | Х    | 0 | 1    | 0 | Х | 0 |

| 1 | X   | Х   | Х | 1 | Х   | Х    | Х | 1    | Х | Х | Х |

As seen from the first part of figure 3.1, the if-else statement works as expected. When the control signal 's' is low, the output is dictated by the input signal 'b', and when the control signal is high, the output signal is dictated by input 'a'.

When examining the second part of figure 3.1, we can see how the X-values in the input affect the output differently with respect to each other. When the control signal 's' is set as X, the simulator interprets it as low. When the control signal is low, the output is set as the same as the 'b', and when 's' is high, the output is set as 'a'.

When running the if-else simulation in trap mode, the simulation waveform does not differ from the non-X-propagation plugin simulation. This was not a surprise, as this was implied in the user guide. [14] When running the resolve mode, the simulation part with no X-values introduced can be omitted since it is unchanged from the non-X-propagation plugin simulation.

When examining the third waveform in figure 3.1, it can be seen that the resolve mode has changed how the simulator handles X-values. When the control signal 's' is X, the output value is set to X when the input values are not the same, and the correct value can't be determined. When the control signal is 1 or 0, the output value is set as the represented input value.

The effect of the pass mode is evident when examining the last part of figure 3.1. The output of the circuit stays as X when the control signal is X. When the control signal can be determined, the output acts in the same way as in the previous simulation.

The simulations in the last two parts in figure 3.1 show that the X-propagation plugin simulations for the if-else statement work the same way as stated in the user manual [14].

The input and output waveforms for the known-value, X-value, resolve mode and pass mode simulations of the case statement are represented in figure 3.2. The X-value simulation for the case statement is done the same way as the if-else statement. In the waveform, figure 's' is the control signal, 'a' and 'b' are the input signals, and 'r' is the output signal.

Figure 3.2. Case statement waveform in normal and X-propagation plugin operation.

The simulation results are combined in tables 3.4, 3.5 and 3.6 separated by the value of the 's' signal.

|   | Nor | mal |   | Resolve |   |   |   | Pass |   |   |   |  |  |  |

|---|-----|-----|---|---------|---|---|---|------|---|---|---|--|--|--|

| s | а   | b   | r | s       | а | b | r | s    | а | b | r |  |  |  |

| X | 0   | 0   | 1 | X       | 0 | 0 | Х | X    | 0 | 0 | Х |  |  |  |

| X | 1   | 0   | 1 | X       | 1 | 0 | Х | X    | 1 | 0 | Х |  |  |  |

| X | 0   | 1   | 1 | X       | 0 | 1 | Х | X    | 0 | 1 | Х |  |  |  |

| X | 1   | 1   | 1 | X       | 1 | 1 | Х | X    | 1 | 1 | Х |  |  |  |

Table 3.4. Case statement simulation results, s=X

|   | Nor | mal |   |   | Resolve |   |   |   | Pass |   |   |  |  |  |  |

|---|-----|-----|---|---|---------|---|---|---|------|---|---|--|--|--|--|

| s | а   | b   | r | s | а       | b | r | s | а    | b | r |  |  |  |  |

| 0 | Х   | 0   | Х | 0 | X       | 0 | Х | 0 | Х    | 0 | Х |  |  |  |  |

| 0 | 0   | Х   | 0 | 0 | 0       | Х | 0 | 0 | 0    | Х | 0 |  |  |  |  |

| 0 | Х   | Х   | Х | 0 | Х       | Х | Х | 0 | Х    | Х | Х |  |  |  |  |

**Table 3.5.** Case statement simulation results, *s*=0

Table 3.6. Case statement simulation results, s=1

|   | Nor | mal |   | Resolve |   |   |   | Pass |   |   |   |  |  |

|---|-----|-----|---|---------|---|---|---|------|---|---|---|--|--|

| s | а   | b   | r | s       | а | b | r | s    | а | b | r |  |  |

| 1 | Х   | 0   | 0 | 1       | Х | 0 | 0 | 1    | Х | 0 | 0 |  |  |

| 1 | 0   | Х   | Х | 1       | 0 | Х | Х | 1    | 0 | Х | Х |  |  |

| 1 | X   | Х   | Х | 1       | X | Х | Х | 1    | Х | Х | Х |  |  |

As seen from figure 3.2, the case statement works as expected. When the control signal 's' is low, the output is dictated by the input signal 'b', and when the control signal is high, the output signal is dictated by input 'a'. Examining the second part of figure 3.2, we can see how the X-values at the input affect the output. As seen in the figure, the output is dictated by control signal 's', and when it is not set as X. When the control signal is X, the output defaults to high. When the control signal is low, the output is set as the 'a' signal, and when high, the output is set as the 'b' signal. Comparing the resolve mode operation of the case statement in the third part of figure 3.2 and the non-X-propagation plugin simulation in the second part of figure 3.2, the difference in output is N. The case statement X-propagation plugin simulation in pass mode shown in the final part of figure 3.2. Surprisingly shows no difference to the resolve mode simulation.

As with the if-else statement, the trap mode on the case statement does not affect the waveform. This is in line with the user guide, so it is working as expected. [14]

#### 3.2 Simulation setup 2 - Random number generator

The second simulation setup to be tested is a random number generator. The circuit was implemented using a linear feedback register. As is often the case, this is a pseudo-random number generator. The feedback value in the code is determined by a polynomial function which, in turn dictates the length of the pseudo-random number chain. In the case tested, the output chain is 15 numbers long. However, the length is irrelevant when testing the X-propagation properties of the design.

There are only a limited number of input signals going into the circuit. This means that only a small amount of X-values come from outside of the circuit. Since the circuit is synchronous, there are registers in the designs which may cause ambiguity on startup or brownout if not reset properly.

The VHDL code of the random number generator is as follows.

```

entity rand_num_generator is

port(

clk, reset : in std_logic;

q : out std_logic_vector(4 downto 0) -- output

);

end rand_num_generator;

architecture arch of rand_num_generator is

signal r_reg, r_next : std_logic_vector(4 downto 0);

signal feedback_value : std_logic;

begin

process(clk, reset)

begin

if(reset='1') then

-- set initial value to '1'.

r_reg(0) <= '1';

r_reg(4 downto 1) <= (others=>'0');

elsif (clk'event and clk='1') then

r_reg <= r_next;</pre>

end if;

end process;

feedback_value <= r_reg(4) xor r_reg(3) xor r_reg(0);</pre>

r_next <= feedback_value & r_reg(4 downto 1);</pre>

q <= r_reg;</pre>

end arch;

```

Listing 3.3. Random number generator. [21]

When reviewing the code, it can be seen that the design has only a clock and a reset as its inputs. This means that, at least in X pessimistic cases, there is a high risk of the simulation getting stuck in a loop of X-values.

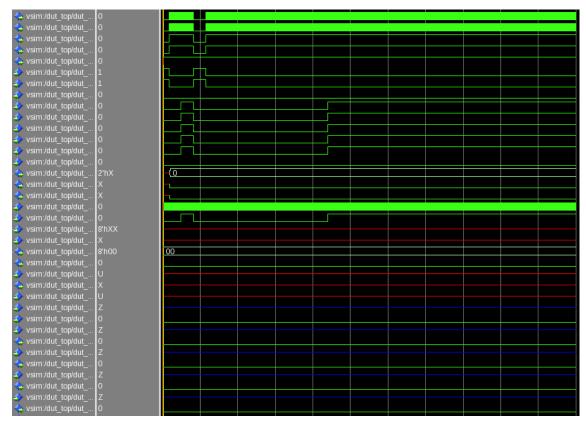

### 3.2.1 X-propagation with simulator A

Simulator A is used to simulate for X-propagation. First the normal operation of the design is verified by simulating it without any abnormal behaviour induced. The registers in the design are all reset and have a reset value. This means no X-values should be found when the simulation is running.

In the normal operation simulation, the random number generator is left to run freely. The DUT is set to run for 13 cycles within one sequence. The input and output waveforms for the normal operation of the random number generator are represented in the first part of figure 3.3. In the picture 'q' is the output of the circuit.

The X-value simulation is done by changing the functionality of the reset of the registers. The standard operation of the reset sets the lowest order bit of the register feeding to the output as '1' and others as '0'. When the value of the lowest order bit of the output register is not defined, it will default to X. The waveform of the simulation is represented

in the second part of figure 3.3.

When the output register does not have any reset value, all the bits in the register will default to X. In this case, the reset is not used by the DUT. The waveform of the simulation without reset values for the output register is represented in the final part of figure 3.3.

| <pre></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1<br>0<br>5'h01<br>5'h01 | (01<br>(01 | <u>10</u>   | /18<br>/18 | <u>χος</u><br>χος | <u>16</u><br>16 | 1B<br>18<br>18 | 1D<br>1D<br>1D | 1E<br>1E | LOF<br>LOF | 107<br>107  | 113<br>113<br>113 | <u>χο</u> 9<br>χο9 | 104<br>104<br>104 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------------|-------------|------------|-------------------|-----------------|----------------|----------------|----------|------------|-------------|-------------------|--------------------|-------------------|

| Image: the second s | 5'h10<br>1               | (10        | <u>, 18</u> |            | <u>, 16</u>       | <u>, 18</u>     | <u>, 1D</u>    | <u>,1E</u>     |          | 07         | <u>, 13</u> | <u>109</u>        | <u>104</u>         | <u>102 1</u>      |

| <pre>/tb_top/DUT_0</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | /clk 0                   |            |             |            |                   |                 |                |                |          |            |             |                   |                    |                   |

| <pre>/tb_top/DUT_0</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | /res 0                   |            |             |            |                   |                 |                |                |          |            |             |                   |                    |                   |

| 🖃 🛧 /tb_top/DUT_0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | /q 5'hXX                 |            | 0X          |            | 3                 | K0              | XX             |                | XX       |            | XX          | X                 | (                  |                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | /r_r 5'hXX               |            | 0X          |            | )                 | (0              | XX             |                | XX       |            | XX          | X                 | (                  |                   |