# Image and Video Coding Techniques for Ultra-low Latency

JAKUB ŽÁDNÍK, MARKKU MÄKITALO, JARNO VANNE, and PEKKA JÄÄSKELÄINEN, Tampere University, Finland

The next generation of wireless networks fosters the adoption of latency-critical applications such as XR, connected industry, or autonomous driving. This survey gathers implementation aspects of different image and video coding schemes and discusses their tradeoffs. Standardized video coding technologies such as HEVC or VVC provide a high compression ratio, but their enormous complexity sets the scene for alternative approaches like still image, mezzanine, or texture compression in scenarios with tight resource or latency constraints. Regardless of the coding scheme, we found inter-device memory transfers and the lack of sub-frame coding as limitations of current full-system and software-programmable implementations.

CCS Concepts: • Computing methodologies  $\rightarrow$  Image compression; • Computer systems organization  $\rightarrow$  Real-time system architecture; • General and reference  $\rightarrow$  Surveys and overviews; Evaluation; Performance;

Additional Key Words and Phrases: Video coding, texture compression, low latency, real-time video system

#### **ACM Reference format:**

Jakub Žádník, Markku Mäkitalo, Jarno Vanne, and Pekka Jääskeläinen. 2022. Image and Video Coding Techniques for Ultra-low Latency. *ACM Comput. Surv.* 54, 11s, Article 231 (September 2022), 35 pages. https://doi.org/10.1145/3512342

#### 1 INTRODUCTION

Since the advent of digital video, the need for saving network bandwidth and storage space has driven the effort for efficient compression. Over the years, the network speed has been increasing together with the processing power, but so did the video parameters—frame rate, resolution, or bit depth—putting more requirements on the video compression systems. To this end, Motion Picture Experts Group (MPEG) and International Telecommunication Union Telecommunication Standardization Sector (ITU-T) have introduced a steady line of video coding standards starting with H.261 [116] in 1988 through the nowadays ubiquitous Advanced Video Coding (AVC/H.264) [151] and High-efficiency Video Coding (HEVC/H.265) [132] up to the newest Versatile Video Coding (VVC/H/266) [20]. Each standard generation aims to approximately double the compression ratio for the same subjective and objective visual quality. However, the computation complexity also increases along with these improvements.

This work was financially supported by the Tampere University Graduate School and is part of the FitOptiVis project [4] funded by the ECSEL Joint Undertaking under Grant No. 783162. It also received funding from the European Union's Horizon 2020 research and innovation programme under grant number 871738 (CPSoSAware).

Authors' address: J. Žádník, M. Mäkitalo, J. Vanne, and P. Jääskeläinen, Tampere University, Korkeakoulunkatu 7, 33720 Tampere, Finland; emails: {jakub.zadnik, markku.makitalo, jarno.vanne, pekka.jaaskelainen}@tuni.fi.

This work is licensed under a Creative Commons Attribution International 4.0 License.

© 2022 Copyright held by the owner/author(s). 0360-0300/2022/09-ART231 https://doi.org/10.1145/3512342

231:2 J. Žádník et al.

Solely improving the coding efficiency is not the only motivation for compression. Because often the energy cost of computation is much lower than the energy required for transmission, a lightweight compression scheme can achieve energy savings [14]. Battery life improvements are especially important in the context of multi-access edge computing [135]. In addition, even with the compression computation overhead, the decreased time spent on transferring the compressed data might result in a lower total time than transporting raw data without compression. In these types of scenarios, the tradeoff between computational complexity and achieved compression ratio must be carefully considered.

For non-interactive video systems, such as video playback, the coding <sup>1</sup> latency is not as important as the quality or file size—as long as the coding speed is fast enough to process the video at a required frame rate. Indeed, modern video codecs can exploit redundancies between frames, which requires frame buffering and an additional delay when buffering the future frames. However, interactive video applications require low latency to be usable. As shown later in the survey, with the current generation of wireless networks, the network transfer time is usually the main factor contributing to the total latency in real-world applications. Even with multi-gigabit Ethernet connections, it can be challenging to achieve sufficiently low latencies. However, recent advances in network technologies, such as WiFi-6 or 5G, promise to lower the transmission latency down to units of milliseconds. With such low latencies, the video coding pipeline becomes the bottleneck.

Faster networks open up space for new applications, such as cloud gaming, extended reality (XR), or internet of skills [37]. However, high latency can either hinder the user experience (cloud gaming) or contribute to motion sickness (virtual reality (VR)). While human-centered applications are tolerant to a degree of latency limited by perception, some automation systems such as robotized factories or autonomous vehicles rely on machine vision to control their actions. In the case of fast-moving and safety-critical applications, the latency requirements can be much stricter. Therefore, it is necessary to consider the coding latency also from the perspective of applications where humans with their imperfect brains are not involved, but the video stream is used to make ultra-low latency control decisions with robots.

Another trend motivating low latency video coding is "edge computing," or more specifically, the slight reversal of this trend: Instead of integrating more computing power to all sensors ("smart cameras") in cyber-physical systems, there is now a move back towards more centralized computing architectures, with processing done in a powerful computer connected with a fast network link to "dumber cameras" [125]. In response to the trend, AUTOSAR, the global leading automotive standardization partnership, has released an Adaptive Platform [49] with the focus on high-performance computing needed by intelligent cars, as an alternative to their previous classic decentralized architecture. Many car features, especially automated and autonomous driving, rely on fast video processing, where compression would play an important role in reducing the bandwidth and the latency between the sensors and the central server.

In general, video coding latency can be reduced by faster algorithms and their intelligent mapping (implementation) to the underlying compute platforms. Since the maximum clock frequencies do not scale anymore according to Moore's law, more processing power is achieved by parallelization, and so "faster" nowadays usually translates to "more parallel." The computational perspective shift requires reformulating traditional approaches to suit parallel execution models, which optimally should be visible at algorithm-level design decisions.

<sup>&</sup>lt;sup>1</sup>In this survey, the word "coding" is used as a general term for both "encoding" and "decoding," since both parts are equally important in a full video system.

### 1.1 Contributions and Research Questions

To our best knowledge, this is the first comprehensive overview of video<sup>2</sup> coding techniques that (a) focuses primarily on the low latency aspect and (b) considers a wide range of alternative techniques, apart from the most common ones. The goal of this survey is also to settle the state-of-the-art video coding implementations into the context of full video systems with the upcoming networking trends in mind.

For categorization, we first define a precise limit for *low* and *ultra-low* latencies based on human perception limits and requirements of the upcoming networking standards. Then, by analyzing the state-of-the-art implementations of video coding schemes, we answer the following research questions:

- (1) What are the main approaches to decreasing latency of video coding schemes and their implementations?

- (2) What are the limitations of the current state-of-the-art video coding schemes in terms of latency?

- (3) What are the computational requirements of the state-of-the-art video coding schemes?

# 1.2 Survey Outline

The rest of the survey is organized as follows. Section 2 formulates video system requirements from the perspective of low latency—we define how low should the latency be in different applications, and how it projects to a required coding speed and compression gain. Section 3 provides a general overview of image and video compression and categorizes existing approaches into four categories. Sections 4–6 contain the results of the survey, providing details about the findings in each of the categories. Section 7 summarizes our findings and proposes possible future research directions.

The main source of literature was the Scopus database, where we searched for each category introduced in Section 3 separately with a focus on real-time and low-latency keywords. The search results were sorted in reverse chronological order to prioritize the most current results. Papers reporting latency (i.e., not just the coding time) and a coding throughput of more than 50 MP per second were included with a priority. Furthermore, papers found outside this procedure were also included, when appropriate. A snowballing approach [153] was used in Section 4 with the help of the pybliometrics library [119] to discover possible related works within citations and references of included papers.

#### 2 REQUIREMENTS OF A LOW-LATENCY VIDEO SYSTEM

Let us define a video system as the end-to-end chain that source video frames have to pass through until they are consumed by a target device. For this survey, the system's latency is the most important requirement. Hand-in-hand with low latency goes high throughput, since the system must be able to process a certain amount of data in a fixed time frame. The compression ratio is limited by the transport channel and directly affects the transmission speed. Therefore, whenever possible, we try to assess also the compression ratio. Visual quality, while certainly one of the key parameters of video compression, is hard to compare objectively. For this reason, we do not concentrate much on visual quality, unless Bjøntegaard metric [17] evaluation is provided, which estimates either the peak signal-to-noise ratio (PSNR) change for the same bitrate or the bitrate change for the same PSNR.

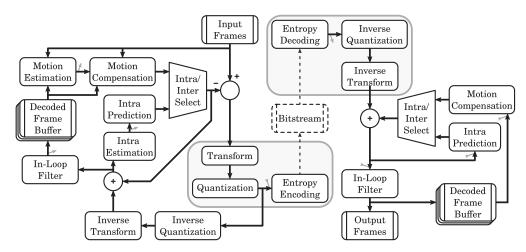

Figure 1 shows a generic diagram of a video system. Every arrow in the diagram represents a data transfer and therefore a possible source of latency. Furthermore, every device performs some

<sup>&</sup>lt;sup>2</sup>We consider "video coding" in a broader sense as "image and video" coding.

231:4 J. Žádník et al.

Fig. 1. Top-level view of a networked video system.

computation and internal memory transfers, again increasing the latency. In practice, devices can be merged. An example video coding system can look as follows: graphics processing unit (GPU) captures and encodes rendered frames from a running game. The encoded video stream has to be transferred to the central processing unit (CPU) to be sent via an operating system network stack. Receiving CPU then sends the encoded data into a hardware decoder integrated within a GPU from where the decoded video is transferred to an head-mounted device (HMD). In this example, the capture and encoding device is the same GPU while on the decoding side, the data has to pass three different devices.

### 2.1 Setting Latency Constraints

In interactive video systems, the "top-level" latency, also called *motion-to-photon latency*, is the time elapsed between a user's input on the source device and the observation on the display device. In machine control systems where the consumer is an algorithm and not a human, this term refers to the latency from the source video acquisition until the point when the transcoded signal is delivered to the input of the vision system. Even though the network is often a major latency contributor, the scope of the survey is limited to the encoder and decoder only.

How low the latency needs to be depends on the application. Kadowaki et al. [66] studied the users' performance solving a simple pointing task with their hand being projected at different *motion-to-photon latencies*. The authors concluded that if the latency is greater than 24.3 ms, the user's performance starts to decrease. Two articles by Lago and Kon [80] and Mäki-Patola and Hämäläinen [92] suggested that an audio latency below 20–30 ms is either imperceptible or acceptable for humans. Even though the articles refer to sound latencies, video is often accompanied by audio, and therefore, audio latency requirements have to be met as well.

Mochizuki et al. [98] face a restriction on the latency of a car surround view system to be under 100 ms, otherwise, the safety of the driver during parking could be violated. As the authors state, 100 ms corresponds to the migration distance of approximately 30 cm at the speed of 10 km/h. While 100 ms is sufficient for a parking system, to maintain the same travel distance of 30 cm at a speed of 100 km/h, the required latency would have to be 10 ms. From the example, it is apparent that low latency is critical for systems like autonomous driving where the vehicle moves fast. For example, a white paper by Ixia [63] defined end-to-end automotive Ethernet latency requirements as 0.25–1 ms for driver assistance and driver safety applications and <10 ms for human-machine interface systems.

A specification by the 3rd generation partnership project (3GPP) [1] defined use cases and requirements for 5G communication in automation. The specification refers to "low latency" as a latency lower than 10 ms and an "end-to-end" latency as a network end-to-end latency—different from the *motion-to-photon latency* defined for a complete video system. Among other things, latency requirements are mentioned for multiple use cases such as augmented reality (AR) (50 ms *motion-to-photon* to prevent motion sickness) or "mobile robots" (cycle time <10 ms for machine control, 10–100 ms for video-operated remote control).

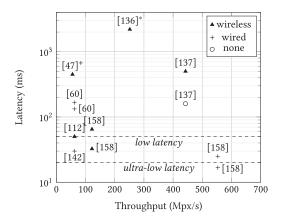

Based on the above observations, we define *low latency* as a *motion-to-photon latency* between 20–50 ms and *ultra-low latency* as a *motion-to-photon latency* lower than 20 ms. For non-critical systems with a human in the loop, *low latency* ensures a high-quality user experience. *Ultra-low latency* sets a requirement for latency-critical systems where a precision higher than the human perception threshold is required to prevent damage or injuries.

The typical latency of current wireless technologies (e.g., 4G and 802.11ac, a.k.a. Wi-Fi 5) is in the order of tens of milliseconds, which by itself is too high for achieving *ultra-low latency*. The newest and upcoming wireless network standards (5G and 802.11ax, a.k.a. Wi-Fi 6) promise to reduce the latency towards units of milliseconds, making them possible to be used in latency-critical applications. For example, the ultra-reliable and low-latency communication (URLLC) paradigm used for the upcoming 5G standard requires 1 ms end-to-end network latency [16].

# 2.2 Throughput Versus Latency

High coding throughput (i.e., number of pixels encoder/decoder can process per unit of time) is a necessary condition to achieving low latency, although by itself it may not be sufficient. A processing latency of one frame might be too high to achieve *ultra-low latency* even at high frame rates—for example, a coding speed of 120 frames per second (FPS) corresponds to 1,000/120 = 8.3 ms coding time. Therefore, the ability of sub-frame coding would allow for achieving lower latencies without the necessity of significantly increasing the coding throughput, which is a very challenging task.

Theoretically, it should be possible to reduce the latency indefinitely, assuming the algorithm can support it. For example, mezzanine compression algorithms are capable of reaching latencies down to below one line of pixels [35]. In practice, however, sub-frame coding has its limits. Even if the algorithm and its implementation allow for sub-frame coding, the integration into a complete system might require buffering between the system pipeline stages, thus lowering the low-latency potential. Furthermore, the control overhead of managing multiple sub-frame streams might be too large if the sub-frame size is too small. Also, for highly parallel devices, most notably GPUs, the workload of encoding a small sub-frame can be too low to fully utilize its computational resources. Therefore, in some scenarios, optimizing for the lowest possible latency can paradoxically damage the coding throughput.

As the last point, data transfers between devices such as CPUs and GPUs are a known source of latency as well as a throughput bottleneck. Thus, spreading the computation across devices must be considered carefully.

#### 2.3 Compression Ratio

The channel bandwidth plays an important role in determining the necessary compression ratio. Table 1 shows the minimum necessary theoretical compression ratios required to transport video (assuming 60 FPS without subsampling) over different digital video interfaces and network channels. The examples are given for 1080p, 4K (3,840  $\times$  2,160) and 8K (7,680  $\times$  4,320) resolutions with 10 bits per color component (assuming three components per pixel). The channel throughput values listed are theoretical maximum values not reflecting the channel overhead, and therefore, the required compression ratios should be perceived as slightly underestimated.

#### 3 GENERAL COMPRESSION TECHNIQUES

We divided the possible video compression algorithms into four categories based on their design goals and coding principles: still image compression, video compression, mezzanine compression, and texture compression. Furthermore, we briefly discuss the impact of machine learning on image and video compression. The following subsections give an overview of these categories.

231:6 J. Žádník et al.

| Raw (60 FPS, 10-bit, 4:4:4) |                   | Vi     | ideo Inter | faces     | Networks |       |        |        |        |       |  |  |

|-----------------------------|-------------------|--------|------------|-----------|----------|-------|--------|--------|--------|-------|--|--|

| Kaw (60 FFS                 | 5, 10-011, 4:4:4) | 3G-SDI | DP 1.4     | HDMI 2.1  | 4G       | 5G mm | WiFi-5 | WiFi-6 | 25 GbE | 5G fu |  |  |

| Resolution                  | Gb/s              | 2.9    | 25.9       | 25.9 42.6 |          | 2.0   | 3.5    | 11     | 25     | 50    |  |  |

| 1080p                       | 3.7               | 1.3    | _          | _         | 3.7      | 1.9   | 1.1    | _      | _      | _     |  |  |

| 4K                          | 14.9              | 5.1    | _          | _         | 14.9     | 7.5   | 4.3    | 1.4    | _      | _     |  |  |

| 8K                          | 59.7              | 20.6   | 2.3        | 1.4       | 59.7     | 29.9  | 17.1   | 5.4    | 2.4    | 1.2   |  |  |

Table 1. Required Compression Ratios of Video (60 FPS, No Subsampling, 10 Bits/channel) at Different Resolutions Transferred Over Various Channels

The channel bandwidths are listed as theoretical maximum values. "DP": DisplayPort standard; "5G mm": 5G mmWave standard; "5G fu": future 5G at short wavelengths.

# 3.1 Still Image Compression

Because video is essentially a stream of images, image compression algorithms can be used to compress video. This is the broadest and most generic category we define. Typical image compression is performed in three stages. First, the input samples are decorrelated. Decorrelation can be achieved with a variety of methods such as transform (e.g., discrete cosine transform, DCT), prediction (e.g., median edge detection, MED) or sub-band coding (e.g., discrete wavelet transform, DWT), often prepended by a color transform that splits the color channels into luminance and chrominance components. Decorrelated samples are then subjected to statistical modeling such as quantization discarding the least important samples, reordering that ensures the most important samples are transported first, or context modeling, which can be used to exploit local image features by predicting the error residuals. The final step is entropy coding, which reduces the statistical redundancies between samples, for example, Huffman, arithmetic, or Golomb-Rice coding. Decompression is performed by repeating the inverse operations of the encoding steps in reverse order: entropy decoding, sample restoration (de-quantization), and inverse transform, possibly followed by a color transform into the original domain.

The most widely used algorithms in this category are variants of the joint photographic experts group (JPEG) algorithm: The original JPEG [143], its more complex improvement JPEG 2000 [130], or JPEG-LS [149] meant primarily for lossless or near-lossless image coding. New JPEG XL [118] standard is intended to supersede the original JPEG for web applications.

#### 3.2 Hybrid Video Compression

Nearly all modern video codecs share the same hybrid coding scheme: First, they look for redundancies both spatially (intra-frame) and temporally (inter-frame) and represent the differences between similar blocks instead of encoding all the redundant pixel data. This enables a reasonably accurate prediction of the original data. The prediction residuals are then encoded via a procedure similar to transform-based still image coding. Typically, a variation of discrete cosine transform (DCT) is used as a decorrelation transform, followed by a quantization driven by a psychovisual model. Finally, the quantized coefficients are entropy-encoded, typically through context-adaptive variable-length coding (CAVLC) or context-adaptive binary arithmetic coding (CABAC). In addition, the modern video encoding flow also includes in-loop filtering, especially for deblocking. Because of the added coding tools, hybrid video codecs can achieve rate-distortion performance superior to typical still image codecs.

Figure 2 shows generalized block diagrams of a video encoder and decoder. The blocks in the gray zone denote the core of the video coding algorithms, which is not fundamentally different from transform-based still image coding. However, the block diagram illustrates that apart from the additional computation of the prediction residuals, the intra and inter prediction complicate the data flow by introducing a feedback loop that replicates a part of the decoding process. Apart

Fig. 2. Block diagram of a hybrid video encoder (left) and decoder (right). Gray zones denote the core of the algorithms that is similar to transform-based still image coding. Grey arrow pins denote intra-/inter-prediction and filter control data transferred to (from) the entropy encoder (decoder).

from the residuals, additional control data from the prediction estimation modules and the in-loop filters, required to restore the frames on the decoding side, are also encoded by the entropy coder (denoted by gray arrow pins in the figure). Additional memory storage is required for storing reference frames required by inter prediction.

Apart from regular video streams, special video formats were encountered during the survey, which often require additional processing steps during encoding. Notably, 360° video used in VR applications require stitching or a reprojection of the multi-camera view into a rectangular planar format [112].

First group of video coding standards are codecs developed by MPEG: *AVC (H.264)* [151], *HEVC (H.265)* [132], and the newest *VVC (H.266)* [20]. Each generation aims to approximately double the compression ratio for the same quality. Compared to Advanced Video Coding (AVC), HEVC simplified the in-loop filtering and added explicit support for parallelism via wavefront parallel processing (WPP), slices, and tiles. VVC further improves the coding efficiency of HEVC and extends its scope to be more versatile, i.e., usable in a broader range of applications such as wide-gamut, high dynamic range (HDR) or 360° video, still image coding or lossless coding.

Another line of codecs are open, royalty free formats by Google (the latest by Aliance for Open Media): *VP8* [13], *VP9* [100], and *AOMedia video 1 (AV1)* [28].

In addition, audio and video coding standard Workgroup of China developed their variants of video codecs: AVS [46], AVS2 [50], and AVS3 [160].

#### 3.3 Mezzanine Compression

Mezzanine compression algorithms are intended to reduce the bitrate of high-resolution video transferred over high-bandwidth links, such as HDMI, DisplayPort, or a 10 Gb Ethernet. These algorithms are intended to be visually lossless with low latency and low complexity. Common use cases of mezzanine compression are professional video production chains or compression of a high-resolution video stream between a video card and a monitor. Willème et al. [152] define requirements for mezzanine compression as follows:

- Support for 1080p-8K, 8-12 bits per component, 4:4:4 and 4:2:2 chroma subsampling.

- Compression ratio in the range of 1.5–6:1.

231:8 J. Žádník et al.

- Visually lossless quality.

- Quality robustness in case of multiple encode-decode passes.

- Low computational complexity and low latency (<32 lines of a frame).

While mezzanine compression could be categorized as a part of still image compression, the low complexity, and low latency requirements justify a separate category. However, since the number of publications found was very low, the results are merged into the still image coding category in Section 4.

Some of the most well-known mezzanine compression algorithms are VC-2 [18], VESA DSC [144], and the newest standard JPEG XS [35]. Multiple proprietary formats exist such as LLVC by Sony or tiny codec (TICO) by intoPIX.

### 3.4 Texture Compression

Texture compression algorithms are primarily designed for offline compression of textures, which are stored into a GPU memory in the compressed state. During rendering, the texture components (texels) are repeatedly read from and decompressed at runtime during the display process. The fast decoding is therefore of utmost importance, and modern GPUs support hardware texture decompression to make the decoding process as fast as possible. Beers et al. [15] define the following design goals of a texture compression algorithm:

- Very fast decoding speed.

- Fast random access to the pixels in the texture, which implies a fixed compression ratio.

- Visual quality can be compromised for higher compression.

- Fast encoding is useful but not necessary.

Typically, the encoding process evolves around designing a codebook that quantizes the original color space and representing pixels as indices pointing into the quantized codebook. Decompression is thus achieved simply with a table lookup. Compared to previous categories, texture compression lacks the entropy coding step, which typically results in worse rate-distortion performance.

There are many variants of texture compression formats, mostly depending on the platform. Desktop GPUs support hardware decompression of the S3 texture compression (S3TC) family (also called block compression (BC) or DirectX texture compression (DXT)): BC1–5 [21, 62, 123] or the more complex BC6H (for HDR textures) and BC7 (for ordinary textures) [88, 124]. The newest evolution of this family is adaptive scalable texture compression (ASTC) [101], which supports variable block sizes and therefore multiple possible compression ratios. It is also the most complex texture compression format up to this date. Contrary to BCx, ASTC is only supported on mobile devices and Intel GPUs. For mobile Android-based devices, Ericsson texture compression (ETC)-based compression is used: ETC1 or ETC2 and EAC. Apple devices support their PowerVR texture compression (PVRTC) compression standard.

#### 3.5 The Role of Machine Learning

In the past decade, the use of machine learning, and especially deep learning, has risen dramatically. We dedicate this last category to two distinct concepts connecting machine learning and image/video compression: the use of machine learning for image/video compression and the compression of visual content for machine vision applications (which typically utilize machine learning for the vision algorithm).

*Machine Learning for Compression.* As in many other fields, machine learning has also been used for solving hard optimization problems in image and video compression. Following a distinction

made by Lie et al. [89] and Hoang and Zhou [59], we can divide applications of machine learning in video compression into two categories:

- (1) Novel compression schemes built primarily with deep learning techniques.

- (2) Use of deep learning tools in traditional coding pipelines.

Due to the high computational complexity of deep learning algorithms, most end-to-end implementations struggle to achieve high coding speed, which was confirmed during our literature search. Therefore, we decided to omit the end-to-end implementations from the survey. The mentioned studies [59, 89] can provide a further overview of this topic.

In some cases, we found deep learning used for accelerating complex steps in existing codecs. These publications are further discussed in their respective sections.

Compression for Machine Vision. Hand in hand with advances in machine learning, the range of machine vision applications has grown steadily. As pointed out by Le et al. [83], Cisco Annual Internet Report [30] predicts the share of machine-to-machine connections will grow from 33% in 2018 to 50% by 2023. Furthermore, the upcoming 5G latency improvements are expected to further accelerate the adoption of machine vision in low-latency systems. Thus, there is a growing need for compression optimized specifically for machine vision algorithms. However, only a handful of implementations were yet published, which we shortly list in this subsection without introducing a new category.

From the machine vision perspective, it can be beneficial to compress and transmit features extracted from the source pixels, instead of the pixels themselves. This is known as "feature compression" and two MPEG standards accompany this effort in the context of visual search applications: compact descriptors for visual search (CDVS) [41] and compact descriptors for visual analysis (CDVA) [42]. CDVS defines a set of handcrafted descriptors and a processing pipeline to ensure better reproducibility and interoperability between applications. CDVA further extends the concept CDVS by including deep features alongside the handcrafted ones and exploiting temporal redundancies between video frames. We found only three real-time implementations of CDVS [43, 51, 133] reaching 98, 144, and 39 MP per second on desktop-grade GPUs, respectively. Compared to other implementations reported later in the survey, the results are relatively slow, and more research would be necessary to decrease the computational complexity of CDVS and CDVA.

"Feature compression" might lead to optimal compression for machine vision, but the results are not directly interpretable by humans. The recent proposal of video coding for machines (VCM) [40] tries to find the balance between both the human and machine vision perception by finding a collaborative coding model.

Recently, end-to-end frameworks based on the idea of an autoencoder were proposed, specifically targeting the compression for machine vision [82, 83, 111]. In Reference [82], the authors achieved a throughput of only 14 MP per second on a high-end desktop GPU. However, the proposed method shows a great potential by outperforming Versatile Video Coding (VVC) in terms of machine vision accuracy.

Another meaning to "feature compression" was given by works that propose compressing intermediate deep features (e.g., Reference [45]). That is, instead of compressing the visual signal itself, part of the target vision neural network is executed on the source device, followed by the deep feature compression, transmission, feature decompression, and computing the rest of the neural network. However, we consider the approach a separate topic out of the scope of this survey.

231:10 J. Žádník et al.

#### 4 STILL IMAGE COMPRESSION

This section presents the implementation results of still image and mezzanine compression algorithms. First, in Section 4.1, we mention implementations evaluating *motion-to-photon latency*. Then, the rest of the section is organized as follows:

*JPEG Variants.* (Section 4.2) This category includes both software (CPU and GPU) and hardware (field-programmable gate array (FPGA)) implementations of different JPEG standards. The results vary greatly given the wide range of design goals and target platforms.

Frame Memory Compression. (Section 4.3) A large group of the results consists of dedicated hardware accelerators (mostly application-specific integrated circuit (ASIC) but also FPGA) designed to reduce the memory footprint within another application (such as reference frame buffering in a video codec or a computer vision application). Despite being used as a part of a larger system, they can still be viewed as standalone image compression algorithms. Common characteristics of these systems are (a) pipelined architecture with a latency of units—tens of clock cycles, (b) lossless or near-lossless quality, (c) low compression ratio usually between 2–3, and (d) custom adaptations of basic statistical algorithms focusing on simplicity.

*Mezzanine Compression.* (Section 4.4) The mezzanine compression results are merged into this section, because only three implementations were found in the search process and the structure of the algorithms closely matches general still image coding. More specifically, VESA display stream compression (DSC) and JPEG XS algorithms are covered.

Other. (Section 4.5) Implementations of algorithms that do not fit to any of the above categories.

Table 2 summarizes basic properties of the reviewed implementations. Because of the large variety of different algorithms, the "Algorithm" column denotes the algorithm's decorrelation and coding steps. The "Format" column denotes the color format and subsampling as specified by the authors. The "Len." (length) column specifies whether the implementation uses variable-, semi-fixed-, or fixed-length coding. The "~" character anywhere in the table denotes an approximate value—for example read from a plot. The entries are sorted first by the coding type (encoding, then decoding), then by a throughput.

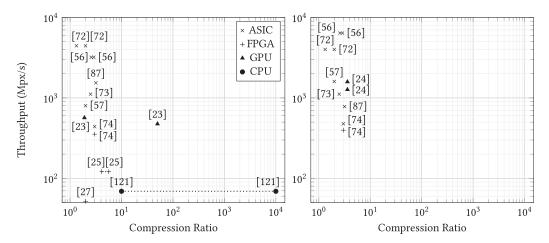

Figure 3 shows a visual comparison of throughputs and compression ratios of those reviewed implementations that report both values. Because the encoding and decoding throughputs usually vary, the figure shows them in two separate plots. The compression ratio is equal for both of the plots.

#### 4.1 Implementations Reporting Latency

Holub et al. [60] proposed a GPU-accelerated coding of the JPEG standard. All encoding and decoding steps were performed on a GPU except the code stream parsing on the decoding side. The results in Table 2 correspond to encoding/decoding throughput of an 8K image at a quality level (Q) of 10 (highest TP) and 95 (lowest TP) for both the encoder and the decoder with and without memory transfers. With JPEG coding, the whole system exhibits a latency of 4 frames (133 ms), the same as an uncompressed video (with 1080i video input). Apart from JPEG, the publication also described GPU texture compression encoding, which is covered in more detail in Section 6.1.

Ubik et al. [138] proposed an FPGA implementation of TICO integrated into a 1080p video streaming system with the latency of 0.58 ms. The choice of a lightweight mezzanine compression

Table 2. Comparison of Reviewed Still Image Coding Implementations

|               |                                        |          | C       | o-Processin           | g       |        |        |             |                |                  |

|---------------|----------------------------------------|----------|---------|-----------------------|---------|--------|--------|-------------|----------------|------------------|

| 1st author    | Algorithm                              | Len.     | TP      | For                   | mat     | Pla    | tf.    | Host        | D              | evice            |

|               |                                        |          | (Mpx/s  |                       |         |        |        |             |                |                  |

| Holub [60]    | DCT## + Huff./RLE##                    | var      | 1625°°  |                       | 44 Q=10 | CPU+   | GPU    | Intel i7 30 | GHz GT         | X 580            |

|               |                                        |          | 824     |                       |         |        |        |             |                |                  |

|               |                                        |          | 1322°°  |                       | 44 Q=95 |        |        |             |                |                  |

|               |                                        |          | 634     |                       | _       |        |        |             |                |                  |

|               |                                        |          | 2057°°  |                       | 44 Q=10 |        |        |             |                |                  |

|               |                                        |          | 899     | -                     |         |        |        |             |                |                  |

|               |                                        |          | 1060°°  |                       | 44 Q=95 |        |        |             |                |                  |

| D 5- 1        | DATASET LAND.                          |          | 586     |                       |         | 0077   | 0011   |             | 0.000          |                  |

| Bruns [24]    | $DWT^{++} + MSB^{++}$                  | var      | 1584°   |                       |         | CPU+   | GPU    | _           | GT             | X 1080           |

|               |                                        |          | 1269°   | D YCbCr4              | 14      |        |        |             |                |                  |

|               |                                        |          | St      | andalone H            | W       |        |        |             |                |                  |

| 1st author    | Algorithm                              | Len.     | TP      | Format                | Platf.  | Tech   | Freq   | Pow.        | Ga/LUT         | Mem              |

|               | O                                      |          | (Mpx/s) |                       |         | (nm)   | (Mhz)  | (mW)        | $(\cdot 10^3)$ | (B)              |

| Kim [72]      | DWT + SPIHT                            | fix      | 4448 E  | YUV420                | ASIC    | 65     | 556    |             | 76.5           | 512              |

|               |                                        |          | 4000 D  |                       |         |        | 500    |             | 107.8          | 0                |

| Guo [56]      | MDA + SFL                              | semi     | 2133 E  | YUV420                | ASIC    | 90     | 300    | _           | 45.1           | _                |

|               |                                        |          | 4267 D  |                       |         |        |        |             | 34.5           |                  |

| Guo [57]      | DPCM + GOQ                             | var      | 800 E   | YUV420                | ASIC    | 40     | 300    | 2.05        | 4.95           | _                |

|               |                                        |          | 1600 D  |                       |         |        |        | 2.60        | 9.75           |                  |

| Lian [87]     | custom + ExpGR                         | var      | 1540 E  | YUV420                | ASIC    | 65     | 578    | 5.3         | 36.5           | 192              |

|               | _                                      |          | 780 D   |                       |         |        | 599    | 5.0         | 34.7           | 256              |

| Kim [73]      | custom + GR-like                       | fix      | 1113 E  | RGBW                  | ASIC    | 130    | 167    | _           | 56.1           | 1K               |

|               |                                        |          | 1113 D  |                       |         |        |        |             | 39.6           | 0                |

| Kim [74]      | DWT + SPIHT                            | fix      | 440 E   | YCgCr422              | ASIC    | 130    | 143    | _           | 50.0           | _                |

|               |                                        |          | 477 D   |                       |         |        | 167    |             | 68.8           |                  |

|               |                                        |          | 354 E   |                       | FPGA    | X      | 115    | _           | _              | 0                |

|               |                                        |          | 397 D   |                       |         |        | 139    |             |                |                  |

| Kefalas [69]  | custom $^{\dagger}$ + DSU $^{\dagger}$ | var      | 124 E   | YCoCg422              | FPGA    | X      | 62     | _           | _              | _                |

|               |                                        |          | 62 E    | YCoCg444              |         |        |        |             |                |                  |

| Carneiro [25] | MED# + GR#                             | var      | 121 E   | _                     | FPGA    | X      | 30     | _           | _              | _                |

| Kim [70]      | MED# + GR#                             | var      | 120 E   | _                     | FPGA    | X      | _      | _           | _              | _                |

| Kau [68]      | MED# + GR#                             | var      | 113 E   | _                     | FPGA    | X      | 113    | _           | 1.55           | 13K <sup>‡</sup> |

| Alonso [6]    | LHE + Huff.                            | var      | 95 E    | YUV/gray              | FPGA    | X      | 95     | _           | 8.1            |                  |

| Chen [27]     | PEP + GR#                              | var      | 52 E    | 12-bit gray           | FPGA    | X      | _      | _           | _              | 264K             |

| Kamalavasan   |                                        |          |         | ,                     |         |        |        |             |                |                  |

| [67]          | DCT** + Huff.**                        | var      | 276 D   | _                     | FPGA    | X      | 200    | 900*        | 7.0            | 248K             |

| Kim [75]      | custom <sup>†</sup> + DSU <sup>†</sup> | var      | 246 D   | _                     | ASIC    | 65     | 82     | 62          | _              | _                |

|               |                                        |          | C       | 1 - 1                 | A7      |        |        |             |                |                  |

| 1st author    | A 1                                    | anith    |         | andalone SV<br>en. TP |         |        | Platf. | Мо          | dal            | +Ca              |

| ist author    | Alg                                    | gorithm  | L       |                       |         | rmat   | riati. | Mo          | uei †          | ‡Cores           |

| de Cea-Domi   | niquag [24] DU/T+                      | + BPC-I  | 2°C°    | (Mpx/<br>ar ~810°°    |         | recole | GPU    | GTX 1       | 000 T;         | 3584             |

| ue Cea-Domi   | ınquez [34] DWI.                       | + DPC-I  | aco V   | ar ~810°°<br>~760°°   |         | yscale | GPU    | GIXI        | UOU 11         | <i>ა</i> 584     |

| Bruns [23]    | DIII/T+                                | + EBCO   | т+      |                       |         |        | GPU    |             |                |                  |

| Diulis [25]   | DWI                                    | + EDCU   | VI V    | ar 186°<br>159°       |         |        | GPU    | _           |                | _                |

| Rubino [121]  | DWT :                                  | orderin  | o 177   |                       | E —     |        | CPU    | Cortex      | -A 53          | 4                |

| 141 Maria     | D W 1 +                                | oruciill | ь V     | 05                    |         |        | CIU    | Cortex      | . 1133         | 4                |

<sup>\*</sup>Dynamic power only, \*\*JPEG XT, \*JPEG 2000, \*+JPEG XS, \*JPEG-LS or LOCO-I, \*\*JPEG, †DSC,  $^{\ddagger}$  plus one row, °only one-way memory transfers, °°without memory transfers.

algorithm was motivated by its latency of only several pixel lines and visually lossless quality. The system was used for distributed streaming of a musical performance over 300 km with an end-to-end latency of approximately 5 ms. However, the authors do not provide throughput measurements, therefore, we omit this publication from Table 3.

TP denotes throughput where E, D, and S denote encoding, decoding, and full system throughput, respectively. Ga/LUT denotes either the number of gates (ASIC) or LUTs (FPGA). "Cores" denotes the number of CPU or GPU cores.

231:12 J. Žádník et al.

Fig. 3. Throughput of still image encoders (left) and decoders (right) compared to a compression ratio. Dotted lines represent multiple compression ratios reported over a range of values.

# 4.2 JPEG Variants

Three FPGA implementations of a JPEG-LS encoder were presented by Kim et al. [70], Kau and Lin [68] and Carneiro et al. [25]. Both References [68, 70] used a pipelined architecture while Reference [25] presented a parallel architecture for better scalability. LOCO-I, the core of the JPEG LS algorithm, was also implemented by Chen et al. [27] with a parallel error prediction (PEP).

Bruns et al. [23] evaluated different CPU/GPU co-processing models for post-compression rate-distortion optimization (PCRD-Opt) and packetization routines of JPEG 2000. The authors concluded that all coding steps should be executed on the GPU for the highest throughput. The throughput values in Table 2 refer to the low-bitrate (100 Mb/s, upper) and high-bitrate (2500 Mb/s, lower) scenarios reported in the publication. The authors reported that performing the whole encoding on a GPU reduces the device-to-host data transfers significantly.

A GPU implementation of JPEG 2000, proposed by de Cea-Dominiquez [34], replaced the embedded block coding with optimized truncation (EBCOT) entropy coding by a custom bit plane parallel coder called BPC-PaCo [44] and a bit stream tightening algorithm. The authors reported only a grayscale throughput; The corresponding throughput of an 8-bit RGB image would be 800/3 = 267 Mpx/s. Also, the reported throughput does not take memory transfers to/from a GPU into account.

Kamalavasan et al. [67] proposed an FPGA JPEG XT decoder targeting decompression of 4K HDR images at 30 FPS in VR headsets. JPEG XT is a backwards-compatible extension to the original JPEG standard. The authors chose this standard for its lower computational complexity compared to JPEG 2000.

#### 4.3 Frame Memory Compression

Guo et al. [55, 56] proposed a lossless embedded compression method based on multi-mode differential pulse code modulation (DPCM) and averaging (MDA) prediction followed by a semi-fixed length (SFL) coding. The length of a SFL-coded partition can be read from a fixed-length part of the partition, thus decreasing the number of data dependencies within the partition compared to a conventional variable-length coding. The basic processing unit is an  $8 \times 8$  pixel block.

Kim et al. [74] proposed FPGA and ASIC implementations of a lossy frame memory compression (FMC) based on a discrete wavelet transform (DWT) and a 1D set partitioning in hierarchical trees (SPIHT). Contrary to the usual dynamic order of SPIHT, the encoder produces a fixed-length

output and therefore has a fixed compression ratio and higher processing speed. By minimizing dependencies between different algorithm passes, the authors achieved a throughput of about one bit-plane per cycle. The results are obtained with a block size  $1 \times 64$  and DWT decomposition level 3, evaluated on a Kodak dataset [48] transformed and subsampled into a YCbCr 4:2:2 format.

The previous design was improved by Kim et al. [72] by dividing a larger block into sub-blocks and processing them in parallel by small SPIHT processing elements. The results were obtained with a block size  $8 \times 8$  and DWT decomposition level 2.

Another work by Kim et al. [73] introduced a lossy compression scheme for RGBW images. The algorithm consists of two custom RGBW prediction steps followed by a fixed-length Golomb-Rice coding. A coding block size  $32 \times 1$  was used to obtain the results. Apart from a lossy mode, the algorithm can support lossless encoding as well.

A lossless FMC was proposed by Lian et al. [87]. Compared to previous works (e.g., Reference [56]), the implementation supports higher bit depths (such as 10 or 12 bits/sample) without a quality degradation and requires less memory. The authors developed a directional prediction method followed by a dynamic unary/Exp-Golomb-Rice coding and implemented the algorithm as two-core to maximize the throughput. The implementation uses encoding partition size  $16 \times 16$  for luma and  $8 \times 8$  for chroma channels.

Guo et al. [57] proposed a DPCM-based compression method where DPCM-predicted values are coded with a lossy gradient-oriented quantization (GOQ) coding. The choice of optimizing for a minimal gradient error was motivated by the fact that in computer vision applications the gradient information is more important. The encoder reads the input in  $n \times 1$  sub-blocks and reorders them into  $n \times k$  blocks suitable for vision processing. Because of that, the decoder reads its input in a block-based order.

# 4.4 Mezzanine Compression

Bruns et al. [24] proposed a GPU-based JPEG XS decoder. All decoding steps were performed on the GPU except for the initial depacketization, which was performed on a CPU due to its serial nature. To fully utilize the GPU and maximize the throughput, the computing kernels operate on the whole frame, thus sacrificing the low latency potential of the algorithm. The GPU-CPU memory transfer was a bottleneck for an unsubsampled 4K video with a bit depth of more than 8 bits. Compression ratios in Figure 3 were calculated from reported bits per pixel (bpp) values and 12 bits/channel video.

Kim et al. [75] proposed an ASIC implementation of a DSC decoder aiming for high power-efficiency. The work concentrates mostly on optimizing the line buffer, which was shown to be a major bottleneck in both area and power consumption.

Kefalas and Theodoridis [69] proposed an FPGA implementation of a DSC encoder without any external memory requirements. The encoder achieves a latency of less than one line. The achieved throughput is twice as high for 4:2:2- and 4:2:0-subsampled video than without subsampling.

#### 4.5 Other

Alonso et al. [6] proposed an FPGA implementation of a logarithmical hopping encoding (LHE) prediction and quantization algorithm [9]. For the entropy coding step, the authors chose Huffman coding. Because the prediction is calculated as an average of the top and left pixels, the predicted value depends on the previous line of the image (as well as on the previous pixel of the current line). The authors demonstrated the algorithm's low complexity and memory requirements by implementing it on a small-factor FPGA-based system on chip (SoC) with a low resource consumption but still achieving enough throughput to stream 1080p video with a latency of 23 clock cycles.

231:14 J. Žádník et al.

Rubino et al. [120, 121] proposed a novel image compression algorithm depth embedded block tree (DEBT) in the context of underwater robotics applications. DEBT is a DWT-based progressive compression scheme that does not have an explicit entropy coding step. Instead, it scans the list of the transform coefficients ordered by their significance, sending the most significant elements first. According to the authors, the algorithm is highly parallelizable. An implementation of DEBT on a Raspberry Pi 3 embedded computer can achieve 30 FPS at 1080p resolution.

### 4.6 Summary

None of the results except Reference [60] (discussed in Section 6.1) and Reference [138] explicitly state full-system latency measurements. In the case of hardware implementations, the authors often report the length of the underlying pipelined architecture in clock cycles, which can be used to determine the resulting latency of the encoder/decoder. Software implementations only report encoding times for the whole image, therefore a latency of one frame has to be assumed.

As shown in Table 2, fixed-function ASIC or FPGA implementations of FMC are the fastest [55–57, 73, 74, 87]. Combined with low latency and good visual quality, they can be seen as a viable target for *ultra-low latency* video coding applications. However, the low compression ratio limits their usability to high-bandwidth transfer channels.

Only References [73, 74] implement fixed-length coding. This property is important in case any of these algorithms were implemented as software encoders, as fixed-length coding allows predictive memory allocations and simplifies the decoding process.

The results of Reference [24] showed that optimizing for maximum throughput might come at the expense of not achieving a sub-frame latency, which is one of the defining features of mezzanine codecs.

Some slower results come from implementations on small-scale embedded devices with a limited computational capacity [6, 121].

An apparent overall trend is to move away from typical entropy coding algorithms and focus on simpler solutions with fewer data dependencies. For applications following a co-processing execution model (most notably CPU-GPU), memory transfers between the device and the host can be a bottleneck.

#### 5 HYBRID VIDEO COMPRESSION

Before reviewing the existing implementations, in Section 5.1, we shortly analyze the underlying complexity of the algorithms used in hybrid video codecs. This is possible, because algorithms presented in this subsection share similar coding principles, unlike, e.g., still image coding (Section 4). Furthermore, the complexity of dedicated video codecs is generally higher compared to other categories, thus giving a non-exhaustive overview of the underlying algorithms might provide a better insight into the possible limitations.

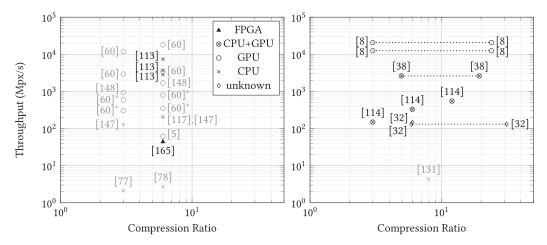

Publications reporting *motion-to-photon latency* of a full video system are presented in Section 5.2. The rest of the results is split into *Intra-frame Compression* (Section 5.3) and *Inter-frame Compression* (Section 5.4) depending on whether the implementation uses only intra-frame prediction or also inter-frame prediction. The division to intra-only and inter-frame coding is based on the fact that inter-frame prediction significantly increases the algorithm's complexity, data dependencies, and memory requirements to improve the coding efficiency. Results that do not fit any of the categories (e.g., because it is not clear whether they include inter-frame prediction or not) are reported in Section 5.5.

Table 3 shows a summary of the collected results. The pixel format column indicating the color space and bit-depth was omitted as most of the reviewed publications did not mention it

specifically. However, the most common video configuration corresponds to the High Efficiency Video Coding (HEVC) main profile, which assumes YUV420 format with a bit depth of 8.

Table 4 shows Bjøntegaard metric [17] results from those publications that report them. Bjøntegaard metric calculates average PSNR (BD-PSNR) and bitrate (BD-Rate) difference between two rate-distortion curves. Other error metrics can be considered for the BD-Rate calculation, but we consider only PSNR unless noted otherwise. In the table, the reference column denotes the source of the reference rate-distortion curve—an HEVC or a AVC reference software (HM or JM, respectively) or an x265 open-source encoder [155].

# 5.1 Computational Complexity Analysis

Bossen et al. [19] provided an overview of HEVC complexity compared to AVC and described the reference HEVC software encoder and decoder. While the decoding complexity is designed to be similar to the previous-generation AVC format, a full-featured HEVC encoder is significantly more complex to meet the design goal of doubling the compression efficiency. Vanne et al. [139] conducted a rate-distortion-complexity analysis of HEVC against AVC. In the analysis, HEVC showed a 23–40% BD-Rate improvement at the cost of 3.2–1.2× encoding and 2.0–1.4× decoding overhead, depending on the test condition. Corrêa et al. [31] studied HEVC encoder complexity and concluded that just by selecting the right parameters, the encoding complexity can be decreased significantly without a significant efficiency cost.

Similar to HEVC, VVC increased the encoding complexity compared to its predecessor. According to Mercat et al. [96], the encoding efficiency (BD-Rate) of the reference VVC test model (VTM) compared to the reference HEVC model (HM) improved by 23–33.1% at the cost of 34–7.5× encoding complexity depending on the test condition. The authors reported a constant 1.8× increase of the decoding complexity. Similar results were reported by Siqueira et al. [128] and Pakdaman et al. [106]. Cerveira et al. [26] conducted a similar analysis focusing on memory usage profiling.

Multiple studies also included the AV1 codec in their comparisons: [52, 81, 94]. According to García-Lucas et al. [52], AV1 reference encoder does not outperform the HEVC reference encoder in terms of coding efficiency, despite the higher encoding complexity. However, both Mansri et al. [94] and Laude et al. [81] report AV1 as more efficient than HEVC. Saldanha et al. [122] conducted a review on hardware implementations of AV1 and VVC coding tools. The authors concluded that in the case of AV1, there are no hardware-based solutions for 2D hybrid transforms supporting any of the 16 allowed combinations. In the case of VVC, the authors claim that hardware implementations of inter prediction are still missing.

The next paragraphs provide a short overview of complexity reduction and dedicated acceleration of hybrid coding modules. Because considering all modules is out of the scope of this survey, we focus only on those commonly reported as the most expensive in the literature (e.g., References [19, 96, 106, 139]).

Inter prediction. Usually, inter prediction is reported as the most computationally expensive step, strongly affected by the quantization parameter (QP) value. Unlike its predecessor, HEVC adopted recursive splitting of macroblocks into coding units (CUs) and then into intra/inter prediction units. To reduce the added complexity, Shen et al. [126] proposed a CU split decision and early termination method for HEVC achieving 42/41% savings of encoding time at the cost of 1.49/1.15% of BD-Rate and 0.049/0.037% BD-PSNR increase. Shen et al. [127] proposed an inter-mode decision algorithm based on a statistical analysis. The authors saved 49–52% of the encoding time at a 0.60–0.88% BD-Rate increase. Another acceleration strategy is to offload the full inter prediction step, or a part of it, to a GPU [53, 58, 134] or an FPGA [10, 12]. A comprehensive review by Zhang et al. [164] covers literature on inter prediction of HEVC up to the year 2019.

231:16 J. Žádník et al.

Table 3. Comparison of Surveyed Hybrid Video Coding Implementations

| 1-4                           | C+ J         | n 1    | TP             | Full S          | ystem               | Di               |                             | D 1: I                   | `i      |

|-------------------------------|--------------|--------|----------------|-----------------|---------------------|------------------|-----------------------------|--------------------------|---------|

| 1st author                    | Standard     | Pred.  | (Mpx/s)        |                 | Encoan              | ng Device        |                             | Decoding I               | Device  |

| Viitamäki [140]               | HEVC         | intra  | 829 S          |                 | n E5-2699v4         | + 2x Arria       | 10                          | 3x laptop                |         |

|                               |              |        | 747 S          |                 |                     |                  |                             | 1 1                      |         |

| Tu [137]                      | AVC*         | _      | 442 S          |                 | 300k + NVID         | IA Titan X       | p hwenc                     | HMD                      |         |

| Kim [71]                      | HEVC/SHVC*   |        | 126 S          |                 | 700HQ               |                  |                             | Galaxy S7 + i7           |         |

| Pitkänen [112]                | HEVC*        |        | 62 S           |                 | 320HK               |                  |                             | Galaxy S8 SoC            |         |

| Fouladi [47]                  | VP8          |        | 55 S           | Xeoi            | n E3-1240v5         |                  |                             | Xeon E3-1240             | V5      |

|                               |              |        | (              | o-Pro           | cessing             |                  |                             |                          |         |

| 1st author                    | Standard     | l Pre  |                |                 | Type                |                  | Host                        | Dev                      | ice     |

| C::: 11 [100]                 | LIEUO        |        | (Mpx           |                 | ODII EDO A          | V T              | 25.0400.4                   | 0 4 : 1                  |         |

| Sjövall [129]<br>Takano [134] | HEVC<br>HEVC | intr   |                |                 | CPU+FPGA<br>CPU+GPU |                  | E5-2680v4<br>n E5-2667v     | 2x Arria 1<br>2x Titan 2 |         |

| Grossi [53]                   | VP8          | inte   |                | -               | CPU+GPU<br>CPU+GPU  |                  | E5-2620v3                   | GeForce (                |         |

| Adeyemi-Ejeye [3              |              | —      |                |                 | CPU+GPU             |                  | 23-202073                   | NVIDIA                   | J1A 700 |

| Wang [145]                    | HEVC         | inte   |                |                 | CPU+GPU             | Xeon I           | E5-2699v3                   | Titan X                  |         |

| Ayadi [11, 12]                | HEVC         | inte   |                |                 | CPU+FPGA            | Cortex           |                             | Kintex-7                 |         |

| Liu [91]                      | MV-HEV       | C inte | er 29          | 2 D             | CPU+FPGA            |                  | Zynq Ultr                   | aScale+ ZCU102           | 2       |

|                               |              |        | Çı             | andalo          | one HW              |                  |                             |                          |         |

| 1st author                    | Standard     | Pred.  | TP             | Type            |                     | Freq             | Power                       | Gates/LUTs               | Mem     |

| 157 4411101                   | o turraur a  | 1100.  | (Mpx/s)        | -) P            | (nm)                | (MHz)            | (mW)                        | $(\cdot 10^3)$           | (kB)    |

| Omori [103]                   | HEVC         | inter  | 995 E          | ASIC            | 28                  | 600              | 15,000                      |                          |         |

| Yang [158]                    | AVC          | _      | 553 E          | ASIC            | Titan X             | ( hwenc          |                             |                          |         |

|                               |              | _      | 202 E          | ASIC            |                     | hwenc            |                             |                          |         |

| ·                             |              | _      | 157 E          | ASIC            |                     | D 5000 hw        |                             |                          |         |

| Jiang [65]                    | AVC          | _      | 415 E          | ASIC            |                     | 080 hwenc        |                             |                          |         |

| V., [15/]                     | HEVC         |        | 586 D          | ASIC            |                     | 080 hwdec<br>350 | 103                         | 2 880                    | 117     |

| Xu [156]<br>Liu [90]          | HEVC         | inter  | 265 E<br>250 E | ASIC            |                     | 504              | 57                          | 2,880<br>3,550           | 172     |

| Pastuszak [110]               | HEVC         | intra  | 249 E          | ASIC            |                     | 200              | 273                         | 1,086                    | 52      |

| Tastuszak [TT0]               | TILVC        | mua    | 24) L          | FPG             |                     | 100              |                             | 93.2                     | 52      |

| Zhang [162]                   | HEVC         | intra  | 249 E          | ASIC            |                     | 320              | 236                         | 2,288                    | 120     |

| Zhang [163]                   | HEVC         | intra  | 249 E          | ASIC            | 90                  | 320              | 290                         | 2,186                    | 127     |

| Ding [36]                     | HEVC         | intra  | 124 E          | FPG             | A x                 | 175              | 2,337                       | 63.5                     | 62.3    |

| Zhang [162]                   | HEVC         | intra  | 93 E           | FPG             |                     | 120              | _                           | 201                      | 120     |

| Zhang [163]                   | HEVC         | intra  | 93 E           | FPG             |                     | 120              |                             | 196                      | 127     |

| Mochizuki [98]                | AVC          | _      | 750 D          | ASIC            | 16                  | 400              | 197                         |                          |         |

|                               |              |        | S              | tandal          | one SW              |                  |                             |                          |         |

| 1st author                    | Standar      | d P    | red.           | TP              | Type                |                  | Mode                        | 1                        | #Cores  |

|                               |              |        | (              | (Mpx/s)         |                     |                  |                             |                          | (used)  |

| Tang [136]                    | HEVC*        |        | -              | 252 S           |                     | i7-67            |                             |                          | 4 (1)   |

| Huang [61]                    | AVC          |        | nter           | 72 E            |                     |                  | Quad Core                   | e 3.3GHz                 | 4       |

| Jiang [64]                    | HEVC         |        | nter           | 52 E            |                     |                  | 320C6678                    |                          | 8       |

| Wieckowski [150]<br>Zhu [166] | VVC<br>VVC   |        | nter<br>nter   | ~684 D<br>537 D |                     | 19-99<br>i7-97   | 80HK                        |                          | 8 (8)   |

| Gudumasu [54]                 | VVC          |        | nter           | 193 D           |                     | i9-99            |                             |                          | 10 (10) |

| Zhang [161]                   | AVS2         |        | iter           | 131 D           |                     |                  | ex-A57 + C                  | Cortex-A53               | 4+4 (4) |

| Wang [146]                    | AVS3         |        | nter           | 70 D            |                     |                  | $\frac{ex-A73}{ex-A73} + C$ |                          | 4+4 (1) |

|                               | -1.00        |        |                | , , ,           |                     | 2310             |                             |                          | (*)     |

$<sup>^*360^\</sup>circ$  video;  $^+$  only one-way memory transfers.

TP denotes throughput where E, D, and S denote encoding, decoding and full system throughput. "cores" denotes the number of CPU cores. "hwenc" and "hwdec" denote the usage of a GPU-integrated hardware encoder or decoder.

| 1st author      | Standard   | TP      | BD-Rate | BD-PSNR | Reference |

|-----------------|------------|---------|---------|---------|-----------|

| Tot dadioi      | otanaara   | (Mpx/s) | (%)     | (dB)    | reference |

| Takano [134]    | HEVC inter | 498 E   | 7.5     | _       | x265      |

| Tang [136]      | HEVC       | 252 S   | -10.7   | 0.33*   | _         |

| Zhang [162]     | HEVC intra | 249 E   | 4.39    | -0.21   | HM 15.0   |

| Zhang [163]     | HEVC intra | 249 E   | 2.79    | -0.13   | HM 15.0   |

| Pastuszak [110] | HEVC intra | 249 E   | 5.46    | -0.13   | HM 16     |

| Ding [36]       | HEVC intra | 124 E   | 10.5    | _       | HM        |

| Zhang [162]     | HEVC intra | 93.3 E  | 4.39    | -0.21   | HM 15.0   |

| Zhang [163]     | HEVC intra | 93.3 E  | 2.79    | -0.13   | HM 15.0   |

| Huang [61]      | AVC inter  | 72.4 E  | -18.1   | 0.93    | JM 19.0   |

|                 |            |         | -22.9   | 1.24    |           |

| Jiang [64]      | HEVC inter | 52.1 E  | _       | -0.93   | HM 10.0   |

|                 |            |         |         |         |           |

Table 4. Quality and Bitrate Comparison of Publications That Report BD-Rate or BD-PSNR

Intra prediction. The overall complexity of an encoder can be decreased by disabling the inter prediction and using the "all-intra" mode. In such a case, inter prediction overhead is zero and most of the computational burden lies on transform and quantization, intra prediction, entropy coding, and in-loop filtering.

Cho and Kim [29] proposed a decision strategy for early CU split and pruning decisions of HEVC intra coding based on a rate-distortion cost estimation. The combined method yielded an encoding time savings of approximately 50% with only 0.6% BD-Rate increase. Zhang and Ma [159] proposed a two-stage intra mode decision strategy that achieved 60% encoding time savings at the cost of 1.0% BD-Rate increase.

Compared to HEVC, the complexity of VVC intra prediction increased significantly by expanding the number of block partitionings and directional prediction modes and introducing new tools. Yang et al. [157] reduced the intra precision complexity of VVC by proposing a low-complexity coding tree unit partitioning and intra prediction mode decision scheme, achieving 63% encoding time savings at the cost of 1.93% BD-Rate increase over the reference VTM encoder. Lei et al. [84] addressed the increased coding tree unit partitioning complexity by pruning redundant partitions and deciding on the binary/ternary splitting direction in advance. This greatly reduces the number of modes to be searched, resulting in a 41% reduction of the encoding time and only a 0.84% increase of bitrate, compared to VTM. Dong et al. [39] reduced the VVC intra prediction complexity by pruning and early termination of non-important prediction modes. The authors achieved up to 53% encoding time savings at the cost of 1.08% BD-Rate increase. Li et al. [86] developed a tunable decision model for estimating the VVC CU partition allowing for early termination. The achieved encoding time savings range between 23–68% at the cost of 0.56–2.6% BD-Rate increase. A deep learning method for predicting the CU partitioning of VVC was presented by Li et al. [85]. The authors managed to reduce the overall encoding time by 45–67% with only a 1.3–3.2% BD-Rate increase.

Entropy coding. Entropy encoding and decoding present a challenge due to its serial nature and high branch divergence [145]. For this reason, Sjövall et al. [129] leave the CABAC encoding on

<sup>\*</sup>spherical PSNR.

231:18 J. Žádník et al.

the CPU side, together with other control logic, in their FPGA-based HEVC encoder. Similarly, a GPU-based HEVC decoder by Wang et al. [145] also leaves the CABAC decoding on the CPU side while the rest of the algorithm is implemented on a GPU. Despite the serial nature of CABAC, there have been efforts to reduce its data dependencies (Pastuszak [108, 109]) and increase its parallelism (Menasri et al. [95]). Notably, [108] achieves a throughput of 13.4 bins/cycle—high enough to encode high tier level 6.2 video (i.e., equivalent of 8K at 120 FPS). To the best of our knowledge, no literature has been published targeting the computational complexity of entropy coding specifically for VVC. However, as both HEVC and VVC use CABAC, improvements made for HEVC entropy coding are likely to be applicable also in the VVC context.

# 5.2 Implementations Reporting Latency

Tu et al. [137] proposed a  $360^{\circ}$  VR video viewing system with AVC coding and a  $3,840 \times 1,920$  resolution operating at 60 FPS. Video is generated with six GoPro cameras, encoded on a GPU-equipped desktop computer, and sent over a wireless network to be displayed on an HMD. The authors measured the latency as approximately 500 and 160 ms with and without a wireless network and display overhead, respectively. For encoding, the authors used hardware codec integrated within the GPU and accelerated some preprocessing steps with compute unified device architecture (CUDA).

Yang et al. [158] proposed a desktop screen sharing system with AVC compression. To save the computation time, the authors exploited high temporal inter-frame redundancy and low-noise characteristics typical for screen content. The encoding was performed by up to four GPU-integrated hardware encoders. The results presented in Table 3 correspond to a high screen activity over the whole 4K screen as this scenario better corresponds to a general video streaming. The authors achieved 17–25 ms  $motion-to-photon\ latency$  on a high-end workstation with a 4K screen capture over a wired network for low-high screen activity. Over the wireless network, the authors achieved 33–65 ms latency for a 2,736  $\times$  1,824 resolution.

Fouladi et al. [47] proposed Salsify—a real-time video conferencing architecture using a VP8 codec and a custom network transport protocol. The authors achieved 449 ms *motion-to-photon latency* over an emulated long-term evolution (LTE) network channel. The Salsify system combines a packet congestion control and a video codec rate control into a single algorithm to prevent them from disrupting each other.

Viitanen et al. [142] proposed a VR gaming cloud-edge system. The source 360° 1080p video is generated on a server running a game. Each frame is split into slices, which are encoded independently, each by its own instance of an open-source Kvazaar HEVC encoder [141], making use of WPP. The encoded video is streamed over a Gigabit Ethernet and decoded on the client with Open-HEVC software decoder [105]. The client laptop accepts control from and sends display frames to an HMD device. The authors were able to achieve close to 30 ms *motion-to-photon latency* while the system can maintain 30 FPS.

A direct continuation of Reference [142] is presented by Pitkänen et al. [112]. Instead of a laptop client, the authors used a smartphone mounted as an HMD and connected via a standard WiFi network. The authors achieved the same video throughput with a *motion-to-photon latency* close to 50 ms.

Tang et al. [136] proposed an omnidirectional stereoscopic video (ODSV) system achieving 2.2 s *motion-to-photon latency* and 0.5 s encoding latency. The relatively high system latency is caused by the complicated nature of the ODSV optical flow calculations. Based on the application and the presence of wireless network modules, we assume a wireless network was used even though this information was not clearly stated in the publication. Nevertheless, the system can maintain 30

FPS at  $4,096 \times 2,048$  resolution with encoding performed by a modified x265 HEVC encoder [155] running on a single thread.

### 5.3 Intra-frame Compression