Ida Wik

# FREQUENCY AND PULSE GENERATION FEATURES IN A MULTIFUNCTIONAL FIELD CALIBRATOR

Master's Thesis Faculty of Information Technology and Communication Sciences Examiners: Professor Karri Palovuori and University Lecturer Erja Sipilä September 2022

## ABSTRACT

Ida Wik: frequency and pulse generation features in a multifunctional field calibrator Master's Thesis Tampere University Master's programme in electrical engineering September 2022

The aim of the Thesis was to investigate improvements that could be made for frequency and pulse generation features of a next-generation multifunctional field calibrator as well as to suggests how the found improvements could be implemented. The improvement investigation was done by reviewing the frequency and pulse generation specifications of multifunctional calibrators that were on the market during the writing process of the Thesis. In addition to that, a customer needs analysis was performed by interviewing experts, and by analyzing customers' feedback. Based on the results of the investigation, it can be concluded that the frequency and amplitude range and resolution of the current solution by Beamex is competitive and do not require alternation. However, the selection of generatable waveforms could be improved by adding a sine wave generation possibility into the frequency generation function. The current solution is only capable of generating symmetric and positive square waves. Furthermore, some requests for dual pulse generation were found during the investigation.

The main focus in the solution design process was the sine wave generation because the dual pulse generation can be utilized easily if the next-generation multifunctional field calibrator has a modular structure. In that case, the number of frequency and pulse generation channels in the calibrator can be increased by adding multiple frequency and pulse generation modules into the calibrator. On the other hand, adding a sine wave generation option to the system is more complicated. Two possible solution suggestions for sine wave generation were designed and evaluated in the present thesis. One solution is based on direct digital synthesis and another one on usage of timer, registers, and direct memory access feature of a microcontroller. In theory, both of the solution suggestions should be able to generate square, pulse, and sine waves. However, by evaluating the solution suggestions, it can be said that the option to generate sine wave generation might not be that high. Hence, it should be re-evaluated if it is profitable to add a sine wave option to the frequency generation.

Keywords: signal generation, direct digital synthesis, microcontroller, direct memory access, frequency generation, pulse generation, multifunctional field calibration.

The originality of this Thesis has been checked using the Turnitin Originality Check service.

## TIIVISTELMÄ

Ida Wik: Taajuus- ja pulssigenerointiominaisuudet kenttäkalibraattorissa Diplomityö Tampereen yliopisto Sähkötekniikan DI-ohjelma Syyskuu 2022

Tämän diplomityön tarkoitus oli etsiä mahdollisia parannusehdotuksia kenttäkalibraattorin taajuus- ja pulssigenerointiin. Lisäksi työssä tutkittiin, kuinka löydetyt parannusehdotukset pystyttäisiin toteuttamaan Beamexin seuraavan sukupolven kenttäkalibraattorissa. Parannusehdotusten etsinnässä käytettiin kolmea metodia: diplomityön kirjoitusprosessin aikana markkinoilla olevien kalibraattoreiden vertailua, alan ammattilaisten haastattelua, sekä asiakaspalautteen analysointia. Näiden metodien avulla saatiin selville, että Beamexin nykyisen kenttäkalibraattorin taajuus- ja pulssigenerointiominaisuuden ulostulon taajuus- ja amplitudialue, sekä niiden resoluutiot ovat sopivia ja kilpailukykyisiä. Sen sijaan parannuskohdat löytyivät generoitavista aaltomuodoista, nykyinen kenttäkalibraattori kykenee generoimaan vain symmetristä ja positiivista kanttiaaltoa, mutta tutkimuksen perustella asiakkailla voisi olla kysyntää myös siniaallon generoinnille, sekä mahdollisuudelle generoida kahta eri pulssijaksoa samanaikaisesti kahdella eri kanavalla.

Työssä keskityttiin suurimmaksi osaksi tutkimaan, kuinka siniaallon generointi voitaisiin lisätä taajuusgenerointiominaisuuteen. Sillä käyttämällä modulaarista rakennetta seuraavan sukupolven kenttäkalibraattorissa, useampikanavainen signaalin generointi olisi yksinkertaisesti toteutettavissa lisäämällä useampia signaalingenerointimoduuleja kalibraattoriin. Sen sijaan siniaallon generointiominaisuuden lisääminen kalibraattoriin on paljon monimutkaisempaa toteuttaa. Tässä työssä esitellään ja analysoidaan kaksi ratkaisua, joilla olisi kanttiaallon lisäksi mahdollista generoida siniaaltoja. Nämä ratkaisut ovat digitaaliseen taajuussynteesin perustuva ratkaisu, sekä mikrokontrollerin kelloa, rekistereitä, ja oikosiirtoa hyödyntävä ratkaisu. Työssä todetaan, että teoriassa molemmat ratkaisut ovat toimivia sekä siniaallon että kanttiaallon generointiin. Kuitenkin ratkaisuja analysoidessa on selvästi nähtävissä, että siniaallon generointimahdollisuuden lisääminen taajuusgenerointiin monimutkaistaisi systeemiä, sekä kasvattaisi sen kustannuksia. Lisäksi asiakkaiden kysyntä siniaallon generoinnille ei todennäköisesti ole niin suuri, että yllä mainittuja siniaallon genreointiin liittyviä ratkaisuja olisi kannattavaa tuottaa. Tätä tulisi kuitenkin vielä uudelleen arvioida tulevaisuudessa.

Avainsanat: signaalin generointi, digitaalinen taajuussynteesi, mikrokontrolleri, oikosiirto, taajuusgenerointi, pulssigenerointi, kenttäkalibraattori.

Tämän julkaisun alkuperäisyys on tarkastettu Turnitin OriginalityCheck –ohjelmalla.

## PREFACE

This Master's Thesis has been done as part of the research and development of the next-generation multifunctional calibrator by Beamex.

First of all, I want to thank Beamex for giving me this opportunity. Also, I want to thank all my colleagues at Beamex for the support and help I received during the writing process of this Thesis. Especially, I want to thank everyone who participated in the interviews, as well as Mats and Markku who helped me to understand some more difficult technical questions which I faced during the designing process. Furthermore, I want to thank Petteri, supervisor of this Thesis from Beamex, for the excellent guidance. Additionally, I thank Karri and Erja, supervisors and examiners of the Thesis, for all the corrections and comments.

Lastly, I want to thank my spouse and my bunny for motivating and supporting me throughout this writing process.

Tampere, 16 September 2022

lda Wik

# CONTENTS

| 1. INTRODUCTION                                     |                                         |    |

|-----------------------------------------------------|-----------------------------------------|----|

| 2.BASICS                                            | OF CALIBRATION                          | 3  |

| 2.1                                                 | Performing a Simple Calibration         | 3  |

| 2.2                                                 | Analyzing Results of Calibration        | 4  |

| 2.3                                                 | Different Types of Calibration          | 6  |

| 3.BASICS                                            | OF SIGNAL GENERATION                    | 8  |

| 3.1                                                 | Analog Signal Generation                | 8  |

| 3.2                                                 | Digital Signal Generation               | 12 |

| 4. NEEDS AND REQUIREMENTS FOR THE SIGNAL GENERATION |                                         |    |

| 4.1                                                 | Current Solutions                       | 25 |

| 4.2                                                 | Customer Needs Analysis                 | 27 |

| 4.3                                                 | Specification Suggestion                | 32 |

| 5.SOLUTIC                                           | N SUGGESTIONS                           | 35 |

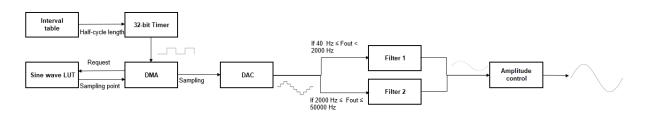

| 5.1                                                 | Direct Digital Synthesis Based Solution | 35 |

| 5.2                                                 | Microcontroller based solution          | 38 |

| 5.3                                                 | Comparison Between the Solutions        | 50 |

| 6.CONCLUSIONS                                       |                                         |    |

| REFERENCES                                          |                                         |    |

APPENDIX A: CODE FOR COUNTING THE OUTPUT FREQUENCY RESOLUTION OF THE SQUARE WAVE GENERATION APPENDIX B: NETLIST FOR FILTER 1 SIMULATION IN LTSPICE APPENDIX C: NETLIST FOR FILTER 2 SIMULATION IN LTSPICE APPENDIX D: CODE FOR COUNTING THE OUTPUT FREQUENCY RESOLUTION OF THE SINE WAVE GENERATION

# LIST OF FIGURES

| Figure 1.<br>Figure 2.<br>Figure 3. | Both cases of the zero error drew into the input-output curve [2]<br>Both cases of the span error drew into the input-output curve [2]<br>Both cases of the linearization error drew in the input-output curve                             | 5      |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Figure 4.                           | [2]<br>A feedback amplifier circuit [6]                                                                                                                                                                                                    | 6<br>9 |

| Figure 5.                           | The relationship between the voltage across the capacitor (black)<br>and the output voltage of the comparator (red). The $V_o$ is the<br>output voltage of the comparator, and the $V_{th}$ is the threshold<br>voltage. [edited from [6]] |        |

| Figure 6.                           | An example circuit of an astable multi-vibrator [7].                                                                                                                                                                                       | 11     |

| Figure 7.                           | Slew rate, glitch, settling time (t <sub>settling</sub> ), and clock or data feedthrough illustrated in a voltage–time curve of a DAC's output                                                                                             |        |

|                                     | [17]                                                                                                                                                                                                                                       | -      |

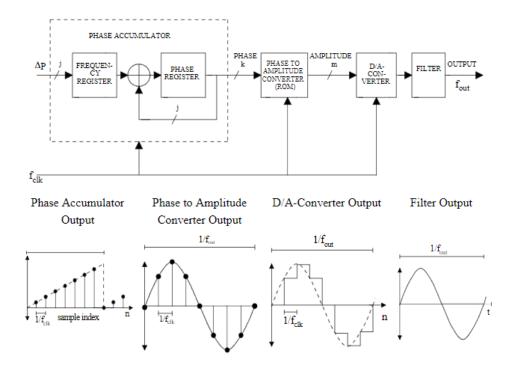

| Figure 8.                           | A block diagram of a conventional DDS [17]                                                                                                                                                                                                 | 20     |

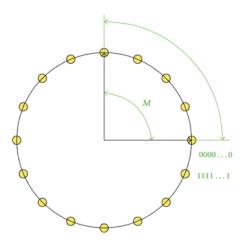

| Figure 9.                           | The operation principle of phase accumulator can be explained by<br>using a phase wheel [27].                                                                                                                                              | 21     |

| Figure 10.                          | A simplified block diagram of the system. F <sub>out</sub> in the diagram is the desired output frequency                                                                                                                                  | 45     |

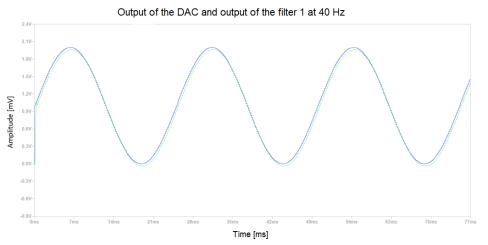

| Figure 11.                          | The blue signal is ouput of the DAC, and the green signal is the output of the filter 1 at 40 Hz.                                                                                                                                          | 47     |

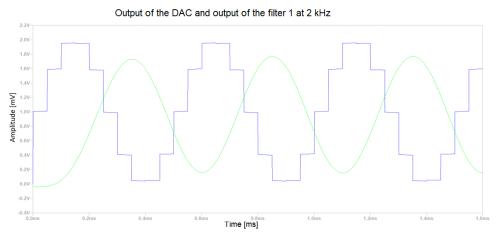

| Figure 12.                          | The blue signals is ouput of the DAC, and the green signal is the output of the filter 1 at 2 kHz                                                                                                                                          | 47     |

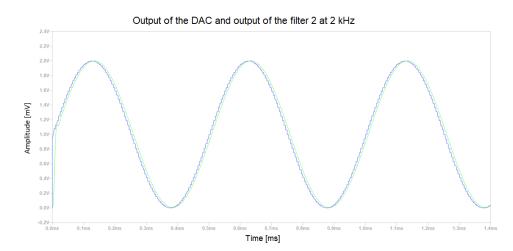

| Figure 13.                          | The blue signals is ouput of the DAC, and the green signal is the output of the filter 2 at 2 kHz.                                                                                                                                         | 47     |

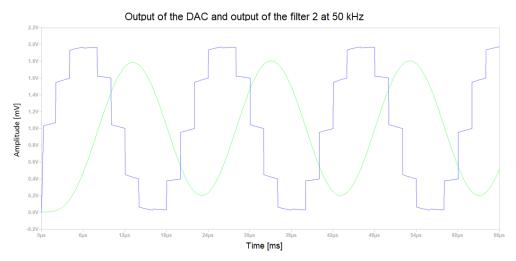

| Figure 14.                          | The blue signals is ouput of the DAC and the green signal is the output of the filter 2 at 50 kHz.                                                                                                                                         | 48     |

|                                     |                                                                                                                                                                                                                                            |        |

# LIST OF SYMBOLS AND ABBREVIATIONS

| ADC                                                                                                                                                                                                                | Analog-to-digital converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ASRC                                                                                                                                                                                                               | Arbitrary sample rate conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ATEX                                                                                                                                                                                                               | Appareils destinés à être utilisés en atmosphères explosives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| DAC                                                                                                                                                                                                                | Digital-to-analog converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| DDS                                                                                                                                                                                                                | Direct digital synthesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DFT                                                                                                                                                                                                                | Discrete Fourier transformation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DMA                                                                                                                                                                                                                | Direct memory access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| FFT                                                                                                                                                                                                                | Fast Fourier transformation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| FET                                                                                                                                                                                                                | Field effect transistors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| FIR                                                                                                                                                                                                                | Finite-impulse response                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| FPGA                                                                                                                                                                                                               | Field-programmable gate array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| IC                                                                                                                                                                                                                 | Integrated circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| IEEE                                                                                                                                                                                                               | Institution of electrical and electronics engineers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| IUC                                                                                                                                                                                                                | Instrument under calibration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| LabVIEW                                                                                                                                                                                                            | Laboratory virtual instrument engineering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| LSB                                                                                                                                                                                                                | Least significant bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| LC                                                                                                                                                                                                                 | Inductor-capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| MCU                                                                                                                                                                                                                | Microcontroller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| LUT                                                                                                                                                                                                                | Look-up table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SMD                                                                                                                                                                                                                | Surface-mount device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Op-amp                                                                                                                                                                                                             | Operational amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PC                                                                                                                                                                                                                 | Personal computer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| RF                                                                                                                                                                                                                 | Radio frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RC                                                                                                                                                                                                                 | Resistor-capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ROM                                                                                                                                                                                                                | Read only memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| RPM                                                                                                                                                                                                                | Revolutions per minute                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| THD                                                                                                                                                                                                                | Total harmonic distortion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| VCO                                                                                                                                                                                                                | Voltage-controlled oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| $egin{aligned} A \ B \ f_{clk} \ f_{in} \ f_s \ f_{out} \ i \ k \ K_m \ M \ m \ n \ n_c \ N_{half-period} \ N_{period} \ N_{period} \ N_{period} \ n_{tot} \ n_{sample} \ r \ T_M \ t_{measurement} \end{aligned}$ | Gain of the amplifier<br>Gain of the feedback circuit<br>Clock frequency<br>Input frequency<br>Sampling frequency<br>Output frequency<br>Ordinal number of the sampling point in a look-up table<br>Number of bits used in ROM<br>Frequency bin with the largest magnitude<br>Phase increment word<br>Size of the timer's reload register<br>Number of bits used in phase accumulator<br>Number of bits used in phase accumulator<br>Number of periods in the sequence<br>Number of counted half-periods<br>Number of counted periods<br>Number of samples of sine wave in on period<br>The ordinary number of sine wave sample<br>Desired output frequency resolution<br>Mean period<br>Measurement time |

| t <sub>pulse</sub>  | Duration of one clock pulse |

|---------------------|-----------------------------|

| t <sub>sample</sub> | Time between samples        |

| $V_i$               | Input voltage               |

| $V_{ ho ho}$        | Peak-to-peak voltage        |

| V <sub>th</sub>     | Threshold voltage           |

| Vo                  | Output voltage              |

## 1. INTRODUCTION

Accurate and traceable measurements are key components in many of the manufacturers' processes, they verify that the processes are done correctly and within standards which assures safety, as well as the high and uniform quality of the processes and their end products. Regular calibrations of the measurement instruments are required to ensure the accuracy of the measurements. In the field, manufacturers can calibrate their measuring instruments with a multifunctional field calibrator, which can be used to perform calibrations, adjustments, and testing of various kinds of measurement instruments. One of the functions of the multifunctional calibrator is frequency and pulse generation capability. Moreover, frequency generation can be seen as the generation of periodical signals, such as square and sine waves, which amplitude and frequency can be adjusted. Likewise, a pulse generation can be seen as the generation of pulse train which amplitude, duty-cycle, and quantity in the sequence can be adjusted.

The present Thesis is done as a part of the development of a next generation multifunctional field calibrator by Beamex, which is a company that specializes in developing and manufacturing calibrators and calibration software. Moreover, the aim of the Thesis is to investigate how the frequency and pulse generation features could be improved in this next generation calibrator. In order to find the improvements that could be added to the next generation calibrator, the frequency and pulse generation capabilities of multifunctional field calibrators presently on the market are examined. In addition to that, a customer needs analysis about these features is performed, to directly find out in which applications customers of Beamex are using the signal generation features of the calibrator and if there are some gaps in these functions. Furthermore, the internal needs of the company are noted, in the search for improvements. These requirements are for example to have a simple and profitable solution for frequency and pulse generation. In this analysis, also the frequency measuring and pulse counting features of the multifunctional calibrator are taken into account, as they are strongly connected to the pulse and frequency generation. After identifying the improvement possibilities, two possible solution designs are suggested.

The second and third chapter of the Thesis are used to cover the background theory of the subject of the Thesis. More specifically, the second chapter discusses the basics of calibration as it is the framework of this Thesis. In the third chapter, the theories of both solution suggestions are covered, and related studies are presented and discussed. The fourth chapter includes the plan for improvement investigation and its results. Furthermore, at the end of chapter four, the specification for frequency and pulse generation is presented. After the theory of the solution suggestions are presented and the desired improvements are listed, the designs for solution suggestions are presented, their pros and cons are weighted, also the solutions are compared to each other in the fifth chapter. Additionally, the open-ended questions about the solutions which require further testing are listed in the fifth chapter. Finally, the Thesis is summarized in the final chapter.

## 2. BASICS OF CALIBRATION

The present chapter is the first part of the theoretical background included in this Thesis. The framework of the Thesis is in the field of calibration. Therefore, it is important that the reader is familiarized with the concept of calibration, which is often misused in the spoken language. After reading through this chapter, the reader understands the basic terminology related to calibration, how to perform a simple calibration, what to do when calibration fails, and what are the common error sources in calibration process.

### 2.1 Performing a Simple Calibration

Calibration is a process in which the accuracy of a measurement instrument is checked by comparing the instrument's outputs induced by known inputs to a traceable reference standard or device. Accuracy describes how close the measured value is to the reference value. A device that provides the reference standard can be called a calibrator. [1], [2] Usually in the calibration process, the output of the instrument under calibration (IUC) is checked at multiple points to cover the whole calibration range. The calibration range defines, what is the output of the instrument for a certain input. It should not be confused with the instrument range which determines the maximum and minimum values that can be measured by the device.[2]

Let's use an example of calibration of a pressure transmitter to explain the terminology of calibration in more detail. The calibration of a pressure transmitter is a very classical example, which is often used for this purpose, e.g., Cable M. [2] and Kuphaldt T. [3] have used it in their books. In this example, let the instrument range of a pressure transmitter be from 0 bar to 20 bar, and the output range is from 4 mA (milliamps) to 20 mA. Hence, if the input is 0 bar the output is 4 mA, and if the input is 20 bar the output is 20 mA. However, an engineer who installed the pressure transmitter has set the calibration range to be from 0 bar to 10 bar. Therefore, if the input is 0 bar the output is 10 bar the output will be 20 mA. With these settings, only the pressure from 0 bar to 10 bar can be measured accurately, although the pressure transmitter. To cover the whole calibration range three different inputs are used 0, 5, and 10 bar. The reference standard states that the outputs of the IUC for the above inputs should be 4 mA, 12 mA, and 20 mA. After the outputs of the IUC are collected, they can be compared to the corresponding reference values.

#### 2.2 Analyzing Results of Calibration

After learning to perform a simple calibrate, it is time to learn how to analyze the result of the calibration. The collected output values of the IUC are accepted if they are within the tolerance limits of the reference value. Moreover, the tolerance limits used in the calibration, define how much an acceptable output value of the IUC can deviate from the corresponding reference value. Furthermore, the used tolerance level depends on factors such as criticality of the monitored process, capability of the test equipment, unity with the similar instruments, and manufacturer's tolerance specification. For instance, in this example the reference value at 0 bar is 4.0 mA and the tolerance level is  $\pm$  0.10 mA. Thus, all the output values between 3.9 mA and 4.1 mA at 0 bar are acceptable. If all the calibration values are within the tolerance limits the calibration is successful, and the device does not need any adjusting to increase the accuracy of it. [3]

The calibration is failed, in other words out of tolerance, if the outputs of the IUC are not within the tolerance limits of the reference values. In this case, the first thing to do, is to make sure that the calibration was executed correctly. After that, one can investigate the suitability of the tolerance level. For example, a question such as "does the tolerance level match with the criticality of the application?" could be asked. In addition to that, one should analyze the calibration uncertainty factors which are elements that affect the accuracy of the measurement result, e.g., environmental factors such as temperature changes, human errors such as incorrectly executed calibration, and the uncertainty of the used reference standard. The uncertainty of reference standard can be evaluated by employing the traceability of the reference standard. It must be bear in mind that, every reference standard needs to be periodically calibrated with a higher-level reference standard, and the higher-level standard needs to be calibrated with an even higher-level reference standard, and so forth. The highest-level reference standard is the international reference standard. Tractability defines this path of calibrations with their uncertainties from the used reference standard back to the international reference standard. [2], [4]

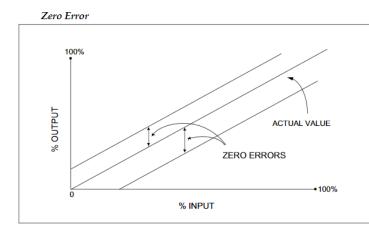

Some common instrument errors, which cause calibration to be out of tolerance, are zero error, span error, and linearization error. These errors can be identified and analyzed by drawing the output values of the IUC to known inputs, and the corresponding reference values to an input-output curve. In zero error, all the measured values are sifted due to a nonzero output response to a zero input. In the case of the pressure transmitter this means that the output is less or more than 4 mA at 0 bar. In figure 1, both cases of the zero error in the input-output curve.

Figure 1. Both cases of the zero error drew into the input-output curve [2].

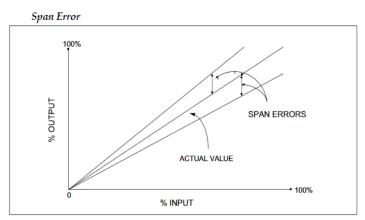

A span error is an error in the slope of the input-output function. Hence, the error is magnified as the output and input values increase. The Span error of the pressure transmitter could be seen as follows, the output is 4 mA at 0 bar but at 5 bar the output is more or less than 12 mA, and at 10 bar the input is less than 20 mA or is not measured, as the maximum output has been reached before the maximum input value. In Figure 2 both cases of the span error are presented.

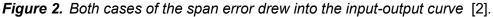

A linearization error is seen as nonlinearity of the input-output-curve. In the case of the pressure transmitter, the output for 0 bar is 4 mA and the output for 10 bar is 20 mA, but the output for 5 bar is less or more than 12 mA. Both cases of the linearization error are illustrated in Figure 3.

**Figure 3.** Both cases of the linearization error drew in the input-output curve [2]. All the mentioned errors can be corrected by adjusting the IUC. The zero error can be corrected by producing a parallel shift of the input-output curve. By adjusting the slope of the input-output function, the span error is fixed. Linearity adjustment can use to correct the linearization error. However, in case of large linearization error, the only option is to replace the instrument. [2]

#### 2.3 Different Types of Calibration

In this subchapter, the questions about how and when to calibrate are discussed. Calibration needs to be repeated occasionally, because factors such as environment, drift, and process changes influence the measurement accuracy of the instrument. Suitable calibration intervals can be designed based on aspects such as criticality of the monitored process, manufacturer's recommendations, standards, intervals in similar instruments, and the previous calibrations of the instrument. [1],[4]

How the calibration is performed depends on the instrument and its location. An instrument can be linear, non-linear, or discrete. The earlier mentioned pressure transmitter is an example of calibration of a linear instrument. Calibration of a non-linear instrument, such as a square root characterizer, is more complicated than calibration of a linear instrument as more calibration points are required. Often nonlinear instruments have their own manufacturer's recommended calibration procedures. For discrete instruments, e.g., process switch, the purpose of calibration is to check that the state of instrument is changed at the correct input value. Moreover, the location of the instrument influences the calibration procedure, which can be dived into field and bench calibration based on the location in which the calibration is performed. Field calibration is performed at the site in which the instrument has been installed, which allows calibrating at the instrument operating environment. When the instrument is removed from its installation

place to be calibrated or a new instrument is calibrated before installation the procedure is referred to as bench calibration. [2], [3]

Furthermore, calibration can be done as a loop calibration or individual instrument calibration. In the individual instrument calibration, the input and output of the IUC are disconnected from the systems it operates, and the input is connected to a source that produces controlled known values. The individual instrument calibration allows adjusting of the specific instrument. However, it does not consider the tolerance of the whole loop, for that loop calibration, is needed. As the name implies, in the loop calibration, IUC kept connected to the other components in the loop. By doing so, the tolerance of the whole loop in the calibration can be analyzed. If adjustments are made after loop calibration, they will made for the whole loop. [2], [3]

## 3. BASICS OF SIGNAL GENERATION

The present chapter is dived into two subchapters: analog and digital signal generation. The fully analog signal generation methods are based on oscillators and are too preliminary to be employed as a signal generator in a multifunctional calibrator. However, they can be used to discuss some of the main problems that typically occur during the designing process of a signal generator. Some common problems are such as narrow output frequency range, as well as instability of the output frequency and amplitude. Most of the problems can be overcome by utilizing digital signal generation instead of analog signal generation. However, the conversion from digital to analog brings its own challenges, which are discussed in the second subchapter, which focuses on digital signal generation. Moreover, the second subchapter covers the operation principles of two digital signal generation methods which are later suggested as solutions for the current problem.

### 3.1 Analog Signal Generation

The traditional signal generators are mainly based on oscillators, which are circuits that consist of an amplifier and a feedback loop. The output of an oscillator is an oscillating signal, which can be either a sine, a square, or a triangular wave, depending on the oscillator type. Furthermore, oscillators can be divided into two categories; harmonic oscillators and relaxation oscillators which are presented in separate sub subchapters.

#### 3.1.1 Harmonic Oscillators

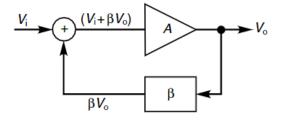

Harmonic oscillators are sinusoidal signal generators, which types, and working principles are discussed in this sub subchapter. The basic operating principles of harmonic oscillators can be understood by viewing the harmonic oscillator as an amplifier with a feedback loop, and by applying the Barkhausen criterion which states that the output of a feedback amplifier circuit, presented in Figure 4, is sinusoidal if the gain of the full circuit is one and the phase shift between input voltage  $V_i$  and output voltage  $V_o$  is zero. The gain of the full circuit, which is also referred to as loop gain, consists of the gain of the amplifier *A* and the gain of the feedback circuit  $\beta$ . Moreover, if the loop gain is less than one the output is damped, and if the loop gain is much more than one the output signal is no more sinusoidal. The frequency at which the oscillator oscillator is compared to a solution of the solution of the signal is no more sinusoidal.

called as oscillator's resonance frequency and it is determined by the feedback loop as it induces a phase shift to the  $V_o$  in order to match it with the phase of  $V_i$ . [5], [6]

Figure 4. A feedback amplifier circuit [6].

Moreover, the harmonic oscillators can be divided into subcategories, and in this section, three common types of harmonic oscillators are presented. The first presented harmonic oscillator type is an oscillator whose feedback loop is a resistance-capacitor (RC) circuit, or an inductor-capacitor (LC) circuit. The amplifying element of RC or LC circuits can be e.g., an operational amplifier (op-amp), or a field-effect transistor (FET). Some wellknown examples of this type of harmonic oscillator are a Wien bridge oscillator which is based on an RC circuit, and a Colpitts oscillator which is based on an LC circuit. As discussed earlier, the values of feedback loop components determine the resonance frequency of the oscillator. Therefore, components of the feedback loop must be altered, if it is desired to change the output frequency of the RC or LC circuit oscillator. In addition to being highly impractical to change the component values manually, the resistors and reactive components of the feedback loop cause instability of the output frequency and amplitude as the component values may vary due to the temperature, and input voltage changes. Furthermore, there can be small inaccuracies in the component values leading to an inaccurate output frequency. Moreover, the component value variations change the feedback loop gain to be less or more than one which causes the output signal to be damped or lose its shape. [5], [6]

The next presented harmonic oscillator type is a voltage-controlled oscillator (VOC) which provides quicker and easier alternation of the output frequency than the oscillators based on an RC or LC circuit. As the name suggests, the output frequency of VCO is controlled by the input voltage. In theory, all the oscillators based on RC and LC circuits could be turned into VCOs by replacing a capacitor in the feedback network with a voltage-controlled capacitor whose capacitance is determined by the input voltage. Therefore, by changing the input voltage, the output frequency is altered.

The third oscillator type is crystal oscillators, which have a very stable resonance frequency, unlike the LC or RC-circuit oscillators. In crystal oscillators, the feedback loop is a piezoelectric circuit that consists of the piezoelectric material such as Quartz crystal. Moreover, by applying an alternating electrical field across the crystal, it begins to

oscillate at a frequency determined by the size of the crystal. This phenomenon is called the inverse piezoelectric effect. The output frequency of crystal oscillator is very stable because the size of the crystal determines the resonance frequency of the crystal oscillator. There are crystals available with resonance frequencies from 10 kHz to 100 MHz. In addition to the size of the crystal, small changes in the resonance frequency can be done by adding a tuning capacitor in series with the crystal. Similar to the oscillators based on an RC or LC circuit the output frequency of the crystal oscillator cannot be quickly changed. Hence, the crystal oscillator by itself is not a suitable solution for the signal generator which is used as test equipment. However, it can be used as a reference frequency for frequency synthesis. [5], [6]

### 3.1.2 Relaxation Oscillators

In this section, the second type of oscillator which is the relaxation oscillator is discussed. In addition to that, this section presents simple methods, how one can transform a square wave into a sine, or a triangular wave. The benefits of the relaxation oscillators are the possibility to generate different waveforms simultaneously, easy alternation of the output frequency, and good amplitude stability because the Barkhausen criterion is not implied. Also, a stable output frequency can be provided by using a cheap and simple integrated circuits (IC) such as the 555 timer in the oscillator circuit. However, most of the basic relaxation oscillators cannot generate frequencies below a few hertz, which is desirable in the case of the Thesis.

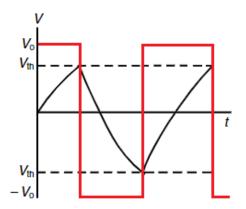

Relaxation oscillators are oscillators, which oscillation is based on charging and discharging of a capacitor. In these oscillators, a capacitor is charged through a resistor, and the voltage across the capacitor is monitored by a comparator which compares this voltage to a threshold voltage. The value of the threshold voltage is defined by the comparator's output voltage and voltage divider. When the voltage across the capacitor reaches the threshold voltage, the output voltage of the comparator, (which is also the output voltage of the whole circuit), becomes reversed. This leads to the threshold voltage becoming reversed, and the capacitor begins to discharge in order to reach the new threshold voltage. When it reaches the new threshold voltage, the output voltage of the comparator is reversed again, and a new cycle of charging and discharging of the capacitor begins. Figure 5 describes the relationship between the voltage across the capacitor and the output voltage of the comparator. The output frequency can be controlled by the charging current of the capacitor, as it determines the speed of the capacitor charging. [6], [7]

**Figure 5.** The relationship between the voltage across the capacitor (black) and the output voltage of the comparator (red). The V<sub>o</sub> is the output voltage of the comparator, and the V<sub>th</sub> is the threshold voltage. [edited from [6]].

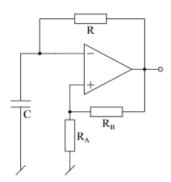

Figure 6 illustrates a simple relaxation oscillator circuit in which the comparator is based on an op-amp, and two resistors ( $R_A$  and  $R_B$ ). The threshold voltage is defined by the output voltage of the op-amp and the potential divider formed by  $R_A$  and  $R_B$ . The capacitor (C) is charged via the resistor (R). This type of oscillator circuit can be referred to as an astable multi-vibrator or a square wave generator. [6], [7]

Figure 6. An example circuit of an astable multi-vibrator [7].

A triangular wave can be obtained from the astable multivibrator described above, by connecting the output of the op-amp of the circuit to an integrator. An integrator is an op-amp whose output is the integral of the input voltage. Thus, a nonlinear increase or decrease in the input leads to a linear increase or decrease in the output. [5]–[7] Hence, if the input of the integrator is a square wave the output will be a triangular wave. In addition to relaxation oscillators, this technique could be applied to other signal generators whose output is a square wave to generate triangular waves. Furthermore, a sine wave can be produced from a triangular wave by a sine function network, which utilizes diodes' electrical characteristics of becoming slowly conductive. [5] Another option is to use lowpass filtering to produce a sine from square wave by removing harmonic components of the square wave. Both forementioned methods for converting

other waveforms are quite robust and are not effective for input signals with wide range of amplitudes and frequencies.

### 3.2 Digital Signal Generation

This subchapter presents more advanced methods for signal generation that are based on generating a signal digitally and then converting it to an analog signal. Circuits that consist of both analog and digital parts can be referred to as mixed-signal circuits. The benefits of implementing a signal generator with a mixed-signal circuit instead of with a fully analog circuit are a smaller size, higher output frequency accuracy, and improved output characteristics such as wider output frequency range. Moreover, two methods employing mixed-signal circuits for signal generation are discussed in this subchapter. These methods are a method based on a microcontroller (MCU) and a method based on a direct digital synthesis (DDS) chip. The main focus is on the DDS as there is more scientific discussion around it. However, before going into details of these methods in sub subchapters 3.2.2 and 3.2.3, a component that is often the main limiting factor in both of the methods is discussed in sub subchapter 3.2.1. This component is a digitalto-analog converter (DAC) which is used to convert a digital signal into an analog signal.

### 3.2.1 Digital-to-Analog Converter

It does not matter how pure, accurate, and easily adjustable output signal it is possible to be generated digitally if it cannot be converted to an analog signal without compromising the characteristics of the signal. Therefore, the DAC is a critical component in the mixed-signal signal generators, and the characteristics of the DAC that affect the final output signal must be understood before discussing the digital signal generation methods. The DACs can be separated into two classes based on the output of the DAC which can be current or voltage. However, in the discussion of the basic characteristics and working principles of DAC, the quantity of the output does not matter, hence, in this section only voltage output is discussed.

#### 3.2.1.1 Sampling Rate and Resolution

The influence of resolution and sampling rate of a DAC to the output signal of a signal generator are considered in this section. The resolution of a DAC is expressed as bits, e.g., a 16-bit DAC can generate 2<sup>16</sup> different output values between the maximum and minimum output which are defined by the reference voltage of the DAC. In other words, the resolution of the DAC defines the number of different output values that can be used to represent a cycle of waveform. Moreover, the sampling rate of the DAC affects the number of samples that can be employed to represent a cycle of a waveform, because

the sampling rate of the DAC defines the number of sampling points that can be generated in a second. Therefore, the sampling rate of the DAC sets the maximum output frequency which is half of the maximum sampling rate of the DAC. [5], [8] Sampling rate of the DAC can be also referred as DAC speed.

In addition to the DAC speed, the generated waveform sets further demands for the sampling rate and resolution, which can be understood by comparing the generation of square and sine wave to each other. The frequency and alternation of the amplitude of a square wave can be accurately represented with only two different values, high and low. Hence, square waves can be easily generated even with low resolution and sampling rate, as the DAC must only alternate between two different output values. On the other hand, only the frequency of a sine wave can be accurately represented with two sampling points per cycle. To represent the amplitude profile of the sine wave, more sampling points per cycle are required, in fact, a pure analog sine signal has an infinite number of amplitude values between its lowest and highest points.

In order to increase the number of sampling points per cycle of a sine wave, a study by Wang L. et al. [9] employed a method called a time-interleaving DAC. In which four DACs are used to generate one period of a sine wave. The first DAC generates a part of the sine wave that is from the beginning to quarter period, and the second DAC from quarter period to half period, and so forth. By applying this technique, one period of the sine wave has four times more voltage levels than a sine wave produced by a single DAC. However, the benefit of employing multiple DACs depends on the desired output frequency as the number of useable voltage levels decreases as the output frequency increases. Hence, the benefit of using multiple DACs increases as the output frequency increases. However, the noise increases as the number of employed DACs increases. Therefore, at low frequencies the usage of multiple DACs can decrease the quality of the output signal, due to the increased noise. [9]

One possible technique that can be used to maintain the quality of the sine wave through the whole output frequency range is to employ different sampling frequencies for different output frequencies. In other words, use lower sampling frequency to produce lower output frequencies, and so forth. A method, proposed by Wang L. and Zhao Y. [10] widened the output frequency range by utilizing an arbitrary sample rate conversion (ASRC) to change the sampling frequency of the DAC according to the output frequency. The ASCR algorithms employ integration oversampling and continuous-time resampling filters to resample a signal [11]. In the study of Wang L. and Zhao Y. [10] the system was successfully implemented with a field-programmable gate array (FPGA), and they suggest that based on the results of the experiment their method is effective. On the other hand, even if the highest possible resolution and sampling rate are applied in the sine wave generation, the output signal will still have the 'stepped' waveform appearance rather than continuous one. This is due to the sample-and-hold technique which DAC employs in the conversion process. In this technique the DAC holds the output at certain level for certain amount of time. This is not an issue in a square and pulse wave generation but becomes a problem in a sine wave generation as it induces high frequency components into the output signal. These components are called sin(x)/xroll of images, and their location in the frequency domain depends on the desired output frequency and the sampling frequency. The first image appears at sampling frequency deducted by the desired output frequency, hence by applying a lowpass filter with cutoff at the frequency of the first sin(x)/x roll image the output sine wave can be 'smoothed'. [5], [8], [12]

#### 3.2.1.2. Dynamic and Statical Errors of DAC

In addition to sampling rate and resolution of the DAC, the errors of the DAC affect the quality of the output signal. These errors can be divided into static and dynamic errors, and these errors are well-known and defined in datasheets of DACs. The statical characteristics of DAC that should be noted in the designing process of the signal generator are offset, gain error, and non-linearity. All of them can be obtained by comparing the ideal and actual transfer functions to each other. The transfer function describes the relationship between inputs and outputs of a system. The gain of the DAC can be seen as a slope of the transfer function. Therefore, the gain error is the difference between the slope of the ideal and actual transfer function. The offset error is the difference between a single point in the ideal and actual transfer function. [13] The gain and offset error of the DAC influence the amplitude accuracy of the output signal. The non-linearity of the DAC causes harmonic distortion in the signal. Distortion is the difference between an input waveform and an output waveform, and harmonics are frequencies that are integer multiples of the fundamental frequency. For example, if the fundamental frequency is 50 Hz, the 2<sup>nd</sup> harmonics is 100 Hz, the 3<sup>rd</sup> harmonics is 150 Hz, and so forth. With these definitions in mind, harmonic distortion can describe to be the amount of distortion in the output signal caused by the harmonics in the output signal. Hence, the output signal has the frequency components of the input signal, but also the harmonics of the input frequency components which induces the distortion. As the location of the harmonic components depends on the fundamental frequency, it is difficult to filter them out as the cutoff frequency should be adjusted every time the output frequency changes. Hence, it is easier to choose a DAC with good linear properties, than to try to filter out the harmonics. In addition to choosing DAC with good linear properties,

harmonic cancelation techniques can be employed to further decrease the harmonic components of the output signal. Total harmonic distortion (THD) is a percentage that defines the total amount of harmonic distortion in the output signal. Lower the percentage, less harmonic distortion in the signal. [5], [7], [13]

In the literature, different variations of harmonic cancelation techniques have been proposed. One popular harmonic cancelation technique that is described at least in studies [14]–[16] is to add periodical signal to its time-shifted and scaled versions with correct scaling factors that define the order harmonics that are canceled out. Malloug H. et al. [14] suggest that this technique can be implemented by generating phase-shifted digital square waves which are then combined and scaled to a sinusoidal signal by a summing network. For example, the study by Malloug H. et al. [16] applied phase-shift register to generate five time-shifted square waves and combined them with current-steering DAC with an output filter. The issue with this harmonic cancelation technique arises from the required high accuracy of the scaling factors. Malloug H. et al. [14] reported that even small errors in the scaling ratios between different phase-shifted signals reduce the effectiveness of this technique.

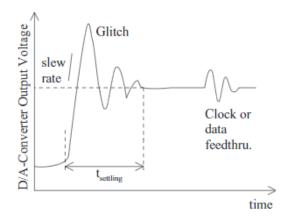

Dynamic errors of DACs are discussed in this paragraph and following paragraph. A slew rate of DAC is the maximum rate at which output of the DAC can be changed. Issue with slew rate is that if the slew rates of the increase and decrease are different, spurious harmonics (spurs) that are non-signal components that exists only in one frequency are induced to the output signal. The slew rate of increase is illustrated in Figure 7, also settling time is presented in that Figure. The settling time describes the time it takes for the output of the DAC to stabilities after it has been changed. It can be expressed as the time it takes to stabilize to a static value within a defined error band. For example, if the settling time is 1  $\mu$ s to  $\pm \frac{1}{2}$  least significant bit (LSB) it takes 1  $\mu$ s to stabilize to a static value with  $\pm \frac{1}{2}$  LSB error band. [13], [17] To have highly stable output frequency, the settling time should be as short as possible and the error band as small as possible. Moreover, the settling time influences the maximum DAC speed.

**Figure 7.** Slew rate, glitch, settling time (*t*<sub>settling</sub>), and clock or data feedthrough illustrated in a voltage–time curve of a DAC's output [17].

Furthermore, during the settling time, glitches can occur at the output, especially when there is a large change in the output. Glitches can be negative or positive, in Figure 7 positive glitch occurs during the settling time. The Glitch energy, also referred to as glitch impulse is the total area under the glitch in a voltage-time curve. The size of the glitches increases as the output frequency rises because there are fewer output samples of the DAC that can be used to present the digital input as an analog output. Study by Richen J. et al [18] propose three types of DAC architectures that reduce the size of the glitches. The dynamic characteristics of DAC that influence the quality of the output signal are slew rate, glitch energy, and settling time. The three types are a voltage-mode, a currentmode, and a current-steering DACs which all input gray code instead of the natural binary code. In gray code, the difference between two successive bits is only one bit, e.g., in 4bit natural binary code one is 0001 and two is 0010, but in gray code in one is 0001 and two is 0011. According to the Richen J. et al [18] by replacing the natural binary code input of DAC by gray code input the size of glitches are reduced. The reason for this, is that in gray code transient state of zero which occur switching the input values can be avoided, unlike in natural binary code. [18] In Figure 7, the clock or data feedthrough is also illustrated which is an interference in the DAC output signal caused by clock or/and data signals coupling to the DAC's output. Proper layout and fabrication methods can eliminate clock and data feedthrough. [13], [17]

#### 3.2.2 Microcontroller Based Method

A simple method for square wave generation with a MCU is to employ one of its timers to generate square waves at the desired frequency from the clock frequency. This technique can be explained by going through the operation principles of timer. A basic timer contains two registers; a current and reload register. The current register keeps track of time by counting the input clock pulses of the clock signal, and the reload register determines the length of the intervals between the output interrupts. Moreover, in a countdown timer, the current register counts from the value of the reload register to zero, and in a count-up counter from zero to the value of the reload register. [19] When the counter reaches zero or the value of the reload register, the state of the output changes. Hence, by controlling the value of the reload register, one can control the frequency of the output square wave of timer as the value of the reload register determines the number of input clock pulses that a half cycle of the output square wave consists of. Furthermore, the output frequency range of the timer depends on the value of the reload register and the input clock frequency. Therefore, the output frequency can be calculated by the following equation

$$f_{out} = \frac{f_{clk}}{m}$$

[20](1)

in which  $f_{out}$  is the output frequency,  $f_{clk}$  is the clock frequency, and *m* is the value of the reload register. The maximum value of the reload register depends on the size of the timer, e.g., in 16-bit timer it is 2<sup>16</sup>-1. The value for the *m* can be calculated by dividing the half period of the wanted output frequency by the period of the clock pulse and rounding it up to the closest integer. The duty cycle of the square wave can be altered to obtain pulse waves by separately defining the time for the high and low time. Furthermore, the value of the reload registers must be updated after every timer overflow, to set the length of the next half cycle.

Moreover, the resolution of the output frequency is the length of one clock pulse which is determined by the input clock frequency. Thus, with a higher clock frequency, a higher resolution can be achieved. However, as the clock frequency increases, also the minimum output frequency increases. Hence, the used clock frequency is often compromise between the output frequency range and the resolution. By increasing the size of the timer, it is possible to expand the output frequency range. One way to increase the timer size is to use a prescaler, which allows user to define the number of clock pulses that are counted as a one pulse by the timer. For example, it can be set that the value of the current register changes every fourth clock pulse.

Furthermore, the generated square wave can be used in the generation of other waveforms, such as a sine wave, by using it as a sampling frequency which determines the speed at which sampling points of a sine wave are transferred to a DAC. In this technique the sampling points of the desired waveform, which is a sine wave in this case, are stored in a look-up table (LUT). The values for the sampling points can be calculated by using following equation

$$y(n_{sample}) = \sin\left(n_{sample} * \frac{2\pi}{n_{tot}}\right)$$

(2)