Aarno Lindqvist

# DEVELOPING LOGIC SYNTHESIS FLOW FOR NVDLA IP

Master of Science Thesis

Faculty of Information Technology and Communication Sciences

Examiners: Prof. Timo Hämäläinen

M.Sc. Saman Payvar

May 2022

#### **ABSTRACT**

Aarno Lindqvist: Developing Logic Synthesis Flow for NVDLA IP Master of Science Thesis

Tampere University

Master's Degree Programme in Information Technology

May 2022

Modern digital devices require high computing performance; thus, markets have a huge demand for SoC. The most powerful SoC are implemented on ASIC chips since, it is the most cost-efficient technology when production volumes are high. An important step on ASIC design process is the logic synthesis. By utilizing dedicated software tool, it transfers RTL code into gate-level netlist. The logic synthesis process is executed multiple times alongside the RTL code development to meet the desired specifications for the chip.

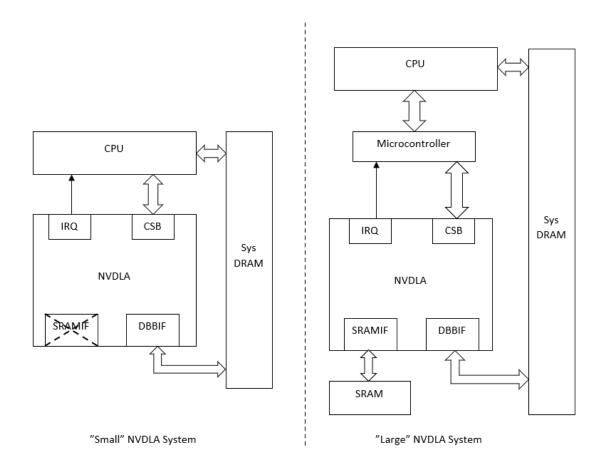

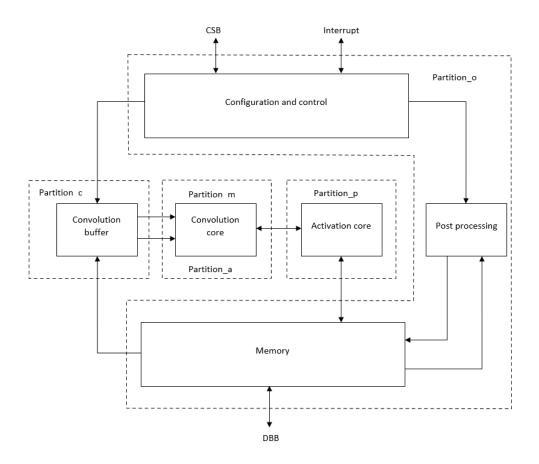

This thesis project used the NVDLA IP as a use case to execute logic synthesis. NVDLA is an open-source deep learning accelerator developed by NVIDIA. The design is able to execute CNNs making it efficient. Each component in the NVDLA can be configured independently, which make it flexible and cost effective. NVDLA software ecosystem has extensive cover of software features. NVDLA is divided into five partitions according to their functionality. Each partition is an individual top-level synthesis hierarchy.

The target of this thesis is to develop a logic synthesis flow for NVDLA in the company design environment. This was achieved by exploiting NVDLA design environment, company internal memory wrapper, and Synopsys Design Compiler and IC Compiler 2 tools to execute logic synthesis for TSMC 7 nm standard cell technology. All the used RTL codes and scripts were downloaded from NVDLA GitHub webpage. The memory wrapper was created by the company memory wrapper tool. It connects the NVDLA design and the RAM instances. The Design Compiler tool was used to generate the initial netlist for NVDLA partitions. The IC Compiler 2 tool was used to create individual floorplans for each partition. The generated DEF file was used for second pass synthesis to obtain the final logic synthesis results. The results demonstrate that the company design environment can be used to run synthesis for open-source IP blocks. Further, the developed flow provides a platform to exploit different kind of open-source IP's on industrial development environment since, it can generate synthesis results for 7 nm standard cell technology quickly.

Keywords: SoC, ASIC, Logic Synthesis, NVDLA, STA

The originality of this thesis has been checked using the Turnitin OriginalityCheck service.

# TIIVISTELMÄ

Aarno Lindqvist: Logiikka synteesi vuon kehittäminen NVDLA lohkolle Diplomityö Tampereen yliopisto Tietotekniikan diplomi-insinöörin tutkinko-ohjelma Toukokuu 2022

Nykyaikaiset digitaaliset laitteet tarvitsevat paljon laskentatehoa, näin ollen markkinoilla on suuri tarve järjestelmäpiireille. Kaikista tehokkaimmat järjestelmäpiirit toteutetaan ASIC piiriteknologialla, koska se on kaikista kustannustehokkain piiriteknologia vaihtoehto kun tuotanto määrät ovat suuria. Tärkeä vaihe ASIC kehitys prosessissa on logiikka synteesi. Hyödyntämällä räätälöityjä ohjelmistotyökaluja, se muuttaa RTL koodin porttitason piirikuvaukseksi. Logiikka synteesi prosessi toistetaan useasti RTL koodin kehityksen rinnalla, jotta piirille asetetut tekniset tavoitteet täyttyisivät mahdollisimman nopeasti.

Tämä diplomityö suoritti logiikka synteesin NVDLA prosessori lohkolle. NVDLA on avoimeen lähdekoodiin perustuva laitteistonkiihdytin, joka on tarkoitettu suorittamaan koneoppimisalgoritmeja. Tämä tekee siitä hyvin tehokkaan prosessori lohkon. Jokainen NVDLA:n sisäinen osa voidaan konfiguroida itsenäisesti, mikä tekee siitä joustavan ja kustannustehokkaan. Sen ohjelmisto ekosysteemi kattaa suuren määrän ohjelmisto-ominaisuuksia. NVDLA on jaettu viiteen osaan niiden toiminnallisuuden perusteella. Jokainen osa on itsenäinen ylätason synteesi hierarkia.

Tämän diplomityön tavoitteena oli kehittää logiikka synteesi vuo NVDLA prosessori lohkolle kohde yrityksen suunnitteluympäristössä. Tämä saavutettiin hyödyntämällä NVDLA suunnitteluympäristöä, yrityksen sisäistä muistikäärettä, ja Synopsyksen Design Compiler ja IC Compiler 2 työkaluja. Näiden avulla logiikka synteesi suoritettiin TSMC:n 7 nanometrin standardi soluteknologialle. Käytetyt RTL koodit ja skriptit ladattiin NVDLA GitHub verkkosivulta. Muistikääre luotiin yrityksen sisäisellä muistikääre työkalulla. Se yhdistää NVDLA lohkon RAM muisteihin. Design Compiler työkalua käytettiin ensimmäisen piirikuvauksen muodostamiseen. IC Compiler 2 työkalua käytettiin yksilöllisten pohjapiirrosten luomiseen jokaiselle osalle. Luotua DEF tiedosta hyödynnettiin toisella synteesi kerralla lopullisten synteesi tulosten saamiseksi. Tulokset osoittavat, että yrityksen suunnitteluympäristöä voidaan käyttää synteesi tulosten tuottamiseen avoimen lähdekoodin prosessori lohkoille. Näin ollen, kehitettyä vuota voidaan hyödyntää alustana erilaisten avoimen lähdekoodin prosessori lohkojen vertailuun teollisessa kehitysympäristössä. Sen avulla voidaan luoda synteesi tulokset 7 nanometrin standardi soluteknologialle nopeasti.

Avainsanat: Järjestelmäpiiri, ASIC, Logiikka synteesi, NVDLA, STA

Tämän julkaisun alkuperäisyys on tarkastettu Turnitin OriginalityCheck -ohjelmalla.

iii

#### **PREFACE**

This thesis work was done in the SoC organization of Nokia during 2021 and early 2022.

First, I would like to thank my supervisor Juha Liias for the opportunity to do the thesis at Nokia. I want to thank Prof. Timo Hämäläinen and M.Sc. Saman Payvar for their valuable feedback during the writing process. Especially I want to thank my colleague Ajay Ganesha for the excellent mentoring throughout the thesis project. Many thanks also to my colleagues Syed Gillani and Vishnu Shibu for their support in the project work.

Finally, I want to thank my family and friends for supporting me during my University studies.

Tampere, 12th May 2022

Aarno Lindqvist

# **TABLE OF CONTENTS**

| 1.INTRODUCTION                               | 1  |  |  |

|----------------------------------------------|----|--|--|

| 2.SYSTEM ON A CHIP DESIGN                    | 4  |  |  |

| 2.1 SoC                                      |    |  |  |

| 2.2 ASIC                                     |    |  |  |

| 2.2.1 Abstraction levels                     |    |  |  |

| 2.3 Logic synthesis                          | 9  |  |  |

| 2.3.1 EDA tool limitations                   |    |  |  |

| 2.3.2 Logic synthesis flow                   |    |  |  |

| 2.3.2.1 RT-level synthesis                   |    |  |  |

| 2.3.2.2 Module generator                     | 12 |  |  |

| 2.3.2.3 Gate-level synthesis                 |    |  |  |

| 2.3.2.4 Cell-level synthesis                 |    |  |  |

| 2.3.3 Efficient use of synthesis tool        |    |  |  |

| 2.3.4 Timing considerations                  |    |  |  |

| 2.3.5 Static timing analysis (STA)           |    |  |  |

| 2.4 Design Compiler (DC) synthesis flow      |    |  |  |

| 2.5 Synthesis in practise with DC            |    |  |  |

| 2.5.1 DC commands used during synthesis      | 27 |  |  |

| 2.6 Design optimization using DC             | 28 |  |  |

| 2.6.1 Design rule constraints (DRC)          |    |  |  |

| 2.6.2 Optimization constraints               |    |  |  |

| 2.6.3 Design optimization strategies         |    |  |  |

| 3.LITERATURE REVIEW                          |    |  |  |

| 4.NVDLA IMPLEMENTATION FLOW                  |    |  |  |

| 4.1 NVDLA                                    |    |  |  |

| 4.1.1 Hardware architecture                  |    |  |  |

| 4.1.2 Software design                        |    |  |  |

| 4.2 Implementation flow                      |    |  |  |

| 4.3 Detailed system description              |    |  |  |

| 4.3.1 Partition_m                            |    |  |  |

| 4.3.2 Partition_o                            |    |  |  |

| 4.3.3 Partition_p                            |    |  |  |

| 4.3.4 Partition_a                            |    |  |  |

| 4.3.5 Partition_c                            |    |  |  |

| 4.3.6 Memory wrapper                         |    |  |  |

| 5.SYNTHESIS RESULTS                          |    |  |  |

| 5.1 Power                                    |    |  |  |

| 5.2 Area                                     |    |  |  |

| 5.3 Timing                                   |    |  |  |

| 5.4 Comparison to literature                 |    |  |  |

| 5.5 Analysis of the developed synthesis flow |    |  |  |

| 6.CONCLUSIONS                                |    |  |  |

| DEEEDENCES 77                                |    |  |  |

# **LIST OF FIGURES**

| Figure 1.  | Basic ASIC design flow [21]                                       | 2  |

|------------|-------------------------------------------------------------------|----|

| Figure 2.  | Basic design elements of a SoC [1]                                |    |

| Figure 3.  | Digital ICs [2]                                                   | 6  |

| Figure 4.  | Logic synthesis flow [7]                                          | 11 |

| Figure 5.  | Modest hypothetical standard-cell library for ASIC technology [7] | 15 |

| Figure 6.  | Synthesis iterations in an area-delay space [7]                   |    |

| Figure 7.  | A basic synthesis flow. [9].                                      |    |

| Figure 8.  | Two different NVDLA systems [6]                                   |    |

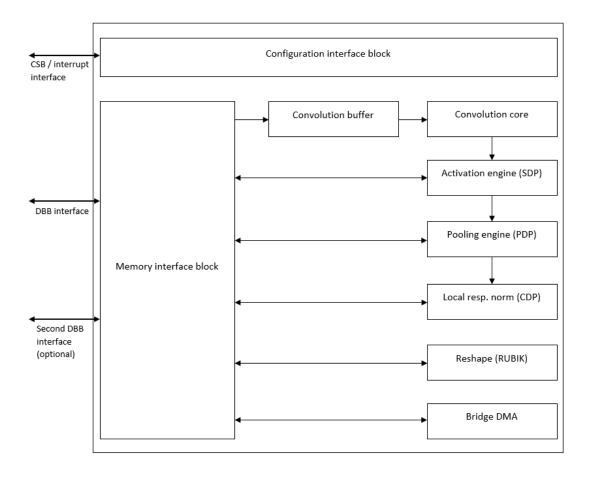

| Figure 9.  | Headless NVDLA architecture [6]                                   |    |

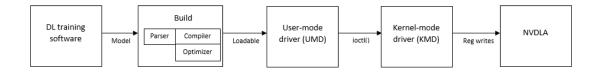

| Figure 10. | NVDLA system software dataflow [6]                                | 48 |

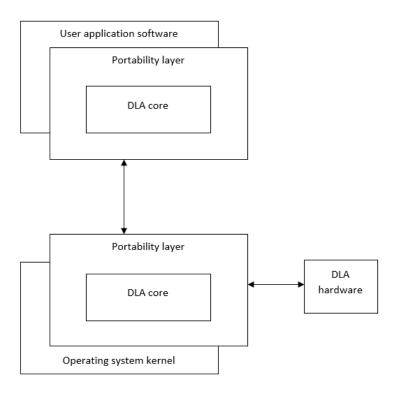

| Figure 11. | Visualization of portability layers in the NVDLA system [6]       | 50 |

| Figure 12. | The directory structure for logic synthesis [6]                   | 51 |

| Figure 13. | Output files of a synthesis run [6]                               | 53 |

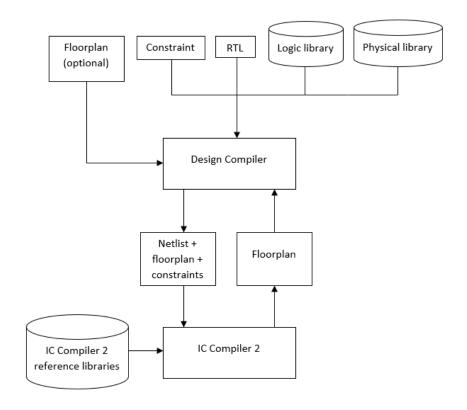

| Figure 14. | The floorplan exploration flow from DC to ICC 2 [9]               |    |

| Figure 15. | NVDLA top-level structure [10, 28]                                | 55 |

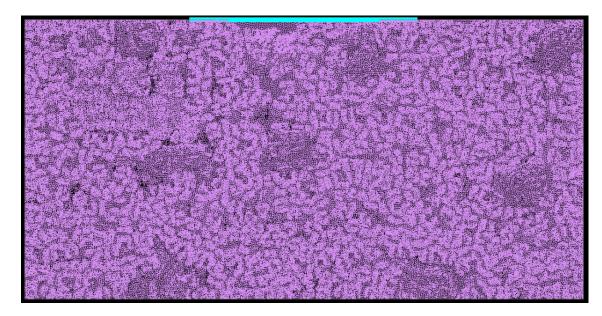

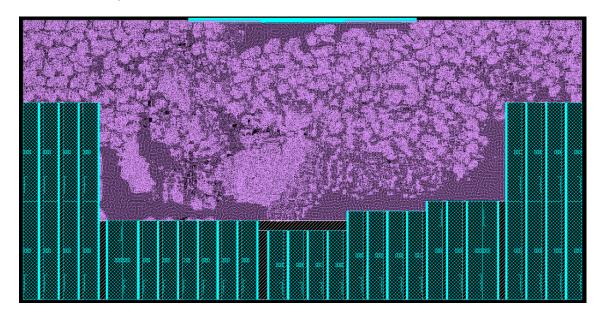

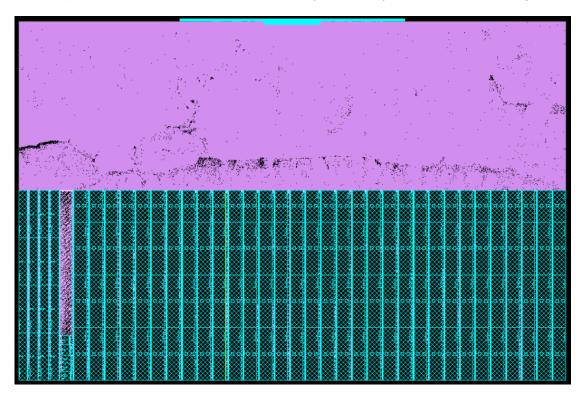

| Figure 16. | Layout picture of partition m                                     |    |

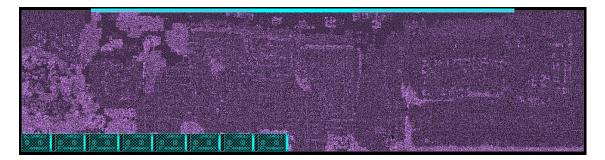

| Figure 17. | Layout picture of partition o                                     |    |

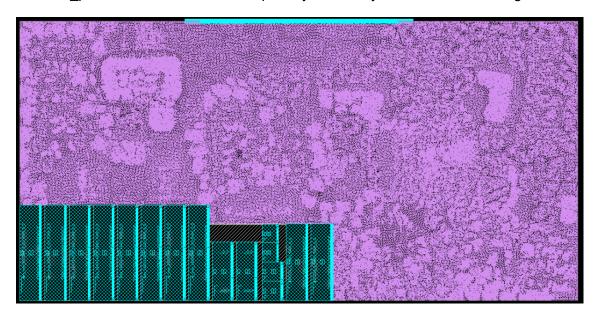

| Figure 18. | Layout picture of partition p                                     |    |

| Figure 19. | Layout picture of partition a                                     |    |

| Figure 20. | Layout picture of partition c                                     |    |

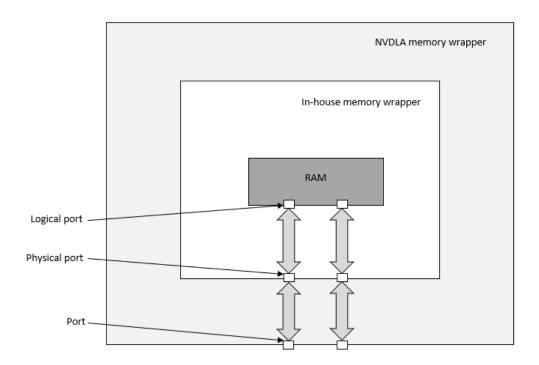

| Figure 21. | Memory wrapper                                                    |    |

|            |                                                                   |    |

#### LIST OF SYMBOLS AND ABBREVIATIONS

Al Artificial intelligence

AMBA Advanced microcontroller bus architecture

API Application programming interface

ARM Advanced RISC machines

ASIC Application specific integrated circuit

ASSP Application specific standard product

AXI Advanced extensible interface

BDMA Bridge direct memory access

CAD Computer aided design

CDP Cross-channel data processor

CE Communication element

CLPD Complex programmable logic device

CNN Convolutional neural network

CPU Central processing unit

CSB Configuration space bus

CTS Clock tree synthesis

DBBIF Data backbone interface

DC Design compiler

DFT Design for test

DL Deep learning

DLA Deep learning accelerator

DNN Deep neural network

DRAM Dynamic random-access memory

DRC Design rule constraint

DSP Digital signal processor

EDA Electronic design automation

FIFO First in first out

FPGA Field programmable gate array

RTOS Real time operating system kernel

HDL Hardware description language

I/O Input/Output

I2C Inter integrated circuit

IC Integrated circuit

IoT Internet of things

IP Intellectual property

IRQ External interrupt interface

KMD Kernel mode-driver LCD Liquid-crystal display

LRN Local response normalization

MAC Multiply-accumulate

NLR No local reuse

NoC Network on chip

NRE Non-recurring engineering

NVDLA Nvidia Neep learning accelerator

OCP Open core protocol

PCI Peripheral component interconnect

PDP Planar data processor PE Processing element

PLD Programmable logic devices

PReLU Parametric rectified linear unit

RAM Random access memory

RC Resistor-capacitor

ReLU Rectified linear unit

ROM Read only memory

RTL Register transfer level

SATA Serial AT attachment

SDP Single data processor

SIMD Single instruction, multiple data

SoC System on a chip SOP Sum of products

SPI Serial peripheral interface SRAM Static random-access memory

STA Static timing analysis

TCL Tool command language

TSCM Taiwan semiconductor manufacturing company

UMD User mode-driver USB Universal serial bus

VHDL Very high-speed hardware description language

V Voltage

nm nanometre

mm millimetre

mW milliwatt

#### 1. INTRODUCTION

The target of the thesis project is to develop a logic synthesis flow for NVDLA in the company design environment. The flow can be used to review different kind of IP's quickly. The idea is to utilize both publicly available and internal scripts and RTL designs as much as possible to develop the flow. This will be achieved by utilizing NVDLA design environment, company internal memory wrapper, and Synopsys Design Compiler and IC Compiler 2 tools to run logic synthesis for TSMC 7 nm standard cell technology. All the needed codes and scripts can be downloaded from NVDLA GitHub webpage. The company memory wrapper tool is utilized to generate a memory wrapper which is able to connect the NVDLA design with needed RAM instances. The Design Compiler is used to generate the initial netlists for NVDLA partitions. To improve the results a floorplan will be created for each partition with IC Compiler 2 tool. The generated DEF file is then used for second pass synthesis to obtain the final synthesis results.

The challenge in developing the flow is to integrate all the needed parts together: the NVDLA design, the memory wrapper and the memory instances with the synthesis scripts. Also, meeting the timing constraints is an issue which requires synthesis setup and floorplan explorations. As mentioned earlier the RTL codes of the NVDLA design and the reference synthesis scripts were readily available at the GitHub webpage. The principle of re-use was exploited. However, the scripts needs to be modified to be able to use them in this project. The memory wrapper will be created for this project. Memory instances has been acquired by the company from a vendor and will be utilized in this project. Each synthesis partitions need a floorplan; they will be created manually in this project. By implementing the above tasks, the result is a flow that can be used to evaluate different IP blocks for 7 nm standard cell technology. Further by optimizing the developed flow the synthesis results of NVDLA can be improved.

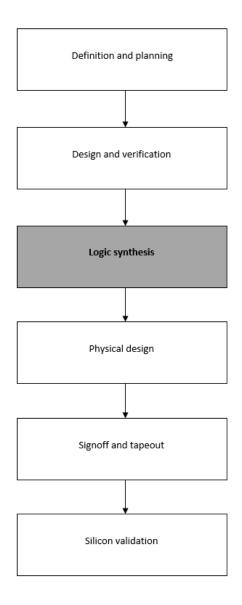

First, the ASIC design flow will be explained to get an idea about the field of the thesis project. The basic ASIC design flow is shown in Figure 1.

Figure 1. Basic ASIC design flow [21].

The focus area of this thesis project is the logic synthesis. It is important part of the ASIC design flow and is highlighted with grey background colour in Figure 1. The ASIC design process starts from marketing research and architecture specification based on the market requirements. Then the RTL code is designed and verified. The logic synthesis step transforms the RTL code into netlist which can be then processed to the form of real circuit in the physical design. After that the circuit is finalised and send to vendor for fabrication in the signoff and tapeout step. When the produced chip comes back from vendor, it is tested in silicon validation. After that the chip should be completed product.

Thesis is organized into 6 main sections 1. Introduction, 2. System on a Chip Design, 3. Literature review, 4. NVDLA Implementation flow, 5. Synthesis results, and 6. Conclusion. Section 2. contains theoretical background of System on Chip, ASICs, logic synthesis flow and related timing, Design compiler synthesis flow, Synthesis in practice

with DC, and design optimization with DC. Section 3. contains review of the related literature. Section 4. contains discussions about the NVDLA hardware architecture and software design, the implementation flow, and detailed system description. Section 5. present the synthesis results from power, area, and timing views. It also compares the results to literature and analyses the developed synthesis flow. Finally, section 6. concludes the thesis and discusses about the future works.

#### 2. SYSTEM ON A CHIP DESIGN

On the highest level this thesis is related to the system on a chip (SoC) design, which is implemented by utilizing ASIC technology. Modern SoCs are basically all around us in every day devices. Therefore, SoCs are studied first. After that ASIC technology is introduced and then the logic synthesis process is discussed in detail. Logic synthesis is the actual topic of this thesis project.

#### 2.1 SoC

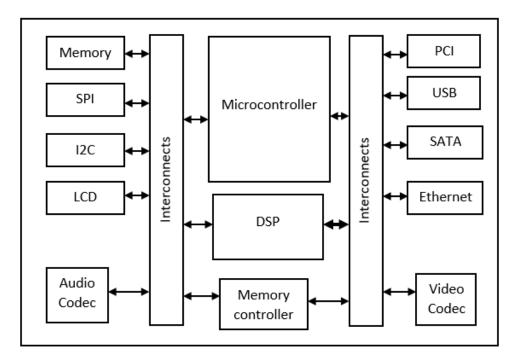

A SoC is set of processors, memories, and interconnections [3]. It is a computer system which is designed to implement an application specific functionality for some given application domain [3]. Most of the SoC designs are executed on ASIC or FPGA devices. The huge demand on markets like consumer electronics, automobiles and telecommunication has led to a need for more and more advanced electronic devices. At the same time the development of IC technology on the past 40 years has given the solution to that demand, thus the empirical law of Moore [2,4]. Historically, the concept of a computer has been a single processor combined with a memory on a board [3]. On modern IC chips there can be up to 10 billion transistors which allows the integration of complete complex systems on a chip [2]. Usually, a SoC contains signal processing elements, hardware accelerator, microprocessor or microcontroller cores and memories [2]. The function of signal processor or hardware accelerator is to take care of heavy computing whereas the microprocessor or controller takes care of the process and some low performance computing [2]. The memories store the software codes and data. In most of the cases there is also on-chip analogue interface, processing circuits for preand post-processing and many wireless interfaces [2]. The development of complex systems like the SoC might require working time of thousands of man-years [2]. Commonly, used design elements of a SoC are shown in Figure 2.

Figure 2. Basic design elements of a SoC [1].

The difference between general-purpose computer on a board and SoC is the design target. When designing a SoC, the specific application is known so all the components of the system can be optimized for that purpose. Highlighting the customisation is what distinguishes a system architecture from a computer architecture. [3, 25].

#### **2.2 ASIC**

ASIC is abbreviation for Application Specific Integrated Circuit. Integrated circuits (IC) are electronic circuits that are made of silicon wafer. A silicon wafer can consist of up to thousands of dies. One ASIC die can have few billion transistors. As the name implies ASICs are integrated circuits that are designed for some specific application. ASICs are tailored directly for the customers use case with specific requirements. ASICs are used in real-time computing and digital signal processing systems that require high computing performance and low power consumption. Here is some market segments and applications where ASICs could be used: Tire pressure monitor for automotive industry, 5G radio for telecommunication industry, Patient monitoring for medical industry, UHD TV for display industry, Smart phone for digital consumer industry, Robotics for manufacturing industry and Radar processing for military industry. [1,2].

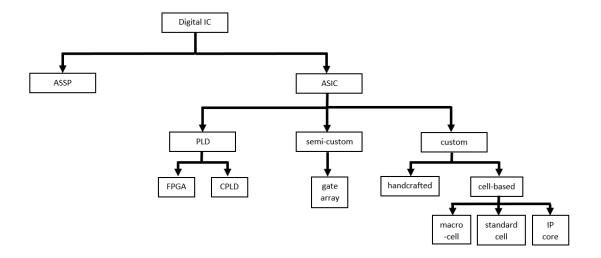

The class of PLDs (Programmable Logic Devices) include FPGAs (Field-Programmable Gate Arrays) and CLPDs (Complex Programmable Logic Devices). PLD chips contain programmable logic elements and wires which connects all the logic elements together. Semi-custom ASICs are ICs that contains some finished metal layers and contact and

some custom designed metal layers and contact, thus the time-to-market is shorter compared to custom ASICs. One example of semi-custom ASIC is a gate array. Custom ASICs are the most tailored ICs. In these all the metal layers are specially designed for a client's application. Custom ASIC can be also design by using IP (Intellectual Property) cores. The purpose of using IP cores is to reuse commonly used part of IC design that are already finished to make the time spend to the design process shorter. [2].

IP cores can be represented in three forms soft cores, firm cores, and hard cores. Soft cores are synthesisable HDL codes. Soft cores are flexible, but their performance is not that predictable because they are not yet fully tested and optimized. Firm cores are already optimised for area and performance. Hard cores are finished parts of the chip that execute some functionality. They are optimised for performance, size and power and they are mapped to some specific technology. Microprocessors like Intel Itanium and ARM are examples of IPs also FPGA-based accelerators like decoders and encoders are IPs. NVDLA is a soft IP core. [2].

In the industry most popular digital IC technologies are FPGAs and cell-based custom ASICs. Usually, big custom ASICs are design by using standard cells, macro-cells, and IP cores. These can be designed in-house, or they can be purchased from an external supplier. Figure 3 visualizes the most relevant digital IC technologies. There are also other digital IC technologies that are not presented in Figure 3.

Figure 3. Digital ICs [2].

The most common ways to implement NVDLA would be to use FPGA or cell-based technologies. This thesis project focuses on standard-cell ASIC's, for that reason let's study them little bit more. In standard-cell ASIC technology, a circuit is created from a set of predefined logic components referred as standard cells. The cells are ready-made

components whose functionality and layouts are validated and tested. The benefit of standard-cell ASIC technology is significantly simplified development process. It enables the work to be done at the gate level in preference to the transistor level. The building blocks are normally delivered by the device manufacturer as a library of standard cells. Usually, the library contains basic logic gates, such as AND, OR, and NAND gates, combinational components, such as 2-to-1 multiplexer and 1-bit full adder, and memory elements, such as latch and D flip-flop. Some of these libraries might also include blocks with more sophisticated functioning, such as an adder, and random-access memory (RAM). [7, 19].

#### 2.2.1 Abstraction levels

When the number of transistors in the chip rises to hundreds of millions, a human or a computer cannot deal with the quantity of information directly. The complexity needs to be managed; therefore, a system is characterized with abstraction levels. Single abstraction level shows only the chosen elements of the system and pays no attention to the related details. Hence, the amount of information is reduced to show only the decisive information i.e., it scales down the system to a more manageable level. High abstraction level contains only vitally important information about the system, while low abstraction level contains profound information which was previously ignored. The low abstraction level is complex but models the system at the real circuit level. Usually, the development process flow from high abstraction level towards the low abstraction level.

A digital system is divided into 4 abstraction levels:

- 1. Transistor level

- 2. Gate level

- 3. Register transfer level (RTL)

- 4. Processor level

Different representations of the abstraction levels do exists such as division into 6 abstraction levels [2]. The division is made by the size of the elementary building components, starting from the smallest, these are the transistors, logic gates, functional units, and processors. Another dimension of the system are the views [7]. Next, the 4 abstraction levels are studied independently.

The *transistor-level abstraction* is the lowest. The basic electrical components are utilized at this level such as, resistors, inductors, and transistors. The behaviour is modelled with differential equations or with voltage diagrams. Input-output characteristics can be examined with analog simulation software tools. At this level, a digital circuit behaves as

an analog system i.e., the signals are time dependent and has continuous value. The final physical layout of components and interconnects are constructed at the transistor level. It is the result of the design process. [7].

The *gate-level abstraction* is one level above the transistor level. The basic logic gates are utilized at this level for example, AND, OR, and memory components, such as, flipflop. Signals are described as logic 1 or logic 0 depending on the set voltage threshold. System with only two values can be presented by Boolean algebra equations thus, complicated differential equations are not needed anymore. Practically, the abstraction changes a continues system to a discrete system. It is good to notice that the signal is still continues, it is just interpreted with a pre-set voltage threshold. The timing information is also easier to interpret by just using the *propagation delay* which is the time needed to generate a valid output value. At this level the physical view expresses the placement and the routing of the logic gates and the wires. Also, the number of gates in a system can be counted, it is called as *gate count*. The gate count tells the area of a circuit based on the area of two-input NAND gate. With this method the equivalent gate count is independent from the device technology. [7]. The synthesis results for NVDLA are presented on this abstraction level.

The next abstraction level is the *register-transfer-level abstraction*. At this level logic gates form components that are used to create functional units such as, adders, registers, and multiplexers. The RT level is more abstract than the lower levels. Signals are interpreted with a particular data type for example as an unsigned integer. The behaviour of data is described with finite state machines (FSM). An elementary property at this level is that the storage elements utilize common *clock signal*. The clock signal is used to synchronize the data input into the storage elements at the rising or falling edge of the clock signal. In an appropriate system, all the data signals should stabilize during a clock period. Since, the timing can be examined in clock cycles, the variations in propagation delays and signal glitches has no effect to the functioning and can be disregarded. At this level the physical features are presented as the floorplan. The floorplan is useful tool, when defining the clock period because it visualizes the longest path. [7].

Finally, the highest abstraction level is the *processor-level abstraction*. The intellectual property (IP) blocks such as, processors, memory, and buses are utilized at this level. The behaviour is expressed as computation steps and communication processes. The signals are formed to a set and specified with different data types. The computation steps forms the time measure. Multiple computations can be executed in parallel, and the data

is changed between components with communication protocol. At this level, the physical layout is expressed as floorplan. Naturally, with larger components than on RT level. [7].

#### 2.3 Logic synthesis

In the ASIC design flow logic synthesis step is the process which converts an RTL code into a technology specific gate level netlist [1]. The output can be also referred to as celllevel netlist [7]. The synthesis step can be executed after the verification of the RTL code is done and the design met the coverage goals. Synthesis is performed by the EDA tool which inputs are RTL code, design constraints and the standard cell library. The output of synthesis is optimized gate level netlist which is created from the basis of inputs. The most common logic synthesis tools are Synopsys Design Compiler and Cadence Genus. The synthesis tool takes into consideration power, performance, and area as the most important factors to create the gate level netlist. The goal of synthesis process is to meet specified constraints by considering costs for different implementations. Gate level netlist is structural representation of the design presented as standard cells. Gate level verification is performed for the netlist to check that the functionality of the design is correct after the synthesis. After that pre layout STA (Static timing analysis) is performed to check possible timing violations in the design. In this stage STA is executed without using the parasitic (RC) effect. The goal is to repair any setup timing violations and to enhance the total performance of the design. The hold time violations are usually repaired after the CTS (Clock tree synthesis) and routing. Finally, before physical implementation the DFT (Design for Testability) is performed for the gate level netlist. This is performed by using DFT tool and the goal is to find possible faults in the design. To make this stage more convenient the RTL should be made DFT friendly. The benefit of this is faster scan chain insertion and it enables the total fault coverage for the design. [1].

#### 2.3.1 EDA tool limitations

The design process of digital circuit is not easy by any means. Completing the process involves many challenging tasks, requiring lots of data processing by complicated algorithms thus, computers are utilized to execute it. Therefore, one could ask whether the whole synthesis process can be automated. Then the engineer would only design a high-level behavioral model and EDA tools take care of the rest of the process i.e., the logic synthesis and placement and routing. However, the EDA tools have fundamental limitations that make this impossible on a full scale, this emerge from the theories of computational algorithms such as, the graph theory. [7].

The logic synthesis is an intractable problem and there is no polynomial-time algorithm to solve it. The logic synthesis process can be seen as a searching problem. The resulting circuit has  $O(2^n)$  solutions thus, the optimal solution is a result of exhaustive global search. That is why, in actual synthesis tools, the search space is limited to local search and clever tactics and heuristics are utilized to lead the search into desired direction. The HDL code sets the starting point for the search hence, a good HDL code is essential. Since, the local search might not get an efficient solution from bad starting point. [7].

Synthesis and also other design steps comprise computationally hard problems. EDA tools have this theoretical limitation by nature. Heuristic algorithms can find desired solutions but may not suit for all types of inputs. These limitation will also remain in the future and therefore a design engineer's expertise will be needed. [7].

#### 2.3.2 Logic synthesis flow

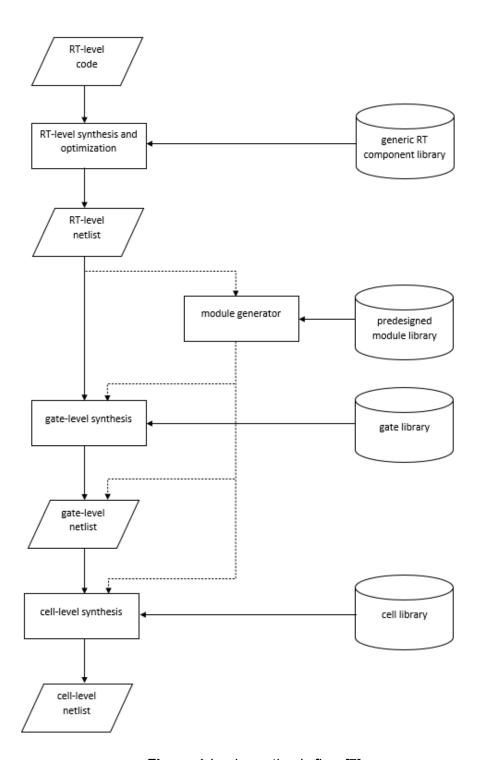

Logic synthesis is the process where RTL code is realized into RTL descriptions by utilizing elementary logic cells from the target technology library. The process is usually divided into steps to make it more comprehensible. These are RT-level synthesis, gate-level synthesis, and cell-level synthesis or technology mapping. As a first step, this list could include high-level synthesis where an algorithm is transformed into a system architecture containing of systems data path and control path which could be further transformed into HDL code. However, it is essentially different compared to other steps and it is performed by different software tools, which are not of interest to this thesis. Thus, it will not be discussed further in this thesis, although it is an important area of research today. [7].

The synthesis flow is visualized in Figure 4. The final circuit is formed level by level. It is an iterative process where first an RT-level netlist is transformed and optimized to a gate-level netlist which is finally transformed and optimized to a cell-level netlist. Complex RT-level components are generally processed with a module generator, these components include for example adder and comparator. [7].

Figure 4. Logic synthesis flow [7].

# 2.3.2.1 RT-level synthesis

In *RT-level synthesis* a behavioral RTL description is transformed into a circuit build from components provided by *a generic RT-level library*. The generic RT component library contains technology independent components. Thus, they are universal to all technologies. Generally, the components are categorized into three classes: functional units, routing units, and storage units. *Functional units* will be utilized to produce the

logic, relational, and arithmetic operators confronted in RTL code. *Routing units* are different kind of multiplexers utilized to build the routing structure of an RTL description. *Storage units* refers to registers and latches, which are utilized in sequential circuits to storage data at intermediate stages of RTL logic. [7].

An RT-level netlist is derivated and optimized during RT-level synthesis. This is the process where RTL statements are transformed into equivalent structural implementations. The usage of optimization techniques may decrease the complexity of circuit and improve performance. General optimization techniques include operator sharing, common code elimination and constant propagation. The scope of RT-level optimization is highly restricted compared to gate- and cell-level synthesis. Thus, it is only executed temporarily. At this stage the importance of good design is highlighted because it may amend the RT-level structure significantly. Thus, software tools can derive better implementation. [7].

#### 2.3.2.2 Module generator

The RT-level synthesis creates a netlist of generic RT-level components from the initial RTL descriptions. These components have to be amended into lower abstraction level, to process them further towards the final circuit. RT-level components include logical operator, multiplexers, adder, subtractor, incrementor, decrementor, comparator, shifter, and multiplier. Some of the components are uncomplicated and can be mapped straight into gate-level implementation, these are called as *random logic* component. Typically, these embodies less regularity and enables optimization subsequently in gate-level synthesis phase. Examples of random logic components are logical operators and multiplexers. The other components are referred as *regular logic*. A module generator is used for these more complex components. It is a specialised software which is able to derive the components for the gate-level implementation phase. Typically, regular logic has some kind of recurring structure and is designed in advance. As shown in the Figure 4. a module generator has capabilities to generate modules in various abstraction levels: Gate-level behavioral description, presynthesized gate-level netlist, presynthesized cell-level netlist. [7].

A gate-level behavioral description presents RTL code in a way where it utilizes only simple signal assignment and logical operators. This form allows it to be mapped to a gate-level netlist without much effort. At gate-level the description is general and technology independent. A single *gate-level netlist* is created by flattening the description and merging it with the random logic. The netlist combination is synthesized as a whole in *gate-level synthesis*. [7].

As stated earlier the regular logic components has the regular and repetitive features which allow further explorations of their properties and even manual derivation and synthesis of the netlist at the gate- or even cell-level. Thus, the regular logic and the random logic are dealt with separately. This approach might result a more efficient implementation compared to gate-level synthesis. In this process a presynthesized gate-or cell-level netlist is neither flattened nor merged with the random logic. Gate-level synthesis and even cell-level synthesis is performed separately for the random logic. Once these two separate netlists have been processed, they can be combined. [7].

The non-flattened approach has two benefits. Firstly, it may use highly optimized modules because they can be designed in advance. Secondly, the modules are separated from the other logic modules meaning that the remaining part is smaller requiring less effort to process and optimize it. However, the weakness of this approach is decreased possibilities for additional optimization due to isolation of the non-flattened modules and the random logic. There is no clear rule whether the flattened or the non-flattened approach is more effective. Users can enable or disable this feature in some of the synthesis tools. [7].

#### 2.3.2.3 Gate-level synthesis

The gate-level synthesis process produces elementary gate-level components, for example a NOT-, AND-, NAND-, OR-, and NOR gates. The number of the components is optimized forming the so-called structural view of a design. The generic technology independent components do not possess specific information about the size or the propagation delay. These components are the operators of Boolean algebra. Hence, a design can be presented as a Boolean function. Gate-level synthesis may be performed in two different ways: two-level synthesis and multilevel synthesis. [7].

An example of two-level synthesis is the sum-of-products expression. In that the logic is formed from AND gates and OR gates. Where AND gates are at the first level and OR gates at the second level. Any two-level logic construction may be created with the sum-of-products expression. Two-level synthesis is thus intended to find an optimal sum-of-product expression for Boolean function. This is achieved by minimizing the number of AND gates and the total number of fan-ins to these AND gates. For a maximum of about five input circuits this is done manually by using the Karnaugh map technique. In real applications circuits may have hundreds of inputs, as a consequence optimization cannot be done manually. Thus, it is an intractable problem. However, good algorithms have been developed to create suboptimal but still efficient circuits. Two-level synthesis is good at processing and manipulating logic statements. It scales down the amount of

information required to represent a function and therefore could be used as a preliminary step for multilevel processing. [7].

Multilevel synthesis uses multiple gate levels to represent a Boolean function. With multiple levels the process is not so strict, and it gains more freedom, resulting more efficient and flexible outcome. The design may be explored from area or delay optimization perspective or even from an optimal trade-off point for both the area and delay. Compared to two-level circuit it lowers the number of gates as well as the number of fan-ins. The foundation of contemporary application technology is in small cells with a constrained fan-in count. Making it more suitable for multilevel synthesis. [7].

Processing and optimizing a multilevel logic requires more effort. Usually, it is performed with heuristic methods by following a database of circuit rules. Due to the limited number of restrictions multilevel synthesis may generate substantially different results. A very small change in original description might lead to an entirely different implementation. [7].

#### 2.3.2.4 Cell-level synthesis

Gate-level synthesis process produces and optimized netlist of generic components. *Cell-level synthesis* also known as *technology mapping* transforms the gate-level netlist into technology dependent cell-level netlist. To achieve this the process uses the target technology library. The resulting components are usually called as *cells*. Generally, in ASIC technology a semiconductor vendor delivers the technology library and fabricates the device. A cell is defined by its function and by a set of physical parameters including, for example area, delay, and input and output capacitance load, each cell is also linked to the physical layout. Cell-level synthesis can be performed simply by just transforming generic components into logic cells without any further explorations. However, the generated circuit will not be very efficient. Hence, the functionalities, areas and delays of the cells are worth to exploit. The cell-level synthesis is hard process, involving intractable problems. Again, heuristic algorithms are applied to find solution. Next, an example on a standard-cell library is discussed. [7].

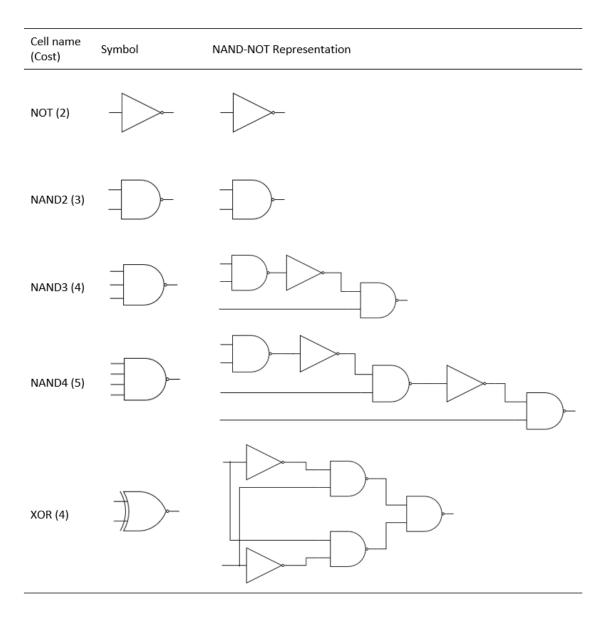

A standard-cell technology library includes hundreds of cells, such as combinational, sequential and interface cells. Some examples of combinational cells are AND-, OR-, NAND-, NOR-, and XOR gates. Also, more complex circuits might be included, like 1-bit full adder and 1-bit 2-to-1 multiplexer. Example of standard-cell library is visualized in Figure 5. The library in the Figure 5. was invented for a sake of example and does not represent any real library. [7].

Figure 5. Modest hypothetical standard-cell library for ASIC technology [7].

The columns represent the cell name and the relative area cost of that cell, its logic gate symbol, and the NAND-NOT representation of that cell. In NAND-NOT representation cells are implemented by utilizing 2-input NAND gates and NOT gates, this simplifies the cell-level synthesis process. [7].

A technology library contains cells which are optimized and fine-tuned for specific technology. This is done by manually designing each cell from the transistor level in preference to simple logic gate level. An example of this is the XOR gate, if it would be implemented with NAND- and NOT gates the area would be 13, which is over 4 times the area of the NAND2 cell. While, with the transistor level implementation the area of the XOR gate is only 4, which is 2 times the area of the NAND2 cell. Hence, the standard-cell library contains various elementary cells. Additionally, a single logic function may have several cells implementing different area-delay trade-offs. [7].

To summarize, the cell-level synthesis or the mapping is an iterative process, where the initial mapping is a one-to-one gate-to-cell translation, it is not the most optimal solution. To make the solution better, NAND-NOT representations are replaced by corresponding more optimal logic gates. Finally, to find the most optimal area-delay trade-off different kind of transistor level implementations are explored. Thus, cell-level synthesis plays a major role in the logic synthesis process, while its complexity is very high. [7].

#### 2.3.3 Efficient use of synthesis tool

Although, synthesis software has some limitations, it is a vigorous and essential tool. It automates various design tasks and executes intractable and recurring computations. Designers should be aware of the features and constraints of software, to be able to adjust it and make compromises when needed. [7].

In general, the performance of logic synthesis tool is highly effective for circuit sized around 2 000 000 instances, this is achieved by studies of algorithms. Even small design includes hundreds of gates, making the use of synthesis tool practical. The synthesis is straightforward from logic operators to gate-level components. Because the mapping can be done directly at this level, there is no need to be concerned about the sharing and optimization of logical operators in an RTL code description. [7].

The RT level optimization includes complicated arithmetic and dependent operators and routing structure. These demand human handling, to determine the wanted design in an RTL description. Recurring small improvements on code can enhance circuit efficiency essentially. Thus, designer's insight and expertise of a circuit has great importance to the end result. [7].

The "data" flow from circuit inputs to outputs through the system demonstrates *routing structure*, which indirectly specifies the layout of the physical circuit. The data flow is described in the RTL code, which forms the initial layout. However, this will be reshaped by the placement and routing process to realize the circuit on a two-dimensional silicon chip. Hence, the resulting implementation will be smaller and faster if the RTL code resembles the structure of the silicon chip. This is due to the fact that synthesis tool cannot make significant global changes. The RTL coding technique creates a basis for synthesis, affecting the result much more than the optimization done by the synthesis tool. [7].

## 2.3.4 Timing considerations

Even though a digital circuit is fast the respond is not instant. Meaning that the output is a function of time. The *propagation delay* represents the time between an input state

change and a valid output value. As a time-domain characteristic for a circuit, it is a major design criterion. Also, a *hazard* is time-domain phenomenon, it is the unwanted state change of an output signal. It is a transient event but might result malfunction in a poorly designed circuit. Next, subsection will discuss the propagation delay and hazard in more detail. [7].

A digital circuit requires some time to generate a valid output response to the change of an input. In digital system, the time needed to propagate a signal from input port through the circuit to output port is called as propagation delay or just delay. Multiple input-output delays may exist due to the large number of ports, but propagation delay usually refers to the worst-case delay i.e., it indicates how fast a digital system can operate. Hence, it symbolizes the performance or the speed of the digital system. For a digital system the two most important design metrics are the speed and area i.e., the circuit size. The system propagation delay can be computed by first figuring out the delays of individual components and by searching all the input-output paths. Then we can add up the delays from all the components for each path and with that define the propagation delay. Now we can notice that the system delay is based on its components and depends on the information they possess. Hence, the most accurate delay estimate will be obtained at the cell level. The netlist contains the detailed physical and electrical information of the cells. In contrast, the RT level offers least information about the physical and the electrical characteristics since at that level the components require further processing. [7].

In order to characterize the propagation delay, the cell level time-domain behavior is studied and analysed at the transistor level, where the modelling is based on transistors, resistors, and capacitors functioning. Main reason for the delay is parasitic capacitance, coming from two overlapping metal layers. A state change in a transistor makes capacitors to charge or discharge which causes the delay. Performing the cell analysis at this level is very complex thus it is applied only at a small scale. Consequently, it gives basic information for the modelling. A simplified linear model is common approach to perform timing analysis at the cell level. [7]. Also, nonlinear delay model, polynomial delay model, and current source delay model can be used [20]. The simplified linear model is unsophisticated model but with it the cell level complexity can be managed. In this model, all parasitic capacitances are summed and represented as one capacitor, which in turn allows consideration of only first-order effects. The delay can be represented by an equation [7].

$$delay = d_{intrinsic} + r \times C_{load}, \tag{2}$$

The circuit inside the cell is expressed by the first term,  $d_{intrinsic}$ , it models the transistor state changing time for example changing from off state to on state. The cell drives external circuit, which is expressed by the second term in the equation. The parameter  $C_{load}$  relates to the path from output of the current cell to the input of driven cell, it is the total capacitive load. It is defined as the sum of parasitic capacitance from interconnected wires and the input capacitance from driven cells. The parameter r models the output impedance, which expresses the driving power of the cell. High driving power can be achieved with small impedance, since it enables higher current. Thus, the capacitive load is charged or discharged in a shorter time. Consequently, with small r value the delay is shorter. Accordingly, bigger transistor shortens the delay. [7].

The cell-level delay calculation are dependent on the accuracy of few factors such as the used parameters and the model. The values of parameters  $d_{intrinsic}$ , r, and input capacitance are defined by the manufacturer and can be considered reasonably accurate. The total input capacitive load can be computed from the netlist, after technology mapping has been completed and fan-out of all the cells are available. Whereas, the wire capacitance is determined by the real length and location of wires, which are not specified at the synthesis process. However, synthesis tools can generate a rough estimate based on a statistical model. The wire capacitance can be determined accurately once place and route step is performed. At cell-level, wiring has a great effect on delay estimation. The linear cell-level model disregards higher-order effects in circuit, which might have an impact to the accuracy of the model. Hence, the impact on the functioning of the circuit may be significant. However, it is possible to use more advanced models. For example, a simple lumped RC model can be replaced with more advanced RC circuits to get more accurate estimation. [7].

With comparatively large transistors the above-mentioned factors have a minor impact on the total delay and can be excluded from the considerations, because of that the synthesis process can generate accurate timing data. However, on nanometre technology the given factors emerge, which complicates the design process. Accurate timing data will be received only after placement and routing. Inherently, the delay of a cell cannot be managed precisely. The delay is also impacted by the manufacturing process and operating environment. A technology vendor can only provide the boundary values, usually this means the maximal propagation delay. [7].

When delays of individual cells are known, path delays can be defined. A path delay is the sum of cell delays on the path. Usually, a digital system contains a great number of different paths, flowing from input to output ports with different delays. The system delay

is the longest path, referring to the worst-case scenario. Generally, it is also known as the *critical path*. [7].

To find the critical path, the netlist can be handled as a graph. Thereby all the possible paths in the netlist can be determined and the longest of them can be found quite easily. Hence the critical path is defined by the topology of the system, and it is also referred as the *topologically critical path*. Sometimes this approach may lead to overestimating the critical path due to the existence of a *false path*. It is a path that exist but according to defined logic, data cannot pass along it. The topographically critical path can be a false path and can be ignored from true system delay calculation. Therefore, both the topography and the internal logic operations must be considered, which makes the critical path determination difficult task. However, it can be determined with software. Hence, synthesis tool is used to execute cell-level timing analysis. Synthesis tool also provides a feature to manually rule out possible false paths. [7].

The same principles apply also at the RT-level and therefore the propagation delay can be already analysed and calculated at this stage. At RT-level the result of the calculation rely on the used components. This implies that if an RT-level design includes mostly simple logical operators being mainly random logic, these will experience lots of transformations and optimization in the logic synthesis phase. Meaning that the initial RT-level delay calculations does not necessarily reflect the complete synthesized circuit at all. There is also another side, if an RT-level design includes mostly complex operators and function blocks, they will have the greatest impact on delay calculations. Since, they are designed in advance and optimized, logic synthesis will not change their delay features notably. Therefore, this type of circuit could have realistic delay calculation already at the RT-level. Consequently, the critical path and thus the performance are known. This will facilitate the RTL code design and ultimately will result more efficient circuit with the preferred area-delay features. [7].

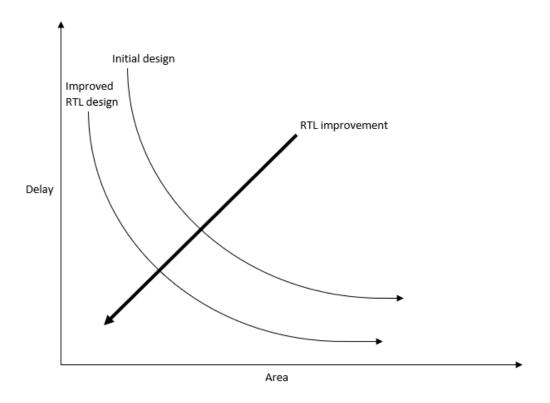

The two most important design specifications are the chip area and the system delay. Usually, the final design is trade-off between these two. In practice, a fast circuit requires more area, and a small circuit is not the most efficient. One application can be implemented with multiple different area-delay characteristics. Multilevel logic synthesis is flexible, it is able to add gates in the circuit to decrease delay. This is useful in a situation where the circuit area is optimized but the system delay still need to be reduced. Intrinsically, the optimal trade-off can only be achieved within a certain range. The area cannot become smaller and the performance better endlessly. The impact of RTL improvements to synthesis iterations is shown in Figure 6 [7].

Figure 6. Synthesis iterations in an area-delay space [7].

The logic synthesis is iterative process. The process introduced in section 2.3.2 finds the optimal area for the circuit. Usually, synthesis is performed for separated IP blocks or partitions of the whole system. To achieve the performance targets, logic synthesis needs timing constraints. A circuit cannot be synthesized exactly to achieve a certain propagation delay. However, the maximal accepted threshold value for propagation delay is set in the timing constraints. As stated previously, the critical path defines the system delay. Therefore, not all paths should be blindly optimized. The synthesis processing sequence is iterative. As a first step synthesis usually generates implementation with the smallest achievable area. Next, the resulting netlist will be analysed to obtain the critical path and the system delay. If the system delay is longer than what the constraints allow, synthesis adds gates in the circuit to make the critical path faster. The regenerated implementation introduces the new critical path, which is assumed to be the second longest path of the initial implementation. The new system delay will be explored to identify if it met the timing constraints. The process iterates through until the resulting implementation is within desired constraints. [7].

The previously described processing sequence is executed at the gate or cell level and is too laborious for human but can be utilized on RT level. The schematics show the placement of complex RT-level components and the preliminary routing configuration. System delay is dominated by the complex components, thus the path through them will

indicate the critical path. The analysis is beneficial for architectural explorations and ultimately will result a more efficient circuit. The designer's knowledge about the system can induce global optimization. Naturally, this is more effective than local optimization at gate- or cell-level, performed by synthesis tool. [7].

The propagation delay indicates the needed time for a system to generate a valid output state. Oscillations at the output port within the transient period are called as *timing hazards*. In digital systems, multiple paths might lead to a single output port. Since, path's delays can vary, signals might reach the output port at different points of time. Consequently, the output port might oscillate before a steady-state is generated. The oscillations are one or more unexpected alternations at the output port, they are called as *glitches*. If a circuit is able to generate glitches it has a timing hazard. There are two types of timing hazards, the next paragraphs will describe them in more detail and explain how to handle them. [7].

A *static hazard* refers to a glitch at output port when assumed to be at a steady-state. Furthermore, it includes two types of hazards, static-1 hazard, and static-0 hazard. A *static-1 hazard* happens when Boolean algebra analysis of a circuit shows that output should be at a steady-state '1' but circuit generates a '0' glitch. Correspondingly, a *static-0 hazard* happens when analysis show that the output should be at a steady-state '0' but a '1' glitch is generated. A *dynamic hazard* refers to a glitch at the time period when a circuit is switching state for example from '0' to '1'. The source of these two hazards is too fast paths i.e., the different propagation delays on each path. [7].

## 2.3.5 Static timing analysis (STA)

The STA calculates time period when certain signal have to be available [11]. The goal is to check that a circuit can operate at the required frequency [11]. Commonly, a sequential circuit is utilized in a digital system, it is a circuit containing memory elements. Further, a synchronous sequential circuit has global clock signal which controls all the memories in the circuit thus, this method makes the design process simpler. The most popular memory element is D-type flip-flop, it has 3 main timing parameters: [7]

- 1. clock-to-q delay: The delay on path between the d input and the q output occurring after the edge of the clock signal.

- 2. setup time: Indicates the time period when the *d* signal must be stable **before** the edge of the clock signal.

- 3. *hold time*: Indicates the time period when the *d* signal must be stable **after** the edge of the clock signal.

The clock-to-q delay is about the same as the delay caused by a combinational element. Setup time and hold time are timing constraints specified for a circuit. They define the time period around the clock edge when the *d* signal must be stable. A change in the *d* signal during the time period is known as *setup time violation* if it happens before the clock edge or *hold time violation* if it happens after the clock edge. These timing violations can create a *metastable state* for the D flip-flop, where the *q* output is in an unknown state and a circuit does not function correctly. [7].

The timing of a combinational circuit is mainly based on the longest path in it i.e., the propagation delay. While the timing of a sequential circuit is primarily determined by the timing constraints specified by the memory components. Where the most important timing parameter is the *maximal clock rate*, which actually contains the propagation delay, the clock-to-q delay, and the setup time constraint. The main objective in designing a sequential circuit is to meet the setup and hold time constraints. [7].

A sequential circuit containing memory elements and combinational logic has a limit for the maximal clock rate  $(T_{c(max)})$  to avoid setup time violation, it is determined as

$$T_{c(max)} = T_{cq} + T_{comb(max)} + T_{setup}, (3)$$

Where  $T_{cq}$  is clock-to-q delay,  $T_{comb(max)}$  is the maximum propagation delay of the combinational logic, and  $T_{setup}$  is the setup time constraint. The hold time constraint  $(T_{hold})$  has some differences to the setup time constraint. To avoid hold time violation, a sequential circuit has to satisfy the inequality

$$T_{hold} < T_{cq} + T_{comb(min)}, \tag{4}$$

Where  $T_{cq}$  is the clock-to-q delay and  $T_{comb(min)}$  is the minimum propagation delay of the combinational logic. [7].

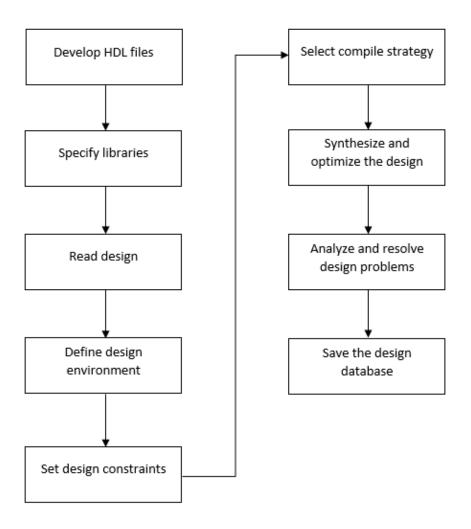

# 2.4 Design Compiler (DC) synthesis flow

Design compiler has its own logic synthesis flow. Usually, it is used on design exploration and design implementation phases. Flowchart of the synthesis flow is presented in Figure 7. [9].

Figure 7. A basic synthesis flow. [9].

The following paragraphs discuss design compiler synthesis flow in more detail.

Develop HDL files: Hardware description language (HDL) files are the input for design compiler, these can be created by using Verilog or VHDL. In the HDL code preparation phase, you have to take to account design data management, design partitioning, and HDL coding style. Design files contain the design descriptions. Naming of these files must be unique. When preparing design for synthesis, managing design file data is important, with appropriate strategy data is not lost. Selected HDL coding strategy is also important because HDL coding is the basis for synthesis. A good method to manage the design data is to organize it systematically. Effective partitioning of a design can improve the synthesis results, decrease compilation time, and simplify the script files and constraints. Partitioning have an effect on design block size thus, block size control must be done carefully. [9].

Design cannot function correctly without constraints; thus, they are very important. They are statements that determine the design goals in measurable circuit characteristics.

These can be timing, area, power, and capacitance. The logic library is crucial for design, it defines the implicit design rule constraints. Explicit optimization constraints such as physical constraints can be also defined. They help in optimization. [9].

Specify libraries: Next in the synthesis flow comes specify libraries step. In this step logic, symbol, and DesignWare libraries are used for design function implementation and for showing synthesis outcome graphically. The mapped logic libraries are called target libraries which are produced in optimization. Target libraries have the cells in them which are used to produce the netlist and definitions for the design's operating conditions. A design is compiled or translated by using the link libraries, even more specifically used libraries are the target libraries which are the subset of the link libraries. Link libraries contain the delay models information that are used to compute timing values and path delays. A pseudo library called ALIB can be used to explore trade-offs between area and delay. ALIB is created by characterizing the target library. ALIB contains real gates mapped from the Boolean functional circuits in the target library. The symbolic representations of the cells are in the symbol library. The DesignWare libraries contain reusable circuits which are used as a building elements within the synthesis run to optimize the speed and area. The physical libraries have to be specified if DC is used in topographical mode. These include the Milkyway reference library, holding physical information about the standard cells and macros. [9].

Read design: RTL design and gate-level netlist are used as an input for design compiler. It utilizes HDL compiler to interpret Verilog and VHDL designs and gate-level netlists. Also, netlist in ddc format can be read in the tool. DC can handle multiple designs when read into memory, even design modification can be made when in memory. [9].

Define design environment: The expected design environment has to be specified to enable optimization of the design. This means the operating condition, system interface features, and wire load models (if synthesis is not run-in topographical mode). Typical operating condition are temperature, voltage, and process fluctuations. System interface features comprise input drives, I/O loads, and fanout loads. Consequently, the design environment setup have an impact on the synthesis outcome. The design environment is specified with commands such as, set\_operating\_conditions, set\_drive, set\_load, set\_driving\_cell, set\_wire\_load\_model, and set\_fanout\_load. [9].

Set design constraints: Constraints determine the design objectives in circuit characteristics for example, time, area, and capacitance. These are used in design optimization during synthesis run. There are two main constraint types design rule constraints and optimization constraints. Design rule constraints (DRC) are located in

the logic library, a design needs them to operate properly. DRC have a priority over optimization constraints. The design rule constraint types involve for example maximum transition time, maximum fanout, maximum capacitance, minimum capacitance, cell degradation, and connection class. Optimization constraints are defined by the designer. DC tries to meet optimization constraints within optimization phase, but cannot break the design rules thus, optimization rules have to be set realistically. The optimization constraints involve for example input and output delays, minimum and maximum delay, maximum area, and power optimization. Constraints are defined on the command line or in a file. Both of the constraints are tried to be met however, the design rule constraints are given priority. [9].

Select compile strategy: The compile strategy has to be set for hierarchical designs. The top-down compilation or the bottom-up compilation can be used for different parts of the design. The top-down compilation compiles the top-level design and the sub designs in conjunction. The bottom-up compilation compiles the sub designs individually from the lowest hierarchy level to the highest level i.e., the top-level design. Also, mixed compile is possible, it utilizes both of the strategies depending on what is the best option for the particular sub design. [9].

Synthesize and optimize the design: In synthesis run the optimization maps the design to best possible structure according to functional, speed, and area specifications. The design synthetization and optimization is incorporated to the compile process which is launch with the compile\_ultra or the compile command. A technology-specific circuit is created in the optimization process. It is executed on three levels architectural optimization, logic-level optimization, and gate-level optimization. The architectural optimization operate on the HDL expressions performing common subexpression sharing, resource sharing, selection of DesignWare components, operator reorganization, and identifies arithmetic expressions to run data path synthesis. The logic-level optimization operate on the technology independent netlist, it performs two procedures structuring and flattening. The gate-level optimization operates on the technology independent netlist. It performs mapping, delay optimization, design rule fixing, and area optimization. [9].

Analyze and resolve design problems: Inherently, the synthesis and optimization results need to be analysed and it is done with area, constraint, and timing reports extracted form DC. These will help to sort out possible issues and to enhance the final outcome of synthesis. Reports can be created during the synthesis run before and after the compilation. [9].

Save the design database: DC does not save the design automatically. Therefore, the design have to be saved manually into ddc, Verilog, svsim, VHDL, or Milkyway format. This can be done for the whole design and for the sub designs whenever needed by using the *write\_file* command. [9].

#### 2.5 Synthesis in practise with DC

Synopsys Design Compiler is vigorous synthesis tool. It is used to execute the logic synthesis for ASIC designs. Logic synthesis is run with the help of special DC commands. This section will discuss about the important commands. [8].

When DC is launched it reads the starting file *synopsys\_dc.setup* located in the working directory. Two starting files are needed: one in the working directory and another one in the root directory, where the DC installation is also located. Also, couple of parameters must be setup to make the tool usable:

- 1. search\_path: Parameter utilized on the synthesis run to search the target technology libraries [8]. On this project it is used for the RTL file paths.

- 2. target\_library: The logic cells are located in the target\_library. DC uses this library to map the logic cells on the cell-level synthesis. [8]. On this project the 7 nm technology file paths are provided with this parameter.

- 3. *link\_library*: This parameter is used to link the logic cells in the target technology libraries with the libraries containing referenced components and designs [9]. This is used for the memory instance file paths.

After these three parameters are setup, the tool can be used from the command prompt [8].

### 2.5.1 DC commands used during synthesis

A digital system is designed by using synthesizable HDL, the design is input for DC. Table 1 introduces some important DC commands utilized during synthesis run. [8].

Table 1. DC commands [8].

| 1 :  | Table 1. DC commands [8].                                                                                                                         |                                                                               |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| Line | Commands                                                                                                                                          | Description                                                                   |

| 1    | read -format <format_type> <filename></filename></format_type>                                                                                    | Read the design in DC.                                                        |

| 2    | analyze -format <format_type> <list file="" names="" of=""></list></format_type>                                                                  | Used to analyse the syntax and translation prior the generic design is built. |

| 3    | elaborate -format <list module="" names="" of=""></list>                                                                                          | Elaborates the design.                                                        |

| 4    | check_design                                                                                                                                      | Check the issues in the design, such as shorts and connections.               |

| 5    | create_clock -name <clock_name> -period <clock_period> <clock_pin_name></clock_pin_name></clock_period></clock_name>                              | Generates the clock for the design.                                           |

| 6    | set_clock_skew -rise_delay <rising_clock_skew> fall_delay <falling_clock_skew> <clock_name></clock_name></falling_clock_skew></rising_clock_skew> | Set the clock skew for the design.                                            |

| 7    | set_input_delay -clock <clock_name><br/><input_delay> <input_port></input_port></input_delay></clock_name>                                        | Define the input port delay.                                                  |

| 8    | set_output_delay -clock <clock_name><br/><output_delay> <output_port></output_port></output_delay></clock_name>                                   | Define the output port delay.                                                 |

| 9    | compile -map_effort <map_effort_level></map_effort_level>                                                                                         | Compile the design. Map effort level can be set to low, medium, or high.      |

| 10   | write -format <format_type>-output <file_name></file_name></format_type>                                                                          | Save the synthesis output.                                                    |

| 11   | set_false_path -from [get_ports <port list="">] -to [get_ports <port list="">]</port></port>                                                      | Define the false path.                                                        |

| 12   | set_multicycle_path -setup <period> -from [get_cells] -to [get_cells]</period>                                                                    | Enable multicycle paths for design setup timing.                              |

| 13   | set_multicycle_path -hold <period> -from [get_cells] -to [get_cells]</period>                                                                     | Enable multicycle paths for design hold timing.                               |

| 14   | set_clock_uncertainty                                                                                                                             | Set the estimated network skew value.                                         |

| 15   | set_clock_latency                                                                                                                                 | Set the estimated source and network latency values.                          |

| 16   | set_clock_transition                                                                                                                              | Set the estimated clock skew value.                                           |

| 17   | set_dont_touch                                                                                                                                    | Disable optimization of the gates that are already mapped.                    |

Commands related to reading the design in DC include analyse and elaborate which pass needed parameters during elaboration. The actual read design command is utilized to pass pre-compiled design in DC. The check design command is utilized after reading to check potential problems in the design. Previously mentioned commands are part of

the basic execution script that DC is running in synthesis run. Hence, this is utilized in this project. The create clock command specifies a clock for the design which is also used as a reference in timing analysis. The clock is linked to the clock pin in the design. If clock pin does not exist, synthesis creates virtual clock for the design. This is set in the constraint files that can be downloaded from GitHub webpage. Clock skew needs to be handled in synthesis; it is the difference between signal arrivals into different flip-flops. Positive clock skew adds margin for the setup timing. Since, the clock signal arrives late to the destination flip-flop compared to the source flip-flop. By contrast, negative clock skew adds margin for the hold timing. Since, the clock signal arrives late to the source flip-flop compared to the destination flip-flop. The clock skew is used to model the propagation delay in the clock tree in order to synthesize the design. It is set in the constraints file with the command set\_clock\_transition. Input and output delays are determined with command in Table 1 at lines 7 and 8. If needed the delays can be determined as minimum or/and maximum delays for both input and output. To do that following commands are utilized: [8]

- set\_input\_delay -clock <clock\_name>-max <delay> <input\_port>

- 2. set input delay -clock <clock name>-min <delay> <input port>

- 3. set output delay -clock <clock name>-max <delay> <output port>

- 4. set output delay -clock <clock name>-min <delay> <output port>

The synthesis is executed with the compile command. This can be done with different levels of effort (low, medium, and high) and is specified with the command in Table 1 at line 9. This project uses newer command compile\_ultra -no\_seq\_output\_inversion -gate\_clock -spg -scan. The resulting synthesis output is saved with the write command. The output can be saved in different formats such as VHDL or database format (ddc). This project saves it in verilog and ddc formats. Possible false paths in the design can be specified with the set false path command. Some know false paths are set in the provided constraints files. Multicycle paths in the design can be specified with commands in Table 1 at lines 12 and 13 to check setup and hold timing. This was used in order to improve setup timing. [8].

# 2.6 Design optimization using DC

SoC design can have multiple functional blocks which is actually good thing for the synthesis. Block-level constraints can be specified to satisfy area, speed, and power targets. The blocks in the design can have different clock and power domains and the functionality can be different. To optimize the design in synthesis, it can be divided into partitions according to the functionality. Hence, the block-level constraints need to be

specified in the sdc files. If block-level constraints are not met, the RTL code or the architecture may need to be changed. [8]. The synthesis tool optimizes the design, but it can usually improve the performance only by 10-20 percentage [22]. NVDLA is divided into 5 partitions based on the functionality, thus synthesis is driven for these individually.

Constraints need to be specified also for the chip-level synthesis. The top-level design integrates different functional blocks together. The top-level constraints need to be specified properly to obtain required speed, area, and power numbers. A key factor is synchronization between the blocks. The don't touch attributes can be set for the verified clocks. Top-level constraints or top-level synthesis model are not specified for NVDLA. Main optimization and design rule constraints (DRC) are shown in Table 2. [8].

Table 2. Optimization and design rule constraints [8].

| Line | Commands                 | Туре                    | Description                                     |