# SAGAR BHALERAO

# Flexible, Low-Voltage, Metal Oxide Thin Film Transistors (TFT) and Circuits for Wearables and Internet of Things (IoT)

Tampere University Dissertations 529

Tampere University Dissertations 529

### SAGAR BHALERAO

## Flexible, Low-Voltage, Metal Oxide Thin Film Transistors (TFT) and Circuits for Wearables and Internet of Things (IoT)

ACADEMIC DISSERTATION To be presented, with the permission of the Faculty of Information Technology and Communication Sciences (ITC) of Tampere University, for public discussion in the Auditorium TB109 of Tietotalo, Korkeakoulunkatu 1, Tampere, on 17<sup>th</sup> December 2021, at 12 o'clock.

#### ACADEMIC DISSERTATION

Tampere University, Faculty of Information Technology and Communication Sciences (ITC) Finland

| Responsible<br>supervisor<br>or/and Custos | Prof. Paul Berger<br>Tampere University<br>Finland                |                                                   |

|--------------------------------------------|-------------------------------------------------------------------|---------------------------------------------------|

| Supervisor(s)                              | Prof. Donald Lupo<br>Tampere University<br>Finland                |                                                   |

| Pre-examiner(s)                            | Prof. Benjamin Iniguez<br>University of Rovira i Virgili<br>Spain | Prof. Jukka Hast<br>University of Oulu<br>Finland |

| Opponent(s)                                | Prof. Rodrigo Martins<br>NOVA University Lisbon<br>Portugal       |                                                   |

The originality of this thesis has been checked using the Turnitin Originality Check service.

Copyright ©2021 author

Cover design: Roihu Inc.

ISBN 978-952-03-2229-8 (print) ISBN 978-952-03-2230-4 (pdf) ISSN 2489-9860 (print) ISSN 2490-0028 (pdf) http://urn.fi/URN:ISBN:978-952-03-2230-4

PunaMusta Oy – Yliopistopaino Joensuu 2021

# ACKNOWLEDGEMENTS

First and foremost, I'd like to thank my supervisors, Prof. Paul Berger and Prof. Donald Lupo, not only do I immensely appreciate everything you have taught me, but I also enjoyed our discussions on many topics. I can't thank you enough for your overwhelming kindness and compassion. I'd like to express my gratitude to Prof. Paul Berger for welcoming me and providing me an opportunity to work at The Ohio State University in the United States.

I would also like to thank Prof. Matti Mäntysalo for giving me the timely guidance. Many thanks to all my colleagues at the Laboratory of Future Electronics for their constant support and help throughout the entire period. I express sincere gratitude to my family, parents and friends.

# ABSTRACT

Multifunctional flexible electronics are booming in many ways. Flexible electronics have opened up a world of possibilities for their widespread use in smart electronics such as artificial electronic-skin (e-skin), flexible displays, consumer electronics, implantable devices. Flexible devices and sensors are paramount in order to realize the true potential of flexible electronics, wearable eco-systems, biomedical and anticipated pervasive Internet of Things (IoT). With special properties like enhanced flexibility, light weight and conformability, flexible technology allows a seamless system integration. Although today's modern electronics are capable of performing everyday needs in existing applications, flexible electronics can provide potential solutions for many as yet unseen applications which requires lower processing capacity, low cost as well as thin, lightweight and environmentally friendly products. To fulfill the needs of a diverse range of applications, next-generation flexible electronics should be engineered with added flexibility and mechanical deformability, by exploring new materials and tactics to overcome the limits of traditional methods.

At the moment, enhanced device performance, greater integration density, fabrication cost and advanced functionality are propelling the traditional silicon semiconductor technology and electronics industry forward, servicing traditional macro-electronic sectors (e.g., mobile phones, laptops, routers, automotive). This unquenchable need for higher performing electronic devices necessitates new technological advances and keeps costs high. The overall performance of modern silicon-based devices and technologies are reaching new levels. With the ballooning consumer electronics needs; the global semiconductor industry is expected to remain growing robustly. But rather than competing with well-developed rigid silicon devices, the goal for flexible electronics is to improve the efficiency of current state-of-the-art thin film transistors (TFTs), required for low energy flexible wearables and Internet of Things (IoT), and mature these designs for low-cost, printable manufacturing.

Thin film transistors (TFTs) are among the most important thin film devices and can form the foundation of any electronic system and application. In this regard,

metal oxide semiconductors are viewed as a potential candidate for flexible electronics, due to a broad range of properties, such as a large band gap, high optical transparency, high mobility, and solution processable deposition at low temperatures compared to CMOS processes. However, despite a dedicated effort by the research community and industry, metal oxide thin film transistors still face great challenges being used in flexible electronics, wearables, and Internet of Things (IoT), such as operating voltage, switching speed, on-off ratio, process temperature and gate dielectric deposition compatible for flexible substrates.

The present thesis investigates solution-processed metal-oxide thin film transistors (TFTs) and inverter circuits for flexible electronics. The low-voltage (< 3 V) thin film transistors using indium oxide (In<sub>2</sub>O<sub>3</sub>), gallium oxide (Ga<sub>2</sub>O<sub>3</sub>) and indium gallium zinc oxide (IGZO) as the active channel semiconductor were fabricated on solid (glass) and flexible (polyimide) substrates. The low-voltage operating thin film transistors were accomplished by following low temperature solution processing and room-temperature anodization routes for metal oxide semiconductor and gate oxide dielectric deposition, respectively. The incorporation of anodized high- $\kappa$  aluminum oxide (Al<sub>2</sub>O<sub>3</sub>) for gate dielectric into the TFT fabrication process has significantly helped to reduce operating and threshold voltages while also improving carrier mobility. On the other hand, solution processing allows low-temperature, large-area deposition while lowering fabrication costs.

The solution-processed metal-oxide TFTs show excellent electrical performance, at a low gate voltage ( $V_g$ ), which could enable novel applications in flexible electronics. Along with electrical characterization, bending performance and SPICE simulation results are also presented. Furthermore, thorough thin film characterization and interface analysis between oxide semiconductor and gate dielectric were performed, using various characterization techniques, such as C-V (Capacitance-voltage) profiling, AFM (atomic force microscopy), TEM (transmission electron microscopy) and TLM (transfer length measurement). Additionally, a low-voltage flexible inverter circuit using solution-processed metal-oxide thin film transistors was fabricated and characterized. The results indicate that flexible, low voltage operating devices and circuits enable a viable alternative to silicon dominated semiconductor devices, and hence a path forward, for wearables and Internet of Things (IoT).

# CONTENTS

| 1 | INTRODUCTION                             |                                              |                                                   |    |

|---|------------------------------------------|----------------------------------------------|---------------------------------------------------|----|

|   | 1.1                                      | Motivat                                      | ion                                               |    |

|   | 1.2                                      | Structur                                     | e of the thesis                                   |    |

|   | 1.3                                      | Aim and                                      | d Scope of the Dissertaion                        |    |

|   | 1.4                                      | The Au                                       | thor's Contribution                               |    |

| 2 | BAC                                      | KGROUI                                       | ND                                                |    |

|   | 2.1                                      | Thin Film Transistors (TFTs)                 |                                                   |    |

|   | 2.2                                      | Metal or                                     | xide semiconductors                               |    |

|   | 2.3                                      | Solution                                     | n processing                                      |    |

|   | 2.4                                      | High-к Gate Dielectrics                      |                                                   |    |

|   | 2.5                                      | 0                                            | Electronics                                       |    |

| 3 | OVERVIEW OF THIN FILM TRANSISTORS (TFTS) |                                              |                                                   |    |

|   | 3.1                                      | Working                                      | g principle                                       |    |

|   | 3.2                                      | Paramet                                      | ters of Interest                                  |    |

|   |                                          | 3.2.1                                        | Current Voltage (IV) Characteristics              |    |

|   |                                          | 3.2.2                                        | Threshold Voltage (VTH)                           |    |

|   |                                          | 3.2.3                                        | Carrier Mobility (µ)                              |    |

|   |                                          | 3.2.4                                        | ON/OFF Ratio (I <sub>ON</sub> /I <sub>OFF</sub> ) |    |

|   |                                          | 3.2.5                                        | Metal Oxide Semiconductor (MOS) capacitance       |    |

|   |                                          | 3.2.6                                        | Breakdown voltage (V <sub>BD</sub> )              |    |

|   |                                          | 3.2.7                                        | Transconductance (g <sub>m</sub> )                |    |

|   |                                          | 3.2.8                                        | Subthreshold swing (S)                            |    |

|   |                                          | 3.2.9                                        | Contact Resistance (R <sub>c</sub> )              |    |

|   |                                          | 3.2.10                                       | Trap State Densities (D <sub>it</sub> )           |    |

| 4 | MAT                                      | TERIALS                                      | AND FABRICATION TOOLS                             |    |

|   | 4.1                                      | Metal O                                      | Dxide Semiconductors                              |    |

|   |                                          | 4.1.1                                        | Ink Formation                                     |    |

|   | 4.2                                      | Substrates - Glass and Kapton Polyimide (PI) |                                                   |    |

|   | 4.3                                      | 3 Metal Shadow Masks                         |                                                   |    |

|   |                                          | 4.3.1                                        | Gate and Drain-Source                             |    |

|   |                                          | 4.3.2                                        | Inverter Circuit                                  |    |

|   | 4.4                                      | Deposit                                      | ion Techniques                                    | 35 |

|   |     | 4.4.1    | Metal Electrodes - E-Beam Evaporator     | 35 |

|---|-----|----------|------------------------------------------|----|

|   |     | 4.4.2    | Metal Oxide Semiconductor - Spin Coating |    |

|   |     | 4.4.3    | High-κ Gate Dielectric - Anodization     |    |

| 5 | FAB | RICATIO  | ON PROCESS AND CHARACTERIZATION          |    |

|   | 5.1 | Device   | structure and Architecture               |    |

|   | 5.2 | Thin Fi  | lm Transistors (TFTs) Fabrication        |    |

|   | 5.3 | Flexible | e Inverter Circuits Fabrication          |    |

|   | 5.4 | Electric | al performance characterization          | 45 |

|   |     | 5.4.1    | Capacitance Voltage (CV)                 | 45 |

|   |     | 5.4.2    | Current Voltage (IV)                     | 46 |

|   |     | 5.4.3    | Flexibility – Bending performance        | 51 |

|   |     | 5.4.4    | Flexible Inverter circuit performance    |    |

|   |     | 5.4.5    | Trap State Densities (Dit)               |    |

|   | 5.5 | Thin fil | m and Material characterization          | 56 |

|   |     | 5.5.1    | Atomic force microscopy (AFM)            | 56 |

|   |     | 5.5.2    | Transmission electron microscopy (TEM)   |    |

| 6 | CON | ICLUSIC  | DNS                                      |    |

|   | 6.1 |          | Finding                                  |    |

|   | 6.2 | · · ·    | Work                                     |    |

# LIST OF FIGURES

| Figure 1. The array of electronic pattern on flexible substrate (for illustrative purpose)                                                                                                                                             | . 22 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 2. The general schematic structure showing comparison between the TFTs and MOSFETs                                                                                                                                              | . 24 |

| <b>Figure 3.</b> The general behavior of (a) transfer and (b) output characteristics of the TFT                                                                                                                                        | . 26 |

| <b>Figure 4.</b> The standard TLM test pattern consists of an array of rectangular metal contacts separated by different lengths                                                                                                       | . 30 |

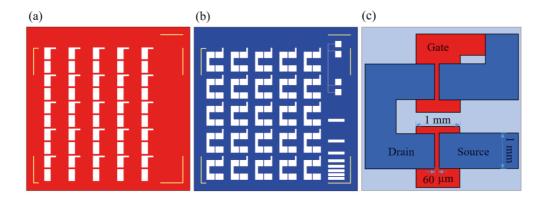

| Figure 5. TFT Masks (a) gate (b) Drain-source and (c) Top view of the drain-source overlapping with gate                                                                                                                               | . 34 |

| Figure 6. Inverter circuit masks (a) gate, (b) Drain-source mask and (c) Top view                                                                                                                                                      | . 34 |

| Figure 7. Photograph of the MBraun e-beam evaporator                                                                                                                                                                                   | . 35 |

| Figure 8. The schematic representation of the spin coating mechanism                                                                                                                                                                   | . 36 |

| Figure 9. The schematic representation of the anodization process                                                                                                                                                                      | . 37 |

| <b>Figure 10.</b> The Schematic representations of TFT architectures. (a) Bottom Gate –<br>Top Contact (BGTC), (b) Bottom Gate – Bottom Contact (BGBC), (c) Top<br>Gate – Top Contact (TGTC) and (d) Top Gate – Bottom Contact (TGBC). | . 39 |

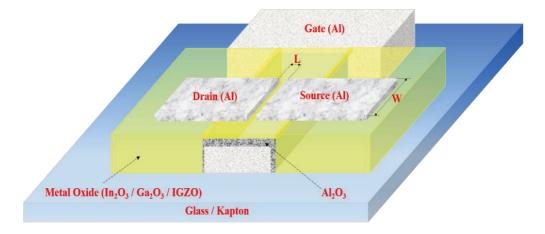

| Figure 11. Schematic representation of metal oxide TFT with Al <sub>2</sub> O <sub>3</sub> gate dielectric                                                                                                                             | . 40 |

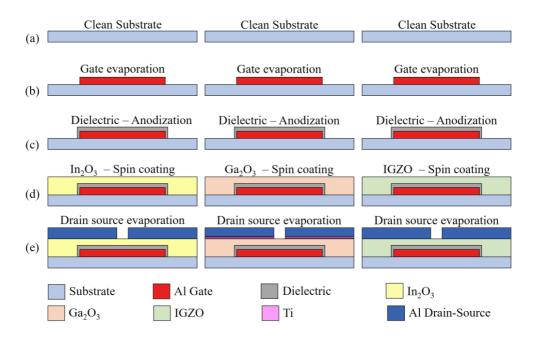

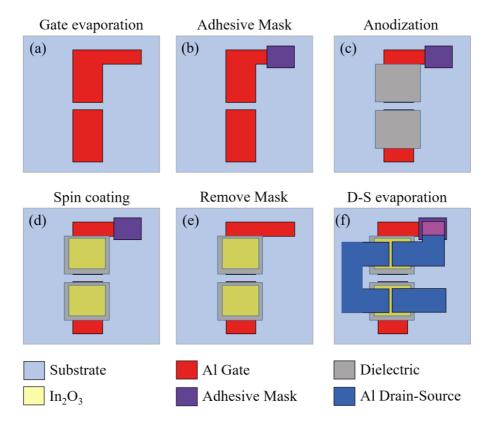

| <b>Figure 12.</b> Solution processed metal oxide TFT fabrication process flow with Al <sub>2</sub> O <sub>3</sub> gate dielectric                                                                                                      | . 41 |

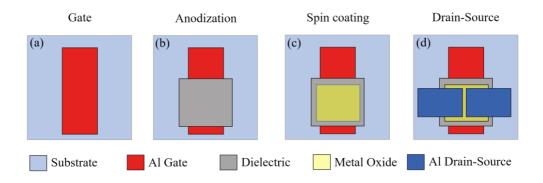

| Figure 13. Top view of the fabrication process flow                                                                                                                                                                                    | . 42 |

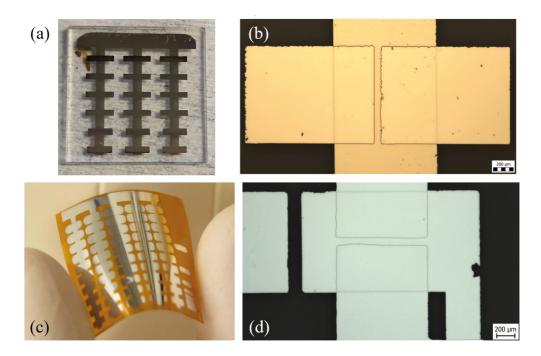

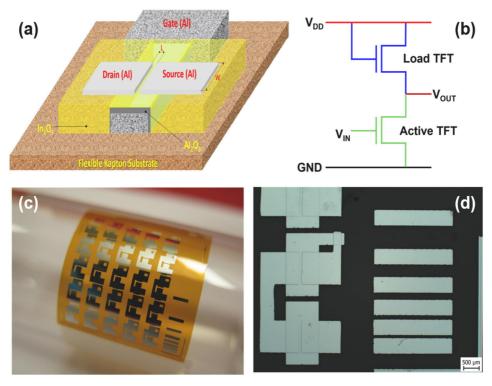

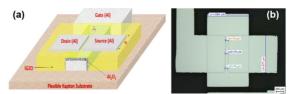

| <b>Figure 14.</b> (a) A photograph and (b ) Optical micrograph of the TFTs fabricated<br>on a glass substrates, (c) A photograph and (d ) Optical micrograph of the<br>TFTs fabricated on a flexible Kapton                                                                                                                                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Figure 15.</b> Proposed two TFT based inverter circuit processed metal oxide inverter circuit fabrication process flow with Al <sub>2</sub> O <sub>3</sub> gate dielectric                                                                                                                                                                                                                                                                    |

| Figure 16. Solution processed metal oxide inverter circuit fabrication process flow with Al <sub>2</sub> O <sub>3</sub> gate dielectric                                                                                                                                                                                                                                                                                                          |

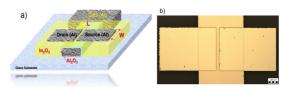

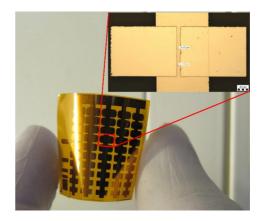

| <b>Figure 17.</b> Figure Heading Flexible inverter circuit (a) A photograph and (b) Optical micrograph. Scale bar 500 μm45                                                                                                                                                                                                                                                                                                                       |

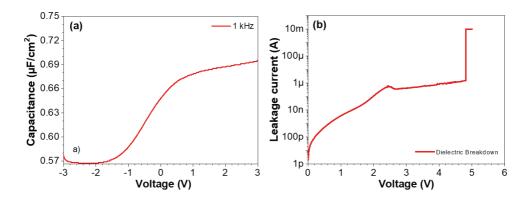

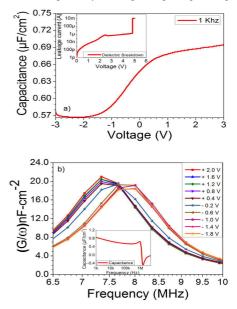

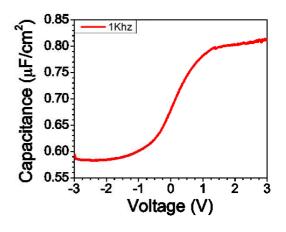

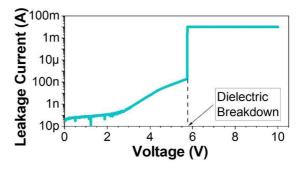

| Figure 18. a) The CV (capacitance voltage) characteristics measured at 1 kHz frequency and (b) Gate dielectric breakdown                                                                                                                                                                                                                                                                                                                         |

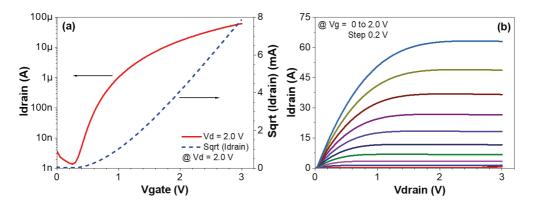

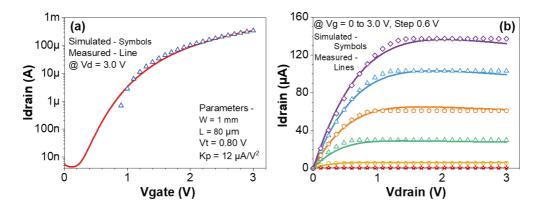

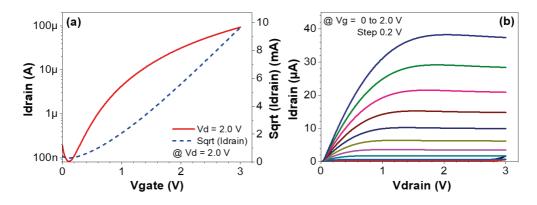

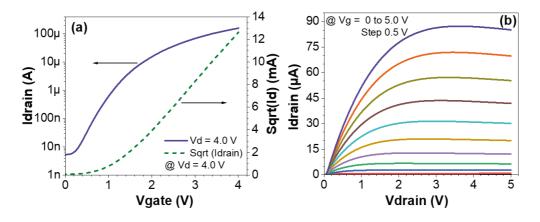

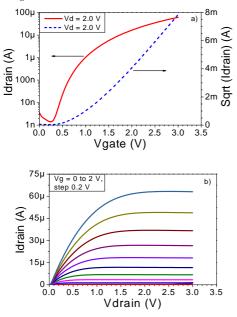

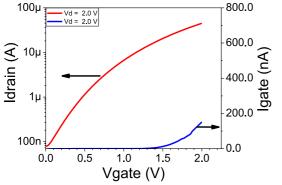

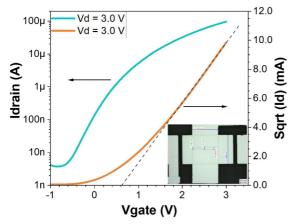

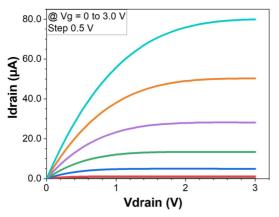

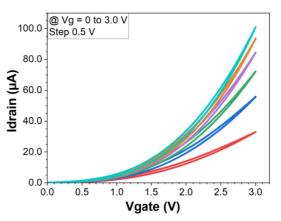

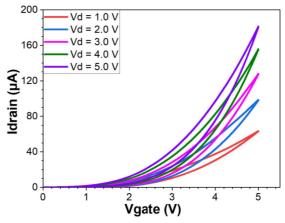

| <b>Figure 19.</b> (a) Transfer and (b) Output characteristic of In <sub>2</sub> O <sub>3</sub> TFT fabricated on glass substate                                                                                                                                                                                                                                                                                                                  |

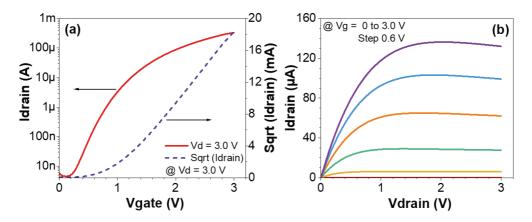

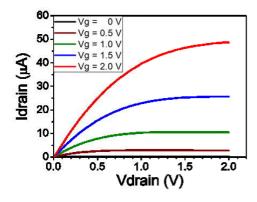

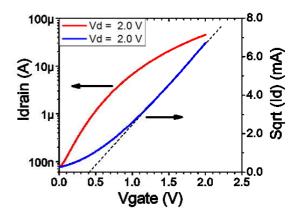

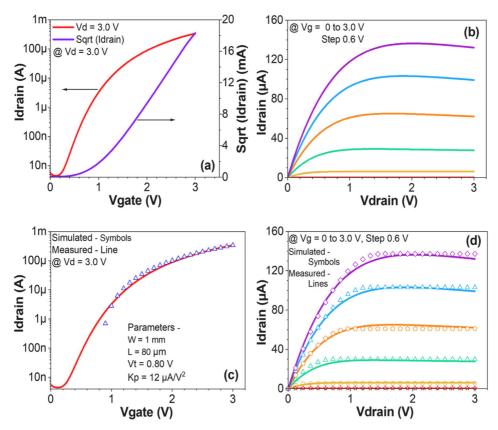

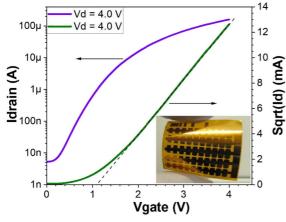

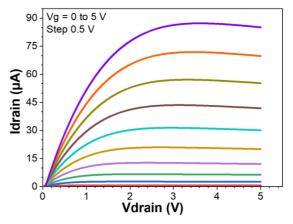

| <b>Figure 20.</b> (a) Transfer and (b) Output characteristic of In <sub>2</sub> O <sub>3</sub> TFT fabricated on flexible Kapton substrate                                                                                                                                                                                                                                                                                                       |

| Figure 21. (a) Transfer and (b) Output characteristic of flexible In2O3 TFT along with modeling                                                                                                                                                                                                                                                                                                                                                  |

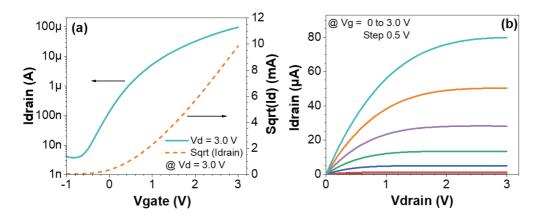

| Figure 22. (a) Transfer and (b) Output characteristic of Ga <sub>2</sub> O <sub>3</sub> TFT fabricated on glass substate                                                                                                                                                                                                                                                                                                                         |

| <b>Figure 23.</b> (a) Transfer and (b) Output characteristic of Ga <sub>2</sub> O <sub>3</sub> TFT fabricated on flexible Kapton substrate                                                                                                                                                                                                                                                                                                       |

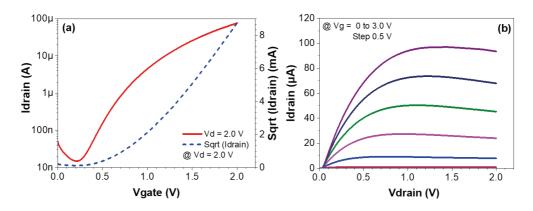

| Figure 24. (a) Transfer and (b) Output characteristic of IGZO TFT fabricated on glass substate                                                                                                                                                                                                                                                                                                                                                   |

| Figure 25. (a) Transfer and (b) Output characteristic of IGZO TFT fabricated on flexible Kapton substrate                                                                                                                                                                                                                                                                                                                                        |

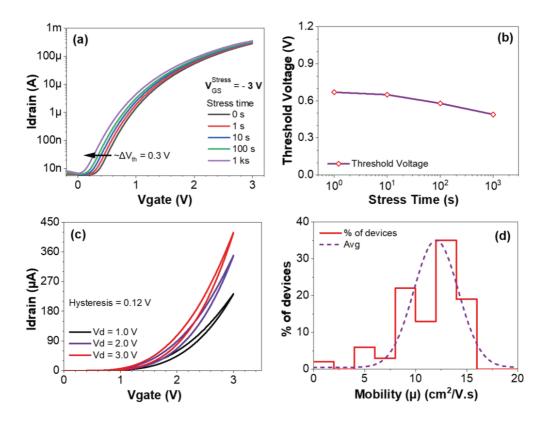

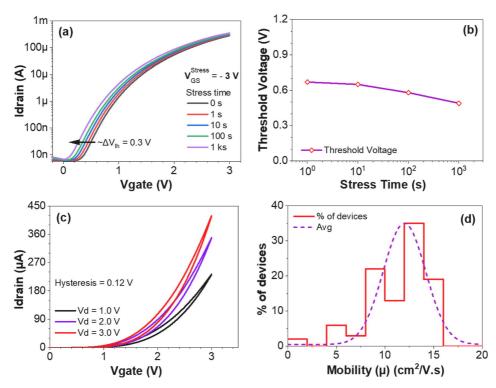

| <ul> <li>Figure 26. (a) Variation of transfer characteristics of In<sub>2</sub>O<sub>3</sub> TFTs measured as a function of gate bias stress time, at negative gate bias stress (NBS) of -3 V, b) Bias stress-induced threshold voltage shift as a function of stress time. c) Transfer characteristics of In<sub>2</sub>O<sub>3</sub> TFTs representing hysteresis, and d) Mobility histogram indicating device reliability and yield</li></ul> |

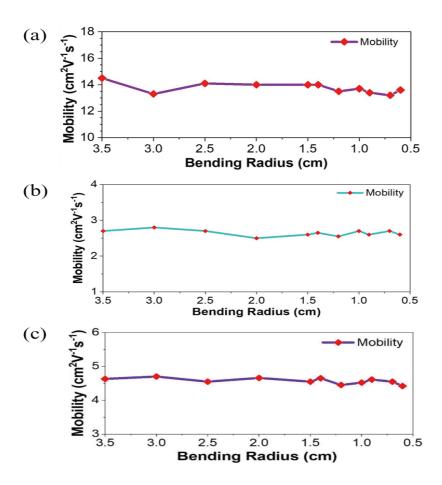

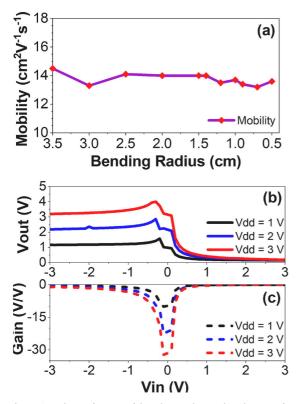

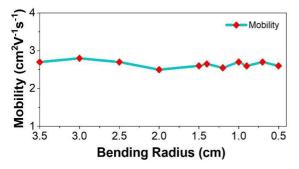

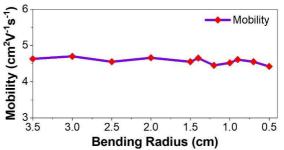

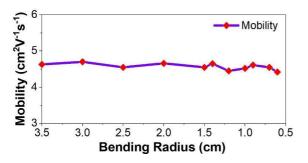

| <b>Figure 27.</b> Bending performance of the flexible TFTs based on a) In <sub>2</sub> O <sub>3</sub> , b) Ga <sub>2</sub> O <sub>3</sub> and c) IGZO                                                   | 52 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

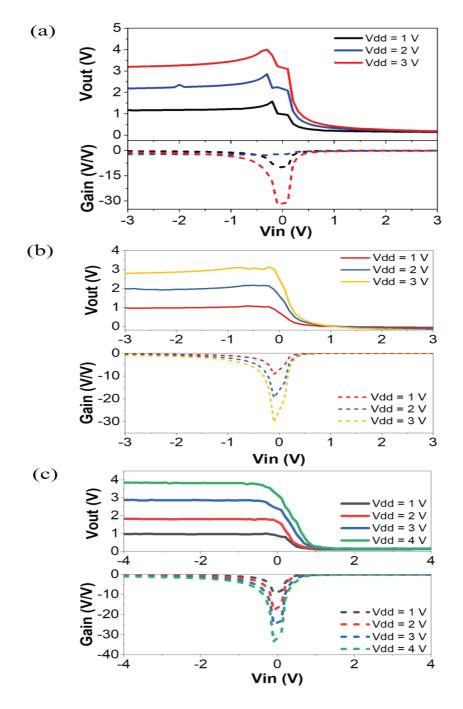

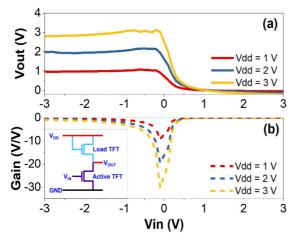

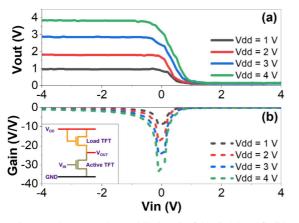

| <b>Figure 28.</b> The output voltage and gain with respect to input voltage of the flexible inverter circuit based on a) In <sub>2</sub> O <sub>3</sub> , b) Ga <sub>2</sub> O <sub>3</sub> and c) IGZO | 53 |

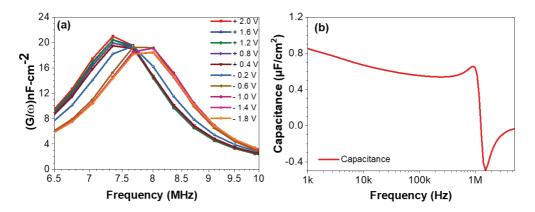

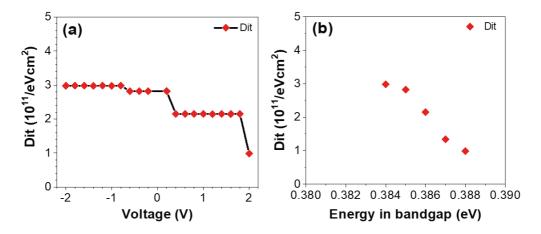

| Figure 29. (a) The $(G_p/\omega)$ plot as a function of frequency (b) The frequency dependance of MOS capacitance                                                                                       | 55 |

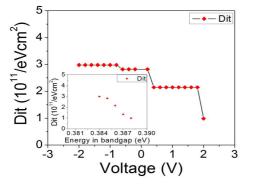

| Figure 30. The trap state densities as function of (a) Biasing voltage and (b) Energy in bandgap                                                                                                        | 55 |

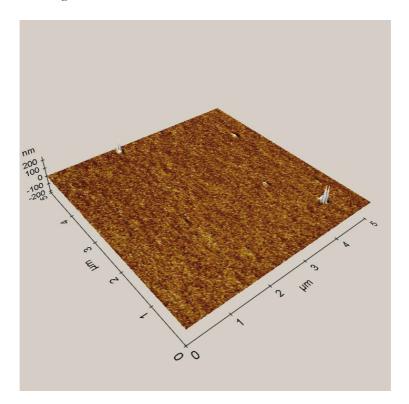

| <b>Figure 31.</b> AFM image of the anodized aluminum oxide (Al <sub>2</sub> O <sub>3</sub> ) showing average roughness value 1.53 nm                                                                    | 56 |

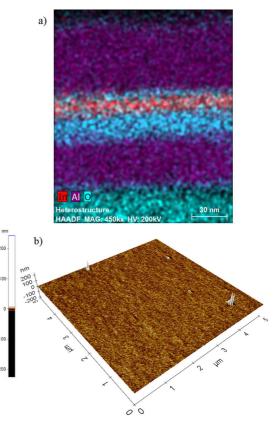

| Figure 32. The cross-sectional image of the TFT, scale bar 30 nm                                                                                                                                        | 57 |

# LIST OF TABLES

| Table 1. Summarized TFT fabrication process parameters                                  | 42 |

|-----------------------------------------------------------------------------------------|----|

| Table 2. TFT measurement bias conditions                                                | 50 |

| Table 3. Summarized metal oxide TFT performance parameters                              | 51 |

| Table 4. Summarized metal oxide based flexible inverter circuit performance parameters. | 54 |

# ABBREVIATIONS

| TFTs                           | Thin Film Transistors                |

|--------------------------------|--------------------------------------|

| IoT                            | Internet of Things                   |

| MO                             | Metal oxide                          |

| In <sub>2</sub> O <sub>3</sub> | Indium oxide                         |

| Ga <sub>2</sub> O <sub>3</sub> | Gallium oxide                        |

| IGZO                           | Indium gallium zinc oxide            |

| $Al_2O_3$                      | Aluminum oxide                       |

| AFM                            | Atomic force microscopy              |

| TEM                            | Transmission electron microscopy     |

| TLM                            | Transfer length measurement          |

| MOS                            | Metal oxide semiconductor            |

| $V_{G}$                        | Gate voltage                         |

| VD                             | Drain voltage                        |

| ID                             | Drain current                        |

| $V_{\text{th}}$                | Threshold voltage                    |

| μ                              | Mobility                             |

| D <sub>it</sub>                | Trap state densities                 |

| PI                             | Polyimide                            |

| PEN                            | Polyethylene naphthalate             |

| PET                            | Polyethylene terephthalate           |

| a-Si                           | Amorphous silicon                    |

| LTPS                           | Low temperature polysilicon          |

| R&D                            | Research and development             |

| RFID                           | Radio-frequency identification       |

| IV                             | Current voltage                      |

| CV                             | Capacitance voltage                  |

| FETs                           | Field effect transistors             |

| AMLCD                          | active-matrix liquid-crystal display |

| ICs                            | Integrated circuits                  |

| Si                             | Silicon                              |

|                                |                                      |

| СРМ              | Conduction band minimum                            |

|------------------|----------------------------------------------------|

| VBM              | Valence band maximum                               |

| EHD              | Electrohydrodynamic                                |

| HfO <sub>2</sub> | Hafnium oxide                                      |

| $ZrO_2$          | Zirconium oxide                                    |

| $SiO_2$          | Silicon oxide                                      |

| MOSFET           | Metal oxide semiconductor field effect transistors |

| CMOS             | Complementary metal oxide semiconductors           |

| W                | Channel width                                      |

| L                | Channel length                                     |

| Cox              | Oxide capacitance                                  |

| $V_{BD}$         | Breakdown voltage                                  |

| $I_{ON}/I_{OFF}$ | Current ratio                                      |

| SS               | Subthreshold swing                                 |

| gm               | Transconductance                                   |

| g <sub>p</sub>   | Peak conductance                                   |

| f                | Frequency                                          |

| q                | Electronic charge                                  |

| R <sub>c</sub>   | Contact resistance                                 |

| BGTC             | Bottom gate – top contact                          |

| BGBC             | Bottom gate – bottom contact                       |

| TGTC             | Top gate – top Contact                             |

| TGBC             | Top gate – bottom Contact                          |

| Al               | Aluminum                                           |

| Au               | Gold                                               |

| Ti               | Titanium                                           |

| IPA              | Isopropanol                                        |

| DI               | Deionized                                          |

|                  |                                                    |

# LIST OF PUBLICATIONS

- Publication I Sagar R. Bhalerao, Donald Lupo, Amirali Zangiabadi, Ioannis Kymissis, Jaakko Leppaniemi, Ari Alastalo and Paul R. Berger, "0.6V Threshold Voltage Thin Film Transistors with Solution Processable Indium Oxide (In<sub>2</sub>O<sub>3</sub>) Channel and anodized high-κ Al<sub>2</sub>O<sub>3</sub> Dielectric", IEEE Electron Device Letters, May 2019. DOI: 10.1109/LED.2019.2918492

- Publication II Sagar R. Bhalerao, Donald Lupo and Paul R. Berger, "2-volt Solution-Processed, Indium Oxide (In<sub>2</sub>O<sub>3</sub>) Thin Film Transistors on flexible Kapton", IEEE Xplore, IEEE International Flexible Electronics Technology Conference (IFETC), Aug. 2019. DOI: 10.1109/IFETC46817.2019.9073721

- Publication III Sagar R. Bhalerao, Donald Lupo and Paul R. Berger, "Flexible, Solution Processed, Indium Oxide (In<sub>2</sub>O<sub>3</sub>) Thin Film Transistor (TFT) and Circuits for Internet-of-Things (IoT)", Materials Science in Semiconductor Processing, Aug 2021 (Accepted)

- Publication IV Sagar R. Bhalerao, Donald Lupo and Paul R. Berger, "Flexible Gallium Oxide (Ga<sub>2</sub>O<sub>3</sub>) Thin Film Transistors (TFTs) and Circuits for the Internet of Things (IoT)", IEEE International Flexible Electronics Technology Conference (IFETC), Aug. 2021. DOI: 10.1109/IFETC49530.2021.9580524

- Publication V Sagar R. Bhalerao, Donald Lupo and Paul R. Berger, "Flexible Thin Film Transistor (TFT) and Circuits for Internet of Things (IoT) based on Solution processed Indium Gallium Zinc Oxide (IGZO)", IEEE International Flexible Electronics Technology Conference (IFETC), Aug. 2021. DOI: 10.1109/IFETC49530.2021.9580506

# 1 INTRODUCTION

#### 1.1 Motivation

One would wonder why anyone would want to look beyond the well-established and highly popular amorphous silicon (a-Si) technology and the availability of low temperature polysilicon (LTPS) when higher performance TFTs are needed. Despite this fact, TFT research and development (R&D) has expanded greatly in recent years in a quest to surpass a-Si. There are some strong driving forces for the continuous R&D effort, the first of which is fabrication cost reduction [1, 2]. Since the demand for much bigger display is rising in popularity, the materials cost is not as big an issue as it is with equipment and processing complexity, which accounts for more than half of the manufacturing cost. As a result, the primary goal is to reduce the number of manufacturing steps, while also simplifying the machinery. Therefore, simple solution deposition and printing methods may be used instead of vacuum deposition and photolithography [3, 4].

The second driving force is flexible electronics. The most popular substrate for TFT processing is glass or silicon, but its rigidity makes it easily breakable. Thus, lightweight, rugged displays with the added flexibility of being rollable, bendable, or foldable, and requiring no more maintenance than a paper document, are highly desirable. Mobile phones with roll-up display, e-books and electronic paper, and electronic smart cards are just a few of these applications [5]. Along with flexible displays, new functionality and applications such as radio-frequency identification (RFID) tags, transparent electronics, medical patches that can be applied to the skin to administer medications or track vital signs, disposable food quality monitor labels, novelty gadgets, Internet of Things (IoT), wearables and more are all possibilities [6, 7]. Therefore, with an eye on all upcoming future applications, flexible thin film transistors must be developed to meet modern needs rather than trying to replace established silicon [8-10].

### 1.2 Structure of the Thesis

The present thesis consists of total six chapters and five peer-reviewed publications, of which four are already published and one is accepted. The first chapter gives a broad overview of the subject, lays out the thesis' structure, and describes the author's contributions to publications. General insights of thin film transistors, materials and flexible electronics are presented in Chapter 2. Chapter 3 provides an overview of TFTs along with fabrication techniques and electrical parameters. The different materials, substrates and tools used for device fabrication are described in Chapter 4. In Chapter 5, device architecture along with comprehensive flexible TFTs and circuit fabrication, along with electrical performance and device characterization, is presented. The major findings are summarized in Chapter 6, and the publications are included at the end of the thesis.

#### 1.3 Aim and Scope of the Dissertation

Despite the focused effort and research on metal oxide semiconductors for thin film transistors (TFTs), the operating voltage, switching speed, on-off ratio, reproducibility, high temperature and vacuum processing are impeding them from being used in flexible electronics, wearables and Internet of Things (IoT). The majority of today's state-of-the-art metal oxide TFTs employ ALD (Atomic layer deposition), PLD (pulsed laser deposition), HVPE (halide vapor phase epitaxy), MBE (molecular beam epitaxy), MOVPE (metalorganic vapor phase epitaxy), and other expensive, high temperature and/or high vacuum deposition techniques, spatially for the gate dielectric and/or channel semiconductor deposition and processing. As a result of sophisticated equipment and complex processing, the cost of the manufacturing increases significantly. This makes them too expensive to scale to the trillions of IoT devices envisioned. Additionally, glass or silicon are the most common widely used substrates for TFT fabrication, however their hardness makes them readily breakable. They are also unsuitable for flexible wearable applications due to their rigidity, which may produce discomfort to the wearer.

The solution processing is believed to be one of the key routes to ultra-low-cost, light weight, easy processability, high-mechanical flexibility, which could be well exploited in scalable fabrication techniques for achieving a long standing goal of economic and high performance circuit fabrication. Low voltage operation, high performance circuitry is, together with energy autonomy, a key requirement for the anticipated "Wearables and Internet of Things (IoT)" to become reality. Therefore, the development of flexible thin film transistors (TFTs) and circuits based on solution-processed metal oxide semiconductors would open up an entirely new realm of possibilities in flexible wearable electronics.

The main objectives of the thesis are -

- To reduce the number of fabrication steps while also utilizing simpler equipment instead of vacuum deposition and photolithography.

- To investigate solution processing routes for active semiconductor (metal oxide) deposition at low temperature.

- To explore low temperature gate dielectric deposition methods compatible for flexible substrates.

- The fabrication of the low voltage (< 3 V) thin film transistors with a reliable device performance at relatively low temperature.</p>

- Fabrication and characterization of low voltage flexible TFTs and circuits for low energy flexible wearables and Internet of Things (IoT).

The scope of this thesis is to investigate the use of different metal oxide semiconductors for the fabrication of flexible thin film transistors and circuits for wearables and the Internet of Things (IoT) by combining solution processing with a room temperature deposited anodized high- $\kappa$  dielectric. In addition to electrical characterization, device performance under bending, interface analysis, and materials characterization are all covered in detail. Initially, TFTs were fabricated on glass substrates to create a device fabrication prototype, which was then used as a reference before the same architectures and processes were moved to flexible substrates. Henceforth, the flexible TFTs and inverter circuit were fabricated on flexible polyimide (Kapton) substrates following the same processes. The device performance analysis includes electrical characterization through current-voltage (IV) and capacitance-voltage (CV) measurements, contact resistance with the help of the transfer length measurement (TLM) method and interface studies using trap states density (D<sub>it</sub>). Furthermore, thin film and material characterization were performed via cross sectional transmission electron microscopy (TEM) and atomic force microscopy (AFM).

### 1.4 The Author's Contribution

**Publication I.** The author was responsible for the majority of the work, including indium oxide  $(In_2O_3)$  TFT fabrication and measurements along with manuscript writing. Amirali Zangiabadi performed the cross sectional TEM measurements. Prof. Donald Lupo and Prof. Paul R. Berger have assisted in the design of experiments and data interpretation as well as revising and improving the manuscript. Other co-authors also revised and improved the manuscript.

**Publication II.** The author was the main contributor and written the manuscript. The author fabricated the flexible TFTs and performed data analysis. The manuscript was revised and improved with the assistance of Prof. Donald Lupo and Prof. Paul R. Berger.

**Publication III.** The author was the main contributor. Flexible TFT and inverter circuit fabrication, electrical characterization and bending performance were carried by the author. The author analyzed the results and was responsible for the manuscript writing. With manuscript revision and improvement, Prof. Donald Lupo and Prof. Paul R. Berger have closely monitored the TFT modeling and bending performance.

**Publication IV.** The author was the main contributor. The author designed, fabricated, and characterized the gallium oxide (Ga<sub>2</sub>O<sub>3</sub>) based flexible TFTs, performed data analysis and drafted the manuscript. With the help of Prof. Donald Lupo and Prof. Paul R. Berger, the manuscript was revised and improved.

**Publication V.** The author made the main contribution. The flexible TFTs based on indium gallium zinc oxide (IGZO) were fabricated and characterized by the author. He also wrote the manuscript. The manuscript was rephrased and updated with the help of Prof. Donald Lupo and Prof. Paul R. Berger.

# 2 BACKGROUND

The chapter aims to provide a brief outline of the basic concepts of the device and processes utilized in the thesis. The thin film transistor (TFT) is discussed first, followed by metal oxide semiconductors. The solution processing and high- $\kappa$  gate dielectric are explored in the subsequent sections. A discussion of flexible electronics concludes the chapter.

#### 2.1 Thin Film Transistors (TFTs)

Realization of a transistor is a milestone in the context of the development of modern microelectronics since the control (i.e., gate) electrode empowers the implementation of functions, such as logic circuits, memory, amplification, processing and conditioning of electronic signal, which play a pivotal role in today's advanced technology [11-13]. Over the decades, transistors have been the foremost building blocks for electronics and continue to form the basis of today's modern devices and technological gadgets. There are many other types of transistors, but field effect transistors (FET) are the most often utilized, namely the metal-oxide-semiconductor field-effect-transistor (MOSFET). They have attracted a lot of attention as an electronic device for a variety of applications, including active-matrix liquid-crystal displays (LCDs), radio frequency identification (RFID) tags, opto-electronics, bio-medical devices, and more recently, flexible devices, printed RFID, and wearable devices [14, 15].

TFTs have similar origins as silicon MOSFET (Metal oxide semiconductor filed effect transistors) and integrated circuits (ICs), but each of these technologies has its own set of applications. With the advancements in fabrication techniques, for the silicon ICs, size is not an unsurmountable limitation, hence silicon ICs have become increasingly dense, and as the feature size is reduced, the cost goes down and performance increase [16, 17]. However, the availability of CMOS chips to populate ever increasing IoT demands could become a limitation as the number of IoT devices reaches the trillions, as is predicted [18]. TFTs, on the other hand, are driven

by large substrate size rather than system density [19]. TFTs have a lower cost per unit area than silicon ICs due to different fabrication processes, but the cost per FET is much higher [20-22].

#### 2.2 Metal Oxide Semiconductors

Metal oxide semiconductors form a distinct class of materials owing to their electrical charge transfer properties, as opposed to traditional covalent semiconductors such as silicon (Si) [23]. Metal oxide semiconductors have received a lot of attention and growth in recent years, due to a broad range of properties that set them apart from traditional silicon, such as a large band gap, high optical transparency, high mobility, and solution processable deposition at low temperatures. Metal oxide semiconductors are high-ionic-bonding valence compounds that contain at least one of the metal cations Zn, In, Ga, Sn, and Cd. The metal (M) ns orbital and oxygen (O) 2p orbitals dominate their conduction band minimum (CBM) and valence band maximum (VBM), respectively [24, 25].

Furthermore, in metal oxides, the charge carrier transport is slightly different due to the interaction between the metal and oxide orbitals. Even though electronic band structures in metal oxide semiconductors allow electron or hole transport, intrinsically achieving a good n-type or p-type conductivity is difficult [26]. Intrinsic point defects act as donors or acceptors in metal oxide semiconductors. However, in general, band gaps are often too large and defect levels too deep to have high concentration carriers. Hence, to achieve moderate or high conductivity, extrinsic doping is required [27, 28]. Nonetheless, despite some shortcomings, metal oxides are regarded as a crucial next generation semiconductor with significant promise, thanks to their outstanding advantages in terms of cost-effective fabrication, simple manufacturing process, environmentally safe production, fast composition changes, and high throughput [29, 30]. Therefore, metal oxide semiconductors have been extensively studied for thin film transistors [31, 32].

#### 2.3 Solution Processing

Solution processing is thought to be one of the main routes to ultra-low cost, light weight, fast processability, high-mechanical flexibility, which could be well suited in

scalable fabrication techniques for achieving a long-standing target of cost-effective and high-performance electronic circuits [33]. Low-voltage operation and highperformance circuitry, as well as energy autonomy, are essential for the "Wearables and Internet of Things (IoT)" to become a reality [34, 35]. Generally, there are two types of solution deposition processes: entire/whole area deposition and selective area deposition. For entire area deposition, spin-coating, dip-coating, and chemical bath deposition are often used, while for selective area deposition, printing methods are used. Amongst all, the most popular methods for depositing oxide films are spincoating, spray-coating, and printing process such as inkjet, gravure, flexography, aerosol jet, electrohydrodynamic (EHD) jet [36, 37].

Spin coating is the commonly used method for the entire area deposition since the resulting devices outperform their printed counterparts in terms of efficiency and durability. However, in recent years, as printing methods have become more popular, selective area deposition has become extremely significant because of lesser material wastage, cost effectiveness, environmentally sustainable processing, and improved device performance [38-42].

#### 2.4 High-κ Gate Dielectrics

The gate dielectric layer has a significant impact on the reliability and overall efficiency of a TFT. A gate dielectric layer contributes to the accumulation of electrons in the active layer by polarization induced by the gate electrode [43-45]. Therefore, numerous studies on gate dielectric have been focused on high- $\kappa$  oxides such as HfO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, ZrO<sub>2</sub>, etc. Since they have a much higher dielectric constant than standard silicon oxide (SiO<sub>2</sub>), they empower reduced leakage current while retaining a high capacitance [46-49]. Furthermore, high- $\kappa$  gate dielectrics also significantly reduce the device operating voltage (10 V or less) compared to silicon oxide devices (~30 V), As a result, TFTs with high- $\kappa$  gate dielectric can be used in power thrifty devices such as wearables and Internet of Things (IoT) applications. However, to deposit a good quality, high- $\kappa$  gate dielectric to minimize the gate leakage current and film densification, a high annealing temperature (>1000 °C) is needed [50, 51]. This high processing temperature has prevented high- $\kappa$  gate dielectrics. Therefore, low, or room temperature processing of gate dielectrics is also needed to

achieve a fully flexible TFT, similar to the low temperature method used for the active layer [53-54].

### 2.5 Flexible Electronics

Modern electronic devices are undergoing a transformative evolution, moving away from being rigid and bulky to being thin, soft, and flexible [55, 56]. The key impetus is to integrate electrical sensors and circuitry into everyday items in order to increase the performance of wearable devices, such as for sports or healthcare applications. Moreover, electronic integration is leading the way for new technologies such as smart tags, artificial robotics, and prosthetic devices along with sophisticated surgical instruments [57-59]. The technology of flexible electronics is now at a stage where device architecture and process integration can propel it. To transform the wellbeing of mankind through upcoming advanced technologies, electronic devices must be flexible, stretchable, lightweight, and environmentally friendly [60, 61]. In general, thin film transistors (TFTs) are essential components for any flexible electronic system and hence flexible thin-film transistors must fulfill specific requirements, such as reproducibility, reliability, high mobility, low threshold voltage, low temperature processing [62-64], etc. Thus, to envision the full potential of flexible electronics, it is possible that device performance, material efficiency, system integration and circuit design will be pushed to their limits [65, 66]. Figure 1 shows an array of electronic pattern on flexible substrate (for illustrative purpose).

Figure 1. The array of electronic pattern on flexible substrate (for illustrative purpose).

# 3 OVERVIEW OF THIN FILM TRANSISTORS (TFTs)

This chapter presents a detailed understanding of the basic concept and operating principle of the thin film transistor (TFT), as well as the key parameters. The first section provides an overview of the device's structure, while the subsequent section explores essential device parameters.

#### 3.1 Working Principle

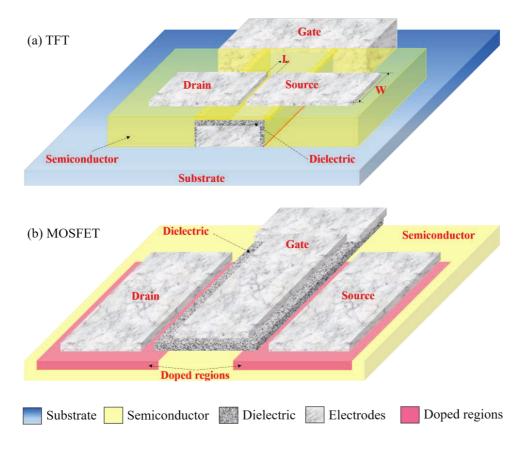

Thin field transistors (TFTs) are field effect devices with 3-terminals, namely - gate, source and drain. In terms of functionality and comprising layers, thin film transistors can be thought of as analogous to field effect devices, such as well-known metal oxide semiconductor field effect transistors in general (MOSFETs) [67]. However, there are significant differences amongst them, some of which may be understood by looking at their conventional architectures shown in Figure 2. Foremost, unlike TFTs, which are fabricated on an insulating substrate, usually glass, MOSFETs have a silicon wafer that serves as both the substrate and the semiconductor. As a result, MOSFETs offer better performance than polycrystalline or amorphous semiconductors since electrons flow in a single crystalline semiconductor with reduced scattering than polycrystalline or amorphous materials.

Furthermore, the temperatures used to fabricate both devices are significantly different, whereas processing temperatures above 1000 °C are typical for MOSFETs, for example to form the dielectric layer, TFTs are restricted by factors like the glass transition of substrate, which for most common glass substrates does not surpass 600 - 650 °C. MOSFETs also possess p-n junctions at the source-drain regions, which aren't present in TFTs. This associates with yet another significant difference in the way the device works, i.e., although both TFTs and MOSFETs depend on the field effect to modulate the conductance of the semiconductor near to its interface with the dielectric, in case of TFTs, an accumulation layer does this, but in MOSFETs, an inversion zone must be created near to the interface; in other words, in a p-type silicon substrate, an n-type conductive layer is formed.

TFTs can be fabricated using solution processing, low temperature and/or low vacuum deposition with amorphous or polycrystalline materials [68, 69]. Similar to the MOSFET, the gate dielectric plays a crucial role in device operation by separating the gate electrode from the active semiconductor material, which is in contact with source-drain electrodes [70]. The dielectric layer was deposited between the semiconductor and a gate contact. The modulation of current that flows through a semiconductor located between the source and drain electrodes is the primary basis of operation for TFT. The electric current flow modulation is generated in the semiconductor channel by capacitive injection and subsequent aggregation of carriers at the semiconductor-dielectric interface, characterized as field effect [71]. Figure 2 shows the general schematic structure comparing the TFTs and MOSFETs.

Figure 2. The general schematic structure showing comparison between the TFTs and MOSFETs.

The majority of TFT static parameters are derived from current-voltage (I-V) characteristics i.e., output and transfer characteristics, in two different operating

regimes: linear and saturation. Usually, the values of the drain current ( $I_d$ ) in the linear and saturation regimes are approximated by equations (1) and (2), respectively [72-78].

$$I_{D,sat} = \frac{W\mu C_{ox}}{2L} (V_{G} - V_{TH})^{2} \text{ for } V_{D} \ge V_{G} - V_{TH}$$

.....(2)

Where W is the channel width,  $\mu$  is the charge carrier mobility,  $C_{ox}$  is the specific capacitance of the gate dielectric per unit area, L is the channel length (Figure 2),  $V_{TH}$  is the threshold voltage,  $V_G$  is the gate voltage and  $V_D$  is the drain voltage.

#### 3.2 Parameters of Interest

To understand and analyze the electronic device, a set of electrical parameters needs to be used as a figure of merits. Some of the key parameters used in this dissertation are -threshold voltage (V<sub>TH</sub>), field effect mobility ( $\mu$ ), current ratio I<sub>ON</sub>/I<sub>OFF</sub>, MOS capacitance, breakdown voltage (V<sub>BD</sub>), transconductance (g<sub>m</sub>), Subthreshold swing (SS), contact resistance (R<sub>c</sub>) and trap states density (D<sub>it</sub>).

#### 3.2.1 Current Voltage (IV) Characteristics

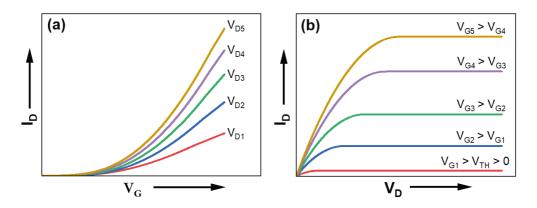

The current-voltage (I-V) characteristics, or plots, are the most important parameters to understand the behavior of the device. There are usually two kinds of currentvoltage (I-V) characteristics in TFTs. The first is the transfer characteristic (I<sub>D</sub> vs. V<sub>G</sub>), which is a plot of drain current (I<sub>D</sub>) vs. gate voltage (V<sub>G</sub>) over a finite number of drain voltages (V<sub>D</sub>). And the second is the output characteristic (I<sub>D</sub> vs. V<sub>D</sub>), which is a plot of drain current (I<sub>D</sub>) vs. drain voltage (V<sub>D</sub>) over a finite number of gate voltages ( $V_G$ ) [78-80]. The general behavior of transfer and output characteristics are represented Figure 3 (a) and (b), respectively.

Figure 3. The general behavior of (a) transfer and (b) output characteristics of the TFT.

#### 3.2.2 Threshold Voltage (VTH)

In general, the threshold voltage ( $V_{TH}$ ) is basically the point at which current begins to flow through the device, specifically, in the accumulation regime for TFTs [81, 82]. However, as there is no inversion charge occurs in TFTs since they are generally accumulation devices, thus in practice threshold voltage needs to be redefined. A linear extrapolation of the square root of drain current ( $I_D$ ) vs. gate voltage ( $V_G$ ) plot at a given drain voltage ( $V_D$ ) is often used to obtain the threshold voltage. On the square root  $I_D$  vs. gate voltage ( $V_G$ ) plot, a straight line is drawn from the point of maximum transconductance till zero. The intersection of this extrapolated line with the x-axis defines the threshold voltage. The threshold voltage may be calculated in the linear region, when  $V_D$  is fixed and  $I_D$  is not constant, as follows:

$$V_{\text{TH,lin}} = V_{\text{TH,Extrapolated}} - \frac{V_{\text{DS}}}{2}$$

.....(3)

However, as with mobility in the linear domain, inadequate charge injection might put the credibility of the linear extrapolation into doubt. So, if the saturation current  $I_{D,SAT}$  is constant and the fixed  $V_D$  is being used in the saturation region, then the values for  $V_{TH}$  are as follows:

$$V_{\text{TH,sat}} = V_{\text{TH,Extrapolated}}$$

.....(4)

TFTs can exhibit non-saturating characteristics, making linear extrapolation challenging. Additionally, the sluggish subthreshold turn-on within the TFTs ends up in substantial drain current before  $V_G$  approaches the projected threshold voltage. As a result, the actual value of the projected threshold voltage becomes more ambiguous. Therefore, A quasi-static capacitance-voltage (QSCV) measurement can be used as an alternative way to obtain  $V_{TH}$ . In this case, by shorted drain/source electrodes, the TFT transitions from the depletion to the accumulation region upon a gate voltage ( $V_G$ ) sweep. In the C-V measurements, the inclusion of the oxide (channel) capacitance in conjunction with the gate-source overlap and gate-drain overlap capacitances (geometrical capacitances) can be observed. The gate voltage ( $V_G$ ) at which the charge accumulation and its corresponding channel capacitance may be detected is designated as the threshold voltage ( $V_{TH}$ ).

#### 3.2.3 Carrier Mobility (µ)

Another important parameter is the carrier mobility  $(\mu)$ , which relates to the efficiency of charge carrier transport in a material, where the transport is restricted to a small area at the gate dielectric to semiconductor channel interface [83, 86]. It can also have a direct influence on the device's maximum drain current and operating frequency. The carrier mobility is defined by the following equation,

$$\mu_{(\text{sat})} = \frac{\left(\frac{\partial(\sqrt{I_D})}{\partial V_G}\right)^2}{\frac{1}{2}C_{\text{ox}}\frac{W}{L}} \qquad \dots \dots \dots (5)$$

where  $I_D$  is the drain current,  $V_G$  is the gate voltage,  $C_{ox}$  the specific capacitance of the gate dielectric per unit area, and W/L is the ratio of width to length (Figure 2) of the TFT channel.

#### 3.2.4 ON/OFF Ratio (I<sub>ON</sub>/I<sub>OFF</sub>)

The ratio of the maximum on-state current ( $I_{ON}$ ) to the minimum off-state ( $I_{OFF}$ ) current is termed as ON/OFF ratio or current ratio. The off-state current (minimum) is usually determined by the measuring equipment's noise level or the gate leakage current ( $I_G$ ), whereas the on-state current (maximum) is determined by the active channel (semiconductor material) and the strength of capacitive injection due to the field effect. The current ratio is a key important figure of merit because it shows how effectively the gate controls the channel and the leakage currents [87-89]. It is normally extracted from the transfer characteristics ( $I_D$  vs.  $V_G$ ), which demonstrates the ability of the device to differentiate between on and off states.

#### 3.2.5 Metal Oxide Semiconductor (MOS) capacitance

The metal-oxide-semiconductor (MOS) capacitor is the core of the TFT. It plays a vital role in dictating the charge carrier density in the channel and the drain current in an active semiconductor channel between drain and source [87-89]. It is basically a two-terminal one-dimensional structure made up of three layers, which includes a metal gate contact, an oxide dielectric, and the semiconductor in question. Under bias (positive or negative), the MOS capacitor may be found in either of three states: accumulation, depletion, and inversion [90-95].

#### 3.2.6 Breakdown voltage (V<sub>BD</sub>)

In order to fabricate durable and stable TFTs, understanding the maximum drain voltage ( $V_D$ ) allowed before dielectric breakdown is crucial [96]. This can be done by measuring the output characteristic of the TFT, with every measurement increasing in full drain voltage ( $V_D$ ), until the TFT breaks permanently [97]. The value of the breakdown voltage ( $V_{BD}$ ) is determined by the measurement done before breakdown. Furthermore, the persistent quest for high-performance devices has been driven by aggressive device scaling. With the device scaling, the thickness of the gate oxide must be reduced. In case of the thin dielectrics, the dielectric breakdown voltage ( $V_G$ ) due to the gate bias plays a significant role in the device operation, which is basically an applied gate voltage which causes a significant increment in the leakage current resulting in dielectric breakdown.

#### 3.2.7 Transconductance (g<sub>m</sub>)

Transconductance  $(g_m)$  is the change in the drain current as a function of a small change in the gate voltage under the constant drain voltage, essentially the DC gain. The electrical property that connects the current flowing across a device's output to the voltage through its input is known as transconductance  $(g_m)$  [98-100]. Transconductance is a measure of a TFT's performance, i.e., under steady state; the higher the transconductance, the larger the gain device can deliver [101]. It is the derivative of drain current (I<sub>D</sub>) with respect to gate voltage (V<sub>G</sub>) and it is represented by the equation (6)

#### 3.2.8 Subthreshold swing (S)

The subthreshold swing (S) is a measure of how quickly a transistor changes its state, i.e., off to on and vice versa [102]. It can be determined using the reciprocal steepest slope (subthreshold slope) in the log of drain current ( $I_D$ ) to gate voltage ( $V_G$ ) curve calculated below threshold. A steeper subthreshold slope also implies reduced biasing voltages needed to switch a TFT, thus lowering power requirements. Subthreshold swing is expressed in millivolts per decade, which signifies the voltage required to raise the drain current by an order of magnitude [103]. The subthreshold swing (S) is given as,

$$SS = \frac{dV_G}{dlog(I_D)} \qquad \dots \dots \dots \dots (7)$$

#### 3.2.9 Contact Resistance (R<sub>c</sub>)

The contacts are an important part of any electronic device where the semiconductor transitions to the connecting wires, at which this interface can lead to parasitic resistance losses that should be minimized. It is important to quantify the contact resistance in order to aid in better understanding how to minimize its deleterious

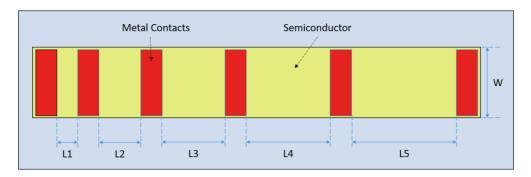

effects. [103, 104]. There are various ways and methods to measure the contact resistance. Amongst all, transfer length measurement (TLM) is the simplest and commonly used techniques for larger commonplace resistance values [105-107]. As shown in Figure 4, a standard TLM test pattern consists of an array of rectangular metal contacts separated by different lengths. The TLM plot can be constructed by comparing resistance between two sets of contacts, by which the contact resistance can be calculated.

Figure 4. The standard TLM test pattern consists of an array of rectangular metal contacts separated by different lengths.

#### 3.2.10 Trap State Densities (D<sub>it</sub>)

In amorphous semiconductors, the localized states caused due to structural defects, induces discrete states in the semiconductor's bandgap, which act as charge carrier traps that slows and reduces TFT response. The electrical performance of TFTs fabricated based on disordered semiconductors are hugely impacted by the density and energetic distribution of these localized states [108, 109]. Therefore, in a semiconductor device, under a low applied gate voltage and hence gate-induced carrier density, the bulk of the charges are trapped deep within the energy gap [110-112]. However, trap states near the transport stage are gradually filled as the gate voltage rises. As a result, the density of trap states ( $D_{it}$ ) influences the TFT's subthreshold slope, i.e., the slope of the transfer characteristics in the exponential area below the threshold voltage. It is observed that, in addition to subthreshold slope, interface trap density ( $D_{it}$ ) can also influence carrier mobility and bias stress effect as well as the semiconductor to drain-source contact interface [113].

# 4 MATERIALS AND FABRICATION TOOLS

Metal oxide semiconductors and their ink formation are discussed in this chapter. The next section discusses the types of substrates (rigid and flexible) utilized for the device fabrication. The chapter also provides an aspect of the design and geometry of the shadow mask used for the thin film transistor and inverter circuit. The deposition techniques for the metal contacts/electrodes (gate, drain-source), as well as gate dielectric and metal oxide semiconductor deposition are also presented in detail.

#### 4.1 Metal Oxide Semiconductors

Any future flexible electronic devices must be adaptable and processable at low temperatures. In this regard, metal oxide semiconductors have attracted a lot of interest for thin film transistors (TFT), due to their exceptional electrical, chemical and mechanical properties [114, 115], along with wide band gap, wide optical transparency, high mobility and low temperature solution processable deposition [116]. The metal-oxide semiconductors, indium oxide (In<sub>2</sub>O<sub>3</sub>), Gallium Oxide (Ga<sub>2</sub>O<sub>3</sub>), and Indium Gallium Zinc Oxide (IGZO) with bandgap 3.6 eV, 4.8 eV and 3.5 eV [116-119], respectively, are exclusively studied in this dissertation for flexible thin film transistors and circuit. Like solids, electronic characteristics of metal oxides can be best explained by their band structures; however, the interaction of the metal and oxygen orbits can result in much more complex electronic phenomena as well as a considerable disparity in carrier transport. The high degree of ionicity within chemical bonding of metal oxide semiconductors provides an electronic structure that differs from covalent semiconductors. In metal oxide semiconductors, the formation of Conduction band minimum (CBM) and valence band maximum (VBM) is facilitated by metal (M) ns and oxygen (O) 2p orbitals, respectively [120], resulting in a widely dispersed CBM and confined VBM. This results in reduced effective masses for electrons, enables greater electron transport than hole, hence, most metal oxide semiconductors display n-type behavior. While most metal oxides' electronic band structures technically facilitate charge transfer, the wide band gaps

hinder thermal carrier formation, resulting in low intrinsic carrier densities. Hence, the novel approaches are required to understand their conductivity mechanism. In general, non-stoichiometry of metal oxides are commonly attributed to electrical conduction. For example, n-type metal oxide semiconductor conductivity may be altered by deposition in oxygen-deficient or metal-rich environment. The oxygen vacancies as well as metal interstitial constitute viable electron donors [121].

#### 4.1.1 Ink Formation

The solution processable inks of the respective metal oxide semiconductors were prepared by dissolving the corresponding precursors in the solvents as follows –

- A. Indium Oxide (In<sub>2</sub>O<sub>3</sub>) Ink To form the In<sub>2</sub>O<sub>3</sub> ink, indium (III) nitrate hydrate In(NO<sub>3</sub>)<sub>3</sub>·xH<sub>2</sub>O was dissolved in 2-methoxyethanol anhydrous 99.8% in 0.2 M concentration [Publication I-III]. The resulting ink was stirred for 12 hours at 75 °C.

- B. Gallium Oxide (Ga<sub>2</sub>O<sub>3</sub>) Ink Ga<sub>2</sub>O<sub>3</sub> ink was prepared by dissolving Gallium (III) nitrate hydrate Ga(NO<sub>3</sub>)<sub>3</sub>·xH<sub>2</sub>O in deionized water (DI) with 0.1 M concentration [Publication IV]. The resulting ink was stirred for 12 hours at 75 °C.

- C. Indium gallium zinc oxide (IGZO) ink IGZO ink was formed by dissolving, indium nitrate hydrate (In(NO<sub>3</sub>)<sub>3</sub>·xH<sub>2</sub>O), gallium nitrate hydrate (Ga(NO<sub>3</sub>)<sub>3</sub>·xH<sub>2</sub>O), and zinc nitrate hydrate (Zn(NO<sub>3</sub>)<sub>3</sub>·xH<sub>2</sub>O) in a proportion of 0.085 : 0.0125 : 0.0275 M respectively [Publication V]. The resulting ink was stirred for 12 hours at 75 °C.

### 4.2 Substrates – Glass and Kapton Polyimide (PI)

In the TFT fabrication process, thin films are deposited onto insulating substrates [128]. The TFT can be fabricated on a rigid or flexible substrate, each of which has a set of advantages and disadvantages. The rigid substrates include glass and silicon wafers, having an advantage of being easy to fabricate, handle, clean and higher temperature processability [129]. On the other hand, the flexible substrates such as Kapton polyimide (PI), polyethylene terephthalate (PET), polyethylene naphthalate

(PEN), Polyurethane, fabric or paper, are gaining popularity for the wearables, lightweight, flexible and printed electronics [130]. Furthermore, despite the good mechanical stability, most of the flexible substrates have a limited thermal range, e.g., in case of polyurethane it is limited to 120°C, making them incompatible with high-temperature processing [131, 132]. Therefore, whether they are rigid or flexible, the substrates must be mechanically, chemically, and thermally stable during the fabrication, measurements and application [133].

Two type of substrates are used in this dissertation for the fabrication of TFTs and circuits: glass and Kapton polyimide (PI). Glass substrates are 25 mm by 25 mm square size with 1 mm thickness and Kapton polyimide are cut from the roll into 25 mm by 25 mm square size having a thickness of 200  $\mu$ m. In addition, multiple test samples were fabricated on glass substrates to aid in the optimization of the device fabrication process.

## 4.3 Metal Shadow Masks

The shadow mask is a collection of a sophisticated designs created by laser cutting or chemical etching on a thin metal sheet, usually stainless steel, and used to selectively deposit materials on substrates using a line-of-sight point-source process, like electron beam or thermal evaporation. They are commonly used to deposit materials onto the desired region of the substrate during vacuum evaporation and sometimes less directional sputtering processes. A number of metal shadow masks were used during the thin film transistors and circuit fabrication and optimization process to delineate gate metal pads and source/drain metal pads. All the metal shadow masks were conceptualized and designed in-house and fabricated from an outside vendor. The minimum dimensions (drain-source gap) were limited to  $60 \,\mu m$ only due to the vendor's manufacturing fidelity.

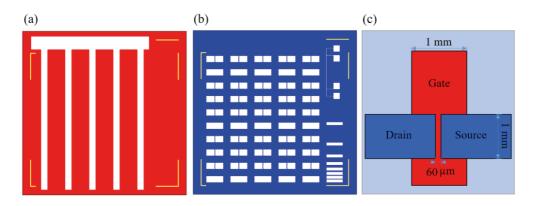

#### 4.3.1 Gate and Drain-Source

Two shadow masks, namely gate mask and drain-source mask as shown in Figure 5 (a) and (b), respectively, were used during the thin film transistor fabrication process to form a gate and drain-source electrodes. Figure 5 (c) represents the top view showing overlapping of the gate and drain-source along with dimensions. To reduce

or eliminate mismatch alignment between the layers, the size of this mask is kept the same as the substrate size.

Figure 5. TFT Masks (a) gate (b) Drain-source and (c) Top view of the drain-source overlapping with gate.

#### 4.3.2 Inverter Circuit

In a similar fashion to the TFT, for the fabrication of the inverter circuit two different shadow masks are used. First is the inverter gate mask and second is the inverter drain-source mask, as shown in Figure 6 (a) and (b), respectively. Figure 6 (c) represents the top view showing dimensions.

Figure 6. Inverter circuit masks (a) gate, (b) Drain-source mask and (c) Top view.

# 4.4 Deposition Techniques

### 4.4.1 Metal Electrodes - E-Beam Evaporator

To form (deposit) various metal contacts (Aluminum, Gold, Titanium) and inter layers (gate, drain-source, TLM and inverter) via metal shadow mask, an e-beam evaporator (which also includes a thermal/resistive source) as shown in Figure 7, provided by MBraun as an integrated part of a glovebox system was used. The use of metal shadow mask empowers the direct deposition and patterning of metal, eliminating the need of lithography techniques that expose samples to chemical developing and etching. The e-beam metal evaporation was always performed under a high vacuum below  $2 \times 10^{-6}$  Torr, which reduces oxidation of the evaporated metal.

Figure 7. Photograph of the MBraun e-beam evaporator.

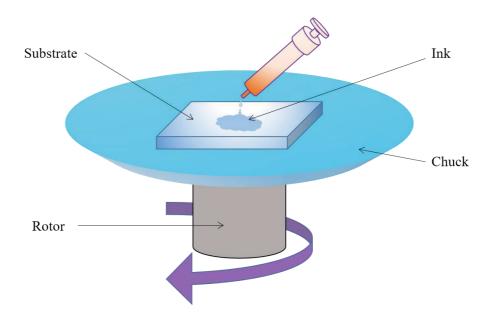

#### 4.4.2 Metal Oxide Semiconductor - Spin Coating

During the device fabrication process to deposit the solution processed metal oxide, the most versatile printing process, namely the spin coating technique was utilized. Although it wastes some ink, spin coating is a facile way for rapid prototyping. Technology transfer to other printing modalities can be leveraged once device optimization is well underway. Regardless of the substrates used, spin coating has many advantages, including ease of use, uniformity, reproducibility, and compatibility [134, 135]. The general mechanism of spin coating is the equilibrium condition between the centrifugal force generated by the rotating base and the viscous force produced by the viscosity of the solution is the theory of this operation. As soon as the desired solution is poured on the substrate, the spinning base containing the substrate is accelerated at higher angular speed, permitting excess solution to be removed from the surface by centrifugal force. The film is then dried and annealed at a specific temperature. The thickness of the resulting films depends on the speed and acceleration profile of the spin coating process as well as the viscosity and the molar concentration of the solution [136, 137]. Figure 8 shows the general mechanism of the spin coating process.

Figure 8. The schematic representation of the spin coating mechanism.

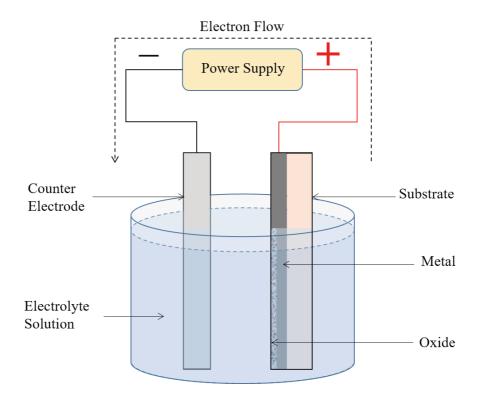

#### 4.4.3 High-κ Gate Dielectric - Anodization

For the high- $\kappa$  gate dielectric, aluminium oxide (Al<sub>2</sub>O<sub>3</sub>) was used for the thin film transistor and circuit fabrication process in the dissertation. The high- $\kappa$  gate dielectric was deposited using the anodization pathway empowering for low voltage device operation, i.e., < 3V, and the procedure was carried out in accordance with previous studies [138, 139]. The room temperature anodization allows high- $\kappa$  gate dielectric deposition on a flexible substrate, eliminating the need of high temperature [140], high vacuum processes [141-144], with additional benefits such as low cost, nanoscale deposition, denser and high-quality films [138-139]. The general representation of the anodization process is shown in Figure 9.

Figure 9. The schematic representation of the anodization process.

The 0.01M electrolyte solution was prepared by dissolving the citric acid monohydrate ( $C_6H_8O_7 \cdot H_2O$ ) in ultrapure deionized (DI) water. To achieve the desired oxide thickness, potentiostatic anodization was used. The working electrode (anode) was formed by immersing the evaporated gate (aluminum) electrode into the

electrolyte solution, with a platinum foil serving as the counter electrode (cathode). A Keithley source meter was utilized to provide the constant voltage (DC) source. For several minutes (30 min.), the anodization potential (5.0 V) was applied until the current dropped below 1  $\mu$ A. An approximately 9 nm aluminum oxide was produced with an oxide formation factor of 1.8 nm V<sup>-1</sup>. This resulted in a total oxide thickness of ~12 nm, included ~2 nm native oxide due to air exposure to deposited aluminum. The overall oxide thickness was confirmed by electron microscopy (TEM). Thereafter, the samples were rinsed with distilled water and dried under nitrogen flow.

# 5 FABRICATION PROCESS AND CHARACTERIZATION

The metal oxide (MO) thin film transistors were fabricated and characterized using the materials, process and equipment described in Chapter 4. The thin films and materials deposited were also investigated using transmission electron microscopy (TEM) and atomic force microscopy (AFM).

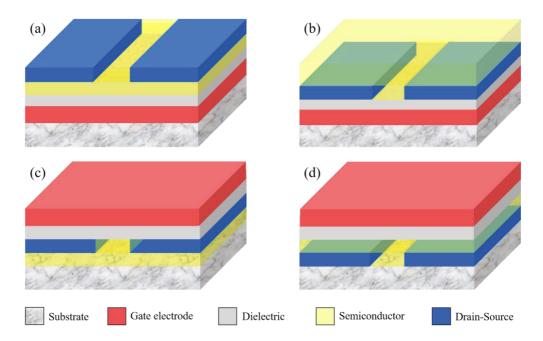

# 5.1 Device structure and Architecture

TFTs are comprised of five parts: substrate, gate, drain-source, semiconductor and gate dielectric.

Figure 10. The Schematic representations of TFT architectures. (a) bottom gate – top contact (BGTC), (b) bottom gate – bottom contact (BGBC), (c) top gate – top Contact (TGTC) and (d) top gate – bottom contact (TGBC).

Depending on the gate and drain-source electrode configurations in the semiconductor, there are four types of TFT architectures, bottom gate – top contact (BGTC), bottom gate – bottom contact (BGBC), top gate – top Contact (TGTC) and top gate – bottom contact (TGBC) [28]. The general schematic representations of these types are shown on Figure 10.

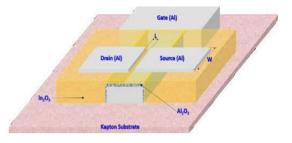

# 5.2 Thin Film Transistors (TFTs) Fabrication

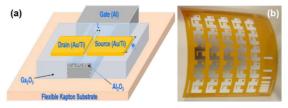

The three different metal oxide (MO) semiconductors, i.e., indium oxide  $(In_2O_3)$ , gallium oxide  $(Ga_2O_3)$ , and indium gallium zinc oxide (IGZO) were used to fabricate the thin film transistors on the two different substrates: glass and flexible Kapton. The initial TFT prototype was developed on a glass substrate with a channel length (L) 60 µm and width (W) 700 µm, with multiple iterations of the device fabrication. Subsequently, by following the same device prototype flexible TFTs were also fabricated on a flexible Kapton (polyimide) foil. Owing to the added advantage in ease of fabrication process, the bottom gate, top contact (BGTC) topology, as shown in Figure 11, was used here for the TFT fabrication. More details can be found in the attached publications I-V.

Figure 11. Schematic representation of metal oxide TFT with Al<sub>2</sub>O<sub>3</sub> gate dielectric.

The thin film transistors were separately fabricated on the  $25 \times 25$  mm glass and flexible Kapton substates. The glass and Kapton substrates were ultrasonically cleaned with acetone, IPA (isopropanol), and DI (deionized water) for 30 minutes each prior to device fabrication.

Figure 12. Solution processed metal oxide TFT fabrication process flow with Al<sub>2</sub>O<sub>3</sub> gate dielectric.