# Advanced grid concept with external busbars applied on III–V multijunction solar cells

Marianna Raappana Optoelectronics Research Centre Physics Unit, Tampere University Tampere, Finland marianna.raappana@tuni.fi Ninja Kajas Optoelectronics Research Centre Physics Unit, Tampere University Tampere, Finland ninja.kajas@tuni.fi Arto Aho Optoelectronics Research Centre Physics Unit, Tampere University Tampere, Finland arto.aho@tuni.fi Ville Polojärvi Optoelectronics Research Centre Physics Unit, Tampere University Tampere, Finland ville.polojarvi@tuni.fi

Timo Aho Optoelectronics Research Centre Physics Unit, Tampere University Tampere, Finland timo.aho@tuni.fi Riku Isoaho Optoelectronics Research Centre Physics Unit, Tampere University Tampere, Finland riku.isoaho@tuni.fi Antti Tukiainen Optoelectronics Research Centre Physics Unit, Tampere University Tampere, Finland antti.tukiainen@tuni.fi Mircea Guina Optoelectronics Research Centre Physics Unit, Tampere University Tampere, Finland mircea.guina@tuni.fi

*Abstract*—We report on the development of an advanced front contact grid design applied on GaInP/GaAs/GaInNAsSb solar cells. Unlike in a conventional grid pattern, the busbars are placed outside the active area of the solar cell. This enables minimizing the shadowing effect caused by the contact grid pattern as well as reaching smaller-active-area solar cells for concentrated photovoltaics, ultimately leading to higher conversion efficiencies. The quality of the solar cells was characterized by electroluminescence and current-voltage measurements. The concept was proven as a viable option for boosting the performance of multijunction solar cells.

# Keywords—contact grid design, front contact, III–V heterostructures, multijunction solar cell, CPV

# I. INTRODUCTION

To date, compound semiconductor solar cells have been the utmost performers when it comes to high-efficiency solar cell technologies - the highest conversion efficiency of 47.1% has been achieved with a metamorphic six-junction III-V solar cell under concentrated light [1]. In order to reach high-efficiency performance with multijunction devices, not only the solar cell materials and the choice of heterostructures need to be developed, but also all the other aspects affecting the photovoltaic conversion must be carefully optimized. These include grid optimization where the contact grid related power losses [2] should be minimized. In this respect, one important loss mechanism originates from the shadowing effect where the metal grid partly covers the area of the cell surface. Since the shadowing related losses are directly proportional to the grid area, reducing the grid area has an immediate effect on the conversion efficiency. However, grid optimization is an interplay of several factors, such as resistive losses originating from the emitter, the grid metals and pattern, and the contact between them.

The limits for minimizing the finger shadowing arise from the technical limitations of the grid fabrication, i.e., how narrow fingers can be fabricated, and especially in concentrated photovoltaics (CPV) the fingers must have a sufficiently large cross-sectional area in order to conduct all the photogenerated charge carriers also under high photogeneration levels. Thus, ideally, high aspect ratios resulting from narrow and thick fingers are desirable in CPV. Since there is only little improvement concerning the minimizing of the finger shadowing, grid optimization focuses usually on optimizing the grid pattern with respect to the finger spacing.

However, losses can be further reduced by minimizing the shadowing effect associated to the busbars. As an ultimate option, the busbars can be removed from the solar cell active area partly [3] or even completely [4, 5, 6], resulting in a busbarless grid concept. This would not only have a positive effect on the conversion efficiency by reducing the area of the unilluminated solar cell, but also enables fabrication of solar cells with smaller areas since busbars are not limiting the solar cell size. This would ultimately decrease the III–V material use and could be beneficial especially for micro-scale CPV [7], which aims at increasing cost-effectiveness by downscaling the module size.

Here we report on the operation of triple-junction solar cells fabricated with an advanced front contact grid design in which the busbars are located outside the solar cell active area. The quality of the device components was characterized both by electroluminescence (EL) and current-voltage (I-V) measurements.

#### II. EXPERIMENTAL

# A. Concept design

The present contact grid concept differs from a conventional front contact grid pattern which is fully located on top of the

Funded by European Research Council AdG AMETIST #695116

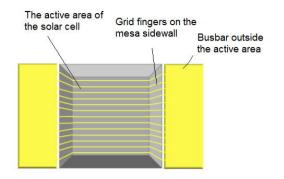

Fig. 1. A schematic of the grid concept.

mesa structure. Here, the busbars, i.e., the contact areas for current extraction, are placed outside the solar cell active area as shown in Fig. 1. The grid fingers are collecting the charge carriers from the emitter and further conduct the current to the busbars across the mesa sidewalls. Thus, an insulating dielectric layer is implemented between the metal fingers and the mesa sidewall in order to preserve the solar cell performance. Plasma enhanced chemical vapor deposition (PECVD) was used for dielectric fabrication since it is a low-cost, widely used, and scalable fabrication method.

# B. Electrical isolation study

Prior to device fabrication, dielectric insulation was investigated using a p-doped GaAs substrate. Subsequent to mesa etching, several different designs of dielectric layers of  $SiO_x$  and  $SiN_x$  with varying layer thicknesses and number of layers were deposited on the front surface of the sample and a planar metal layer on top of it. The samples were characterized using dark *I-V* measurements with a Metrohm Autolab potentiostat.

#### C. Device fabrication

The solar cell structures comprised monolithically stacked GaInP/GaAs/GaInNAsSb heterostructures that were grown on a p-GaAs substrate with a Veeco GEN20 molecular beam epitaxy system. A more detailed description of the growth can be found in [8]. Mesa structures were fabricated by etching. For isolation, a SiO<sub>x</sub>/SiN<sub>x</sub> (300 nm / 300 nm) coating was deposited on the mesa sidewalls by PECVD. The dielectric bilayer was overlapping with the front surface either 5, 10, or 20  $\mu$ m. The front contact metallization consisting of Ni/Au (10 nm / 200 nm) and back metallization of Ti/Au were deposited by electron beam evaporation. The front metals were partly deposited in tilted angle in order to assure the continuity of metal fingers also on steep mesa sidewalls. Lastly, contact GaAs was etched and a TiO<sub>x</sub>/SiO<sub>x</sub> antireflection coating was deposited by electron beam evaporation.

Photolithographic fabrication processes were used for sample masking during the device fabrication. For reference, similar device components were fabricated with a conventional H-pattern grid with two busbars located on top of the mesa structure. The sidewalls of the reference solar cells did not have an isolating coating. The active area of the studied and the reference solar cells was 4 mm<sup>2</sup>.

#### D. Device characterization

In order to study the electrical performance of the device components, their *I-V* performance was characterized with a 7 kW OAI Trisol solar simulator at one-sun (AM1.5D, 1 000 W/m<sup>2</sup>) at 25 °C. *I-V* under dark conditions was measured with a Bio Rad DL8000 instrument. The quality of the device processing was assessed by EL imaging, using a power supply and a microscope attached to a computer. Imaging was conducted at different current values and with two different filters: a Thorlabs shortpass filter (FES800) with a cut-off wavelength of 800 nm and a Thorlabs longpass filter (FEL850) with a cut-off wavelength of 850 nm enabling to detect EL from GaInP and GaAs subcells, respectively. In addition, the device components were imaged by scanning electron microscopy (SEM).

#### III. RESULTS AND DISCUSSION

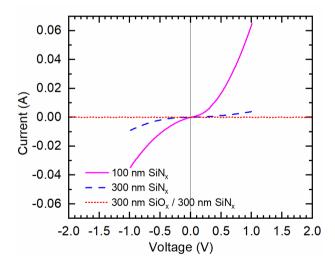

Based on the electrical isolation study, the design of a  $SiO_x/SiN_x$  (300 nm/ 300 nm) was chosen for the actual solar cell components. As presented in Fig. 2, it was the only design that did not conduct measurable current at bias voltages between -4 V and 4 V. The whole measurement range is not shown in the figure. The results from the isolation tests indicate that a thick enough dielectric layer is required between the metal and the semiconductor mesa sidewall for proper electrical isolation.

The averaged parameters obtained from the light-biased *I-V* measurements are summarized in Table I. The open-circuit voltage ( $V_{OC}$ ) values of the studied samples are comparable to the reference value. This indicates that all the three junctions are functional and thus the dielectric layer was sufficiently insulating the metal fingers from the mesa sidewalls and prevented shunting effects. However, slightly decreased fill factor values imply a slightly degraded cell performance.

Fig. 2. Dark *I-V* results of the electrical isolation study.

TABLE I.

PARAMETERS OF CURRENT-VOLTAGE PERFORMANCE

| Sample     | Parameters             |         |                 |

|------------|------------------------|---------|-----------------|

|            | Dielectric offset (µm) | Voc (V) | Fill factor (%) |

| <b>S1</b>  | 5                      | 2.58    | 60              |

| S2         | 10                     | 2.61    | 69              |

| <b>S</b> 3 | 20                     | 2.60    | 66              |

| Ref.       | -                      | 2.63    | 78              |

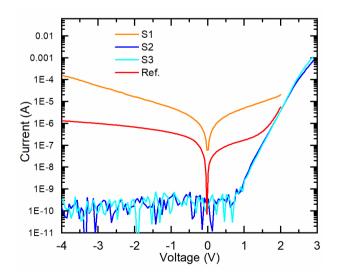

In order to further investigate the electrical performance, the dark I-V data shown in Fig. 3 was analyzed. Logarithmic scale was used for the absolute value of current in order to detect any differences for low current levels. The samples with the 10  $\mu$ m and 20 µm wide offsets show lower leakage current than the reference, and the current values go even below the measurement limit of ~1 nA. This indicates a non-shunting behavior. The sample with the 5 µm wide offset however shows an increased leakage current compared to the reference, which explains the lowered  $V_{OC}$  and fill factor values for sample S1. Except for this one sample, all the other device components with a 5 µm wide dielectric offset were heavily shunted. Most likely the shunting behavior of the 5 µm was due to a non-successful lithography process in which the dielectric layers were not completely covering the sidewalls and thus resulted in shunting electrical contacts between metal and the mesa sidewall.

In order to further investigate the cell performance, the spatial distribution of EL was analyzed. Fig. 4 shows EL detected from GaInP (using FES800) and GaAs (using FEL850) subcells. The GaAs subcell shows similar behavior to the reference cell where the EL signal seems very even throughout the device. This indicates that the current is spread evenly and no shunting is present. However, the EL from the GaInP subcell shows slightly degraded behavior. EL in the middle area of the device is slightly weaker compared to the areas closer to device facets. On the other hand, small bright areas right next to the

Fig. 3. Dark *I-V* results of the device components.

Fig. 4. EL images of GaAs (left) and GaInP (right) subcells. Upper images correspond to sample S3 and lower images to a reference sample.

device sidewalls indicate radiative perimeter recombination or edge emission. Based on the EL data, it is concluded that the smaller fill factor values are associated with decreased shunt resistance of the GaInP top cell, which is seen as a nonuniform EL pattern.

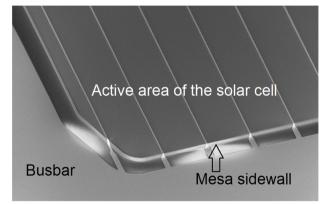

Overall, based on the imaging of the devices shown in Fig. 5, the fabrication was of high quality. With dielectric offsets wider than 5  $\mu$ m the fabrication was proven to be successful also in terms of photovoltaic operation. Moreover, the metal fingers on the steep mesa sidewalls were continuous. In order to ease the fabrication and to reduce the shadowing losses caused by the dielectric overlapping offset, the dielectric could be first fabricated with wider overlapping offset and then etched away from the top of the mesa. This approach could be further studied in the future.

Fig. 5. A SEM image of a fabricated device.

# IV. CONCLUSIONS

A proof-of-concept of an advanced grid design was demonstrated where the busbars were successfully placed outside of the active area of a multijunction solar cell. The achieved open-circuit voltage values were comparable to the reference value. This suggests that the dielectric insulation was adequate between the metal fingers and the mesa sidewall in order to prevent shunting. However, there is still room for improvement concerning the device performance. In summary, the concept was proven to work and can be considered as a viable option for boosting the performance of multijunction solar cells by reducing the shadowing losses.

# ACKNOWLEDGMENT

The work has been financially supported and carried out as part of the European Research Council Advanced Grant project AMETIST, #695116. It is also part of the Academy of Finland Flagship Program PREIN #320168. The authors want to thank Arttu Hietalahti and Severi Mäkelä for his technical assistance. In addition, M. R. acknowledges personal support from The Finnish Foundation for Technology Promotion, Jenny and Antti Wihuri Foundation, and Walter Ahlström Foundation. N. K. acknowledges Fortum Foundation for financial support.

#### REFERENCES

- M. A. Green, E. D. Dunlop, D. H. Levi, J. Hohl-Ebinger, M. Yoshita and A. W. Ho-Baillie, "Solar cell efficiency tables (version 54)," *Progress in Photovoltaics: Research and Applications*, Vol. 27, No. 7, pp. 565–575, 2019.

- [2] H. F. Hong, T. S. Huang and Y. Y. Chen, "Influence of metal grid spacing on the conversion efficiency of concentration solar cell at different illumination levels," *Materials Science and Engineering: B*, Vol. 188, pp. 43–47, 2014.

- [3] N. Hayashi, D. Inoue, M. Matsumoto, A. Matsushita, H. Higuchi, Y. Aya and T. Nakagawa, "High-efficiency thin and compact concentrator photovoltaics with micro-solar cells directly attached to a lens array," *Optics express*, Vol. 23, No. 11, pp. A594–A603, 2015.

- [4] A. Lorenz, C. Gredy, A. Senne, S. Beyer, Y. Yao, P. Papet, J. Ufheil, H. Reinecke and F. Clement, "Flexoprinted busbarless solar cells for multiwire interconnection," *Energy Proceedia*, Vol. 98, pp. 46–60, 2016.

- [5] P. Hacke, B. Murphy, D. Meakin, J. Dominguez, J. Jaramillo, M. Yamasaki and J. Gee, "Busbarless emitter wrap-through solar cells and modules," In 2008 33rd IEEE Photovoltaic Specialists Conference, IEEE, pp. 1–5, 2008, May.

- [6] A. Schneider, R. Harney, S. Aulehla, E. Lemp and S. Koch, "Progress in interconnection of busbar-less solar cells by means of conductive gluing," *Energy Procedia*, Vol. 38, pp. 387–394, 2013.

- [7] A. Ritou, P. Voarino and O. Raccurt, "Does micro-scaling of CPV modules improve efficiency? A cell-to-module performance analysis.," *Solar Energy*, Vol. 173, pp. 789–803, 2018.

- [8] A. Aho, V. Polojärvi, V. M. Korpijärvi, J. Salmi, A. Tukiainen, P. Laukkanen and M. Guina, "Composition dependent growth dynamics in molecular beam epitaxy of GaInNAs solar cells," *Solar Energy Materials and Solar Cells*, Vol. 124, pp. 150–158, 2014.