# 0.6V Threshold Voltage Thin Film Transistors with Solution Processable Indium Oxide (In<sub>2</sub>O<sub>3</sub>) Channel and anodized high- κ Al<sub>2</sub>O<sub>3</sub> Dielectric

Sagar R. Bhalerao, Donald Lupo and Paul R. Berger, Senior Member, IEEE

Abstract— Low voltage operation and low processing temperature of metal oxide transistors remains a challenge. Commonly metal oxide transistors are fabricated at very high processing temperatures (above 500°C) and their operating voltage is quite high (30 - 50 V). Here, thin film transistors (TFT) are reported based upon solution processable indium oxide (In<sub>2</sub>O<sub>3</sub>) and room temperature processed anodized high-k aluminum oxide (Al<sub>2</sub>O<sub>3</sub>) for gate dielectrics. The In<sub>2</sub>O<sub>3</sub> TFTs operates well below V<sub>ds</sub> of 3.0 V, with on/off ratio 10<sup>5</sup>, subthreshold swing (SS) 160 mV/dec, and low threshold voltage V<sub>th</sub> 0.6 V. The electron mobility ( $\mu$ ) is as high as 3.53 cm<sup>2</sup>/V.s in the saturation regime and transconductance g<sub>m</sub> 53 µS. Furthermore, the detailed capacitance voltage (C-V) analysis also investigated, the measurements shows low leakage gate current. Additionally, the interface trap density (Dit) in the oxide/semiconductor interface was quite low i.e. 0.986  $\times$  10<sup>11</sup> – 2.98  $\times$  10<sup>11</sup> eV<sup>-1</sup>.cm<sup>-2</sup>, signifying decent compatibility of In<sub>2</sub>O<sub>3</sub> with anodic Al<sub>2</sub>O<sub>3</sub>.

Index Terms— Metal oxide semiconductors, Solution processable indium oxide  $(In_2O_3)$ , Low voltage TFT, anodization.

# I. INTRODUCTION

Metal oxide semiconductors have been extensively studied in the last few years for a wide range of devices and device applications such as thin film transistors (TFT) for transparent and flexible electronics, active matrix and flat panel displays, bio/medical sensors, and radio frequency (RF) circuits [1-3]. Metal oxide semiconductors gained special attention due to their diverse spectrum of properties that distinguishes them from those of conventional silicon, such as wide band gap, wide optical transparency, high mobility and low temperature solution processable deposition [4]. They have paved the way for the next generation thin film and printed electronics [5]. Amongst all the metal-oxide semiconductors, indium oxide (In<sub>2</sub>O<sub>3</sub>) is the most favorable n-type semiconductors for thin film transistors with a band gap 3.6 - 3.75 eV and high carrier mobility [6]. However, most of the reported research on indium oxide thin film transistors has been based upon vacuum deposition techniques and high temperature annealing, with very high operating voltage 30 - 50 V [7, 8]. On the other hand,

This paragraph of the first footnote will contain the date on which you submitted your paper for review. "This work was supported TEKES (now Business Finland) and the Academy of Finland."

Sagar R. Bhalerao is with the Department of Computing and Electrical Engineering, Tampere University, Finland, (e-mail: sagar.bhalerao@tuni.fi).

thin film transistors based on solution processes has many desirable manufacturing advantages over the conventional vacuum deposition processes, such as low cost, high yield and ease of processing [9, 10]. Although remarkable progress has been made, metal oxide thin film transistors still pose significant challenges, such as operating voltage, switching speed and on/off ratio.

Here we fabricated TFTs based upon  $In_2O_3$  channels by combining the solution-processing route for the semiconductor and an anodization technique for the high- $\kappa$  aluminum oxide  $Al_2O_3$  gate dielectric, which enables a low operating voltage i.e. < 3V device operation. The anodization process was carried out as reported previously [11]. Anodization empowers the room temperature deposition of dielectric, bypassing high temperature, high vacuum processes, with added advantages such as nanoscale deposition, high quality and denser oxide layers to prevent gate leakage current [12]. Furthermore, the anodization process is a low cost, room temperature process, compatible with flexible and printed electronics devices. The detailed analysis of its electrical performance and thorough analysis of MOS capacitors for the interface strap states density was also investigated.

### II. EXPERIMENTAL

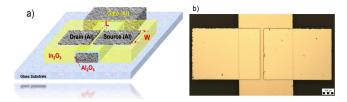

The bottom gate, top contact (BGTC) topology was used here for the device fabrication as shown in Fig. 1. TFTs were fabricated on glass substrates. Prior to device fabrication, the glass substrates were ultrasonically cleaned with acetone, IPA and deionized water for 30 minutes sequentially. Initially, to form a gate contact, 100 nm of aluminum (Al) metal was

Fig. 1. a) Schematic structure of the  $ln_2O_3$  TFT with  $Al_2O_3$  gate dielectric. b) Optical image of the fabricated  $ln_2O_3$  TFT with 70  $\mu m$  gate length.

Donald Lupo is with the Department of Computing and Electrical Engineering, Tampere University, Finland, (e-mail: donald.lupo@tuni.fi).

Paul R Berger is with the Department of Computing and Electrical Engineering, Tampere University, Finland, (e-mail: paul.berger@tuni.fi) and the Department of Electrical and Computer Engineering, The Ohio State University, USA (e-mail: pberger@ieee.org).

deposited on a glass substrate using a shadow mask for patterning.

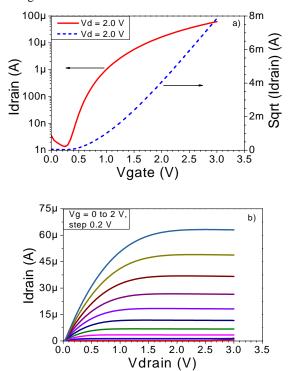

Fig. 2. a) Transfer characteristics of  $In_2O_3$  TFTs with 70  $\mu m$  gate lengths and b) Output characteristics for  $In_2O_3$  TFTs with 70  $\mu m$  gate lengths.

The anodization process was performed next to convert a top surface (~10 nm) of the aluminum metal into a high-κ dielectric, Al<sub>2</sub>O<sub>3</sub>. After the anodization, the substrates were thoroughly washed with deionized water. Subsequently, the solution processed In<sub>2</sub>O<sub>3</sub> semiconductor channel was deposited atop by first spin coating, followed by two-step annealing at 90 °C and at 300 °C for 15 min and 30 min in air, respectively. Furthermore, the In<sub>2</sub>O<sub>3</sub> solution was prepared by dissolving Indium (III) nitrate hydrate In(NO<sub>3</sub>)<sub>3</sub>·xH<sub>2</sub>O in anhydrous 2methoxyethanol 99.8% in 0.2 M concentration as reported by Ari Alastalo et al. [13]. The solution was stirred for 12 hours at 75 °C prior to spin coating. All the precursors were purchased from Sigma-Aldrich and used as-is without any further distillation. Finally, 100 nm of Al metal was deposited to form the drain and source electrodes. The channel width (W) and length (L) was 700 µm and 70 µm, respectively. The Al metal evaporation was performed using an e-beam evaporator under a high vacuum 10<sup>-6</sup> Torr. Under the same conditions as the TFTs, MOS test structures consisting of Al/Al<sub>2</sub>O<sub>3</sub>/In<sub>2</sub>O<sub>3</sub>/Al were also fabricated on the same substrates.

The electrical characterization (I-V and C-V) of the  $In_2O_3$  TFTs were performed using a Cascade probe station connected to the semiconductor device parameter analyzer (Keysight B1500A) with triaxially shielded probes.

# III. RESULTS AND DISCUSSION

The transfer ( $I_d$  vs  $V_g$ ) and output ( $I_d$  vs  $V_d$ ) characteristics of the TFTs devices consisting of  $In_2O_3$  as the semiconductor channel with anodized  $Al_2O_3$  as the gate dielectrics are shown

in Fig. 2. The devices exhibits n-channel behavior, with a very low operating voltage, 3 volts, and the threshold voltage,  $V_{th}$  is determined to be 0.6 V, which is much smaller than that of TFTs fabricated with conventional SiO<sub>2</sub> gate dielectric [14]. The operating voltage of the In<sub>2</sub>O<sub>3</sub> TFTs with Al<sub>2</sub>O<sub>3</sub> make them an ideal choice for integrated circuits (IC) applied to wearables and IoT applications where autonomous power sources would be depleted by TFTs operating at low voltages.

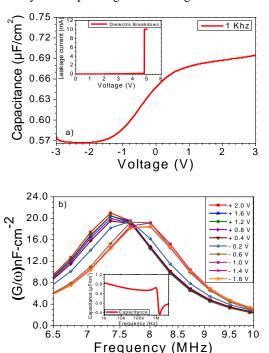

Fig. 3. a) Capacitance voltage characteristics of  $In_2O_3/Al_2O_3$  MOS device measured at 1 KHz frequency. Inset: Breakdown voltage and b)  $G/\omega$  vs  $\omega$  characteristics representing conductance at selected bias voltage. Inset: capacitance vs. frequency

The devices exhibits on/off ratio  $\sim 10^5$  and the electron mobility ( $\mu$ ) was measured as high as 3.53 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> in saturation regime calculated using the equation

$$\mu_{(sat)} = \frac{\left(\frac{\partial (\sqrt{I_D})}{\partial V_G}\right)^2}{\frac{1}{2}C_G \frac{W}{L}}$$

Where,  $I_D$  is the drain current,  $V_G$  is the gate voltage,  $C_G$  is the gate oxide capacitance, and W/L is the ratio of width to length of the TFT channel. The gate oxide thickness were estimated from the capacitance voltage curve shown in Fig. 3 (a) and was extracted to be  $\sim 8$  nm. The  $Al_2O_3$  formed with anodization, exhibits a very low leakage current below the measured breakdown field of 6.07 MV/cm [Fig 3 (a) inset]. The TFT transconductance  $(g_m)$  gain is as high as 53  $\mu S$ . Furthermore, the subthreshold swing S was only 0.16 V/dec., which is comparatively quite low compared to the previously reported [15]. This implies there is a lower defect density of states within the gate oxide. As shown in the Fig. 3 (b) inset, the capacitance per area of the MOS structure show high values  $(0.6 - 0.8 \, \mu F/cm^2)$  over a flat frequency response from 1 KHz to 1.3 MHz shows the good dielectric properties.

To investigate this further, we have calculated the interface

trap density ( $D_{it}$ ) in the oxide by using the conductance method by sweeping from 1 KHz to 5 MHz [16],

$$D_{it} = \frac{2.5}{q} \left( \frac{G_p}{\omega} \right)_{max}$$

Where,  $G_p$  is the peak conductance per unit area,  $\omega = 2\pi r f$  (f - frequency), and q is the electronic charge. To calculate the interface trap density  $(D_{it})$ ,  $(G_p/\omega)$  was plotted as a function of frequency. As shown in the Fig. 3 (b), as the frequency increases,  $G_p/\omega$  also increases and reaches its maximum and as expected with an interface trap model,  $G_p/\omega$  starts to decrease with further increase in frequency [17].

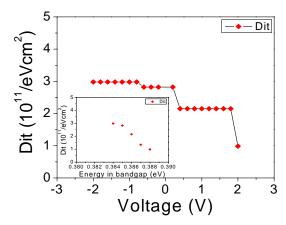

Fig. 4. Trap states density as function of biasing voltage, Inset: Trap states density as a function of energy.

The interface trap density extracted using the measured maximum conductance [18] was about  $0.986 \times 10^{11} - 2.98 \times 10^{11} \, \text{eV}^{\text{-1}}.\text{cm}^{\text{-2}}$ . The subsequent relationships among trap states densities with biasing voltage dependence and their energy levels are represented in the Fig. 4. Summarized results of In<sub>2</sub>O<sub>3</sub> TFT performance parameters are shown in Table 1.

IV. CONCLUSION

TABLE I SUMMARIZED IN2O3 TFT PERFORMANCE PARAMETERS

| V <sub>th</sub> (V) | $\mu_{sat}$ (cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ) | Gm<br>(µS) | SS<br>(V/dec) | $I_{\rm on}/I_{\rm off}$ | D <sub>it</sub><br>(eV <sup>-1</sup> .cm <sup>-2</sup> ) |

|---------------------|----------------------------------------------------------------|------------|---------------|--------------------------|----------------------------------------------------------|

| 0.6                 | 3.5                                                            | 53         | 0.16          | ~105                     | $0.986 - 10^{11}$                                        |

Thin film transistors (TFTs) based on low-temperature, solution-processable indium oxide (In<sub>2</sub>O<sub>3</sub>) with a very thin (< 10nm) anodic aluminum oxide Al<sub>2</sub>O<sub>3</sub> as gate dielectric were demonstrated here with very low voltage device operation. The TFTs shown very good low voltage performance below 3.0 V and the electron mobility ( $\mu$ ) is as high as 3.53 cm<sup>2</sup>/V.s. Furthermore, we also investigated that the dielectric properties of the anodic aluminum oxide Al<sub>2</sub>O<sub>3</sub> and its estimated interface trap density, D<sub>it</sub> about 0.986 × 10<sup>11</sup> – 2.98 × 10<sup>11</sup> eV<sup>-1</sup>.cm<sup>-2</sup>, suggests a very good compatibility of indium oxide (In<sub>2</sub>O<sub>3</sub>) with anodic aluminum oxide Al<sub>2</sub>O<sub>3</sub>. This study shows the low temperature fabrication compatibility for solution-processable metal oxide semiconductors for flexible and printed electronics devices.

## ACKNOWLEDGMENT

The authors would like to extend a special thanks to TEKES

(now Business Finland) and the Academy of Finland for providing funding.

### REFERENCES

- [1] L. Petti, N. Münzenrieder, C. Vogt, H. Faber, L. Büthe, G. Cantarella, F. Bottacchi, T. D. Anthopoulos, and G. Tröster, "Metal oxide semiconductor thin-film transistors for flexible electronics", Appl. Phys. Rev., vol. 3, no. 2, pp. 021303(1–53), Feb. 1986. DOI: 10.1063/1.4953034.

- [2] E. Fortunato, P. Barquinha, and R. Martins, "Oxide Semiconductor Thin-Film Transistors: A Review of Recent Advances", Adv. Mater., vol. 24, no. 12, pp. 2945–2986, May 2012. DOI: 10.1002/adma.201103228.

- [3] J. S. Park, W.-J. Maeng, H.-S. Kim, J.-S. Park, "Review of recent developments in amorphous oxide semiconductor thin-film transistor devices", *Thin Solid Films*, vol. 520, no. 6, pp. 1679–1693 Jan 2012. DOI: 10.1016/j.tsf.2011.07.018.

- [4] J. E. Medvedeva, D. B. Buchholz, and R. P. H. Chang, "Recent Advances in Understanding the Structure and Properties of Amorphous Oxide Semiconductors", Adv. Electron. Mater., vol. 3, no. 9, pp. 1700082(1–17), Sept. 2017. DOI: 10.1002/aelm.201700082.

- [5] M.-G. Kim, M. G. Kanatzidis, A. Facchetti and T. J. Marks, "Low-temperature fabrication of high-performance metal oxide thin-film electronics via combustion processing", *Nature Materials*, vol. 10, pp. 382–388, May 2011. DOI: 10.1038/nmat3011.

- [6] R. Hu, Y. Pei, Z. Chen, J. Yang, Y. Li, J. Lin, Y. Zhao, C. Wang, J. Liang, B. Fan, and G. Wang, "Ultra-High Field-Effect Mobility Thin-Film Transistors With Metal-Organic Chemical Vapor Deposition Grown In<sub>2</sub>O<sub>3</sub> Channel Treated by Oxygen Microwave Plasma", *IEEE Electron Device Letters*, vol. 36, no. 11, pp. 1163 1165, Nov 2015. DOI: 10.1109/LED.2015.2476507.

- [7] X. Yu, T. J. Marks and A. Facchetti, "Metal oxides for optoelectronic applications", *Nature Materials*, vol. 15, pp. 383–396, April 2016. DOI: 10.1038/nmat4599.

- [8] Dhananjay, S.-S. Cheng, C.-Y. Yang, C.-W. Ou, Y.-C. Chuang, M. C. Wu and C.-W. Chu, "Dependence of channel thickness on the performance of In<sub>2</sub>O<sub>3</sub> thin film transistors" *J. Phys. D: Appl. Phys.*, vol. 41, no. 9, pp. 092006(6), April 2008, doi:10.1088/0022-3727/41/9/092006.

- [9] C.-M. Kang, H. Kim, Y.-W. Oh, K.-H. Baek, and L.-M. Do, "High-Performance, Solution-Processed Indium-Oxide TFTs Using Rapid Flash Lamp Annealing", *IEEE Electron Device Letters*, vol. 37, no. 5, pp. 595 598, May 2016. DOI: 10.1109/LED.2016.2545692.

- [10] J.-W. Choi, S.-Y. Han, M.-C. Nguyen, A. H.-T. Nguyen, J. Y. Kim, S. Choi, J. Cheon, H. Ji, and R. Choi, "Low-Temperature Solution-Based In2O3 Channel Formation for Thin-Film Transistors Using a Visible Laser-Assisted Combustion Process", *IEEE Electron Device Letters*, vol. 38, no. 9, pp. 1259 1262, Sept. 2017. DOI: 10.1109/LED.2017.2734905.

- [11] M. Kaltenbrunner, P. Stadler, R. Schwödiauer, A. W. Hassel, N. S. Sariciftci, and S. Bauer, "Anodized Aluminum Oxide Thin Films for Room Temperature Processed, Flexible, Low Voltage Organic Non Volatile Memory Elements with Excellent Charge Retention", Adv. Mater., vol. 23, no. 42, pp. 4892–4896, Sept. 2011. DOI: 10.1002/adma.201103189.

- [12] Y. Qin, D. H. Turkenburg, I. Barbu, W. T. T. Smaal, K. Myny, Wan-Yu Lin, G. H. Gelinck, P. Heremans, J. Liu, and E. R. Meinders, "Organic Thin-Film Transistors with Anodized Gate Dielectric Patterned by Self-Aligned Embossing on Flexible Substrates", Adv. Funct. Mater., 2012, vol. 22, no. 6, pp. 1209–1214, Jan 2012.

- [13] J. Leppäniemi, O.-H. Huttunen, H. Majumdar, and A. Alastalo, "Flexography-Printed In2O3 Semiconductor Layers for High- Mobility Thin-Film Transistors on Flexible Plastic Substrate", Adv. Mater., vol. 27, no. 44, pp. 7168–7175, Oct. 2015. DOI: 10.1002/adma.201502569.

- [14] L. Lan and J. Peng, "High-Performance Indium-Gallium-Zinc Oxide Thin-Film Transistors Based on Anodic Aluminum Oxide", *IEEE Transactions On Electron Devices*, vol. 58, no. 5, pp. 1452 – 1455, May 2011. DOI: 10.1109/TED.2011.2115248.

- [15] A. D. Mottram, Pi. Pattanasattayavong, I. Isakov, G. Wyatt-Moon, H. Faber, Y.-H. Lin, and T D. Anthopoulos, "Electron mobility enhancement in solution-processed low-voltage In2O3 transistors via channel interface planarization", AIP Advances, vol. 8, no. 6, pp. 065015 (8), June 2018. DOI:10.1063/1.5036809.

- [16] Dieter K. Schroder, "Semiconductor Material and Device Characterization", 3rd ed., Wiley-IEEE Press, 2015, pp. 347–349. DOI:10.1002/0471749095.

- [17] S. Kundu, S. K. Roy and P Banerji, "GaAs metal—oxide–semiconductor–device with titanium dioxide as dielectric layer: effect of oxide thickness on the device performance", *J. Phys. D: Appl. Phys.*, vol. 44, no. 15, pp. 155104 (6), April (2011). DOI:10.1088/0022-3727/44/15/155104.

[18] G. Brammertz, H. C. Lin, K. Martens, D. Mercier, C. Merckling, J. Penaud, C. Adelmann, S. Sioncke, W. E. Wang, M. Caymax, M. Meuris, and M. Heyns, "Capacitance–Voltage Characterization of GaAs–Oxide Interfaces", *Journal of The Electrochemical Society*, vol. 155, no. 12, pp. H945–H950 Oct. 2008. DOI: 10.1149/1.2988045.