# HESAM ZOLFAGHARI

# Flexible Low-Area Hardware Architectures for Packet Processing in Software-Defined Networks

Tampere University Dissertations 357

Tampere University Dissertations 357

# HESAM ZOLFAGHARI

# Flexible Low-Area Hardware Architectures for Packet Processing in Software-Defined Networks

ACADEMIC DISSERTATION To be presented, with the permission of the Faculty of Information Technology and Communication Sciences of Tampere University, for public discussion in Zoom on 21 December 2020, at 12 o'clock.

#### ACADEMIC DISSERTATION

Tampere University, Faculty of Information Technology and Communication Sciences Finland

| Responsible<br>supervisor<br>and Custos | Professor Jari Nurmi<br>Tampere University<br>Finland   |                                                                          |

|-----------------------------------------|---------------------------------------------------------|--------------------------------------------------------------------------|

| Pre-examiners                           | Professor Guido Maier<br>Politecnico di Milano<br>Italy | Professor Seppo Virtanen<br>University of Turku<br>Finland               |

| Opponents                               | Professor Guido Maier<br>Politecnico di Milano<br>Italy | Professor Peeter Ellervee<br>Tallinn University of Technology<br>Estonia |

The originality of this thesis has been checked using the Turnitin OriginalityCheck service.

Copyright ©2020 author

Cover design: Roihu Inc.

ISBN 978-952-03-1805-5 (print) ISBN 978-952-03-1806-2 (pdf) ISSN 2489-9860 (print) ISSN 2490-0028 (pdf) http://urn.fi/URN:ISBN:978-952-03-1806-2

PunaMusta Oy – Yliopistopaino Vantaa 2020

# ACKNOWLEDGEMENTS

This dissertation is based on the research carried out throughout the years 2017-2020 in the Electrical Engineering Unit of Tampere University (prior to 2019 by the name Department of Electronics and Communications Engineering at Tampere University of Technology). First and foremost, I express my deepest gratitude to my supervisor, professor Jari Nurmi for sharing with me his many-year experience in custom processor design as well as providing financial support and a peaceful environment for carrying out this research. I am also grateful to assistant professor Davide Rossi from University of Bologna for being the second author of all scientific papers included in this dissertation as well as for arranging a research visit to the Microelectronics Lab of University of Bologna.

I appreciate the time and effort of the respected reviewers, associate professors Guido Maier and Seppo Virtanen for providing constructive feedback on this work. Also, thanks to professor Peeter Ellervee and associate professor Guido Maier for accepting to be the opponents in my thesis defense.

This research was funded by The Pekka Ahonen Fund, Finnish Doctoral Training Network DELTA, HiPEAC, Nokia Foundation, 5G-FORCE project and TETRAMAX project. I hereby express my gratitude to all the above-mentioned funding bodies.

Finally, I wish to thank all members of my family for supporting me throughout the years and providing me with the energy required for achieving my academic goals.

Tampere, November 2020 Hesam Zolfaghari

# ABSTRACT

Computer networks have changed radically in the last 10 years. Advances in computer networks and emergence of new network protocols require more flexibility and programmability in forwarding devices such as switches and routers. The main components of these devices are the control and data plane. The former instructs functionality and the latter just executes the dictated functionality. In the traditional philosophy for designing forwarding devices, the control and data plane were tightly coupled. With increase in the number and complexity of network protocols, this design principle proved to be inefficient. Software Defined Networking (SDN) breaks this tight coupling of the control and data plane. Under this network architecture, a central controller installs forwarding rules on the tables in forwarding devices. SDN-based forwarding devices only contain the data plane and the interface for communicating with the control plane. By matching the value of header fields against the installed rules, the data plane executes the corresponding actions. Research on SDN is done on the control and data planes as well as and the interface making their communication possible.

In this dissertation, the focus is on the programmable data plane. It is the enabling component for protocol-independent packet processing. The most notable hardware architecture for programmable data plane is Reconfigurable Match Tables (RMT). Despite its capabilities, there are a number of shortcomings associated with it that make it unnecessarily complex, limit its flexibility and use the memory resources inefficiently. In response to these shortcomings, a new architecture has been designed and implemented. The packet parser in this new architecture does not employ Ternary Content Addressable Memory (TCAM). As a result, it reduces the area of memories required for Match-Action packet parsing by 50%. The area saving is used for providing packet preprocessing functionality in the packet parser. The crossbar alternatives for search key generation and action input selection have been explored and the most area-efficient alternatives has been selected. Yet another packet parser is designed whose supported throughput is 10 times that of RMT parser whereas the area increase factor is less than 2. Finally, a packet processing pipeline has been designed with enhanced level of flexibility and functionality. Despite the enhancements, it has 31% less area compared to the RMT pipeline.

# CONTENTS

| 1 | Intro | oduction   |                                                      | 17 |

|---|-------|------------|------------------------------------------------------|----|

|   | 1.1   | Objectiv   | ves and scope                                        | 19 |

|   | 1.2   | Researc    | h questions                                          |    |

|   |       | 1.2.1      | Research questions specific to packet parser         |    |

|   |       | 1.2.2      | Research questions specific to the packet processing |    |

|   |       |            | subsystem                                            |    |

|   | 1.3   | Research   | h significance                                       |    |

|   | 1.4   | Contrib    | utions and results                                   |    |

|   | 1.5   | Author'    | s contribution                                       | 22 |

|   | 1.6   | Thesis of  | outline                                              | 22 |

| 2 | Pack  | et Process | ing                                                  | 23 |

|   | 2.1   | Packet r   | processing operations                                |    |

|   |       | 2.1.1      | Parsing                                              |    |

|   |       | 2.1.2      | Integrity checking                                   |    |

|   |       | 2.1.3      | Header field manipulation                            |    |

|   |       | 2.1.4      | Tunnelling                                           |    |

|   |       | 2.1.5      | State modification                                   |    |

|   |       | 2.1.6      | Lookup                                               |    |

|   |       |            | 2.1.6.1 Exact Matching                               |    |

|   |       |            | 2.1.6.2 Ternary Matching                             |    |

|   |       | 2.1.7      | Classification                                       |    |

|   |       | 2.1.8      | Fragmentation and reassembly                         |    |

|   |       | 2.1.9      | Traffic Management                                   |    |

|   | 2.2   |            | e-based packet processing solutions                  |    |

|   |       | 2.2.1      | Software Routers                                     |    |

|   |       | 2.2.2      | Programming Languages                                |    |

|   |       | 2.2.3      | User-space Packet Processing                         |    |

|   | 2.3   |            | packet processing solutions                          |    |

|   |       | 2.3.1      | Solutions based on FPGAs                             |    |

|   |       | 2.3.2      | Solutions based on GPUs                              |    |

|   | 2.4   |            | ased packet processing solutions                     |    |

|   |       | 2.4.1      | Network Processors                                   |    |

|   |       | 2.4.2      | Programmable Switch Chips                            |    |

|   | 2.5   |            | ry of Packet Processing Solutions                    |    |

|   | 2.6   | Applicat   | tions of Programmable Data Plane                     | 41 |

| 3 | AN    | ew Programmable Packet Parser                       | 44 |

|---|-------|-----------------------------------------------------|----|

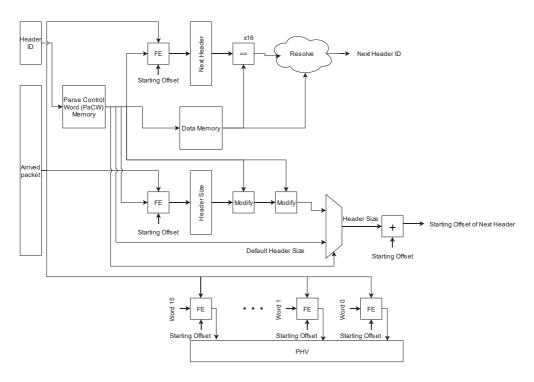

|   | 3.1   | A Closer Look at Packet Parsing                     | 44 |

|   | 3.2   | TCAM-based State Machine                            | 45 |

|   | 3.3   | An Alternative to TCAM-based State Machine          | 46 |

|   |       | 3.3.1 Functional Units                              | 48 |

|   |       | 3.3.2 Instruction Format                            |    |

|   |       | 3.3.3 Instruction Pipeline                          |    |

|   | 3.4   | Throughput Evaluation                               |    |

|   |       | 3.4.1 Parsing Individual Headers                    |    |

|   |       | 3.4.2 Parsing Header Stacks                         |    |

|   |       | 3.4.3 Enhancements for achieving higher throughputs |    |

|   | 3.5   | Implementation Results                              |    |

|   |       | 3.5.1 Discussion of results                         |    |

| 4 | An c  | on-the-fly Packet Pre-processor                     | 58 |

|   | 4.1   | Use Cases for Processing Packets on the Fly         | 58 |

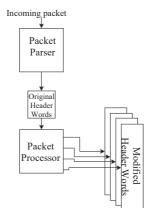

|   | 4.2   | Architecture                                        | 59 |

|   | 4.3   | Packet Preprocessor in Action                       | 60 |

|   |       | 4.3.1 Preprocessing of IPv4 Header                  |    |

|   |       | 4.3.2 Fragmentation of IPv4 Packets                 | 62 |

|   | 4.4   | Implementation Results                              | 67 |

|   |       | 4.4.1 Discussion of results                         | 67 |

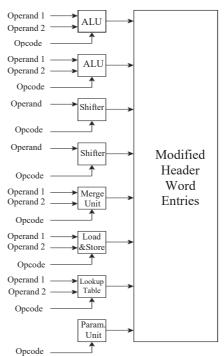

| 5 | Expl  | oring Crossbar Alternatives                         | 69 |

|   | 5.1   | Crossbars in RMT                                    |    |

|   | 5.2   | Crossbar alternatives                               |    |

|   | 5.4   | 5.2.1 Alternative Match Crossbar                    |    |

|   |       | 5.2.2 Alternative Action Crossbars                  |    |

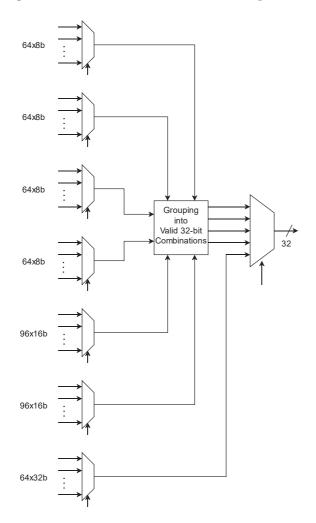

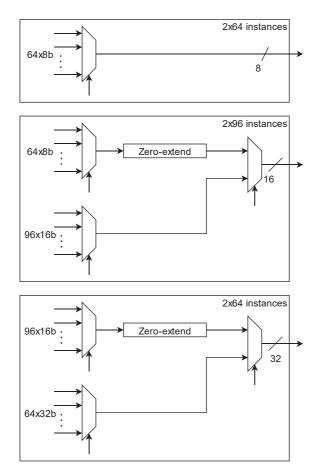

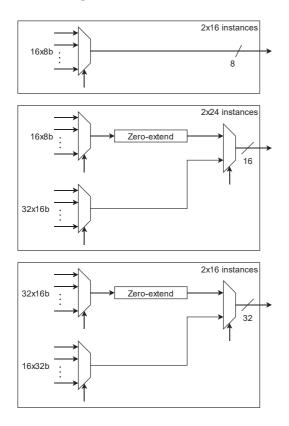

|   |       | 5.2.2.1 Zero-extending Smaller Units                | 72 |

|   |       | 5.2.2.2 Combining Smaller Units                     | 73 |

|   | 5.3   | Reducing Action Crossbars' Area                     | 73 |

|   | 5.4   | Implementation results                              | 75 |

|   |       | 5.4.1 Discussion of results                         | 76 |

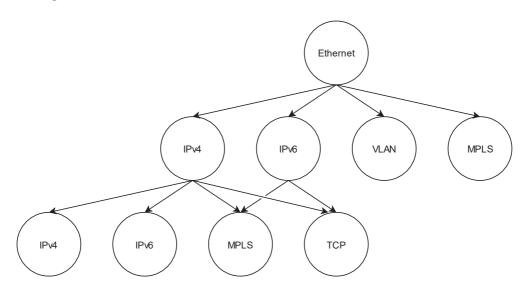

| 6 | Tow   | ards Terabit-level Packet Parsing                   |    |

|   | 6.1   | The Building Block for Terabit-level Packet Parsing |    |

|   | 6.2   | Using the Header Parsers to Build a Packet Parser   |    |

|   | 6.3   | Implementation Results                              |    |

|   | 0.0   | 6.3.1 Discussion of implementation results          |    |

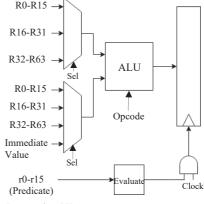

| 7 | A Fl  | exible Packet Processing Pipeline                   |    |

|   | 7.1   | Motivation                                          |    |

|   | / • ± | 1.10 4 . #4011                                      |    |

|      | 7.2       | A New   | Architecture                                     |     |

|------|-----------|---------|--------------------------------------------------|-----|

|      |           | 7.2.1   | Program Control                                  |     |

|      |           | 7.2.2   | Combining Tables                                 |     |

|      |           | 7.2.3   | Action Input Selectors                           |     |

|      |           | 7.2.4   | Pointer-based Header Field Referencing           |     |

|      | 7.3       | Implen  | nentation results                                |     |

|      |           | 7.3.1   | Comparison with other Match-Action Architectures |     |

|      |           | 7.3.2   |                                                  | 91  |

| 8    | Cone      | clusion |                                                  | 93  |

|      | 8.1       | Researc | ch Findings                                      | 93  |

|      | 8.2       |         | Problems and Future Directions                   |     |

| Refe | erences.  |         |                                                  | 97  |

| Publ | lications | 5       |                                                  | 105 |

# List of Figures

| Figure 1. | OSI Model                                                                                                      | .23 |

|-----------|----------------------------------------------------------------------------------------------------------------|-----|

| Figure 2. | High-level view of the internal components of a MAU (adapted from [26])                                        | .37 |

| Figure 3. | Match and Action dependencies in a Match-Action packet processing pipeline (adapted from [26])                 | .38 |

| Figure 4. | Parser used in RMT architecture (adapted from [26])                                                            | .45 |

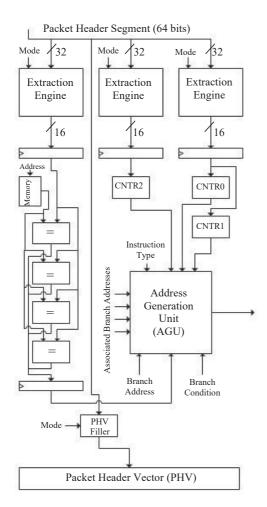

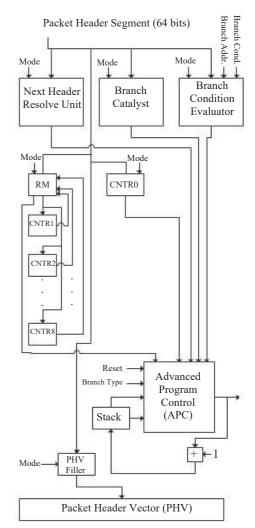

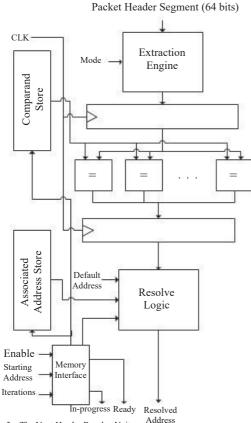

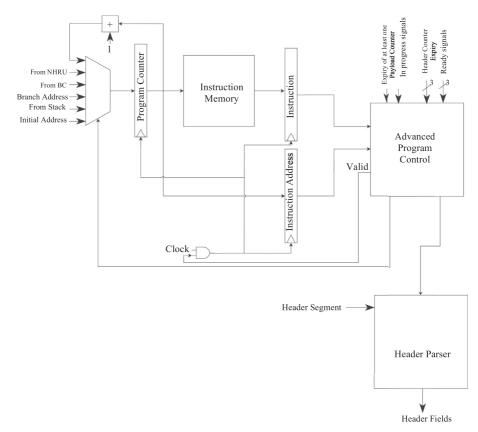

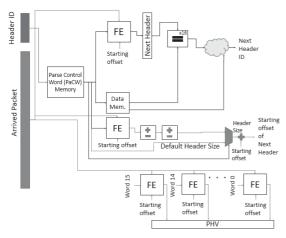

| Figure 5. | The proposed packet parsing processor                                                                          | .47 |

| Figure 6. | Throughput when parsing individual headers                                                                     | .50 |

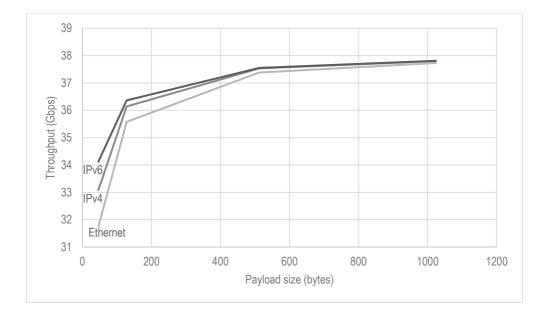

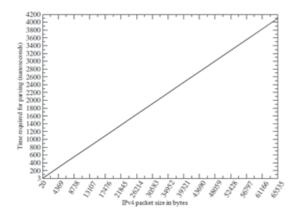

| Figure 7. | Resulting throughput when parsing Ethernet, IPv4, and IPv6 packets with 46-, 128-, 512-, and 1024-byte payload | .51 |

| Figure 8. | Two consecutive 32-bit headers                                                                                 | .53 |

| Figure 9. | Timing diagram for instruction pipeline when parsing two consecutive headers                                   | .54 |

|            | Timing diagram for instruction pipeline of the 8-threaded packet<br>arsing processor   |

|------------|----------------------------------------------------------------------------------------|

| Figure 11. | Procedure for fragmenting IPv4 packets                                                 |

| Figure 12. | IPv4 header containing option                                                          |

| Figure 13. | Alternative match crossbar71                                                           |

| Figure 14. | Action crossbar with zero-extension of smaller units72                                 |

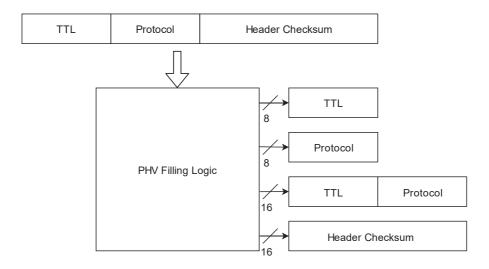

|            | Operation of PHV filling logic when writing the third word of IPv4<br>eader to PHV73   |

| Figure 16. | Action crossbar combining smaller units74                                              |

| Figure 17. | Lightweight action crossbar with zero-extension of smaller units75                     |

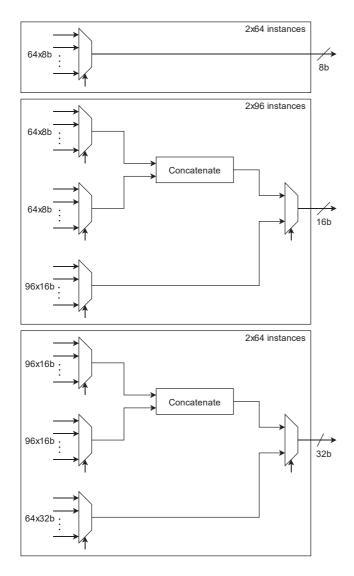

| Figure 18. | Internals of Header Parser [Pvi]                                                       |

| Figure 19. | Parse graph with three levels [P <sub>VI</sub> ]                                       |

| Figure 20. | Packet processing stage [P <sub>VI</sub> ]85                                           |

|            | A fraction of the pipeline reconfiguration architecture (adjusted om P <sub>VI</sub> ) |

## List of Tables

| Table 1. | Contributions made in this dissertation                       | 22 |

|----------|---------------------------------------------------------------|----|

| Table 2. | Summary and comparison of packet processing solutions         | 41 |

| Table 3. | Functional units of the new packet parser                     | 48 |

| Table 4. | Instruction fields                                            | 49 |

| Table 5. | Instruction pipeline stages                                   | 49 |

| Table 6. | Achieved throughput when parsing basic and full header stacks | 52 |

| Table | 7. Area and power dissipation values for components of an 80 Gbps packet parser                                    | 55 |

|-------|--------------------------------------------------------------------------------------------------------------------|----|

| Table | 8. Correspondence of packet parser components in RMT and the proposed architecture                                 | 56 |

| Table | 9. Register index of PHV entries                                                                                   | 60 |

| Table | 10. Integrity checking operations on IPv4 header fields                                                            | 60 |

| Table | 11. Instructions executed on the packet preprocessor during arrival of IPv4 header                                 | 61 |

| Table | 12. Instructions executed by the egress parser                                                                     | 65 |

| Table | <b>13.</b> Area and power dissipation of the components of a single packet preprocessor                            | 67 |

| Table | 14. Per stage area requirement of match crossbar variants                                                          | 76 |

| Table | 15. Per stage area requirement of action crossbar variants                                                         | 76 |

| Table | 16. Header parsing stages                                                                                          | 79 |

| Table | 17. Area and power dissipation of the components of a header parser (adjusted from $P_{VI}$ )                      | 81 |

| Table | 18. Area and power dissipation of components required for 6.4 Tbps packet parsing (adjusted from $P_{VI}$ )        |    |

| Table | 19. Components in each stage of the proposed packet processing pipeline                                            |    |

| Table | <b>20.</b> Area of the constituent components of a packet processing stage (adjusted from $P_{VI}$ )               | 90 |

| Table | <b>21.</b> Comparison of the area (mm <sup>2</sup> ) of RMT, dRMT and the proposed architecture [P <sub>VI</sub> ] | 91 |

| Table | 22. Total area for the three architectures under comparison $[P_{VI}]$                                             | 91 |

# ABBREVIATIONS

| A T T T |                                           |

|---------|-------------------------------------------|

| ALU     | Arithmetic and Logic Unit                 |

| AOI     | AND-OR-Invert                             |

| APCU    | Advanced Program Control Unit             |

| ASIC    | Application-specific Integrated Circuit   |

| BC      | Branch Catalyst                           |

| BE      | Best Effort                               |

| CRC     | Cyclic Redundancy Check                   |

| DPDK    | Data Plane Development Kit                |

| DPI     | Deep Packet Inspection                    |

| dRMT    | Disaggregated Reconfigurable Match Tables |

| DSCP    | Differentiated Services Code Point        |

| DSL     | Domain-specific Language                  |

| EPIC    | Explicitly Parallel Instruction Computing |

| FCS     | Frame Check Sequence                      |

| FD-SOI  | Fully Depleted Silicon on Insulator       |

| FE      | Field Extractor                           |

| ForCES  | Forwarding and Control Element Separation |

| FPGA    | Field-Programmable Gate Array             |

| GbE     | Gigabit Ethernet                          |

| Gbps    | Gigabit per second                        |

| GHz     | Giga Hertz                                |

| GPP     | General Purpose Processor                 |

| GPU     | Graphics Processing Unit                  |

| GRE     | Generic Routing Encapsulation             |

| HDL     | Hardware Description Language             |

| HLS     | High-level Synthesis                      |

| ICMP    | Internet Control Message Protocol         |

| IETF    | Internet Engineering Task Force           |

| IHL     | Internet Header Length                    |

| INT     | In-band Network Telemetry                 |

|         |                                           |

| T /T |                                           |

|------|-------------------------------------------|

| IoT  | Internet of Things                        |

| IP   | Internet Protocol                         |

| IPB  | Incoming Packets' Buffer                  |

| IPC  | Inter-packet Concurrency                  |

| ISA  | Instruction Set Architecture              |

| LoC  | Lines of Code                             |

| LPM  | Longest Prefix Match                      |

| MAC  | Medium Access Control                     |

| MAU  | Match-Action Unit                         |

| Mbps | Megabit per second                        |

| MPLS | Multiprotocol Label Switching             |

| Mpps | Million packets per second                |

| MTU  | Maximum Transmission Unit                 |

| NAT  | Network Address Translation               |

| NFV  | Network Function Virtualization           |

| NHRU | Next Header Resolve Unit                  |

| NIC  | Network Interface Card                    |

| NOP  | No Operation                              |

| NP   | Network Processor                         |

| OSI  | Open Systems Interconnection              |

| PaCW | Parse Control Word                        |

| PC   | Program Counter                           |

| PCIe | Peripheral Component Interconnect Express |

| PHV  | Packet Header Vector                      |

| PiCW | Pipeline Configuration Word               |

| PIEO | Push In Extract Out                       |

| PIFO | Push In First Out                         |

| PISA | Protocol Independent Switch Architecture  |

| PLUG | Pipelined Lookup Grid                     |

| POF  | Protocol-oblivious Forwarding             |

| PPS  | Packets Per Second                        |

| QoS  | Quality of Service                        |

| RAM  | Random Access Memory                      |

| RAN  | Radio Access Network                      |

| RMT  | Reconfigurable Match Tables               |

| RTL  | Register-transfer level                   |

| 1111 | negister-transfer iever                   |

| SDN               | Software Defined Networking                             |

|-------------------|---------------------------------------------------------|

| SMT               | Simultaneous Multithreading                             |

| SR                | Segment Routing                                         |

| SRAM              | Static Random-access Memory                             |

| SRH               | Segment Routing Header                                  |

| Tbps              | Terabit per second                                      |

| TCAM              | Ternary Content Addressable Memory                      |

| ТСР               | Transmission Control Protocol                           |

| TLP               | Thread-level Parallelism                                |

| TLV               | Type-Length-Value                                       |

| TM                | Traffic Management                                      |

| TPP               | Tiny Packet Program                                     |

| TTL               | Time to Live                                            |

| UADP              | Unified Access Data Plane                               |

| UDP               | User Datagram Protocol                                  |

| VDP               | Virtual Data Plane                                      |

| VHDL              | Very High-Speed Integrated Circuit Hardware Description |

|                   | Language                                                |

| VLAN              | Virtual Local Area Network                              |

| VLIW              | Very Long Instruction Word                              |

| VM                | Virtual Machine                                         |

| VNF               | Virtualized Network Function                            |

| WF <sup>2</sup> Q | Worst-case Fair Weighted Fair Queuing                   |

# **ORIGINAL PUBLICATIONS**

PI H. Zolfaghari, D. Rossi and J. Nurmi, "An Explicitly Parallel Architecture for Packet Parsing in Software Defined Networks," 2018 IEEE 29th International Conference on Applicationspecific Systems, Architectures and Processors (ASAP), Milan, 2018, pp. 1-4, doi: 10.1109/ASAP.2018.8445123.

- P<sub>II</sub> H. Zolfaghari, D. Rossi and J. Nurmi, "Low-latency Packet Parsing in Software Defined Networks," 2018 IEEE Nordic Circuits and Systems Conference (NORCAS): NORCHIP and International Symposium of System-on-Chip (SoC), Tallinn, 2018, pp. 1-6, doi: 10.1109/NORCHIP.2018.8573461.

- P<sub>III</sub> H. Zolfaghari, D. Rossi and J. Nurmi, "A Custom Processor for Protocol-Independent Packet Parsing," *Microprocessors and Microsystems*, vol. 72, 2020, pp. 1-11, doi: 10.1016/j.micpro.2019.102910.

- P<sub>IV</sub> H. Zolfaghari, D. Rossi and J. Nurmi, "An Explicitly Parallel Architecture for Packet Processing in Software Defined Networks," 2019 IEEE Nordic Circuits and Systems Conference (NORCAS): NORCHIP and International Symposium of System-on-Chip (SoC), Helsinki, Finland, 2019, pp. 1-7, doi: 10.1109/NORCHIP.2019.8906959.

- Pv

H. Zolfaghari, D. Rossi and J. Nurmi, "Reducing Crossbar Costs in the Match-Action Pipeline," 2019 IEEE 20th International Conference on High Performance Switching and Routing (HPSR), Xi'An, China, 2019, pp. 1-6, doi: 10.1109/HPSR.2019.8808105.

- P<sub>VI</sub> H. Zolfaghari, D. Rossi, W. Cerroni, H. Okuhara, C. Raffaelli and J. Nurmi, "Flexible Software-Defined Packet Processing Using Low-Area Hardware," in *IEEE Access*, vol. 8, pp. 98929-98945, 2020, doi: 10.1109/ACCESS.2020.2996660.

# 1 INTRODUCTION

Computer networks have been subject to fundamental changes during the last decade. As a result of these changes, programmability and the role of software has become an indispensable part of computer networks. Today, computer networks operate based on the Software Defined Networking (SDN) concept. The main idea in SDN is the separation of the control plane from the data plane of forwarding devices such as switches and routers. The control and data plane are the two main logical entities within forwarding devices. They perform routing and forwarding respectively. Routing is the process of determining the routes that packets must traverse for reaching their destination. The outcome of routing is filling in the corresponding database for routing. Forwarding is the process of finding the right interface to which an incoming packet must be directed. As a result, routing is a wider problem which involves all the nodes within a network whereas forwarding is a problem to be solved within a forwarding device only. This tight coupling of the control and data plane was the dominant logical architecture of the forwarding devices. By mid 2000s, a router deployed by service providers was based on 100 million lines of source code [1]. Each new device had to add functionality on top of those of its predecessors. As a result, switches and routers were internally comprised of enormous logic to support all the network protocols that a potential customer may use. Obviously, not all of the functionalities of a commercial forwarding device could be utilized in a given deployment scenario.

Another shortcoming of the tightly coupled model was that it was counterproductive to innovation in the area of computer networks. If the research body had proposals for new network protocols, they had to start writing proposals and submit them to Internet Engineering Task Force (IETF) for standardization which was a lengthy process. Even if the idea was turned into a standard, switch and router vendors had to implement the new functionality into the devices, thus adding a few more years. A prime example is that of VxLAN. The first switch chip that supported VxLAN appeared 3 years after VxLAN was standardized [2].

As a result of these shortcomings, the idea of separating the control and data plane took off. In order for this separation to work, an interface must be made between the control and data planes. One of the first efforts in development of such an interface was Forwarding and Control Element Separation (ForCES) [3]. A working group of the same name was formed at IETF and took the task of providing a standard interface between the control and data planes. Through this interface, the control plane installs forwarding rules in the data plane [4]. The next major step was Ethane [5]. In this architecture, flow management is handled by a centralized controller. Ethane-capable switches maintain a connection with the centralized controller that contains an overall view of the network. Ethane failed to convince commercial switch vendors for adoption.

A successful attempt was OpenFlow. First introduced in [6], it shared the main idea with Ethane. However, it was far more advanced. It provides a logical architecture for switches in which there are a number of tables containing forwarding rules. A match on a table results in the execution of actions associated with the matching entry. OpenFlow has been a commercial success and OpenFlow-based switches are available on the market. Although OpenFlow performs the task of interfacing between the control and data plane very well, it is not flexible because it is dependent on a number of protocols.

For the inception of truly SDN-based networks, further contributions were needed to support protocol-independent processing of packets. This required working on the data plane. The key to achieving this goal is support of programmability in the data plane. As a result of the clear need for the programmable data plane, efforts were made in both hardware and software.

On the programming language level, P4 was introduced in [7]. It is a targetindependent language for describing packet processing behaviour in the data plane. It abstracts the underlying hardware as a series of Match and Action stages. Moving down to the Instruction Set Architecture (ISA) level, the term Protocol-oblivious Forwarding (POF) was first mentioned in [8]. It was continued in [9] and [10]. POF is a generic ISA for the processing of network packets. In a similar approach, NetASM was proposed as an intermediate representation in [11]. It is in the hardware-software interface of packet processing. On the hardware level, the Reconfigurable Match Tables (RMT) architecture appeared in 2013. It is a fully programmable protocol-independent architecture that sustains 640 Gigabits per second (Gbps) throughput. Clearly, RMT was not the first hardware architecture for packet processing, as Field-Programmable Gate Arrays (FPGAs) and Network Processors existed prior to RMT, but the innovation of RMT was maintaining programmability and performance.

Another development was the shift from middleboxes to commodity hardware for implementing network functions. Middleboxes are devices that perform nonforwarding functions. These devices were becoming costly, hard to manage and they increased the failure points within the network [12]. Network Function Virtualization (NFV) is the proposed solution for solving these issues. A network function, such as Network Address Translation (NAT) can be instantiated on a server. This class of network functions are referred to as Virtualized Network Functions (VNFs) [13]. The need for programmability manifested itself for implementing a wide range of network functions. However, packet processing on the general-purpose processor of a server has its own problems. The time between arrival of a packet at network interface card until being processed by the processor results in high latency. Moreover, even high-end processors can be overloaded with packets [14]. In order to solve these issues, SmartNICs appeared as a new class of Network Interface Cards (NICs) with enhanced functionality, performance and flexibility for offloading network functions and providing better performance [15]. SmartNICs come in a wide range of platforms such as Application-specific Integrated Circuit (ASIC), embedded processor, and FPGA for varying levels of flexibility and performance [16].

## 1.1 Objectives and scope

In this dissertation, the focus is on architectural aspects of Match-Action packet processing. The implementation target is ASIC. Specifically, the focus is on the problem of programmable packet parsing and packet processing. Issues such as packet scheduling and switch fabric are not within the scope of this dissertation. In the contributions made in this thesis, the key objectives are programmability, low hardware complexity and sustaining line rate throughput of 640 Gbps and above.

## 1.2 Research questions

There are research questions common to both packet parsing and packet processing as well as research questions specific to each of the two problems. One of the most recurring questions common to both packet parsing and packet processing is the question of which architecture is better, pipelined or run-to-completion. In the case of run-to-completion, is it better to use conditional execution or branches in order to support the high-throughput nature of packet processing? Since increasing the frequency is not possible beyond a point, what architectural techniques are beneficial for enhancing performance?

#### 1.2.1 Research questions specific to packet parser

Regarding the packet parser, the author investigates how programmability is achieved without expensive lookup entities such as Ternary Content Addressable Memories (TCAMs). Ways of enhancing the performance of the parser without increasing the operating frequency are also explored. With increase in line rates and complexity of network protocols, the question is, whether the parser is supposed to perform parsing only? Is there any performance benefit in processing the packets as they arrive?

### 1.2.2 Research questions specific to the packet processing subsystem

As for the packet processing subsystem, the first step in designing architectures with reduced area is to find out the major contributors to area. Since efficient use of lookup resources is a key goal, the author investigates and provides solution for program control mechanisms other than matching while still providing wire-speed performance. Support of advanced workloads is also a design goal. Simultaneous support of diverse set of protocols requires deep instruction memories which in turn cause noticeable increase in total area. The question is, how is it possible to support as many actions as possible while keeping the area overhead of instruction memories low.

Another research question relates to crossbars used for generating search keys, selecting operands to actions, and combining tables. Large crossbars occupy large area and make physical design challenging. Is it possible to use smaller crossbars in order to minimize the area while still maintaining programmability and performance? Is it feasible to combine as many match tables as required without large multiplexers? Minimizing recirculation is another research item addressed in this dissertation. Recirculation of packets increases packet processing latency and reduces throughput. What can be done in order to minimize the need for recirculating packets? Another question is whether the field referencing mechanisms in the latest programmable architectures are sufficient for supporting state of the art network protocols?

### 1.3 Research significance

Research on programmable data plane is mainly done in research and development departments of leading switch and router vendors. The amount of academic research on this topic is very small. Consequently, the outcome of research is not available to the public. The research based on which this dissertation is written provides substantial insight into the state-of-the-art packet processing hardware. Programmable architectures for protocol-independent packet processing are still in their infancy. Many SDN-related standards and contributions such as [7] and [17] describe the switch as a logical entity. The designer is free in making design choices as long as the desired functionality is achieved. The requirement analysis and architectural exploration in this thesis paves the way for further contributions and innovations for high-performance programmable packet processing hardware.

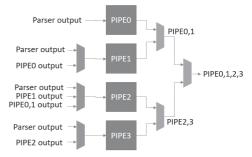

Performance in digital systems can be enhanced by increasing the operating frequency or replicating the functional units for providing parallelism. Upscaling the operating frequency is subject to physical limits. At 6.4 Terabits per Second (Tbps), there are 10 billion minimum-sized packets per second each of which requiring multiple cycles of processing. This means that even a processor with frequency of 10 Gigahertz (GHz) will not be able to keep pace with the rate of packet arrival. There are physical barriers that hinder scaling the frequency of digital systems beyond 5 GHz. Even within the range of feasible operating frequency values, lower frequencies are preferred to avoid excessive power and heat dissipation. The only solution for terabit-level packet processing is replication of functional units. The significance of low-area design is that the savings in area can be exploited for providing more on-chip match tables and/or more computational units without violating area constraints. Integrating more match tables increases the lookup capacity. Instantiating more functional units enhances functionality and/or throughput. An entire packet processing pipeline can be replicated so that the arriving packets are divided into the available pipelines.

The significance of supporting novel protocols by software means is obvious. Due to the time-consuming and costly nature of designing, implementing and verifying new hardware, it is best to have hardware that can be programmed for as many different purposes as possible.

# 1.4 Contributions and results

| Table 1.         Contributions made in this dissertation                                                          |                                                                                                  |                         |  |  |

|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------------------------|--|--|

| Contribution                                                                                                      | Innovation                                                                                       | Original<br>Publication |  |  |

| A low-area programmable packet parser                                                                             | Use of program control instead of TCAM                                                           | Pı, P∥, P∥I             |  |  |

| Packet pre-processor                                                                                              | Enhancement of packet parser with packet processing functionality, processing packets on the fly | Piv                     |  |  |

| Alternative crossbar architectures                                                                                | Use of smaller crossbars while maintaining<br>functionality                                      | Pv                      |  |  |

| A pipelined parser for 6.4 Tbps parsing                                                                           | Tenfold increase in throughput                                                                   | P <sub>VI</sub>         |  |  |

| A flexible packet processing pipeline<br>with advanced addressing mode and<br>more efficient use of lookup tables | Custom action depth, advanced field referencing, unlimited table combination                     | Pvi                     |  |  |

Table 1 outlines the contributions made in this dissertation.

# 1.5 Author's contribution

The author of this thesis has been the first author of all papers included in this dissertation. The contribution includes coming up with the research idea, software implementation of selected network protocols, architecting the design, Register-Transfer Level (RTL) implementation, verification, and programming the implemented architecture. In addition, for  $P_{VI}$ , the ASIC synthesis has also been done by the author of this dissertation.

# 1.6 Thesis outline

This thesis is organized as follows. Chapter 2 provides an in-depth overview of packet processing solutions and justifies the need for custom hardware architectures. Chapter 3 contains the first contribution, which is a fully programmable packet parser. Chapter 4 provides enhancements to the packet parser for packet processing. Chapter 5 compares crossbar alternatives for the Match-Action pipeline. Chapter 6 provides an alternative packet parser for terabit-level packet parsing. Finally, chapter 7 provides a new packet processing pipeline with enhanced level of flexibility. Finally, chapter 8 concludes the work.

# 2 PACKET PROCESSING

Computer networks are the underlying means for communication of computer systems including servers, desktop computers, laptops, tablets, smart phones, and Internet of Things (IoT) devices. Internet is a prime example of a gigantic computer network. In computer networks, data traverses in the form of network packets. In order to simplify the design, operation, management, and troubleshooting of computer networks, networks are built of logical entities, each belonging to a layer. A reference model for this layered approach is the Open Systems Interconnection (OSI) model elaborated in [18]. Figure 1 illustrates the OSI model.

| Application layer  |

|--------------------|

| Presentation layer |

| Session layer      |

| Transport layer    |

| Network layer      |

| Data link layer    |

| Physical layer     |

Figure 1. OSI Model

The lowest layer is the physical layer. It deals with electrical, optical, or wireless signals. As such, it has no knowledge of the contents of these signals. An instance of a system operating at the physical layer can be found in [19]. The next layer is the data link layer. It deals with accessing the transmission medium and addressing of nodes within a single network. The next layer is the network layer. This layer solves the problem of communication between independent networks which means how a packet destined to a node in another network must reach the target network. The next layer is the transmission of variable-length data segments between two logical end points. The upper layers deal with more application-oriented matters. It is thanks to this layered model that when sending an email, it is not of significance whether the recipient of the email is using the Internet on a wired or wireless connection. Neither is it necessary to know what operating

system the recipient has. The message is created at the application layer and submitted to the lower layers in turn. Each layer is concerned only with its own specific issues. At the recipient's side, the flow of the corresponding packet(s) starts at the physical layer and moves upwards to the application layer.

The layered approach allows for interoperability. As far as a given implementation of a layer's functionality is fulfilled and the data is received and produced in the same format, different implementations can be swapped. Associated with each layer are a set of protocols each of which is a specific implementation of the tasks associated with the layer in question. For instance, the most dominant layer-2 protocol is Ethernet. The most dominant layer-3 protocol is the Internet Protocol (IP). Currently, IPv4 and IPv6 are being used on the Internet. At the transport layer, Transmission Control Protocol (TCP) and User Datagram Protocol (UDP) are in common use. Each protocol has a header to wrap around the data it receives from the next higher layer protocol's data.

Packet processing refers to the operations performed on network packets. These operations are performed on the header(s) of network packets. It is also possible for the payload of the packet to undergo processing. For instance, in the case of packet fragmentation, the original packet is broken into multiple smaller packets each of which carries a fraction of the original payload. The payload may also be subject to encryption. Packet processing operations are executed in network switches, routers, Network Interface Cards (NIC), and in general-purpose processor as instructed by the operating system. This chapter provides an overview of packet processing operations and the packet processing solutions.

### 2.1 Packet processing operations

Packet processing operations can be classified based on different criteria. One such criterion is the direction of the packet. Processing on an incoming packet is called ingress processing while processing on an outgoing packet is called egress processing. Another classification is based on packet processing operations of which the most basic one is forwarding. Forwarding was discussed in the introductory section of chapter 1. Packet processing operations can be listed as follows:

-Parsing

- -Integrity checking

- -Header field manipulation

- -Tunnelling

-State modification -Lookup -Classification -Fragmentation and reassembly -Traffic management

Each of them will be discussed in more detail.

### 2.1.1 Parsing

Parsing is the first step in processing of packets. In this chapter it is categorized as one of the packet processing operations. In the chapters to follow, parser is the prelude to packet processing. During parsing, the headers present in a packet are recognized and consequently, the kind of processing required for the packet is determined. According to [20], parsing can be done as the packets arrive or after the packet has been received in its entirety. Parsers operating based on these two models are referred to as streaming and non-streaming parsers respectively. Parsing must not be confused with Deep Packet Inspection (DPI) in which the payload of the packet is subject to inspection. Packet parser deals only with the headers.

### 2.1.2 Integrity checking

The contents of a packet might become corrupted during transmission as a result of noise or other defects. The purpose of integrity checking is to detect errors within the header. Ethernet frames contain a Frame Check Sequence (FCS) field that carries an error detection code. It is calculated using 32-bit Cyclic Redundancy Check (CRC). In IPv4, checksum of the header is calculated and then compared with the value contained in the Header Checksum field. After each header field manipulation, the checksum is recalculated and written to the Header Checksum field. Header checksum field using one's complement addition [21].

#### 2.1.3 Header field manipulation

Manipulation of header fields is the most obvious form of packet processing. One of the examples of header field manipulation is decrementing the value of Time-to-

Live (TTL) and Hop Limit fields within the IPv4 and IPv6 header respectively. Updating the value of checksum in IPv4 is another instance of header field manipulation.

### 2.1.4 Tunnelling

Tunnelling refers to the process of encapsulating a packet into another packet. It basically means adding a new header in front of the current header(s). One of the use cases for tunnelling is when a network cannot carry packets of a specific type. In this case, the packets have to be encapsulated in packets that can be transported by the network in question. For instance, if IPv6 packets need to traverse a network supporting only IPv4, IPv6 packets must be encapsulated into IPv4 as described in [22]. At the end of the so-called tunnel, the wrapping is removed.

### 2.1.5 State modification

Implementing the functionality of certain protocols requires maintaining state. A notable example is Transmission Control Protocol (TCP). Apart from such protocols, it is possible to associate some form of state with packets belonging to stateless protocols. For instance, a router can be configured to keep track of the payload length of IPv6 packets whose next header is UDP. With each IPv6 packet that fulfils this criterion, the router retrieves the state and adds the payload length of the packet to it. State modification may be used just for statistical or billing purposes and hence not affect the fate of packets. Alternatively, the value of the state may be used as basis for modifying header fields or even dropping packets for which a threshold value has been reached.

#### 2.1.6 Lookup

Lookups are one of the most widely used operations in packet processing. The nature of packet processing requires that some fields be selected as the search key to be used for looking up a table and retrieving the associated data. For instance, when an Ethernet frame arrives in a switch, the destination address is used as a search key to look up into the forwarding table to find out the port to which the frame must be forwarded. When an Internet Control Message Protocol version 6 (ICMPv6) [23] is

encountered, the Type and Code fields must be used to obtain the correct instruction(s) for processing the ICMP message in question. Therefore, lookups are required both for retrieving data items and for program flow. Lookup can be regarded as a sub-operation of packet classification, which will be discussed shortly.

#### 2.1.6.1 Exact Matching

Exact matching is a kind of matching in which an exact match for the search key in question is being searched. This kind of matching is encountered in forwarding of Ethernet frames. When presenting the Destination Media Access Control (MAC) address to the lookup table, an exact match is looked for. If a memory is used to host all possible MAC addresses, 2<sup>48</sup> entries are required because MAC addresses are 48 bits wide. This amount of memory is gigantic. Instead of this naïve approach, hashing is used because a switch will deal with a far more limited range of MAC addresses rather than the whole address space. The major issue brought upon by hashing is that of collisions. It refers to the problem of distinct search keys being mapped to the same entry in the hash table. One of the most widely used solutions to this issue is cuckoo hashing [24].

#### 2.1.6.2 Ternary Matching

Ternary matching allows a third state in addition to the default zero and one states to be stored in the match table. One use case of ternary matching is Longest Prefix Matching (LPM) in which the stored entries contain a non-ternary part called prefix followed by the ternary part. In LPM, matching entry with the longest prefix is searched. TCAMs can provide the means for ternary matching because they can store don't care bits as well. TCAMs have single-cycle latency [25] at the cost of area and power consumption. The area of a TCAM block is 6-7 times that of an Static Random Access Memory (SRAM) with equal size [26]. A TCAM consumes as much as 15 watts [27].

#### 2.1.7 Classification

The purpose of classification is grouping packets into classes. Packets in a given class receive similar processing. The basis for classification is matching. Therefore,

classification is the outcome of an earlier match operation. The simplest form of classification is packet forwarding in which the basis for matching, and hence classification, is the destination address. All the packets having the same destination will be steered to the same port. More advanced packet classification involves using the value of multiple fields as the basis for matching. For instance, the *5-tuple* refers to source IP address, destination IP address, protocol/next header, source port and destination port fields from IPv4/IPv6 and TCP/UDP. It is used for identifying a transport-layer session. Use of 5-tuple as the basis for classification has use cases in NAT [28] and traffic management purposes [29].

#### 2.1.8 Fragmentation and reassembly

If the size of a packet is larger than the Maximum Transmission Unit (MTU) of the network connected to the outgoing port, the packet has to be fragmented. This means that the payload of the packet must be broken into fragments and each sent as an independent packet. In the header of each fragment, there should be sufficient information to allow the reassembly of the fragments in the receiving host. In IPv4, the routers fragment a packet if its size is above the MTU of the path it must be forwarded to. In IPv6, fragmentation is done only by the source node. The minimum supported MTU as required by IPv6 is 1280 bytes [30].

Use of fragmentation and reassembly of packets is not limited to IPv4 and IPv6. Rather, it is sometimes done inside a network switch or router. Variable-length packets are fragmented into smaller fixed-size units called *cells* for better management of resources such as the internal switching fabric and packet buffers. The packet is then reassembled before being sent out through an egress port.

#### 2.1.9 Traffic Management

Traffic Management (TM) deals with the problem of differentiating treatment of certain packets. Not all packet processing systems implement TM. In the absence of TM, all packets are treated equally and forwarded in *Best Effort* (BE) mode. Traffic management is a collective term for a wide range of operations such as marking, traffic policing, priority-based packet scheduling and traffic shaping. For each of these operations, there are various algorithms. The purpose of TM is providing Quality of Service (QoS) and/or preventing congestion. A notable instance of traffic management mechanism for IP traffic is Differentiated Services (DiffServ) [31].

### 2.2 Software-based packet processing solutions

In this section packet processing solutions employing software are discussed. Software switches and routers provide switching and routing functionality on general-purpose computers by means of software. The benefit of software routers is their flexibility and use of commodity hardware. In addition to general-purpose programming languages such as C, custom programming languages for packet processing have emerged to describe packet processing functionality. The operating system kernel performs packet processing services to applications sending and receiving packets. For enhanced performance, the operating system kernel can be bypassed. This concept is known as user-space packet processing. Each of the aforementioned subjects are elaborated in the subsections that follow.

#### 2.2.1 Software Routers

Click [32] is a flexible and configurable software router. Its original implementation achieves forwarding rate of slightly over 170 Megabits per second (Mbps). At the time Click was presented, processors were running at sub 1.0 Giga Hertz (GHz) frequencies. With increase in processor speeds software routers achieved better performance. RouteBricks [33], builds a software router made of four servers connected through a mesh topology. It achieves throughput of 35 Gbps.

CuckooSwitch [34], is a software-based Ethernet switch. It has two underlying components: Intel Data Plane Development Kit (DPDK) and a scheme for ensuring consistency in spite of concurrent access of a writer and multiple readers. It achieves throughput of 92.22 Gbps.

Another development that pushed research for software routers was the rise of virtual machines (VM). Software routers steer packets towards or out of virtual machines. Open vSwitch [35] is a virtual switch that achieves 18.8 Gbps throughput when used as an Ethernet switch. With increase in the number of protocols and correspondingly increase in the complexity of software routers, the need to make them programmable became ever evident. PISCES [36] is a programmable software switch. It achieves throughput of slightly over 10 Gbps in a benchmark in which minimum-sized Ethernet frames arrive.

### 2.2.2 Programming Languages

As a general-purpose programming language, C can be used for implementing packet processing functionality. Linux kernel is implemented in C and contains components for processing of packets. C language does not natively support protocol-specific features such as variable-length fields and encapsulation. Apart from the limitations of C, the protocol format may be incompatible with the processing width and byte ordering of the computer that executes packet processing code written in a general-purpose programming language. Consequently, the applications need to perform the required adjustments before using the value of a header field. A Domain-specific Language (DSL) for describing the format of packets overcomes these shortcomings. PacketTypes [37] is a language specialized for packet specification. In this language, the layout of fields within a packet as well as constraints on their values can be defined as a type. It has native support for encapsulation, variable-length fields, and optional fields. The principle operation in PacketTypes is checking their membership of packets in a type. PacketTypes has been used for network monitoring, packet classification, and formal declaration of protocol formats.

P4 is a declarative domain-specific language for instructing the data plane on how the packets must be processed. P4 was first introduced in [7]. Many commercial switches today are P4-programmable. Currently, P4 has two releases, P4<sub>14</sub> and P4<sub>16</sub> that are described in detail in [38] and [39] respectively. P4 is based on an abstraction of the data plane in which the parser is followed by a Match-Action pipeline. Using P4 language, the headers can be described. The description of headers contains an ordered list of header fields and their size. The parse graph can also be described. Tables are described in terms of their size, the search key, the kind of lookup and the action that must be executed upon match. Associated with each packet is a set of metadata items called intrinsic metadata. It contains information such as the port on which the packet has arrived, the port to which it must be forwarded, whether the packet is a clone or recirculated packet, and other relevant information. P4 contains a number of primitive actions such as arithmetic and logical operations, header addition and removal, packet dropping, etc. More complex actions can be defined as a combination of primitive actions.

Domino [40] is a domain-specific imperative language with syntax similar to C. It is used to express data plane algorithms. The central concept in Domino is packet transaction which is an atomically executed code block separated from other blocks. Packet transactions allow the programmer to focus on the operations that must be performed on a packet, rather than concurrency issue brought upon by other packets. In other words, packet transactions provide the illusion that a packet arrived at a switch is processed to completion and then processing of the next packet starts. When compiled for execution, packet transactions run at line rate in a guaranteed manner. It achieves this by imposing certain constraints. For instance, it does not allow loops nor unstructured control flow statements such as goto statements. When dealing with an array element within a transaction, only one element is allowed. What triggers the execution of a packet transaction is a guard that is a predicate. For instance, a guard could be defined as a header field having a specific value. Once this predicate evaluates to true, the packet transaction associated with it is executed. Domino has been evaluated in terms of its expressiveness when used to implement various data plane algorithms for traffic engineering, congestion control, active queue management, network security and measurement. The authors have compared the number of lines of code (LoC) for the data plane algorithms written in Domino and P4. The LoC value for Domino is considerably smaller than those of P4.

In chapter 1, ISA-level contributions such as POF and NetASM were mentioned. Describing desired packet processing functionality at ISA-level is cumbersome. However, this does not undermine the significance of ISA. A widely adopted ISA is of benefit to compiler development and hardware design. The compiler converts a given higher-level language to ISA-level representation. Hardware architects provide microarchitecture required for hardware implementation of the ISA in question.

#### 2.2.3 User-space Packet Processing

Implementation of protocol stacks in operating systems has improved over the years. However, at high rates of packet arrival, these implementations lag behind. The survey in [41] has gathered the shortcomings of packet processing in OS from a number of research works. One of the notable shortcomings is the high cost of context switch to kernel and back to user space. Every time an application needs to receive a packet, it must make an OS system call. After the OS has taken control, another context switch is made back to the application. According to [42], as many as 1000 CPU cycles are consumed per packet in these context switches. The solution to this inefficiency is user-space packet processing in which the kernel is bypassed. This bypassing enables the packet buffers to be directly accessible from the user space. The other solutions required for mitigating inefficiencies of packet processing by kernel are sharing the packet buffer between user space and NIC, processing packets in batches and supporting the multi-queue feature of modern NICs for load balancing [43].

Data Plane Development Kit (DPDK) is an open source set of libraries for fast packet processing in the user space. The purpose of DPDK is sending and receiving packets with minimum possible number of cycles. According to [44], the throughput of layer-3 forwarding of 64-byte packets with LPM as default lookup method using Intel NICs ranges from 29.76 to 74.4 Million packets per second (Mpps). For some packet processing functions, the throughput is hundreds of Mpps [45]. As of now, DPDK supports the dominant CPU architectures and NICs from different vendors. Instead of the interrupt-driven approach taken by the operating system's kernel, it uses polling because when the rate of packet arrival is high, interrupt-driven approach is inefficient. The other similar frameworks are netmap [46] and PFQ [47].

# 2.3 Hybrid packet processing solutions

In addition to the software-based solutions, there are solutions implemented on FPGAs. FPGAs are devices with a pool of hardware resources that can be interconnected in order to achieve the desired hardware architecture. The desired hardware architecture is provided in the form of Hardware Description Languages (HDLs) such as Verilog and Very High-Speed Integrated Circuit Hardware Description Language (VHDL). In recent years, it has become possible to describe the desired functionality in higher-level languages such as C/C++. The concept of using higher-level languages for obtaining the corresponding functionality in hardware is called High-level Synthesis (HLS). So, FPGAs are hardware solutions but since they allow reconfigurability, they have flexibility characteristics similar to software. For this reason, it is considered as a hybrid solution.

In 2010s, Graphics Processing Units (GPUs), received attention for use as the platform for execution of packet processing. GPUs are specialized processors for graphical operations such as high-performance rendering of images. The most notable architectural characteristic of GPUs is large pool of parallel resources for thread-level parallelism (TLP).

#### 2.3.1 Solutions based on FPGAs

NetFPGA is an open-source FPGA-based platform for implementing network processing functionality. There are 1 Gbps, 10 Gbps and 100 Gbps NetFPGA variants [48]. NetFPGA SUME [49] is the latest in the line-up of NetFPGA devices. It is a Peripheral Component Interconnect Express (PCIe) board containing four 10 Gbps ports. The board hosts XILINX Virtex-7 690T device for custom logic realization. With more than 690K logic cells, 52,920 kb block Random Access Memory (RAM), and high-speed transceivers, it can be programmed for standalone, peripheral, and switch use cases.

SwitchBlade [50] is a platform for rapid deployment of custom protocols. It is designed with the aim of providing the right balance between flexibility of software and performance offered by hardware. It is implemented on NetFPGA board. In SwitchBlade, workloads pertaining to multiple protocols can run in parallel. Each corresponding data plane is called a Virtual Data Plane (VDP). Functional units in SwitchBlade are organized in pipelined fashion. The main operations in the pipeline are preprocessing in which fields for matching are selected, hashing, matching and post-processing. Both LPM and exact matching are supported by SwitchBlade. In the experimentation performed by the authors, it has been used for IPv4 and IPv6 forwarding, path slicing and OpenFlow switch. The forwarding rate of SwitchBlade is  $1.5 \times 10^6$  packets per second (pps) for 64-byte packets. This translates to 732.42 Mbps throughput.

As mentioned earlier, the functionality of FPGAs is dependent on HDLs or languages such as C/C++. The fact is that many network innovators are not familiar with HDLs. Furthermore, even C/C++ languages are at a low abstraction layer for describing network processing functionality. For this reason, many FPGA-based platforms come with a toolchain that takes the desired functionality in a language close to networking. In [51], a complete solution is provided in which the functionality is described in high-level language called PX. The PX-specific compiler converts the code into the equivalent HDL and then to the bitcodes required for configuring the underlying FPGA platform. It achieves 100 Gbps throughput when dealing with minimum-sized Ethernet frames.

In a similar approach, [52] accelerates network functions for commodity servers. It is programmed in a language called ClickNP. When configured as a firewall, it can process 64 million packets per second (Mpps) with each packet being 64 bytes. Another work in which a complete solution is provided is P4FPGA [53]. It is P4 compiler with a custom backend for generating HDL code to be used as the input

to synthesis and place and route on FPGA. P4FPGA has been evaluated in terms of its capability to support different data plane applications. Match-Action processing for L2/L3 forwarding on P4FPGA takes 124 ns for packets whose size is up to 1024 bytes.

FPGAs have been extensively used for packet parsing. In these solutions, the header sequence is described in HDL or a higher abstraction layer. In [54], a domain-specific language called PP is used for describing headers. Based on this description, the FPGA is configured for providing the desired implementation. For a stack containing Virtual Local Area Network (VLAN), IPv4/IPv6 and TCP/UDP, it achieves throughput values of 302 and 578 Gbps using 1024- and 2048-bit datapaths respectively. The latency figures are above 300 ns. However, it is stated that these figures are raw throughput values obtained by multiplying datapath width and operating frequency. The effect of short packets and quantization over wide word must be taken into account. As a result, the actual packet parsing throughput is less than the provided values.

Since P4 language also describes headers, some solutions use it as the input to the tool chain that generates the HDL. This approach is used in [55] and [56] and the achieved throughput is 100 Gbps. The highest achieved parsing throughput using FPGAs is in [57] in which up to 1 Tbps throughput is achieved.

#### 2.3.2 Solutions based on GPUs

PacketShader [58] uses the architectural features of GPUs to enhance the performance of software routers. In addition, I/O optimizations have been provided for implementing batch processing to eliminate the overhead caused by memory management on a per-packet basis. In IPv4 forwarding, PacketShader achieves throughput of almost 40 Gbps. For IPv6 forwarding, the throughput value is 38.2 Gbps.

The work in [59] considers both strong and weak points of GPUs. On the strong side, GPUs hide memory latency incurred by lookups by switching to another thread. General-Purpose Processors (GPPs) also support multithreading but they support 2 or 4 threads. In GPUs, tens of threads are supported and the switching between them occurs very fast. On the weak side, the high memory access latency of GPUs is undesirable for packet processing. In addition, the memory bandwidth degrades in packet processing applications because random memory locations are accessed. The main argument of their work is that performance brought by GPUs is not due

to their computational capacity, rather due to efficient context switching in hardware. In order to emulate such efficient context switching in CPUs, a technique called G-Opt is developed. It is based on group prefetching and fast context switching. It reorders code for concurrent memory access. This access pattern allows software pipelining. Use of G-Opt on GPPs yields throughput similar to GPUs. For instance, using 4 cores, G-Opt achieves throughput of close to 50 Mpps while with GPU this figure is 40 Mpps.

APUNet [60] evaluates whether fast context switching in GPP can solve a wide range of network applications. The findings confirm that besides the fast context switching, the computational capacity of GPUs is indeed a key contributor to performance. However, a barrier to achieving the full performance gain of GPUs in packet processing is the transfer bottleneck of PCIe. Typical PCIe bandwidth is considerably smaller than that of GPU memory. In response, the authors suggest use of integrated GPU in which CPU and GPU share memory. As a result of this unified memory space, the data transfer overhead is eliminated.

# 2.4 ASIC-based packet processing solutions

So far, the relevant software and hybrid solutions have been reviewed. Software and virtual routers achieve throughputs in the range of tens of Gbps. FPGA-based solutions provide throughputs in the range of hundreds of Gbps. But as discussed earlier, FPGA-based solutions are based on a high- or low-level description of the workload. As a result of this, FPGA solutions contain hardware specific to a known set of protocols. This is in contrast with the protocol-independence principle of SDN. Solutions compliant with SDN do not contain any protocol-specific state. By removing this dependence on specific protocols from FPGAs, their performance will degrade. In addition, TCAMs are required in high-throughput environments because of their parallel search capability. In FPGAs, it is possible to achieve TCAM functionality by emulation. However, this is inefficient in terms of resource usage. Another issue with FPGAs is that they run at considerably lower frequencies when compared with ASICs. In Terabit-scale packet processing, the minimum required operating frequency is 1.0 GHz. Because of their low operating frequency, FPGAs rely on ultrawide datapaths. Multiplying datapath width by operating frequency gives a raw throughput value which is not achievable for small packets. This issue is discussed in [54]. The latency figures for parsing alone is in the range of hundreds of ns while commercial routers and switches perform entire processing in such a time

window [61]. This is confirmed by the line-up of high-end commercial products. As will be seen in sections 2.4.1 and 2.4.2, hardly any such device is built upon FPGAs. In this segment, the ASICs have no rivals. This is the motivation for using ASIC-based solutions.

### 2.4.1 Network Processors

Network Processors (NPs) gained popularity in early to mid-2000s. They were basically processors with functional units optimized for processing packets. The focus, at that point, was not protocol-independence. Instead they contained the logic for implementing and accelerating the most commonly used network protocols. In [62], some of the shortcomings of NPs are presented. The main challenge in reaching high performance with NPs is the large gap between the processor and the memory. As opposed to GPPs, use of caching is of little help because locality of reference is missing in network processing. Instead, NPs mitigated this issue by using multithreading. When an NP core requests an item from memory, it switches to another thread.

One of the most notable network processors was the Intel IXP2800 and IXP2850, the latter of which has integrated cryptographic units. The store-and-forward packet processing is performed by 16 32-bit micro-engines, each of which can run 8 threads. The maximum operating frequency is 1.4 GHz. Each micro-engine has an 8K instruction store. The micro-engines cooperate with each other for solving packet processing problems. The complete datasheet is available in [63].

Today network processors are not as widely used as early 2000s. However, there are a few of them in use. Cisco has a 400 Gbps multicore network processor which is comprised of 672 general-purpose processors [64]. Each of the processors has an 8-stage pipeline. The instruction set contains network-specific instructions. It can be programmed in C and assembly language. Another notable network processor is Nokia NP4. It is a 3 Tbps network processor that supports deep packet lookups and real-time telemetry [65].

### 2.4.2 Programmable Switch Chips

In the post-NP era, Pipelined Lookup Grid (PLUG) [66] was one of the first architectures providing flexibility with the aim of supporting new protocols. It consists of a grid of tiles that can be combined for implementing different protocols.

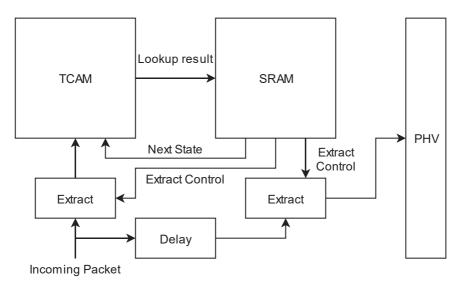

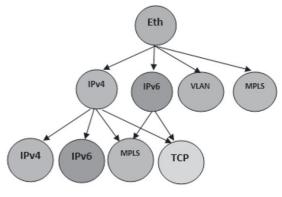

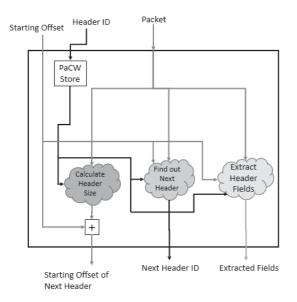

In [20], a programmable packet parser was presented. It operates based on the Match-Action principle. Based on the action determined by its current state, it extracts a specific field of the arrived header to determine its next state. Actions associated with a given state determine what fields of the arrived header must be extracted and what fields must be written to the field buffer. This parser achieves throughput of 40 Gbps.

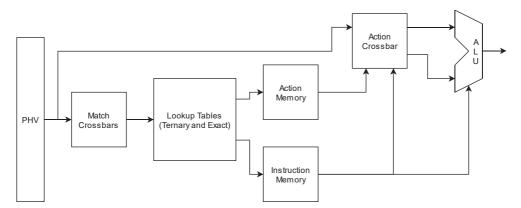

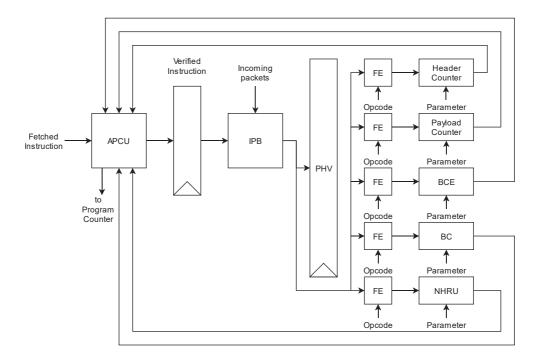

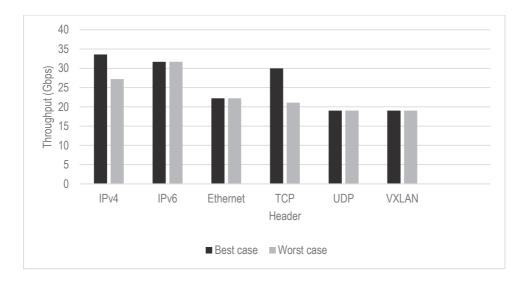

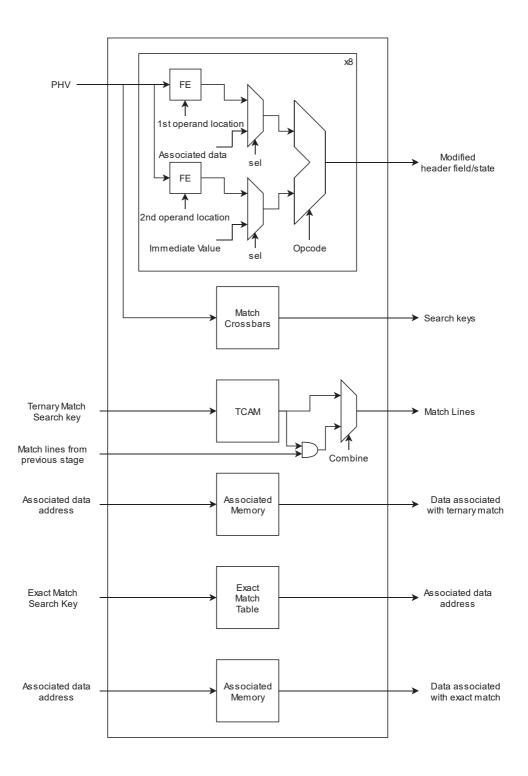

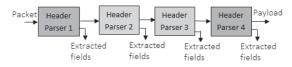

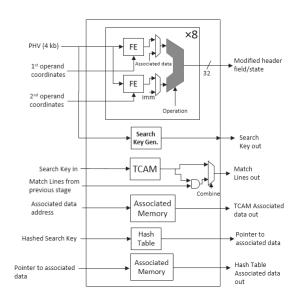

RMT [26] contains 16 instances of the parsers presented in [20] and a 32-stage pipeline of Match and Action Units (MAU). The parsers write header fields to a 4096-bit register called Packet Header Vector (PHV) which traverses through the pipeline. The PHV has 224 entries. The physical architecture of RMT closely resembles the switch abstraction made by P4. Inside each MAU, there are 16 TCAMs, each being a  $2K \times 40$ -bit unit. In addition, there are 106 SRAM blocks each of which is  $1K \times 112$  bits. These units can be flexibly assigned for exact match, action memory and statistics. What is meant by action memory is the parameters required for modification of header fields. Match crossbars generate the search key from the fields in PHV and present it to the ternary and exact match tables. The outcome of the match determines the actions to be executed. The actions are executed by action engines. Each action engine is an Arithmetic Logic Unit (ALU) for modifying PHV entries. There is an action engine associated with each PHV entry. Figure 2 provides a high-level view into a MAU. Only one of the 224 ALUs is illustrated. The output of the ALU is modified header field.

Figure 2. High-level view of the internal components of a MAU (adapted from [26])

If the dependencies in the program allow, it is possible to overlap the operation of MAU instances. In other words, it is not mandatory for MAU<sub>i</sub> to start match operation after action execution in MAU<sub>i-1</sub> has been done. However, this

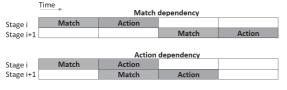

overlapping is not always possible due to dependencies. There are match dependencies and action dependencies. Match dependencies occur when field(s) modified by a MAU must be used as the search key in the subsequent MAU. In this case, the matching in subsequent MAU starts only after the action execution in current MAU is over. Action dependencies occur when field(s) modified by a MAU must be used as input(s) to action execution in the subsequent MAU. In this scenario, matching in subsequent MAU can overlap with action execution in current MAU. Figure 3 illustrates the two dependencies with respect to time.

| Match dependency |       |                   |        |        |  |  |  |

|------------------|-------|-------------------|--------|--------|--|--|--|

| Stage i          | Match | Action            |        |        |  |  |  |

| Stage i+1        |       |                   | Match  | Action |  |  |  |

|                  |       | Action dependency |        |        |  |  |  |

| Stage i          | Match | Action            |        |        |  |  |  |

| Stage i+1        |       | Match             | Action |        |  |  |  |

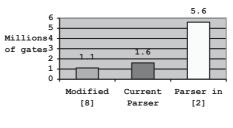

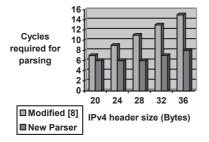

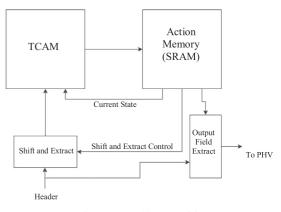

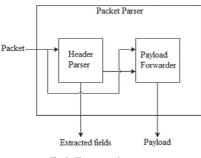

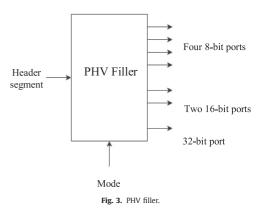

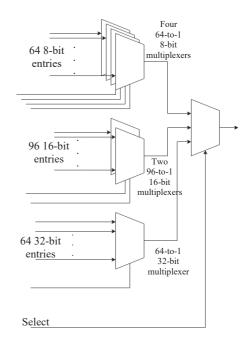

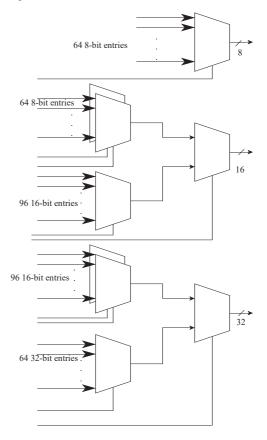

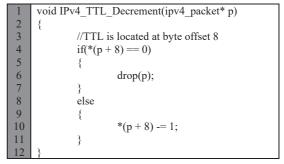

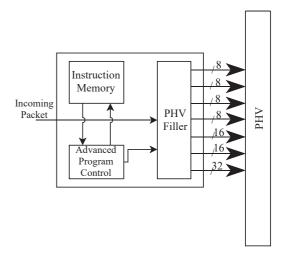

Figure 3. Match and Action dependencies in a Match-Action packet processing pipeline (adapted from [26])