Vladimír Guzma Improving Energy Efficiency of Application-Specific Instruction-Set Processors

Julkaisu 1504 • Publication 1504

Tampereen teknillinen yliopisto - Tampere University of Technology

Tampere 2017

Tampereen teknillinen yliopisto. Julkaisu 1504 Tampere University of Technology. Publication 1504 Doctoral candidate: Vladimír Guzma

Laboratory of Pervasive Computing

Faculty of Computing and Electrical Engineering

Tampere University of Technology

Finland

Supervisor: Jarmo Takala, Dr.Tech., Professor

Laboratory of Pervasive Computing

Faculty of Computing and Electrical Engineering

Tampere University of Technology

Finland

Pre-examiners: Johan Lilius, Ph.D., Professor

Department of Information Technologies

Åbo Akademi University

Finland

Carlo Galuzzi, Ph.D., Assistant Professor Department of Knowledge Engineering

Maastricht University The Netherlands

Opponents: Carlo Galuzzi, Ph.D., Assistant Professor

Department of Knowledge Engineering

Maastricht University The Netherlands

Leonel Sousa, Ph.D., Professor INESC-ID, Instituto Superior Técnico

Universidade de Lisboa

Portugal

### **Abstract**

Present-day consumer mobile devices seem to challenge the concept of *embedded computing* by bringing the equivalent of supercomputing power from two decades ago into hand-held devices. This challenge, however, is well met by pushing the boundaries of embedded computing further into areas previously monopolised by Application-Specific Integrated Circuits (ASICs). Furthermore, in areas traditionally associated with embedded computing, an increase in the complexity of algorithms and applications requires a continuous rise in availability of computing power and energy efficiency in order to fit within the same, or smaller, power budget. It is, ultimately, the amount of energy the application execution consumes that dictates the usefulness of a programmable embedded system, in comparison with implementation of an ASIC.

This Thesis aimed to explore the energy efficiency overheads of Application-Specific Instruction-Set Processors (ASIPs), a class of embedded processors aiming to compete with ASICs. While an ASIC can be designed to provide precise performance and energy efficiency required by a specific application without unnecessary overheads, the cost of design and verification, as well as the inability to upgrade or modify, favour more flexible programmable solutions. The ASIP designs can match the computing performance of the ASIC for specific applications. What is left, therefore, is achieving energy efficiency of a similar order of magnitude.

In the past, one area of ASIP design that has been identified as a major consumer of energy is storage of temporal values produced during computation – the Register File (RF), with the associated interconnection network to transport those values between registers and computational Function Units (FUs). In this Thesis, the energy efficiency of RF and interconnection network is studied using the Transport Triggered Architectures (TTAs) template. Specifically, compiler optimisations aiming at reducing the traffic of temporal values between RF and FUs are presented in this Thesis. Bypassing of the temporal value, from the output of the FU which produces it directly in the input ports of the FUs that require it to continue with the computation, saves multiple RF reads. In addition, if all the uses of such a temporal value can be bypassed, the RF write can be eliminated as well. Such optimisations result in a simplification of the RF, via a reduction in the actual number of registers present or a reduction in the number of read and write ports in the RF and improved energy efficiency. In cases where the limited number of the simultaneous RF reads or writes cause a performance bottleneck, such optimisations result in performance improvements leading to faster execution times, therefore, allowing for execution at lower clock frequencies resulting in additional energy savings.

Another area of the ASIP design consuming a significant amount of energy is the instruction memory subsystem, which is the artefact required for the programmability of the embedded processor. As this subsystem is not present in ASIC, the energy consumed for storing an application program and reading it from the instruction memories to control processor execution is an overhead that needs to be minimised. In this Thesis, one particular tool to improve the energy efficiency of the instruction memory subsystem – instruction buffer – is examined. While not trivially obvious,

ii Abstract

the presence of buffers for storing loop bodies, or parts of them, results in a reduced number of reads from the instruction memories. As a result, memories can be put to lower power state leading to lower overall energy consumption, pending energy-efficient buffer implementation. Specifically, an energy-efficient implementation of the instruction buffer is presented in this Thesis, together with analysis tools to identify candidate loops and assess their suitability for storing in the instruction buffer.

The studies presented in this Thesis show that the energy overheads associated with the use of embedded processors, in comparison to ad-hoc ASIC solutions, are manageable when carefully considered during the design of an embedded system for a particular application, or application domain. Finally, the methods presented in this Thesis do not restrict the reprogrammability of the embedded system.

### **Preface**

The work presented in this Thesis was carried out at the Institute of Software Systems, Department of Computer Systems, and concluded at the Department of Pervasive Computing at the Tampere University of Technology, Tampere, Finland, as a part of multiple research projects. The research work included a six month visit to the Department of Electrical and Computer Engineering, University of Maryland, College Park, USA.

I would like to express my gratitude to my supervisor Prof. Jarmo Takala and my former supervisor Dr. Pertti Kellomäki for their support and motivation that encouraged me to study and work towards my doctoral degree. My Thesis pre-examiners, Prof. Johan Lilius and Prof. Carlo Galuzzi deserve my deepest gratitude for providing valuable comments and improving this manuscript. I would also like to thank Prof. Shuvra S. Bhattacharyya from the University of Maryland who made my research visit possible and for his guidance during the visit.

I am especially grateful to the co-authors of the publications that form this Thesis, Dr. Pekka Jääskeläinen, Dr. Pertti Kellomäki, Dr. Teemu Pitkänen, and Prof. Jarmo Takala. Dr. Pitkänen, in particular, provided invaluable hardware expertise that made these publications possible.

A special thanks belong to Dr. Andrea Cilio for almost single-handedly producing the specification of the whole hardware-software co-design framework used for research work presented in this Thesis, and to my colleagues from FlexDSP research group for bringing this work into existence.

Finally, my deepest gratitude is extended to my family for their support during my years in academia.

Watford, UK, September 2017 Vladimír Guzma

# **Table of Contents**

| ΑJ | ostrac             | et e e e e e e e e e e e e e e e e e e                                                                                             | I              |

|----|--------------------|------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Pr | eface              |                                                                                                                                    | iii            |

| Li | st of A            | Abbreviations                                                                                                                      | vii            |

| Li | st of I            | Figures                                                                                                                            | ix             |

| Li | st of T            | Tables                                                                                                                             | X              |

| Li | st of I            | Publications                                                                                                                       | xi             |

| 1  | 1.1<br>1.2<br>1.3  | Oduction       Scope and Objectives       Main Contributions       Author's Contribution                                           | 1<br>3<br>5    |

|    | 1.4                | Thesis Outline                                                                                                                     | 6              |

| 2  | <b>Mod</b> 2.1 2.2 | <b>Ielling, Estimation, and Exploration of Energy for Embedded Systems</b> Modelling and Estimation of Energy for Embedded Systems | 7<br>7<br>10   |

| 3  | Red                | ucing Energy Demands of Register Files and Interconnection Network                                                                 | 15             |

|    | 3.1<br>3.2<br>3.3  | Energy Demands of Register Files and Interconnection Networks Lifespan of Bypassed Variables                                       | 15<br>18       |

|    | 3.4<br>3.5<br>3.6  | Performing Bypassing                                                                                                               | 19<br>26<br>31 |

|    | 3.7                | Networks                                                                                                                           | 33<br>35       |

| 4  | Red                | ucing Energy Demands of Instruction Memory Hierarchies                                                                             | 37             |

|    | 4.1                | Background of Memory Hierarchies                                                                                                   | 37             |

|    | 4.2                | Detection of Loops for Execution from Buffer                                                                                       | 39             |

|    | 4.3                | Control of Execution of Loops from Buffer                                                                                          | 40<br>42       |

|    | 4.4<br>4.5         | Loop Types Stored in Buffer                                                                                                        | 42             |

|    | 4.5<br>4.6         | Implementations of Loop Buffering                                                                                                  | 45             |

|    | 4.7                | Final Remarks on Loop Buffering                                                                                                    | 49             |

|    | T./                | I mai nomaino di Loop Danoinis                                                                                                     | マン             |

vi Table of Contents

| 5  | Cone         | clusions                                            | 51 |

|----|--------------|-----------------------------------------------------|----|

|    | 5.1          | Main Results                                        | 51 |

|    | 5.2          | Future Development                                  | 52 |

| Bi | bliogr       | raphy                                               | 55 |

| Ap | pend<br>Prin | ix A<br>ciples of Transport Triggered Architectures | 61 |

| Pu | blicat       | tions                                               | 63 |

|    | Publi        | ication [P1]                                        | 65 |

|    | Publi        | ication [P2]                                        | 65 |

|    |              | ication [P3]                                        |    |

|    | Publi        | ication [P4]                                        | 65 |

|    |              | ication [P5]                                        |    |

|    | Publ         | ication [P6]                                        | 66 |

## **List of Abbreviations**

**ALU** Arithmetic Logic Unit

**ASIC** Application-Specific Integrated Circuit

**ASIP** Application-Specific Instruction-Set Processor

**CIM** Control and Index Memory

**CPU** Central Processing Unit

**DSP** Digital Signal Processor

**DVS** Dynamic Voltage Scaling

**EDA** Electronic Design Automation

**FLOP** Floating-Point Operation

**FMA** Fused Multiply-Add

**FMAC** Fused Multiply-Accumulate

**FPGA** Field Programmable Gate Array

**FPU** Floating-Point Unit

FU Function Unit

**GPU** Graphics Processing Unit

**HLS** High-Level Synthesis

**I-cache** Instruction Cache

**ILP** Instruction-Level Parallelism

IP Intellectual Property Block

**IPC** Instructions Per Cycle

**IRF** Instruction Register File

**ISA** Instruction-Set Architecture

MAC Integer Multiply-Accumulate

**NOP** No Operation

viii List of Abbreviations

**RF** Register File

**RISC** Reduced Instruction-Set Computer

**ROB** Reorder Buffer

**RTL** Register-Transfer-Level

SBB Short Backward Branch

**SOP** Sum-Of-Product

TCE TTA-based Co-Design Environment

TTA Transport Triggered Architecture

**VLIW** Very Long Instruction Word

# **List of Figures**

| 1.1 | An example of an execution of 'Sum-Of-Product' expression                                    |    |

|-----|----------------------------------------------------------------------------------------------|----|

| 1.2 | Example of a simple instruction memory access to control three FUs                           | 4  |

| 2.1 | Simple example of design flow                                                                | ç  |

| 2.2 | Simple example of exploration and estimation flow                                            | 12 |

| 3.1 | Naïve example of clustering Register Files and Function Units                                | 17 |

| 3.2 | Simple example of multiple result use and single value use bypassing                         | 19 |

| 3.3 | Simple example of a single FU bypassing                                                      | 20 |

| 3.4 | Simple example of multiple FUs bypassing                                                     | 21 |

| 3.5 | Simple example of multiple FUs bypassing with multiple uses of same bypass register.         | 22 |

| 3.6 | Simple example of register allocation without and with knowledge of bypassing                |    |

|     | opportunities                                                                                | 23 |

| 3.7 | Example detection of bypassing late during code generation                                   | 28 |

| 3.8 | Example detection of bypassing early during code generation                                  | 30 |

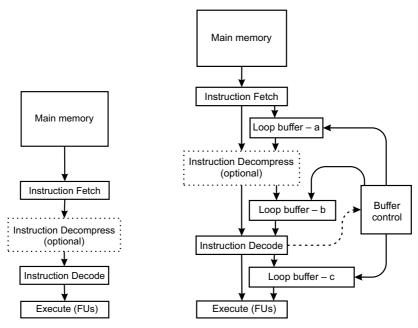

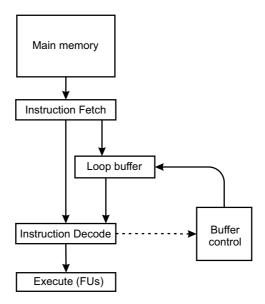

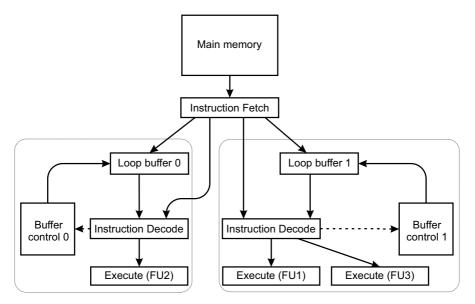

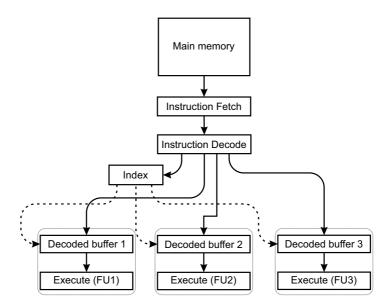

| 4.1 | Example of multiple possible placements of loop buffer                                       | 38 |

| 4.2 | Problematic conditional execution inside the loop and result of loop buffer friendly         |    |

|     | compiler optimisation of if-conversion                                                       | 41 |

| 4.3 | Examples of multiple types of conditional control in a loop                                  | 43 |

| 4.4 | Example of negative effect of loop unrolling with instruction buffer                         | 44 |

| 4.5 | Example of a simple centralised instruction buffer                                           | 45 |

| 4.6 | Example of a simple distributed instruction buffer with two clusters                         | 46 |

| 4.7 | Example of a simple hierarchical instruction buffer with <i>Index</i> controlling individual |    |

|     | Decoded buffers                                                                              | 47 |

| A.1 | An example of an execution of AND operation on RISC and TTA                                  | 62 |

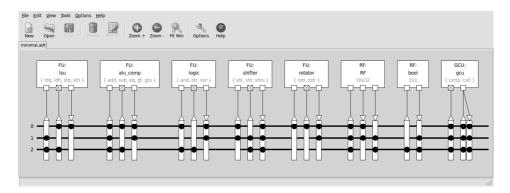

| A.2 | Example of a simple TTA with five FUs and two RFs                                            | 62 |

# **List of Tables**

| 2.1 | Summary of reported modelling and estimation techniques | 11 |

|-----|---------------------------------------------------------|----|

| 2.2 | Summary of reported exploration techniques              | 14 |

| 3.1 | Summary of reported bypassing techniques                | 35 |

| 4.1 | Summary of reported instruction buffering techniques    | 48 |

## **List of Publications**

This Thesis is composed of an introductory part and seven original publications. The original publications are referred to in the text as [P1], [P2], [P3], [P4], [P5], and [P6].

- [P1] Vladimír Guzma, Pekka Jääskeläinen, Pertti Kellomäki, Jarmo Takala, "Impact of Software Bypassing on Instruction Level Parallelism and Register File Traffic", in *Embedded Computer Systems: Architectures, Modeling, and Simulation*, vol. 5114, pp. 23–32, 2008, Springer Berlin Heidelberg

- [P2] Vladimír Guzma, Teemu Pitkänen, Pertti Kellomäki, Jarmo Takala, "Reducing Processor Energy Consumption by Compiler Optimization", in *Proceedings of the IEEE Workshop on Signal Processing Systems*, Tampere, Finland, Oct. 7–9, 2009, pp. 063-068

- [P3] Vladimír Guzma, Teemu Pitkänen, Jarmo Takala, "Use of Compiler Optimization of Software Bypassing as a Method to Improve Energy Efficiency of Exposed Data Path Architectures", in *EURASIP Journal on Embedded Systems*, vol. 2013, no. 1, 2013

- [P4] Vladimír Guzma, Teemu Pitkänen, Jarmo Takala, "Reducing Instruction Memory Energy Consumption by using Instruction Buffer and After Scheduling Analysis", in *Proceedings of the International Symposium on System-on-Chip*, Tampere, Finland, Sep. 29–30 2010, pp. 99–102

- [P5] Vladimír Guzma, Teemu Pitkänen, Jarmo Takala, "Instruction buffer with limited control flow and loop nest support", in *Proceedings of the International Conference on Embedded Computer Systems*, Samos, Greece, July 18-21 2011, pp. 263–269

- [P6] Vladimír Guzma, Teemu Pitkänen, Jarmo Takala, "Effects of loop unrolling and use of instruction buffer on processor energy consumption", in *Proceedings of the International Symposium on System-on-Chip*, Tampere, Finland, Oct. 31 – Nov. 2 2011, pp. 82-85

## 1 Introduction

The computing power of instruction-set processors has been growing following *Moore's Law* for several decades ([1] and [2]), with manufacturing technologies using smaller and smaller sizes of primitive components, allowing for an increase in the available number of computing operations and memory bits per clock cycle. Such advances, eventually, allow for two major directions in instruction-set processor design.

On one hand, more computing power with more memory allows for more complex algorithms, working with increasingly large sets of data. This trend leads to processor designs with higher theoretically achievable computing power utilising larger amounts of memory, with a large number of transistors in the same package size.

On the other hand, from one technology generation to the next one, the same amount of computing power and memory becomes available in smaller packages, with less energy required to perform the same task. This makes the use of programmable instruction-set processors feasible, although with worse energy efficiency, in the areas previously requiring the design of an Application-Specific Integrated Circuit (ASIC) developed at significant costs. Therefore, high efficiency and development cost can be traded for speed-to-market and re-usability.

Furthermore, for tasks where general-purpose instruction-set processors do not offer enough computing power to fit into the available power budget for the particular domain of applications, domain-specific instruction-set extensions can be added to the processor design. One typical example is the integration of a Multiply-Accumulate (MAC) operation. When applied to floating point numbers, a Fused Multiply-Add (FMA) operation, sometimes referred to as Fused Multiply-Accumulate (FMAC) operation, allows to select one or two rounding modes (standardised by the IEEE Computer Society [3]), the choice being left to the system designer and the particular application requirements. Those operations are rather common instruction-set extensions available in processors designed for the digital signal processing domain – Digital Signal Processors (DSPs). Such instruction-set extensions improve computing performance and increase the energy efficiency of domain-specific processors, as well as contribute to the reduction in the size of an application's instruction code and, consequently, the required instruction memory.

The race, however, is always on between improvement in energy efficiency and computing power of domain-specific instruction-set processors, and the increasing computational complexity and the bit rates of algorithms required in new products. While performance and energy efficiency are almost always in favour of ASICs (see Campbell [4]), prohibitive costs of such designs and time to market requirements favour solutions using reusable parts, such as DSPs.

Fortunately, in cases where even DSPs do not provide enough computing performance, or if they are too costly in terms of energy or area, further customisations can take place. By adding application-specific instruction-set extensions, computationally intensive parts of an application can be accelerated considerably. At the same time, by removing parts of the design, which are

never required, or rarely used in a particular application (e.g. integer division), we achieve a reduction in the area and an increase of the energy efficiency in the final processor.

This process results in the formation of an Application-Specific Instruction-Set Processor (ASIP), tailored to the performance and energy efficiency requirements of a single application, or a small set of applications with similar computing requirements. Advances in automated design tools, availability of processor architecture templates, and the possibility of licensing of custom accelerator blocks in form of semiconductor intellectual property cores (Intellectual Property Block (IP) or IP core), make such an application-specific customisation a viable design choice.

While not as energy-efficient as ASICs, ASIPs allow for faster time to market and for minor software updates. As an added benefit, when an ASIP is not used for the purpose it was designed for, it can still offer a certain amount of flexibility to accelerate similar applications, although without achieving the maximum efficiency [5, 6].

Alternatives, such as Field Programmable Gate Arrays (FPGAs) are important tools for prototyping of applications and allowing flexibility in choosing which part of the application and architecture design to accelerate. Their energy efficiency, however, often prevents their use once the design reaches deployment stage. An interesting alternative is the combination of the heterogeneous 'Central Processing Unit (CPU)' and reconfigurable component [7–9]. This area, however, is out of the scope of this Thesis.

Putting together all the concerns above, designers of new products need to consider the number of conflicting performance, power, and area requirements leading to multiple choices in the design process:

- The design of an ASIC is the most expensive in terms of design time, verification, and optimisation. At the same time, it can achieve the highest energy and area-efficiency for specific requirements of data bandwidth and computing performance, with minimal overheads.

- An *off-the-shelf* processor, either general-purpose or domain-specific, such as a DSP, takes less time to design and is easy to test and verify, as only algorithm and performance verification are needed. However, a processor that provides enough computing performance and memory bandwidth to implement the desired application(s) needs to be selected. As a result, the application designer has no control over energy efficiency and depends on the provider of the off-the-shelf solution, resulting in worse energy efficiency than a custom-designed integrated circuit [4].

- A combination of the above approaches can be achieved by an instruction-set processor template. This allows one to reuse the common parts of the design and add application-specific computing blocks or include third-party IP blocks. This allows for tailoring of computing performance to the requirements of a specific application by using instruction-set extensions as well as reducing energy requirements by eliminating the need for components of the processor not required for the particular use case. As a result, in terms of design time, this approach sits between the other two. Design and verification of custom circuitries are only required for small parts of the whole processor, which accelerate calculation with high energy efficiency. The common components of a processor are provided and pre-verified by the provider of the platform.

The ultimate objective of the ASIP design is to achieve computing performance and energy efficiency close to that of the ASIC solution. Focusing on computing performance, data bandwidth

throughput, or overall energy consumed affects battery life. One suitable way to view performance in a computing domain is performance per power (floating-point operation (FLOP)/Watt) [4], or *performance per energy* (Floating-Point Operation (FLOP)/Joule).

In order to achieve this goal, a balance needs to be found between the amount of data used, transmitted either over air or by wire, the computing power required to process this data, and the energy needed for the whole computation and data transmission. For example, the use of space-efficient data compression reduces the required data bandwidth when transmitting over the air, but additional computing power is required to decompress the data before the actual algorithmic computation starts. Alternatively, higher data bandwidth can lead to a reduced demand for computing power, at the expense of a more complex receiver.

Such a balance and the design process leading to it are highly iterative. Extensive profiling of an application is required in multiple stages of a design process, which then provides feedback to guide further architectural design changes. The use of automated, or semi-automated, hardware-software co-design tools, template architectures, and IP libraries allows for many design decisions, requiring exploration of a large design space. With so many options available for the customisation of an architecture and widening range of compiler optimisation techniques matching them, a detailed exploration of all possible design decisions is not practical. It is, therefore, important to prune design-space early by discarding decisions that do not lead to a promising direction. The early estimation of energy and performance results of custom designs as well as generated components can benefit this process to a great extent.

#### 1.1 Scope and Objectives

The focus of this Thesis is on the evaluation of the impact of compiler optimisations and architectural changes on energy demands of programmable embedded processors, in order to narrow the set of possible implementations early in the design process.

While the solutions proposed in this Thesis can be applied to both statically and dynamically scheduled architectures, in order to allow for a clear evaluation of the impact of the proposed solutions, the research work presented herein is based on a flexible Transport Triggered Architecture (TTA) template, proposed by Corporaal [10]. The goal of the TTA is to tackle the scalability problem of Very Long Instruction Word (VLIW), where the addition of an FU requires the addition of interconnections with the RF, thus limiting the scalability for performance (discussed further in Chapter 3). Arguing that the worst-case scenario of all FUs being used simultaneously is rare, the TTA addressed scalability by exposing the underlying interconnection to the programmer/code generation. The execution of the operation is decomposed into a number of moves, which explicitly state the source and destination for each of the interconnection buses, defining moves to provide operands of operation for a particular FU, as well as move(s) to store the result of the computations in a RF. The addition of an FU, therefore, is just a matter of connecting the FU to some of the existing interconnection buses. Together with static schedule, this architecture template allows flexibility to study the compiler optimisations required for improvements to the energy efficiency of an overall system in combination with architectural changes to components sometimes taken for granted. Characteristics of the TTA are presented in the Appendix A.

In this Thesis, the scope of hardware-software co-design investigated is narrowed to two main areas:

• The efficient use of software bypassing of temporal variables with required architecture customisation. its impact on the energy of multiple critical system components.

(b) SOP using temporal variables  $t_1$ ,  $t_2$ , and reuse of common operations.

**Figure 1.1:** 'Sum-Of-Product (SOP)' expression with hardware support (1.1a) and with the use of temporal variables and reuse of common operations (1.1b).

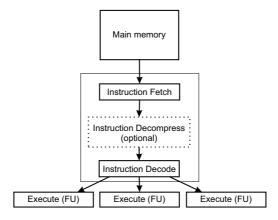

Figure 1.2: Example of a simple instruction memory access to control three FUs.

• The impact of application and architecture-specific, program-controlled, instruction stream buffer on the overall energy of memory subsystem.

The reason for studying the first area is based on the argument that in their own right, the existence of temporal variables does not impact or contribute to the computation of an algorithm. They exist only as artefacts of programmable processor design, with computational logic distributed to multiple components. Let's take as an example the expression "x = (a\*b) + (c\*d)", known as "Sum-Of-Product (SOP)" [11]. As shown in Figure 1.1, we can compute such an expression in the designated hardware unit (see Figure 1.1a) or with the use of common arithmetic operations utilising temporal variables stored in the RF (see Figure 1.1b). It is, therefore, possible to argue that the purpose of temporal variables is to allow for programmability of the programmable processor and, as such, an energy overhead incurred by their use is a waste, when compared to an ASIC design, and should be kept to the minimum.

The reason to study the second area comes from the observation that in order to perform computation, programmable processors, such as ASIPs, need to read a stream of instructions describing the algorithm being executed, usually stored in the memory. This reading from instruction memory involves multiple phases (see Figure 1.2) and comes with considerable energy costs, very much notable in multiple issue architectures, such as VLIW. The presence of such an instruction memory hierarchy is costly, both in terms of area and energy, when compared to an ASIC designs, and should be minimised.

The objective of this Thesis is, therefore, to outline methods that allow for clear understanding of trade-offs in energy efficiency and computing performance when designing programmable embedded processors for a particular application or a small set of applications, extending the focus

1.2. Main Contributions

beyond the computing performance and energy efficiency of Arithmetic Logic Units (ALUs), Floating-Point Units (FPUs), and custom Intellectual Property Blocks (IPs).

#### 1.2 Main Contributions

The architectural and energy efficiency studies presented in this Thesis were carried out using an Application-Specific Instruction-Set Processor, based on the Transport Triggered Architecture paradigm. Specifically, the TTA-based Co-Design Environment (TCE) framework was used [12].

One area of study presented in this Thesis is the impact and practical viability of implementing a software bypassing mechanism for reducing the usage of hardware registers to store temporal values during application execution. The use of such a bypassing mechanism affects multiple architectural components of processor design and parts of the code generation tool-chain and also impacts run-time characteristics such as:

- The execution cycle counts.

- The number of read and write accesses to individual registers.

- The number of required ports for simultaneous access to the RF.

- The complexity of the interconnection networks.

- The number of required registers.

The work presented in this Thesis introduces an opportunistic, yet conservative software bypassing algorithm. It evaluates the effects of software bypassing on computing performance, processor area and, most importantly, the energy requirements of individual components of the design listed above. Additionally, a comparative study of software bypassing and design technique of *connectivity reduction* [13, 14] is presented, demonstrating energy savings while maintaining higher reprogrammability.

The second area of study presented in this Thesis is the energy efficiency of the instruction stream in the embedded processors. There are three basic hardware components that are required for execution of instruction:

- The instruction memory block(s).

- The processor's instruction fetch, possibly decompress, and instruction decode mechanism.

- (Optionally) the intermediate storage, such as instruction cache, instruction scratchpad, or instruction loop buffer.

This Thesis presents a method for determining the size of the intermediate storage for a particular application in order to maximise energy efficiency. The energy demand of all three components above is considered, as well as the optimisations introduced by code generation pipeline, loop unrolling in particular [15].

Additionally, an energy-efficient control mechanism for instruction buffer (sometimes referred to as loop buffer) is presented, and its energy efficiency is evaluated for a number of different loop types with varying amounts of control structures.

#### 1.3 Author's Contribution

The work presented in this Thesis is based on the results reported in the publications [P1]–[P6]. The Author of this Thesis is the main author of all these publications. None of these publications have been previously used in any academic thesis.

The publication [P1] establishes the basic algorithm for safe software bypassing and proposes a condition that guides the aggressiveness of bypassing in order to investigate the advantages and disadvantages of RF traffic. An actual software bypassing algorithm with aggressiveness control has been proposed and implemented by the Author of this Thesis and experimental work has been carried out.

The publication [P2] investigates the efficiency of bypassing in terms of energy of the RF as well as interconnection network. The hardware cost estimation model was developed by Dr. Teemu Pitkänen and is also used in publication [P3]. The Author of this Thesis provided the experimental setup, and improved bypassing algorithm as well as carried out experimental work.

Comparative study of software bypassing and connectivity reduction with regard to energy efficiency is presented in publication [P3]. The Author of this Thesis provided experimental setup and an improved bypassing algorithm.

In the publication [P4], the Author of this Thesis developed a method to analyse the existing binary of an application and combine it with execution trace information to establish the most efficient size of the instruction buffer. The hardware implementation of the instruction buffer and its hardware cost estimation model were provided by Dr. Teemu Pitkänen and are also used in publications [P5] and [P6].

In the publication [P5], the Author of this Thesis provided an improved method for the detection of more complex loop structures and cooperated with Dr. Teemu Pitkänen in improving the instruction buffer control required to accommodate such loops.

The publication [P6] studies trade-offs associated with the use of compiler optimisations to improve computational efficiency and energy efficiency of the instruction buffer. The Author of this Thesis provided experimental setup and carried out experimental work while using the same hardware cost estimation model presented in publication [P5].

#### 1.4 Thesis Outline

The introductory part of this Thesis discusses multiple approaches to the research questions investigated in publications [P1]–[P6] and presented in this Thesis. Chapter 2 discusses the methods and findings in the area of power modelling, estimation, and exploration of the embedded systems based on the VLIW concept, similar to the framework used for experiments presented in this Thesis. Chapter 3 discusses approaches to improving computing performance by bypassing reads/writes of temporal values from/to RFs. The impact of these methods on the energy of RFs and the interconnection network is compared between the methods discussed in publications [P1]–[P3], presented in this Thesis as interesting alternative approaches. Chapter 4 discusses the approaches to improving the energy efficiency of instruction memories by reducing the number of memory fetch operations in memory blocks by using energy-efficient buffering and compares state of the art with methods discussed in publications [P4]–[P6] presented as part of this Thesis. Finally, Chapter 5 concludes the introductory part of this Thesis with final remarks. The second part of this Thesis consists of six original publications.

# 2 Modelling, Estimation, and Exploration of Energy for Embedded Systems

Embedded systems, by their nature, are subject to power and area limitations. Providing sufficient computing performance within the restriction of available power budget as well as area limitations can be a difficult goal to achieve using existing off-the-shelf components. Application-Specific Instruction-Set Processors (ASIPs) offer a possibility to customise a range of components of the processor. Such a customisation can help achieve the required computing performance without spending energy and area on processor components with little or no use for execution of the particular application. Specifically, ASIPs based on the VLIW paradigm are popular owing to their ability to deliver large amounts of computing power at relatively low frequency, resulting in controllable power costs. Fundamental in the process of optimising ASIP for performance and energy efficiency is the understanding of how power is spent on the different parts of the system. Once this is achieved, individual components can be optimised for power, performance, or both, based on the application(s) executed in the system.

#### 2.1 Modelling and Estimation of Energy for Embedded Systems

The precise area of any proposed ASIP design is known at the end of the design phase, before the start of the actual production. However, when it comes to computational performance and power consumption, precise characteristics of the system can only be obtained once the actual processor is produced. Only then it becomes possible to reliably measure a processor's computational performance, taking into account the real environmental factors such as surrounding temperature and possible frequency throttling to prevent overheating. Similarly, the actual power required by the processor can be accurately measured only when the processor is running an application. Once the precise characteristics of the implemented design are collected, it is possible to compare them against the design goals. If the design goals are not achieved, the whole process needs to be reiterated to further progress towards the design goals.

The complexity of modern embedded systems makes manual designing of the whole system time consuming. In addition, a mistake made at the design phase, necessitates redesigning or adjusting of the design goals. When starting from scratch, the design requires the use of low-level Register-Transfer-Level (RTL) abstraction to design fundamental components, which can be synthesised to a gate-level description. The existence of the RTL designs of fundamental components, consequently, allows for the reuse of the parts of the design in multiple places and for the creation of higher level micro-architectural components. A system-level design can then be created utilising those components. Given the complexity of the designs, starting from scratch is simply not practical. The design process, therefore, depends on Electronic Design Automation (EDA) for placement of components and connections and common hardware description languages, such as Verilog or VHDL, for designing individual components.

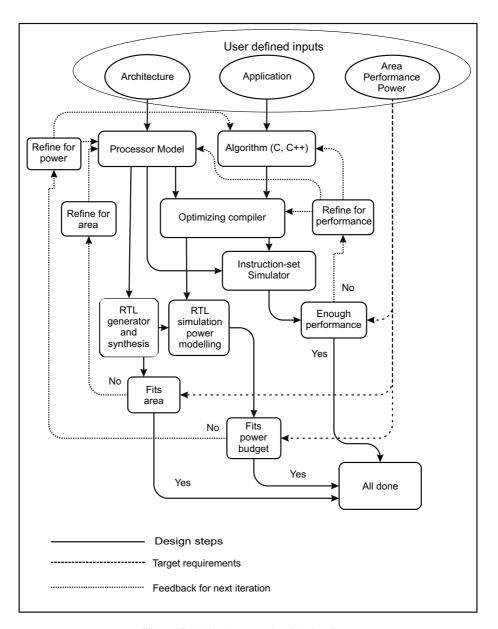

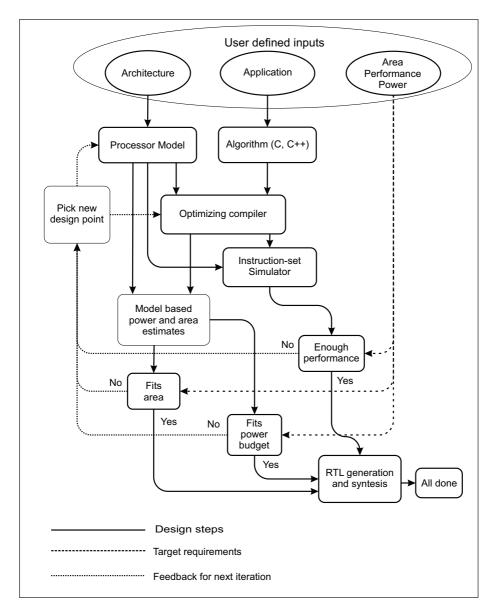

The presence of IP libraries allows EDA tools to speed up the development of embedded system designs. Starting from simple logic gates, modern EDA tools include libraries of pre-designed micro-architectural components and allow for addition of custom IP during the design process. The initial stage of design process depends on the experience of the designer. Once this initial stage is completed, additional tools are required to assess the performance. In principle, at least the code generation of the application executable code, simulation of the execution of the application, and collection of the computing performance information are necessary. Power modelling is also possible during simulation, to provide power consumption estimates. Once the computing performance and consumed power of a particular iteration of design are known, it is possible to assess whether the achieved design fits the design goals and reiterate it based on the collected data (simple outline of design flow in Figure 2.1).

Such highly specialised tools, allowing for different degrees of design automation, are available from commercial vendors (such as Synopsys [16], Cadence [17], and Mentor Graphics [18]), as well as past and present academic research projects (such as [12, 19, 20]). While EDA tools help speed up the system design process, they have their drawbacks. In particular, the simulation of application execution on a selected design can be conducted at multiple levels, with RTL being the most accurate, both in terms of performance and power, but also the most time-consuming one. On the other hand, at the system-level, design can be simulated using an instruction-level simulator, with high simulation speed but, traditionally, lower power estimation accuracy.

In their often-cited work, Benini et al. [21, 22] presented a study of power modelling and power estimation for VLIW-based embedded systems. In their work, the authors proposed power models for the main components of an embedded VLIW system, such as the actual VLIW core, the Register Files, and instruction and data caches. One area omitted in the model presented is the interconnection networks. In addition to presenting the framework for modelling the processor components, the authors integrated their models with multiple simulators from RTL to instruction-level. The method presented by the authors achieved maximum error between RTL and instruction level power modelling of less than 8%, with an average error of about 5.2%. These results were achieved with instruction-level power modelling being four orders of magnitude faster than RTL modelling. As a conclusion, the authors advocated the viability of high-level power estimation in terms of efficiency and absolute accuracy. With these findings, the viability of instruction-level power modelling as an alternative to time-consuming RTL simulations impacted a large area of research in the following years.

Specifically targeting FU execution and interconnection for VLIW, Sami et al. [23] proposed an extension of instruction-level power modelling to pipeline-level modelling. The authors argued that in multi-issue architectures, inter-instruction conflicts may impact the accuracy of instruction-level modelling focused on considering a single instruction as an individual unit of execution with the associated power costs based on the instruction fetch cycle. Effects such as stalls due to data hazard or register bank access conflicts impact the accuracy of power modelling and prevent specific compiler optimisation techniques, such as re-scheduling for minimal power variation between instructions, from being applied effectively. By exposing the energy model to individual pipeline stages, the proposed method allowed for more accurate modelling of the required pipeline power. The individual power contributions of pipeline stages of different FUs in the VLIW processor are combined at each cycle, as well as power contributions of the processor core interconnections. By applying this method, the authors in [23] reported observed average error of 4.8%, and a maximum error of 10%, compared to the measured power, with four orders of magnitude estimation time speed-up compared to gate-level estimation on a set of DSP benchmarks. When considering artificial microbenchmarks, the authors observed the average error of instruction decode to be the smallest (1.27%) and that of instruction execution, the highest

Figure 2.1: Simple example of design flow.

(6.75%), with an average interconnection error of 13.59% and the maximum error of 116.91%.

The work presented by Zyuban and Kogge [24] addresses the energy-complexity of RFs. The authors observed that an increase in available Instruction-Level Parallelism (ILP), a tendency to utilise wide issue processor concept, and an increasingly complex out-of-order execution lead to a substantial portion of the energy of the processor being spent on the RF. The actual cost depends on the RF implementation. In their work, the authors compared different implementation techniques as a function of architectural parameters, such as the number of required registers and the number of read and write ports. In principle, to allow for optimal execution throughput in a wide-issue processor, the number of read ports in the RF needs to match the number of read

operands in instruction and issue width. In conclusion, the authors encouraged the development of an inter-instruction communication mechanism as an alternative to centralised RF, since circuit trickery is not sufficient to keep up with the increasing demands of wide-issue architectures on the number of registers and ports.

For practical purposes, Raghavan et al. [25] developed empirical formulae for modelling energy per access and leakage power and area for RFs of different sizes. The authors based their approach on the implementation of over 100 RF designs and their low-level simulations. The analysis of the collected data allowed for mathematical formulation of the model. In their verification, the authors reported a 10% error in their model as compared to the detailed simulation.

Looking at estimation of area, delay, and energy of interconnection, Nagpal et al. [26] proposed a tool that considers known models of delay and energy and solves the optimisation problem of finding the lowest energy interconnection design to satisfy architectural constraints. The authors argued that their proposed model can be used for early evaluation of architectural and compiler optimisations.

Of particular interest to the architectural concept used in the publications [P1], [P2] and [P3], is the analysis of different bus structures for TTA, as presented by Mäkelä et al. [27]. The authors studied multiple interconnect bus types (tri-state, and/or, multiplexer, and segmented multiplexer bus) and formulated equations for delay and power. Those were then verified by power analysis. The authors concluded that their equations highlight the characteristics of each bus type.

Heading off the processor core, discussed in Chapter 4 as well as publications [P4] and [P5], is an area of work presented by Artes et al. [28]. In their work, the authors discussed the energy efficiency of multiple-loop buffer architecture. Aiming to reduce the power demands of instruction memory organisation, the authors analysed energy efficiency of multiple types of loop buffer organisations, ranging from central loop buffer to distributed loop buffers. The authors observed an energy reduction of 68% to 74% in instruction memory organisation using a synthetic benchmark and of 40% in its real-world biomedical application in heart beat detection.

Overall, models of individual components, such as those discussed above and summarised in the Table 2.1, can be used during design and optimisation of individual parts of a processor design, with results implemented as part of IP libraries. In combination with wider libraries of designs available as part of EDA tools, such libraries allow for rapid prototyping and evaluation of individual components, as well as overall system-level design. In particular, fast high-level estimation of the power consumption of individual components allows for narrowing down of the set of viable design options, followed by more detailed but time-consuming low-level synthesis and estimation. In case of parametric designs of critical components, this process can be taken one step further with automatic, or semi-automatic high-level exploration of design-space, the topic of discussion in Section 2.2.

#### 2.2 The Design-Space Exploration Problem

In order to speed up a system, the most used component should be optimised first; the application of this argument to embedded systems is not very clear. With the availability of multiple implementations of individual components to choose from as well as the availability of tools to customise critical components, the process of finding a fitting combination to achieve the required performance within given power constraints becomes extremely tedious. At the beginning of the design process, a system designer can use the knowledge of the application or application domain to select a high-level design template. However, selecting individual components to fit

| Reference              | Method                                                                | Estimated components                           | Average error                        |

|------------------------|-----------------------------------------------------------------------|------------------------------------------------|--------------------------------------|

| Benini et al. [21, 22] | power models and<br>multiple simulators                               | VLIW core, the RFs instruction and data caches | 5.2 % instruction-level vs RTL model |

| Sami et al. [23]       | pipeline-level<br>modelling                                           | VLIW core including interconnect               | 4.8% vs measured power               |

| Zyuban and Kogge [24]  | different RF implementations                                          | RFs                                            |                                      |

| Raghavan et al. [25]   | empirical formulae<br>for energy per access<br>leakage power and area | RFs                                            | 10% vs detailed simulation           |

| Nagpal et al. [26]     | models of delay and energy                                            | early evaluation of architecture and compiler  |                                      |

| Mäkelä et al. [27]     | formulated equations for delay and power                              | multiple interconnection<br>bus types          |                                      |

| Artes et al. [28]      | analyse multiple loop<br>buffer types                                 | loop buffers                                   |                                      |

**Table 2.1:** Summary of reported modelling and estimation techniques.

into this design as well as their parameters and evaluating the results can become costly and time-consuming as well.

For example, achieving speed-up allows for execution on lower clock frequency leading to energy savings. However, the optimisation of one processor component, for power or performance, may increase the power or performance demands of another component, in order to achieve the required overall performance and fit the power budget. For example, speeding up execution by exploiting more ILP by adding another FU can indeed reduce the total execution time and allow for execution on the lower clock frequency. As a result, the sum of energy spent on execution using FUs can be lower than that without an additional FU. On the other hand, the addition of an FU increases the complexity of the interconnection network. An increased demand for the number of required register ports can result in an increase in required energy of those components, a higher increase than the savings achieved by the addition of FUs and reduction in the execution time.

With huge design spaces and a variety of components and parametrisation, an exhaustive exploration of all possible variations of processor design manually would be, for practical purposes, impossible. An automated or semi-automated exploration of such a design-space is somehow the more feasible solution. The design-space exploration tools (often part of commercial EDA packages) can automatically or semi-automatically iterate through a variety of components and component parameters and estimate the resulting costs in terms of area and power as well as estimate computational performance (simple outline of estimation and exploration flow in Figure 2.2).

In case of design and optimisation of an individual component and reuse of design of others, the interfaces to the overall system are defined, as are the requirements for performance, area, and power. This allows for incremental improvement of the individual components, independent of each other. As a result, even an exhaustive exploration of all possible component configurations may be possible.

In cases where the design-space exploration of the whole system is required, exhaustive design-space exploration becomes prohibitively expensive in terms of computing resources required. In order for a design-space exploration to produce reasonable results in a realistic time-frame, the exploration space needs to be navigated efficiently, avoiding the evaluation of parametric

**Figure 2.2:** Simple example of exploration and estimation flow.

combinations which are clearly inferior to already found results, and continuously progress towards better results. Multiple optimisation methods can be used to navigate this design space, each of them having their advantages and disadvantages. The hill climbing family of algorithms, for instance, tends to find only locally optimal solutions which can differ from a global optimum. The branch-and-bound family of techniques, on the other hand, aims at finding a globally optimal solution.

An interesting example of such a whole system design-space exploration is presented by Ascia et al. [29]. In their work, the authors presented a system-level framework for VLIW architectures, providing an evaluation of performance, area cost, and power consumption of a VLIW core,

as well as the memory hierarchy subsystem. In addition, the framework also includes multiobjective design-space exploration, guided by a tunable compiler and architectural parameters such as RFs, FUs and memory sub-system, as well as speculative execution and hyperblock creation. Multiple design-space exploration strategies were evaluated, ranging from analytical to heuristical. Analytical methods are based on clustering of dependent parameters. Givargis et al. [30] showed that two parameters are dependent if a change in the value in the first parameter changes the optimal value of the second parameter. For example, the associativity and line size of an instruction cache are dependent, but associativity of an instruction cache and the line size of a data cache are independent. Once dependence is established, the parameters are separated to individual clusters, with no dependence between clusters, and each cluster can be explored exhaustively. Another method discussed is a use of genetic algorithms as optimisation tools, based on previously published work of Ascia et al. [31]. Each exploration strategy comes with its own trade-off between quality of the solutions found and time taken for the exploration to conclude.

A different approach to this problem is presented by Eusse et al. [32]. In their work, the authors coupled High-Level Synthesis (HLS) with pre-architectural performance estimation. The aim of this approach was to provide an initial architectural seed for a target application. The pre-architecture estimation engine then provides a cycle-approximate expectation of a performance for the target application. As a result, statistics such as the required RF size and FU utilisation can be obtained. This feedback drives light-weight refinement steps to maximise ASIP resource utilisation and performance.

Another interesting approach to the problem of efficient early exploration of system-level design was presented in the *Sesame* environment by Erbas et al. [33]. In their work, the authors proposed decoupling the architecture from the application resulting in two different models. First, the application model describes application behaviour in an architecturally independent fashion. This model is used to study the application behaviour and analyse the application performance requirements, such as computationally intensive tasks. While expressing functionality of the application, this model does not consider architectural issues, such as resource utilisation, timing characteristics, or bandwidth limits. Second, the platform architecture model defines architecture resources and their performance constraints. Putting these two together, the explicit mapping phase maps an application model onto the architecture model for co-simulation. In principle, the co-simulation is trace-driven. The simulation of application model produces the application events – the trace, and the architecture model simulates their timing consequences. Afterwards, system performance can be evaluated based on collected performance estimates, as well as utilisation characteristics of the processor components. Analysis of this evaluation can lead to architecture, application, or mapping changes.

Artes et al. [34] focused on the exploration of individual system components. The authors explored the design space of distributed loop buffers, discussed further in Section 4.6.2. The authors presented three implementations of the distributed loop buffers considering energy savings resulting from the use of loop buffer as well as a performance of application and area occupancy. By utilising a high-level energy estimation tool as well as energy models of the proposed loop buffer implementations, high-level trade-off analysis for a particular application is possible. Based on the results of the analysis, components of loop buffer implementation can be modified in terms of depth, width, as well as memory implementation technology to suit the particular needs of a specific application.

Overall, design-space exploration tools, either at system-level or component specific, allow for a fast multi-object analysis of designs consisting of components present in IP libraries with those specifically designed to improve a particular component of the system. Such an exploration can produce a set of viable designs worth low-level estimation or lead to the conclusion that current

component optimisation is insufficient and system designer needs to look further to achieve design goals. The Table 2.2 summarises briefly the exploration techniques discussed above.

**Table 2.2:** Summary of reported exploration techniques.

| Reference         | Exploration method                                              | Explored components  |

|-------------------|-----------------------------------------------------------------|----------------------|

| Ascia et al. [29] | Multiple strategies,<br>from clustering to genetic              | VLIW core and memory |

| Eusse et al. [32] | HLS and pre-architectural estimation feedback                   | ASIP core            |

| Erbas et al. [33] | application model and platform architecture model co-simulation | system level         |

| Artes et al. [34] | high-level energy estimate and energy model                     | loop buffers         |

# 3 Reducing Energy Demands of Register Files and Interconnection Network

The discussion presented in Chapter 2 has emphasised the importance of Register Files (RFs) and interconnection networks during optimisations for energy efficiency of embedded systems as well as the impact they have on the achievable computing performance.

This chapter briefly presents the problem of energy efficiency of RFs and interconnection networks and discusses multiple solutions for reducing their energy demands.

#### 3.1 Energy Demands of Register Files and Interconnection Networks

Registers, as storages of temporal data, are commonly used in designs of both Application-Specific Integrated Circuits (ASICs) and Application-Specific Instruction-Set Processors (ASIPs). In case of ASICs, the registers are placed between logical components to allow for different component latencies and pipelined computations, with designated connectivity between logical components. In case of ASIPs, the registers are typically grouped into a Register File (RF) and are reused in various stages of application execution as a means for storage of different temporal values used by multiple components of the processor. Since registers are reused by multiple components, it is also necessary to provide the corresponding connectivity to deliver temporal values where required. The popularity of multiple issue architectures with their ability to efficiently utilise available ILP [35] increases the requirements for the availability of registers and associated connectivity.

The number of registers in an RF and their requirement to be accessed by multiple components affect the computing performance, a complexity of the design, achievable frequency, and energy efficiency to great extent. Balfour et al. [36] argued that the energy consumption of processors is dominated by the communication and the data and instruction movement, not the actual computation on the FUs. As a consequence, embedded programmable processors such as ASIPs, even when designed for low-power, still consume more energy than a fixed function ASIC, where communication can be aggressively optimised. The authors argued that advances in semiconductor technology provide more benefit for computation in the FUs than in the RFs and transport buses for data and instruction delivery.

A direct utilisation of the VLIW paradigm and increasing the number of Function Units (FUs) to increase the achievable performance, as well as increasing the capacity of RFs to provide an adequate number of values to be processed in the FUs, also increases the demand for interconnection bandwidth. For example, as each FU requires two input values from the register, and writes a single result value to the register, the required number of ports to access the RF is three times the number of FUs. Such a worst-case scenario, however, happens only if all of the FUs are used simultaneously. The actual number of ports used varies during the application execution, depending on the ILP present in the application (see [10]). To put this observation into context,

in [24] the authors presented an energy model of multi-ported, centralised RF, and concluded that such a centralised solution to inter-instruction communication is prohibitively expensive when exploring available ILP for architectures capable of executing multiple Instructions Per Cycle (IPC).

In areas where energy efficiency is of fundamental importance, such as the design of embedded systems, attempting to achieve the required computing performance by providing more computational resources in form of additional FUs and RFs is, therefore, by itself infeasible. Achieving the required computing performance is possible by the addition of the FUs. The energy requirements of individual FUs add up, increasing the energy requirements with the number of added FUs. In order to effectively use all the added FUs, and the number of the registers in the RFs, the number of read and write ports must be increased resulting in significant increase in the required energy. With each added FU requiring two read and one write port as well as full connectivity, for example, interconnection complexity increases significantly resulting in a further increase in required energy.

This bottleneck, therefore, sets a limit on scaling for performance and exploitation of available ILP. Additionally, increasing the performance of VLIWs by adding FUs, as well as RFs and their ports, results in an increased power density of the RF and increased likelihood of *heat stroke* [37]. During a heat stroke, the temperature of a part of the chip exceeds the critical limit causing the processor to stop being cooled, stalling computation for an extensive amount of time and making the design useless without an expensive cooling mechanism and thus impractical for embedded systems.

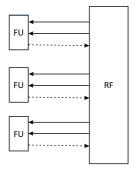

#### 3.1.1 Reducing Complexity of Hardware at the Expense of Software

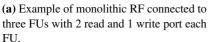

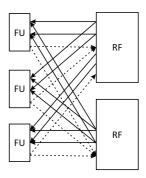

Often, the solution to the problem of energy consumption of RFs in the VLIW-based ASIP designs is to group registers into multiple clustered RFs, for lower costs of area and energy, with a limited number of read and write ports, as well as limited connectivity [38–41], as shown in Figure 3.1. The sum of the number of registers in individual RFs can be equal to or larger than the number of registers in the monolithic RF (shown in Figure 3.1a). Similarly, the total number of read and write ports in clustered RFs needs to match the number of ports of the original RF. However, to maintain the performance requirement of each FU being able to access any register, in the most naïve implementation, every single FU would need to be connected to each clustered RF, perhaps with multiple FUs sharing the RF port, as shown in Figure 3.1b, resulting in a great increase in interconnectivity.

Owing to such a separation of registers into multiple RFs, the task of the code generation subsystem for clustered VLIW becomes harder [42]. In order to avoid access port conflicts and resulting stalls, the compiler needs to assign values to multiple RFs in such a way that the sum of the register reads or writes in each individual RF in a single instruction is no more than the number of ports available in such an RF. If such an assignment is performed early, the instruction scheduling phase of code generation needs to take into account how the individual registers will be accessed by individual instructions, to prevent stalls. On the other hand, if the instruction scheduling is performed first, the assignment of variables used in instructions to individual registers and RFs needs to consider possible stalls as well. Therefore, this solution not only increases code generation complexity (giving an additional twist to know phase-ordering problem) but also impacts performance as compared to a single fully connected RF.

Taking this clustering approach further and focusing on connectivity, it is also possible to cluster interconnection network as shown in Figure 3.1c. Clustering an interconnection network results in a limited number of FUs forming computing clusters, accessing a clustered RFs. Such a separation

**(b)** Example of two RF clusters connected to three FUs with 2 read and 1 write port for each FU.

(c) Example of two RF clusters connected to two FUs clusters (two FUs and one FU) with 2 read and 1 write port for each FU and two connections between RFs.

**Figure 3.1:** Naïve example of monolithic RF (3.1a), clustered RF (3.1b), and clustered RF with two FU clusters (3.1c).

of RFs and FUs, while contributing to lowering the costs of area and energy, can also impact the available computing performance. Compilers need to produce a code that assigns transient values to the registers in the RF cluster, which is connected to the computing cluster, where the computation takes place. Unfavourable assignment leads to the required value in the RF being connected to the *wrong* computing cluster, resulting in the communication between computational clusters to transfer the value, possibly leading to a further stall in computation.

In the case where the transient variable is used multiple times as an input to computation in different computing clusters, such a clustering provides yet another challenge for code generation. In order to achieve the required performance without sacrificing area and energy efficiency, it is necessary to customise the clustering layout as well as the number of simultaneous accesses allowed to the RFs present in the clusters. Once such a customised layout is found, perhaps using exploration methods discussed in Chapter 2, further work is needed to improve the energy efficiency of execution in individual clusters.

One approach to improving efficiency, be it in the presence of a heavily clustered architecture or just a single cluster, is that of targeting RF accesses by better utilisation of the interconnection network. Routeing of the computation of one FU to the input of another FU allows skipping read from RF (possibly write as well). This approach of bypassing RF reads and writes, can be

characterised in multiple ways:

- What lifespan bypassed variables can have, discussed in Section 3.2.

- How is bypassing performed, discussed in Section 3.3.

- How are bypassing opportunities detected, discussed in Section 3.4.

- How is bypassing controlled, discussed in Section 3.5.

Finally, alternative methods to reduce the power consumption of the RF and interconnection networks are discussed in Section 3.6.

#### 3.2 Lifespan of Bypassed Variables

Before deciding how to implement the bypassing mechanism, it is important to consider the lifespan of a bypassed variable the time it remains available for use outside of the RF. Several aspects need to be taken into consideration. Firstly, what is the distance between the instruction which produces the value and the instruction which consumes such a value? Secondly, how many times is the produced value used? While a majority of the values produced during computations are of temporal nature, used only once, others can be used multiple times, spanning basic block boundaries, or be used as arguments of a function call. Finally, what is the number of values that can be bypassed simultaneously?

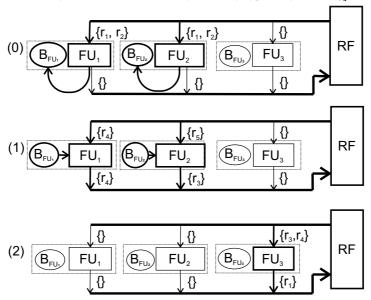

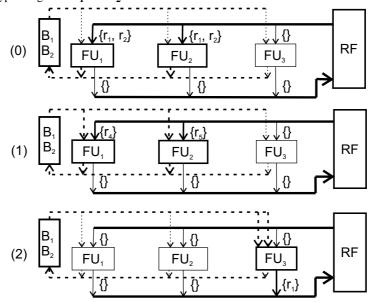

Synthetic examples in Figure 3.2 show several simple cases of bypassing, with Figure 3.2a demonstrating multiple bypassing opportunities. In the simple case, bypassing is only allowed for consecutive instructions, as shown in Figure 3.2b, with bypass of registers  $\mathbf{r_1}$  and  $\mathbf{r_5}$ . This brings the trade-off between utilising bypassing for saving power and scheduling freedom. In case the value is used only once, in addition to bypass read of RF, the write of RF is also skipped. In case the result value is used multiple times, the result value needs to be written into the RF. Depending on the implementation of bypassing, this can mean that the single use of a value gets bypassed and, at the same time, the value is written into the RF, or no bypass is possible at all, as shown in Figure 3.2b with register  $\mathbf{r_0}$ .

In more complex case, the distance between source and destination could be considerable. As a result, a bypassing mechanism needs to be more complex and allow the bypassed value to remain available for a considerable number of cycles. With a single bypass register, denoted as **B** in Figure 3.2b, even with the ability to retain the value of such register for more than a single cycle, only one value can be bypassed at any time. In order to bypass more than a single value, more bypassing registers are needed, as shown in Figure 3.2c. The presence of multiple bypass registers, in turn, requires some kind of an allocation method in a similar fashion as general-purpose register allocation does. Selecting a register with long live range for bypass, for example, prohibits the use of bypass for other registers during that live range.

In case the value to be bypassed is used multiple times, the implementation determines whether all the uses can be bypassed. As mentioned before, how many values can be bypassed simultaneously depends on the number of available bypassing registers, as shown in Figure 3.2c. Additionally, when the use of a bypassed value spans basic block boundaries or is used in a function call, in addition to bypassing, the value also needs to be written into the RF.

| add $\mathbf{r_0}, r_1, r_2$                   | add $\mathbf{r_0}, r_1, r_2$                       |

|------------------------------------------------|----------------------------------------------------|

| $\text{mul } \mathbf{r_5}, r_4, \mathbf{r_0}$  | $\operatorname{mul} \mathbf{B}, r_4, \mathbf{r_0}$ |

| add $\mathbf{r}_1, \mathbf{r}_5, \mathbf{r}_0$ | add $\mathbf{B}, \mathbf{B}, \mathbf{r_0}$         |

| $\text{mul } \mathbf{r_4}, \mathbf{r_1}, r_2$  | $\operatorname{mul} \mathbf{r_4}, \mathbf{B}, r_3$ |

| mul $r_5, r_2, r_3$                            | mul $r_5, r_2, r_3$                                |

| add $r_4, {\bf r_4}, r_3$                      | add $r_4, {\bf r_4}, r_3$                          |

(a) Example code with two bypassing opportunities for register  $\mathbf{r_0}$  and one for register  $\mathbf{r_5}$ ,  $\mathbf{r_4}$ , and  $\mathbf{r_1}$  respectively.

(b) Example code with bypass (denoted as register B) of register  $r_5$  and  $r_1$ . Bypassing of register  $r_0$  is skipped due to multiple uses and register  $r_4$  due to distance.

```

add B_1, r_1, r_2

mul B_2, r_4, B_1

add B_1, B_2, B_1

mul B_2, B_1, r_3

mul r_5, r_2, r_3

add r_4, B_2, r_3

```

(c) Example code with bypass (denoted as registers  $B_1$  and  $B_2$ ) of registers  $\mathbf{r}_5$ ,  $\mathbf{r}_1$ , multiple uses of  $\mathbf{r}_0$  and longer distance of  $\mathbf{r}_4$ .

Figure 3.2: Example of multiple result use and bypassing opportunities on Figure 3.2a, bypass of single use values utilising single bypass register  $\bf B$  on Figure 3.2b, and utilising multiple bypass registers  $\bf B_1$ ,  $\bf B_2$  with multiple uses on Figure 3.2c.

#### 3.3 Performing Bypassing

Once the decision on the desired lifespan and multiplicity of bypasses is reached, further aspects need to be considered. In principle, in order to perform a bypass, the underlying hardware must have the ability to do so and opportunities for bypass need to be identified. Afterwards, the most suitable candidates can be selected and bypassing implementation of instructed to perform the bypass.

The methods of bypassing can be broadly classified into three different categories, depending on the interaction between code generation and hardware execution:

- In the first method, bypassing is performed by using a designated connection circuitry, without the interference from the code generation and routeing the result of one operation to the input of another operation, or multiple operations, directly using a bypassing network [36].

- In the second method, detection of bypassing opportunities during code generation is combined with hardware during execution for recognising those opportunities and routeing bypassed values through a designated bypassing network [43].

- The third method is based purely on code generation, where the compiler detects bypassing opportunities and instructs hardware directly on how to perform bypasses [19, 44], [P1], [P2], and [P3].

Regardless of the used method, there are two fundamental options to implement bypassing. Bypasses can be performed exclusively on a single FU [36], where only a previous output of the

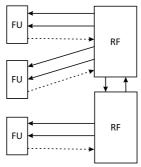

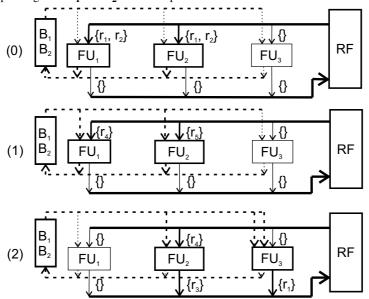

| $FU_1$                                                    | $FU_2$                                                    | $FU_3$              | cycle |

|-----------------------------------------------------------|-----------------------------------------------------------|---------------------|-------|

| add $\mathbf{B}_{\mathbf{FU_1}}, r_1, r_2$                | sub $\mathbf{B}_{\mathbf{FU_2}}, r_1, r_2$                |                     | (0)   |

| $\operatorname{mul} \mathbf{r_4}, r_4, \mathbf{B_{FU_1}}$ | $\operatorname{mul} \mathbf{r_3}, r_5, \mathbf{B_{FU_2}}$ |                     | (1)   |

|                                                           |                                                           | div $r_1, r_4, r_3$ | (2)   |

(a) Code example of bypassing a result of the computation to the input on single  $FU_1$  and  $FU_2$  and combining them in  $FU_3$  over three cycles using bypass registers  $\mathbf{B}_{\mathbf{FU}_x}$ .

(b) Example of bypassing a result of the computation to the input on single  $FU_1$  and  $FU_2$  and combining them in  $FU_3$  over three cycles using FU specific bypass registers  $\mathbf{B}_{\mathbf{F}\mathbf{U}_x}$ .

Figure 3.3: Simple example of bypassing a result of the computation on a single FU using FU specific bypass registers  $B_{FU_x}$ .

calculation of the FU can be used as an input to the later computation. Figure 3.3 shows an example of bypassing a single FU. Alternatively, bypasses can be also performed between different FUs, where the output of the computation on one FU can be used as an input to the computation on a different FU. Figure 3.4 shows an example of bypassing between different FUs [19]. Somehow, the specific case of bypassing between different FUs is a situation where the result of a single FU calculation can be bypassed as an operand to multiple FUs. Figure 3.5 shows an example of bypassing single results to multiple FUs.

#### 3.3.1 Performing Bypassing Fully in Hardware