Jari Nikara

# **Application-Specific Parallel Structures for Discrete Cosine Transform and Variable Length Decoding**

| Tampereen teknillinen yliopisto. Julkaisu 481 Tampere University of Technology. Publication 481                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                            |

| Jari Nikara                                                                                                                                                                                                                                |

| Application-Specific Parallel Structures for Discrete Cosine Transform and Variable Length Decoding                                                                                                                                        |

| Thesis for the degree of Doctor of Technology to be presented with due permission for public examination and criticism in Tietotalo Building, Auditorium TB104, at Tampere University of Technology, on the 18th of June 2004, at 12 noon. |

|                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                            |

| Tampereen teknillinen yliopisto - Tampere University of Technology Tampere 2004                                                                                                                                                            |

### **ABSTRACT**

This Thesis considers the design of application-specific parallel structures for digital signal processing. Due to wideness of the subject, the discussion has been restricted to the studies of the discrete cosine transform and variable length decoding.

New area-efficient parallel structures, which process data in a sequential form at data rate, are developed for the discrete cosine transform. The development of the structures begins with the derivation of novel regular fast algorithms. The algorithms lend themselves for vertical mapping resulting in modular cascaded structures that can be freely pipelined due to the loop-free structure. In order to prove the feasibility and estimate the performance, the unified transform kernel for discrete cosine transform and its inverse is implemented on a standard cell CMOS technology with a data path synthesis. Finally, the comparison to a state-of-the-art design reveals up to 15% smaller estimated area than in the reference design.

For the variable length decoding, a novel multiple-symbol decoding scheme is proposed. The critical path of the resulting decoder is minimized by introducing a new multiplexed add unit. In order to prove the feasibility and determine the limiting factors of the scheme, the decoder has been implemented on an FPGA technology. When applied to MPEG-2 standard benchmark scenes, on average 4.8 codewords are decoded per cycle resulting in the throughput of 106 million symbols per second. Although, a straightforward and fair comparison of variable length decoders is extremely difficult due to different implementation approaches, the performance of the decoder can be considered promising with 16–100 % better throughput at 2–3.6 times lower frequencies than the reference designs on the same FPGA technology.

In both the case studies, the discrete cosine transform and variable length decoding, the modularity and achievable high speed operation provide flexibility for the design re-use in the current and future applications.

### **PREFACE**

This research work has been carried out during the years 2000 - 2004 at the Institute of Digital and Computer Systems, former Digital and Computer Systems Laboratory, of Tampere University of Technology, Tampere, Finland as a part of the wider related research projects of which one included a one-year visit to Computer Engineering Laboratory, Delft University of Technology, Delft, The Netherlands.

I am grateful to my supervisors, Prof. *Jarmo Takala* and Prof. *Stamatis Vassiliadis*, for guiding and encouraging me to study and work towards doctoral degree. Furthermore, my sincere thanks to my Thesis reviewers, Prof. *Olli Silven* and Prof. *Jorma Skyttä*, for their constructive comments on the manuscript. Special thanks to *Tuomas Järvinen*, M.Sc., *Perttu Salmela*, M.Sc., Mr. *Harri Sorokin*, *Vesa Lahtinen*, M.Sc., *Georgi Kuzmanov*, M.Sc., for sharing ideas, knowledge, and opinions about those various different topics related, more or less if at all, to this Thesis.

I would like to thank all the co-authors: Prof. *David Akopian*, *Mihai Sima*, M.Sc., *Petri Liuha*, M.Sc., Prof. *Jaakko Astola*, *Jukka Saarinen*, Dr. Tech., *Konsta Punkka*, M.Sc.. In addition, *Rami Rosendahl*, M.Sc., deserves special thanks for co-operation. My warmest thanks to personnel in Tampere and Delft for nice working atmosphere.

This Thesis was financially supported by the Graduate School in Electronics, Tele-communications, and Automation (GETA), Academy of Finland, National Technology Agency (TEKES), Nokia Foundation, Jenny and Antti Wihuri Foundation, Ulla Tuominen Foundation, and the Foundation of Advancement of Technology, which are gratefully acknowledged.

Finally, I would like to express my gratitude to my parents *Erkki* and *Marjatta Nikara*, sisters *Virpi* and *Kirsi*, and my wife *Anu* for their support and love during these years.

Tampere, May 2004

Jari Nikara

iv Preface

# TABLE OF CONTENTS

| At  | stract  |                                     | i |

|-----|---------|-------------------------------------|---|

| Pre | eface   |                                     | i |

| Ta  | ble of  | Contents                            | V |

| Lis | st of P | Publications                        | X |

| Lis | st of F | igures                              | i |

| Lis | st of T | Tables                              | V |

| Lis | st of A | Abbreviations                       | i |

| Lis | st of S | Symbols                             | i |

| 1.  | Intro   | oduction                            | 1 |

|     | 1.1     | Objective and Scope of Research     | 3 |

|     | 1.2     | Main Contributions                  | 4 |

|     |         | 1.2.1 Author's Contribution         | 5 |

|     | 1.3     | Thesis Outline                      | 6 |

| 2.  | Disc    | rete Cosine Transform               | 7 |

|     | 2.1     | Definitions and Properties          | 8 |

|     | 2.2     | One-Dimensional Fast Algorithms     | 9 |

|     |         | 2.2.1 Well-Known Pioneer Algorithms | О |

|     |         | 2.2.2 Regular Algorithms            | 2 |

|     | 2.3     | Two-Dimensional Algorithms          | 5 |

|     | 2.4     | Hardware Structures                 | 8 |

|    |       | 2.4.1     | One-Dimensional Structures                       | 19 |

|----|-------|-----------|--------------------------------------------------|----|

|    |       | 2.4.2     | Two-Dimensional Structures with Matrix Transpose | 21 |

|    |       | 2.4.3     | Direct Two-Dimensional Structures                | 25 |

|    | 2.5   | Summa     | ary                                              | 27 |

| 3. | Perfe | ect Shuf  | fle Topology DCT Algorithms                      | 29 |

|    | 3.1   | Prelim    | inaries                                          | 29 |

|    | 3.2   | One-D     | imensional Transform                             | 35 |

|    |       | 3.2.1     | Processing Columns                               | 37 |

|    |       | 3.2.2     | Interconnection Permutations                     | 38 |

|    |       | 3.2.3     | Final Algorithm                                  | 41 |

|    | 3.3   | Two-D     | imensional Transform                             | 43 |

|    |       | 3.3.1     | Row-Column Decomposition                         | 43 |

|    |       | 3.3.2     | Direct Computation                               | 45 |

|    | 3.4   | Summa     | ary                                              | 48 |

| 4. | Pipe  | line Stru | actures for Perfect Shuffle Topology DCT         | 49 |

|    | 4.1   | Basic I   | Processing Units                                 | 49 |

|    | 4.2   | Basic I   | Permutation Units                                | 52 |

|    | 4.3   | Final S   | Structures                                       | 54 |

|    | 4.4   | Case S    | tudy: Unified DCT and IDCT                       | 57 |

|    |       | 4.4.1     | Algorithms and Structures                        | 57 |

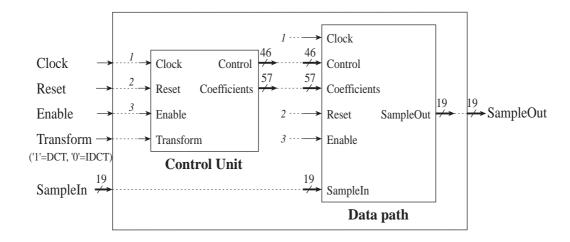

|    |       | 4.4.2     | Implementation of Direct 8 × 8 DCT/IDCT          | 61 |

|    | 4.5   | Summa     | ary                                              | 64 |

| 5. | Varia | able Len  | ngth Coding                                      | 67 |

|    | 5.1   | Definit   | ions and Properties                              | 67 |

|    | 5.2   | Variah    | le Length Decoders                               | 70 |

|    |       | 5.2.1    | Serial Decoders            | 71 |

|----|-------|----------|----------------------------|----|

|    |       | 5.2.2    | Parallel Decoders          | 73 |

|    |       | 5.2.3    | Multiple-Symbol Decoders   | 78 |

|    | 5.3   | Summa    | ary                        | 82 |

| 6. | Varia | able Len | ngth Decoding Scheme       | 85 |

|    | 6.1   | Algorit  | thm                        | 85 |

|    |       | 6.1.1    | Decoding Example           | 88 |

|    | 6.2   | Genera   | al Structure               | 89 |

|    |       | 6.2.1    | Decoder example            | 92 |

|    | 6.3   | Critical | l Path                     | 93 |

|    | 6.4   | Summa    | ary                        | 94 |

| 7. | MPE   | EG-2 Vai | riable Length Decoding     | 95 |

|    | 7.1   | Overvi   | ew to MPEG-2 Standard      | 95 |

|    | 7.2   | Decode   | er Specification           | 96 |

|    | 7.3   | Hardw    | are Model                  | 97 |

|    |       | 7.3.1    | Codeword Detector          | 98 |

|    |       | 7.3.2    | Chrominance Format Counter | 98 |

|    |       | 7.3.3    | Multiplexed Add            | 99 |

|    |       | 7.3.4    | Memory Address Generator   | 99 |

|    |       | 7.3.5    | Symbol Fetch               | 01 |

|    |       | 7.3.6    | Entire Decoder             | 01 |

|    | 7.4   | Experi   | mental Results             | 03 |

|    | 7.5   | Discus   | sion and Comparison        | 06 |

|    |       | 7.5.1    | Reference Decoders         | 07 |

|    |       | 7.5.2    | Comparison Results         | 09 |

|    | 7.6   | Summa    | ary                        | 11 |

| viii | Table of Contents |     |

|------|-------------------|-----|

|      |                   |     |

| 8.   | Conclusions       | 113 |

| Bi   | bliography        | 115 |

### LIST OF PUBLICATIONS

This Thesis is a monograph which contains some unpublished material. However, the thesis is based on the work already published during the research studies in the following international publications. In the text, these publications are referred to as [P1], [P2], ..., [P7].

- [P1] J. Nikara, J. Takala, D. Akopian, J. Astola, and J. Saarinen, "Sequential architecture for discrete cosine transform," in *Proceedings of the 18th NORCHIP Conference*, Turku, Finland, Nov. 6–7 2000, pp. 53–58.

- [P2] J. Nikara, J. Takala, D. Akopian, and J. Saarinen, "Pipeline architecture for DCT/IDCT," in *Proceedings of the IEEE International Symposium on Circuits and Systems*, vol. 4, Sydney, Australia, May 6–9 2001, pp. 902–905.

- [P3] J. Nikara and J. Takala, "Unified pipeline architecture for in-order 8x8 DCT and IDCT," in *Proceedings of the 5th World Multiconference in Systemics, Cybernetics, and Informatics*, vol. 4, Orlando, FL, U.S.A., July 22–25 2001, pp. 30–35.

- [P4] J. Takala, J. Nikara, and K. Punkka, "Pipeline architecture for two-dimensional discrete cosine transform and its inverse," in *Proceedings of the 9th IEEE International Conference on Electronics, Circuits and Systems*, vol. 3, Dubrovnik, Croatia, Sept. 15–18 2002, pp. 947 950.

- [P5] J. Nikara, S. Vassiliadis, J. Takala, M. Sima, and P. Liuha, "Parallel multiple-symbol variable-length decoding," in *Proceedings of the IEEE International Conference on Computer Design*, Freiburg, Germany, Sept. 16–18 2002, pp. 126–131.

- [P6] J. Nikara, S. Vassiliadis, J. Takala, and P. Liuha, "FPGA-based variable length decoders," in *Proceedings of the IFIP WG 10.5 International Con-*

- ference on Very Large Scale Integration of System-on-Chip, Darmstadt, Germany, Dec.  $1-3\ 2003$ , pp. 437-441.

- [P7] J. Nikara, S. Vassiliadis, J. Takala, and P. Liuha, "Multiple-symbol parallel decoding for variable length codes," to appear in *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 12, no. 7, July 2004.

# LIST OF FIGURES

| 1  | Signal flow graph to compute the DCT via real parts of the DFT               | 10 |

|----|------------------------------------------------------------------------------|----|

| 2  | Signal flow graph of the DCT based on the sparse matrix factorization        | 11 |

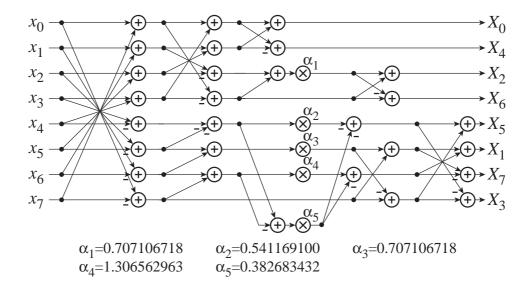

| 3  | Signal flow graph of the DCT based on the rotations                          | 12 |

| 4  | Signal flow graph of the in-place DCT with separated irregularities .        | 13 |

| 5  | Signal flow graph of the in-place DCT with distributed irregularities        | 14 |

| 6  | Signal flow graph of the constant geometry DCT algorithm                     | 15 |

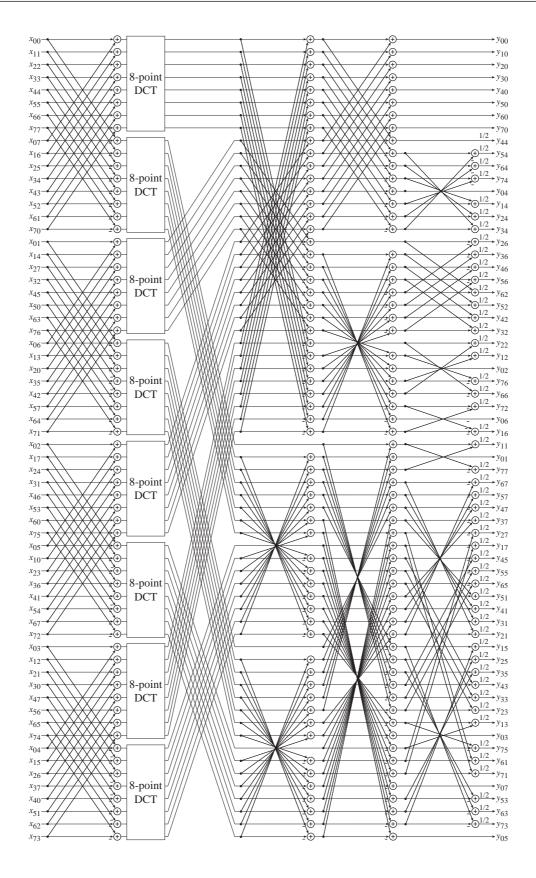

| 7  | Signal flow graph of the direct $8 \times 8$ DCT by utilizing an 8-point DCT | 17 |

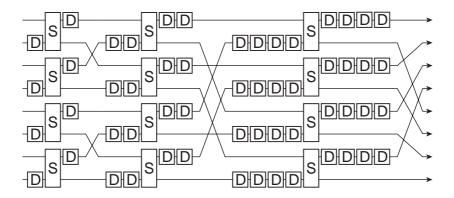

| 8  | Block diagram of the pipeline structure with double buffering                | 19 |

| 9  | Block diagram of the fully sequential DCT pipeline                           | 21 |

| 10 | Register-based matrix transpose network by using double buffering .          | 22 |

| 11 | Block diagrams of the basic switching units                                  | 22 |

| 12 | Example of the iterative $8 \times 8$ matrix transpose                       | 23 |

| 13 | Block diagram of the column parallel $8 \times 8$ matrix transpose           | 24 |

| 14 | Block and timing diagrams of the sequential matrix transpose                 | 25 |

| 15 | Block diagram of the $8\times 8$ DCT/IDCT with matrix transpose              | 26 |

| 16 | Block diagram of the fully sequential $8 \times 8$ direct DCT                | 27 |

| 17 | Simplification of the interconnection permutation                            | 39 |

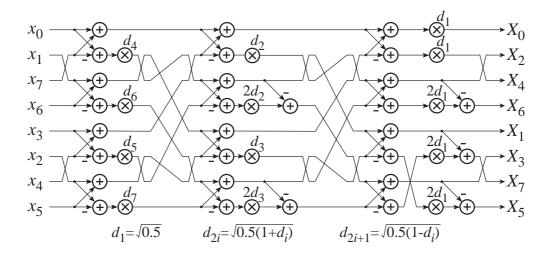

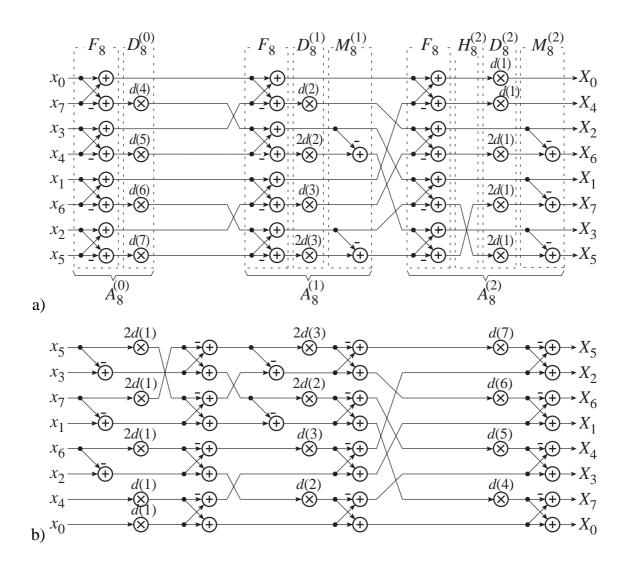

| 18 | Signal flow graph of the regular perfect shuffle topology DCT                | 43 |

| 19 | Signal flow graph of the regular perfect shuffle topology $8 \times 8$ DCT   | 47 |

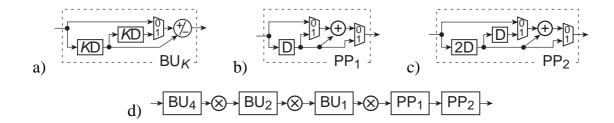

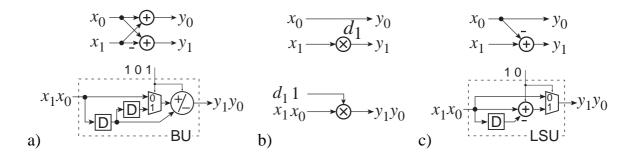

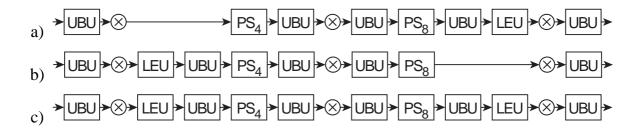

| 20 | Block diagrams of the basic data processing units                            | 50 |

| 21 | Unified butterfly unit                                                      | 51 |

|----|-----------------------------------------------------------------------------|----|

| 22 | Direct two-dimensional butterfly unit                                       | 52 |

| 23 | Block diagrams of the basic data permutation units                          | 53 |

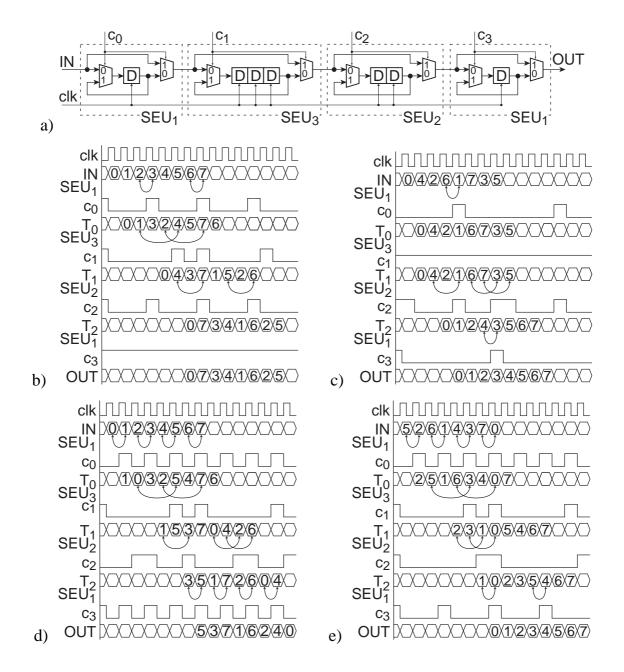

| 24 | Sequential matrix transpose network for $2^k \times 2^k, k \leq 3$ , matrix | 54 |

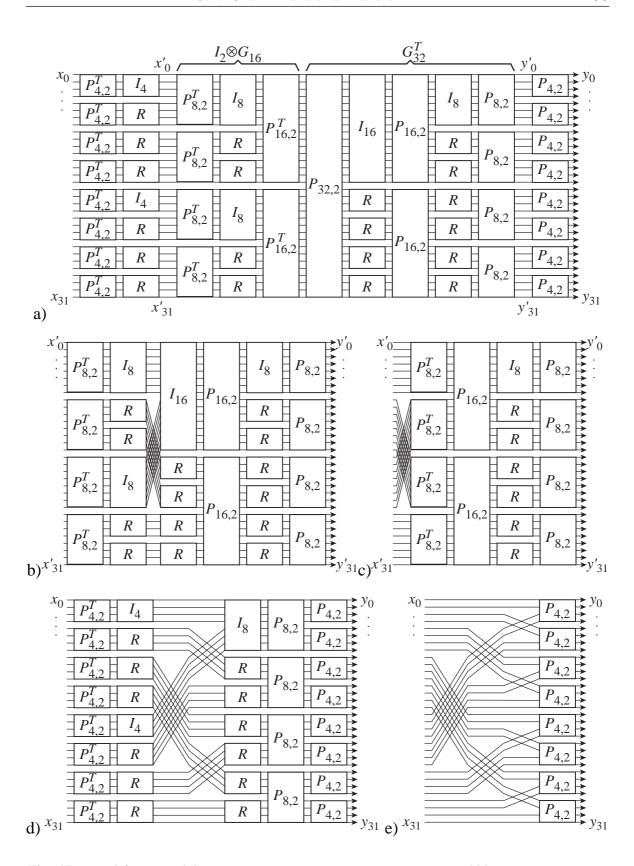

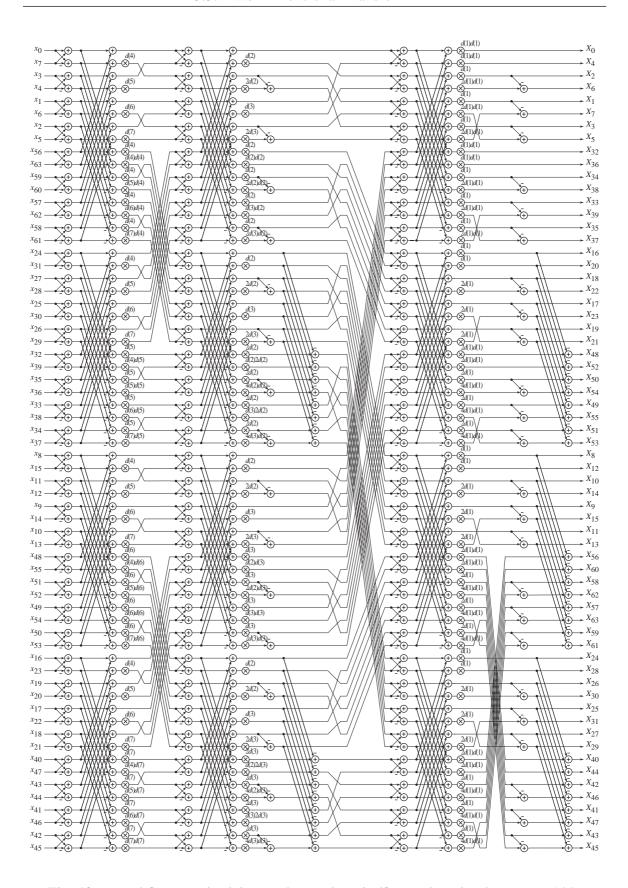

| 25 | Pipeline structures for regular perfect shuffle topology DCT                | 56 |

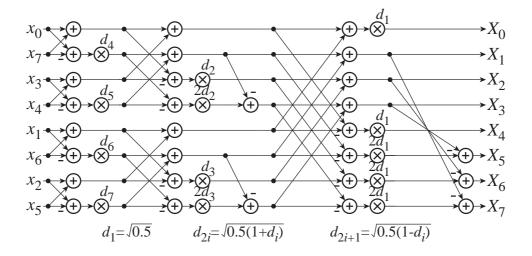

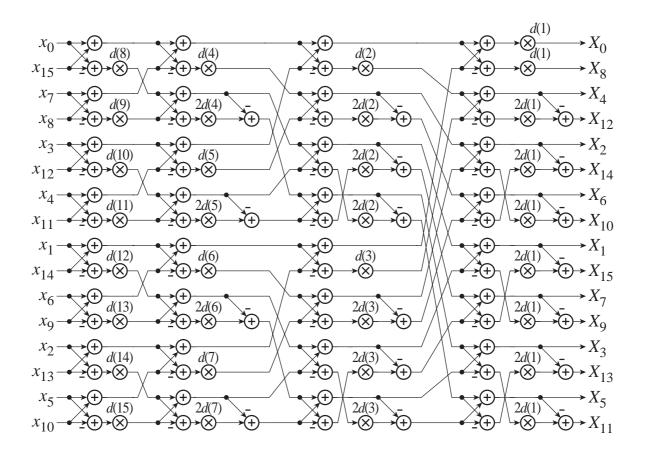

| 26 | Signal flow graphs of the 8-point DCT and IDCT                              | 58 |

| 27 | Block diagrams of the 8-point DCT kernels                                   | 59 |

| 28 | Unified input/output permutation network                                    | 60 |

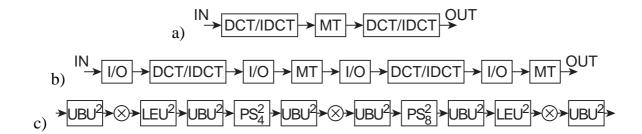

| 29 | Block diagrams of the unified two-dimensional DCT/IDCT                      | 61 |

| 30 | Block diagram of the verification environment of the DCT/IDCT $$ . $$       | 63 |

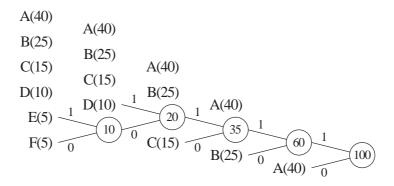

| 31 | Example of the Huffman coding                                               | 69 |

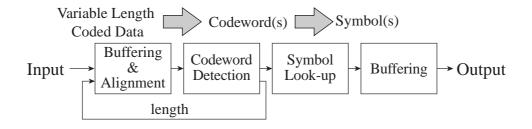

| 32 | Block diagram of the generalized variable length decoding                   | 71 |

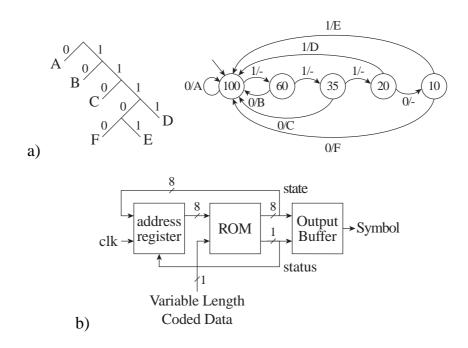

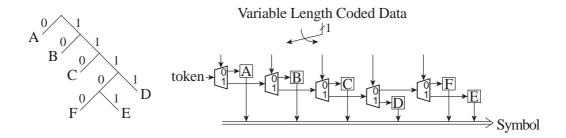

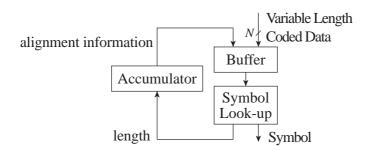

| 33 | Variable length decoding as a finite-state machine                          | 72 |

| 34 | Direct mapping of the VLD onto demultiplexers and storage locations         | 73 |

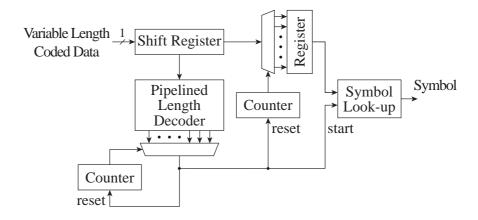

| 35 | Block diagram of the parallel constant output rate decoder                  | 74 |

| 36 | Block diagram of the loop-free parallel decoder                             | 75 |

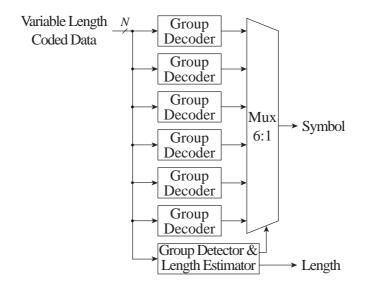

| 37 | Block diagram of the parallel group-based decoder                           | 77 |

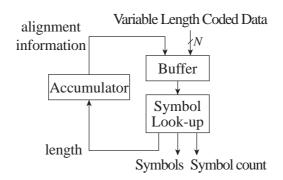

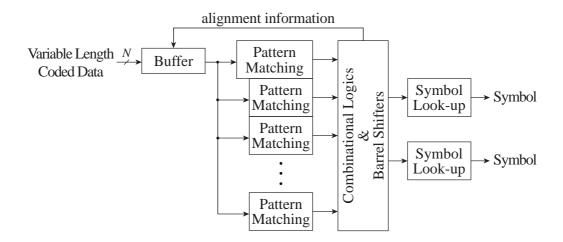

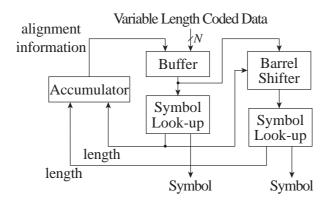

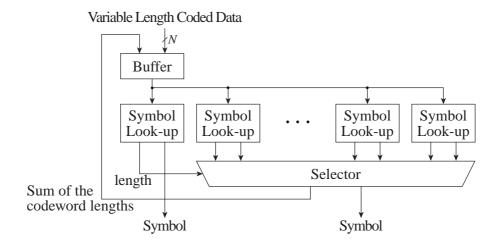

| 38 | Block diagram of the variable I/O rate multiple-symbol decoder              | 79 |

| 39 | Block diagram of the group-based multiple-symbol decoder                    | 80 |

| 40 | Block diagram of the 2-symbol decoder with an additional shifter            | 80 |

| 41 | Block diagram of the 2-symbol decoder with parallel symbol look-ups         | 81 |

| 42 | Block diagram of the 2-symbol decoder with length prediction                | 82 |

| 43 | Principle of the proposed variable length decoding scheme                   | 90 |

| 44 | Block diagram of the generalized codeword detection                         | 90 |

| 45 | Block diagram of the 8-to-1 multiplexed add unit                            | 91 |

|    | List of Figures                                        | XIII |

|----|--------------------------------------------------------|------|

|    |                                                        |      |

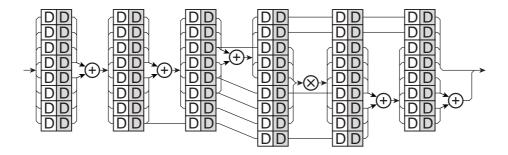

| 46 | Principal structure of entire variable length decoder  | 92   |

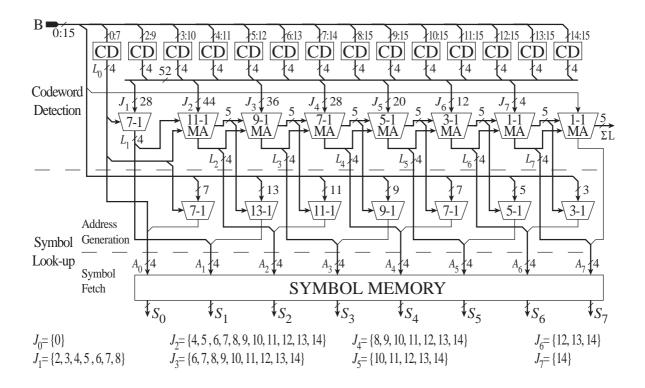

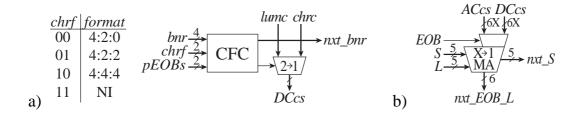

| 47 | Block diagram of the MPEG-2 modified codeword detector | 98   |

| 48 | Block diagrams of the MPEG-2 specific units            | 99   |

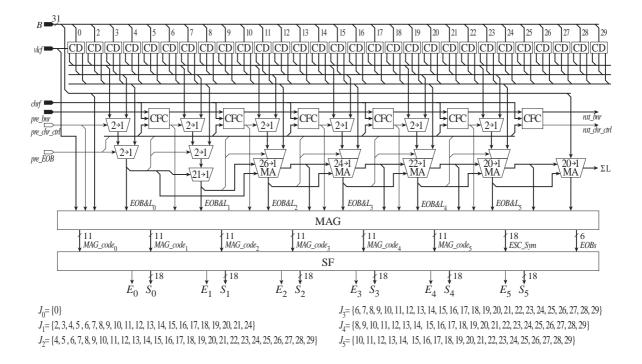

| 49 | Block diagram of the MPEG-2 variable length decoder    | 102  |

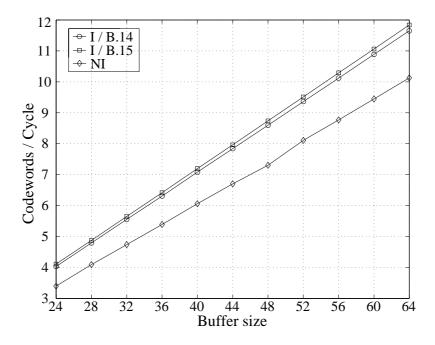

| 50 | Throughput of the proposed approach                    | 104  |

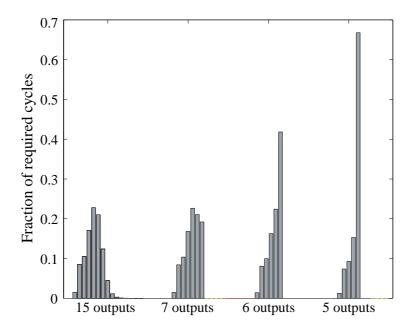

| 51 | Distribution of symbols over the decoder outputs       | 105  |

# LIST OF TABLES

| 1  | Characteristics of the $8 \times 8$ DCT/IDCT pipeline implementation | 62  |

|----|----------------------------------------------------------------------|-----|

| 2  | Comparison of the $8 \times 8$ DCT/IDCT structures                   | 63  |

| 3  | Gate count estimates for the basic units                             | 64  |

| 4  | Comparison of the fully sequential unified DCT/IDCT pipelines        | 64  |

| 5  | Summary of the Huffman coding example                                | 69  |

| 6  | Variable length decoding example                                     | 89  |

| 7  | Properties of the MPEG-2 benchmark scenes                            | 97  |

| 8  | Memory address generation in the demonstration implementation        | 100 |

| 9  | Experimental results of the MPEG-2 variable length decoder           | 106 |

| 10 | Characteristics of the MPEG-2 variable length decoder                | 107 |

| 11 | Comparison of the FPGA-based variable length decoders                | 110 |

### LIST OF ABBREVIATIONS

ACM Association for Computing Machinery

AO And-Or

ASIC Application-Specific Integrated Circuit

ASIP Application-Specific Instruction-set Processor

BU Butterfly Unit

CCITT the International Telegraph and Telephone Consultative Commit-

tee

CD Codeword Detector

CFC Chrominance Format Counter

CLA Carry Look-Ahead

CLB Configurable Logic Block

CMOS Complementary Metal Oxide Semiconductor

CW Codeword

D Delay register

DCT Discrete Cosine Transform

DFT Discrete Fourier Transform

DHT Discrete Hartley Transform

DIF Decimation-In-Frequency

DIT Decimation-In-Time

DHT Discrete Hartley Transform

DRU Data Reordering Unit

DSD Delay-Switch-Delay unit

DSP Digital Signal Processor

DWHT Discrete Walsh-Hadamard Transform

EOB End-Of-Block

FFT Fast Fourier Transform

FPGA Field Programmable Gate Array

FSM Finite-State Machine

IDCT Inverse Discrete Cosine Transform

IDRU Inverse Data Reordering Unit

IEC International Electrotechnical Commission

IEE the Institution of Electrical Engineers

IEEE the Institute of Electrical and Electronics Engineers

IEICE the Institute of Electronics, Information and Communication En-

gineers

I/O Input/Output

IRE Institute of Radio Engineers

ISO International Organization for Standardization

ITU International Telecommunication Union

ITU-T the ITU Telecommunication Standardization Sector

JPEG Joint Photographic Experts Group

LEU Local Exchange Unit

LIFO Last-In-First-Out

LSB Least Significant Bit

LSU Local Subtraction Unit

LUT Look-Up Table

M Multiplexer

MA Multiplexed Add

MAG Memory Address Generator

MPEG Moving Picture Experts Group

MSB Most Significant Bit

MT Matrix Transpose

MVM Matrix-Vector Multiplier

PLA Programmable Logic Array

PP Post-Processor

PU Post-processing Unit

PS Perfect Shuffle

RAM Random Access Memory

ROM Read Only Memory

S Switch

SEU Shift-Exchange Unit

SF Symbol Fetch

SoC System on Chip

UBU Unified Butterfly Unit

VHDL VHSIC Hardware Description Language

VHSIC Very High Speed Integrated Circuit

VLC Variable Length Coding

VLD Variable Length Decoding

VLSI Very Large Scale Integration

WSES World Scientific and Engineering Academy and Society

### LIST OF SYMBOLS

### Discrete Cosine Transform

$C_N^{i}$  discrete cosine transform matrix of type i of order N

N input sequence size

$b_m$  DCT scaling factor of mth output

$I_N$  identity matrix of order N

$\bar{I}_N$  anti-diagonal identity matrix of order N

$P_N$  permutation matrix of order N

$P_{N,R}$  stride-by-R permutation matrix of order N

X sample vector

$x_i$  ith sample value

$P_N^H$  Hadamard permutation matrix of order N

$h_N(\cdot)$  Hadamard permutation function for N-point vector

$J_N$  J permutation matrix of order N

$F_N$  radix-2 butterfly matrix of order N

$D_N^*$  DCT scaling matrix of order N

$d(\cdot)$  DCT coefficient function of order N

$C_N^{(0)}$  Hadamard ordered DCT matrix

$M_N^{(s)}$  local subtraction matrix of order N of sth processing column

| List of Symbols | List | of S | Sym | bols | S |

|-----------------|------|------|-----|------|---|

|-----------------|------|------|-----|------|---|

| X | Y | ı | ı |

|---|---|---|---|

| $D_N^{(s)}$           | DCT coefficient matrix of order N of sth processing column                                        |

|-----------------------|---------------------------------------------------------------------------------------------------|

| $A_N^{(s)}$           | sth processing column matrix of order $N$                                                         |

| $U_N^{(s)}$           | output permutation matrix of order $N$ of the $s$ th processing column                            |

| $V_N^{(s)}$           | input permutation matrix of order $N$ of the $s$ th processing column                             |

| $\mu_n(\cdot)$        | binary-valued parametrization function to unify representation of<br>the processing columns       |

| $H_N^{(s)}$           | local exchange matrix of order $N$ of the $s$ th processing column                                |

| $	au_i(\cdot)$        | binary-valued parametrization function to unify representation of<br>the DCT coefficient matrices |

| $C_{N 	imes N}$       | two-dimensional DCT transform matrix of order $N^2$                                               |

| $P_N^O$               | output permutation matrix of order $N$                                                            |

| $K_N$                 | DCT kernel matrix of order N                                                                      |

| $P_N^I$               | input permutation matrix of order N                                                               |

| $A_{N 	imes N}^{(s)}$ | sth processing column matrix of order $N^2$                                                       |

| $D_{N	imes N}^{(s)}$  | DCT coefficient matrix of order $N^2$ of the sth processing column                                |

| $P_{N	imes N}^{I}$    | input permutation matrix of order $N^2$                                                           |

|                       |                                                                                                   |

| $P_{N 	imes N}^O$     | output permutation matrix of order $N^2$                                                          |

# Variable Length Decoding

| $S_k$ | kth symbol                             |

|-------|----------------------------------------|

| $p_k$ | probability of the symbol $s_k$        |

| S     | set of symbols                         |

| Н     | entropy                                |

| Ck    | codeword for the symbol s <sub>k</sub> |

$l_k$  length of the codeword  $c_k$

$l_{av}$  average codeword length

$c_i^k$  ith code symbol of the codeword  $c_k$

L set of codeword lengths

$l_{min}$  minimum codeword length

$l_{max}$  maximum codeword length

$d_{max}$  maximum number of codewords with equal length

X input data stream

$x_i$  ith input data stream element

B sliding window over input data stream

$b_i$  ith data element in the sliding window

*idx* index to the first undecoded bit in the input data stream

N length of the sliding window

M maximum number of the codewords in the sliding window

$W_i$  ith codeword in the sliding window

$L_i$  length of the *i*th codeword in the sliding window

$j_i$  index to starting location of the *i*th codeword in the sliding win-

dow

$J_i$  set of possible starting points for the *i*th codeword in the sliding

window

J set of possible starting points for the codewords in the sliding

window

$m_i$  codeword length at position i in the sliding window

$A_i$  index to symbol table for *i*th codeword in the sliding window

| List of Symbols              |  |

|------------------------------|--|

|                              |  |

| delay of 3-4 AND-OR          |  |

| delay of the multiplexer     |  |

| delay of the multiplexed add |  |

codeword table parameter

xxiv

τ

$t_M$

$t_{MA}$

T

### 1. INTRODUCTION

In general, advances in technologies allow the implementation of more complex systems. On the other hand, they also encourage engineers to design complex systems requiring advanced solutions and technologies. Likewise, the development creates new markets for several novel systems. As a result, the amount of all kind of information processing is increasing around us all the time. Consequently, more computational power—more speed is required in future [24]. However, the cost of design is the greatest threat to continuation of the semiconductor roadmap [46]. Therefore, the main issue is to support real-time applications with making, however, the compromise between performance and cost.

History has proven the cyclic behaviour between hardware and software implementations of signal processing applications [85]. While an application is implemented initially on software, its first real-time implementation requires typically application-specific hardware. Later, the advances in technology make the software implementation again possible. At that time, however, newer and more aggressive algorithms have been studied, causing the cycle to repeat itself.

The main advantage of software implementations is flexibility; modifications on the functionality can be realized by re-programming without physical changes on hardware. Therefore, the software implementations are often preferred. On software, however, there is always some overhead due to instruction fetch, instruction decode, and perhaps inappropriate instruction set. In addition, different data and processing rates require buffering of data. All these facts imply either reduced speed, increased area, or power consumption. Altogether, the software implementation is always a trade-off between flexibility, speed, area, and power consumption. Despite of the rapid advances in processor architectures and integrated circuit technologies, there are always applications requiring higher performance than provided by a state-of-the-art programmable processor at reasonable cost.

In general, higher performance can be achieved by exploiting parallelism. The resulting increased costs are kept reasonable by adding just some application-specific features, i.e., special instructions or even customized functional units on hardware, as done in digital signal processors (DSP). Another approach is application-specific instruction-set processors (ASIP), where the instruction-set and hardware are tailored according to the requirements of the given application. Customization level in ASIPs varies on three architectural levels depending on the approach: instruction extension, inclusion or exclusion of predefined blocks, and parametrization of cache sizes, number of registers, etc. [32]. One actively studied solution nowadays is reconfigurable computing, which achieves potentially higher performance than software but adopts a higher level of flexibility than hard-wired hardware. The reconfigurable systems contain usually a general-purpose processor managing data-dependent control and possible memory accesses, while the computational tasks are mapped onto the reconfigurable hardware [18]. The extreme level of customization is represented by application-specific integrated circuits (ASIC) based on standard cell or full custom design, which are designed to perform only specified computation with very limited control.

All the previously discussed approaches offer distinct advantages and drawbacks in applications. Therefore, there is no single ultimate solution suitable for all possible design cases but they are exploited as combinations. Furthermore, when considering the hardware design its abstraction level has changed from logic design via standard cell design to block based design and there seems to be no sign to end of this trend—systems keep on becoming more and more complex. The number of processing units will increase while the overall gate count for custom logic is decreasing [32]. This arises a demand for packing know-how into intellectual property (IP) blocks which may be re-used. This ongoing change introduces two major problems: where to get the components from, and how to verify that they work together as desired [71].

Although the systems have become more complex, the life cycles of applications have shortened due to rapid advances in technologies and various applications. This implies less time for the design and test and thus, emphasizes flexibility for the design re-use. The flexibility enables covering a wide range of applications. E.g., the structure with achievable high-speed operation covers high data rate applications but it can be also exploited as a shared resource in low data rate applications. Simple interfaces and control make the structure easy to integrate into larger systems, e.g., as an

accelerator in parallel with the DSP, building block of the ASIP, or configurable unit in a reconfigurable system. In any case, due to the cyclic behaviour between hardware and software implementations, acceleration with application-specific hardware, and changes in abstraction level and complexity of the design, there is continuous need for the studies of design and implementation of signal processing functions on hardware.

The studies in this Thesis consider the development of application-specific parallel structures for the discrete cosine transform (DCT) and variable length decoding (VLD). The attractiveness of the DCT is based on its predominant use in transform coding [86]. It has been applied actively to data compression applications, e.g., in speech, image, and video coding. It can be exploited in filtering and subsequently, in transmultiplexer systems based on filter banks as in [116]. Other applications that involve the DCT are, e.g., data analysis, classification, and pattern recognition [86]. Variable length coding (VLC) and subsequently the VLD have been utilized either alone for data compression or as a part of compression application, e.g., for text, speech, image and video compression. Since both the DCT and VLD have an essential role in image and video coding [31, 74, 94] they have been adopted as a part of various current standards, e.g., JPEG [42, 44], MPEG-1 [41], and MPEG-2 [43, 45]. Although the real-time applications based on the previous standards can nowadays be implemented on software, the performance is a serious bottleneck in some applications, e.g., in multichannel coding, transcoders, video servers, and related professional applications processing multiple video streams.

## 1.1 Objective and Scope of Research

The general objective of this Thesis is to develop area-efficient realizations of digital signal processing functions. Software implementations introduce overhead and typically instruction level parallelism is limited implying lower utilization of arithmetic resources. Furthermore, data memory bandwidth is often a serious bottleneck in high data rate applications. Therefore, in this Thesis, only application-specific parallel structures are considered. The structures are developed in such a way that the throughput can be tailored according to the input data rate of an application. Furthermore, the aim is to create general methodology to construct modular structures from the given algorithms. In general, modularity is considered to describe the granularity of the algorithm or structure.

In this Thesis, two types of systems are considered: constant and variable output rate systems. Constant output rate systems are illustrated with the computation of the discrete cosine transform. In general, the DCT algorithms possess irregularity, which restricts the area-efficient exploitation of inherent parallelism. Regularity defines the similarities in nodes and interconnections. Therefore, the objective is to derive the regular fast algorithm for the DCT. Regularity allows the utilization of linear mapping methods [84] for reducing the dimensionality of the problem and mapping the algorithm onto a parallel structure. Furthermore, since the data is often in a sequential form, another objective is to develop a single rate system, i.e., data rate equals to clock rate.

In this Thesis, the variable output rate systems are exemplified with variable length decoding. The major design problem is to break the recursive data dependencies in input data, which complicate substantially the design of parallel variable length decoder. Therefore, the objective is to develop a multiple-symbol VLD scheme and parallel structure that will at least partially break the recursive dependency related to the VLD.

### 1.2 Main Contributions

In this Thesis, the high-performance computational platforms are developed by making use of inherent parallelism of the given applications. In the first application, discrete cosine transform, the temporal parallelism is utilized while in the second application, variable length decoding, spatial parallelism is exploited. The resulting hardware structures are modular lending themselves to very large scale integration (VLSI) implementations. To summarize, the main contributions are the following:

- Up-to-date survey of related work in respect of the pipeline computation of the discrete cosine transform and multiple-symbol variable length decoding, which provides motivation and bases for the work presented in this Thesis.

- Novel regular fast algorithms for the one- and two-dimensional discrete cosine transforms, which do not reach the lower bound on arithmetic complexity but the regularity allows efficient utilization of temporal parallelism.

- New modular pipeline structures for computing the discrete cosine transform, which can be extended to support larger transform sizes by replicating the basic processing units.

- So far the most area-efficient unified pipeline structure supporting both the 8 × 8 discrete cosine transform and its inverse.

- Demonstration implementation of the unified structure supporting both the 8 × 8 discrete cosine transform and its inverse, which is synthesized onto a standard cell CMOS technology.

- Novel variable length decoding scheme for decoding multiple symbols in parallel.

- New multiplexed add unit solution, which reduces the number of logic levels in the critical path of the codeword detection in variable length decoder.

- Demonstration implementation of MPEG-2 variable length decoder, which is synthesized onto an FPGA technology.

### 1.2.1 Author's Contribution

Let us first consider the studies of DCT. The derivation of the fast DCT algorithms is continuation for the algorithm development reported earlier, e.g., in [2, 5, 104, 105]. Author rescheduled the constant geometry algorithm and found possibilities to optimize interconnections for minimizing the area of permutations in pipeline structures. The author had an essential role in deriving and formalizing the regular perfect shuffle topology algorithms. The development of computational structures for the derived algorithms was done by the author. In addition, the author has supervised the analysis of word length requirements, modeling, and synthesis of the structure.

The author was responsible for the deriving and verifying the multiple-symbol variable length decoding scheme. The author was also responsible for developing the structure, as well as applying the scheme for MPEG-2 variable length decoding. Furthermore, the author analyzed the pre-processed MPEG-2 data streams and analyzed the performance of the proposed decoder with different design parameters.

The work reported in this Thesis has been reported earlier in seven publications [P1–P7] and in six of them, the author has been the main author. Consequently, some chapters contain verbatim extracts from the publications. With respect to the extracts, copyrights are retained by the respective copyright holders.

The co-authors of the publications [P1–P7] have seen this clarification and agree with the author. In addition, none of the publications have been used in another person's academic thesis or dissertation.

### 1.3 Thesis Outline

The first three chapters cover the studies on discrete cosine transform. In Chapter 2, an introduction to the DCT and the related work is given in order to provide background and motivation for work reported ensuing two chapters. Starting with the definitions and properties of the DCT the discussion continues with a glance at some popular algorithms and implementations close to pipeline structures. The chapter is concluded with a short summary. Subsequently, the derivation of the novel regular fast algorithms for the one- and two-dimensional DCT is studied in Chapter 3. After providing the preliminaries for the derivation, the formulation of the algorithms, which are exploited and partially reported earlier in [P1 – P4], is described in details. Chapter 4 covers the derivation of the new pipeline structures for the DCT, IDCT, and both the transforms, which are published earlier in [P1 – P4]. First, the operational columns in the algorithms are mapped vertically onto basic units which are then cascaded to construct the pipelines. The chapter is concluded with a case study on the unified  $8 \times 8$  DCT/IDCT implementation and comparative discussion.

Then, the topic of the discussion is changed to variable length decoding on hardware in Chapter 5. Before going into the details of decoding, the variable length coding is studied briefly. Subsequently, the related work of the decoders is outlined in order to have basis for the further research of the VLD. Next, in Chapter 6, a novel VLD scheme is described, which has been proposed for the first time in [P5] and studied more carefully in [P7]. Furthermore, the structure of the decoder is presented before discussion on the performance in general. In Chapter 7, the presented VLD scheme and structure are applied to MPEG-2 video coding standard, which has been reported earlier in [P7]. First, the standard is outlined briefly in order to understand the fundamentals that affect to decoder design. Before modeling the structure, the specifications are determined according to the statistics of the benchmark scenes. Then, the performance of the resulting decoder is analyzed with different design parameters. The chapter is concluded with the comparison and the discussion on related problems reported in [P6]. Finally, Chapter 8 concludes Thesis.

### 2. DISCRETE COSINE TRANSFORM

By applying appropriate transforms, the complexity of a mathematical problem may be reduced, e.g., differential and integral equations may be replaced with the easier algebraic ones [86]. Representing a waveform having relatively complex variations in a signal amplitude with a sum of the oscillatory cosine function is called a cosine transform. When the waveform and cosine functions are sampled at certain intervals, the transform becomes a discrete cosine transform [74]. The DCT has been considered one of the best tools in digital signal processing and therefore, it has many applications, e.g., in the area of multimedia and telecommunications. Especially, in image and video coding it has been employed as the main tool for data compression.

Traditionally the objective in the development of fast algorithms in the field of digital signal processing has been the minimization of arithmetic complexity, i.e., the number of arithmetic operations and especially the number of multiplications. However, in hardware realizations, the number of arithmetic units depends on mapping methods, thus there are also other properties in the algorithms reflecting on the cost of a specific implementation. Especially, when targeting at structures consisting of cascaded processing units, there are specific properties, which make certain algorithms efficient for implementations.

In this chapter, an introduction to the DCT and the related work is given in order to provide background and motivation for our work. Rao and Yip's book [86] gives a good baseline for the discussion but thereafter several algorithms and structures have been reported. However, without taking restricted publication-specific comparisons into account extensive up-to-date surveys are missing. In addition, our objective is to develop a cascaded structure, which, in general, is referred to as a pipeline. The principal idea is to reduce the dimensionality of the signal flow graph of the algorithm by applying vertical mapping, i.e., the two-dimensional signal flow graph is collapsed or folded into a one-dimensional data path. Consequently, each processing column is

to be mapped onto a single processing unit. Therefore, in the following survey, some popular fast algorithms are introduced and their suitability for pipeline computations are discussed. Similarly, some DCT implementations close to pipeline structures are briefly outlined.

### 2.1 Definitions and Properties

The orthogonal DCT is classified into four different types: DCT of type I, II, III, and IV of which transform matrices are defined as [118]

$$\left[C_{N+1}^{\mathrm{I}}\right]_{mn} = \sqrt{\frac{2}{N}} \left[b_m b_n \cos\left(\frac{mn\pi}{N}\right)\right], \quad m, n = 0, 1, \dots, N$$

(1)

$$\left[C_N^{\text{II}}\right]_{mn} = \sqrt{\frac{2}{N}} \left[ b_m \cos\left(\frac{m(n+\frac{1}{2})\pi}{N}\right) \right], \quad m, n = 0, 1, \dots, N-1$$

(2)

$$\left[C_N^{\text{III}}\right]_{mn} = \sqrt{\frac{2}{N}} \left[ b_n \cos\left(\frac{(m+\frac{1}{2})n\pi}{N}\right) \right], \quad m, n = 0, 1, \dots, N-1$$

(3)

$$\left[C_N^{\text{IV}}\right]_{mn} = \sqrt{\frac{2}{N}} \left[\cos\left(\frac{(m+\frac{1}{2})(n+\frac{1}{2})\pi}{N}\right)\right], \ m, n = 0, 1, \dots, N-1$$

(4)

where  $b_m$  is a scaling factor defined as

$$b_m = \begin{cases} \frac{1}{\sqrt{2}} & \text{, if } m = 0 \text{ or } m = N \\ 1 & \text{, if } m \neq 0 \text{ and } m \neq N \end{cases}$$

(5)

The DCT of type I (DCT-I) was introduced by Wang and Hunt in [120]. The first definitions of the DCT and its inverse, which according to previous classification are known as the DCT of type II (DCT-II) and DCT of type III (DCT-III), respectively, were given by Ahmed *et al.* in [1]. The DCT of type IV (DCT-IV) was introduced by Jain in [47].

Let us next summarize the main properties of the DCT matrices given in (1)–(4). Since the DCT matrices are orthogonal the inverse transform matrices are obtained with a matrix transpose. In addition, the DCT-I and DCT-IV matrices are symmetric which means that the inverse transform is the transform itself. On the contrary, the DCT-II and DCT-III are transposes for each others. These relations can be formulated

as

$$\begin{bmatrix} C_{N+1}^{I} \end{bmatrix}^{-1} = \begin{bmatrix} C_{N+1}^{I} \end{bmatrix}^{T} = C_{N+1}^{I}, \qquad \begin{bmatrix} C_{N}^{II} \end{bmatrix}^{-1} = \begin{bmatrix} C_{N}^{II} \end{bmatrix}^{T} = C_{N}^{III},

\begin{bmatrix} C_{N}^{III} \end{bmatrix}^{-1} = \begin{bmatrix} C_{N}^{III} \end{bmatrix}^{T} = C_{N}^{II}, \qquad \begin{bmatrix} C_{N}^{IV} \end{bmatrix}^{-1} = \begin{bmatrix} C_{N}^{IV} \end{bmatrix}^{T} = C_{N}^{IV}.$$

(6)

From the multidimensional point of view, an essential property is separability which allows the decomposition of the multidimensional transform into successive one-dimensional transforms. [86]

In image and video processing, especially the two-dimensional DCT-II and its inverse, i.e., DCT-III, have gained popularity due to good energy compaction properties. The computation of the DCT-II as a matrix product is computationally expensive thus several fast algorithms for the DCT-II have been suggested over the years. Before taking an overview into the fast DCT-II algorithms and their properties, let us note that in this Thesis, we concentrate only on the DCT-II and DCT-III. Therefore, from now on, the DCT and its inverse refer to DCT-II and DCT-III, respectively.

### 2.2 One-Dimensional Fast Algorithms

The DCT can be computed via other discrete trigonometric transforms, e.g., discrete Fourier transform (DFT), discrete Walsh-Hadamard transform (DWHT) and discrete Hartley transforms (DHT) [70, 113, 115]. However, such approaches result in additional computational complexity. The fast algorithms with lower arithmetic complexity can be obtained by considering the direct factorization of the DCT matrix. When the factorization results in sparse component factors, the decomposition represents a direct fast algorithm for the DCT. Since the matrix factorization is not unique, the different types of the fast algorithms can be derived. Some of the proposed fast algorithms derived with the matrix factorization can be categorized into decimation-in-time or decimation-in-frequency algorithms as in [126, 127].

In the following, some fast algorithms are described. First, well-known pioneer algorithms are introduced, which have advantages in some realizations but introduce critical drawbacks when targeting at the area-efficient pipeline computation at data rate. In such cases, regularity in particular is a beneficial property. Therefore, a viewpoint is focused on regular algorithms, which represents novelty in the survey.

Fig. 1. Signal flow graph to compute the DCT via real parts of the DFT [3].

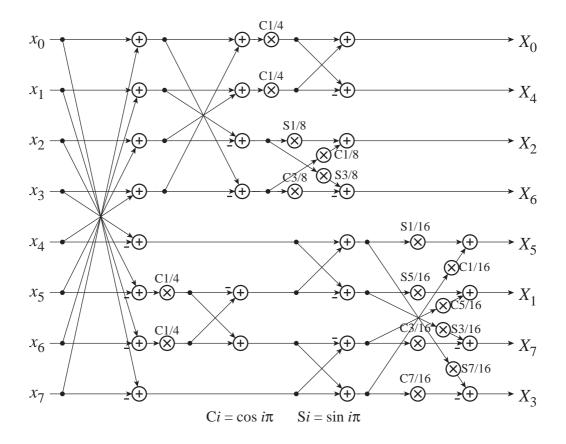

## 2.2.1 Well-Known Pioneer Algorithms

The natural basis for developing the fast algorithms for the DCT is its relation to a discrete Fourier transform (DFT). In addition to introducing the discrete cosine transform, Ahmed *et al.* in [1] suggested the computation of the DCT by using one double length fast Fourier transform (FFT). In [28], Haralick accelerated computation by taking two *N*-point FFTs instead one double length FFT. Tseng and Miller in [111] proved, however, that the DCT can be computed more efficiently with the aid of one double length modified FFT and especially exploiting only its real parts. As an example, a signal flow graph to compute the scaled DCT via real parts of the 16-point DFT as proposed by Arai *et al.* in [3] is illustrated in Fig. 1. In any case, the relation between the FFT and DCT can be utilized in various different ways as described, e.g., in [69, 79, 115].

The first fast DCT algorithm based on the sparse matrix factorization of the DCT matrix has been reported by Chen *et al.* in [11] and Wang in [117]. Since the presented factorization of the algorithm consists of a matrix which cannot be recursively factorized, the factorization is only partially recursive. However, the non-recursive matrix possesses some regularity; it can be decomposed into the product of sparse matrices, which are of five distinct types, all having at most two non-zero elements in each row [86]. The resulting signal flow graph of the 8-point DCT algorithm is illustrated in Fig. 2.

Fig. 2. Signal flow graph of the DCT based on the sparse matrix factorization [11].

Loeffler *et al.* in [67] presented a class of the 8-point DCT algorithms based on planar rotations. The algorithms require only 11 multiplications, which is shown to be the theoretical minimum number of the multiplications for the 8-point transform [22]. The number of the multiplications is decreased from the traditional approaches by interpreting the multiplications as rotations, which can be performed with three multiplications and three additions by introducing two new coefficients instead of four multiplications and two additions. For example, consider the following formulation [67]

$$y_0 = a \cdot x_0 + b \cdot x_1 = (b-a) \cdot x_1 + a \cdot (x_0 + x_1)$$

$$y_1 = -b \cdot x_0 + a \cdot x_1 = -(a+b) \cdot x_0 + a \cdot (x_0 + x_1).$$

(7)

An example of Loeffler's 8-point DCT algorithm is depicted in Fig. 3. The 8-point algorithm can be extended in a recursive way to support larger transform sizes but the resulting algorithms do not reach anymore the theoretical lower bound on the number of the multiplications.

Fig. 3. Signal flow graph of the DCT based on the rotations [67].

## 2.2.2 Regular Algorithms

In general, the fast algorithms for the DCT do not possess the regularity found, e.g., in Cooley-Tukey FFT algorithms. For example, the previously discussed fast DCT algorithms, Chen's sparse matrix factorization and Loeffler's algorithm reaching the theoretical lower bound on the number of multiplications with planar rotations, do not result in area-efficient pipeline structures due to their high control complexity. In addition, the algorithms consist of the variable number of operations at operational columns implying that the resulting pipeline structure would be a multirate system, i.e., the pipeline would require a higher clock rate than a sample rate. Nevertheless, some regular fast algorithms for the computation of the DCT have been reported over the years.

## In-Place Algorithms

One category of the regular fast DCT algorithms is well-known in-place algorithms where the computations can be performed in-place, i.e., the results of intermediate computations can be stored into the same locations as the operands. Consequently, the in-place algorithms lend themselves especially to software implementations due to efficient memory utilization. However, these algorithms have also good properties for vertical mapping due to simple and regular processing columns.

Fig. 4. Signal flow graph of the in-place DCT with separated irregularities [34].

The basis for the derivation of the first reported in-place algorithms is the reordering of the input sequence into even and odd indices as proposed earlier in [79]. In addition, Lee in [56] reordered both halves in bit-reversed order when considering the matrix factorization of the IDCT matrix. With the aid of this rearrangement, the N-point IDCT has been decomposed into a sum of two N/2-point IDCTs. The transform size can be further reduced by repeating the decomposition. The procedure results in a simple structure with recursive modularity improving the regularity but the drawback is the secant coefficients introducing round off errors with finite word length.

In [19], Cvetković and Popović derived an in-place DCT algorithm which does not require the additional bit-reversed permutation of the input halves. Instead, the output of the algorithm illustrated in Fig. 4 is in bit-reversed order. The same algorithm and the matrix decomposition of the algorithm with the output in natural order have been reported by Hsiao *et al.* in [34]. In order to avoid round off problems with the coefficients of secants, Hou in [33] proposed an in-place algorithm with pure sine or cosine coefficients. However, the approach results in additional multiplications by two. By using the different derivation technique, Lee and Huang in [57] entered corresponding in-place algorithm with a perfect shuffle output permutation [102] which will be defined in Section 3.1.

In all the in-place algorithms discussed so far, the computations are performed with a kernel of real-valued radix-2 butterfly operations and a separate post-processing stage, or alternatively a pre-processing stage, containing all the DCT-related irregular

*Fig. 5.* Signal flow graph of the in-place DCT with distributed irregularities [119].

additions and permutations. Instead, the separate pre- or post-processing is avoided in a regular in-place algorithm proposed by Wang in [119] where irregularities are distributed between the butterfly columns as illustrated in Fig. 5. The matrix factorization is based on the successive order reduction of the Hadamard ordered DCT matrix. The algorithm can be characterized as simple as the previous in-place algorithms and its coefficients are pure cosines, which can be generated with the recursive equations depicted below the signal flow graph in Fig. 5. The input sequence is Hadamard ordered, which will be defined in Section 3.1, and the output is obtained in natural order.

### Constant Geometry Algorithms

Another category of the regular fast DCT algorithms is constant geometry algorithms where the interconnection topology and geometry between the computation columns are the same, i.e., constant. The constant geometry algorithms have been used in software implementations where sequential data access and storage are required. In addition, the constant geometry algorithms lend themselves to VLSI implementations. Full-column and partial-column structures are typically based on such algorithms. In these structures, the computations are performed iteratively one column of the signal flow graph or part of the column at a time.

A constant geometry algorithm based on Wang's in-place algorithm with the distributed irregularities has been presented by Takala *et al.* in [5, 105]. The derivation

Fig. 6. Signal flow graph of the constant geometry DCT algorithm [105].

is based on a method to localize irregularities into block matrices of order four as proposed in [5]. Therefore, the achieved constant geometry algorithm illustrated in Fig. 6 can be interpreted to be a rescheduled version of the in-place algorithm in Fig. 5. The corresponding derivative constant geometry algorithm of Hou's in-place algorithm in [33] has been presented by Kwak and You in [55]. In this algorithm, a computational kernel is performed with consecutive stages of the radix-2 butter-fly operations and all the irregularities have been separated into a post-processing column containing only additions.

In general, the post-processing is a disadvantage in unified pipeline realizations, when both forward and inverse transforms need to be supported. The post-processing in the forward transform maps as a pre-processing in the inverse transform, thus in the unified approach both pre- and post-processing need to be realized implying additional hardware cost. In Wang's in-place algorithm in [119], the irregular additions are local, thus they map in similar fashion in forward and inverse transforms. On the other hand, the representation of the algorithm contains anti-diagonal matrices, which imply complex data permutations requiring large data storage in VLSI implementations. Such problems are avoided in Takala's constant geometry algorithm in [105]. The drawback is that the interconnections between the operation columns in an *N*-point algorithm are *N*-point permutations implying higher area cost in pipeline structure.

# 2.3 Two-Dimensional Algorithms

The previous discussion on the categorization and features of the one-dimensional DCT algorithms applies also to two-dimensional DCT algorithms, which can be derived by using either a row-column decomposition or a direct computation. The row-column decomposition exploits the separability property of the DCT, i.e., the two-dimensional transform is computed by performing the one-dimensional DCT first over the rows and then over the columns or vice versa. On the contrary, the direct computation produces the result of the two-dimensional transform at once, i.e., the algorithms operates directly over the two-dimensional data set. In other words, the dimensions are not separated and, therefore, the computation of the one-dimensional transforms over the rows and columns cannot be identified from the direct two-dimensional transform. Let us remark, that the direct two-dimensional algorithm can be, however, derived with the aid of the one-dimensional transform as will be done later in this Thesis.

The direct two-dimensional algorithms are based on the same derivation approaches as the one-dimensional algorithms. Without going into details but outlining the development of the algorithms, the relation between the DFT and DCT has been exploited, e.g., by Makhoul in [69] and Vetterli in [114]. From the authors mentioned previously when considering the one-dimensional DCT algorithms, Lee and Huang in [57], Kwak and You in [55], and Hsiao *et al.* in [35] have extended their approaches to support also the direct two-dimensional computation. Kamangar and Rao in [51] presented non-recursive as well as recursive algorithms for the two-dimensional DCT, which have been derived with an approach very similar to Chen's approach to derive the one-dimensional DCT in [11]. In [27], Haque presented the two-dimensional extension of Lee's algorithm in [56]. Correspondingly, Hou's one-dimensional DCT algorithm in [33] has been extended to two-dimensional DCT by Chan and Ho in [7] and Wu and Paoloni in [124].

In [13–15], Cho *et al.* presented an approach to compute the two-dimensional DCT algorithm by exploiting the one-dimensional algorithm but, however, operating directly over the two-dimensional data set. In addition to any available one-dimensional algorithm only permutations, pre-, and post-additions are required as illustrated in Fig. 7. The presented approach introduces systematic expressions for the algorithms and in that sense, it can be considered to possess some regularity. Furthermore, the

*Fig.* 7. Signal flow graph of the direct  $8 \times 8$  DCT by utilizing an 8-point DCT [13].

approach results in the optimal two-dimensional algorithm from the multiplicative complexity theory point of view when Loeffler's DCT algorithm in [67] is used to compute the 8-point DCT [123]. Nevertheless, the resulting algorithm do not possess regularity that would be advantageous when mapping onto hardware. The representation of the post-additions in the algorithm contains anti-diagonal matrices requiring the complex data permutations and large data storage.

In general, the direct computation is considered to produce algorithms with a lower arithmetic complexity and especially with the lower number of multiplications than the row-column decomposition. Typically the control complexity of algorithms derived with the row-column decomposition is lower implying regularity and modularity. Since these properties are preferred especially in VLSI implementations, the row-column decomposition has gained popularity in hardware realizations. It is also possible to obtain regular and modular algorithms with the direct computation but at the expense of arithmetic complexity. However, modularity and regularity may be the key properties to efficient implementations.

#### 2.4 Hardware Structures

The main objectives in realizing the algorithms is to achieve required system performance with minimum cost. In general, the direct implementation or so called one-to-one mapping of the algorithm leads to an expensive realization. Therefore, the mapping methods described, e.g., in [84, 87, 92] can be utilized for reducing the dimensionality of a signal flow graph in different directions; horizontal, vertical, or in both directions. In principle, the exploitation of spatial parallelism, i.e., horizontal mapping, results in a column structure where the computations are performed recursively on parallel data, i.e., nodes at a single processing stage are computed at a time. In such a structure, the throughput is limited by the delay of the basic arithmetic units used to realize the nodes. The exploitation of temporal parallelism with the aid of vertical mapping, in turn, results in sequential structures, where the computations are performed over data in sequential form and the overall structure can be considered as a pipeline. In such a structure, the throughput can be tailored with additional pipeline registers if the data dependencies, i.e., the feedback loops in the structure, can be avoided. In addition, data is often in sequential form, thus structures operating over sequential data are advantageous. In the following, computational structures for such a data format are described.

*Fig. 8.* Block diagram of the pipeline structure with double buffering [54]. D: Delay register. Control logic is omitted for clarity.

#### 2.4.1 One-Dimensional Structures

In [54], Kovać and Ranganathan presented a six-stage pipeline structure based on the modified Arai's DCT algorithm in Fig. 1. With the aid of the modifications the number of subtractions has been decreased but they do not affect the structure, i.e., Arai's original algorithm could be mapped onto the same structure. In any case, the resulting pipeline structure is illustrated in Fig. 8. Each operational column in the algorithm has been mapped onto a corresponding stage in the pipeline. The operational stages are separated with register-based double buffering stages. In other words, a left column of the registers is first filled and then copied onto a right column for computation. During the computation over the values in the right register column the left column is refilled. Altogether, the structure requires high number of register and introduces complicated control. Let us remark that the control and selection resources are not included into the figure.

The irregularities in the DCT algorithms restrict the exploitation of the linear mapping methods. Hence the structures based on Chen's fast DCT algorithm [11, 117] have been fully parallel and consequently expensive. The reduction in the amount of hardware has been achieved by using advanced circuit techniques and optimizations that are very close to technology and, in general, time demanding. E.g., in [112], Uramoto *et al.* have exploited multiplier accumulators based on distributed arithmetic in order to have critical path of adders instead of multipliers. For minimizing the routing area and its parasitics, a column-interleaved memory structure has been employed. In addition, the number of memory cells has been halved with the aid of dual-plane feature and dual-port configuration. Correspondingly, Matsui *et al.* in [72] achieved improvements in chip area and speed by introducing and applying

a sense-amplifying pipeline flip-flop circuit technique. Instead of the conventional synchronous design style, an asynchronous DCT processor has been presented by Johnson *et al.* in [50].

The linear mapping methods can be efficiently applied to the regular fast DCT algorithms although the irregularities may limit the exploitation of the parallelism or decrease the utilization rate of resources. In principle, applying the vertical mapping to the in-place algorithms corresponds to serializing the computation. The level of the mapping can be varied to have different level of parallelism. E.g., Cheng *et al.* in [12] have mapped the in-place algorithm with regular butterfly kernel and post-processing stage managing the irregularities only half. Instead in [110], Tan *et al.* have applied vertical mapping to Hou's algorithm [33] in order to have fully sequential structure for sequentially represented data. The relation between the DCT and DFT can also be utilized in the structural derivation. E.g., in [108], Takala *et al.* have mapped Wang's in-place DCT algorithm with the distributed irregularities [119] onto a pipeline structure by using an efficient mapping technique, which has been proposed earlier by Groginsky and Works in [26].

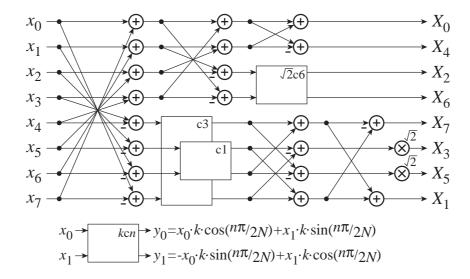

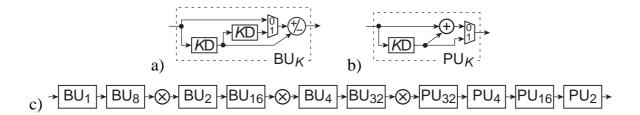

In [34], Hsiao *et al.* mapped their DCT algorithm efficiently onto a pipeline structure depicted in Fig. 9. The structure has single input and output interface and each computational stage has been mapped vertically onto a corresponding unit, i.e., butterfly stages onto processing elements BU<sub>4</sub>, BU<sub>2</sub>, and BU<sub>1</sub> with single arithmetic unit, multiplications onto multipliers and post-processing stages onto post-processors PP<sub>1</sub> and PP<sub>2</sub>. With such an arrangement, the amount of hardware is minimized. In addition, the required throughput rate can be achieved with the aid of additional pipelining, since the structure does not consist of feedback paths. Furthermore, due to regularity the structure is comparable easy to extend to support larger transform sizes.

The vertical mapping can also be applied to the constant geometry algorithms in [55, 105] in order to select an optimal level of parallelism with respect to performance requirements and resources. On the other hand, the constant interconnections may increase the hardware cost in pipeline structures when the constant interconnection network is repeated between every stage. Instead, the constant interconnections are, in principle, advantageous for horizontal mapping. However, the pure column structures for computing the DCT are rare due to irregularities in the fast algorithms but the principal concept can be found, e.g., in [48,105]. Likewise, the applying mapping in both directions, i.e., multiprojection, has not been reported when considered only the DCT structures.

**Fig. 9.** Block diagram of the fully sequential DCT pipeline [34]: (a) radix-2 butterfly unit having operands K samples apart  $(BU_K)$ , (b) post-processor 1  $(PP_1)$ , and (c) post-processor 2  $(PP_2)$ , and (d) entire pipeline structure. KD: Shift register of size K. Clock and control signals are omitted for clarity.

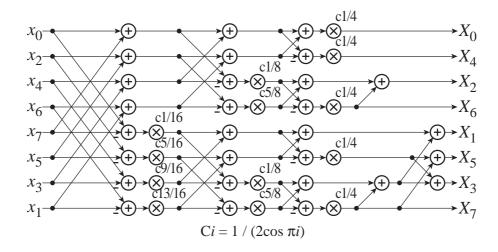

# 2.4.2 Two-Dimensional Structures with Matrix Transpose

In the two-dimensional transforms based on the row-column decomposition, large silicon area may be consumed into the realization of the matrix transpose. The most straightforward realization of the matrix transpose is to exploit double buffering according to the direct interpretation of the transpose, i.e., rows in, columns out. The implementation can be memory-based as in [50, 112] or register-based as in [54]. The realization based on the double buffering is, however, expensive;  $2N^2$  storage locations are needed for an  $N \times N$  matrix transpose as illustrated with the aid of a register-based transpose network in Fig. 10. Furthermore, latency is increased since all the samples must be stored before reading. If the  $N \times N$  transpose is to be performed with  $N^2$  memory locations like in [68], either dual-port memory or higher write/read-rate is needed since the data is in sequential form, i.e., when a new sample is written in, a transposed sample need to be read out. This implies higher cost for memory-based transpose units.

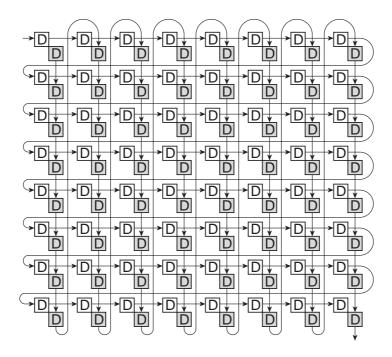

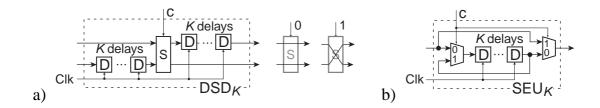

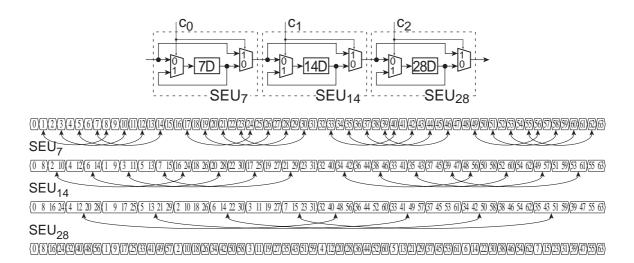

In the advanced register-based transpose networks, two principal switching units, i.e., a 2-port delay-switch-delay unit (DSD) and 1-port shift-exchange unit (SEU) introduced in [98], are exploited to perform the reordering of the data elements. In principle, the delay-switch-delay unit of size K (DSD $_K$ ) depicted in Fig. 11(a) exchanges the first K data elements entering to the lower port with the K elements entering to the upper port. Correspondingly, the shift-exchange unit of size K (SEU $_K$ ) illustrated in Fig. 11(b) is capable of exchanging elements in a serial sequence K elements apart. The latencies of these units depend on the size of the shift registers; the latency of DSD $_K$  or SEU $_K$  is K cycles.

Fig. 10. Register-based matrix transpose network by using double buffering [54].

In [98], Shung *et al.* proposed a sequential permutation network which can be used to perform any arbitrary permutation over sequentially represented data. In general, the arbitrary permutations of an N-point sequence,  $N=2^k$ , can be realized as the sequential permutation network of the cascaded SEUs arranged in increasing and decreasing order:  $SEU_{2^0}$ ,  $SEU_{2^1}$ , ...,  $SEU_{2^{k-1}}$ , ...,  $SEU_{2^1}$ ,  $SEU_{2^0}$ . Such a realization requires less registers than the conventional double buffering approach but still more than the original data.

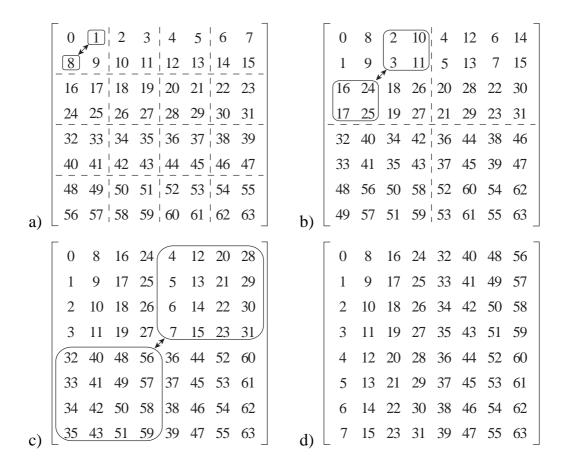

In [6], Carlach *et al.* proposed an iterative method for an  $8 \times 8$  matrix transpose, which has been generalized for an  $N \times N, N = 2^k$ , matrix by Takala *et al.* in [109]. In principle, the entire  $N \times N$  matrix is divided into  $(N/2)^2$  submatrices of order

Fig. 11. Block diagrams of the basic switching units: (a) delay-switch-delay unit of size K ( $DSD_K$ ) and (b) shift-exchange unit of size K ( $SEU_K$ ). S: Switch. c: Control signal. Clk: Clock signal.

*Fig.* 12. Example of the iterative  $8 \times 8$  matrix transpose: (a) the first iteration, (b) the second iteration, (c) the third iteration, and (d) the transposed matrix.

two and each submatrix is transposed. The resulting  $N \times N$  matrix is then divided into submatrices of order four which are transposed as 2-by-2 matrices of 2-by-2 blocks. This operation is iterated until the entire  $N \times N$  matrix is divided into four  $N/2 \times N/2$  submatrices and the resulting 2-by-2 block matrix is transposed in order to have finally the transposed matrix. The described method is illustrated with the aid of an  $8 \times 8$  matrix in Fig. 12, and the resulting column parallel  $8 \times 8$  matrix transpose unit proposed by Carlach *et al.* in [6] is depicted in Fig. 13.

In general, the previously described iterative method for the matrix transpose of an  $N \times N, N = 2^k$ , matrix requires k steps. At each step, the transpose is performed within 2-by-2 blocks. This implies that the distance of data elements to be exchanged at a single step is constant. Therefore, the corresponding structure can be constructed by cascading the SEUs in increasing order of size:  $SEU_{N-1}$ ,  $SEU_{2(N-1)}$ , ...,  $SEU_{(N/2)(N-1)}$  as reported by Takala *et al.* in [108, 109]. The latency of the resulting generalized sequential matrix transpose network is  $\sum_{i=0}^{k-1} (2^i)(N-1) = (N-1)^2$

Fig. 13. Block diagram of the column parallel matrix transpose [6].

cycles, which equals to the maximum distance of single data element to be moved in the  $N \times N$  matrix transpose in a vector form. The sequential  $8 \times 8$  matrix transpose network is illustrated in Fig. 14. Let us remark that the diagram in the figure illustrates only the functionality, not the timing.

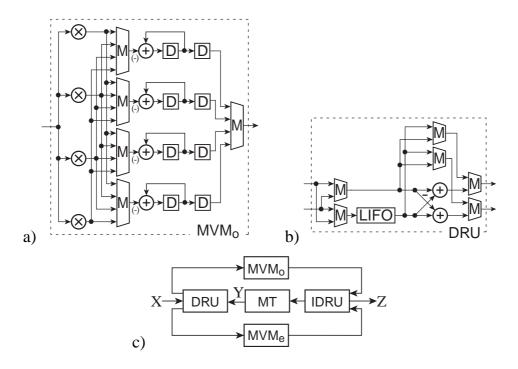

Although any one-dimensional structure can be exploited for the two-dimensional structure based on the row-column decomposition, let one two-dimensional structure, which has been proposed by Madisetti and Willson in [68], be introduced in more details. The basis for the structural derivation is the DCT algorithm presented by Chen *et al.* in [11]. When the transform matrix is decomposed into even and odd rows, the DCT as well as its inverse requires the computation of two  $4 \times 4$  by  $4 \times 1$  matrix-vector products. Such operations can be performed in parallel with two matrix-vector multipliers. The matrix-vector multiplier performing the product of the odd rows MVM $_0$  requires four multipliers in addition to four accumulators as illustrated in Fig. 15(a). Instead, the product of the even rows can be computed with three multipliers and four accumulators.

In addition to the matrix-vector products, the DCT requires several additions and subtractions before the matrix-vector product whereas the IDCT requires the grouping of even and odd samples. These operations can be performed in a data reordering unit DRU depicted in Fig. 15(b). Correspondingly, the DCT requires the regrouping of even and odd coefficients after the matrix-vector product while the IDCT requires some additions and subtractions, which are performed in an inverse reordering unit IDRU. The objective has been to minimize the core area and keep input and output requirements simple with the single-pixel interfaces. The resulting structure is illustrated in Fig. 15(c).

Fig. 14. Block and timing diagrams of the sequential matrix transpose.

The feature that makes the structure in Fig. 15(c) different from the other row-column structures is the exploitation of the parallelism and time multiplexed computation of the DCT over dimensions. In other words, for four clock cycles, the matrix-vector multipliers operate on a column at the input X and stores samples from Y into last-in-first-out (LIFO) buffer. For the next four cycles, multipliers operate on a row Y while samples from X are stored. Katayama *et al.* in [52] presented a corresponding structure but instead of the line parallel operation, the structure operates line-by-line. With such a modification, the number of accumulators is reduced from eight to two.

#### 2.4.3 Direct Two-Dimensional Structures

Instead of applying the row-column decomposition, Lee  $et\ al.$  in [59] proposed a direct two-dimensional DCT structure. In order to reduce computational complexity with the aid of rotation techniques, real input values are mapped into complex numbers in the  $N\times N$  DCT algorithm presented by Duhamel and Guillemot in [21]. Furthermore, the algorithm is modified for increasing the regularity and applying the vertical mapping. In any case, the resulting structure still possess high degree of parallelism; 16 values are processed in parallel, which reflect on the amount of hardware resources. On the other hand, the parallel processing provides a good throughput rate. Another highly parallel direct two-dimensional DCT structure is presented by Lim  $et\ al.$  in [63]. The structure is based on the implementation of the matrix multiplication as a systolic array. The interconnection complexity is minimized by using bit-serial interfaces between processing elements. However, the amount of hardware is huge.

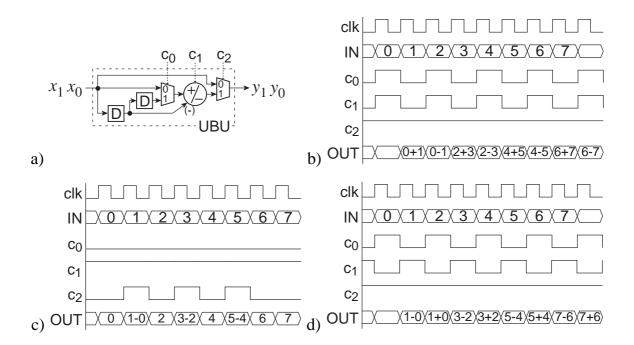

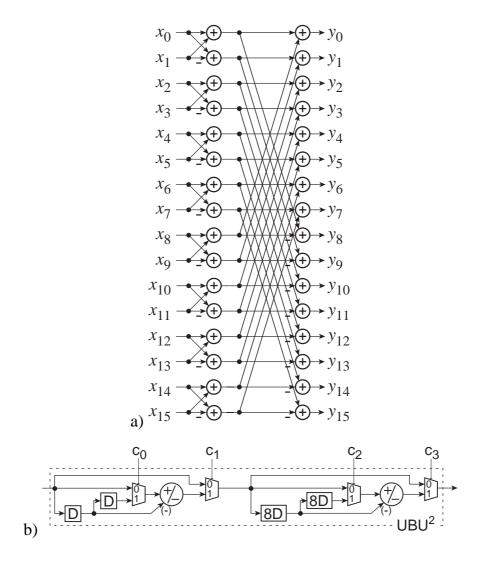

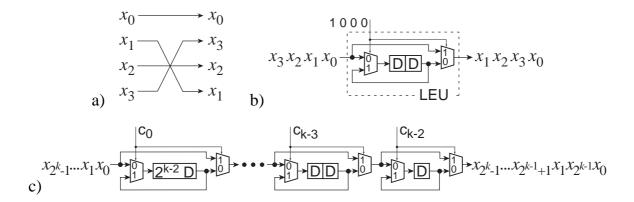

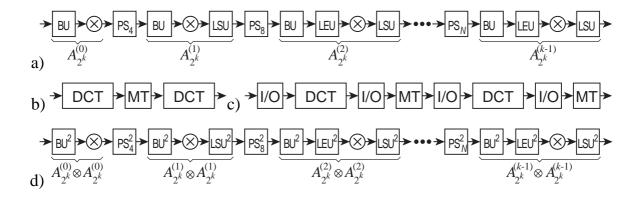

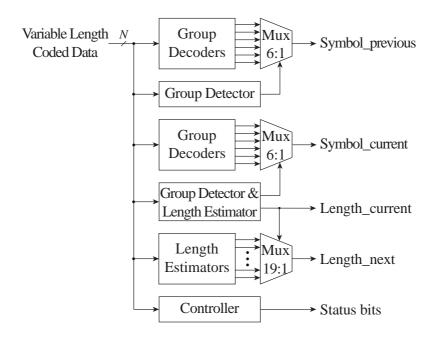

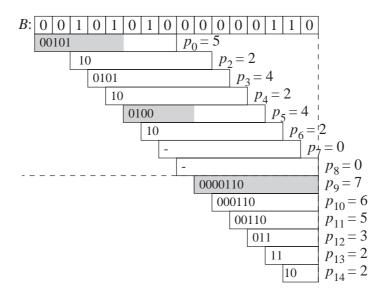

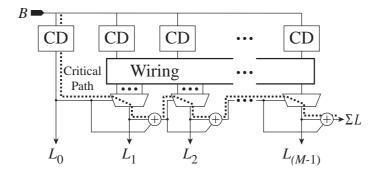

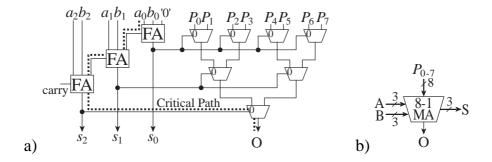

Fig. 15. Block diagram of the 8 × 8 DCT/IDCT with matrix transpose: (a) matrix-vector multiplier performing the product of the odd rows (MVM<sub>o</sub>), (b) data reordering unit (DRU), and (c) entire structure [68]. M: Multiplexer. LIFO: Last-in-first-out buffer. MVM<sub>e</sub>: matrix-vector multiplier for even rows. IDRU: Inverse data reordering unit.