Ismo Hänninen

# Computer Arithmetic on Quantum-Dot Cellular Automata Nanotechnology

Tampereen teknillinen yliopisto. Julkaisu 852 Tampere University of Technology. Publication 852

Ismo Hänninen

# Computer Arithmetic on Quantum-Dot Cellular Automata Nanotechnology

Thesis for the degree of Doctor of Technology to be presented with due permission for public examination and criticism in Tietotalo Building, Auditorium TB222, at Tampere University of Technology, on the 7th of December 2009, at 12 noon.

#### **ABSTRACT**

The traditional digital technologies are reaching their performance limits, and the desired growth of computing power can be continued only by adopting emerging circuit technologies and new design approaches into use. This thesis provides a practical view on the emerging quantum-dot cellular automata (QCA) nanotechnology, presenting techniques to construct high-density, performance optimized, and noise tolerant basic arithmetic circuits. Several novel arithmetic units are proposed, described at the logic, the pipeline, and the layout level, and verified using quantum mechanical simulation.

Design analysis shows, that on the self-latching QCA nanotechnology, the basic serial and parallel arithmetic structures for addition, or multiplication, typically have comparable latency, but the throughput follows the degree of parallelism. The circuit area is dominated by the passive wiring overhead, characterized by a square-law dependency on operand word length. Hierarchical probabilistic analysis shows, that bit-stage level macro component reliability has about linear effect on the total reliability, while component types affect whole with weights determined by the word length, and the wiring dominates also the reliability. The power dissipation is analyzed near the ultimate limit of computation efficiency, using the Landauer's principle, showing that irreversible information erasures consume significant power on molecular QCA, severely limiting the operating frequency.

The studies in this thesis show, that QCA systems have to address emerging technology characteristic, that have not had much impact in traditional engineering work. Design optimization has to be started from the reliability and power challenges, which will determine the feasibility of any planned system.

#### **PREFACE**

The work presented in this thesis has been carried out at the Department of Computer Systems at Tampere University of Technology, Tampere, Finland, where the author held an assistant's position during the years 2007–2009.

I would like to express my deepest gratitude to my supervisor Prof. Jarmo Takala for his guidance and encouragement during the nano-arithmetic research, which was at the time a one-man undertaking apart from that. Grateful acknowledgments go also to Prof. Peeter Ellervee and Prof. Sorin Cotofana for their constructive reviews, improving the manuscript of the thesis.

Sincere thanks to my esteemed teaching colleagues, Prof. Marko Hännikäinen, Prof. Timo D. Hämäläinen, Jarno Vanne, M.Sc., and Erno Salminen, M.Sc. Together we have seen to the education of future computer engineers, giving them the basic tools for project management, scientific writing, and computer arithmetic. I would also like to recognize all the other fellows at the department for inspiring conversations on a multitude of topics and a friendly environment, and the staff who helped with all the practical matters, Mrs. Johanna Reponen, Ms. Irmeli Lehto, and Timo Rintakoski, M.Sc.

Finally, I am obliged to my mother Marjatta Hänninen, and parents-in-law Eliisa and Mauri Rintanen for their continuous support to our family during this endeavor. My heartfelt gratitude to my dear wife Susa and sons Konsta and Otso, for enduring the absence of the husband and the father during the many conference trips and the frequent inattention at other times. Susa and the little bears, thanks to you, and praises to the Heavenly Father for you!

Orivesi, November 2009 Ismo Hänninen

## **TABLE OF CONTENTS**

| Αŀ  | stract  | i                                           |

|-----|---------|---------------------------------------------|

| Pro | eface   |                                             |

| Tal | ble of  | Contents v                                  |

| Lis | st of F | igures ix                                   |

| Lis | st of T | ables xi                                    |

| Lis | st of A | bbreviations xiii                           |

| Lis | st of S | ymbols xv                                   |

| Lis | st of P | ublications                                 |

| 1.  | Intro   | duction                                     |

|     | 1.1     | The Necessary Technology Transition         |

|     | 1.2     | Bringing the Emerging Technologies Into Use |

|     | 1.3     | Objectives and Research Statements          |

|     | 1.4     | Main Contributions                          |

|     | 1.5     | Thesis Outline                              |

| 2.  | Quai    | ntum-Dot Cellular Automata                  |

|     | 2.1     | QCA Basics                                  |

|     | 2.2     | Interconnects                               |

|     | 2.3     | Signal Dynamics                             |

|     | 2.4     | Clocking Approaches and Pipelining          |

|     | 2.5     | Physical Implementations                    |

|     | 2.6     | Simulation Models                           |

|     | 2.7     | Digital Design                              |

| 3. | Bina  | ry Adders                            | 25  |

|----|-------|--------------------------------------|-----|

|    | 3.1   | Previous Work                        | 25  |

|    | 3.2   | Robust Full Adder                    | 26  |

|    | 3.3   | Robust Serial Adder                  | 29  |

|    | 3.4   | Pipelined Ripple Carry Adder         | 30  |

|    | 3.5   | Verification                         | 32  |

|    | 3.6   | Design Analysis                      | 35  |

|    | 3.7   | Summary                              | 40  |

| 4. | Bina  | ry Multipliers                       | 41  |

|    | 4.1   | Previous Work                        | 41  |

|    | 4.2   | Serial-Parallel Multiplier           | 42  |

|    | 4.3   | Pipelined Array Multiplier           | 47  |

|    | 4.4   | Radix-4 Multiplier                   | 53  |

|    | 4.5   | Verification                         | 63  |

|    | 4.6   | Design Analysis                      | 65  |

|    | 4.7   | Summary                              | 72  |

| 5. | Relia | ability Analysis                     | 73  |

|    | 5.1   | Previous Work                        | 73  |

|    | 5.2   | Probabilistic Transfer Matrices      | 75  |

|    | 5.3   | Pipelined Ripple Carry Adder         | 76  |

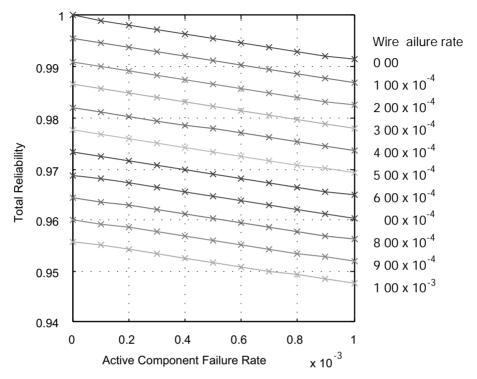

|    | 5.4   | Array Multiplier                     | 83  |

|    | 5.5   | Summary                              | 89  |

| 6. | Pow   | er Analysis                          | 91  |

|    | 6.1   | Previous Work                        | 91  |

|    | 6.2   | Irreversibility Power                | 92  |

|    | 6.3   | Pipelined Ripple Carry Adder         | 93  |

|    | 6.4   | Serial-Parallel and Array Multiplier | 99  |

|    | 6.5   | Summary                              | 104 |

| T 1 | 1   | C  | $\sim$ |      |     |

|-----|-----|----|--------|------|-----|

| Tab | le. | ot | ( '0   | ntei | 1ts |

vii

| 7.  | Conc    | clusions           | 05 |

|-----|---------|--------------------|----|

|     | 7.1     | Main Results       | )5 |

|     | 7.2     | Future Development | 06 |

| Bil | bliogra | aphy               | 07 |

## LIST OF FIGURES

| 1  | QCA cell polarizations and wires                                 | 10 |

|----|------------------------------------------------------------------|----|

| 2  | QCA primitive logic gates                                        | 11 |

| 3  | QCA wire crossings                                               | 13 |

| 4  | QCA zone clocking                                                | 17 |

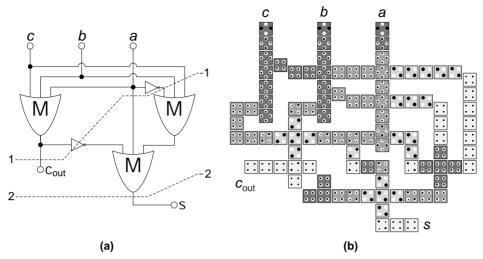

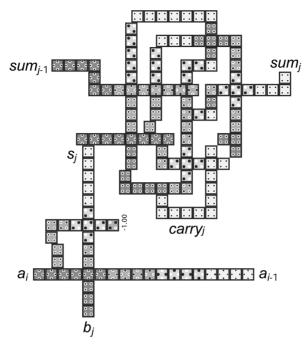

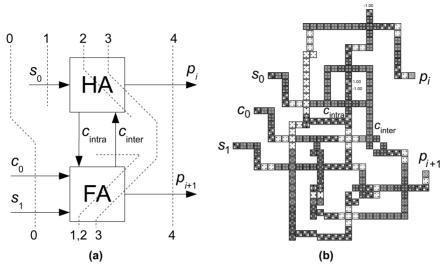

| 5  | Full adder, logical structure and QCA layout                     | 28 |

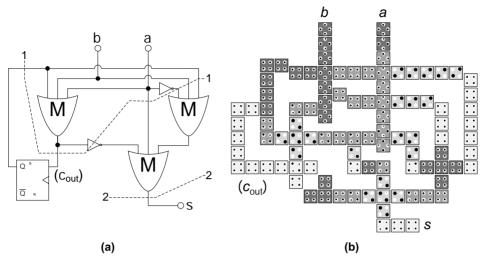

| 6  | Serial adder, logical structure and QCA layout                   | 29 |

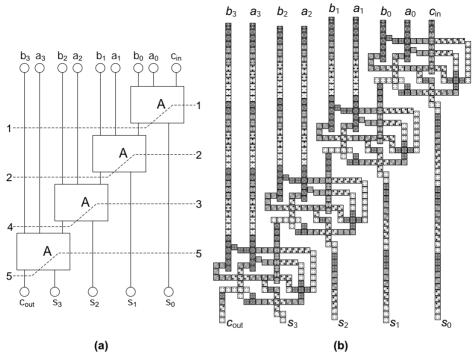

| 7  | Ripple carry adder, logical structure and QCA layout             | 31 |

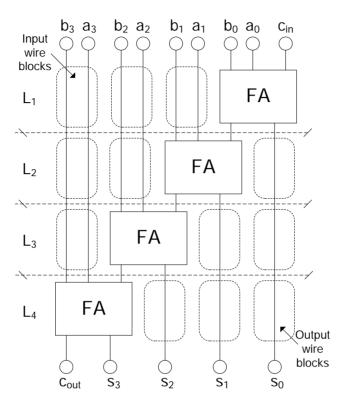

| 8  | Full adder, simulation waveforms                                 | 33 |

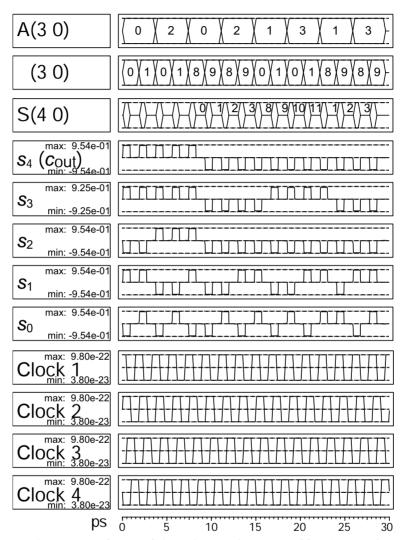

| 9  | Ripple carry adder, simulation waveforms                         | 34 |

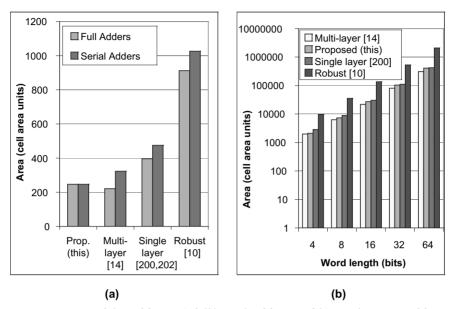

| 10 | Adder circuit area comparison                                    | 38 |

| 11 | Ripple carry adder, wiring overhead and active area              | 39 |

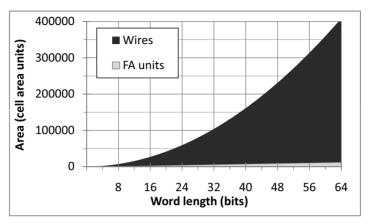

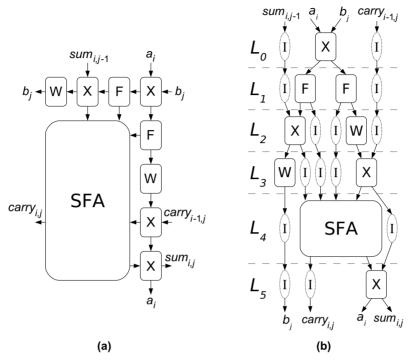

| 12 | Serial-parallel multiplier, logical structure                    | 43 |

| 13 | Serial-parallel multiplier, timing                               | 44 |

| 14 | Serial-parallel multiplier, QCA layout of the cell               | 45 |

| 15 | Serial-parallel multiplier, QCA layout of 3-bit and 16-bit units | 46 |

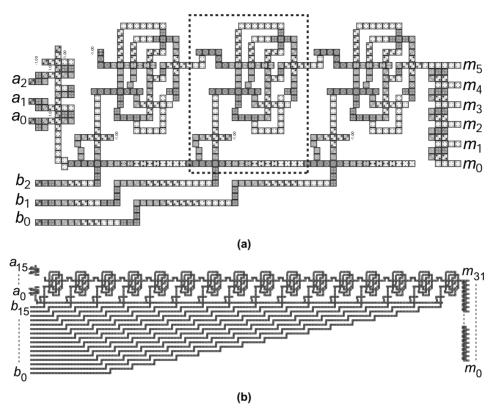

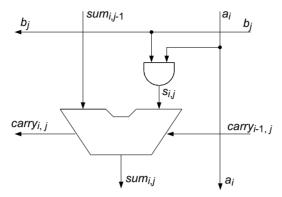

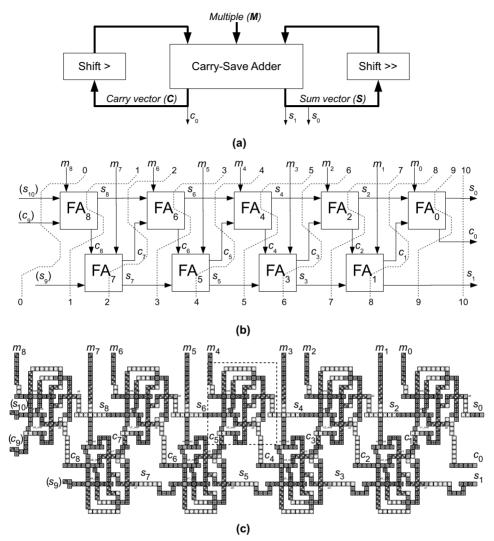

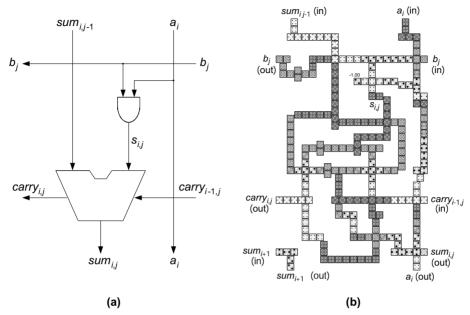

| 16 | Pipelined array multiplier, logical structure of the cell        | 47 |

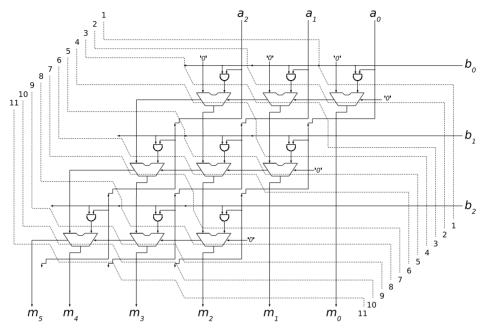

| 17 | Pipelined array multiplier, logical structure of 3-bit unit      | 48 |

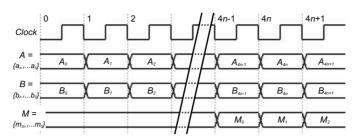

| 18 | Pipelined array multiplier, timing                               | 49 |

| 19 | Pipelined array multiplier, QCA layout of the cell               | 50 |

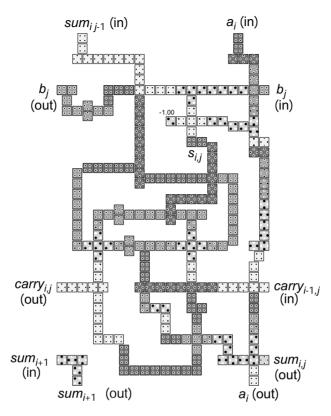

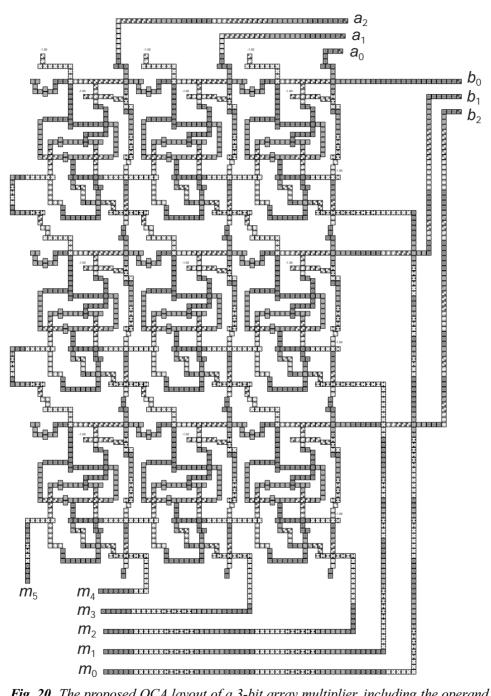

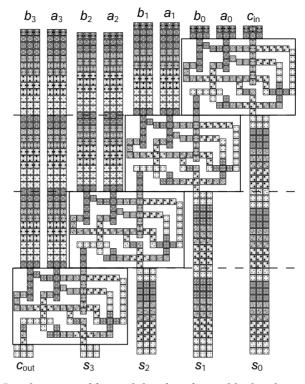

| 20 | Pipelined array multiplier, QCA layout of 3-bit unit             | 51 |

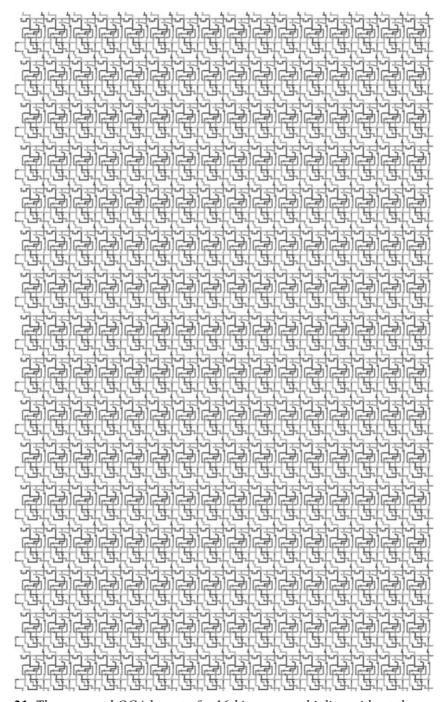

| 21 | Pipelined array multiplier, QCA layout of 16-bit unit            | 52 |

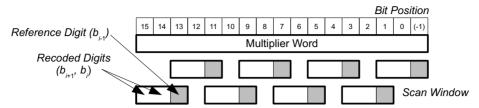

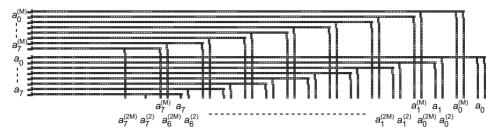

| 22 | Radix-4 multiplier, overlapped scanning                          | 54 |

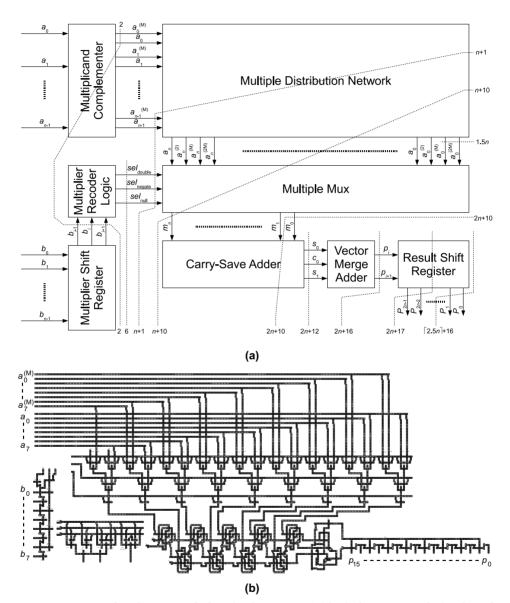

| 23 | Radix-4 multiplier, block diagram and QCA layout                 | 56  |

|----|------------------------------------------------------------------|-----|

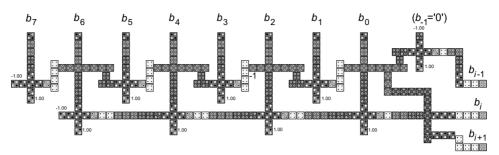

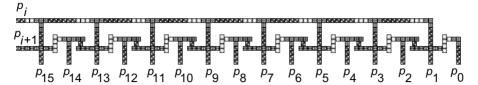

| 24 | Radix-4 multiplier, multiplier shift register                    | 58  |

| 25 | Radix-4 multiplier, multiplier recoder                           | 58  |

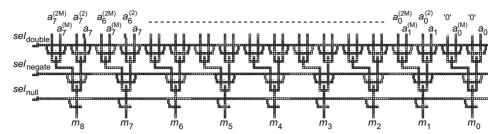

| 26 | Radix-4 multiplier, multiple distribution network                | 59  |

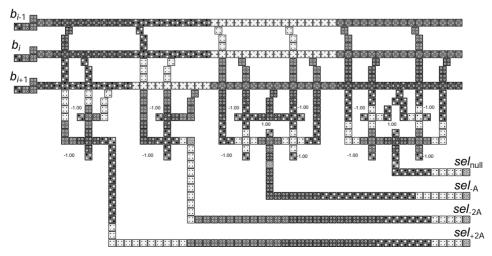

| 27 | Radix-4 multiplier, multiple selection mux                       | 60  |

| 28 | Radix-4 multiplier, sequential carry-save adder with shifting .  | 61  |

| 29 | Radix-4 multiplier, sequential vector merge adder                | 62  |

| 30 | Radix-4 multiplier, result shift register                        | 63  |

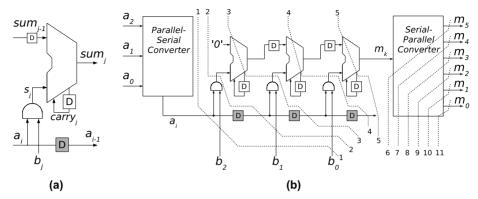

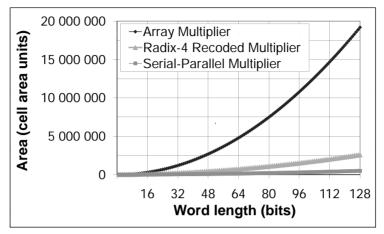

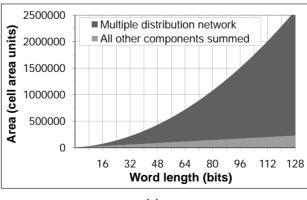

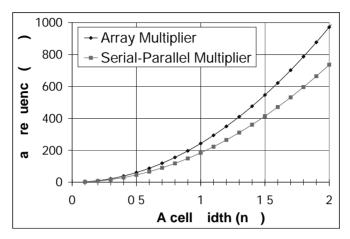

| 31 | Multiplier circuit area comparison                               | 66  |

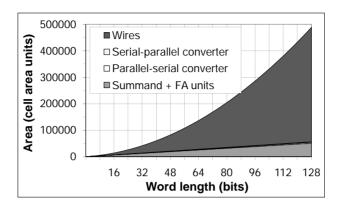

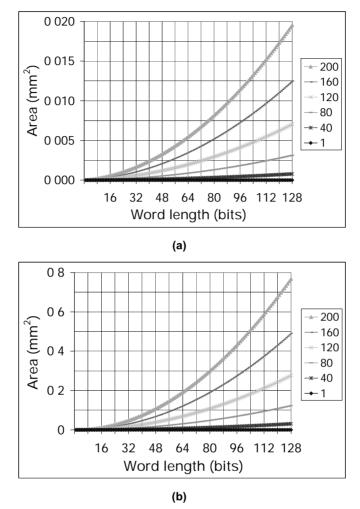

| 32 | Multiplier circuit area component contributions                  | 67  |

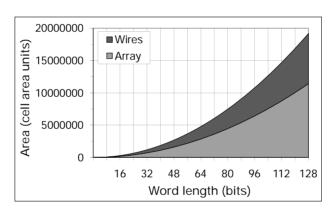

| 33 | Multiplier circuit area with different feature sizes             | 69  |

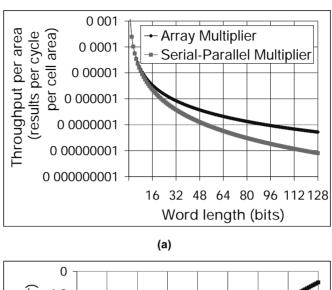

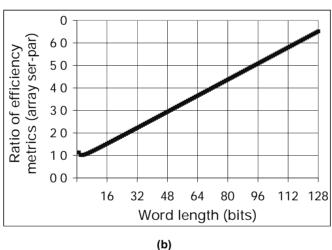

| 34 | Multiplier performance-area efficiency                           | 70  |

| 35 | Ripple carry adder, dependencies of the components               | 77  |

| 36 | Ripple carry adder, component probabilistic transfer matrices .  | 78  |

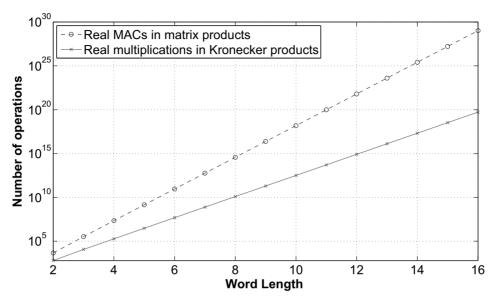

| 37 | Ripple carry adder, complexity of forming probability matrix .   | 79  |

| 38 | Ripple carry adder, hardened wire blocks                         | 83  |

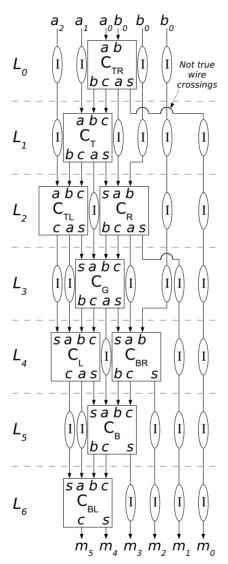

| 39 | Array multiplier cell, logical structure and QCA layout          | 84  |

| 40 | Array multiplier cell, components and dependencies               | 85  |

| 41 | Array multiplier cell, component probabilistic transfer matrices | 86  |

| 42 | Array multiplier, dependencies of the components                 | 87  |

| 43 | Array multiplier, total reliability vs. component failure rate   | 89  |

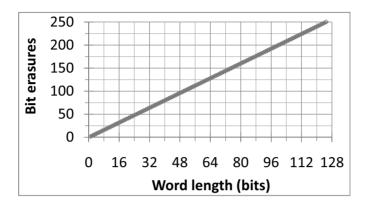

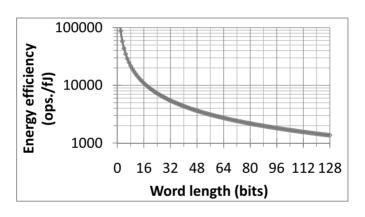

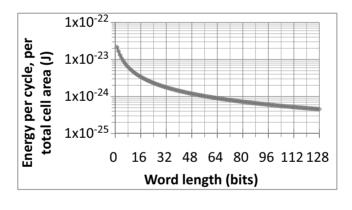

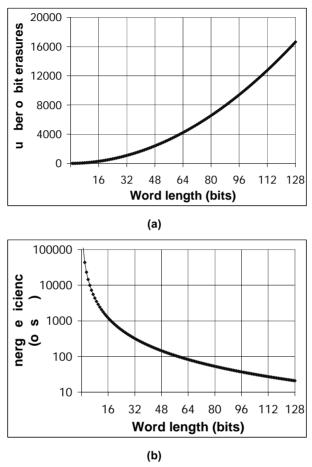

| 44 | Adder bit erasures and energy efficiency                         | 95  |

| 45 | Adder power density and energy comparison                        | 96  |

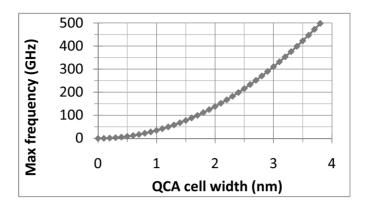

| 46 | Adder maximum operating frequency                                | 97  |

| 47 | Multiplier bit erasures and energy efficiency                    | 101 |

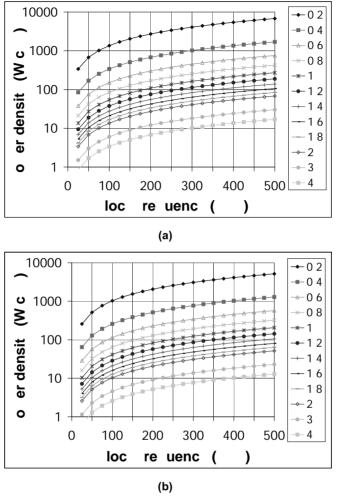

| 48 | Multiplier power density                                         | 102 |

| 49 | Multiplier maximum operating frequency                           | 103 |

# LIST OF TABLES

| 1  | QCA majority and minority gates' truth tables              | 11 |

|----|------------------------------------------------------------|----|

| 2  | Adder designs                                              | 36 |

| 3  | Adder performance and area comparison                      | 40 |

| 4  | Radix-4 multiplier, recoding function                      | 55 |

| 5  | Radix-4 multiplier, latency and area of the components     | 57 |

| 6  | Multiplier designs                                         | 65 |

| 7  | Multiplier performance and area comparison                 | 72 |

| 8  | Ripple carry adder, reliability approximation              | 80 |

| 9  | Ripple carry adder, 99% level reliability requirements     | 81 |

| 10 | Ripple carry adder, 99.999% level reliability requirements | 82 |

| 11 | Full adder truth table and state compression               | 94 |

### LIST OF ABBREVIATIONS

AM Array Multiplier

AOI And-Or-Inverter

ATPG Automatic Test Pattern Generation

CMOS Complementary Metal Oxide Semiconductor

CSA Carry-Save Adder

EQCA Extended Quantum-Dot Cellular Automata

FA Full Adder

FFT Fast Fourier Transform

GALS Globally Asynchronous, Locally Synchronous

HA Half Adder

IC Integrated Circuit

IEEE The Institute of Electrical and Electronics Engineers

ITM Ideal Transfer Matrix

ITRS International Technology Roadmap for Semiconductors

LSB Least Significant Bit

MAC Multiply-Accumulate

MSB Most Significant Bit

PIP Propagated Instruction Processor

PLA Programmable Logic Array

PTM Probabilistic Transfer Matrix

RAM Random Access Memory

RCA Ripple Carry Adder

RMQDA Restricted Minima Quantum-Dot Array

SA Serial Adder

SBSA Serial Bit-Stream Analyzer

SCQCA Split Current Quantum-Dot Cellular Automata

SD Signed-Digit

SFA Summand and Full Adder Block

SIMD Single Instruction, Multiple Data

TSC Totally Self-Checking

ULP Unit in the Last Position, the weight of LSB bit

Verilog Verilog Hardware Description Language

VHDL VHSIC Hardware Description Language

VHSIC Very High Speed Integrated Circuit

VLSI Very Large Scale Integration

QCA Quantum-Dot Cellular Automata

## LIST OF SYMBOLS

# Quantum-Dot Cellular Automata

| '0'     | bit with value zero              |

|---------|----------------------------------|

| '1'     | bit with value one               |

| in      | input binary signal              |

| $in_i$  | <i>i</i> th input binary signal  |

| out     | output binary signal             |

| $out_i$ | <i>i</i> th output binary signal |

# Binary Adders

| а         | input operand bit                                                                             |

|-----------|-----------------------------------------------------------------------------------------------|

| b         | input operand bit                                                                             |

| c         | input operand bit                                                                             |

| $c_{in}$  | input carry bit                                                                               |

| $c_{out}$ | output carry bit                                                                              |

| S         | output sum bit                                                                                |

| M(a,b,c)  | three-input majority function defined as $M(a,b,c)=(a\wedge b)\vee(b\wedge c)\vee(a\wedge c)$ |

| $\wedge$  | logical AND operation                                                                         |

| V         | logical OR operation                                                                          |

| n      | input operand word length (bits)                     |

|--------|------------------------------------------------------|

| $a_i$  | <i>i</i> th bit of the input operand word (0 is LSB) |

| $b_j$  | <i>j</i> th bit of the input operand word (0 is LSB) |

| $s_k$  | <i>k</i> th bit of the sum output word (0 is LSB)    |

| A(3:0) | 4-bit input operand word                             |

| B(3:0) | 4-bit input operand word                             |

| S(4:0) | 5-bit output sum word                                |

# Binary Multipliers

| n         | input operand word length (bits)                            |

|-----------|-------------------------------------------------------------|

| $a_i$     | <i>i</i> th bit of the first input operand word (0 is LSB)  |

| $b_j$     | <i>j</i> th bit of the second input operand word (0 is LSB) |

| A         | first input operand word (multiplicand)                     |

| $A_i$     | first input operand word, on index $i$ of a data word set   |

| В         | second input operand word (multiplier)                      |

| $B_j$     | second input operand word, on index $j$ of a data word set  |

| L         | latency of the complete result word (clock cycles)          |

| $L_{LSB}$ | latency of the least significant result bit (clock cycles)  |

| $L_{MSB}$ | latency of the most significant result bit (clock cycles)   |

|           |                                                             |

## Serial-Parallel Multiplier

| M         | output multiplication result word                                                 |

|-----------|-----------------------------------------------------------------------------------|

| $M_k$     | output multiplication result word, on index $k$ of a data word set                |

| $M_{k,i}$ | ith bit of the output multiplication result word, on index $k$ of a data word set |

| $M_{k,LSB}$ | LSB bit of the output multiplication result word, on index $k$ of a data word set |

|-------------|-----------------------------------------------------------------------------------|

| $M_{k,MSB}$ | MSB bit of the output multiplication result word, on index $k$ of a data word set |

| $m_k$       | kth bit of the multiplication result output word (0 is LSB)                       |

| $s_j$       | summand bit, cell index $j$                                                       |

| $sum_j$     | output sum bit, cell index $j$                                                    |

| $carry_j$   | output carry bit, cell index $j$                                                  |

### Array Multiplier

| M             | output multiplication result word                                  |

|---------------|--------------------------------------------------------------------|

| $M_k$         | output multiplication result word, on index $k$ of a data word set |

| $m_k$         | kth bit of the multiplication result word (0 is LSB)               |

| $s_{i,j}$     | summand bit, cell on column $i$ and row $j$                        |

| $sum_{i,j}$   | output sum bit, cell on column $i$ and row $j$                     |

| $carry_{i,j}$ | output carry bit, cell on column $i$ and row $j$                   |

### Radix-4 Multiplier

| $n_A$ | multiplicand operand word A length (bits) |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|

| $n_B$ | multiplier operand word B length (bits)   |  |  |  |  |

| $n_P$ | output result word P length (bits)        |  |  |  |  |

| P     | output multiplication result word         |  |  |  |  |

| M     | internal multiple word                    |  |  |  |  |

| S     | internal sum vector                       |  |  |  |  |

| C     | internal carry vector                     |  |  |  |  |

| +A    | positive multiple word (the multiplicand) |  |  |  |  |

| +2A                   | doubled multiple word                                                        |

|-----------------------|------------------------------------------------------------------------------|

| -A                    | negated multiple word                                                        |

| -2A                   | doubled negated multiple word                                                |

| $p_i$                 | ith bit of the multiplication result output word (0 is LSB)                  |

| $m_i$                 | ith bit of the internal multiple word (0 is LSB)                             |

| $s_j$                 | jth bit of the sum vector (0 is LSB)                                         |

| $c_k$                 | kth bit of the carry vector (0 is LSB)                                       |

| $a_i^{(2)}$           | <i>i</i> th bit of the doubled multiple word (0 is LSB)                      |

| $a_i^{(M)}$           | ith bit of the negated multiple word (0 is LSB)                              |

| $a_i^{(2M)}$          | ith bit of the doubled negated multiple word (0 is LSB)                      |

| Cinter                | internal inter-digit carry bit                                               |

| C <sub>intra</sub>    | internal intra-digit carry bit                                               |

| >                     | 1-bit arithmetic shift to right                                              |

| >>                    | 2-bit arithmetic shift to right                                              |

| $sel_{double}$        | mux control signal for selecting doubled multiple (active high)              |

| sel <sub>negate</sub> | mux control signal for selecting negated multiple (active high)              |

| $sel_{null}$          | mux control signal for selecting zero multiple (active high)                 |

| $sel_{-A}$            | internal control signal for selecting negated multiple (active high)         |

| $sel_{-2A}$           | internal control signal for selecting doubled negated multiple (active high) |

| $sel_{+2A}$           | internal control signal for selecting doubled multiple (active high)         |

| $L_{total}$           | latency of the complete result word (clock cycles)                           |

# Reliability Analysis

| n         | input operand word length (bits)                         |

|-----------|----------------------------------------------------------|

| $a_i$     | <i>i</i> th bit of the input operand word (0 is LSB)     |

| $b_j$     | <i>j</i> th bit of the input operand word (0 is LSB)     |

| $L_i$     | ith row parallel component level                         |

| $\otimes$ | Kronecker (alternatively tensor) product                 |

| *         | element-wise matrix multiplication                       |

| $P_i$     | PTM of the parallel components on row $i$                |

| ν         | vector representing the probabilities of each input case |

| R         | total reliability, confidence of no failures             |

|           |                                                          |

## Ripple Carry Adder

| $s_k$           | <i>k</i> th bit of the sum output word (0 is LSB)        |

|-----------------|----------------------------------------------------------|

| $C_{out}$       | output carry bit                                         |

| $P_{RCA}$       | PTM of the complete ripple carry adder                   |

| $P_{RCA,ideal}$ | ITM of the complete ripple carry adder                   |

| $P_{FA}$        | PTM of a full adder                                      |

| $P_{IW}$        | PTM of an input wire block                               |

| $P_{OW}$        | PTM of an output wire block                              |

| p               | uniform signal error probability                         |

| $p_{FA}$        | uniform full adder component error probability           |

| $p_W$           | uniform wire component error probability                 |

| a               | full adder contribution in the reliability approximation |

| b               | wire block contribution in the reliability approximation |

### Array Multiplier

$s_{i,j}$  summand bit, cell on column i and row j

$sum_{i,j}$  output sum bit, cell on column i and row j

$carry_{i,j}$  output carry bit, cell on column i and row j

$m_k$  kth bit of the multiplication result word (0 is LSB)

$P_{AM}$  PTM of the complete array multiplier

$P_{AM,ideal}$  ITM of the complete array multiplier

$P_{SFA}$  PTM of a summand and full adder block

$P_W$  PTM of a wire block

$P_F$  PTM of a fanout block

$P_X$  PTM of a wire crossing block

$P_I$  PTM of an ideal wire

$P_{C,TR}$  PTM of the cell at top-right corner

$P_{C,T}$  PTM of the cells in the middle of top row

$P_{C,TL}$  PTM of the cell at top-left corner

$P_{C,R}$  PTM of the cells in the middle of rightmost column

$P_{C,G}$  PTM of the general cells in the middle

$P_{C,L}$  PTM of the cells in the middle of leftmost column

$P_{C,BR}$  PTM of the cell at bottom-right corner

$P_{C,B}$  PTM of the cells in the middle of bottom row

$P_{C,BL}$  PTM of the cell at bottom-left corner

$p_A$  uniform active logic error probability

$p_W$  uniform wire component error probability

# Power Analysis

| n         | input operand word length (bits)                             |

|-----------|--------------------------------------------------------------|

| $E_{sig}$ | logical signal minimum energy content                        |

| $E_{dis}$ | energy loss due to single bit erasure                        |

| $k_B$     | the Boltzmann constant, $1.3807 \times 10^{-23} \text{ J/K}$ |

| T         | temperature in Kelvin degrees                                |

#### LIST OF PUBLICATIONS

This thesis is a monograph, which contains some unpublished material, but is mainly based on the work already published in the following peer-reviewed international publications. In the text, these publications are referred to as [P1], [P2],..., [P8].

- [P1] I. Hänninen and J. Takala, "Robust adders based on quantum-dot cellular automata," in *Proceedings of the IEEE International Conference on Application-specific Systems, Architectures and Processors*, Montréal, QC, Canada, Jul. 8-11, 2007, pp. 391–396.

- [P2] I. Hänninen and J. Takala, "Pipelined array multiplier based on quantum-dot cellular automata," in *Proceedings of the European Conference on Circuit Theory and Design*, Seville, Spain, Aug. 26-30, 2007, pp. 938-941.

- [P3] I. Hänninen and J. Takala, "Binary multipliers on quantum-dot cellular automata," *Facta Universitatis*, vol. 20, no. 3, pp. 541-560, Dec. 2007. [Online]. Available: http://factaee.elfak.ni.ac.yu/fu2k73/15hanninen.html

- [P4] I. Hänninen and J. Takala, "Reliability of n-bit nanotechnology adder," in *Proceedings of the IEEE Computer Society Annual Symposium on VLSI*, Montpellier, France, Apr. 7-9, 2008, pp. 34-39.

- [P5] I. Hänninen and J. Takala, "Arithmetic design on quantum-dot cellular automata nanotechnology," in *Embedded Computer Systems: Architectures, Modeling, and Simulation*, ser. Lecture Notes in Computer Science, M. Bereković, N. Dimopoulos, and S. Wong, Eds. Berlin/Heidelberg, Germany: Springer, 2008, vol. 5114, pp. 43-52.

- [P6] I. Hänninen and J. Takala, "Reliability of a QCA array multiplier," in *Proceedings of the IEEE Conference on Nanotechnology*, Arlington, TX, USA, Aug. 18-21, 2008, pp. 315–318.

- [P7] I. Hänninen and J. Takala, "Binary adders on quantum-dot cellular automata," to appear in *Journal of Signal Processing Systems* (Springer, New York, NY, USA). [Online]. Available: http://dx.doi.org/10.1007/s11265-008-0284-5

- [P8] I. Hänninen and J. Takala, "Radix-4 recoded multiplier on quantum-dot cellular automata," in *Embedded Computer Systems: Architectures, Modeling, and Simulation*, ser. Lecture Notes in Computer Science, K. Bertels, N. Dimopoulos, C. Silvano, and S. Wong, Eds. Berlin/Heidelberg, Germany: Springer, 2009, vol. 5657, pp. 118–127.

#### 1. INTRODUCTION

The computing power offered by the integrated circuit (IC) technology has grown exponentially for nearly five decades, following the *Moore's Law* (original 1965 [1], updated later [2]): the number of primitive components per chip doubles every eighteen to twenty-four months, consequently doubling also the number of the available memory bits and computation operations per time unit. This trend, broken down in detail in the International Technology Roadmap for Semiconductors (ITRS) reports [3], has enabled the modern-day world and plays a prominent role in the development of all fields of science and engineering. However, the progress of IC industry is in danger of halting soon, if only traditional computer hardware technologies are utilized.

### 1.1 The Necessary Technology Transition

In about a decade, the traditional digital circuit technologies are reaching their practical and theoretical limits, as the beneficial continuous downscaling of electronics becomes more challenging. Most technologies, like the nearly everywhere present complementary metal oxide semiconductor (CMOS), use transistors as current switches, representing binary information as currents and voltages. However, these primitive devices have several problems when they get really small: the on/off levels become inadequate, the leakage currents significant, the resistance high, the charge quantized, and the wires very large in comparison with the active devices. [3]

In the long run, the most severe problem is the heat generation, as the circuit capacitances are charged to a potential and again discharged to ground, usu-

ally wasting nearly all of the energy contained in the logic signal. This is already a problem with the present technologies, but if molecular device densities are reached, the problem becomes truly unmanageable: on the operational frequencies of hundreds of gigahertz, with each transistor moving only *one* electron across one volt potential, the power densities reach the *megawatt* per square centimeter region. Careful adiabatic charging can lower the power dissipation, but not enough to enable true molecular electronics. [4]

Several *emerging technologies* have been proposed to replace the current semiconductor transistor approach. Quantum-dot cellular automata nanotechnology (QCA) is one of the foremost candidates, offering robust ways to reach circuit densities  $10^{11}$  to  $10^{12}$  devices/cm<sup>2</sup> and clock frequencies several orders of magnitude higher than the expected technological peak of the CMOS. The concept was introduced in the early 1990s [5,6] and has already been demonstrated in laboratory environment with small proof-of-concept systems [7–9], but adopting QCA into general use requires still considerable advances both in the design methodology and the manufacturing processes.

### 1.2 Bringing the Emerging Technologies Into Use

There is a definite need for pressing the emerging technologies into service, but this is very challenging, due to novel characteristics complicating both the digital design process and the actual physical manufacturing. Early research into QCA circuits and systems has demonstrated that these two levels of engineering work are much more tightly coupled than on the traditional technologies. The digital designer has to aim at an optimized end product while being well aware of the underlying implementation technology.

Design optimization can be characterized with several comparable metrics of performance and cost, which are affected by the chosen computation algorithm, hardware structure, and logical components. The relationship between the designer choices and the quality of the results is governed by novel principles, on the emerging technologies. For example, on QCA a logic signal is

propagated by the copy-operation from a cell automaton to another, and with high operating frequencies, the automata wires are relatively long in comparison with the distance that the signal can propagate during a clock cycle. Thus, the length of a wire translates directly into significant delay and distinct number of pipeline stages, which has tremendous effect on which types of arithmetic units are practical. Another important issue is the underlying imperfect cellular interaction, which also has to be compensated by applying sub-gate level pipelining.

The emerging technologies are inherently unreliable, both the manufacturing processes and the runtime operation of a chip inside a computer system. Circuit primitives will deviate from the traditional, practically deterministic behavior and operate with stochastic characteristics, raising general *design-for-reliability* to top concern. Improvements can be aimed at various design levels, typically introducing redundancy or reconfigurability into the system, with a significant cost increase. The unreliable physical layer has to be taken into account from the start of the design work, or getting a complete system to run might turn out to be so expensive, that the gains of applying new technology would be totally lost. Fault-tolerant design requires profound understanding about the relationship between physical implementation and design abstractions, and this understanding can be found with the aid of reliability analysis techniques.

Power consumption and the resulting heat dissipation already set the performance limit of the traditional digital circuits, but this is an even more dominating cost factor for the emerging technologies: there is room for a tremendous number of devices in the nanoworld, having possibly molecular device densities. The combined heat generation must not exceed what we can cool off, and as each device is allowed to dissipate less and less, we possibly need a paradigm shift from irreversible computing to reversible computing. The already present *design-for-power* trend reaches unprecedented weight in the industry, when the reversibility aspects have to be addressed.

### 1.3 Objectives and Research Statements

The objective of this thesis is to find more efficient methods of designing and analyzing arithmetic circuits on the QCA technology, and solutions to the following problem statements are presented:

How to design cost-efficient basic arithmetic circuits, accounting for the imperfect cellular interaction inherent to QCA? The arithmetic circuits on QCA have been studied only very little, leaving the analysis of the traditional design metrics of performance and complexity superficial. Especially, the technology-inherent noise coupling interaction has not been taken into account, or has been avoided with an unjustified performance penalty, preventing the use of the resulting basic blocks to construct multi-bit arithmetic [10]. Several standard arithmetic structures have not been adapted to QCA, at all.

Which factors contribute to the measurable design characteristics on QCA? The effects of algorithmic, structural, and component choices on performance and cost metrics have previously been analyzed only very little, especially the gains vs. the costs of parallelism in the computation [11–14]. Neither the contribution of active and passive circuitry, nor the role of the operand word length, has been established.

How reliable should the QCA primitive devices be, to enable the construction of large arithmetic units? The existing designs have not been adequately analyzed, to find out where the costly reliability improvements could be most beneficially aimed at [15]. Especially, macroblock level analysis, needed to hierarchically model large arithmetic units, has not been conducted before, and it has not been established how the underlying device failure rate requirements scale with the operand word length. There has been very little work on the dependencies of architectural decisions and reliability, on QCA.

What is the role of irreversible power dissipation in QCA arithmetic? The dissipation characteristics of large designs, including macrocomponent level contributions, have not been analyzed although some work has been conducted on the primitive device level power and energy dynamics [16, 17].

Especially, operating frequency limitations of complete arithmetic units on molecular QCA have not been determined and the major limiting factor, information erasure dissipation (irreversibility), has not been identified before. It has not been clear, whether the costly reversible computing paradigm is necessary, for reaching maximum performance on the technology.

#### 1.4 Main Contributions

This thesis provides a practical view on digital design work on QCA, using several case studies to illustrate the various aspects of constructing highly parallel (in a general sense, including several co-existing data sets in a pipeline) hardware structures with this computing paradigm, offering potential nanotechnology implementations. The studied arithmetic units are sufficiently massive to reveal the fundamental characteristics, while retaining enough structural regularity to enable modeling and simulation to some extent. In short, the main contributions are described in the following:

Efficient arithmetic designs for QCA. The presented techniques allow the construction of high-density, performance optimized, and noise tolerant basic arithmetic circuits on QCA. Several novel arithmetic units are designed, utilizing the inherent characteristics of the technology, and aiming at modularity and customization to varying operand word lengths. The designs are described at the logic, the pipeline, and the layout level, and verified with quantum mechanical simulation.

- Novel binary adder units for QCA technology:

- Robust full adder, with minimized area using only one QCA fabrication layer.

- Robust serial adder, with minimized area and latency, and maximum throughput.

- Pipelined ripple carry adder, with noise robustness, minimized area and latency, and maximum throughput.

- Novel binary multiplier units for QCA technology:

- Serial-parallel multiplier, with noise robustness.

- Pipelined array multiplier, with noise robustness and highest performance-area efficiency.

- Radix-4 multiplier, with noise robustness and customizable degree of parallelism (the most flexible algorithm on QCA, thus far).

**Design analysis factors on QCA arithmetic.** The analysis of the presented arithmetic designs and cases reported in the literature leads to the following conclusions, on the relationship between the degree of parallelism and the traditional design metrics, on pipelined QCA:

- The basic serial and pipelined arithmetic structures have equal latency, but the throughput differs, following the degree of general parallelism.

- Passive wiring overhead typically dominates the circuit area, with a square-law dependency on the operand word length.

Reliability analysis and improvement on QCA arithmetic. The reliability levels of complete arithmetic units are established via probabilistic analysis, hierarchically constructing the total failure rate from the failure rates of the underlying components. For the important cases of the pipelined ripple carry adder and the pipelined array multiplier, the following conclusions are drawn:

- Bit-stage level macro component (a full adder, for example) reliability has about linear effect on the total reliability.

- Component types affect the total reliability with different weights, depending on the operand word length.

- Passive wiring overhead dominates also the reliability.

• Large operand length arithmetic on the failure-rich tecnologies is not feasible, unless a multi-level redundancy scheme is developed for tolerating very high primitive component failure rates. (However, complete fault-tolerant design methodology is out of the scope of the thesis.)

**Electrical power analysis on QCA arithmetic.** The power dissipation of complete arithmetic units is analyzed near the ultimate limit of computation efficiency, using the Landauer's principle [18]. Based on the pipelined ripple carry adder, the pipelined array multiplier, and the serial-parallel multiplier, the following conclusions are drawn for molecular QCA:

- Irreversible information erasures consume significant power, as opposed to the situation on traditional technologies.

- Clock frequencies of the designs are limited much lower than the expected switching speeds of the primitive devices.

- Reaching the full technology potential requires reversible computing principles, to be incorporated into the designs.

All the achieved results, modeling, designing and optimization work presented as the contribution of this thesis were developed by the author. The work was reported earlier in eight publications [P1]– [P8] and the author was the main author in all of them. Consequently, some chapters contain verbatim extracts from those papers while the copyrights of the extracts are retained by the respective copyright holders.

### 1.5 Thesis Outline

An introduction to the quantum-dot cellular automata computing paradigm is given in Chapter 2, describing the basic circuit constructs, interconnects, signal dynamics, clocking approaches, physical implementation variants, available modeling approaches, and digital design efforts. Next, novel arithmetic

units, adders and multipliers, are proposed at the logic, the pipeline, and the QCA layout level, including performance and cost comparison with previous design proposals, in Chapters 3 and 4, respectively.

Chapter 5 presents a reliability study based on probabilistic transfer matrices, which are used to formulate the component failure rates of two of the proposed arithmetic designs, the pipelined ripple carry adder and the array multiplier. Chapter 6 continues with a power analysis at the fundamental Landauer's limit, determining the absolute minimum power dissipation that the laws of the nature allow for the QCA ripple carry adder, serial-parallel multiplier, and array multiplier. Finally, Chapter 7 concludes the thesis.

### 2. QUANTUM-DOT CELLULAR AUTOMATA

The quantum-dot cellular automata (QCA) concept is very intuitive: we have bistable cellular automata, which are operated under clocked control. There are various ways to construct the physical cells and apply the clocking, but the implementation technologies are still under development. As a result, this treatment stays mostly at an abstract level without the physical details. A survey on the history of the development of the general cellular automata concept can be found in [19].

**Chapter Contents.** The general principles of constructing the circuit primitives are introduced in Sec. 2.1 and Sec. 2.2, the signal dynamics behavior described in Sec. 2.3, and the clocking approaches enabling inherent pipelining summarized in Sec. 2.4. This account is valid for all QCA implementations based on the *electrostatic interaction*, which is believed to offer the best performance, in comparison with other possible approaches (which utilize the magnetic coupling). For completeness, the QCA physical implementation variants are introduced in Sec. 2.5, and the simulation models described briefly in Sec. 2.6. The conclusion of the chapter follows in Sec. 2.7 with a survey into general digital design for QCA.

## 2.1 QCA Basics

The information storage and transport on electrostatic quantum-dot cellular automata [6] is based on the local position of charged particles inside a small section of the circuit, called a cellular automaton (which is essentially a structured charge container), and there is no electrical particle current in the circuit

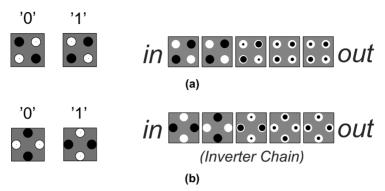

Fig. 1. QCA cell polarizations and wires: a) type 1 cell, direct non-inverting wire, and b) type 2 cell, inverter chain wire. The four quantum-dots of a cell function as localization centers for electrons: white dot denotes empty center, black dot denotes a center with an electron, and smaller black dots denote smaller localization likelihood during switching. These binary cells are the standard approach, but cells with other dot arrangements can be constructed.

at all. The QCA cell has a limited number of quantum-dots, which the particles can occupy, and these dots are arranged such that the cell can have only two polarizations (two degenerate quantum mechanical ground states), representing binary value zero or one. A cell can switch between the two states by letting the charged particles tunnel between the dots quantum mechanically.

The cells exchange information by classical Coulombic interaction. An input cell forced to a polarization drives the next cell into the same polarization, since this combination of states has minimum energy in the electric field between the charged particles in neighboring cells. Information is copied and propagated in a wire consisting of the cell automata. Figure 1 shows the available two cell types and the corresponding wires.

The QCA cells can form the primitive logic gates shown in Fig. 2. The simplest structure, the inverter, is usually formed by placing the cells with only their corners touching. The electrostatic interaction is inverted, because the quantum-dots of different polarizations are misaligned between the cells. The other gates are usually based on a three-input majority gate of the cell type one, relaxing to minimum energy between the input and output cells, having the truth table shown in Table 1. The gate performs the two-input AND-

**Fig. 2.** QCA primitive logic gates: a) different inverters, b) 3-input majority gate, and c) 3-input minority gate. Gray levels indicate different clocking zones, required to achieve reliable operation without noise coupling (see Sec. 2.3).

operation when the third input is fixed at logical zero, and the two-input OR-operation when the third input is fixed at logical one. This completes a universal logic set, capable of implementing any combinatorial computation. [5]

The majority gate is classified as a threshold gate, where the sum of weighted inputs has to exceed a given threshold value before the output is set (an introduction to threshold logic can be found in [20]). Synthesis of general majority logic for the nanotechnologies was considered in [21, 22], while an optimal representation of 3-minterm Boolean logic using majority gates was developed in [23, 24]. An alternative universal logic approach is based on a very similar *minority gate*, constructed with the cell type two [25].

**Table 1.** Truth tables of the QCA majority and minority gates, enabling AND, OR, NAND, and NOR operations.

| Majority Gate |        |                 |                 |     |  |  |

|---------------|--------|-----------------|-----------------|-----|--|--|

|               | $in_1$ | in <sub>2</sub> | in <sub>3</sub> | out |  |  |

| Two-input     | 0      | 0               | 0               | 0   |  |  |

| AND           | 0      | 0               | 1               | 0   |  |  |

| $(in_1=0)$    | 0      | 1               | 0               | 0   |  |  |

|               | 0      | 1               | 1               | 1   |  |  |

| Two-input     | 1      | 0               | 0               | 0   |  |  |

| OR            | 1      | 0               | 1               | 1   |  |  |

| $(in_1 = 1)$  | 1      | 1               | 0               | 1   |  |  |

|               | 1      | 1               | 1               | 1   |  |  |

Majority Gate

| Minority Gate |        |        |                 |     |  |

|---------------|--------|--------|-----------------|-----|--|

|               | $in_1$ | $in_2$ | in <sub>3</sub> | out |  |

| Two-input     | 0      | 0      | 0               | 1   |  |

| NAND          | 0      | 0      | 1               | 1   |  |

| $(in_1 = 0)$  | 0      | 1      | 0               | 1   |  |

|               | 0      | 1      | 1               | 0   |  |

| Two-input     | 1      | 0      | 0               | 1   |  |

| NOR           | 1      | 0      | 1               | 0   |  |

| $(in_1 = 1)$  | 1      | 1      | 0               | 0   |  |

|               | 1      | 1      | 1               | 0   |  |

NI:-- - --:4--- C - 4 -

The QCA cells can be used to construct also more complex gate-level primitives, which could make circuit synthesis easier. An *and-or-inverter* (AOI) gate has been proposed in [26,27], and other programmable multi-input gates constructed using several majority voters in [28,29]. For increased robustness against defects and faults, a *block majority gate* was proposed in [30,31], and  $3 \times 3$  cell grid *tile-based design* in [32–35].

It should be noted, that QCA is usually classical digital computing, not quantum computing: the binary information is contained in the classical degrees of freedom, instead of the superposition of states, while the quantum effects are used only to enable switching. Still, it is possible to construct both true quantum computers and analog information processors based on QCA [36]. Allowing multi-state cells enables also discrete ternary logic, based on the extended quantum-dot cellular automata (EQCA) [37,38].

### 2.2 Interconnects

Physical distance translates directly into timing delay and distinct number of pipeline stages, on QCA. Another important characteristic of the interconnects is the capability to create signal wire crossing in several ways.

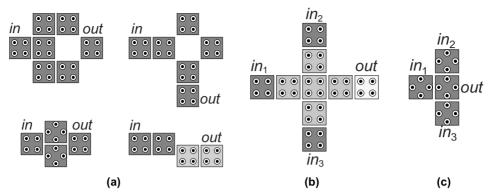

Coplanar Crossing. The two basic cell types are orthogonal and can be positioned to have minimal interaction with each other, enabling the coplanar wire crossing shown in Fig. 3(a). One of the wires uses only cell type one, while the other uses only cell type two, resulting in the wires operating independently on the same fabricational layer. With this approach, it is possible to implement all the logic and interconnects on a single QCA layer, with no counterpart in the traditional technologies. The problem of the coplanar crossing is the high sensitivity to manufacturing faults: misplaced cells can easily break the symmetrical arrangement, leading to unwanted signal coupling between the two wires [39]. A recent effort to increase the robustness of the structure against defects and thermal effects can be found in [40,41].

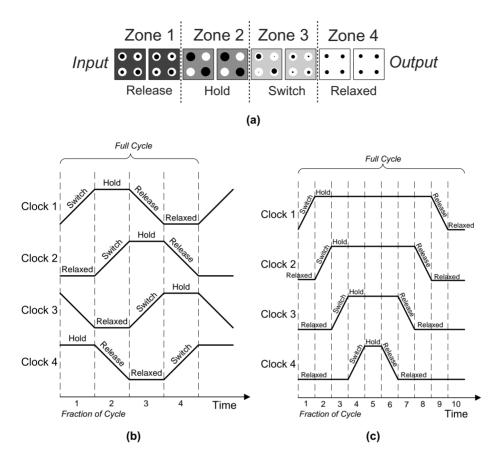

Fig. 3. QCA wire crossings: a) coplanar crossing, with the gray levels indicating different clocking zones, required to achieve reliable operation without noise coupling (see Sec. 2.3), and b) multi-layer crossing.

Multi-Layer Crossing. A traditional multi-layer crossing shown in Fig. 3(b) can be constructed with either cell type, as long as the vertical distance of the wires is large enough to prevent signal leaking from one layer to another, and there is a way to create vias of stacked cells between the layers. This approach is more tolerant to misplaced cells than the coplanar crossing, but requires an implementation technology with many active QCA layers on top of each other [42]. Another possibility is to create the vias and crossing layer using another technology, for example CMOS. The multi-layer technologies have not been demonstrated yet, and although the required precision of cell placement is not as high as with the pure single-layer technology, there are various other problems, which are likely to be as challenging. Due to this, the designs presented in this study use only the coplanar crossing.

**Logical Crossing.** Physical wire crossings can be eliminated by replacing them with logic gates, using node duplication, adjusting the timing of the crossing signals, or utilizing crossing-minimizing routing algorithms. Typically, this causes both area and performance penalty, but can be used to alleviate the manufacturing challenges considerably [43–47].

# 2.3 Signal Dynamics

The ideal QCA cell has very symmetrical and local interaction, but in real implementations, the electric field and quantum coherence transmit the interaction farther than the nearest neighbor. This weak interaction was earlier believed to be adequately canceled out by distance and layout symmetry, but a recent study clarified that the lack of *timing* symmetry can create sneak noise paths in crucial circuit structures. There is unwanted signal coupling between circuit sections, and even inside the primitive circuit elements. The problem is severe, as the QCA cells affect their neighbors in a very non-linear, bistable way: a small change in the polarization of a cell causes a much larger change in an un-polarized cell next to it, amplifying both the correct and the unwanted signals. Newly polarized cells provide positive feedback, which drives the injection point of the signal to an even stronger polarization [10,48]. This implementation problem was anticipated earlier by an esteemed physicist [49].

The coplanar wire crossing is extremely sensitive to noise coupling: In static case (when all the cells have settled to a polarization), the wire of the cell type two causes a symmetrical and effectively self-canceling interaction to the output side of the other wire, but in dynamical case (when the signals are arriving to the crossing), the polarization is at first present only at the input side, so that the compensating interaction from the output side is missing. This small unbalance causes the signal to couple into the output segment of the type one wire, followed by rapid copying from cell to cell and amplification, making the later compensation insignificant. When the real signal of the type one wire arrives to the crossing, it will not be strong enough to switch the output segment already settled in strong erroneous polarization.

The majority gate is also sensitive to signal timing, as the requirement for fair majority voting is, that all the input signals must be present with equal magnitude, when the active center cell starts to switch. If there is glitching in the center cell, the erroneous polarization gets copied to the output section of the gate, which effectively functions as a noise amplifier. However, the problem with both of these circuit primitives can be fixed with timing constraints:

the real input signals must be present and driving strongly, when the crucial circuit section begins to switch. QCA clocking schemes potentially offer the capability for this. (Explanation of the clocking follows in Sec. 2.4.)

**Zone Clocking.** A simple arrangement of the QCA clocking zones ensures, that the real signals beat the noise signals racing through the circuit [10, 48]. A coplanar wire crossing functions correctly, when the output section of the cut wire is switched only after the other parts have firmly settled. Similarly, a majority gate functions reliably when it is placed on three clocking zones: the first zone secures the inputs, the second zone performs majority voting, and the third zone latches the result. Such zone assignments are shown with different gray levels in Fig. 2 and 3.

Wave Clocking. There is no robust method of avoiding noise coupling under wave clocking (coarse inhomogeneous clocking field), because we cannot control precisely, which cells are contained in the switching section at each moment. Careful design and precise manufacturing might enable the coplanar wire crossing and the majority gate to work, but it is still unknown, if this can be reliably achieved [50]. In view of this, only designs based on the robust clocking zone approach are considered in this thesis.

## 2.4 Clocking Approaches and Pipelining

On QCA, a clocking mechanism determines via an electric field when the cells are un-polarized, latch their input values, and start driving other cells. It is used both for designing sequential circuits, creating pipelines, and forcing the circuit to stay in the quantum mechanical ground state, which depends on the inputs of the circuit, and represents the correct computational result and successful signal propagation. The clock provides also additional energy, enabling true signal gain on this nanotechnology. Non-clocked cell arrays seem unpractical, since they relax to the ground state too slowly [51].

A large array of cells switching at the same time can get stuck in a local energy minimum of the combined electric field, called a *kink* state, never reaching the

ground state, producing an erroneous computation result. To prevent this, the active phase of the clock is applied only to a small section of the circuit at each time instant, making the probability of the kink state to diminish [6]. The practical section size set by this phenomenon is not yet determined, but background thermal fluctuations set another upper limit: on molecular QCA, a single majority gate would function up to the temperature of 450 K, and a wire segment of 50 cells would still operate correctly at room temperature [52].

Clocking Structure. The section size can be restricted by dividing the cell array into zones controlled by different clocks, discrete clock phases for adjacent zones. This *zone clocking* [6] is simple and provides exact control for the timing of the circuit (over single QCA cell), but requires very fine-grained clocking circuit, possibly unpractical to manufacture on the molecular technologies. The clocking circuit underneath the cell layer can be made more coarse-grained and much easier to manufacture, if we increase the spacing between the clocking wires, and apply an inhomogeneous, smoothly graded electric field over the QCA plane. Multi-phase clocking signals cause the active clocking field to travel through the circuit in a continuous manner, creating a wave of computation. This *wave clocking* [53] approach was developed especially for molecular QCA, but it provides only coarse control over the timing of the circuit (grouping tens of cells together). A two-dimensional approach applicable for systolic structures was proposed in [54,55].

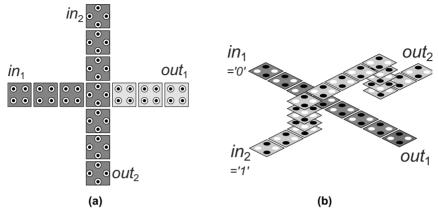

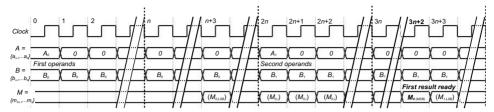

Clocking Waveforms. The waveforms of the usual Landauer-type clocking [6,53] are simple, and rely only on adiabatic switching principles to limit the dissipation of changing the state of a cell: the clock transition speed is limited, enabling the re-use of the signal energy already present in the circuit. Figure 4(a) shows a wire spanning four clocking zones and Fig. 4(b) the corresponding Landauer clock waveforms. During a complete cycle, each zone goes through the four phases (Release, Hold, Switch, and Relaxed, defined in [6]), and the wire effectively implements a stage of a micropipeline or a register. Since only one of the zones can hold a valid bit during a clock fraction, four zones are needed to construct one logical pipeline stage. This scheme is simple, but when applied to a circuit of normal irreversible logic, it leads

Fig. 4. QCA zone clocking: a) a wire spanning four clocking zones, shown at Landauer clock fraction three, b) Landauer clocking waveforms, and c) Bennett clocking waveforms.

to energy dissipation caused by erasing information [18], which becomes the dominant factor on molecular QCA with high operating frequencies [17].

As the ultimate power limits of irreversible computing are quickly reached, *Bennett-type clocking* [16,56] was recently proposed to achieve fully reversible operation on QCA, while using cheap irreversible logic gates. The underlying principle (originating from [57]) is that we first compute the results by latching the cell array, from the input side to the output side, and then uncompute by letting the array to relax to an unpolarized state, from the output side to the input side, eliminating most of the bit erasures and limiting the dissipation to

either the inputs or the outputs of the logic circuit. This scheme makes *any* QCA circuit fully reversible, without additional circuit area or complexity cost, while the penalty is paid fully in the timing. Figure 4(c) illustrates the Bennett clock waveforms, making a circuit spanning four clocking zones to operate reversibly, using more than twice the number of clock fractions, in comparison with the simple Landauer scheme. The major drawback is that the natural pipelining is lost, when all of the clocking zones are occupied by the same bit (one element of a data set in a pipeline). An improved floorplan to achieve general space/time tradeoff was proposed in [58].

# 2.5 Physical Implementations

There are various ways to construct the physical QCA cells with bistability and dominating local interaction, and apply the clocking, but the material systems are still very early in their development. Most of the research has been on intercellular electrostatic interaction, promising the best performance, implemented with metal-dot, semiconductor, or molecular approach. However, in the near future, the first large-scale circuits might be realized with magnetic interaction, with lower performance, but less challenging manufacturing [59].

An introduction to early work on the QCA implementation challenges can be found in [60], while image charge neutralization was considered in [61, 62], cell-level improvements to reach the ground state more robustly in [63, 64], and a three-dimensional layer approach to remove the metastable states proposed in [65]. *Restricted minima quantum-dot arrays* (RMQDA) concept, based on passive non-clocked wires and active clocked amplifier segments, was proposed in [66], and *split current QCA* (SCQCA), a technology based on resonant tunneling currents, was proposed in [67]. In the following, the main approaches to physical QCA implementation are summarized, the first three based on electrostatic interaction and the fourth on magnetic interaction.

**Metal-Island QCA.** The realization based on Coulomb blockade effect in tunnel junction connected metallic islands has been demonstrated in labora-

tory environment, but since the feature size is fairly large (around one micron dot-to-dot distance), the quantum mechanics needed for operation are present only in cryogenic sub-Kelvin temperatures. The experiments have been typically conducted at 15 mK [68], using liquid helium cooling, while 300 mK has been the highest reached temperature. This approach has enabled small proof-of-concept circuits (low-temperature prototypes of the future molecular systems), showing that the bistable cellular automata can be realized and switched by controlling the tunneling of electrons, but it is not practical to construct large circuits this way. [7–9, 69–82]

**Semiconductor QCA.** The semiconductor realization of the electrostatic cells promises a way to mass manufacturing of QCA circuits, since the industry has already decades of experience with the constantly improving processes. The challenge here is the need to reach extremely small feature size, for the circuits to operate above the sub-Kelvin temperatures. The future lithography processes might reach small enough granularities to enable a somewhat higher operating temperature, up to about 77 K [83], which could be acceptable in a supercomputer. Possible application is the classical part of a quantum computer, with state-of-the-art cooling system. [84–90]

**Molecular QCA.** The most desired implementation of QCA is based on single molecules acting as cells (transition metal atoms as quantum dots), as the molecules are naturally small enough (< 1 nm dot-to-dot distance) to enable the quantum effects at the room temperature, and they also lead to extremely high device densities. The challenge is again the manufacturing. First, large amounts of the right kind of molecules should be created, which seems very possible with chemical synthesis. Second, these cells should be deposited with unprecedented precision to form a circuit layout, which turns out to be very difficult. A promising way to do this might be high-resolution electron beam lithography combined with DNA self-assembly. [6,52,53,91–107]

**Magnetic QCA.** The other flavour of QCA uses bistable magnetic cells to store information, and magnetic coupling to transport it between the cells. The benefit of this is the availability of the crucial quantum effects also at high temperatures and relatively large feature sizes, which simplifies the manufac-

turing process very much. There have been several proposals to implement magnetic QCA, but common for all of them is the limited operating speed, for nanomagnets around 10–100 MHz. [108–116]

The designs presented in this thesis have been verified with a simulation model of the electrostatic QCA, but in principle, they should be relatively easy to adapt also to the magnetic technology. For example, the standard wire construct of a magnetic variant might be an inversion chain, which a design automation tool should handle correctly while translating wire blocks between the technologies. However, the tools do not exist, yet.

### 2.6 Simulation Models

High-abstraction level design models for QCA have not been much studied, but the logic behavior can be coarsely explored with simple digital bistable approximations. However, since the QCA circuits are still at such an early stage of research, more faithful modeling has to be done at the quantum mechanical level. As full quantum mechanics simulation is not computationally feasible for systems of even tens of the cellular automata, several approximations have been proposed for more practical circuit verification, but it is not yet clear, how well these approximations really match the physical implementations. Complete treatment of the quantum mechanical modeling of QCA circuits can be found in [36], while the main approaches are summarized in the following. The few technology-dependent design and simulation tools available are M-AQUINAS [85], Q-BART [117, 118], and QCADesigner [119–123], while a Bayesian network based probabilistic approach has been described in [124–128] and a Hopfield neural network based simulator in [129]. Classical SPICE tool based modeling has been proposed in [130–132].

The starting point is the *full quantum mechanical model*, where the fully coherent system is modeled by the many-body Schrödinger equation. This is feasible for a couple of cells only, since the computational burden scales exponentially with the number of cells, preventing use in system verification [133].

The problem can be slightly alleviated by approximating the cells as *coupled two-state systems*, which raises the circuit size limit to 10–15 cells. The way to model larger QCA circuits of practical size is the *Hartree-Fock approximation*, which models the intracellular dynamics quantum mechanically and the intercell interactions with classical Coulombic coupling [36]. The state variables of the Hartree-Fock approximation scale linearly with system size, but error is introduced by failure to model the time-dependent dynamics correctly, losing sight of the intercell correlations. An intermediate approximation accounting for second-order correlations was recently implemented in [122].

Implementation of the Hartree-Fock Approximation. The current state-of-the-art implementation of the Hartree-Fock approximation is included in the freely available QCADesigner tool [119–123], internally using coherence vector formalism, based on the density matrix approach. Each QCA cell is considered as a simple two-state system, represented by a Hamiltonian matrix. The charge neutral cells interact through a quadrupole-quadrupole moment, which decays inversely as a power of five of the distance between the cells, making it possible to limit the effective computation neighborhood.

The cell Hamiltonian is projected into a vector describing the energy environment of the cell on a Pauli spin basis. This is used to form the steady state coherence vector, describing the stationary energy state of the cell. The coherence vector represents the density matrix of a cell (as a Pauli spin projection, the polarization the third component), which is used in the equation of particle motion. For each cell, the simulation evaluates the equation of motion (a partial differential equation) using an explicit time marching algorithm.

Computational Complexity of the Hartree-Fock Approximation. The simulation model of an arbitrary circuit design (for example, a full adder unit) consists of a large array of parallel QCA cells, each having a polarization state and an effective neighborhood of interacting cells. The main parameters of the explicit time marching algorithm are the time step and total running time, which limit the accuracy and the reached evolution stage of the modeled system. For each time step taken, the computation has to be carried across the complete cell array; for each cell, this is equivalent to evaluating the energy

environment vector, the steady state coherence vector, and the equation of quantum mechanical particle motion of the coherence vector.

The main burden of computation is directly determined by the number of cells in the array, and the effective neighborhood of a cell. Typical QCA designs require that at least next-to-neighbor interactions have to be included in the energy environment of a cell, or some of the phenomena needed for the circuit to operate are missed completely. This means that the effective neighborhood consists of at least 24 cells, each of these containing two electrons participating in the combined energy state. On each simulation step, after updating the energy environment and steady state vectors of a cell, the coherence vector of the cell is stepped forward in time. The existing simulation engine evaluates the partial differential equation with the Euler method or the Runge-Kutta method, which are local constant complexity operations.

# 2.7 Digital Design

In addition to the development of the underlying implementation technology, there has been a considerable amount of research into circuit and systems design for QCA. The early research aims to shorten the time required to master the technology, utilizing the special characteristics from the physical layout to high level system design; the coplanar wire crossing, sub-gate level pipelining, processing-in-wire, and memory-in-motion paradigms enable very cost efficient logic, but they also present new design challenges.

**Memories.** Although QCA is inherently a self-latching technology, where even simple wires function as shift registers, several general purpose structures have been proposed to enable traditional RAM type addressable memory. Most of the proposed designs circulate the stored bits continuously inside a QCA wire loop, dynamically refreshing the value, and implementing a serial memory (an addressable shift register) [134–136], a fully parallel memory with one bit per loop [42, 120], or a serial-parallel hybrid [137–139]. More complex H-structured memory and the corresponding execution model have been proposed in [140–142], while the loop-based memory approach has been

replaced with a line-based approach, requiring special clocking zones and timing, in [143, 144]. A scheme to verify the timing of the basic memory structures using Verilog modeling has been presented in [145].

**Programmable logic.** Nanoscale circuits and architectures will have to tolerate higher percentages of defects than the current circuits, and the necessary redundancy can be flexibly provided by a programmable computing platform. Reconfigurable logic has been proposed for QCA in [29, 47, 83, 146–150].

**Processors.** In addition to the basic logic, more complex designs for QCA have been proposed, aimed at signal processing tasks. A serial bit-stream analyzer (SBSA) for telecommunications was proposed in [151, 152], an approach to synthesize energy minimizing QCA arrays for vision computing in [153], a SIMD array propagated instruction processor (PIP) for image processing in [154], a hybrid fast Fourier transform (FFT) processor with data permutation implemented using QCA in [155], and basic blocks for stochastic computing for signal processing in [156]. A general purpose microprocessor Simple 12 with universal clocking floorplan was proposed in [48, 117, 118, 157–159], and a design based on accumulator architecture in [42, 119, 160].

**Design Methodology.** Abstraction level can be raised to cope with large system complexity and to develop a systematic design flow, but this extremely important area has been only preliminary studied for QCA. A top-down methodology utilizing modeling with the standard VHDL language was described in [152], and an environment for behavioral and logic level QCA design (named HDLQ), generating Verilog code, was proposed in [161]. Tile-based modular approach was presented in [32–35, 135], and methodical construction of sequential systems in [162–164]. Globally asynchronous, locally synchronous (GALS) design approach was adapted to QCA to achieve layout-timing independent operation in [165–167].

**Design automation.** Coping with design complexity requires software tools, which transform a high-level digital system description into a valid description of the physical QCA layout, solving the general challenges of logic synthesis, placing and routing. Simple 3-minterm Boolean logic reduction to op-

timal majority logic was developed in [23,24], a genetic algorithm based optimizer in [168], synthesis of symmetric functions in [169] and mathematical cellular automata logic in [170], and evolutionary synthesis of small QCA circuits in [129,171]. A logic-level area cost model for synthesis was proposed in [172], while a true multi-level threshold/majority/minority network synthesis methodology and a tool (named MALS) were presented in [21,22,173, 174]. Physical design automation was divided into steps of clock zone partitioning, zone placement, and cell placement, providing the first partitioning and placement algorithm for automatic QCA layout generation, in [175–178]. Since wire crossings are crucial constructs on QCA, algorithmic approaches to crossing minimization have been developed in [43–46, 175].

**Testing, defects, and faults.** The defects and faults of the physical QCA implementations have not been experimentally established, but they are expected to turn out crucial to design feasibility. The basic types of QCA defects (cell displacement, misalignment, and omission) have been characterized and a testing scheme proposed in [179–182], the effects of scaling the size of the cells were inspected in [183, 184], and the defect tolerance properties of tile-based design were analyzed in [34, 35] and sequential systems in [162–164]. The effects of clock shifts and timing errors were simulated in [10,48,185,186], switching error likelihood determined using probabilistic networks in [128], general displacement tolerance studied in [39, 187, 188], and thermal robustness of the wire crossing schemes predicted in [40, 41]. Logic-level fault masking in crossbar-based programmable logic array (PLA) was considered in [150] and the applicability of N-detect stuck-at fault testing for QCA designs in [189]. Faults in logically reversible one dimensional QCA arrays were studied in [190–192], utilizing the bijective nature of the gates to simplify testing significantly. Automatic test pattern generation (ATPG) for combinatorial QCA logic was developed in [193–195]. For detecting system run-time errors, synthesis tool support for totally self-checking (TSC) threshold logic circuits was presented in [173], and triple modular redundancy with shifted operands was proposed as a circuit improvement in [196]. Block gates were proposed to obtain fault tolerance in [30, 31].

### 3. BINARY ADDERS

Previous arithmetic designs for QCA have not been optimized or the effects of optimization evaluated, leading to inefficiency and unacceptable penalty paid for the noise robustness (the dynamic problem of the physical cellular automata described in Sec. 2.3). The approaches presented here allow the construction of high-density, performance optimized, and noise tolerant basic adder circuits, utilizing the inherent characteristics of QCA technology, and aiming at modularity and customization to varying operand word lengths. Based on the novel designs and the literature, the relationship between the degree of parallelism (in the general sense of the term, including several coexisting data sets) and the traditional design metrics of performance and cost are analyzed, on pipelined QCA. This was reported earlier in [P1] and [P7].

**Chapter Contents.** The previous work on digital design and adders on QCA is summarized in Sec. 3.1, while the novel full adder, serial adder, and ripple carry adder units are described in Sec. 3.2, Sec. 3.3, and Sec. 3.4, respectively. The verification approach utilized for the proposed designs is reported in Sec. 3.5, and the design analysis presented in Sec. 3.6. The conclusion of the chapter follows in Sec. 3.7.

### 3.1 Previous Work

In addition to the development of the underlying implementation technology, there has been a considerable amount of research into circuit and systems design for QCA. The early research aims to shorten the time required to master this emerging technology, and even to guide its development with actual per-

formance and cost metrics. The special characteristics of QCA have not been encountered in traditional technologies, but in the nanotechnology implementations they affect everything, from the physical layout to high level system design. The coplanar wire crossing, ultra-fine-grained pipelining below logic gate level, processing-in-wire, and memory-in-motion paradigms enable very cost efficient logic, but they also present new design challenges. Introduction to the well-develop field of general computer arithmetic, including the addition algorithms and hardware structures, can be found in books [197, 198].