Tuomas Järvinen

Systematic Methods for Designing Stride Permutation Interconnections

Tampereen teknillinen yliopisto. Julkaisu 505 Tampere University of Technology. Publication 505

Tuomas Järvinen

# Systematic Methods for Designing Stride Permutation Interconnections

Thesis for the degree of Doctor of Technology to be presented with due permission for public examination and criticism in Tietotalo Building, Auditorium TB104, at Tampere University of Technology, on the 19th of November 2004, at 12 noon.

Tampereen teknillinen yliopisto - Tampere University of Technology Tampere 2004

ISBN 952-15-1263-6 (printed) ISBN 952-15-1395-0 (PDF) ISSN 1459-2045

## ABSTRACT

This Thesis considers systematic methods for designing stride permutation interconnections, which are common in several digital signal processing algorithms. Managing such interconnections becomes important especially in parallel hardware implementations, which is the principal design problem considered in this Thesis.

In the first proposed method, the stride permutations are represented with permutation matrices, which are decomposed into smaller, more efficiently implementable matrices. The derived decompositions can be directly mapped onto networks consisting of multiplexers, registers and interconnection wirings. In order to estimate the complexity, the lower bound of the number of registers in stride permutations is derived, which is shown to be equal to the number of registers in the proposed networks. In addition, the multiplexing complexity is shown to be reduced compared to other existing approaches.

The second developed method is based on parallel memories which are in-place updated for the minimization of memory usage. This, unfortunately, complicates the control generation and interconnections. To overcome these drawbacks, two different approaches are developed resulting in a simplified control generator and switching network, respectively. Moreover, it is shown that resulting memory-based networks can be easily modified for the run-time configuration of sequence sizes and strides.

The systematic methods for designing stride permutation interconnections presented in this Thesis are shown to be competent compared to other existing approaches that are often design specific. The proposed methods are applicable to various designs since the sequence length, stride, and parallelism of computation are given as parameters having any power-of-two values. In addition, the methods are well suitable for automatic design generation.

## PREFACE

The work presented in this Thesis has been carried out in the Institute of Digital and Computer Systems at Tampere University of Technology during the years 2000-2004.

I would like to thank my supervisor Prof. *Jarmo Takala* for guiding and encouraging me towards doctoral degree. Grateful acknowledgements go also to Prof. *Shuvra Bhattacharyya* and *John Glossner*, Ph.D., for reviewing and providing constructive comments on the manuscript.

It has been my pleasure to work in the Institute of Digital and Computer Systems. Many thanks to all my colleagues for the discussions and pleasant working atmosphere. Especially *Jari Nikara*, Dr.Tech., *Perttu Salmela*, M.Sc., *Vesa Lahtinen*, Dr.Tech., *Tero Rissa*, M.Sc., *Konsta Punkka*, M.Sc., *Rami Rosendahl*, M.Sc., and Mr. *Harri Sorokin* deserve a big hand for helping me in several matters. In addition, I would like to thank all my co-authors: Prof. *David Akopian*, *Jukka Saarinen*, Dr.Tech., *Teemu Sipilä*, M.Sc.

This Thesis was financially supported by Tampere Graduate School in Information Science and Engineering (TISE), National Technology Agency (TEKES), HPY Research Foundation, Nokia Foundation, Jenny and Antti Wihuri Foundation, Ulla Tuominen Foundation, The Finnish Society of Electronics Engineers, Emil Aaltonen Foundation, and the Foundation of Advancement of Technology, which are all gratefully acknowledged.

Finally, I would like to thank my parents, *Mikko* and *Maija Järvinen*, for their encouragement in my studies. My warmest thanks go to my wife *Anu* and son *Viljami* for their love, support, and understanding.

Tampere, October 2004 Tuomas Järvinen

## **TABLE OF CONTENTS**

| Ab      | stract | ·                                                                 |  |  |  |  |

|---------|--------|-------------------------------------------------------------------|--|--|--|--|

| Preface |        |                                                                   |  |  |  |  |

| Tał     | ole of | Contents                                                          |  |  |  |  |

| Lis     | t of P | Publications                                                      |  |  |  |  |

| Lis     | t of F | <i>ïgures</i>                                                     |  |  |  |  |

| Lis     | t of T | Tables                                                            |  |  |  |  |

| Lis     | t of A | Abbreviations                                                     |  |  |  |  |

| Lis     | t of S | ymbols                                                            |  |  |  |  |

| 1.      | Intro  | duction $\ldots$ $\ldots$ $\ldots$ $\ldots$ $1$                   |  |  |  |  |

|         | 1.1    | Objective and Scope of Research   5                               |  |  |  |  |

|         | 1.2    | Main Contributions                                                |  |  |  |  |

|         |        | 1.2.1 Author's Contribution                                       |  |  |  |  |

|         | 1.3    | Thesis Outline   7                                                |  |  |  |  |

| 2.      | Perm   | nutations                                                         |  |  |  |  |

|         | 2.1    | Definitions                                                       |  |  |  |  |

|         | 2.2    | Bit-Permute/Complement Permutations                               |  |  |  |  |

|         | 2.3    | Stride Permutations                                               |  |  |  |  |

|         | 2.4    | Preliminaries for Matrix Representation of Stride Permutations 14 |  |  |  |  |

| 3. | Previous Work                                                   |         |                                                            | 17 |

|----|-----------------------------------------------------------------|---------|------------------------------------------------------------|----|

|    | 3.1                                                             | Switch  | ing Networks                                               | 18 |

|    | 3.2                                                             | Regist  | er-Based Networks                                          | 21 |

|    |                                                                 | 3.2.1   | One-Dimensional Networks                                   | 21 |

|    |                                                                 | 3.2.2   | Two-Dimensional Networks                                   | 24 |

|    |                                                                 | 3.2.3   | Application Specific Networks                              | 26 |

|    | 3.3                                                             | Stride  | Permutations with Parallel Memories                        | 31 |

|    |                                                                 | 3.3.1   | Parallel Memory Systems                                    | 32 |

|    |                                                                 | 3.3.2   | Access Scheme                                              | 33 |

|    |                                                                 | 3.3.3   | Stride Access                                              | 36 |

|    |                                                                 | 3.3.4   | Stride Permutation Access                                  | 38 |

|    |                                                                 | 3.3.5   | Parallel Memories in FFT and Viterbi Processors            | 39 |

|    | 3.4                                                             | Summ    | ary                                                        | 44 |

| 4. | <ul> <li>4. Register-Based Stride Permutation Network</li></ul> |         | 47                                                         |    |

|    |                                                                 |         | 48                                                         |    |

|    |                                                                 | 4.1.1   | Square Matrix Transpose Network                            | 48 |

|    |                                                                 | 4.1.2   | One-Dimensional Network                                    | 51 |

|    |                                                                 | 4.1.3   | Two-Dimensional Network                                    | 52 |

|    | 4.2                                                             | Realiza | ation Structures                                           | 65 |

|    |                                                                 | 4.2.1   | Basic Switching Units                                      | 65 |

|    |                                                                 | 4.2.2   | Networks for Square Matrix Transpose                       | 66 |

|    |                                                                 | 4.2.3   | Networks for Power-of-Two Strides                          | 67 |

|    | 4.3                                                             | Compl   | exity Analysis                                             | 70 |

|    |                                                                 | 4.3.1   | Lower Bound of Register Complexity                         | 70 |

|    |                                                                 | 4.3.2   | Register and Multiplexer Complexities of Proposed Networks | 74 |

|    | 4.4    | Comparison |                                 | 76  |

|----|--------|------------|---------------------------------|-----|

|    | 4.5    | Summa      | ary                             | 77  |

| 5. | Men    | nory-Bas   | sed Stride Permutation Networks | 79  |

|    | 5.1    | Low Co     | ontrol Complexity Scheme        | 80  |

|    |        | 5.1.1      | Access Scheme                   | 81  |

|    |        | 5.1.2      | Row Address Generation          | 85  |

|    | 5.2    | Low In     | terconnection Complexity Scheme | 87  |

|    |        | 5.2.1      | Operation Scheduling            | 89  |

|    |        | 5.2.2      | Row Address Generation          | 93  |

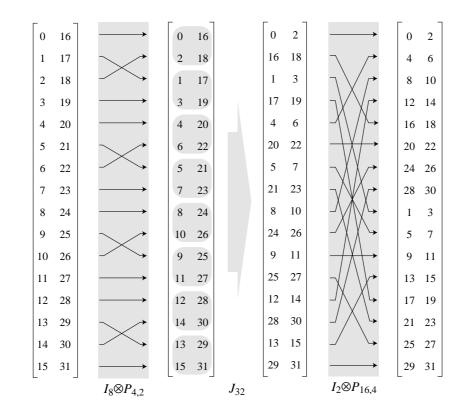

|    |        | 5.2.3      | Design Example                  | 94  |

|    |        | 5.2.4      | Implementation Complexity       | 96  |

|    | 5.3    | Compa      | rison                           | 100 |

|    | 5.4    | Summa      | ary                             | 103 |

| 6. | Con    | clusions   |                                 | 105 |

|    | 6.1    | Main R     | Results                         | 105 |

|    | 6.2    | Future     | Development                     | 106 |

| Bi | bliogr | aphy.      |                                 | 107 |

vii

#### LIST OF PUBLICATIONS

This Thesis is a monograph, which contains some unpublished material, but is mainly based on the following publications. In the text, these publications are referred to as [P1], [P2], ..., [P8].

- [P1] T. Järvinen, J. Takala, D. Akopian, and J. Saarinen, "Register-Based Multi-Port Perfect Shuffle Networks," in *Proceedings of the IEEE International Symposium on Circuits and Systems*, vol. 4, Sydney, Australia, May 6–9 2001, pp. 306–309.

- [P2] J. Takala, T. Järvinen, P. Salmela, and D. Akopian, "Multi-Port Interconnection Networks for Radix-*R* Algorithms," in *Proceedings of the IEEE International Conference on Acoustics, Speech, and Signal Processing*, vol. 2, Salt Lake City, UT, U.S.A., May 7-11 2001, pp. 1177-1180.

- [P3] J. Takala and T. Järvinen and J. Nikara, "Multi-Port Interconnection Networks for Matrix Transpose," in *Proceedings of the IEEE International Conference on Acoustics, Speech, and Signal Processing*, vol. 4, Phoenix, AZ, U.S.A., May 26-29 2002, pp. 874-877.

- [P4] J. Takala and T. Järvinen, "Stride Permutation Access in Interleaved Memory Systems," in *Domain-Specific Multiprocessors - Systems, Architectures, Modeling, and Simulation*, S. S. Bhattacharyya and E. F. Deprettere and J. Teich, Eds., Marcel Dekker Inc., New York, NY, U.S.A., 2004, ch. 4, pp. 63-84.

- [P5] T. Järvinen, P. Salmela, J. Takala, and T. Sipilä, "In-Place Storage of Path Metrics in Viterbi Decoders," in *Proceedings of the IFIP WG 10.5 International Conference on Very Large Scale Integration of System-on-Chip*, Darmstadt, Germany, Dec. 1–3 2003, pp. 295–300.

- [P6] T. Järvinen, J. Takala, "Register-Based Permutation Networks for Stride Permutations,"in *Computer Systems: Architectures, Modeling, and Simulation*, Lecture Notes in Computer Science, vol. 3133, A. D. Pimentel and S. Vassiliadis, Eds., Springer-Verlag, Heidelberg, Germany, 2004, pp. 108–117.

- [P7] T. Järvinen, P. Salmela, H. Sorokin, and J. Takala, "Stride Permutation Networks for Array Processors," in *Proceedings of the IEEE 15th International Conference on Application-Specific Systems, Architectures and Processors*, Galveston, TX, U.S.A., Sept. 27–29, 2004, pp. 376–386.

- [P8] T. Järvinen, P. Salmela, T. Sipilä, and J. Takala "Systematic Approach for Path Metric Access in Viterbi Decoders," to appear in *IEEE Transactions on Communications*.

## LIST OF FIGURES

| 1  | Signal flow graph of constant geometry FFT algorithm                            | 2  |

|----|---------------------------------------------------------------------------------|----|

| 2  | Signal flow graph of radix-2 FFT algorithm                                      | 3  |

| 3  | Block diagrams of partial-column structures for 16-point radix-2 al-<br>gorithm | 4  |

| 4  | Examples of bit-permute/complement permutations                                 | 12 |

| 5  | Block diagram of crossbar network                                               | 19 |

| 6  | Block diagrams of 8-port shuffle/exchange networks                              | 20 |

| 7  | Block diagram of 8-port Benes network                                           | 20 |

| 8  | Permutation examples with single-stage shuffle/exchange networks .              | 21 |

| 9  | Block diagram of network supporting arbitrary permutations                      | 22 |

| 10 | Block diagrams of one-dimensional matrix transpose networks                     | 24 |

| 11 | Block diagram of two-dimensional matrix transpose network                       | 25 |

| 12 | Principle of iterative method for square matrix transpose                       | 27 |

| 13 | Block diagram of two-dimensional matrix transpose network                       | 28 |

| 14 | Block diagram of commutator unit                                                | 28 |

| 15 | Block diagram of cascaded FFT structure                                         | 28 |

| 16 | Block diagram of double-buffered matrix transpose network                       | 29 |

| 17 | Network for bit-permute/complement permutations                                 | 30 |

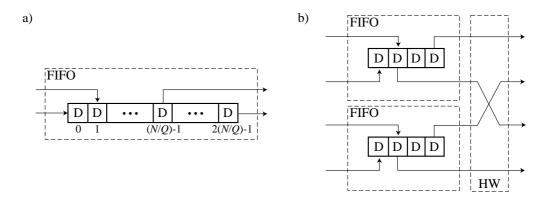

| 18 | Block diagram of FIFO-based approach to stride permutations                     | 30 |

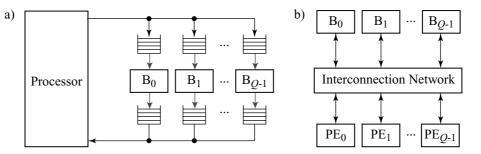

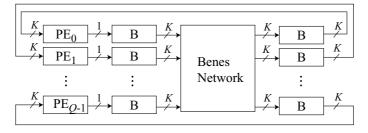

| 19 | Block diagrams of two principal parallel memory systems                         | 32 |

| 20 | Examples of common parallel memory access schemes                              | 34 |

|----|--------------------------------------------------------------------------------|----|

| 21 | Convolutional encoders and corresponding trellis diagrams                      | 38 |

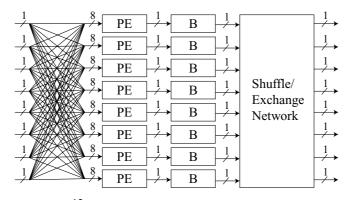

| 22 | Block diagram of radix- $2^k$ Viterbi decoder                                  | 41 |

| 23 | Example of cluster structure in radix-8 Viterbi decoder                        | 41 |

| 24 | Block diagram of radix-2 FFT structure                                         | 42 |

| 25 | Block diagram of radix-2 Viterbi decoder                                       | 42 |

| 26 | Block diagram of radix- $2^k$ Viterbi decoder                                  | 43 |

| 27 | Block diagram of radix-2 Viterbi decoder                                       | 43 |

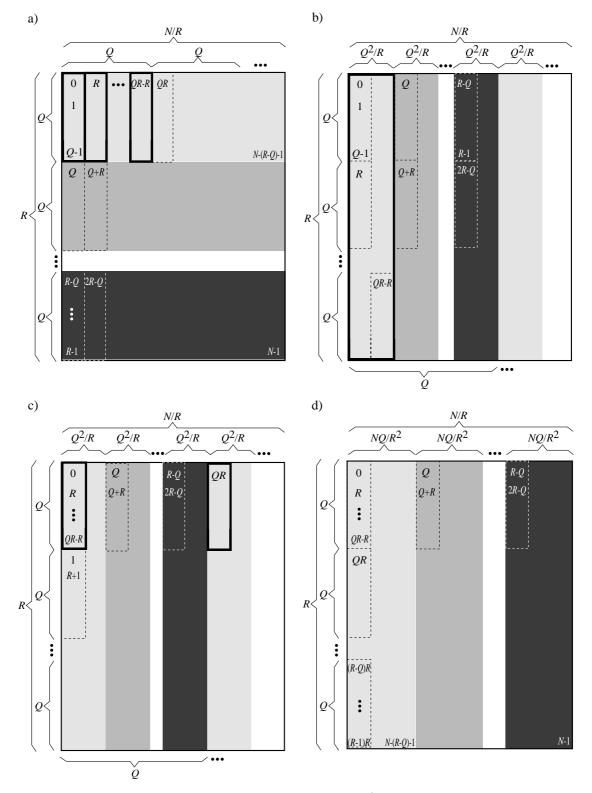

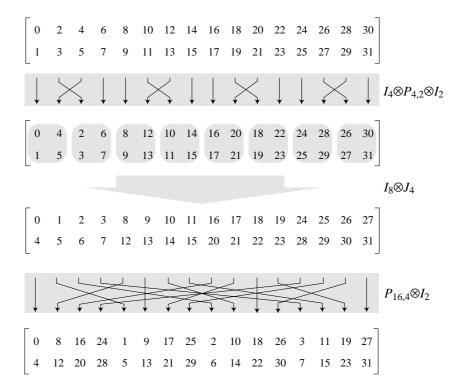

| 28 | Decomposition examples of $8 \times 8$ matrix transpose $\ldots \ldots \ldots$ | 50 |

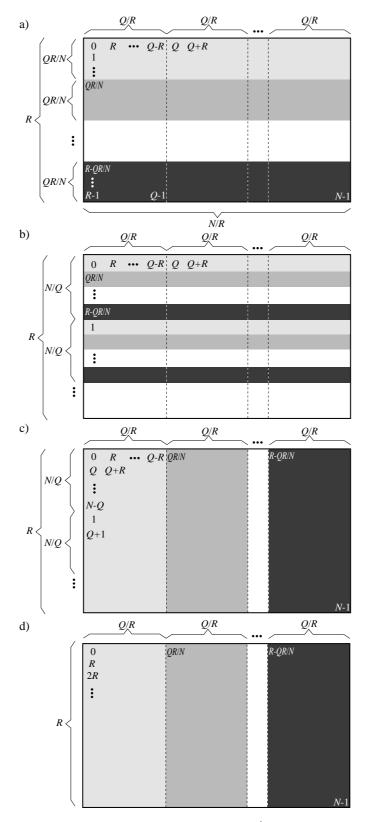

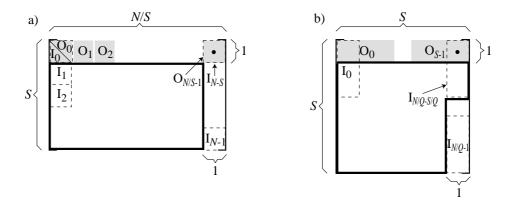

| 29 | Illustration of decomposition in Case 1                                        | 54 |

| 30 | Illustration of decomposition in Case 1                                        | 55 |

| 31 | Illustration of decomposition in Case 2                                        | 57 |

| 32 | Illustration of decomposition in Case 2                                        | 58 |

| 33 | Illustration of decomposition in Case 3                                        | 60 |

| 34 | Illustration of decomposition in Case 3                                        | 61 |

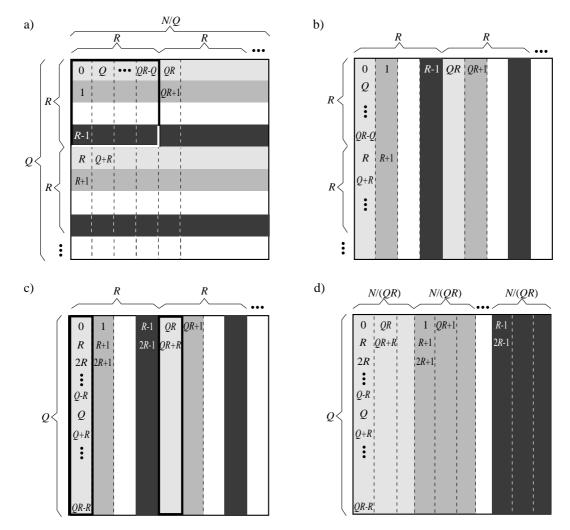

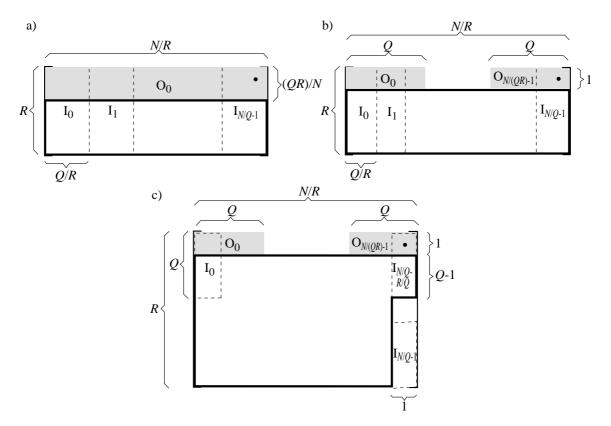

| 35 | Example of decomposition in Case 1                                             | 63 |

| 36 | Example of decomposition in Case 2                                             | 64 |

| 37 | Example of decomposition in Case 3                                             | 64 |

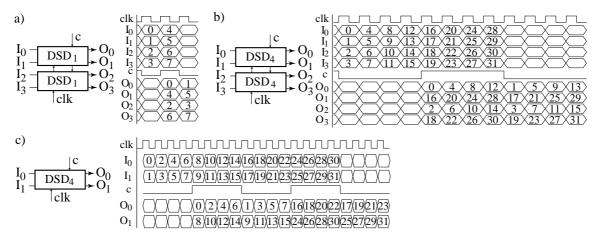

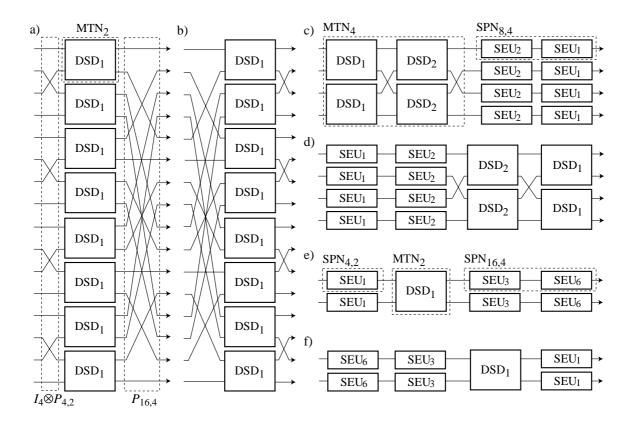

| 38 | Permutation examples with DSD units                                            | 66 |

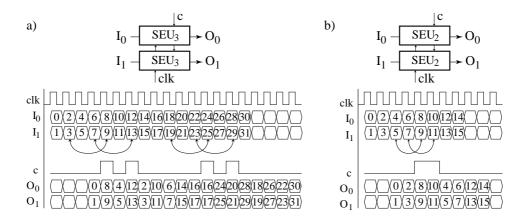

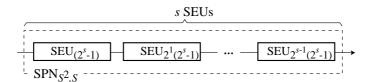

| 39 | Permutation examples with SEUs                                                 | 66 |

| 40 | Block diagram of one-dimensional square matrix transpose network               | 67 |

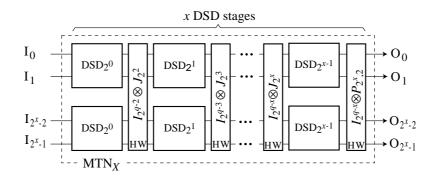

| 41 | Block diagram of matrix transpose network                                      | 67 |

| 42 | Block diagram of two-dimensional square matrix transpose network               | 68 |

| 43 | Block diagram of one-dimensional stride permutation network                    | 68 |

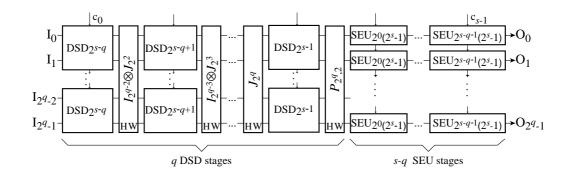

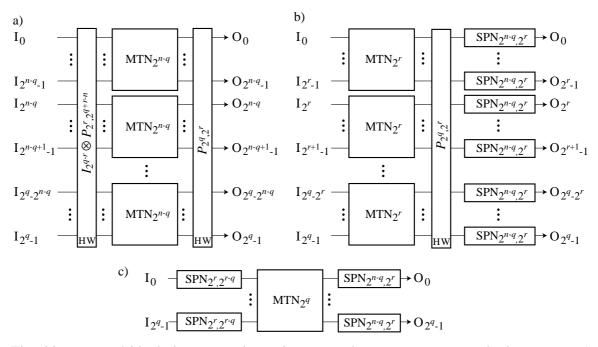

| 44 | Block diagrams of two-dimensional stride permutation networks                  | 69 |

| 45 | Examples of permutation networks with fixed parameters                                                                   | 71  |

|----|--------------------------------------------------------------------------------------------------------------------------|-----|

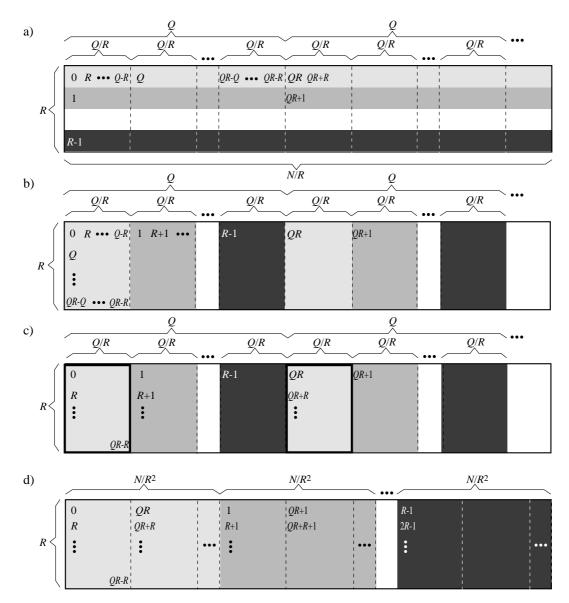

| 46 | Illustration of deriving the lower bound of register complexity for one-dimensional and square matrix transpose networks | 72  |

| 47 | Illustration of deriving the lower bound of register complexity for two-dimensional networks                             | 73  |

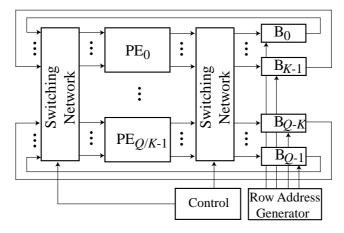

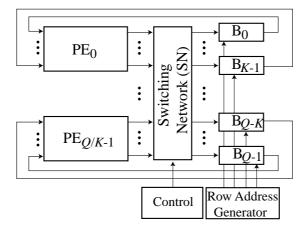

| 48 | Block diagram of low control complexity scheme                                                                           | 81  |

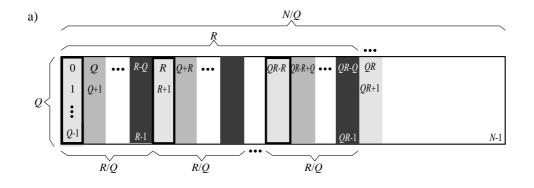

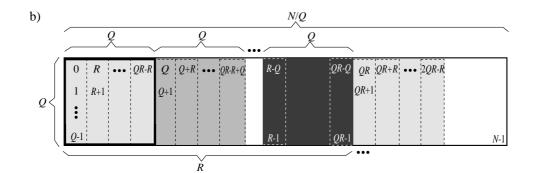

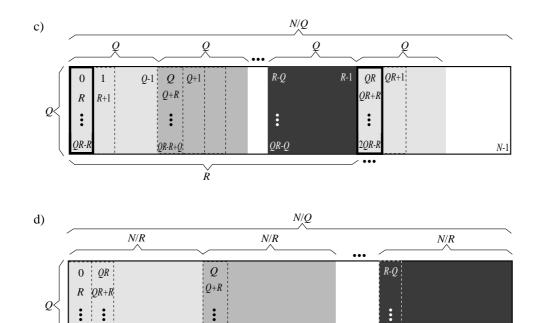

| 49 | Illustration of access scheme for 64-element array                                                                       | 82  |

| 50 | Illustration of access scheme for 32-element array                                                                       | 84  |

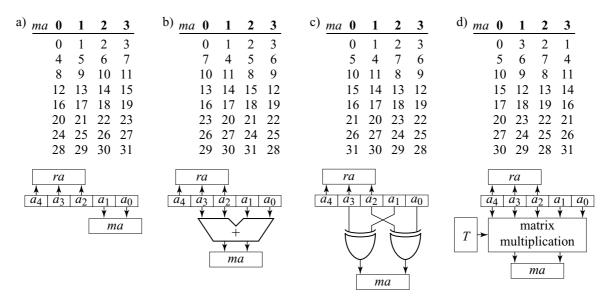

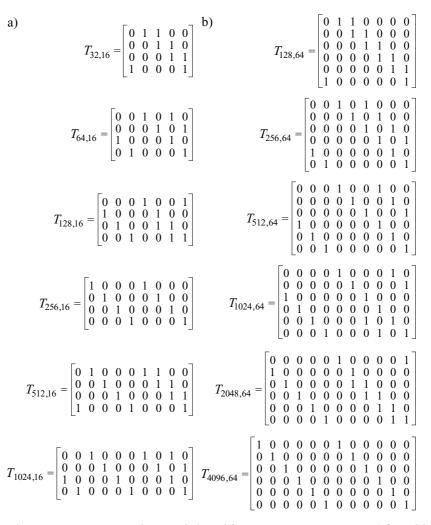

| 51 | Examples of module address transformation matrices                                                                       | 86  |

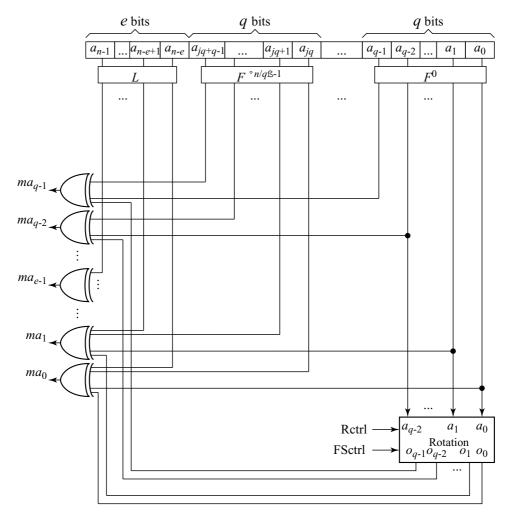

| 52 | Block diagram of module address generation                                                                               | 88  |

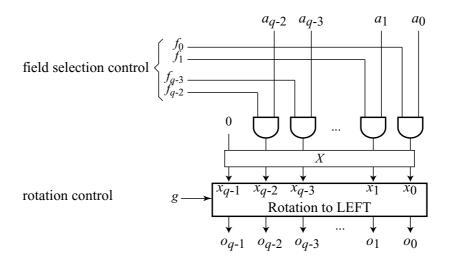

| 53 | Block diagram of rotation unit                                                                                           | 88  |

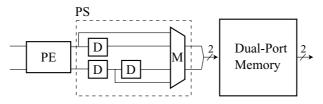

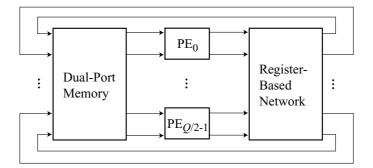

| 54 | Block diagram of low interconnection complexity scheme                                                                   | 89  |

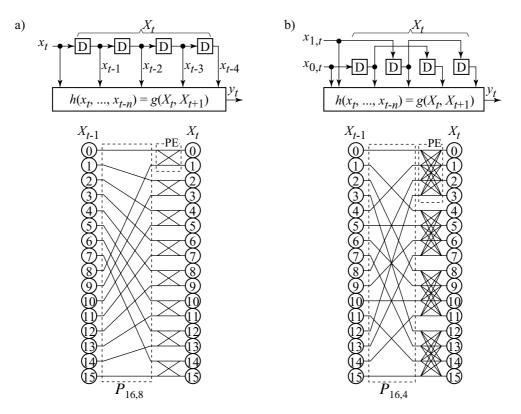

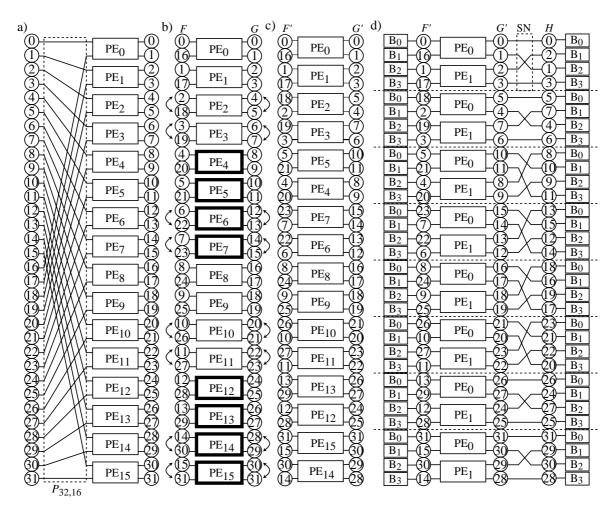

| 55 | Example of operation rescheduling                                                                                        | 90  |

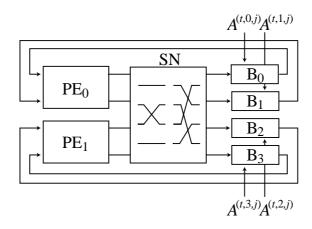

| 56 | Block diagram of radix-2 structure                                                                                       | 95  |

| 57 | Illustration of data evolution in four memory modules                                                                    | 96  |

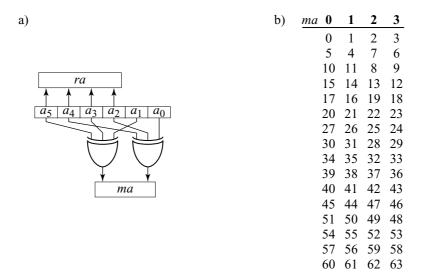

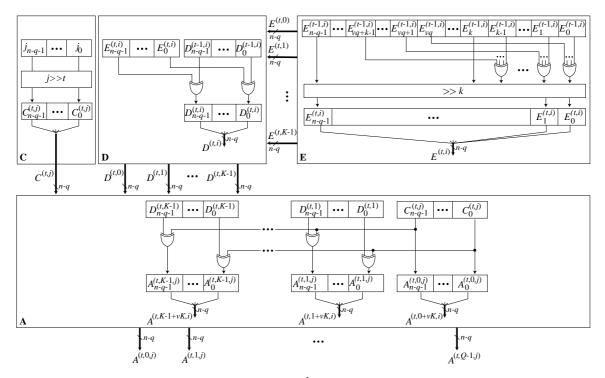

| 58 | Block diagram of row address generator                                                                                   | 97  |

| 59 | Configuration example of computation kernel                                                                              | 100 |

# LIST OF TABLES

| 1 | Example of life time analysis of data elements                              | 23  |

|---|-----------------------------------------------------------------------------|-----|

| 2 | Complexities of square matrix transpose networks                            | 76  |

| 3 | Comparison of permutation networks for power-of-two strides                 | 77  |

| 4 | Complexity figures of row address generator                                 | 98  |

| 5 | Overview of memory-based scalable structures for radix- <i>K</i> algorithms | 101 |

| 6 | Comparison of interconnection complexities in radix-K structures .          | 102 |

## LIST OF ABBREVIATIONS

| ACM    | Association for Computing Machinery |

|--------|-------------------------------------|

| В      | Memory module                       |

| BPC    | Bit-Permute/Complement              |

| CSSU   | Compare-Select-Store Unit           |

| D      | Delay register                      |

| DAB    | Digital Audio Broadcasting          |

| DCT    | Discrete Cosine Transform           |

| DNA    | DeoxyriboNucleic Acid               |

| DRAM   | Dynamic Random Access Memory        |

| DSD    | Delay-Switch-Delay                  |

| DSP    | Digital Signal Processing           |

| DVB    | Digital Video Broadcasting          |

| DVD    | Digital Versatile Disc              |

| FFT    | Fast Fourier Transform              |

| FIFO   | First-In-First-Out                  |

| FPGA   | Field Programmable Gate Array       |

| FSctrl | Field Selection control             |

| GF     | Galois Field                        |

| xviii | List of Abbreviations                                 |

|-------|-------------------------------------------------------|

| HW    | Hard-Wired                                            |

| Ι     | Input                                                 |

| ILP   | Integer Linear Programming                            |

|       |                                                       |

| IEEE  | the Institute of Electrical and Electronics Engineers |

| LSB   | Least Significant Bit                                 |

| М     | Multiplexer                                           |

| MSB   | Most Significant Bit                                  |

| MTN   | Matrix Transpose Network                              |

| NoC   | Network-on-Chip                                       |

| 0     | Output                                                |

| OFDM  | Orthogonal Frequency Division Multiplexing            |

| PE    | Processing Element                                    |

| PN    | Permutation Network                                   |

| PS    | Permutation Section                                   |

| RA    | Row Address                                           |

| Rctrl | Rotation control                                      |

| S     | Switch                                                |

| SE    | Shuffle-Exchange                                      |

| SEU   | Switch-Exchange Unit                                  |

| SIMD  | Single Instruction stream, Multiple Data stream       |

| SN    | Switching Network                                     |

| SoC   | System-on-Chip                                        |

| SPN   | Sequential Permutation Network                        |

# VHDL VHSIC Hardware Description Language

- VHSIC Very High Speed Integrated Circuit

- XOR eXclusive-OR

# LIST OF SYMBOLS

| а             | initial address                                            |

|---------------|------------------------------------------------------------|

| $A^{(t,i,j)}$ | row address for module $i$ at access $j$ and stage $t$     |

| b             | target address                                             |

| С             | complement vector                                          |

| $C^{(t,j)}$   | base address at access $j$ and stage $t$                   |

| СР            | number of connection patterns                              |

| $d_i^t$       | <i>i</i> th data element at stage <i>t</i>                 |

| D             | number of registers                                        |

| $D^{(t,i)}$   | correction coefficient for module $i$ at stage $t$         |

| $E^{(t,i)}$   | correction coefficient for module $i$ at stage $t$         |

| f(i)          | index function                                             |

| f'(i)         | modified index function $f(i)$                             |

| $f_{N,S}(i)$  | index function for stride-by- $S$ permutation of order $N$ |

| F             | input data order                                           |

| $F_k$         | k-point FFT                                                |

| g(i)          | index function                                             |

| g'(i)         | modified index function $g(i)$                             |

| G             | output data order                                          |

| $gcd(\cdot, \cdot)$  | greatest common denominator                                                           |

|----------------------|---------------------------------------------------------------------------------------|

| Н                    | data storage order                                                                    |

| h(i)                 | index function                                                                        |

| $I_K$                | identity matrix of order K                                                            |

| $J_K$                | J permutation matrix of order K                                                       |

| k                    | $\log_2 K$                                                                            |

| K                    | radix                                                                                 |

| L                    | latency                                                                               |

| l(i)                 | life time of data element                                                             |

| М                    | number of multiplexers                                                                |

| та                   | module address                                                                        |

| $\min(\cdot, \cdot)$ | minimum function                                                                      |

| mod                  | modulo operator                                                                       |

| n                    | $\log_2 N$                                                                            |

| Ν                    | size of data sequence                                                                 |

| $P_N$                | permutation matrix of order N                                                         |

| $P^{-1}$             | inverse of permutation matrix P                                                       |

| $P^{T}$              | transpose of permutation matrix P                                                     |

| $P_{N,S}$            | stride-by-S permutation of order N                                                    |

| $P_{S^2}^{(i)}$      | <i>i</i> th step in decomposition of permutation $P_{S^2}$                            |

| $P_{N,S}(Q)$         | decomposition of stride-by- $S$ permutation matrix of order $N$ for $Q$ -port network |

| q                    | $\log_2 Q$                                                                            |

| Q                         | number of ports in permutation network                   |

|---------------------------|----------------------------------------------------------|

| r                         | $\log_2 R$                                               |

| R                         | modified stride                                          |

| ra                        | row address                                              |

| rem                       | remainder after division                                 |

| $\operatorname{rot}_i(a)$ | <i>i</i> -bit left rotation of bit vector <i>a</i>       |

| S                         | $\log_2 S$                                               |

| S                         | stride                                                   |

| t                         | time instant                                             |

| <i>t<sub>diff</sub></i>   | $t_{output} - t_{input}$                                 |

| t <sub>input</sub>        | input clock cycle of data element                        |

| t <sub>out put</sub>      | output clock cycle of data element                       |

| Т                         | module transformation matrix                             |

| $T_H$                     | leftmost $q \times (n-q)$ part in T                      |

| $T_L$                     | rightmost $q \times q$ part in T                         |

| $T_{N,Q}$                 | module transformation matrix for <i>Q</i> -module system |

| V                         | row transformation matrix                                |

| $\pi(i)$                  | bit index function                                       |

| $\otimes$                 | Kronecker product, i.e, tensor product                   |

| ĿJ                        | floor function                                           |

| $<\cdot>_X$               | modulo X                                                 |

| [·]                       | ceiling function                                         |

| σ                         | relatively prime to two                                  |

| xxiv     | List of Symbols |

|----------|-----------------|

| Æ        | exclusive-or    |

| $\oplus$ | exclusive-of    |

| $\wedge$ | and             |

| $\vee$   | or              |

## **1. INTRODUCTION**

Digital signal processing (DSP) has become an important tool in consumer, communications, medical, and industrial products. A wide variety of approaches is used to implement DSP algorithms, ranging from the use of off-the-shelf microprocessors to field-programmable gate arrays (FPGA) to custom integrated circuits (IC) [37]. While programmable approaches continue to progress in performance, historical digital signal processors were unable to execute applications like rake receiver, evaluation of image sequences or radar signals [85, 106]. As programmable approaches progress, higher bit rate applications continue to gain momentum still favoring application-specific hardware. In addition, power consumption is of major concern in the design of portable devices, which favors application-specific hardware where large parallelism and low clock rate can be utilized.

Unfortunately, the design of application-specific hardware is considered to be costly. This together with the ever-increasing design complexity and higher integration level have been the key drivers for system-on-chip (SoC) designs. Lower design costs require greater reuse of intellectual property, silicon implementation regularity, or other novel circuit and system architecture paradigms [57]. In order to improve the design productivity, increased reuse, freedom of choice, and pervasive automation should be utilized [33].

Parallelism of computation is often employed in application-specific hardware structures for DSP algorithms. One extreme is a fully parallel implementation where the operations in a signal flow graph are mapped directly onto functional units, which is referred to as a direct-mapped implementation. This way the maximum parallelism can be obtained allowing the minimum clock rate to be used, resulting in reduced energy per operation [17, 30]. Power efficiencies of direct-mapped hardware are up to four orders of magnitude greater than for general-purpose microprocessors, and this gap is increasing [57].

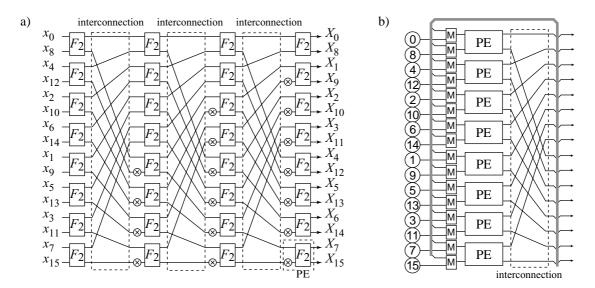

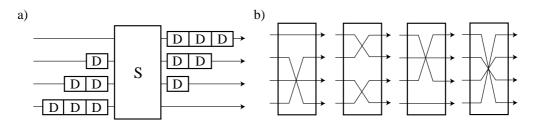

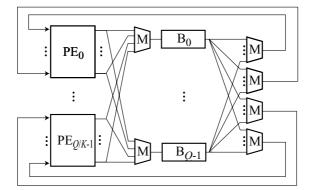

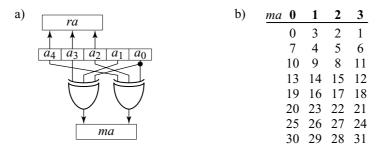

*Fig. 1.* 16-point radix-2 constant geometry *FFT* algorithm: a) signal flow graph, b) corresponding column structure.  $F_2$ : 2-point *FFT*. *PE*: processing element. M: multiplexer.

Direct-mapped implementations may result, however, in excessive throughput and area implying that mapping onto reduced computational resources could be economically useful. For such a design problem, linear mapping methods have been proposed [60, 85]. Most digital signal processing algorithms can be formulated as regular and iterative algorithms, which in turn are especially suitable for linear mapping to array processor structures [85]. These array processors consist of parallel processing elements computing the node functions of the signal flow graph, and an interconnection network which provides communication means between the processing elements.

In the linear mapping methods, the dimensionality of signal flow graphs is reduced by using horizontal, vertical, or both projections, as described, e.g., in [85]. These mapping methods can be illustrated with fast Fourier transform (FFT) as an example. Basically, the parallel structures of FFTs can be divided into three categories: direct-mapped (fully parallel), column, and cascaded (pipeline) structures [42]. As an example, the signal flow graph of a radix-2 constant geometry FFT is depicted in Fig. 1(a) where the constant geometry refers to the constant interconnection topology between the processing columns. By applying the horizontal projection to the given signal flow graph, a column structure is obtained, as depicted in Fig. 1(b). In this structure, the computation is performed for a single column at a time and the data elements are reordered with hardwired interconnections.

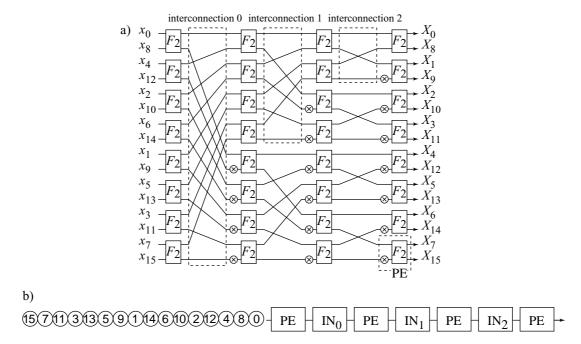

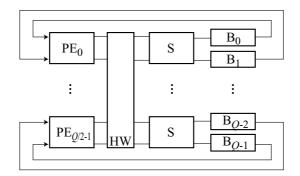

*Fig. 2.* 16-point radix-2 *FFT* algorithm: a) signal flow graph, b) corresponding cascade structure. *PE:* processing element. *IN:* interconnection network.

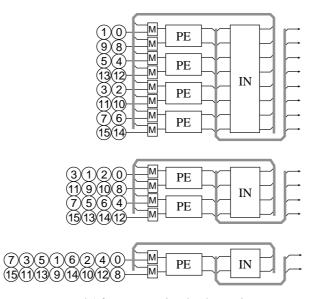

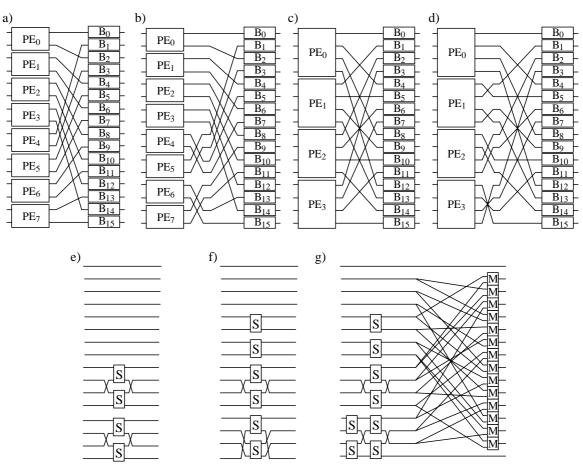

Cascaded structures are obtained by applying vertical projection to the signal flow graph. Consider the signal flow graph of a radix-2 FFT in Fig. 2(a), which is vertically projected resulting in a cascade structure illustrated in Fig. 2(b). In this structure, the computation is performed simultaneously on four processing columns. Such an approach implies that the interconnections require a temporal reordering of intermediate data elements, which is realized with an interconnection network having a storage capability. This is in contrast to the column structure where the interconnections are spatial and can be hardwired. Temporal interconnections are resulted also if both the horizontal and vertical projections are applied to a signal flow graph. Such a mapping produces a partial-column structure where the computation is performed for a part of the column at a time. Examples of the partial-column structures for a 16-point radix-2 constant geometry FFT are shown in Fig. 3.

In all the previous parallel structures, managing the interconnections becomes crucial, which is the principal problem considered in this Thesis. The mapping onto reduced number of processing elements is made according to horizontal and vertical projections, which complicates the interconnections. Chronologically correct processing is maintained by delaying certain operands with registers or memory modules. Thus the interconnections cannot be hardwired, in general. Exceptions are direct-mapped and full column structures, where hardwired interconnections can be employed.

Fig. 3. Partial-column structures of 16-point radix-2 algorithm. PE: processing element. IN: interconnection network. M: multiplexer.

The interconnections considered in this Thesis are called stride permutations and they will be discussed in detail in the next chapter. These type of permutations have several practical applications. For example, consider a matrix transpose, which is a special case of stride permutations. Similarly, the common perfect shuffle permutation [105] is a stride permutation. The perfect shuffle has a close relation to several practical algorithms; e.g., Cooley-Tukey radix-2 FFT [24] algorithm can be scheduled into a form where the interconnections between the processing columns are perfect shuffles. In the same way, FFTs with other radices can be given in a form where interconnections are stride permutations. In this Thesis, hardware realizations of these stride permutations are referred to as stride permutation networks.

Stride permutations can also be found in trellis coding and especially in Viterbi algorithm used for decoding convolutional codes. Convolutional encoders are often described with the aid of a shift register model [65]. Decoding of convolutional codes is represented with the aid of a trellis diagram [41], which is a state diagram of the convolutional encoder expressed in time. Trellis diagrams can be given in a form where operand accesses are made in stride permutation order, just like in FFTs. In addition, the processing nodes have similarities; in both algorithms, FFT and Viterbi, the number of input and output operands is K. Therefore, these types of algorithms are referred to as radix-K algorithms and their realizations as radix-K structures in the following. Typically, K is a power-of-two. Although the examples given in this Thesis consider FFT and Viterbi algorithms, other algorithms with the corresponding stride permutation topology exist, e.g., discrete sine, cosine, and Hartley transforms [4,108]. Currently, FFT is perhaps the most ubiquitous algorithm used to analyze and manipulate digital or discrete data [91]. It is used, e.g., in electroacoustic music and audio signal processing, medical imaging, image processing, pattern recognition, computational chemistry, error-correcting codes, spectral methods for partial differential equations, and mathematics [91]. Any time the analyzed or manipulated data set is very large and accuracy is essential, very large FFTs are required [26]. Example applications employing large FFTs are found in radio astronomy where FFTs of tens of gigapoints are used [26].

Viterbi algorithm was initially proposed for decoding of convolutional codes in [117]. Later on, it has been used as maximum-likelihood sequence estimator for detecting data signals in digital transmission [87,99]. As a result, Viterbi algorithm has been adopted in consumer products like magnetic storage devices [86], modems [35, 53, 54], DVB [36], DAB [34], DVD players [47], and mobile phones [111]. It has also been used in other areas such as character recognition, voice recognition, and DNA analysis, to name few examples. The algorithm is so fundamental that one would expect ever-widening application [48].

### 1.1 Objective and Scope of Research

The objective of this Thesis is to develop systematic design methods for stride permutation interconnections. Such design methods alleviate substantially automatic design generation. Therefore, the structures realizing the stride permutation interconnections are described with the aid of design parameters such as the size of permutation, stride, and the number of input/output ports. All the parameters are assumed to be powers-of-two.

As the first objective, a systematic design method for stride permutation networks consisting of delay registers and multiplexers is to be developed. These networks are referred to as register-based stride permutation networks in the following. The problem to be solved is to derive the networks with the aid of decompositions of stride permutation matrices. The networks should have minimum register and multiplexer complexities.

The second objective is to develop a systematic design method for stride permutation networks based on a parallel memory system. Such networks are called memorybased stride permutation networks in the following. The problem in this approach is to find an access scheme that supports all power-of-two stride permutations. The amount of memory and the complexities of control and interconnections should be kept in minimum.

#### 1.2 Main Contributions

In this Thesis, systematic design methods for stride permutations are developed. To summarize, the main contributions are the following:

- Survey of previous work in hardware realizations of stride permutations.

- Systematic method for deriving hardware structures based on decompositions of stride permutation matrices.

- Decompositions of stride permutation matrices, which can be mapped directly onto hardware.

- Register-based stride permutation networks, which have the lowest register and multiplexer complexities presented so far.

- Two systematic methods for designing memory-based stride permutation networks: low control complexity scheme and low interconnection complexity scheme.

- Low control complexity scheme, which supports stride and bit reversal permutations, uses minimum amount of memory, and results in simple row address generation.

- Low interconnection complexity scheme, which uses minimum amount of memory and results in reduced interconnection complexity by rescheduling the operations.

- Derivation of lower bound for register complexity in stride permutations.

#### 1.2.1 Author's Contribution

The author derived the decompositions of stride permutation matrices and developed and analyzed the register-based stride permutation networks. In addition, derivation of the lower bound for register complexity as well as the comparison against other reported structures were carried out by the author. The studies on register-based stride permutation networks have been reported earlier in [109], [P1, P2, P3]. In general, these earlier networks do not result in the minimum register complexity thus the work has been continued in [P6] and [P7] where the design method resulting in minimum register complexity is introduced for the first time.

The author was responsible for verifying the low control complexity scheme, which has been initially published in [P4]. In addition, the low interconnection complexity scheme, which has been published in [P5] and [P8], was developed and verified by the author. The author conducted the comparison against the earlier published schemes.

The work reported in this Thesis has been published earlier in eight publications [P1-P8]. Therefore, some chapters contain verbatim extracts from the publications. These extracts are under copyright of respective copyright holders. None of the publications has been used in another person's academic thesis.

## 1.3 Thesis Outline

To start with, permutations and their presentations are reviewed in Chapter 2. A class of permutations called bit-permute/complement permutations as well as its subclass, stride permutations, are defined. In Chapter 3, a review of previous work on the realizations of stride permutations is made. The review is divided into three parts: switching, register-, and memory-based networks. Some traditional interconnection means are reviewed followed by more application-specific structures. In the context of memory-based networks, parallel memory systems are defined, some principal access schemes are reviewed, and a stride permutation access scheme is defined. In addition, some parallel memory structures used in FFT and Viterbi computations are reviewed. Chapter 3 contains some material already published in [P4, P8].

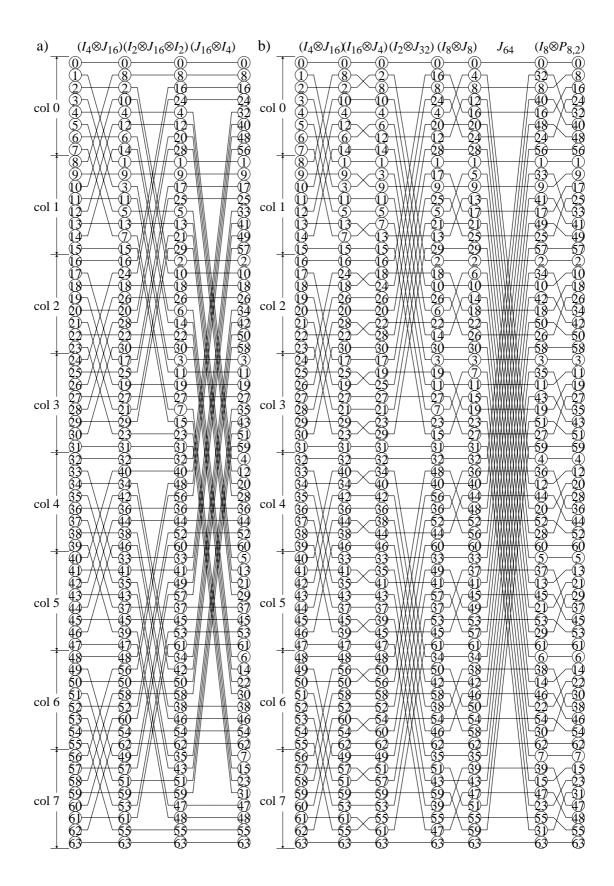

In Chapter 4, a new systematic design method for register-based stride permutation networks is proposed. First, stride permutation matrices are decomposed into smaller

block-diagonal matrices starting from a square matrix transpose. The square matrix transpose is the basis for other stride permutations, which are decomposed subsequently. Some examples of decompositions are provided with fixed design parameters. Then, the mapping of the decompositions onto hardware structures is discussed. A lower bound of register complexity is derived and register and multiplexer complexities of the proposed networks are given. The chapter is concluded with a comparison against the other reported register-based networks. Some parts of this Chapter have been published earlier in [P1–P3, P6, P7].

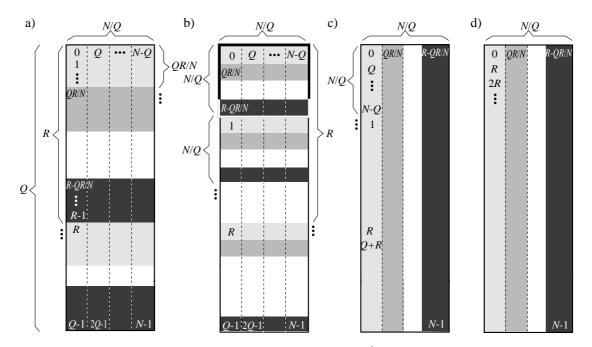

Memory-based stride permutation networks for stride permutations are developed in Chapter 5. First, a low control complexity scheme is defined by specifying the row and module addresses and control generation. Then, a low interconnection complexity scheme is developed where the rescheduling of operations is suggested followed by the definition of a row address generator. An example design is provided with fixed design parameters and complexity figures are given. At the end, an overview and comparison of different parallel memory structures for FFT and Viterbi algorithms are given. Some material in Chapter 5 has been reported in [P4, P5, P8]. Chapter 6 concludes the Thesis.

### 2. PERMUTATIONS

In this chapter a class of permutations referred to as stride permutations is reviewed. The stride permutations are a subclass of bit-permute/complement (BPC) permutations, which are named after the index mapping method, i.e., the permuted data sequence is obtained by permuting and complementing the index bits of the initial data sequence. In such a way, a rich number of permutations can be defined including, e.g., matrix transpose, bit reversal, vector reversal, shuffle permutations [25,75].

The chapter is organized as follows. First, different representations of permutations are reviewed. Then, BPC permutations are defined according to [25] followed by the definition of a subclass of BPC permutations. This subclass considers stride permutations, which are discussed throughout the thesis. At the end of this chapter, some preliminaries for mathematical representation of stride permutations are given.

## 2.1 Definitions

A permutation, in general, is defined as follows [72]:

**Definition 1 (Permutation):** 1. The arrangement of any determinate number of things, as units, objects, letters, etc., in all possible orders, one after the other; called also alternation. 2. Any one of such possible arrangements. [72]

Permutations can be represented in several different ways. One often used method is based on permutation matrices.

**Definition 2 (Permutation Matrix):** A permutation matrix  $P_N$  is an  $N \times N$  matrix with all elements either 0 or 1, with exactly one 1 at each row and column. [74]

As an example, a matrix P,

$$P = \left(\begin{array}{rrrr} 0 & 1 & 0 \\ 0 & 0 & 1 \\ 1 & 0 & 0 \end{array}\right),$$

is a permutation matrix. Let A be a matrix

$$A = \left(\begin{array}{rrrr} 1 & 2 & 3 \\ 4 & 5 & 6 \\ 7 & 8 & 9 \end{array}\right).$$

Then *PA* is a row-permuted version of *A*, and *AP* is a column-permuted version of *A*:

$$PA = \begin{pmatrix} 4 & 5 & 6 \\ 7 & 8 & 9 \\ 1 & 2 & 3 \end{pmatrix}; \qquad AP = \begin{pmatrix} 3 & 1 & 2 \\ 6 & 4 & 5 \\ 9 & 7 & 8 \end{pmatrix}.$$

Permutation matrices are orthogonal: if *P* is a permutation matrix, then  $P^{-1}=P^{T}$ . The product of permutation matrices is another permutation matrix. [74]

The second method for the representation of permutations is to use an index function f(i). With such an index function, the data sequence  $X, X = (x_0, x_1, \dots, x_{N-1})$ , is reordered as  $Y, Y = (y_0, y_1, \dots, y_{N-1})$  where  $y_i$  is given as

$$y_i = x_{f(i)}, \quad \text{or} \tag{1}$$

$$y_{f^{-1}(i)} = x_i.$$

(2)

In this thesis, the index functions will be used as given in (1), where the data sequence X is reordered as  $Y, Y = (x_{f(0)}, x_{f(1)}, \dots, x_{f(N-1)})$ . Third method of using the index functions is based on their definition of bit positions of the index in binary form, as done in bit-permute/complement permutations.

## 2.2 Bit-Permute/Complement Permutations

Initially, the BPC permutations were defined by Nassimi and Sahni in [75] where they suggested an algorithm to route data in a mesh-connected parallel computer. The suggested algorithm supports any permutation, which can be represented as permuting and complementing of the bits of a processor address. The bit permutation is made according to bit index function,  $\pi(i)$ , which is fixed, i.e., it is the same for each address. The bit permutation may also be accompanied by complementing the fixed set of address bits. Thus the name bit-permute/complement permutation. Since the processor address is obtained by permuting the address bits, it is required that the number of processors is a power-of-two [92].

Consider that permutation of elements is a one-to-one mapping of input addresses from the set  $\{0, 1, ..., N - 1\}$  onto itself, i.e., the source address of element  $a = (a_{n-1}, a_{n-2}, ..., a_0)$  is mapped onto target address  $b = (b_{n-1}, b_{n-2}, ..., b_0)$ , where  $n = \log_2 N$ . The leftmost bit represents the most significant bit. In BPC permutations, the target address *b* is formed from its source address *a* by applying a fixed bit permutation  $\pi(i)$  to the address bits and then complementing a fixed subset of bits of the result. The complementing is equivalent to exclusive-oring (XOR) by an *n*-bit complement vector c,  $c = (c_{n-1}, c_{n-2}, ..., c_0)$ . A source address *a* maps to a target address *b* by the equation

$$b_j = a_{\pi(j)} \oplus c_j, \quad j = 0, 1, \dots, n-1,$$

(3)

where  $\oplus$  represents a bitwise XOR operation.

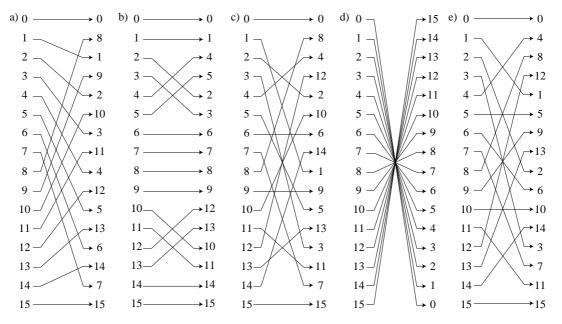

Besides [75], BPC permutations have been discussed, e.g., in [25, 32, 77, 92]. According to [25, 75], many familiar permutations fall into a class of BPC permutations. For example, a perfect shuffle permutation [105] is a BPC permutation defined as

$$\begin{cases} \pi(j) = j+1 \mod n \\ c_j = 0 \end{cases}, \ j = 0, 1, \dots, n-1, \tag{4}$$

where mod represents a modulo operation. An example of perfect shuffle permutation applied to a 16-element data sequence is shown in Fig. 4(a).

Another example is a bit shuffle permutation where the number of bits n is even. The bit shuffle permutation is expressed as

$$\begin{cases} \pi(j) = 2j \mod n \\ c_j = 0 \end{cases}, \ j = 0, 1, \dots, n-1.$$

(5)

A bit shuffle permutation is illustrated with a 16-element data sequence in Fig. 4(b).

Similarly, a bit reversal permutation belongs to BPC permutations. In the bit reversal permutation, the bits of the source address of each element  $(a_{n-1}, a_{n-2}, ..., a_0)$  are

*Fig. 4. BPC* permutations on 16-element data arrays: a) perfect shuffle, b) bit shuffle, c) bit reversal, d) vector reversal, and e)  $4 \times 4$  matrix transpose.

reversed to form the element's target address  $(a_0, \ldots, a_{n-2}, a_{n-1})$ , which is expressed as

$$\begin{cases} \pi(j) = n - 1 - j \\ c_j = 0 \end{cases}, \ j = 0, 1, \dots, n - 1.$$

(6)

An example of bit reversal permutation is given in Fig. 4(c).

Furthermore, vector reversal permutations are BPC permutations. In vector reversal permutations, the source address *i* is mapped to the target address (N-1) - i, i = 0, 1, ..., N-1, which is performed by complementing all the bits of the source address, i.e.,

$$\begin{cases} \pi(j) = j \\ c_j = 1 \end{cases}, \ j = 0, 1, \dots, n-1.$$

(7)

An example of the vector reversal permutation is shown in Fig. 4(d).

A matrix transpose can also be thought as a BPC permutation. Consider a transpose of an  $S \times V$  matrix. The operation can be described with an *SV*-element vector as follows; first the elements of the matrix are read into a vector in column-wise. Then, the elements are reordered according to a permutation

$$\begin{cases} \pi(j) = j + v \mod s + v \\ c_j = 0 \end{cases}, \ j = 0, 1, \dots, s + v - 1.$$

(8)

where  $s = \log_2 S$ ,  $v = \log_2 V$ . After the permutation, the elements are written back into a  $S \times V$  matrix in column-wise. In Fig. 4(e), a  $4 \times 4$  matrix transpose is depicted.

### 2.3 Stride Permutations

The described matrix transpose is also known as a stride permutation; stride-by-*S* permutation of an *N*-element vector can be performed by dividing the vector into *S*-element subvectors, organizing them into  $S \times (N/S)$  matrix form, transposing the obtained matrix, and rearranging the result back to the vector presentation [44]. This interpretation implies that the stride *S* has to be a factor of vector length, i.e., *N* rem *S* = 0 where rem denotes remainder after division.

In the stride permutations, the address bits are shifted cyclically without complementation. Thus, they are also called shuffle permutations, as done in [29]. A stride-by-*S* permutation of an *N*-element sequence can be represented as

$$\begin{cases} \pi(j) = j + s \mod n \\ c_j = 0 \end{cases}, \ j = 0, 1, \dots, n - 1.$$

(9)

Since the binary representation of permutations is used, only power-of-two strides are possible. In the following, the discussion is limited to power-of-two stride permutations.

Another representation for stride permutations is given with an index function as follows;

**Definition 3 (Stride Permutation):** Let us assume a vector  $X = (x_0, x_1, ..., x_{N-1})$ . Stride-by-S permutation reorders X as  $Y = (x_{f_{N,S}(0)}, x_{f_{N,S}(1)}, ..., x_{f_{N,S}(N-1)})^T$  where the index function  $f_{N,S}(i)$  is given as

$$f_{N,S}(i) = (iS \mod N) + \lfloor iS/N \rfloor \mid N \operatorname{rem} S = 0,$$

$$i = 0, 1, \dots, N-1$$

(10)

where  $\lfloor \cdot \rfloor$  is the floor function.

For the matrix representation of stride permutations, the stride-by-S permutation ma-

trix of order N is defined as

$$[P_{N,S}]_{mn} = \begin{cases} 1, & \text{iff } n = (mS \mod N) + \lfloor mS/N \rfloor \\ 0, & \text{otherwise} \end{cases}, \\ m, n = 0, 1, \dots, N-1. \end{cases}$$

(11)

For example, the permutation matrix  $P_{8,2}$  associated to stride-by-2 permutation of an 8-element vector is the following (blank entries represent zeros):

By multiplying the source vector with a permutation matrix, the stride permutation is performed, i.e.,  $Y = P_{N,S}X$  where X and Y are the source and reordered vectors, respectively, and  $P_{N,S}$  is the stride-by-S permutation matrix of order N. As an example,

$$P_{8,2}(0,1,2,3,4,5,6,7)^T = (0,2,4,6,1,3,5,7)^T$$

(12)

where T represents a transpose.

In this Thesis, the discussion is limited to practical cases where the strides and array lengths are powers-of-two,  $N = 2^n$ ,  $S = 2^s$ . Some properties of stride permutations in such cases are given in the following.

## 2.4 Preliminaries for Matrix Representation of Stride Permutations

For ordinary products of matrices, left evaluation is used, i.e.,

$$\prod_{i=0}^{n} A_{i} = (((A_{0} \cdot A_{1}) \cdot A_{2}) \cdot \dots \cdot A_{n}).$$

(13)

The formulation used here is based on tensor products: tensor product (or Kronecker product) is denoted by  $\otimes$ .

The proofs for the following theorems can be found, e.g., in [29] and [44].

#### **Theorem 1 (Factorization of stride permutations):**

$$P_{a,bc} = P_{a,b}P_{a,c} \tag{14}$$

$$P_{abc,c} = (P_{ac,c} \otimes I_b) (I_a \otimes P_{bc,c})$$

(15)

where  $I_K$  denotes the identity matrix of order K.

**Corollary 1 (Periodicity):** *Stride permutations are periodic with the following pro-perties.*

1) Period of  $P_{2^n,2^s}$  is lcm(n,s)/s where lcm(a,b) denotes the least common multiple of n and s. In other words,

$$I_{2^n} = \prod_{1}^{\operatorname{lcm}(n,s)/s} P_{2^n,2^s}.$$

(16)

2) Consecutive stride permutations always result in a stride permutation:

$$P_{2^n,2^a}P_{2^n,2^b} = P_{2^n,2^{(a+b) \mod n}}.$$

(17)

*Proof.* Property 2) If a + b > n, the left side of (17) can be written as  $P_{2^n,2^{kn+(a+b) \mod n}} = P_{2^n,2^{kn}}P_{2^n,2^{(a+b) \mod n}}$  where k > 1 is an integer. By substituting  $2^n$  for S in (10), we find that  $P_{2^n,2^n} = P_{2^n,1} = I_{2^n}$ . Therefore,  $P_{2^n,2^{kn}} = I_{2^n}$  and the result follows. Property 1) Let us assume that period of  $P_{2^n,2^s}$  is k, thus  $ks \mod n = 0$ , i.e., ks is a multiple of n. This implies that k is a multiple of n/s, i.e., k = mn/s. k has to be integer, thus s has to be a factor of mn. The smallest number fulfilling the requirement is lcm(n,s) and, therefore, k = lcm(n,s)/s.

**Theorem 2** (Relationship between tensor product and stride permutation): If  $A_a$ and  $B_b$  are matrices of order a and b, respectively, then,

$$A_a \otimes B_b = P_{ab,a} \left( B_b \otimes A_a \right) P_{ab,b} . \tag{18}$$

**Theorem 3.** *The transpose of a matrix product is the product of the transposes in reverse order:*

$$(ABC)^T = C^T B^T A^T. (19)$$

Finally, a special permutation matrix  $J_K$  of order K is defined as

$$J_K = \left(I_2 \otimes P_{K/2, K/4}\right) P_{K, 2} \tag{20}$$

or alternatively as

$$J_K = P_{K,K/2} \left( I_2 \otimes P_{K/2,2} \right). \tag{21}$$

The permutation  $J_K$  exchanges the odd elements in the first half of a vector with the even elements of the last half of the vector. Based on the properties of tensor product and stride permutations, the following property holds:

$$J_N \otimes I_M = (I_{N/2} \otimes P_{2M,2}) J_{NM} (I_{N/2} \otimes P_{2M,M}), \quad N = 2^n > M = 2^m.$$

(22)

# **3. PREVIOUS WORK**

Managing data permutations in the parallel hardware implementations of digital signal processing algorithms is crucial. Especially in partial column and cascaded structures, the complexity of permutations is increased since data elements must be delayed in order to meet chronologically correct processing. In this chapter, three principal approaches for the hardware realization of stride permutations are reviewed: switching, register-, and memory-based networks. The focus in the review is on the scalability and stride permutation support of the networks. Similarly, the realization complexity in terms of registers and multiplexers and memory usage is studied. In addition, the complexity of design process is considered.

The first section begins with common switching networks, which have been rigorously studied in supercomputing area. It is remarked that such networks cannot be utilized for stride permutations performed over less number of ports than the sequence size due to the absence of storage registers. For managing the storage problem, the register-based networks are studied in the second section. Such networks are divided into one- and two-dimensional networks and further into application specific networks. In order to reduce the complexity of such networks, a register minimization methodology is reviewed.

The third section is limited to memory-based structures. At first, two principal types of memory systems are reviewed: time-multiplexed (interleaved) and spacemultiplexed (parallel) memory systems. Then, some principle access schemes are discussed including low order interleaving, row rotation, and linear transformation. After that, a specific access pattern called stride access, which is one of the common access patterns discussed in several research papers, is reviewed. From the stride access, the discussion is continued with a stride permutation access, which is rarely considered by the earlier research of parallel memory systems. Differences between stride access and stride permutation access are emphasized. At the end of this chapter, a review of parallel Viterbi and FFT structures with parallel memory systems is made. The chapter is concluded with a brief summary.

#### 3.1 Switching Networks

Over the years, a lot of research effort has been placed on interconnection networks used in multiprocessor architectures for connecting processors and memories together. The problem of data interconnections is found also in other fields including telecommunications where routers are used for switching data packets [22], and driven by the growing integration level in silicon, also in system-on-chip (SoC) designs where networks-on-chip (NoC) are used for connecting components like processors, controllers, and memory arrays [9]. In general, there is a wide variety of applications where the realizations of data interconnections are needed.

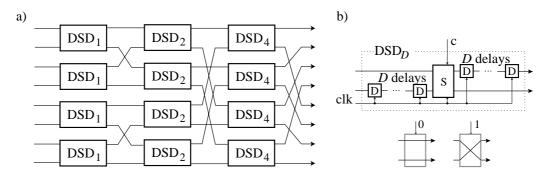

Interconnection networks can be classified, e.g., based on timing philosophy, switching methodology, or control strategy [10]. On the other hand, network topologies can be used in the classification; there are, e.g., single- and multistage networks which refer to topologies where one or several stages of switching elements are used, respectively. Furthermore, many permutations share commonalities thus the networks can also be classified based on the class of permutations they support. As an example, a class of networks for bit-permute/complement permutations is proposed in [2]. Because of such a wide variety, determining the best network for a certain application is a difficult task and requires a careful selection of the metrics for the comparison [66]. The discussion in this Thesis is limited to networks which support stride permutations.

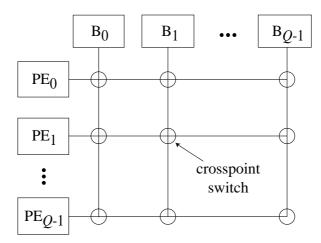

A network illustrated in Fig. 5 is called a crossbar network which is an example of switching networks performing arbitrary permutations between the input and outputs. In the figure, Q processing elements communicate through Q memories and the crossbar network provides conflict-free communication paths such that a processing element can access any memory module if there is no other element reading or writing in the same module. The paths between the inputs and outputs in the network are realized with  $Q^2$  crosspoint switches, which makes the network infeasible for large systems [98].

*Fig. 5. Crossbar network connecting Q processing elements to Q memory modules* [98]. *PE: processing element. B: memory module.*

In general, the networks with the capability of passing all the N! permutations on N elements in one pass through the network are known as rearrangeable networks [8]. These rearrangeable networks are also called as permutation networks [15].

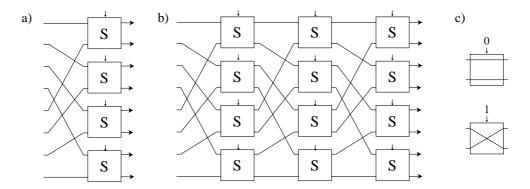

Stone presented in [105] shuffle/exchange (SE) networks based on perfect shuffle permutations. One stage in a *Q*-port SE network consists of a hardwired perfect shuffle permutation of size *Q* followed by *Q*/2 switches of type  $2 \times 2$ . Examples of such networks are depicted in Fig. 6 where a single-stage SE network and a  $\log_2 Q$ -stage SE network called Omega network [63] are shown. The capability of performing arbitrary permutations, i.e., rearrangeability, with the SE networks has been studied, e.g., in [67, 116]. In such papers, one of the main problems to be solved considers finding the minimum number of stages needed for performing arbitrary permutations. In case of a single-stage SE network, the minimum number of passes is studied. Although a theoretical lower bound of  $2\log_2 Q - 1$  stages of  $2 \times 2$  switches is known [118], the sufficiency of such bound for SE networks has neither been proved or disproved [116].

A well-known rearrangeable network is the Benes network [8], which is built in a recursive manner by using  $2 \times 2$  switches. A *Q*-port Benes network consists of  $2\log_2 Q - 1$  stages of Q/2 switches in parallel. An example of 8-port Benes network built up from 4-port Benes networks is shown in Fig. 7. For the Benes networks, studies have been conducted for developing schemes for setting the switches concurrently with data propagation, e.g., in [76, 90].

Fig. 6. 8-port shuffle/exchange networks: a) single-stage SE network, b) Omega network, and c) connection patterns. S: switch.

Fig. 7. 8-port Benes network where 4-port Benes network is shown with dashed lines. S: switch.

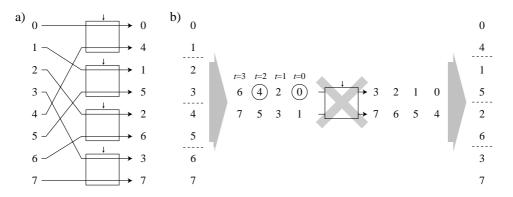

The drawback of switching networks, of which the preceding networks are examples, is that they cannot be used for stride permutations performed in parts with less number of ports than the size of the permutation. As an example, consider the perfect shuffle permutation of 8 data elements. With a single-stage SE network such permutation can be performed with straight connected switches, as depicted in Fig. 8(a). On the other hand, consider the same permutation divided into four parts such that two data elements enter the network at a time, as shown in Fig. 8(b). The network in this case is a 2-port SE network, which actually reduces to a 2-port switch. In such a case, the elements 0 and 4 should be the first two data elements at the output. However, the elements 0 and 1 enter the network at a time, thus the element 0 should be delayed two cycles until the element 4 is available at the input. With the switching networks, such an arrangement is not possible. Therefore, the networks where registers are used for delaying the data elements are discussed in the following. Such networks are referred to as register-based networks.

Fig. 8. Perfect shuffle permutation with: a) 8-port single-stage SE network, b) 2-port SE network resulting in conflicts. t: time instant.

### 3.2 Register-Based Networks

Because the switching networks cannot be used for stride permutations performed over less number of ports than the sequence size, register-based networks are reviewed in this section. The variation among register-based networks is considerable thus the review is limited to networks which support stride permutations. The discussion is divided into one- and two-dimensional networks based on the network topologies; the one-dimensional networks operate over sequential data streams while the two-dimensional networks are applied to parallel data streams. In the initial context, some of the reviewed networks are referred to as data format converters. For simplicity, they are called as permutation networks in this Thesis.

## 3.2.1 One-Dimensional Networks

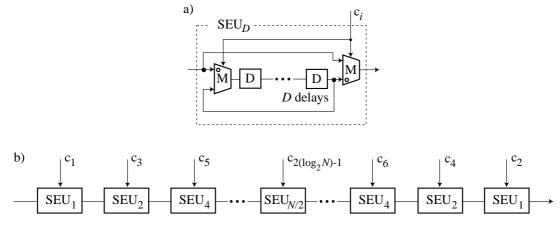

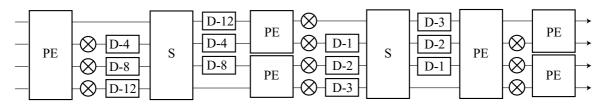

In [96], Shung *et al.* proposed a one-dimensional permutation network based on shift exchange units (SEU), which supports arbitrary data permutations over sequential data streams. The structure of a SEU of size D, SEU<sub>D</sub>, is depicted in Fig. 9(a). It consists of a delay line of D registers and two multiplexers, which either inputs the data element into the delay line or bypasses it. The bypass results in the exchange of data elements which are D elements apart in the data stream. A one-dimensional permutation network consisting of  $\log_2 N - 1$  cascaded SEUs is shown in Fig. 9(b).

One method of reducing the network complexity is proposed by Parhi in [79, 82]. This systematic methodology minimizes the number of registers based on the life time analysis of data elements. In general, the data elements have different life times

*Fig. 9.* One-dimensional permutation network [96]: a) shift exchange unit (SEU), b) permutation network of  $\log_2 N - 1$  stages of SEUs. N: number of data elements. D: number of delay registers. c: control signal. M: 2-to-1 multiplexer. D: delay register.

making the reuse of registers possible. In such a case, a new data element can be assigned to a register if the former data element is read out. Although the method was initially proposed for one-dimensional networks, it can be applied to two-dimensional networks as well.

In Table 1, an example case of the life time analysis of a  $4 \times 4$  matrix transpose is shown. The network operates in sequential manner, and the clock cycles for the data element input and output are denoted as  $t_{input}$  and  $t_{output}$ , respectively. The difference between the output and input cycles is denoted as  $t_{diff}$ , i.e.,  $t_{diff} = t_{output} - t_{input}$ . The absolute value of the most negative  $t_{diff}$  determines the minimum number of registers, and it is added to each  $t_{diff}$  for obtaining the life time l(i) of a data element *i*. The life period denotes the cycles when the data element must be stored in the network. In case of the  $4 \times 4$  matrix transpose over sequential data stream, overall nine registers are required.

Based on the life time analysis, Parhi proposed several types of register-based permutation networks in [80]. The networks are divided into various classes according to the number and the size of the input and output words. However, the operation of all the networks is sequential although they may have multiple input and output ports.

A forward-circulate register allocation scheme begins with first calculating the minimum number of registers and connecting them into a chain. The data elements are read in one at a time and forwarded to the next register if the register is available. Otherwise, the data element is circulated, i.e., read again by its current register. In

| data element | t <sub>input</sub> | tout put | t <sub>diff</sub> | l(i) | life period         |

|--------------|--------------------|----------|-------------------|------|---------------------|

| 0            | 0                  | 0        | 0                 | 9    | $0 \rightarrow 9$   |

| 1            | 1                  | 4        | 3                 | 12   | $1 \rightarrow 13$  |

| 2            | 2                  | 8        | 6                 | 15   | $2 \rightarrow 17$  |

| 3            | 3                  | 12       | 9                 | 18   | $3 \rightarrow 21$  |

| 4            | 4                  | 1        | -3                | 6    | $4 \rightarrow 10$  |

| 5            | 5                  | 5        | 0                 | 9    | $5 \rightarrow 14$  |

| 6            | 6                  | 9        | 3                 | 12   | $6 \rightarrow 18$  |

| 7            | 7                  | 13       | 6                 | 15   | $7 \rightarrow 22$  |

| 8            | 8                  | 2        | -6                | 3    | $8 \rightarrow 11$  |

| 9            | 9                  | 6        | -3                | 6    | $9 \rightarrow 15$  |

| 10           | 10                 | 10       | 0                 | 9    | $10 \rightarrow 19$ |

| 11           | 11                 | 14       | 3                 | 12   | $11 \rightarrow 23$ |

| 12           | 12                 | 3        | -9                | 0    | $12 \rightarrow 12$ |

| 13           | 13                 | 7        | -6                | 3    | $13 \rightarrow 16$ |

| 14           | 14                 | 11       | -3                | 6    | $14 \rightarrow 20$ |

| 15           | 15                 | 15       | 0                 | 9    | $15 \rightarrow 24$ |

**Table 1.** Life time analysis of data elements for one-dimensional  $4 \times 4$  matrix transpose net-<br/>work [82].  $t_{input}$ : clock cycle of data element input.  $t_{output}$ : clock cycle of data<br/>element output.  $t_{diff} = t_{output} - t_{input}$ . l(i): life time of data element.

certain cases, the forward-circulate scheme results in deadlocks, which implies that the data element cannot be forwarded or circulated [80].

Compared to the previous scheme, a forward-backward allocation scheme results in a register chain with simpler control. The most important advantage, however, is that the forward-backward scheme never results in deadlocks. Thus, the scheme can be used for arbitrary permutations. In the scheme, all the data elements with life times less or equal to the number of registers are allocated in a forward manner until they are read out or they reach the last register. Data elements that cannot be forwarded are backward allocated to some available registers so that required feedback connections are minimized.

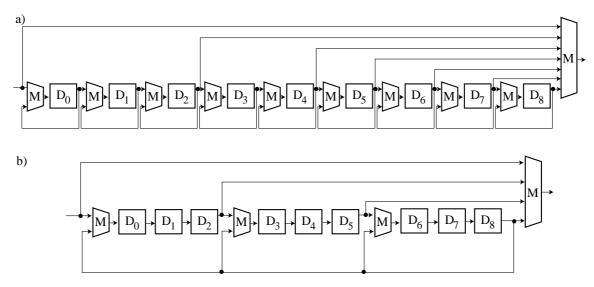

A  $4 \times 4$  matrix transpose network based on the forward-circulate register allocation scheme is shown in Fig. 10(a). In such a case, each register has a feedback connection from its output and a multiplexer in its input for circulating the data elements. In Fig. 10(b), a  $4 \times 4$  matrix transpose network based on the forward-backward allocation scheme is illustrated. It contains less multiplexers and the same amount of registers as the network based on the forward-circulate scheme. Later on in [81],

*Fig. 10.* 4×4 matrix transpose networks based on a) forward-circulate, b) forward-backward register allocations [80]. D: register. M: multiplexer.

Parhi applied the forward-backward register allocation scheme to data permutations in video applications.

Applying one-dimensional networks to permutations in parallel data streams requires that either the frequency of the network is increased or that multiple one-dimensional networks are used in parallel. In the latter case, additional interconnection lines between the networks may be required, which increases the network complexity. For managing the interconnection, register, and multiplexer complexities, the networks, which are initially designed to operate over parallel data streams, are proposed. Such networks are called two-dimensional networks based on their topology, and they are discussed in the following.

#### 3.2.2 Two-Dimensional Networks

The general approach in two-dimensional permutation networks is that the data elements are reordered with switching elements on parallel delay lines. In these networks, an exchange of data elements between the delay lines is often needed, which in turn results in additional multiplexers and connection wirings. Although the minimization of register complexity is still one of the design objectives, there are several schemes where also the reduction of multiplexer and interconnection complexities and power consumption are devoted to. Next, the discussion is continued with twodimensional permutation networks supporting arbitrary permutations.

| a)        |                              |     |   |   |     |   |   |             |   |   |             |    |    |             |    |    |             |       |            |             |    |   |       |    |     |       |

|-----------|------------------------------|-----|---|---|-----|---|---|-------------|---|---|-------------|----|----|-------------|----|----|-------------|-------|------------|-------------|----|---|-------|----|-----|-------|

| <i>a)</i> | time                         | t=1 |   |   | t=2 |   |   | <i>t</i> =3 |   |   | <i>t</i> =4 |    |    | <i>t</i> =5 |    |    | <i>t</i> =6 |       |            | <i>t</i> =7 |    | / |       |    |     |       |

|           | Input                        | 0   | 1 | 2 | 3   | 4 | 5 | 6           | 7 | 8 | 9           | 10 | 11 | 12          | 13 | 14 | 15          |       |            |             |    |   |       |    |     |       |

|           | $\overline{D_0 D_1 D_2 D_3}$ |     |   |   |     | 0 | 1 | 2           | 3 | 4 | 5           | 6  | 7  | 8,          | 9  | 10 | 11          | 3 🕄   | )14        | 15          |    |   |       |    |     |       |

|           | $D_4 D_5 D_6 D_7$            |     |   |   |     |   |   |             |   | 0 | 1           | 2  | 3  | 4,          | 5  | 6  | 7           | 2 (9) | 10         | 11          | 3  | 7 | 14)15 |    |     |       |

|           | $D_8 D_9 D_{10} D_{11}$      |     |   |   |     |   |   |             |   |   |             |    |    | 0.          | -1 | 2  | `3          | 15    | <b>₩</b> 6 | `7          | 20 | 6 | 10+11 | 30 | 7)( | 1)(5) |

|           | Output                       |     |   |   |     |   |   |             |   |   |             |    |    | 0           | 4  | 8  | 12          | 1 5   | 9          | 13          | 2  | 6 | 10 14 | 3  | 71  | 1 15  |

*Fig. 11. Two-dimensional* 4 × 4 *matrix transpose network* [6]: *a*) *register allocation table, b*) *resulting network.* M: *multiplexer.* D: *register.*

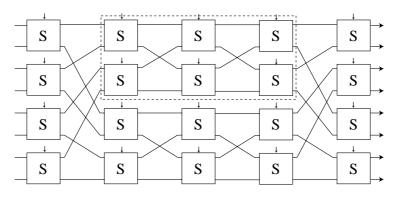

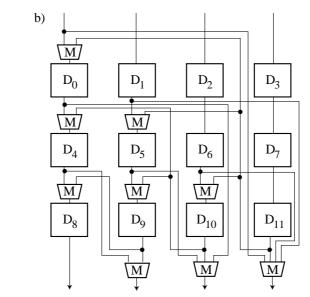

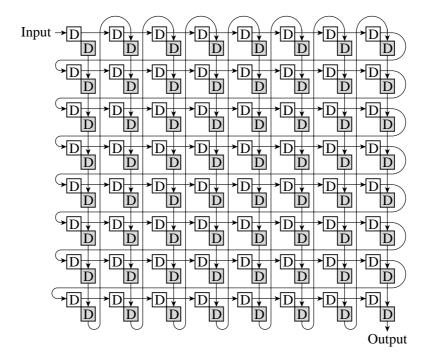

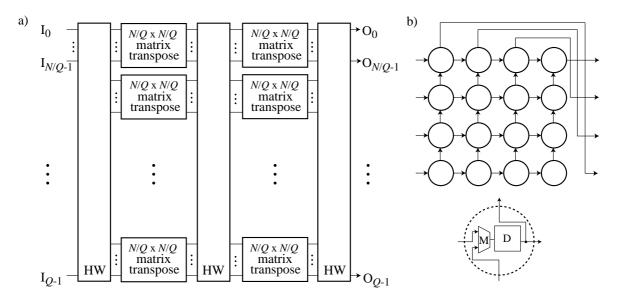

Bae and Prasanna presented in [6,7] a design methodology for two-dimensional permutation networks resulting in the minimum number of registers. In Fig. 11, the methodology is illustrated with a  $4 \times 4$  matrix transpose where four data elements are read in and written out in parallel. First, the minimum number of registers is determined. Then, the data is allocated to the registers such that at each clock cycle the parallel shifting is carried out. When all the data elements are available for the output, they are written out immediately. A backward allocation of the data elements is illustrated with the arrows in the register allocation table in Fig. 11(a). Such allocation is needed when the parallel shifting moves the data elements forward in the delay lines and there is not enough registers before the output. Moving the data elements inside the network and passing the data elements to output imply a need for multiplexers. The circles in Fig. 11(a) denote that the data element is passed to output. The resulting structure of  $4 \times 4$  transposer is illustrated in Fig. 11(b). It is worth noting that the methodology has limitations among the stride permutations: it does not support cases where the number of ports is less than the stride. In a low-power register allocation scheme suggested by Srivatsan et al. in [103, 104], the main objective is the reduction of power consumption, not the minimization of area although the minimum number of registers is obtained. In addition, the proposed scheme supports arbitrary permutations. Compared to the previous schemes, the data elements stay in a single register as long as possible instead of moving forward at each cycle. The resulting networks have gated clocks, more multiplexers, and larger area compared to the Parhi's one-dimensional networks [104]. As an example, due to the reduced data element transitions, the power consumption of a one-dimensional  $4 \times 4$  matrix transposer is shown to be 42% lower and area two times larger compared to Parhi's network in Fig. 10(b) [104].