Erno Salminen On Design and Comparison of On-Chip Networks

Julkaisu 872 • Publication 872

Tampere 2010

Tampereen teknillinen yliopisto. Julkaisu 872 Tampere University of Technology. Publication 872

Erno Salminen

# **On Design and Comparison of On-Chip Networks**

Thesis for the degree of Doctor of Technology to be presented with due permission for public examination and criticism in Tietotalo Building, Auditorium TB109, at Tampere University of Technology, on the 19th of February 2010, at 12 noon.

Tampereen teknillinen yliopisto - Tampere University of Technology Tampere 2010

ISBN 978-952-15-2325-0 (printed) ISBN 978-952-15-2348-9 (PDF) ISSN 1459-2045

### Erno Salminen

# **On Design and Comparison of On-Chip Networks**

Contact Information:

|         | Erno Salminen                    |

|---------|----------------------------------|

| mail:   | Tampere University of Technology |

|         | Department of Computer Systems   |

|         | P.O.Box 553                      |

|         | FIN-33101 Tampere                |

|         | Finland                          |

| tel:    | +358-3-3115 4540 (office)        |

|         | +358-40-5832 182 (mobile)        |

| fax:    | +358-3-3115 4561                 |

| e-mail: | erno.salminen@tut.fi             |

### ABSTRACT

This thesis focuses on the design of on-chip communication networks and methods for benchmarking them. Network-on-Chip (NoC) paradigm seeks to achieve greater design productivity and performance in large integrated circuits. Such systems include heterogeneous set of components that have different requirements for communication.

This thesis presents simulation-based evaluation methods for NoCs. In addition, several detailed guidelines are given in order to promote disciplined NoC benchmarking. Discussion starts with thorough surveys of 60 existing NoCs and over 40 evaluation studies. The presented benchmarking methodology relies on abstract workload models based on task graphs. They are executed with a Transaction Generator (TG) that sends and receives data to/from the benchmarked NoC and collects statistics. TG was used in several configurations and was essential part for completing this work. The error in time estimates was mostly below 10% whereas the speedup against cycleaccurate HW/SW co-simulation was over 200x.

Heterogeneous IP Block Interconnection (HIBI) was designed to obtain a topologyindependent, scalable, and still high-performance network for integrating intellectual property blocks. Six other NoCs were implemented for reference and benchmarked with HIBI in various configurations and using multiple workloads. Over 30 published implementation results were gathered. Furthermore, several FPGA prototypes were implemented and they confirmed the utility of HIBI in multiprocessor environment. In general, HIBI and 2-D mesh performed better than others in the presented cases considering the trade-off between area and throughput.

The main goals of the work were met. The presented methodology along with TG has been adopted by an OCP-IP workgroup that is seeking to standardize NoC benchmarking methods.

### PREFACE

The work presented in this thesis has been carried out in the Department of Computer Systems at Tampere University of Technology during the years 2001-2009.

I thank my supervisor Prof. *Timo D. Hämäläinen* for guiding and encouraging me towards doctoral degree. Grateful acknowledgements go also to Prof. *Kees Goossens* and Dr. *Juha Plosila* for the thorough reviews and the constructive comments on the manuscript.

It has been my pleasure to work in the Department of Computer Systems. Many thanks to all my colleagues for the discussions and pleasant working atmosphere. Especially Dr. *Kimmo Kuusilinna*, Dr. *Vesa Lahtinen*, Dr. *Tero Kangas, Jouni Riihimäki*, M.Sc., Dr. *Ari Kulmala*, *Petri Kukkala*, M.Sc., *Heikki Orsila*, M.Sc., and *Kalle Holma*, M.Sc., deserve a big hand for helping me in several matters. In addition, I would like to thank all the other co-authors and colleagues. Our lively discussions both on and off-topic have been pleasant and stimulating.

This thesis was financially supported by Graduate School in Telecommunication System-on-Chip Integration (TELESOC), Nokia Foundation, Ulla Tuominen Foundation, Foundation of Advancement of Technology, which are all gratefully acknowledged.

My warmest thanks go to my beloved wife *Hannele* and our lovely ever-energetic kids *Ilona* and *Otto* for their love, support, and understanding.

#### "Sitä saa, mitä tulee"

- A Finnish proverb and the guiding principle during this work

Tampere, December 2009 Erno Salminen

## **TABLE OF CONTENTS**

| Ab  | stract | ••••       |                               | i   |

|-----|--------|------------|-------------------------------|-----|

| Pre | face   |            |                               | iii |

| Tal | ole of | Content    | ts                            | v   |

| Lis | t of P | Publicatio | ons                           | xi  |

| Lis | t of F | igures .   |                               | iii |

| Lis | t of T | ables .    |                               | ix  |

| Lis | t of A | Abbrevia   | tions                         | xi  |

| 1.  | Intro  | duction    |                               | 1   |

|     | 1.1    | Objecti    | ive and scope of research     | 4   |

|     | 1.2    | Thesis     | outline                       | 5   |

| 2.  | Com    | municat    | tion networks                 | 7   |

|     | 2.1    | Basic p    | properties and terminology    | 7   |

|     |        | 2.1.1      | Structural properties         | 8   |

|     |        | 2.1.2      | Temporal properties           | 8   |

|     |        | 2.1.3      | Performance measures          | 10  |

|     | 2.2    | Networ     | rk topologies                 | 12  |

|     |        | 2.2.1      | Single-hop topologies         | 12  |

|     |        | 2.2.2      | Multi-hop topologies          | 15  |

|     | 2.3    | Floorpl    | lan of network-on-chips       | 17  |

|     |        | 2.3.1      | Basic floorplan optimizations | 18  |

|    |      | 2.3.2    | Irregular size of processing elements                | 18 |

|----|------|----------|------------------------------------------------------|----|

|    |      | 2.3.3    | Wiring                                               | 20 |

|    | 2.4  | Router   | s                                                    | 22 |

|    | 2.5  | Other a  | aspects of communication performance                 | 24 |

|    |      | 2.5.1    | The latency components                               | 24 |

|    |      | 2.5.2    | Network interface                                    | 26 |

|    |      | 2.5.3    | Overlapping the computation with communication       | 27 |

|    |      | 2.5.4    | Intertwined transfers and out-of-order data delivery | 28 |

|    |      | 2.5.5    | Limited buffering at the receiver                    | 30 |

|    |      | 2.5.6    | Scheduling anomalies                                 | 32 |

|    |      | 2.5.7    | Data synchronization                                 | 33 |

|    |      | 2.5.8    | Serial links and data encoding                       | 34 |

| 3. | Surv | ey of ne | twork-on-chips                                       | 37 |

|    | 3.1  | NoC pr   | roposals                                             | 37 |

|    |      | 3.1.1    | Switching policy                                     | 38 |

|    |      | 3.1.2    | Utilized topologies                                  | 39 |

|    |      | 3.1.3    | Routing                                              | 42 |

|    |      | 3.1.4    | Quality-of-Service                                   | 42 |

|    |      | 3.1.5    | Testing and fault-tolerance                          | 43 |

|    | 3.2  | NoC co   | omparisons                                           | 43 |

|    |      | 3.2.1    | Compared topologies                                  | 46 |

|    |      | 3.2.2    | Evaluation methods and metrics                       | 47 |

|    |      | 3.2.3    | Test cases                                           | 47 |

|    |      | 3.2.4    | Prototyping                                          | 49 |

|    | 3.3  | Repres   | entative NoC                                         | 50 |

|    | 3.4  | Survey   | of reusable hardware IP components                   | 51 |

| 4. | Basi | cs of co | mmunication network evaluation     | 55 |

|----|------|----------|------------------------------------|----|

|    | 4.1  | Introdu  | action to benchmarking             | 55 |

|    |      | 4.1.1    | Benchmark classification           | 56 |

|    | 4.2  | Analyt   | ical topology comparison           | 57 |

|    | 4.3  | Model    | ing traffic load                   | 61 |

|    |      | 4.3.1    | Data rate and spatial distribution | 62 |

|    |      | 4.3.2    | Burstiness                         | 65 |

|    |      | 4.3.3    | Communication-to-computation ratio | 65 |

|    |      | 4.3.4    | Traffic generation                 | 66 |

|    |      | 4.3.5    | Traffic profile capture            | 68 |

|    | 4.4  | Genera   | al guidelines for NoC benchmarking | 70 |

|    |      | 4.4.1    | Workload                           | 71 |

|    |      | 4.4.2    | System model                       | 72 |

|    |      | 4.4.3    | Measurement                        | 73 |

|    |      | 4.4.4    | Concluding the findings            | 74 |

|    |      | 4.4.5    | Metrics                            | 75 |

|    |      | 4.4.6    | Cost function                      | 75 |

| 5. | Prop | osed No  | C benchmarking methodology         | 81 |

|    | 5.1  | Applic   | ation model                        | 84 |

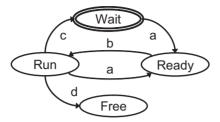

|    |      | 5.1.1    | Application tasks                  | 85 |

|    |      | 5.1.2    | Connections                        | 88 |

|    |      | 5.1.3    | Triggering events                  | 88 |

|    |      | 5.1.4    | Real-time constraints and paths    | 89 |

|    | 5.2  | Mappi    | ng model                           | 89 |

|    | 5.3  | Platfor  | m model                            | 90 |

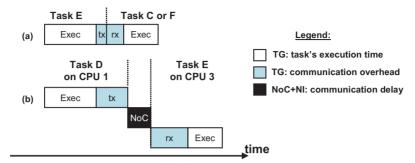

|    |      | 5.3.1     | Resource model                                      | 91  |

|----|------|-----------|-----------------------------------------------------|-----|

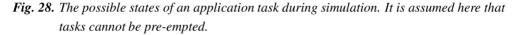

|    |      | 5.3.2     | Network model                                       | 93  |

|    | 5.4  | Measu     | rement constraints                                  | 97  |

|    | 5.5  | Implen    | nentation of the methodology                        | 98  |

|    |      | 5.5.1     | Utilized Transaction generator                      | 98  |

|    |      | 5.5.2     | Evaluation of accuracy and simulation speedup of TG | 100 |

|    |      | 5.5.3     | Utilized Stochastic generator                       | 101 |

|    | 5.6  | Discus    | sion                                                | 104 |

| 6. | On t | he credil | bility of load-latency measurements                 | 107 |

|    | 6.1  | Introdu   | action to load vs. latency measurements             | 107 |

|    | 6.2  | Measu     | rement setup                                        | 108 |

|    | 6.3  | Units o   | of measurement                                      | 112 |

|    | 6.4  | Latenc    | y breakdown                                         | 113 |

|    | 6.5  | Impact    | of the transfer count and length                    | 116 |

|    | 6.6  | Networ    | rk-specific settings                                | 117 |

|    | 6.7  | Discus    | sion                                                | 119 |

| 7. | Hete | rogeneo   | us IP Block Interconnection (HIBI) v.2              | 123 |

|    | 7.1  | HIBI to   | opology                                             | 124 |

|    | 7.2  | Arbitra   | tion                                                | 125 |

|    | 7.3  | Data tr   | ansfer operations                                   | 128 |

|    | 7.4  | Bufferi   | ng and signaling                                    | 132 |

|    | 7.5  | Wrapp     | er structure                                        | 132 |

|    | 7.6  | Runtim    | ne reconfiguration                                  | 134 |

|    | 7.7  | Summa     | ary and comparison to previous HIBI version         | 136 |

| 8. | Benc  | chmarke | d reference network-on-chips          | 139 |

|----|-------|---------|---------------------------------------|-----|

|    | 8.1   | Networ  | rk interface                          | 139 |

|    | 8.2   | Packet- | -switched bus                         | 141 |

|    | 8.3   | Packet- | -switched mesh                        | 142 |

|    | 8.4   | HERM    | IES mesh                              | 142 |

|    | 8.5   | Packet- | -switched ring and octagon            | 143 |

|    | 8.6   | Circuit | and packet-switched crossbar          | 143 |

| 9. | Com   | parison | of NoC implementation results         | 145 |

|    | 9.1   | Implen  | nentation results from literature     | 145 |

|    |       | 9.1.1   | Router parameters                     | 145 |

|    |       | 9.1.2   | Minimum latency                       | 147 |

|    |       | 9.1.3   | Area                                  | 148 |

|    |       | 9.1.4   | Operating frequency                   | 149 |

|    |       | 9.1.5   | Router power                          | 149 |

|    | 9.2   | Implen  | nentation results of studied networks | 152 |

|    |       | 9.2.1   | Reference networks                    | 152 |

|    |       | 9.2.2   | HIBI version 2                        | 155 |

|    | 9.3   | Referen | nce NoCs relative to literature       | 157 |

| 10 | . Com | parison | of NoC performance results            | 159 |

|    | 10.1  | Perform | nance results from literature         | 159 |

|    | 10.2  | Perform | nance evaluation of reference NoCs    | 161 |

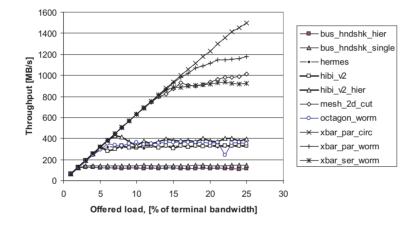

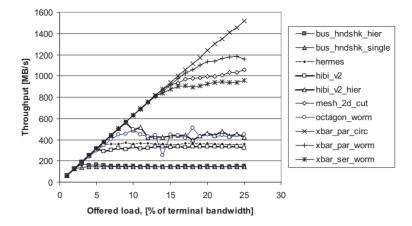

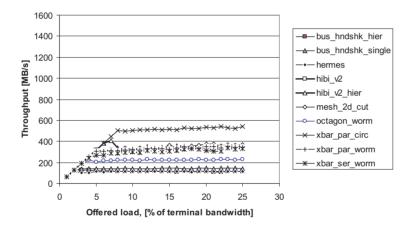

|    |       | 10.2.1  | Spatially uniform random traffic      | 162 |

|    |       | 10.2.2  | Spatially localized random traffic    | 162 |

|    |       | 10.2.3  | Hot spot random traffic               | 165 |

|    |       | 10.2.4  | Relative cost of reference NoCs       | 165 |

| 10.3 Comparison of hierarchical bus and 2-D mesh           | 167 |

|------------------------------------------------------------|-----|

| 10.3.1 Test Setup                                          | 167 |

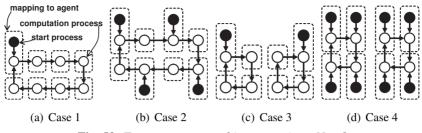

| 10.3.2 Test Cases                                          | 168 |

| 10.3.3 Static Runtime Analysis                             | 169 |

| 10.3.4 Synthesis Results                                   | 170 |

| 10.3.5 Simulation Results                                  | 171 |

| 10.3.6 Relative Cost of the Networks                       | 173 |

| 10.3.7 Results with other networks                         | 175 |

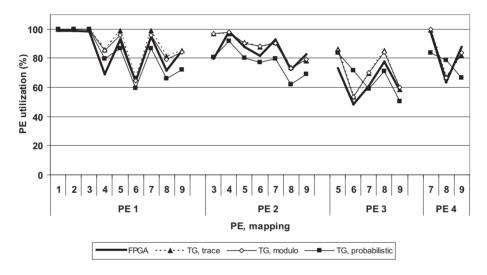

| 10.3.8 Impact of task mapping                              | 176 |

| 10.3.9 Discussion                                          | 180 |

| 10.4 Performance evaluation of HIBI with synthetic traffic | 180 |

| 10.4.1 Simple image processing                             | 180 |

| 10.4.2 The effect of network parameters                    | 183 |

| 10.5 H.263 Video encoder simulation                        | 187 |

| 10.5.1 Data-parallel video encoder test case               | 187 |

| 10.5.2 Modeling with Transaction Generator                 | 190 |

| 10.5.3 Exploration results                                 | 191 |

| 10.6 HIBI-based multiprocessor SoCs                        | 195 |

| 10.6.1 Wireless video terminal on FPGA                     | 195 |

| 10.6.2 MPEG-4 Video encoder of FPGA                        | 196 |

| 10.7 Lessons learned                                       | 199 |

| 11. Conclusions                                            | 203 |

| Bibliography                                               | 207 |

#### LIST OF PUBLICATIONS

This thesis is a monograph which contains unpublished material but is mainly based on the following publications. In the text, these publications are referred to as [P1], [P2], ..., [P13].

- [P1] Erno Salminen, Vesa Lahtinen, Kimmo Kuusilinna, and Timo D. Hämäläinen "Overview of Bus-based System-on-Chip Interconnections," in *IEEE International Symposium on Circuits and Systems*, vol. 2, Scottsdale, AZ, USA, May 2002, pp. 372-375.

- [P2] Tero Kangas, Jouni Riihimäki, Erno Salminen, Kimmo Kuusilinna, and Timo D. Hämäläinen "Using a Communication Generator in SoC Architecture Exploration," in *International Symposium on System-on-Chip*, Tampere, Finland, Nov. 2003, pp. 105-108.

- [P3] Erno Salminen, Kimmo Kuusilinna and Timo D. Hämäläinen, "Comparison of Hardware IP components for System-on-Chip," in *International Sympo*sium on System-on-Chip, Tampere, Finland, Nov. 2004, pp. 69-73.

- [P4] Erno Salminen, Ari Kulmala and Timo D. Hämäläinen, "HIBI-Based Multiprocessor SoC on FPGA," in *IEEE International Symposium on Circuits and Systems*, Kobe, Japan, May 2005, pp. 3351-3354.

- [P5] Erno Salminen, Tero Kangas, Timo D. Hämäläinen and Jouni Riihimäki, "Requirements for Network-on-Chip Benchmarking," in *Norchip*, Oulu, Finland, Nov. 2005, pp. 372-375.

- [P6] Erno Salminen, Tero Kangas, Jouni Riihimäki, Vesa Lahtinen, Kimmo Kuusilinna, and Timo D. Hämäläinen "HIBI Communication Network for Systemon-Chip," *Journal of VLSI Signal Processing-Systems for Signal, Image, and Video Technology*, Jun. 2006, vol. 43, no. 2-3, pp. 185-205, June 2006.

- [P7] Erno Salminen, Tero Kangas, and Timo D. Hämäläinen "The Impact of Communication on the Scalability of the Data-parallel Video Encoder on MP-SoC," in *International Symposium on System-on-Chip*, Tampere, Finland, Nov. 2006, pp. 191-194.

- [P8] Erno Salminen, Tero Kangas, Jouni Riihimäki, Vesa Lahtinen, Kimmo Kuusilinna, and Timo D. Hämäläinen "Benchmarking Mesh and Hierarchical Bus Networks in System-on-Chip Context," *Journal of Systems Architecture*, Aug. 2007, Vol. 53, Issue 8, pp. 477-488.

- [P9] Cristian Grecu, Andrè Ivanov, Partha Pratim Pande, Axel Jantsch, Erno Salminen, Umit Ogras, Radu Marculescu, "Towards Open Network-on-Chip Benchmarks", in *International Symposium on Networks-on-Chip*, Princeton, NJ, USA, May 2007, pp. 205-205

- [P10] Erno Salminen, Ari Kulmala, and Timo D. Hämäläinen "On Network-on-Chip Comparison,"in *Euromicro Conference on Digital System Design*, Lübeck, Germany, Aug. 2007, pp. 503-510.

- [P11] Erno Salminen, Ari Kulmala, Timo D. Hämäläinen, "Survey of Network-on-Chip Proposals", white paper, OCP-IP, April 2008, 13 pages.

- [P12] Erno Salminen, Cristian Grecu, Timo D. Hämäläinen, Andrè Ivanov, "Networkon-Chip Benchmarking Specifications Part I: Application Modeling and Hardware Description", Version 1.0, OCP-IP, April 4, 2008, 15 pages.

- [P13] Erno Salminen, Ari Kulmala, Timo D. Hämäläinen, "On the Credibility of Load-latency Measurement of Network-on-Chips", in *International Sympo*sium on System-on-Chip, Tampere, Finland, Nov. 2008, pp. 91-97.

# LIST OF FIGURES

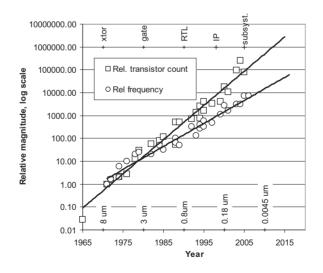

| 1  | Historical scaling of transistor count and operating frequency in inte-<br>grated circuits. Furthermore, feature size and design abstraction level |    |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------|----|

|    | are illustrated along the time axis.                                                                                                               | 1  |

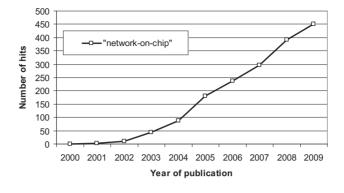

| 2  | Search hits for "network-on-chip" in IEEE Xplore archive                                                                                           | 4  |

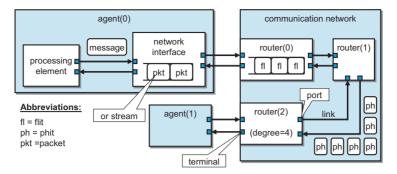

| 3  | Simple network example and corresponding terminology                                                                                               | 9  |

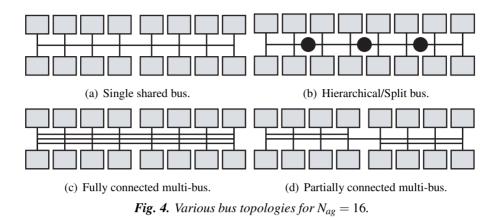

| 4  | Various bus topologies for $N_{ag} = 16. \ldots \ldots \ldots \ldots$                                                                              | 13 |

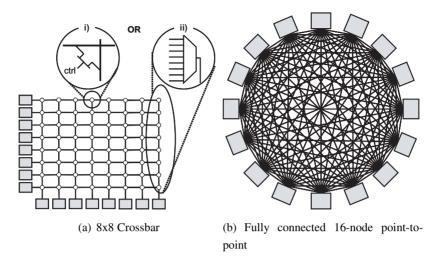

| 5  | Crossbar and point-to-point topologies.                                                                                                            | 14 |

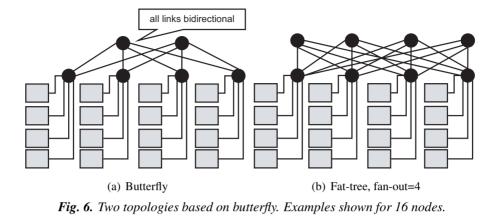

| 6  | Two topologies based on butterfly. Examples shown for 16 nodes.                                                                                    | 15 |

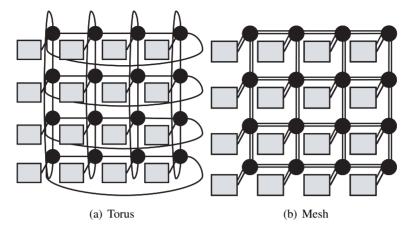

| 7  | Networks based on two-dimensional tori: 16-node torus and mesh. For simplicity, bidirectional links are illustrated only for the mesh.             | 16 |

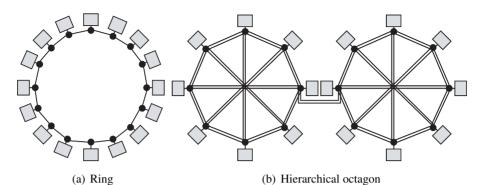

| 8  | Networks based on one-dimensional tori: 16-node ring and 2 8-node octagons (hierarchical express ring).                                            | 17 |

| 9  | 8-node examples of layout optimization                                                                                                             | 18 |

| 10 | Conceptual example of varying PE sizes in 16-node mesh                                                                                             | 19 |

| 11 | Customized 16-node networks with varying PE size                                                                                                   | 20 |

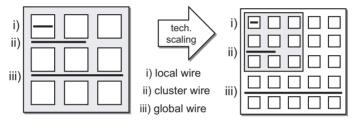

| 12 | Scaling wires with technology                                                                                                                      | 21 |

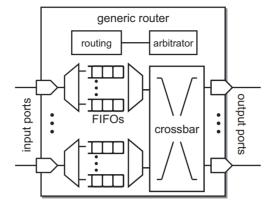

| 13 | The basic structure of a network router.                                                                                                           | 23 |

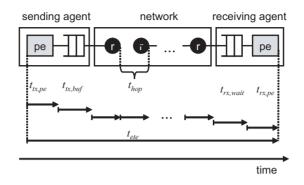

| 14 | The 5 latency components of inter-PE data transfer                                                                                                 | 25 |

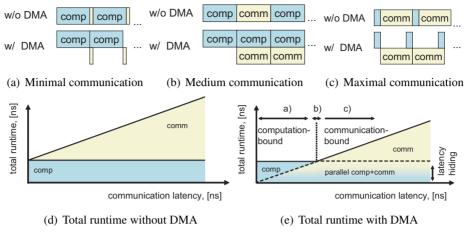

| 15 | The three basic scenarios of overlapping computation with commu-<br>nication.                                                                      | 27 |

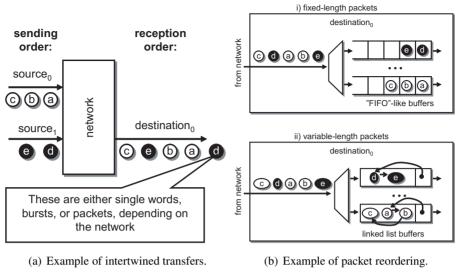

| 16 | Intertwined transfers and packet reordering                                                                                                        | 29 |

| 17 | The impact of limited buffering to transfer initiation. There are two                                                                                                                                   |     |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|    | basic choices when the receiver reserves the buffers for incoming data.                                                                                                                                 | 31  |

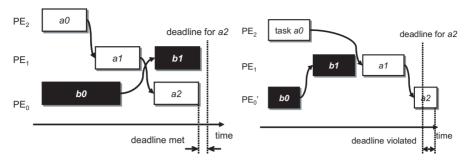

| 18 | An example of scheduling anomaly.                                                                                                                                                                       | 33  |

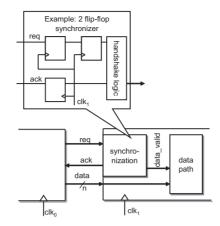

| 19 | Example of synchronization between clock domains                                                                                                                                                        | 34  |

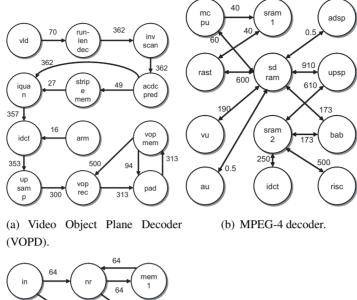

| 20 | Four examples of traffic profiles from [22]. Nodes represent SoC resources and arrows show the sustained traffic rate in $Mbytes/s$ .                                                                   | 63  |

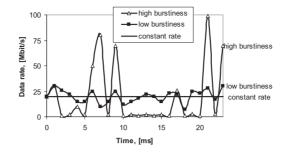

| 21 | Traffic examples with different level of burstiness. The average data rate is the same in three all cases.                                                                                              | 65  |

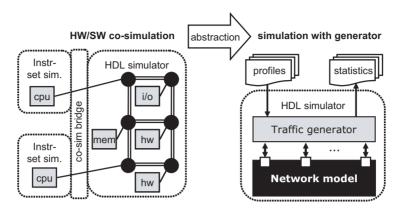

| 22 | HW/SW co-simulation and simulation using a traffic generator                                                                                                                                            | 67  |

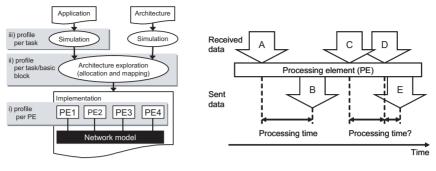

| 23 | Creating a traffic profile.                                                                                                                                                                             | 69  |

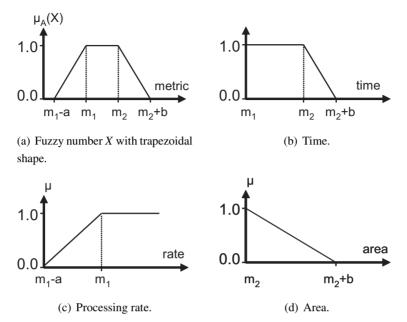

| 24 | Using fuzzy numbers for representing the design objectives. The membership function, shown on Y-axis, is interpreted as relative goodness. Value 1.0 means best solution(s) and value 0.0 unacceptable. | 78  |

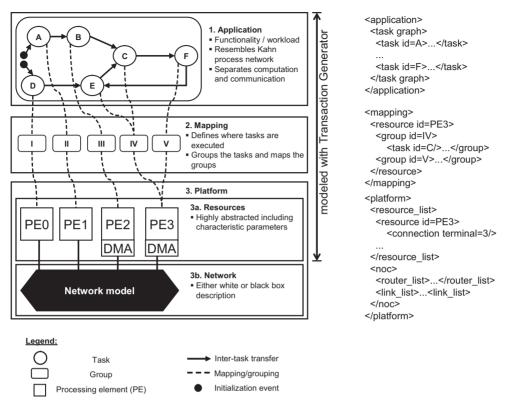

| 25 | Conceptual view of the utilized system model and pseudo-XML                                                                                                                                             | 82  |

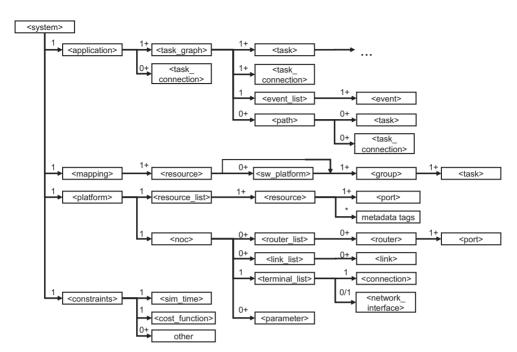

| 26 | Major tags in XML system model. The numbers show the minimum number of occurrences of each tag. Each of the four major sections occurs exactly once. Task description is shown in Fig. 27               | 83  |

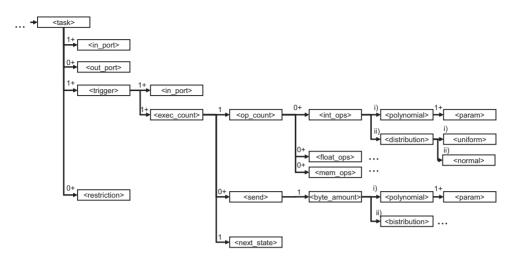

| 27 | XML tags for describing the workload of application tasks                                                                                                                                               | 85  |

| 28 | The possible states of an application task during simulation. It is assumed here that tasks cannot be pre-empted                                                                                        | 87  |

| 29 | Different communication costs between two tasks when a) tasks are<br>on the same PE or b) on different PEs. The task and PE symbols                                                                     |     |

|    | correspond to Fig. 25                                                                                                                                                                                   | 93  |

| 30 | Three types of supported NoC terminals                                                                                                                                                                  | 94  |

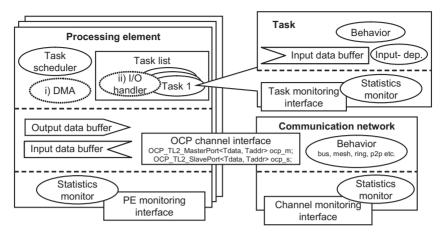

| 31 | SystemC classes of Transaction Generator. Data transfers to/from processing element are implemented either $i$ ) with a DMA or $ii$ ) with                                                              |     |

|    | own I/O handler thread                                                                                                                                                                                  | 99  |

| 32 |                                                                                                                                                                                                         | 100 |

| 33 | The accuracy of Transaction Generator [85, 103]                                                                                                                                                         | 103 |

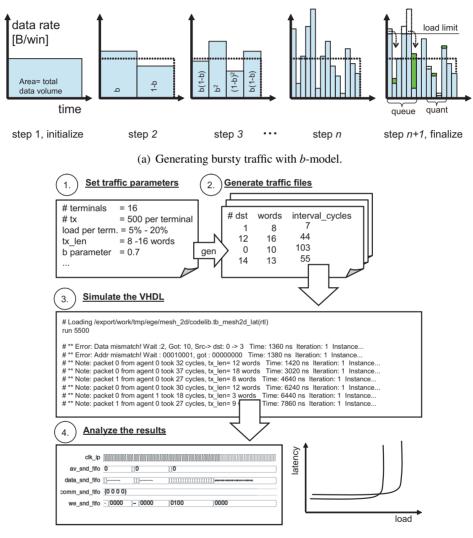

| 34 | Generating and using stochastic traffic                                                                                                                       | 105   |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

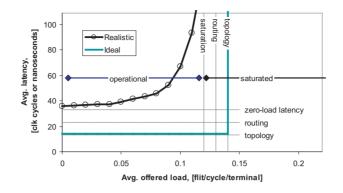

| 35 | Example of load vs. latency curve. X-axis shows the transfer rate<br>and Y-axis the delay. Six analytical bounds are shown in addition to<br>measured values. | 108   |

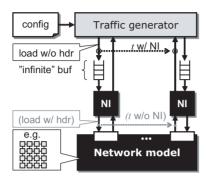

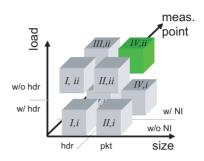

| 36 | Basics of load-latency measurement: different setups and the result-<br>ing deviations in measured performance                                                | 110   |

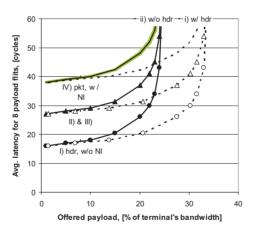

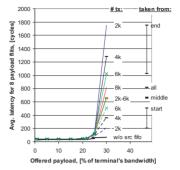

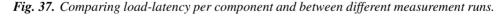

| 37 | Comparing load-latency per component and between different mea-<br>surement runs                                                                              | 114   |

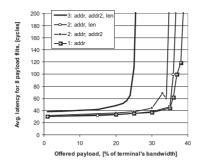

| 38 | Impact of network specific settings: lengths of packet header and payload, and the depth of buffers at the routers. Header is 3 flits unless otherwise noted. | 118   |

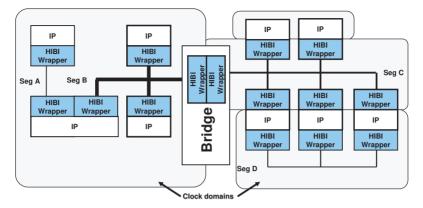

| 39 | Example of a hierarchical HIBI network with multiple clock domains and bus segments                                                                           | 124   |

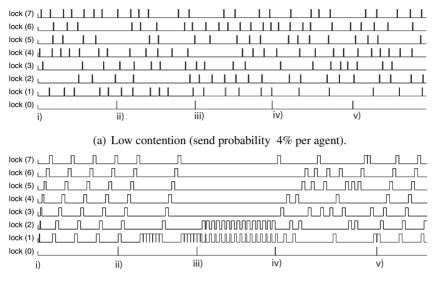

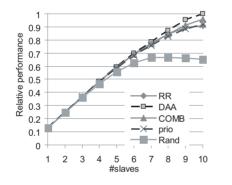

| 40 | Various arbitration schemes for 8-agent single bus and uniform ran-<br>dom traffic. The differences become evident on highly utilized bus                     | 127   |

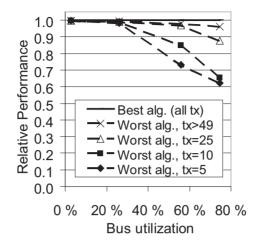

| 41 | Relative performance of arbitration algorithms in MPEG-4 encoding [130]                                                                                       | 128   |

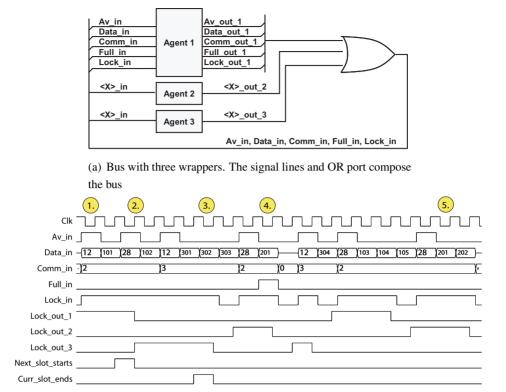

| 42 | Example of bus structure and timing of bus transfers                                                                                                          | 130   |

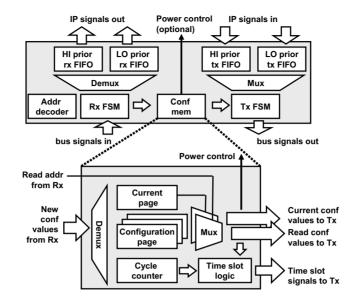

| 43 | Structure of HIBI v.2 wrapper and configuration memory                                                                                                        | 133   |

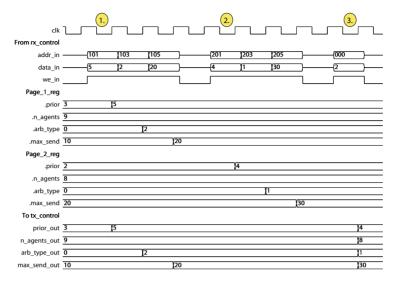

| 44 | Example of runtime configuration                                                                                                                              | 135   |

| 45 | Network interface logic needed for constructing packets                                                                                                       | 140   |

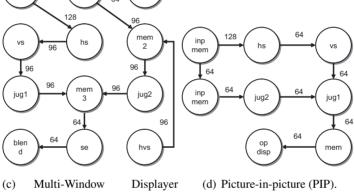

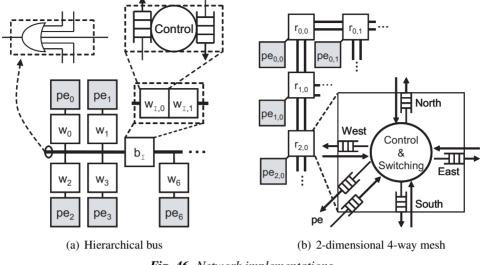

| 46 | Network implementations.                                                                                                                                      | 141   |

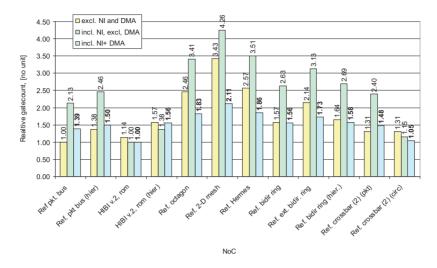

| 47 | The relative areas of reference networks. Calculated for 16-terminal networks. Values in each data set are scaled so that the smallest has an area of 1.0.    | 154   |

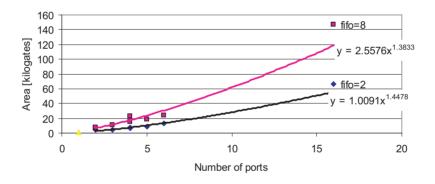

| 48 | The area of network (router) as a function of degree.                                                                                                         | 154   |

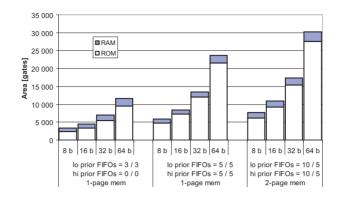

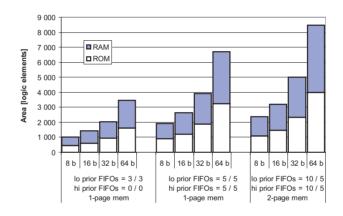

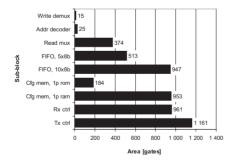

| 49 | Area of HIBI v.2 wrapper and its sub-blocks                                                                                                                   | 156   |

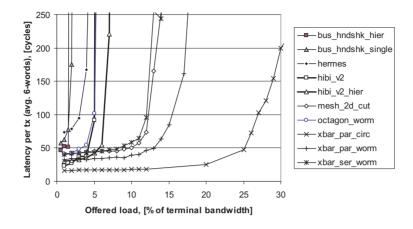

| 50 | Latency and throughput as function of offered load. Average transfer                                                                                          | 100   |

| 50 | length is 6 payload words. Spatially uniform traffic between 16 agents                                                                                        | . 163 |

| 51 | Offered load vs. throughput with spatially localized traffic. There are 16 agents and transfer length is 6 words on average                                       | 164 |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|    |                                                                                                                                                                   |     |

| 52 | Test case types used in comparison, $N = 8$                                                                                                                       | 168 |

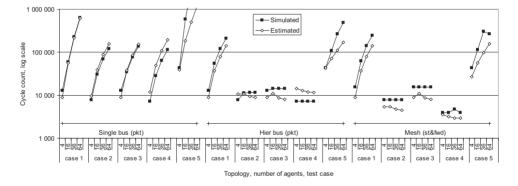

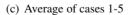

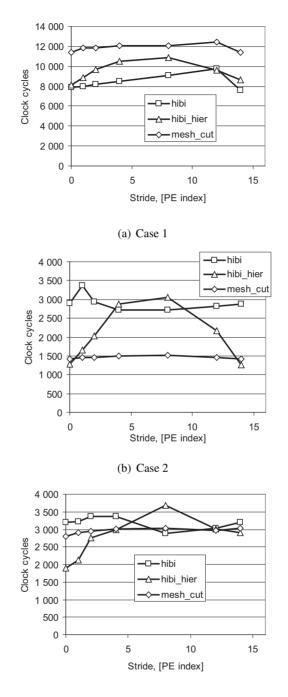

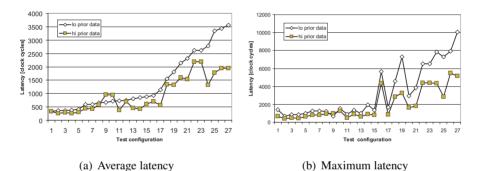

| 53 | Estimated and simulated cycle counts for three networks                                                                                                           | 172 |

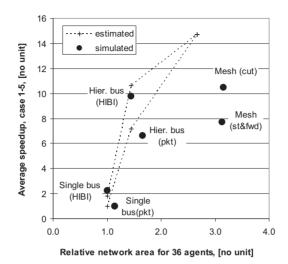

| 54 | Speedup and relative performance, $P = 16, D = 1024$                                                                                                              | 174 |

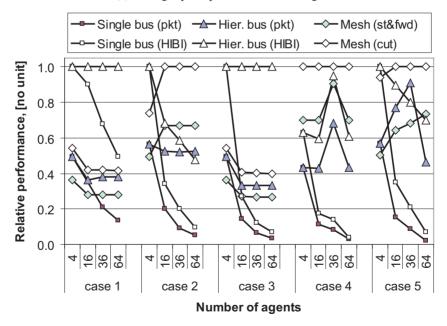

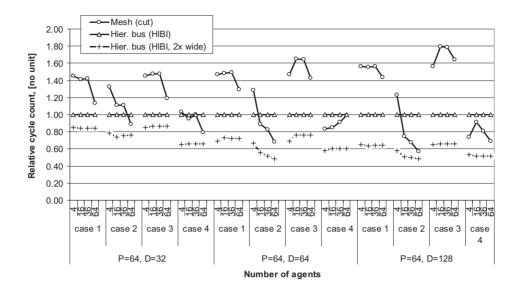

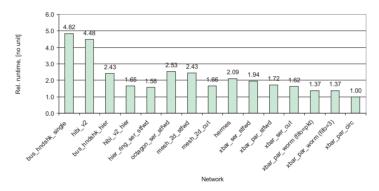

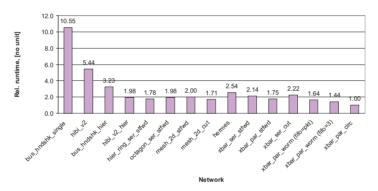

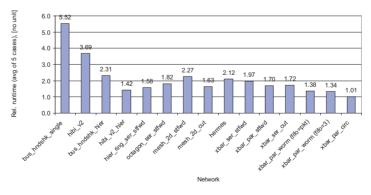

| 55 | The relative runtimes with 4 test cases. Processing time P=64 cycles and data amount D=32, 64 or 128 words                                                        | 175 |

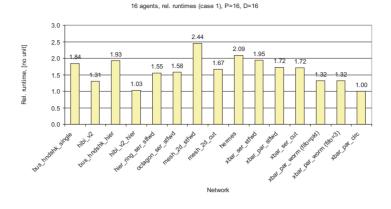

| 56 | The relative runtimes with test cases 1-3. Processing time P=16 cycles and data amount D=16 words                                                                 | 177 |

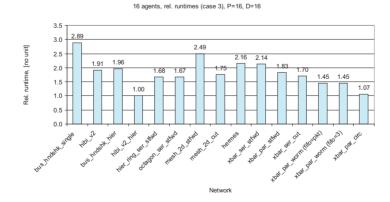

| 57 | The relative runtimes with test cases 4 and 5 and average of all five. Processing time P=16 cycles and data amount D=16 words $\ldots$                            | 178 |

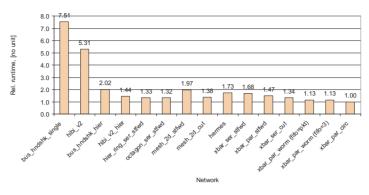

| 58 | The runtimes for test cases 1, 2 and 3 with varying stride value in mapping of tasks. Processing time P=16 cycles and data amount D=16 words                      | 179 |

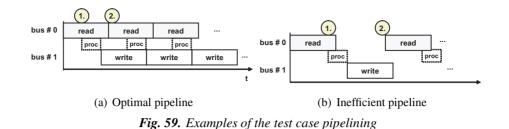

| 59 | Examples of the test case pipelining                                                                                                                              | 181 |

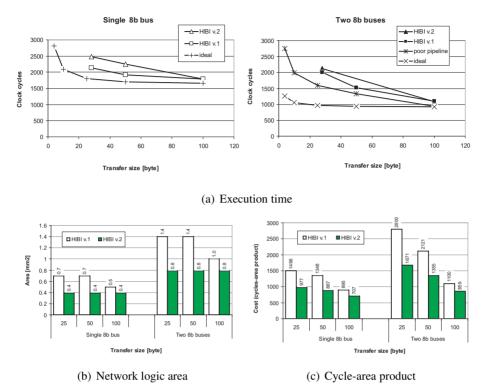

| 60 | Results of the case study: execution time in cycles, logic areas, and cycle-area product                                                                          | 182 |

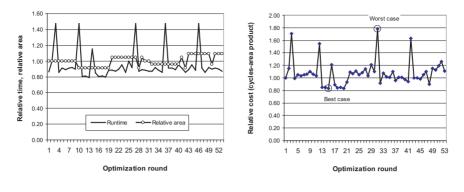

| 61 | Results of the optimization process                                                                                                                               | 184 |

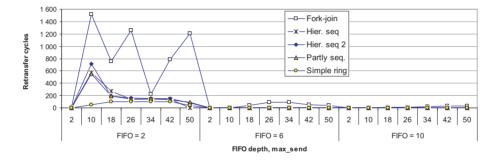

| 62 | Number of retransfers as a function of FIFO size and <i>max_send</i> parameter                                                                                    | 184 |

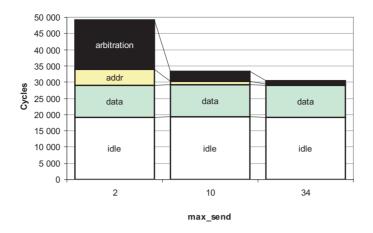

| 63 | Increasing transfer length reduces arbitration overhead                                                                                                           | 185 |

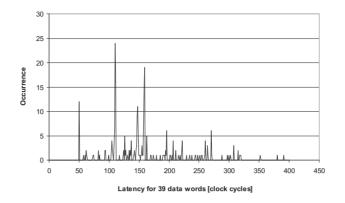

| 64 | Latency variation for system in which four agents send a total of 1000 39-word messages with uniform distribution. Both bus width and data word width are 32 bits | 186 |

| 65 | Effect of relative priority on latency in a test case in which two agents write to the same target                                                                | 186 |

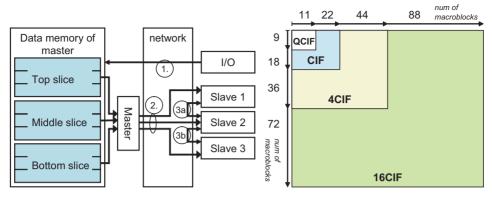

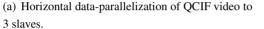

| 66 | Data parallel video encoding                                                                                                                                      | 189 |

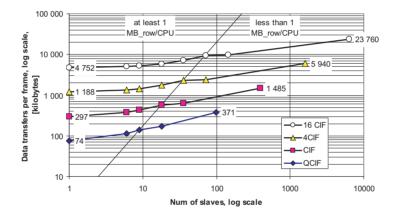

| 67 | Task graph and the example mapping of the video encoder applica-<br>tion. Each slave has identical set of encoding tasks that are initiated<br>by master's task $C1$ | 190 |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

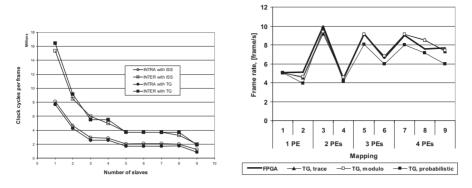

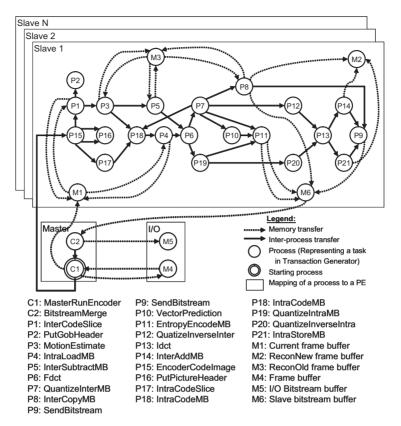

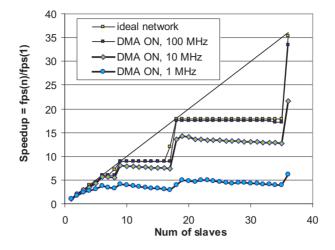

| 68 | Speedup for CIF-sized frames with different bus frequencies. DMA is ON in all cases.                                                                                 | 192 |

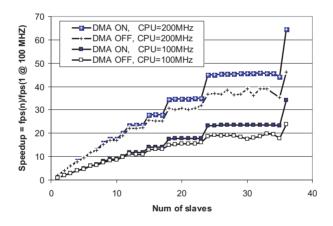

| 69 | Speedup for 4CIF with PE frequency is 100 or 200 MHz, and bus frequency is 100 MHz. Results are given with and without DMA.                                          | 192 |

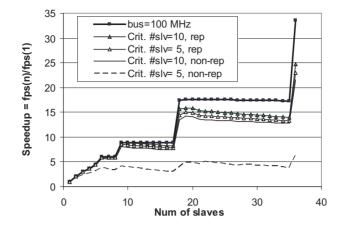

| 70 | Speedup for CIF when bus frequency depends on the number of slaves. Results are shown for repeated and non-repeated wires. DMA is ON in all cases.                   | 193 |

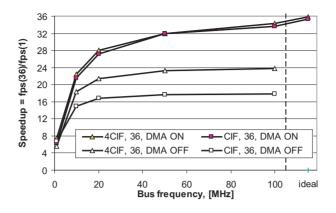

| 71 | Speedup for CIF and 4CIF as a function of bus frequency. System size is 36 slave PEs. Results are shown with and without DMA                                         | 194 |

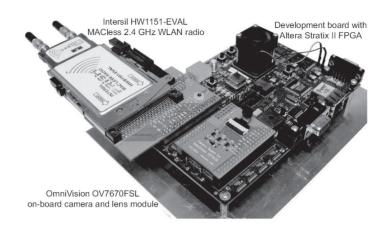

| 72 | Wireless video terminal on FPGA development board. [124]                                                                                                             | 196 |

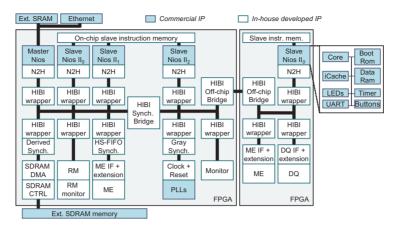

| 73 | The block diagram of HIBI-based MPSoC on (two) FPGA(s)                                                                                                               | 197 |

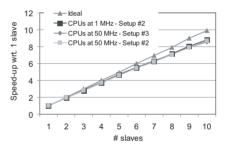

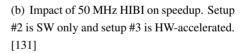

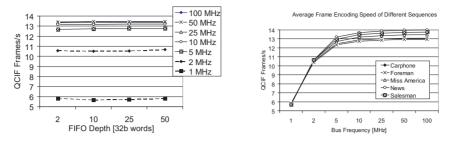

| 74 | The speedup achieved by increasing the number of encoding slave processors with respect to one slave. Test case is MPEG-4 encoder with CIF frames.                   | 197 |

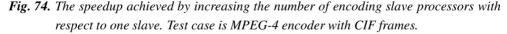

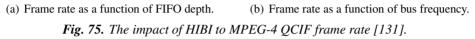

| 75 | The impact of HIBI to MPEG-4 QCIF frame rate [131]                                                                                                                   | 198 |

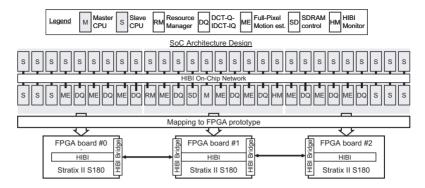

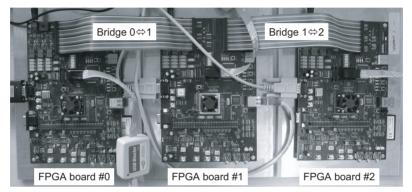

| 76 | A hierarchical HIBI used for interconnecting 58 IP components on a 3-FPGA prototype [129]                                                                            | 199 |

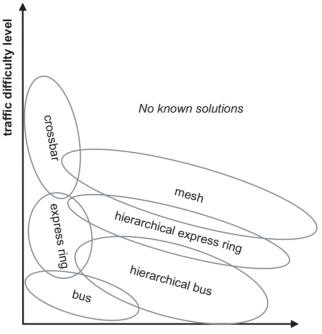

| 77 | The suitability of reference networks considering the number of ter-<br>minals and difficulty of the traffic load. The cost function is area<br>divided by runtime.  | 200 |

### LIST OF TABLES

| 1  | The topology symbols used in other tables                                                                                 | 38  |

|----|---------------------------------------------------------------------------------------------------------------------------|-----|

| 2  | Extensive summary of network-on-chip proposals in literature [P11].                                                       | 40  |

| 3  | Extensive summary of network-on-chip proposals in literature (con-<br>tinued) [P11]                                       | 41  |

| 4  | Summary of comparative NoC studies [P10]                                                                                  | 44  |

| 5  | Summary of comparative NoC studies (continued) [P10]                                                                      | 45  |

| 6  | Datasheet for a stereotypical NoC and suggested research directions [P11].                                                | 51  |

| 7  | Comparison of processor cores [P3]                                                                                        | 52  |

| 8  | Comparison of accelerator IP cores [P3]                                                                                   | 53  |

| 9  | A brief summary of network topology analysis                                                                              | 59  |

| 10 | Comparison of bus and NoC. Adapted and extended from [26,71]                                                              | 60  |

| 11 | Examples of reported traffic loads in multiprocessor applications                                                         | 64  |

| 12 | Simulation guidelines for NoC evaluation [P10]                                                                            | 71  |

| 13 | Metrics for NoC evaluation. The values for all except throughput should be minimized.                                     | 76  |

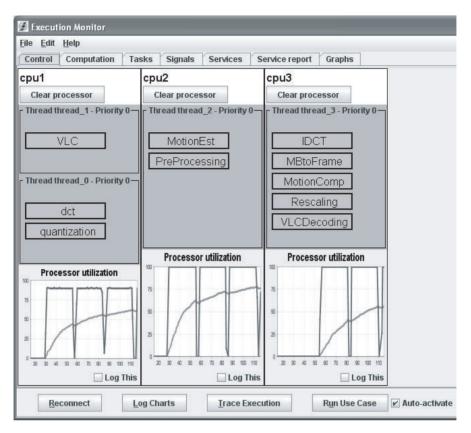

| 14 | Statistics visualized by Execution Monitor [84]. The information is collected either from TG simulation or FPGA prototype | 101 |

| 15 | Summary of application models used in exploration [85]. This work utilizes the same TG as [85, 103]                       | 102 |

| 16 | Measurement settings and the maximum observed differences on pe-<br>formance.                                             | 120 |

| 17 | Properties of HIBI v.1 and v.2.                                                                                                             | 137 |

|----|---------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 18 | Implementation result examples of NoC routers [P10]                                                                                         | 146 |

| 19 | Relative power consumption in NoCs                                                                                                          | 151 |

| 20 | Implementation results of reference NoCs                                                                                                    | 153 |

| 21 | Reported differences between NoCs [P11]                                                                                                     | 160 |

| 22 | The impact of spatial distribution of traffic to the NoC's throughput. Minimum and maximum values in each column are shown in <b>bold</b> . | 166 |

| 23 | Summary of throughputs and relative costs with three traffic classes.                                                                       | 166 |

| 24 | The number of trigger events in test cases as they are scaled with the number of agents $(N)$                                               | 168 |

| 25 | Absolute logic area of the networks (in kilogates) and their relative areas. Area of PE is assumed to be 50 kilogates.                      | 171 |

| 26 | The runtimes in kilocycles for test cases with $P = 16 \ cycles, D = 1024 \ words.$                                                         | 172 |

# LIST OF ABBREVIATIONS

| ACK  | Acknowledge                             |

|------|-----------------------------------------|

| ACM  | Association for Computing Machinery     |

| ASIC | Application-Specific Integrated Circuit |

| BE   | Best Effort                             |

| BIST | Built-In Self-Test                      |

| CAD  | Computer-Aided Design                   |

| CIF  | Common Intermediate Format              |

| CMOS | Complementary Metal Oxide Semiconductor |

| СМР  | Chip Multiprocessor                     |

| CPU  | Central Processing Unit                 |

| DAA  | Dynamically Adaptive Arbitration        |

| DCT  | Discrete Cosine Transform               |

| DMA  | Direct Memory Access                    |

| DRAM | Dynamic RAM                             |

| DSM  | Deep-Submicron                          |

| DSP  | Digital Signal Processing               |

| eCos | Embedded Configurable Operating System  |

| EDA  | Electronic Design Automation            |

| EIB   | Element Interconnect Bus                              |

|-------|-------------------------------------------------------|

| FFT   | Fast Fourier Transform                                |

| FIFO  | First-In-First-Out                                    |

| flit  | Flow control digit                                    |

| FPGA  | Field Programmable Gate Array                         |

| GALS  | Globally Asynchronous, Locally Synchronous            |

| GT    | Guaranteed Throughput                                 |

| HW    | Hardware                                              |

| HIBI  | Heterogeneous IP Block Interconnection                |

| IIR   | Infinite impulse response                             |

| IDCT  | Inverse Discrete Cosine Transform                     |

| IEEE  | the Institute of Electrical and Electronics Engineers |

| IP    | Intellectual Property                                 |

| ISS   | Instruction-Set Simulator                             |

| JPEG  | Joint Picture Experts Group                           |

| KPN   | Kahn Process Network                                  |

| LSB   | Least Significant Bit                                 |

| LUT   | Look-Up Table                                         |

| MCA   | Multicriteria Analysis                                |

| MoC   | Model of Computation                                  |

| MPI   | Message Passing Interface                             |

| MPEG  | Motion Picture Experts Group                          |

| MPSoC | Multiprocessor System-on-Chip                         |

| MSB    | Most Significant Bit                                                          |

|--------|-------------------------------------------------------------------------------|

| NACK   | Negative Acknowledge                                                          |

| NI     | Network Interface                                                             |

| NoC    | Network-on-Chip                                                               |

| OCP    | Open Core Protocol                                                            |

| OCP-IP | Open Core Protocol International Partnership                                  |

| OFDM   | Orthogonal Frequency Division Multiplexing                                    |

| P2P    | Point-to-point                                                                |

| PC     | Personal Computer                                                             |

| PE     | Processing Element                                                            |

| QCIF   | Quarter CIF                                                                   |

| QoS    | Quality-of-Service                                                            |

| RC     | Resistive-capacitive                                                          |

| R&D    | Research and Development                                                      |

| ROM    | Read-Only Memory                                                              |

| RAM    | Random Access Memory                                                          |

| RM     | Resource Manager                                                              |

| RTL    | Register Transfer Level                                                       |

| RISC   | Reduced Instruction-Set Computer                                              |

| RTOS   | Real-Time Operating System                                                    |

| SI     | (French) le Système International d'unités, The International System of Units |

| SoC    | System-on-Chip                                                                |

| SDRAM | Synchronous DRAM                    |

|-------|-------------------------------------|

| SPMD  | Single Program, Multiple Data       |

| SRAM  | Static RAM                          |

| SW    | Software                            |

| TDMA  | Time Division Multiplexed Access    |

| TG    | Transaction Generator               |

| TLM   | Transaction-Level Model             |

| UML   | Unified Modeling Language           |

| VC    | Virtual Channel                     |

| VHDL  | VHSIC Hardware Description Language |

| VHSIC | Very High Speed Integrated Circuit  |

| VLSI  | Very Large Scale Integration        |

| WLAN  | Wireless Local Area Network         |

| XML   | Extensible Markup Language          |

| XSM   | XML System Model                    |

#### **1. INTRODUCTION**

The complexity of integrated chips has increased in an exponential rate for the past decades. This empirical observation is known as *Moore's law* [167]. The term complexity is commonly interpreted as a number of transistors but, historically, also the frequency has scaled in a similar manner. This is illustrated in Fig. 1. which plots the data collected from [49,91]. The computation performance has also increased exponentially and that has been due to three facts: increased transistor budget, increased frequency, and architectural innovations (such as cache memories, pipelining, and instruction level parallelism). A system-on-chip (SoC) integrates a large number of components into a single chip. Usually, the components are not homogeneous but vary in both size and type, for example they can be processors, memories, hardwired

Fig. 1. Historical scaling of transistor count and operating frequency in integrated circuits. Furthermore, feature size and design abstraction level are illustrated along the time axis.

components, and interconnected with a network-on-chip (NoC). This Thesis concentrates on the design and benchmarking of NoCs.

The growth of transistor counts is estimated to continue for several years possibly at a slightly reduced rate, though [30,92,168]. Wire delays, clock skew together with finite rise and fall times of the clock will limit further frequency scaling [82,232]. Parallel processing is commonly utilized in scientific processing that requires high performance [49] and it is utilized to meet the strict computation requirements of modern user applications, such as real-time video encoding [98]. An integrated parallel processing device is referred to as a chip-level multiprocessing (CMP) platform [30] or multiprocessor system-on-chip (MPSoC) [97,249]. Few recent general-purpose examples are Intel Dual and Quad Core processors [70,202], IBM Cell processor [100], and Intel TeraFLOPS [236]. The results of this thesis have been utilized in MPSoCs on FPGA for MPEG-4 encoding [128] and for wireless networking [124].

Component reuse offers a great improvement in system design and it is necessary to handle the complexity [37]. Sylvester and Keutzer have proposed block-based hierarchical design style where the size of the used hardware block is in the range of  $50\ 000 - 100\ 000$  equivalent gates (or  $50k - 100k\ gates$ ) [232]. Such blocks can be designed and verified without excessive attention on various deep-submicron (DSM) effects, such as wire delays. Direct consequence is that the number of components will increase as the chip complexity increases. Large component count emphasizes the impact of communication on the overall performance and cost of SoC. Note however that system integrators nowadays work with larger entities, subsystems that already include several intellectual property (IP) components in order to implement complex functions.

Automated design tools are necessary for handling the complexity of a large MPSoC. *Koski* design flow is one example which includes high-level design and requirements capture in UML, automated design space exploration, code generation and hardware synthesis, FPGA prototyping, and back-annotation of measured values. Despite author's contribution to Koski, detailed discussion is beyond the scope of this thesis and interested readers are referred to [103, 104].

Koski follows platform-based design methodology [112, 217]. The basic principle is a sequence of refinement steps that go from the initial specification towards the final implementation using platforms at various level of abstraction. One pillar of the

methodology is the separation (or orthogonalization) between:

- function (what the system is supposed to do) and architecture (how it does it);

- communication and computation.

Separation of concerns and clear, unambiguous interfaces allow the designer to concentrate only on one part of the system without modifying the other part. For example, the communication network can be designed, modified, and optimized while keeping the computation resources fixed. Separation between communication and computation, allows also interleaving their execution to maximize the performance.

Traditionally, SoCs utilize a single shared bus or a bus hierarchy for interconnecting the IP components. In the late 1990's and early 2000's, many researchers proposed replacing dedicated, design-specific wires with a general purpose, packet-switched network, hence marking the beginning of the network-on-chip (NoC) era. The major goal of NoC is to achieve greater design productivity by handling the increasing parallelism, manufacturing complexity, wiring problems, uncertainty, and by introducing communication-centric design methodologies.

NoCs have been widely reported in several special issues in journals, numerous special sessions on conferences and recently also in a dedicated NoC symposium <sup>1</sup>. As an example of increased interest, Fig. 2 shows the hit count for the search "network-on-chip" in the IEEE Xplore document archive <sup>2</sup>.

The key research areas in network-on-chip design are summarized in [26, 180] as

- Communication infrastructure: topology and link optimization, buffer sizing, floorplanning, clock domains, power

- Communication paradigm: routing, switching, flow control, quality-of-service, network interfaces

- Benchmarking and traffic characterization for design- and runtime optimization

- Application mapping: task mapping/scheduling and IP component mapping.

<sup>&</sup>lt;sup>1</sup> www.nocs.org

<sup>&</sup>lt;sup>2</sup> http://ieeexplore.ieee.org

Fig. 2. Search hits for "network-on-chip" in IEEE Xplore archive.

The three critical challenges for NoC according to Owens *et al.* are power, latency, and CAD compatibility [184].

#### 1.1 Objective and scope of research

The objective of this work was to design an efficient communication method for IP components in a System-on-chip.

This thesis presents an extensive survey of network-on-chips, a new proposal for benchmarking them, and a detailed comparison of various networks. In addition, a new NoC, HIBI, is presented and analyzed. A set of reference network implementations is implemented for comparison purposes. An analysis follows the conceived guidelines and considers HIBI and reference NoCs. Simulation and FPGA execution are emphasized. The results of the comparison are discussed relative to those from the literature.

This thesis concentrates on digital components only and abstraction is mostly at the register transfer level (RTL). The studied networks are targeted for interconnecting intellectual property components, such as microprocessor cores, memories, and hard-wired accelerators.

To summarize, the main contributions of this thesis are the following:

• Surveys of existing NoCs and evalutation studies are presented

- Development of the HIBI NoC

- Systematic method for comparing NoCs

- synthesizable reference implementation for various topologies

- versatile traffic generation for networks

- benchmarking guidelines

- standardization work on benchmarking

- Comprehensive comparison of NoCs using the above method

#### 1.2 Thesis outline

The outline of this thesis as follows. At first, Chapter 2 introduce the basic concepts of communication networks and Chapter 3 presents a literature study and analysis of existing network-on-chip proposals and their comparisons. In addition, a survey of IP components is given. Chapter 4 presents the basics of communication network evaluation and Chapter 5 presents a new benchmarking methodology for NoCs. Chapter 6 discusses the latency measurement of NoCs in detail. Chapter 7 presents the developed HIBI network and Chapter 8 the reference NoCs. The results of NoC comparison are given in Chapters 9 and 10. Chapter 11 concludes the Thesis.

\_\_\_\_

### 2. COMMUNICATION NETWORKS

Due to some inconsistencies found in literature let us start by defining the terms that will be used in this thesis. After that the basic network structures and components are introduced, followed by a discussion about topology-independent issues in intra-SoC communication.

#### 2.1 Basic properties and terminology

This terminology follows mostly the definitions by Dally and Towles [51]. Synonyms that are used in the literature are shown in parentheses. A *communication network* (*switching fabric*) is a system that transports data between its *terminals*, i.e. its input and output ports. A specific *network-on-chip*, NoC, paradigm will be discussed later in its own section. A communicating entity is here called an *agent* that may consist of one or multiple processing elements (PEs), memory banks, and a *network inter-face* (NI). The number of agents is here denoted as  $N_{ag}$ . Agents perform *transactions* by exchanging *messages*. A split transaction performs bidirectional communication with two separately transferred messages, such as a read request and a response. Each message can create one or more *packets* depending on the parameters of the communication network. Packets have a restricted maximum length unlike the messages. The data injected to the network are referred to as the *traffic load*. The load is characterized by its spatial (where) and temporal (when) distributions.

The network interface is responsible of splitting messages into packets at the source and combining, and possibly reordering, them at the destination. Agents that can initiate transfers are called *masters* and agents only responding are called *slaves*. Such distinction is not always made when some or all the agents operate in both modes.

A non-blocking network allows simultaneous transfers between all source-destination

pairs provided that the destination is free and is not the destination of any other transfers. *Blocking* networks have more restrictions on simultaneous transfers, for example, some link along the path may be blocked although the destination is free.

#### 2.1.1 Structural properties

The topology defines the arrangement of the network's routers (switches, network nodes) and links (channels). The topologies are divided, somewhat superficially, into two categories: direct and indirect. The routers in a direct network are always connected to (at least one) agent; they all are network terminals. In an indirect network, there are routers that are connected only to other routers. Each router has two or more ports and their number is here referred to as router's degree (or radix). In this thesis, all links and ports are unidirectional and the degree defines the sum of input and output ports in a router. A bidirectional link is formed from two unidirectional links. The term router is not commonly used with bus networks. Instead, the connection between the resource and the network is done by a bus wrapper or bridge.

A link contains the data and control bits going *downstream* (direction from source to destination) and also the flow control bits going *upstream*. All these bits are considered to form a *wire bundle* to avoid confusion with the bus topology. A packet may require several *hops* to reach the destination; one hop denoting here the traversal of one link. Networks that do not have any routers, for example point-to-point, have just one hop.

## 2.1.2 Temporal properties

Networks are divided into two categories with respect to their connection type: *circuit-switched* and *packet-switched*. Circuit-switching forms a path from the source to the destination prior to the transfer by reserving the routers (switches) and links. All data follow that route and the path is torn down after the transfer has completed. This guarantees the latency and attained throughput. However, the time required for setting up the circuit may be long and the bounds for setup time hard to define. In the packet-switching scheme, the source creates and sends packets to the network and each packet is routed separately to the destination. This Thesis uses a terminological

Fig. 3. Simple network example and corresponding terminology.

convention that circuit-switched networks include switches whereas packet-switched networks include routers.

*Contention* (*congestion*) for the shared resources of the network, such as router ports or links, introduces varying latencies for packets. *Arbitration* is the method to resolve the contention.

*Routing* is the mechanism that determines the *path* (*route*), the set of links, taken between the source and destination. With *deterministic* routing, all packets between the source-destination pair always follow the same route and hence remain in-order. *Adaptive* routing tries to avoid the congested regions, *hot-spots*, by varying the route. Hence, packets may occasionally arrive to the destination out-of-order. *Oblivious* routing, a subclass of adaptive algorithms, does not consider the state of the network when determining the route, for example, the route is selected pseudo-randomly for each packet. Some adaptive routing schemes allow *misrouting* which means that packets are routed away from the minimal route at some points.

*Flow control* manages the reservation of network resources, mainly router buffers and links. Each packet consists of one or multiple *flow control digits, flits*, that is the smallest unit of data to which resources can be allocated. A packet can be divided into *header, payload*, and *tail flits*. The header provides control data for the network and determines at least the destination, and optionally other control information, such as packet length or priority. It is followed by the payload, or *body*, that is the actual data. Tail denotes the end of the packet and may provide information for checking the integrity of the data. The length of these parts varies between networks and the payload and tail may be omitted in some cases. If they are present, they must follow

the same route as the header and remain in order. There are also cases where the header and the payload are transmitted in parallel within one flit <sup>1</sup> as well as cases where the length of the payload varies between packets. The data is transmitted on channels one *physical digit, phit*, at a time. A phit does not necessarily have the same size as a flit. For example, the buffers are allocated for 32-bit flits but serial links use 1-bit phits.

Fig. 3 depicts an example of the terms. The shown network is indirect since router(1) is not a terminal. The network has 4 unidirectional links between the routers and all routers have a degree of 4. The message sent by PE(0) is split into two network packets and each packet contains three flits. Here, the phits are smaller than flits, and hence, each packet contains six phits. In the remainder of this thesis, however, the flit and phit sizes are always equal and that number of bits referred to as the *data width*. The hop count  $N_{hops}$  from agent(0) to agent(1) is 2 hops:  $router(0) \rightarrow router(1)$  and  $router(1) \rightarrow router(2)$ . The number of routers in that path is  $N_{hops} + 1 = 3$ .

#### 2.1.3 Performance measures

In this thesis, the term *performance* refers to metrics that should be maximized, such as throughput and error tolerance. *Cost* metrics, such as application runtime, area, latency, and power consumption, should be minimized. The performance metrics are also discussed later, for example, in Sections 3.2.2 and 4.4.6.

*Throughput*, or *accepted traffic load*, is the maximum data rate that can be delivered to destination terminals with given load conditions, for example Bytes/s. It is the sum of data rates at destination ports <sup>2</sup>. In this thesis, the term *bandwidth* refers to theoretical maximum accepted load and throughput to realized accepted load. Some sources use these terms interchangeably, though. *Saturation* occurs when increasing offered load does not increase the accepted load; it remains constant and sometimes is may even drop. As the offered load increases beyond the saturation point, the average transfer latency experienced by the agents (end-to-end latency) approaches infinity.

*Scalability* in general means that something is capable of being easily expanded or upgraded on demand. Scalability is often hard to prove and the term is often used

<sup>&</sup>lt;sup>1</sup> This scheme is traditionally used in bus topologies although they are not generally considered as packet-switched networks.

<sup>&</sup>lt;sup>2</sup> Measuring at input terminals is misleading if network drops packets.

too carelessly. For parallel applications, there is some consensus that as the size of a scalable machine increases, a corresponding increase in performance is obtained. Scalable network architecture allows adding/removing components with modest effort, and the performance should increase/decrease correspondingly.

*Bisection* is a set of channels (*cut*) that partitions the network into two halves such that the number of routers of both halves differ at most by one. *Bisection bandwidth* is the bandwidth of the smallest such cut. Bisection is one scalability metric of the network. If bisection grows slower than  $N_{ag}$  or is constant, it will become a system bottleneck as network grows unless data is localized efficiently.

*Latency* refers to the time between the first bit entering the network at the source terminal and the last bit arriving at destination terminal. It is measured in seconds or in clock cycles but the latter option is not always possible, for example with asynchronous networks. Usually the maximum and average of all packet latencies are monitored. Another important aspect is the difference between latencies which is called *jitter*. Latency can be measured on multiple levels, for example for transactions, messages, packets, or packet headers.

Latency of a packet can be defined as

$$T_{pkt} = T_{hdr} + T_{ser} + T_{cont}.$$

(1)

where  $T_{hdr}$  denotes header latency,  $T_{ser}$  serialization latency, and  $T_{cont}$  contention overhead [51]. Header latency  $T_{hdr}$  is the time required for the head of the message to reach the destination:

$$T_{hdr} = (N_{hops} + 1) \cdot T_{router} + N_{hops} \cdot T_{link}.$$

(2)

$T_{router}$  is the time needed per router without any contention and  $T_{link}$  is the propagation delay of a link. Note that there is one router more than there are links in a path. The message must be serialized on the links so that  $T_{ser} = N_{msg\_bits}/b_{link}$ , where  $N_{msg\_bits}$  denotes message size in bits and  $b_{link}$  denotes the link bandwidth. The last term is caused by contention and is generally hardest to analyze without simulation. In most cases, the measurement setup must ensure that the traffic sources will not be stalled during measurement.

*Fault tolerance* describes the ability of the network to perform in the presence of one or more faults. It has been recognized for long a time in large networks such as

telephone and internet, but it is also emerging into the NoC domain. A fault in an integrated chip cannot always be repaired after fabrication. However, the faulty parts can be avoided once detected, for example by routing the data via a fully functional path. Deep-submicron technologies also increase the number of transient errors (soft errors) [92] and emphasize the importance of fault tolerance. There are five key elements to tolerate faults: avoidance, detection, containment, isolation, and recovery. Fault-tolerance can be achieved via error detection and correction, stochastic communication, adaptive routing, and both temporal and spatial redundancy [69].

*Quality-of-service* (QoS) refers to the levels of guarantees given for data transfers. Guarantees can be related to timing (min. throughput, max. latency, max. latency jitter), integrity (max. error rate, max. packet loss), and packet delivery (in-order or out-of-order). Most contemporary articles concentrate on timing aspects. Transfers are categorized as

- a) Best effort (BE) scheme forwards packets as soon as possible but no guarantees are given for latency or throughput in general case. This is the most common approach nowadays. If packet injection to the network is restricted by the NI, a (loose) upper bound can be determined for the network latency [94] but not always for the waiting time at the NI.

- b) *Guaranteed throughput* (GT) scheme can offer a minimum level of transfer capability through the network.

# 2.2 Network topologies

This section reviews some basic topologies that have been proposed for NoCs. Their properties are analyzed later in more detail.

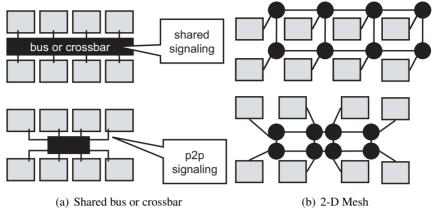

## 2.2.1 Single-hop topologies

The term *bus* refers to a set of signals connected to all communicating devices. A bus is called *multimaster* or *shared* when there are more than 2 agents that are able to initiate transfers. Fig. 4 shows few variations of the bus topology: single, hierarchical and multibus. Only a single agent (rectangle in figure) can transfer data on a shared

bus at any time. All other agents can receive data simultaneously and hence *broadcast* operation is very simple. The limitations are obvious: the bandwidth is shared among agents, the length of wires increases with system size, and some means for *arbitra-tion* (resolving contention) are needed. Despite these limitations, bus topology has been very widely utilized, especially in small-scale systems, for example  $N_{ag} < 16$ . Moreover, parallel computers utilizing a shared bus with up to 70 processors have been built [49].

Simple modifications to the basic shared bus topology alleviate the problems. Dividing the long bus lines into shorter segments, Fig. 4(b), improves electrical properties and allows multiple parallel transfers. The segments are connected together with *bus bridges* (black circles). A topology that uses a simple three-state buffer or similar combinatorial logic is here called a *split bus* whereas a *hierarchical bus* uses more complex bridge elements that possibly buffer the data. However, bridges impose an area penalty and the transfers that cross the bridges experience a longer latency than local transfers within one segment. Therefore, hierarchical buses are best suited to traffic with locality. A hierarchical bus is built either as a simple chain of bus segments or as a tree like structure <sup>3</sup>.

A ring-bus is formed by connecting together the ends of a split-bus [152]. It is considered a circuit-switched ring in the presented taxonomy. Latency in a hierarchical bus is analyzed, for example, in [43]. Energy-area and delay-area trade-offs in segmented buses are analyzed in [72].

$<sup>^{3}</sup>$  It is presented here due to similarity with other bus topologies although it is a multi-hop topology.

Fig. 5. Crossbar and point-to-point topologies.

The bandwidth can be increased by adding several parallel bus links. The agents can be connected to all links, as in Fig. 4(c), or only to a subset, as in Fig. 4(d). The former is also called *multi-layer bus* and suffers from long wires just like the single bus topology.

A multibus topology having an equal number of links and agents is called a *crossbar*, and shown in Fig. 5(a). A regular crossbar allows two transactions (sending and reception) per terminal. It is almost similar to a *fully connected point-to-point* (P2P) network, but a true P2P allows that one agent transfers data simultaneously to all targets or receives from all sources.

The crossbar in Fig. 5(a) shows inputs on the left and outputs on the bottom. The connections are formed with i) pass transistors or ii) with multiplexers. A crossbar topology is also called a *star* [44, 143] but the difference is merely related to the drawing style only and not to the functionality.

The implementation cost of both crossbar and P2P grows as  $N_{ag}^2$  and they exhibit long wires which limit their utilization mostly to small scale systems. At the same time, these topologies offer by far the largest bandwidth. Partially connected P2P network can result in major saving in network area in cases where all agents do not communicate and the needed source-destination pairs are known, for example inside a hardwired accelerator component. Partially connected crossbar is actually a sort of an multilayer bus.

2.2.2 Multi-hop topologies

The previous networks (except hierarchical bus) deliver data in one hop. Most other topologies deliver data with multiple hops, and they are derived from two families of regular networks : *butterflies* (k-ary n-flies) or *tori* (k-ary n-cubes, or hypercubes, or cubes for short). It is of course possible to have a *hybrid* topology or customize it according to application.

Fig. 6 shows two examples of butterflies. A fat-tree is a *folded butterfly* network and has many variations, for example [32,51,109,189]. It differs from a regular tree since the number of links (bandwidth) does not decrease towards the root. There are two major drawbacks with these networks: butterfly offers in its minimal form only a single path between terminals, and the longest links in a butterfly must traverse at least half the perimeter of the machine [51]. However, they allow simple routing and the maximum hop count increases logarithmically with the network size. Varying router degrees can be used to increase the scalability and performance in eXtended Generalized Fat-Tree (XGFT) [109]. Butterflies are also called *multistage interconnection networks* and there are several variations; for example, so called Banyan, Clos, and Benes variants of the butterfly network can replace a crossbar if some blocking is allowed. Splitting one large crossbar into several smaller crossbars results in notable area savings.

Fig. 7 and 8 shows four multihop network examples based on tori. Fig. 7(a) shows a 16-node 2-D torus (4-ary 2-cube) where each PE is connected to a router which is connected to 4 neighbor routers. A 2-D mesh (4-ary 2-mesh), Fig. 7(b), is a de-

Fig. 7. Networks based on two-dimensional tori: 16-node torus and mesh. For simplicity, bidirectional links are illustrated only for the mesh.

generate version of the torus since it does not have the wraparound links. All k-ary n-cubes have the number of nodes  $N_{ag} = k^n$  packed in a regular n-dimensional grid and channels between nearest neighbors.

Typically, the links are bidirectional, as illustrated by two unidirectional links <sup>4</sup> for the mesh. Unidirectional links with a single driver are beneficial because they can be pipelined [22] A unidirectional mesh is also called a *Manhattan (street)* network.

A unidirectional ring (*16-ary 1-cube*) is shown in Fig. 8(a). A (hyper)cube topology can be extended to an *express* (*hyper*)*cube* by adding a number of long links between non-neighboring nodes. Adding long-range links to the mesh in systematic way has been studied by Ogras *et al.* [181] and it was shown to improve performance notably. For an 8-node ring this scheme is also called an *octagon* (octa = eight), Fig. 8(b). Assuming identical PEs, the system can be scaled without increasing the maximum wire length. The longest link inside one octagon ring is about 4 side lengths of a PE [107]. Larger networks can be built hierarchically from 8-node octagon rings or using a Spidergon topology that allows the scheme to be extended for other ring sizes than eight [61].

The performance increases with increased cube dimensions due to lower average hop count but saturates quickly when network costs are kept constant [51]. For example, the limited number of pins per router or the size of the crossbar inside each router

<sup>&</sup>lt;sup>4</sup> A multibit, unidirectional link is actually a point-to-point *bus*.

Fig. 8. Networks based on one-dimensional tori: 16-node ring and 2 8-node octagons (hierarchical express ring).

might force adoption of narrower links as the router's degree increases. However, Soteriou *et al.* found 3-D tori superior among the studied topologies in many cases [227]. They used a planar layout, whereas a "true" 3-D IC was considered in [62] and [192]. However, laying out 3-dimensional structures on a 2-dimensional chip may prove to be difficult, either resulting in long wires or routing congestion. Therefore, 3-D topologies are omitted here for brevity and because they are not widely utilized in NoCs (see Tables 2 and 3). The next section discusses the issues related to the floorplan of the chip.

## 2.3 Floorplan of network-on-chips

A floorplan refers to the placement of system components on a chip. The floorplan of the bus (single, hierarchical, multibus) and mesh resembles the conceptual view very closely. The long wraparound links in a torus can be removed by using so called *folded torus* floorplan. In a mesh, all links have a constant length (1 side length of PE) irrespective of  $N_{ag}$  whereas in a folded torus some links have twice this length.

The ring floorplan can also be realized with constant length links. Few links that are longer than one PE side length are needed depending on the number of PEs.

Fig. 9. 8-node examples of layout optimization.

## 2.3.1 Basic floorplan optimizations

Fig. 9 shows simple floorplan optimizations for the bus and mesh. Similar techniques can be applied to other topologies as well. A conceptual, unoptimized layout, where the network logic, bus wrapper or router, is always adjacent to PE, is shown on top. A simple optimization to layout, shown on bottom, moves the network logic towards the center of the system. The longest link in the bus and the total link length in the mesh are consequently reduced although some of the PE-wrapper (PE-router) links become longer. Those links are unidirectional, point-to-point signals and are hence suitable for repeater insertion or pipelining. They also have lower utilization than those between the routers or wrappers. In the bus topology, the longest wire length is now defined as the size of the wrappers instead of the PE size. In the mesh, the longest wire remains the same but the total wire length is reduced. Routability of wires in different topologies has been studied in [213].

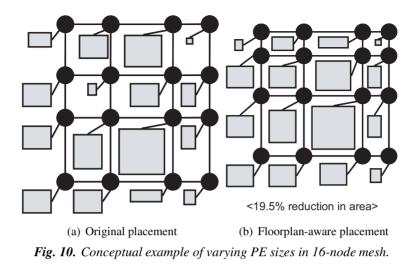

#### 2.3.2 Irregular size of processing elements

Fig. 10(a) shows how a regular mesh can be applied when the size and shape of the agents varies. The minimum column width (or row height) is now determined by the largest agent on the column (row) which leads to unutilized space on the chip and hence excess area. The PE locations can be reordered in order to minimize area as shown in Fig. 10(b).

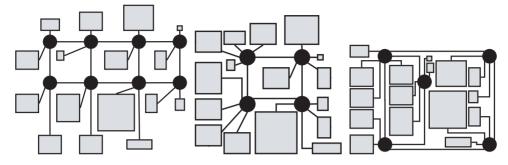

Mesh topology can be customized by connecting many PEs to the edge routers, as shown in Fig. 11(a) for top and bottom rows. The example has only 8 routers instead of 16 which implies notable savings in area at the expense of reduced aggregate bandwidth. The router degree remains the same (4 + 4 or 5 + 5). Another option is to increase the router degree further and hence create so called *star-mesh* network. Fig. 11(b) shows a regular topology having 4-PE clusters. A cluster has star (crossbar) topology whereas the clusters are connected through mesh. The star-mesh is an example of a topology that combines two topologies: one at the local level (star, i.e. crossbar) and one at the global level (mesh). In principle, any topologies can be combined. Lee *et al.* [144] have shown that such hybrid topologies are beneficial in many cases.

An example of an irregular topology, where the routers are connected to a varying number of PEs, is shown in Fig. 11(c). This last approach may be supported by an automated synthesis tool for optimizing the topology and few examples are presented in [22]. One possibility (not shown) is to allow large PEs to span multiple "slots" in a regular mesh. Such an irregular scheme is called *mesh with regions*. To avoid deadlock, routing is somewhat more complex in irregular topologies than in regular ones <sup>5</sup>. These networks have been studied, for example, in [86].

<sup>&</sup>lt;sup>5</sup> Note that a request-response deadlock between communicating ends can still happen regardless of the routing policy or topology.

(a) Sharing mesh routers on top and (b) Regular custom network (c) Irregular custom network bottom row (star-mesh)

Fig. 11. Customized 16-node networks with varying PE size.

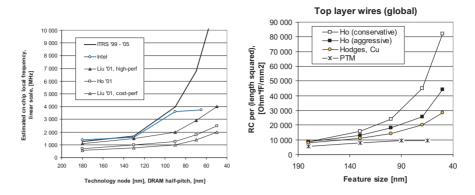

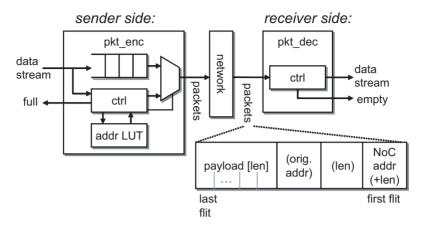

### 2.3.3 Wiring