# Timo Viitanen Hardware Accelerators for Animated Ray Tracing

Julkaisu 1551 • Publication 1551

| Timo Viitanen                                                                                                                                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hardware Accelerators for Animated Ray Tracing                                                                                                                                                                                                       |

| Thesis for the degree of Doctor of Science in Technology to be presented with due permission for public examination and criticism in Tietotalo Building, Auditorium TB109, at Tampere University of Technology, on the 25th of May 2018, at 12 noon. |

|                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                      |

| Tampereen teknillinen yliopisto - Tampere University of Technology Tampere 2018                                                                                                                                                                      |

Tampereen teknillinen yliopisto. Julkaisu 1551 Tampere University of Technology. Publication 1551 Doctoral candidate: Timo Viitanen

Laboratory of Pervasive Computing

Faculty of Computing and Electrical Engineering

Tampere University of Technology

Finland

Supervisor: Jarmo Takala, Prof.

Laboratory of Pervasive Computing

Faculty of Computing and Electrical Engineering

Tampere University of Technology

Finland

Instructor: Pekka Jääskeläinen, D.Sc. (Tech.)

Laboratory of Pervasive Computing

Faculty of Computing and Electrical Engineering

Tampere University of Technology

Finland

Pre-examiners: Gwo-Giun Lee, Prof.

Department of Electrical Engineering National Cheng Kung University

Taiwan

Timo Aila, D.Sc. (Tech.)

NVIDIA Finland

Opponent: Samuli Laine, D.Sc. (Tech.)

NVIDIA Finland

### **Abstract**

Future graphics processors are likely to incorporate hardware accelerators for real-time ray tracing, in order to render increasingly complex lighting effects in interactive applications. However, ray tracing poses difficulties when drawing scenes with dynamic content, such as animated characters and objects. In dynamic scenes, the spatial datastructures used to accelerate ray tracing are invalidated on each animation frame, and need to be rapidly updated. Tree update is a complex subtask in its own right, and becomes highly expensive in complex scenes. Both ray tracing and tree update are highly memory-intensive tasks, and rendering systems are increasingly bandwidth-limited, so research on accelerator hardware has focused on architectural techniques to optimize away off-chip memory traffic. Dynamic scene support is further complicated by the recent introduction of compressed trees, which use low-precision numbers for storage and computation. Such compression reduces both the arithmetic and memory bandwidth cost of ray tracing, but adds to the complexity of tree update.

This thesis proposes methods to cope with dynamic scenes in hardware-accelerated ray tracing, with focus on reducing traffic to external memory. Firstly, a hardware architecture is designed for linear bounding volume hierarchy construction, an algorithm which is a basic building block in most state-of-the-art software tree builders. The algorithm is rearranged into a streaming form which reduces traffic to one-third of software implementations of the same algorithm. Secondly, an algorithm is proposed for compressing bounding volume hierarchies in a streaming manner as they are output from a hardware builder, instead of performing compression as a postprocessing pass. As a result, with the proposed method, compression reduces the overall cost of tree update rather than increasing it. The last main contribution of this thesis is an evaluation of shallow bounding volume hierarchies, common in software ray tracing, for use in hardware pipelines. These are found to be more energy-efficient than binary hierarchies. The results in this thesis both confirm that dynamic scene support may become a bottleneck in real time ray tracing, and add to the state of the art on tree update in terms of energy-efficiency, as well as the complexity of scenes that can be handled in real time on resource-constrained platforms.

## Preface

The work described in this Thesis took place over 2013-2018 in the Department of Pervasive Computing, Tampere University of Technology, Finland, and in part during my research visit to the DSPCAD group, University of Maryland, USA.

I am thankful to Prof. Jarmo Takala for the opportunity to pursue this research, and all his guidance and support. The guidance of Dr. Pekka Jääskeläinen was also invaluable: he encouraged me in taking up this intriguing and complex research topic, and seeing the work through despite a variety of distractions. Moreover, I am grateful for my thesis pre-examiners Dr. Timo Aila and Prof. Gwo-Giun Lee for their valuable comments. Prof. Shuvra Bhattacharyya has my special thanks for arranging an opportunity to visit his research group in Maryland.

It has been a joy to work with the many friends and colleagues in Jarmo's research group. I would like to thank, in particular, my closest collaborators in this work, *Matias Koskela*, M.Sc., *Heikki Kultala*, M.Sc. and *Kalle Immonen*, M.Sc., for their helpful assistance, insightful comments, and many fruitful discussions. Many others in the group also helped in this work and contributed to a lively, creative atmosphere. In addition, I would like to express special thanks to Prof. Bhattacharyya's research group at Maryland and in particular *Lin Li*, B.Sc., and *Kyunqhun Lee*, B.Sc.

I gratefully acknowledge the financial support that allowed me to work on this interesting topic. In the past four years, I have received support from the *TUT Graduate School*, the *EU commission* via the ARTEMIS joint undertaking ALMARVI, the *National Technology Agency of Finland (TEKES)*, and the *Nokia Foundation*.

Finally, I am thankful to my parents *Ulla* and *Oiva*, and siblings *Tuula* and *Tapio* for their constant support.

# Contents

| Al       | ostra | $\mathbf{ct}$ |                                  | iii  |

|----------|-------|---------------|----------------------------------|------|

| Pr       | eface | e             |                                  | v    |

| Ac       | crony | ms            |                                  | ix   |

| No       | omen  | clatur        | e                                | xi   |

| Lis      | st of | Public        | cations                          | xiii |

| 1        | Intr  | oducti        | on                               | 1    |

|          | 1.1   | Scope         | and Objectives of Research       | 4    |

|          | 1.2   |               | Contributions                    |      |

|          | 1.3   |               | r's Contribution                 |      |

|          | 1.4   |               | Outline                          |      |

| <b>2</b> | Stre  | aming         | Linear BVH Construction          | 7    |

|          | 2.1   | _             | Construction Methods             | 8    |

|          |       | 2.1.1         | Linear BVH                       |      |

|          |       | 2.1.2         | Refinement Based Construction    |      |

|          |       | 2.1.3         | Spatial Splits                   |      |

|          |       | 2.1.4         | Other Build Algorithms           |      |

|          |       | 2.1.5         | Refitting                        |      |

|          |       | 2.1.6         | Summary                          | 15   |

|          | 2.2   | Hardw         | vare Accelerated Construction    | 15   |

|          |       | 2.2.1         | Binned SAH Acceleration          |      |

|          |       | 2.2.2         | Refit Acceleration               | 16   |

|          |       | 2.2.3         | k-Dimensional Tree Accelerators  | 17   |

|          |       | 2.2.4         | Imagination Technologies Builder |      |

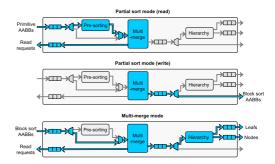

|          | 2.3   | Sorting       | g Hardware                       | 18   |

|          | 2.4   | Thesis        | Contribution                     | 19   |

| 3        | Reb   | uilding       | g and Refitting Compressed BVHs  | 23   |

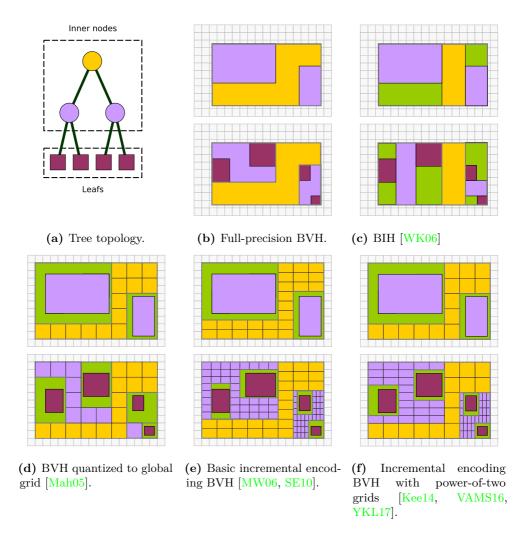

|          | 3.1   | BVH (         | Compression Methods              | 24   |

|          |       | 3.1.1         | Coordinate Compression           | 24   |

|          |       | 3.1.2         | Pointer Compression              | 26   |

|          |       | 3.1.3         | Primitive Compression            | 27   |

|          |       | 3.1.4         | Entropy Coding                   | 29   |

|          |       | 3.1.5         | Comparison                       | 29   |

<u>vi</u> \_\_\_\_\_ Contents

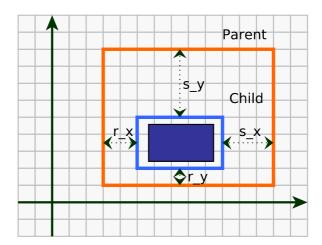

|    | 3.2    | Incremental Encoding              | 30 |

|----|--------|-----------------------------------|----|

|    | 3.3    | Thesis Contribution               | 32 |

| 4  | Har    | dware-Accelerated Shallow BVHs    | 33 |

|    | 4.1    | Traversal Architectures           | 34 |

|    |        | 4.1.1 Programmable Platforms      |    |

|    |        | 4.1.2 Fixed-Function Accelerators |    |

|    |        | 4.1.3 Memory Access Schemes       |    |

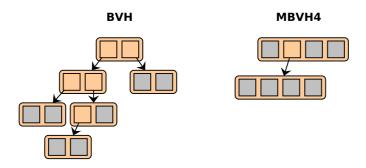

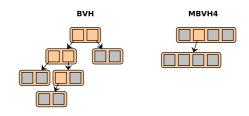

|    | 4.2    | Multi-Bounding Volume Hierarchies |    |

|    |        | 4.2.1 Construction                |    |

|    |        | 4.2.2 Traversal                   |    |

|    | 4.3    | Thesis Contribution               | 40 |

| 5  | Con    | clusion                           | 43 |

|    | 5.1    | Main Results                      | 44 |

|    | 5.2    | Open Research Issues              | 45 |

| Bi | bliog  | graphy                            | 47 |

| Ρι | ıblica | ations                            | 59 |

# Acronyms

**AABB** Axis Aligned Bounding Box

**AAC** Approximate Agglomerative Construction

AR Augmented Reality

**ASIC** Application Specific Integrated Circuit

ATRBVH Agglomerative Treelet Restructuring Bounding Volume Hierarchy

AVX Advanced Vector Extensions

**B-KD tree** Bounded k-dimensional tree

**BIH** Bounding Interval Hierarchy

BRAM Block Random Access Memory

**BSAHA** Binned SAH Accelerator

**BSP** Binary Space Partition

**BVH** Bounding Volume Hierarchy

CAD Computer Aided Design

**CBVH** Compressed Bounding Volume Hierarchy

CMBVH Compressed Multi Bounding Volume Hierarchy

**CPU** Central Processing Unit

**DE-tree** Dual Extent tree

**DRAM** Dynamic Random Access Memory

FIFO First In First Out

FoV Field of View

FPGA Field Programmable Gate Array

FPU Floating Point Unit

GTU Geometry and Tree Update unit

**HMQ** Hierarchical Mesh Quantization

viii Acronyms

IOSP Implicit Object Space Partition

**GPGPU** General-Purpose Graphics Processing Unit

**GPU** Graphics Processing Unit

**HCCMesh** Hierarchical Culling oriented Compact Mesh

**HLBVH** Hierarchical Linear Bounding Volume Hierarchy

k-d tree k-dimensional tree

LBVH Linear Bounding Volume Hierarchy

LFD Light Field Display

**LoD** Level of Detail

MBVH Multi Bounding Volume Hierarchy

MIC Many Integrated Cores

MIMD Multiple Instruction Multiple Data

MVH Minimal Bounding Volume Hierarchy

NURBS Non Uniform Rational Basis Spline

**QBVH** Quad Bounding Volume Hierarchy

RACBVH Random Accessible Compressed Bounding Volume Hierarchy

RAU Ray Accumulation Unit

RBVH Rasterized Bounding Volume Hierarchy

RTL Register Transfer Level

**SAH** Surface Area Heuristic

**SBVH** Split Bounding Volume Hierarchy

SIMD Single Instruction Multiple Data

**SIMT** Single Instruction Multiple Thread

**sk-d tree** Spatial K-Dimensional tree

SMT Simultaneous Multi-Threading

**SPBVH** Shared Plane Bounding Volume Hierarchy

SRAM Static Random Access Memory

SSE Streaming SIMD Extensions

TBU Tree Build Unit

TRBVH Treelet Restructuring Bounding Volume Hierarchy

VR Virtual Reality

# Nomenclature

#### Ray traversal (Chapter 2):

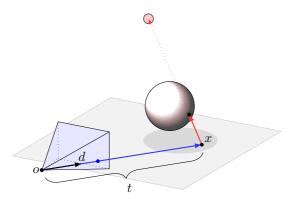

x Ray-scene intersection point

$egin{array}{ll} o & & {

m Ray\ origin} \\ d & & {

m Ray\ direction} \end{array}$

t Parametric distance to intersection, x = o + dt

#### Surface Area Heuristic (Section 2.2.1):

$\begin{array}{ll} C & \text{Surface Area Heuristic cost of a BVH tree} \\ C_{node} & \text{Heuristic cost of traversing an inner node} \end{array}$

$C_{leaf}$  Heuristic cost of traversing a leaf

$C_{tri}$  Heuristic cost of a primitive intersection test

$A(N_i)$  Surface area of inner node i $A(L_i)$  Surface area of leaf node i

A(R) Surface area of tree bounding box

$n_{nodes}$  Number of nodes in tree  $n_{leafs}$  Number of leafs in tree

#### Binned SAH construction (Section 2.2.1):

S Number of candidate splits per axis in binned SAH construction

#### External mergesort (Section 2.3):

N Sort input size

M Size of fast local memory

B Minimum block size for transfers between local and external memory

k Multi-merge width

#### Heap layout (Section 3.1.2):

i Element index

K Tree branching factor

#### Triangle strips (Section 3.1.3):

X Nomenclature

$v_i$  ith vertex of a triangle strip n Number of vertices in a strip.

#### Incremental encoding (Section 3.2):

$\begin{array}{ll} b & \text{Number of bits used to store an AABB coordinate} \\ r_x, r_y, r_z & \text{Lower bound offsets relative to parent AABB} \\ s_x, s_y, s_z & \text{Upper bound offsets relative to parent AABB} \end{array}$

## List of Publications

This Thesis consists of an introductory part and four original publications. In the text, these publications are referred to as [P1] through [P4].

- [P1] VIITANEN T., KOSKELA M., JÄÄSKELÄINEN P., KULTALA H., TAKALA J.: MergeTree: a HLBVH constructor for mobile systems. In SIGGRAPH Asia Technical Briefs (2015), p. 12.

- [P2] VIITANEN T., KOSKELA M., JÄÄSKELÄINEN P., KULTALA H., TAKALA J.: MergeTree: A Fast Hardware HLBVH Constructor for Animated Ray Tracing. *ACM Transactions on Graphics* 36, 5 (2017), 169.

- [P3] VIITANEN T., KOSKELA M., JÄÄSKELÄINEN P., IMMONEN K., TAKALA J.: Fast Hardware Construction and Refitting of Quantized Bounding Volume Hierarchies. *Computer Graphics Forum 36*, 4 (2017), 167–178.

- [P4] VIITANEN T., KOSKELA M., JÄÄSKELÄINEN P., TAKALA J.: Multi Bounding Volume Hierarchies for Ray Tracing Pipelines. In SIGGRAPH Asia Technical Briefs (2016), p. 8.

# 1 Introduction

Ray tracing is the future and ever will be.

-- David Kirk

Computer-generated images are ubiquitous in modern society and form a main component of human-computer interaction. Moreover, computer graphics are applied to entertainment, e.g., video games and motion pictures, at a grand scale. As a result, great effort has gone to optimizing rendering performance, allowing increasingly smooth and high-quality visuals in real-time applications, and offline rendering almost indistinguishable from photographs. Recently, rendering systems are further challenged by emerging consumer-grade Virtual Reality (VR) and Augmented Reality (AR), which require images to be drawn at very high resolutions and frame rates for an immersive experience. Moreover, a large amount of rendering is done in mobile devices, which have tight energy constraints. The combination of mobile AR in particular is predicted to open applications of high societal impact in, e.g., industry, medicine, entertainment and education [vKP10]. Since rendering for mobile AR combines the tight energy budgets of mobile platforms with the performance requirements of high-quality VR, it may require novel architectural approaches.

Most real-time and interactive rendering is performed by means of rasterization and the z-buffer algorithm, accelerated by Graphics Processing Units (GPUs). Given a 3D scene made up of geometric primitives — usually triangles — and a camera point, the rasterization approach performs geometric transforms to project each primitive to a screen coordinate frame, and then shades all pixels of the resulting 2D primitive to decide their color. The z-buffer algorithm [Cat74] is used to handle occlusions between primitives. In the first GPUs, shading was performed with a fixed-function pipeline with a limited selection of operating modes, but is now fully programmable. As a result, the GPUs of today are massively parallel general-purpose computation engines used to accelerate many applications beyond graphics.

A long-standing goal in computer graphics research is to replace or augment rasterization in real-time rendering with ray tracing, an alternative approach where it conceptually easier to model many lighting effects realistically. A basic operation in ray tracing is ray traversal, i.e., determining the closest hit point between a ray and a 3D scene. At its simplest, this operation is used to traverse primary rays for each pixel starting from the camera origin. Various visual effects can then be modeled by traversing secondary rays that start with the intersection point. For example, reflections are handled by casting a reflection ray which is a mirror image of the primary ray, or shadows are drawn by casting shadow rays at light sources to test whether they are occluded.

Figure 1.1: Example of a path traced image with shadows, glossy materials and indirect illumination. Scene by Jay-Artist, CC BY 3.0.

Other effects can be rendered by casting a set of rays drawn from a random distribution: doing this with, e.g., primary, reflection and shadow rays gives focal blur, glossy reflections and soft shadows, respectively [CPC84]. Photorealistic images can be generated with path tracing [Kaj86] which emulates the physical behavior of light by integrating over many secondary rays which act as pseudo-photons, rebounding in the scene at random until they reach a light source. An image rendered this way is at first noisy, but eventually converges to a physically correct distribution. Path tracing is the gold standard of photorealistic rendering and used to render, e.g., the animated motion pictures of Disney and Pixar [KFF\*15]. Figure 1.1 shows an example of a path traced scene.

A ray tracing system uses ray traversal and two other primitive operations, tree build and shading, as building blocks for higher-level rendering algorithms. Briefly, tree builds are used to adapt the acceleration data structure used in ray traversal to changes in the scene between animation frames, while shader programs model material appearance. Over the past decade, the performance of all three operations has improved sharply by taking advantage of the growing capabilities of GPU and multicore Central Processing Unit (CPU) hardware. Moreover, an extensive literature has developed optimizing ray tracing at the algorithm level, e.g., by carefully selecting the traversed rays with adaptive sampling, and filtering away the noise caused by low sample counts [ZJL\*15]. As a result, current ray tracers are capable of rendering some effects in real time.

A classic motivation for ray tracing has been the above conceptual simplicity of generating visual effects that require complex workarounds in rasterization-based systems. In addition, some works on ray tracing are motivated by its logarithmic scaling with regards to the number of primitives: with sufficiently large scenes, it may outperform rasterization, which has linear complexity [SKBD12]. However, in practice, the complexity of rasterization can be kept in check with visibility determination algorithms [COCSD03]. Rather than displacing rasterization completely, real-time ray tracing is more likely to be used as part of a hybrid system which combines both techniques [PBMH02]. Several applications have been proposed for video games [FGD\*06, Bik07].

The recent push for commercial VR and AR seems to strengthen the case for ray tracing. In VR headsets, a rasterization pipeline needs to first draw a planar image and then resample it to compensate for lens distortion. Moreover, the work done to render virtual

scenes can be sharply reduced by using fewer samples in the peripheral vision, based on head or gaze tracking. In ray tracing it is convenient to build lens distortion into ray generation [PJB13], and to sample the area of accurate vision more densely [WRK\*16].

There is recent interest in near-eye Light Field Displays (LFDs) for VR which can control the direction of the emitted light, allowing the construction of lightweight headsets with a wide Field of View (FoV), and side benefits such as the use of focal depth 3D cues [LL13]. LFD images have to be rendered from many views, which is advantageous for ray tracing. Finally, in AR, it is interesting to create virtual objects which blend seamlessly into the surroundings. To this end, the renderer needs estimates of the shape, materials and illumination of the surrounding scene. Several state-of-the-art methods to produce these estimates make heavy use of ray tracing [RTKPS16, KPR\*15].

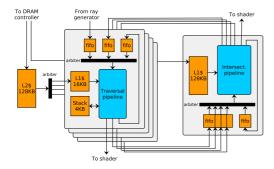

Recently, there has been growing academic and industrial interest in hardware ray tracers, including a product launch by the major mobile GPU vendor Imagination Technologies [Pow15]. Ray tracing architectures have been proposed ranging from fixed-function hardware pipelines [WSS05, NPP\*11, LSL\*13], to exotic programmable Multiple Instruction Multiple Data (MIMD) processors [SKKB09, KSS\*15], to hybrid architectures integrating ray tracing functionality to conventional GPUs [Kee14]. These architectures form a trade-off curve between performance and flexibility. At one end of the curve, fixed-function accelerators can be said to have the most short-term interest, since they are likely to reach a greater performance in a given energy and silicon area budget, and thus become practical sooner than programmable systems. In some cases, fixed-function pipelines are 2-3 orders of magnitude more efficient than a general-purpose processors [HQW\*10], though the available benefits are more limited in a memory-intensive, floating-point heavy application such as ray tracing.

Possibly the strongest motivation for hardware ray tracing is that it may render some complex visual effects at a lower energy cost than multi-pass rasterization based methods [KKW\*13]. Today's rendering systems are increasingly limited by the thermal design power and memory bandwidth of the GPU. Previously, the graphics community might have relied on transistor scaling to provide steadily improving performance in a given power budget. However, due to the recent breakdown of Dennardian CMOS scaling, the energy efficiency gains from scaling have diminished, and attention in circuit design is turning to hardware specialization to take advantage of increasing transistor counts [Tay12]. Mobile devices operate under far more stringent power constraints and, as a result, the potential efficiency benefits of ray tracing have spurred the development of several mobile ray tracing accelerators, which have been proposed as enablers of photorealistic mobile AR and VR [KKK12, NKK\*14, LSL\*13].

Recent work on ray tracing accelerators has provided promising insights into the rendering process which may allow order-of-magnitude reductions in its computational cost: namely, that the cost of hardware ray tracing is dominated by memory accesses, which can be reduced to a small fraction by rearranging the access pattern [AK10, KSS\*15] and compressing the acceleration data structure [Kee14]. Hardware ray tracers are able to reach very high simulated ray traversal throughputs, e.g., giving performances close to a desktop General-Purpose Graphics Processing Unit (GPGPU) in a mobile envelope [LSL\*13], or orders of magnitude higher performances in a desktop envelope [Kee14].

Aside from ray traversal, a main component of the ray tracing problem is *tree update*, i.e., supplying the traversal process with a data structure which indexes the scene geometry and accelerates ray traversal. In photorealistic offline rendering, or when visualizing static scenes, the runtime of tree update is of no consequence, and the main consideration is

to produce trees with high tree quality which are cheap to traverse. However, when ray tracing animated scenes in real time, tree update must be done before each animation frame – e.g. at 90Hz for recent VR headsets – and doing this fast enough while retaining a reasonable tree quality is a challenging sub-problem. Most applications of interest have animated geometry, e.g., in computer games it is commonplace to display complex particle effects or crowds of detailed characters moving based on *skeletal animation*. Ray tracing accelerators proposed and demonstrated so far have been mostly limited to static or mostly static scenes, ruling out these applications.

#### 1.1 Scope and Objectives of Research

The general subject of this Thesis is to explore techniques for hardware-accelerated ray tracing, and especially the real-time ray tracing of large-scale animated scenes.

A complete ray tracing rendering system combines the low-level tools of tree update, ray traversal and shading to generate various visual effects. This Thesis is limited to implementations of tree update and traversal, ruling out shading and system-level optimizations. It should be noted that shading can rival traversal and construction in terms of computational cost [LKA13], and there is a large literature of high-level optimizations such as denoising [ZJL\*15] to reduce the amount of ray traversal operations needed to generate a high-quality image.

Previous work on ray tracing accelerators can be divided into programmable and fixed-function systems. Since fixed-function accelerators are often significantly more efficient than programmable systems, they are more likely to be of practical interest in the short term, and this Thesis focuses on them.

The focus on animated scenes places emphasis on the sub-problem of tree update, i.e., refitting or reconstructing the acceleration data structure. As the data structure of choice, we focus on Bounding Volume Hierarchy (BVH) and certain variants. BVH is presently popular since other structures are impractical to update. Real time BVH update on desktop CPUs and GPGPUs has been the subject of intensive study, and can be regarded as a solved problem. Hence, the work in this Thesis focuses on two open cases.

Firstly, fast tree updates consume a large amount of memory bandwidth, which is then unavailable for rendering and shading. Bandwidth is especially limited in mobile systems, but savings would also be useful on the desktop. Secondly, *compressed trees* are efficient to traverse, but updating them remains an open problem. These points lead to the two main research questions which Thesis answers:

- Can high-performance GPGPU tree construction algorithms be efficiently adapted into a bandwidth economical, hardware-accelerated context?

- Is it possible to reach real-time update rates for Compressed Bounding Volume Hierarchies (CBVHs)?

The objective of this research is to develop effective methods for tree construction and compressed tree update in bandwidth-limited systems.

#### 1.2 Main Contributions

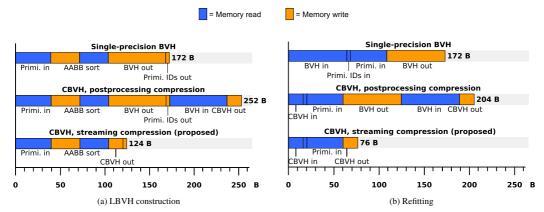

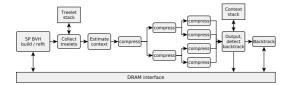

This Thesis proposes techniques to support animated scenes in hardware-accelerated ray tracing, with a focus on energy- and memory-constrained systems such as mobile phones. In [P1,P2], a hardware architecture is proposed for the Linear Bounding Volume Hierarchy (LBVH) tree construction algorithm, which forms the basis for the state-of-the-art high performance GPU tree builders. In order to improve memory bandwidth economy, LBVH is expressed as streaming processes, and an external sorting algorithm is used. The architecture is evaluated extensively with Register Transfer Level (RTL) implementation, power analysis and system-level simulations.

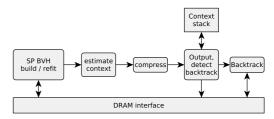

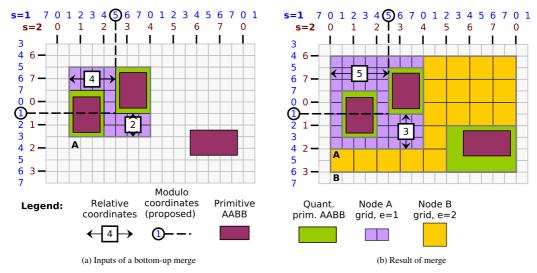

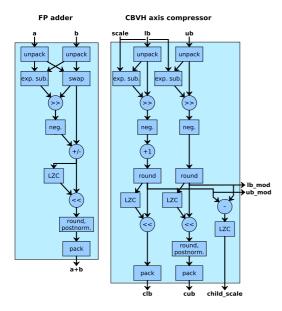

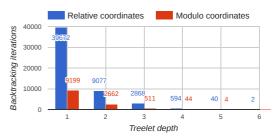

Article [P3] introduces algorithmic techniques for streaming bottom-up compression of BVHs, aimed for a possible hardware implementation. The benefit is that tree update processes can directly output compressed trees, in the best case halving memory traffic. As CBVH nodes are encoded relative to the parent [VAMS16, Kee14], this requires estimating the parent context of each node, and backtracking to repair the hierarchy when the estimated context is wrong. Novel techniques of modulo encoding and treelet-based compression are proposed to minimize backtracking.

The main drawback of [P3] is that state-of-the-art CBVHs based on *plane sharing* [VAMS16] cannot be compressed. In [P4], we make an initial step toward addressing this shortcoming by showing that Multi Bounding Volume Hierarchies (MBVHs) could be used to save memory traffic in the place of plane sharing.

In summary, the main novel contributions in this Thesis are the following:

- a bandwidth-conserving hardware architecture for LBVH tree construction, which trades off tree quality for major runtime, energy and chip area savings compared to the state-of-the-art hardware builder,

- algorithmic techniques for streaming bottom-up update of CBVHs, which reduce the memory traffic cost of CBVH update by up to half, and

- an evaluation of hardware ray tracing with MBVHs.

#### 1.3 Author's Contribution

This Thesis includes four publications [P1-P4]. [P1] proposes a hardware LBVH build unit. The author invented the key techniques of the architecture of hardware heap based external sorting and streaming hierarchy emission, designed the architecture, wrote a cycle-level simulator, and performed the measurements and analysis of results.

[P2] extends [P1] with a complete hardware implementation and system-level modeling results. The Thesis Author implemented the hardware unit, performed ASIC synthesis and power analysis, modified the cycle-level simulator designed in [P4] for use in system-level energy modeling, and performed the additional measurements and analysis.

[P3] proposes algorithms for streaming bottom-up CBVH compression. The Thesis Author designed the algorithms, extended a software ray tracer with the proposed methods, and performed measurements and analysis.

[P4] proposes the use of MBVHs in hardware ray tracing. For this work, the Thesis Author designed a MBVH traversal unit architecture, wrote a software ray tracer and cycle-level hardware simulator, and performed the measurements and analysis of results.

The Thesis Author was the main author and wrote the main body of text for each publication.

#### 1.4 Thesis Outline

This Thesis consists of five previous publications and an introductory part. Chapter 2 briefly introduces some basic concepts in ray tracing. Chapters 2-4 expand on the relation of the Thesis main contributions to the state of the art. Chapter 2 focuses on the LBVH accelerator architecture proposed in [P1,P2], Chapter 3 on the streaming CBVH update algorithm proposed in [P3], and Chapter 4 on the application of MBVH to ray traversal accelerators proposed in [P4]. Finally, Chapter 5 discusses the main results, proposes future work and concludes the introductory part. The publications [P1-P4] then follow.

# 2 Streaming Linear BVH Construction

Ray tracing renders images of 3D scenes specified as lists of geometric primitives, most often triangles. The basic operation in ray tracing,  $ray\ traversal$ , can be defined as follows: given a 3D scene, a ray origin o, and ray direction d, find the intersection x between the ray and the scene,

$$x = o + dt, (2.1)$$

which has the shortest parametric distance t from the origin. Figure 2.1 shows an example of ray traversal.

A straightforward way to compute ray traversal is to loop over all geometric primitives, compute intersection tests between the ray and each primitive, and select the intersection with lowest t. However, brute-force traversal quickly is infeasible for nontrivial scenes. Fast ray tracing is based on organizing the primitives with an acceleration data structure optimized for ray traversal. There is a large body of research on such data structures, the main classes being k-dimensional trees (k-d trees), grids, and BVHs. A good, though now somewhat dated overview is given by the state of the art survey of Wald et al. [WMG\*09].

Recently, research has converged on the BVH as the data structure of choice, as it both gives good rendering performance and is easy to construct and update [WMG\*09]. The focus of this Thesis is on BVHs and certain variants optimized for hardware acceleration. In a BVH, each node subdivides primitives into two disjoint sets, whose bounding volumes are stored. If a traced ray does not intersect a bounding volume, all primitives underneath can be discarded, resulting in logarithmic typical-case complexity for ray traversal. The bounding volumes are nearly always Axis Aligned Bounding Boxs (AABBs) in ray tracing, though more complex volumes have been used in collision detection [LMK17].

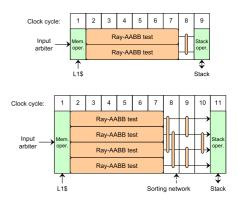

Ray traversal in a BVH is typically done in depth-first, stack-based manner. Traversal begins by pushing the root node onto a traversal stack. Nodes are then repeatedly popped from the stack and visited. When visiting an inner node, the ray is tested against the child AABBs of the node, and intersecting children are pushed to the stack. Visits to leaf nodes cause ray-triangle tests. Important optimizations in traversal are to push children so that they are visited in a closest-first order, and to perform depth culling, i.e., skip traversal of nodes that are farther than the closest intersection found so far. Ray traversal performed this way typically requires a number of node visits and intersection tests that is roughly logarithmic with regard to the scene size.

The main alternatives to BVHs, grids and k-d trees, can be characterized as *spatial split* data structures: they divide the scene's 3D space into subvolumes, and each primitive is referenced from all leaf volumes -k-d tree leafs or gridcells - which overlap that

Figure 2.1: Example of ray traversal. o: ray origin, d: ray direction, t: parametric distance, x: intersection point. Red: secondary (shadow) ray.

primitive. BVHs, meanwhile, are *object split* structures where each primitive is referenced once, and the nodes may refer to overlapping volumes. An in-depth comparison of BVH and k-d tree ray traversal is given by Vinkler et al. [VHB14]. In general, BVHs require more floating-point computations, while k-d trees are more memory-intensive.

Methods to build or update BVHs have been a subject of extensive study. If a BVH is built once and used for a large amount of rendering work, the main characteristic of interest when choosing the update method is *tree quality*, i.e., how good is the rendering performance given by the resulting tree. In animated, and especially real time rendering, build speed becomes a relevant consideration. The last few years have seen significant advances in GPGPU build algorithms which exhibit both real-time performance and good quality compared to older gold-standard algorithms. A main contribution of this Thesis is a streaming, hardware-oriented build algorithm, which is a step toward bringing these advances to mobile systems.

It should be noted that practical rendering systems often add a higher level of organization atop the BVH or k-d tree, similar to scene graph libraries in conventional rendering. One such organization is described by Wald et al. [WBS03], where the scene is divided into objects, which are organized in a top-level acceleration tree. Objects are then handled depending on their type of animation. Completely static objects can use a pre-built high-quality tree. Rigid-body motions are handled by translating and rotating incoming rays before traversing the object tree. Finally, objects with unstructured animation require full rebuilds on each frame.

This chapter surveys the state of the art related to the contributions of this Thesis on hardware BVH construction. First, we introduce basic methods used to evaluate the quality of BVHs, followed by a description of state-of-the-art fast BVH construction algorithms. Next, previous hardware builders are reviewed. Since the algorithm proposed in the Thesis work makes heavy use of sorting, we also discuss sorting accelerator architectures. Finally, the relation of the Thesis work to the state of the art is summarized.

#### 2.1 BVH Construction Methods

Acceleration data structures can be said to have different levels of *quality* depending on how they are constructed. With a high-quality tree, ray traversal requires fewer intersection tests and traversal steps, and consequently, images are rendered faster. A

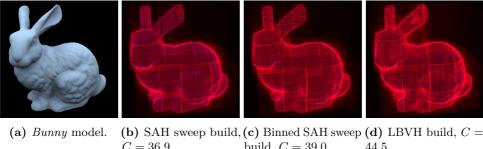

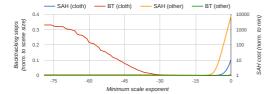

C = 36.9.build, C = 39.0.

Figure 2.2: Example of the effect of tree quality on traversal cost, ranging from a slow, highquality build method (SAH sweep) to a fast, low-quality build method (LBVH). Cost is measured with primary ray tracing. Red color component denotes the number of inner node visits per pixel, blue denotes the number of ray-triangle tests.

standard way to evaluate the quality of a BVH tree is its Surface Area Heuristic (SAH) cost, introduced by Goldsmith and Salmon [GS87] and adapted to BVHs by Macdonald and Booth [MB90]. The SAH cost of a data structure is the expected cost to traverse a random non-terminating ray through the scene. For a BVH, the heuristic cost C can be computed as:

$$C = C_{node} \sum_{i=0}^{n_{\text{nodes}}} \frac{A(N_i)}{A(R)} + C_{leaf} \sum_{i=0}^{n_{\text{leafs}}} \frac{A(L_i)}{A(R)} + C_{tri} \sum_{i=0}^{n_{\text{leafs}}} \frac{P_i A(L_i)}{A(R)},$$

where  $A(N_i)$  and  $A(L_i)$  are the surface areas of the given inner nodes and leafs, respectively, A(R) is the surface area of the scene AABB,  $P_i$  is the primitive count within a given leaf,  $C_{node}$  is the cost of traversing an inner node,  $C_{leaf}$  the cost of traversing a leaf, and  $C_{tri}$ the cost of a primitive intersection test [KA13].

In addition to measuring tree quality, SAH is widely used as a basis for tree build algorithms. The most well-known such algorithm is the SAH sweep [MB90] which builds BVHs by recursively partitioning the set of primitives top-down. At each step, SAH sweep attempts to split the remaining primitives into two subsets along all possible axis-aligned planes. The split plane giving the lowest SAH cost is selected and used to generate an inner node, the algorithm proceeds recursively into the two children, and recursion terminates when there is no split available which would improve the SAH. This algorithm is generally used as a gold standard against which other builders are benchmarked. Builders are often evaluated based on their resulting SAH cost normalized to a tree constructed with SAH sweep. A less expensive variant is the binned SAH sweep [Wal07], which considers only, e.g., 8 or 16 candidate split planes per axis, trading off quality for build speed.

Figure 2.2 shows an example with trees of different quality, and the resulting measured traversal cost in node visits and intersection tests. It is visible that cost is unevenly distributed over the image, and mostly concentrated on edges of objects, where rays may pass closely by many triangles without hitting them. In practice, traversal performance is also highly viewpoint-dependent.

It has been shown [AKL13] that SAH is an imperfect quality measure since, in practice, rays tend to begin and terminate inside the scene. The heuristic can be improved by introducing a term for AABB overlap. In practice, SAH-based top-down construction

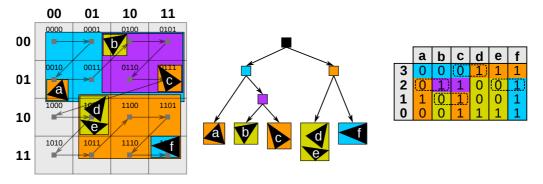

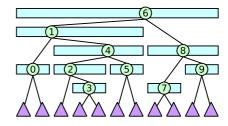

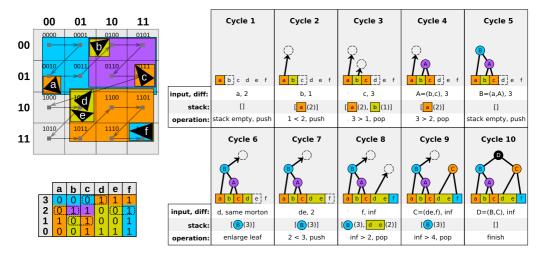

Figure 2.3: Example of LBVH. Left: locations of primitives in space, overlaid with a Morton code grid. Right: Morton codes of each bit. Center: generated hierarchy.

tends to also give good overlap, but some more complex build algorithms may further optimize SAH cost without giving a corresponding traversal performance benefit.

#### 2.1.1 Linear BVH

Most of the recent fast GPGPU BVH builders aimed at real-time operation are based on the LBVH algorithm by Lauterbach [LGS\*09], which organizes triangles by placing them on a space-filling curve. LBVH construction has roughly linear complexity in terms of arithmetic operations and memory accesses with respect to scene primitive count, compared to  $\mathcal{O}(n \log n)$  for top-down SAH builds.

LBVH can be divided into four main stages:

- In Morton code computation, a regular  $2^k \times 2^k \times 2^k$  grid is fitted in the scene AABB. All primitives are then assigned a Morton code by quantizing their AABB centroids to the grid and interleaving the bits of the grid coordinates. Typically, k = 10 (for 30-bit codes), or k = 21 (63-bit codes).

- Next, the primitives are sorted into Morton code order with a GPU-accelerated sorting algorithm such as a parallel prefix radix sort.

- In hierarchy emission, the bits of sorted Morton codes are used to generate the topology of the final BVH tree, i.e., generate child pointers for each node. In some implementations, primitives with identical Morton codes are grouped into the same leaf [LGS\*09], while in others, an arbitrary hierarchy is generated so that there is one primitive per leaf [Kar12].

- Finally, AABB computation converts the BVH topology into a final BVH by computing node AABBs, in a step similar to BVH refitting.

LBVH is illustrated in Figure 2.3. Primitives are assigned Morton codes by binning to a coarse grid (left). The hierarchy (center) is generated based on bit patterns in sorted codes (right). For example, here the most significant bit corresponds to a halfway split of the scene along the vertical axis: primitives with a '0' bit are in the upper half of the scene volume, and primitives with '1' in the lower half. The root node splits primitives into subsets based on this bit. The subsets are recursively subdivided according to lower Morton code bits to form the rest of the hierarchy.

The original LBVH of Lauterbach already gave order-of-magnitude faster builds than previous algorithms, but has later been extensively optimized. Out of the above stages, Morton code computation is cheap and trivially parallel, and GPU sorting is a well studied general problem. Hence, most attention has gone to improving hierarchy emission and AABB computation.

The main insight enabling parallel hierarchy emission is that each LBVH node corresponds to a continuous range of primitives with an identical Morton code prefix, i.e., the resulting topology is a binary prefix tree. For example, in Figure 2.3, the children of the root node have prefixes of 0 and 1. Moreover, a node can be considered to have a hierarchy level l, such that a node with low level has a longer prefix, and a split position, which is the primitive array index separating its child ranges. By comparing the Morton codes of successive sorted primitives, it is possible to determine whether that boundary is a node split, and determine the hierarchy level of that split. Lauterbach's method generates a per-primitive split list, and then sorts the splits by their level and their primitive range upper bound, resulting in a memory layout where it is easy to find parent-child relationships between nodes.

To understand the GPU implementation of the above algorithm, and later improvements, we need to examine the concept of parallel prefix sum, or scan [HSO07]. Scans are used in GPGPU computing to perform operations where each parallel thread of execution produces a dynamic amount of output data, which should be stored continuously. To parallelize such a problem, it is broken into multiple passes. The initial pass computes the amount of output for each work item n,  $o_n$ . An intermediate pass computes, for each item, a prefix sum of the output sizes of all earlier items:  $p_n = o_1 + o_2 + ... + o_n - 1$ . A final pass performs the computation, and places the outputs at memory locations  $p_n ... p_n + o_n - 1$ . A common application is the parallel prefix radix sort, which parallelizes the binning stages in radix sorting. Parallel prefix sums allow highly parallel computation of some problems at the cost of extra computation.

Lauterbach's LBVH first performs scans to generate the split list; then further scans for each hierarchy level to determine the memory locations of nodes. A drawback of the method is that scans are performed on intermediate data arrays much larger than n, and hierarchy emission generates many singletons, or nodes with only one child. Singletons are later removed with a postprocessing pass, but the leftover nodes are fragmented in memory, and construction requires a large memory arena. The later Hierarchical Linear Bounding Volume Hierarchy (HLBVH) of Pantoleoni and Luebke [PL10] addresses these drawbacks: it only emits full nodes and, furthermore, the number of kernel executions is reduced by processing p hierarchy levels at a time (p=3 in the paper [PL10]). Each level set takes as inputs the leafs of the previous launch, which are further refined into treelets of up to  $p^2-1$  nodes. For each level set, a single kernel launch first generates an array of treelet  $block\ descriptors$ , after which a scan is used to emit the corresponding hierarchy.

Garanzha et al. [GPM11] also perform hierarchy emission top-down, but do this in a single kernel call by means of the *task queue* mechanism in CUDA. Each task in the queue encodes the primitive range covered by an inner node. For each input range, the algorithm compares the first and last Morton codes in the range; determines the highest differing bit; and uses a binary search to find the corresponding split position. The resulting child ranges on each side of the split are then fed into the task queue. Initially, the kernel is fed a single task corresponding to the root node, which encompasses all primitives, and the algorithm then proceeds top-down.

Karras [Kar12] performs single-kernel hierarchy emission without task queues by defining

- (a) Memory layout of Karras [Kar12]

- (b) Memory layout of Apetrei [Ape14]

**Figure 2.4:** BVH memory layouts used to accelerate parallel GPGPU LBVH construction. The method of Karras (a) places each node at the edge of its primitive range closest to the parent split. The method of Apetrei (b) places nodes at their own split positions.

a special node layout, illustrated in Figure 2.4a, where the children of a node are placed at indices surrounding the node's split position. A GPU thread is launched for each inner node, which can determine whether it is at the left or right end of its primitive range by examining the surrounding Morton codes. The algorithm then finds the other end of the range by means of a binary search, and performs a second binary search in the range to determine the split position, which gives the child indices. AABB computation proceeds via a bottom-up reduction: each GPU primitive is assigned a GPU thread which traverses up the hierarchy, joining its AABB to the parent, via parent pointers generated earlier. Each inner node has an atomic counter which is used to kill the first thread entering the node, and allow the second thread to pass. This work also notes that the LBVH can be easily adapted to building point cloud kd-trees and octrees.

Apetrei [Ape14] performs joint hierarchy emission and AABB computation with a bottomup reduction similar to the one used by Karras for AABB computation. Each GPU thread starts at a single primitive and works up the hierarchy, joining its primitive range and AABB to the parent. By using a memory layout where each node is at its split position, as shown in Figure 2.4b, the parent of any primitive range is found by examining the Morton codes at the ends of the range, without incurring a binary search. This results in a very simple implementation, and is currently considered the state of the art.

The above works are limited to scenes small enough to fit in GPU memory. Zeidan et al. [ZNA15] consider out-of-core LBVH construction, i.e., the case of very large scenes. In their framework, blocks of data are paged into GPU memory on demand. Primitive sorting is performed by means of an external sorting algorithm which first performs GPU-accelerated block sorts followed by a multi-way merge. The algorithm then builds a top-level hierarchy top-down, until it encounters nodes with primitive ranges small enough to fit in GPU memory, which are processed on GPU. An earlier example of out-of-core LBVH-like build is the method of Kontkanen et al. [KTO11] for point-based global illumination, which uses Morton code sorting to build an octree of points.

#### 2.1.2 Refinement Based Construction

Plain LBVH, as described above, exhibits very fast build speeds but poor tree quality. Hence, a common approach in recent tree construction research has been to begin with a LBVH tree and postprocess it to improve quality. Doyle [DTM17] calls this approach refinement based construction.

The initial LBVH and HLBVH papers already propose refinement based techniques. Lauterbach et al. [LGS\*09] generate a high-level hierarchy with LBVH, and then refine the large leaves with binned SAH sweeps. Pantoleoni and Luebke [PL10], in turn, propose to rebuild the upper levels of the hierarchy with binned SAH: the reasoning is that high levels of hierarchy have far more impact on tree quality per node and, therefore, the high-quality rebuild gives a better quality improvement per compute effort. Conceptually, in this kind of a top-level build, the high bits of the Morton code are used to bin the scene primitives into the cells of a coarse grid, and a LBVH subtree is built inside each gridcell: the subtree roots are then used as primitive inputs for a high-quality build.

The method of Garanzha et al. [GPBG11] performs the initial steps of LBVH, Morton code computation and sorting, but follows up with an approximate binned SAH sweep build: the SAHs of candidate splits are evaluated based on primitive counts recorded in a multi-level grid.

Bittner et al. [BHH13] give a generic BVH optimization algorithm based on removing inefficient subtrees and inserting them to more advantageous positions in the tree. The method is evaluated on a tree constructed with a SAH sweep, but could also be used to optimize LBVH trees.

Karras and Aila [KA13] have proposed a local optimization technique which rearranges small treelets of, e.g., 8 nodes to improve tree quality. Dynamic programming is used to find a treelet topology which maximizes SAH. The method, later dubbed Treelet Restructuring Bounding Volume Hierarchy (TRBVH), maps well to GPGPU computing as treelets are abundant and can be optimized in parallel. The approach is reminiscent of tree rotations, but considers a larger search space. The resulting trees are often superior to sweep SAH.

The Agglomerative Treelet Restructuring Bounding Volume Hierarchy (ATRBVH) method of Domingues and Pedrini [DP15] replaces the exhaustive search in TRBVH with an agglomerative rebuild, improving on the runtime of TRBVH at the cost of a small decrease in quality. Agglomerative construction considers all available pairs of nodes, and iteratively joins nodes with the lowest cost metric, in this case the surface area of the resulting node, until only the root node remains. Agglomerative construction is not among the fastest builders when applied to complete trees, having  $\mathcal{O}(n^2)$  complexity with regard to the number of input primitives, but it is inexpensive for treelets of a few nodes.

Meister and Bittner [MB17] give a parallel locally-ordered clustering method which is a relative of LBVH – the method includes Morton code sorting and AABB computation, but hierarchy emission proceeds bottom-up by joining nearest-neighbor nodes, searched from a neighborhood on the Morton code order.

Hunt et al. [HMF07] proposed an approximate SAH sweep build which, instead of sweeping the complete primitive list to find optimal splits, samples a constant-sized *cut* of nodes from an initial low-quality hierarchy. The idea is recently applied on modern CPU-based BVH construction by Hendrich et al. [HMB17], using LBVH to generate the initial hierarchy.

#### 2.1.3 Spatial Splits

Several methods have been proposed for splitting large triangles into multiple triangle references in BVH construction, giving, in effect, a hybrid structure between k-d trees and BVHs. This has little effect on scenes with evenly tessellated geometry, such as the

Stanford Bunny, but often gives a significant jump in ray tracing performance for complex scenes with unevenly sized primitives. The drawback is that the resulting hierarchy has a somewhat larger memory footprint due to the duplicate references, and cannot be used for refitting.

A seminal work in this direction was Split Bounding Volume Hierarchy (SBVH) by Stich et al. [SFD09], which often gives a ca. 25% traversal performance improvement over a SAH sweep. Their work, largely speaking, modifes a SAH sweep builder to consider spatial splits in addition to object splits, and selects the most advantageous split in terms of SAH. Recently, Ganestam and Doggett [GD16] propose a builder with triangle splits which gives quality similar to SBVH with a runtime closer to binned SAH. Out of the LBVH-based fast builders described above, TRBVH and Garanzha et al. [GPBG11] incorporate spatial splits generated with faster, lower-quality methods.

#### 2.1.4 Other Build Algorithms

Beside Morton code sorting, some recent builders aim for fast, high-quality builds with other operating principles which deserve mention.

The gold-standard SAH sweep and SBVH algorithms build the tree top-down. An elegant way to apply similar ideas bottom-up is to start with a leaf list which initially contains all primitives, and iteratively merge the leaf pair with the lowest distance metric into an inner node, until only the root node is left. Typically, a SAH-like distance metric is used. This approach is called agglomerative construction. Naive agglomerative construction is  $O(n^3)$  wrt. the number of input primitives and only suitable for trivial scenes, but is amenable to optimization. Walter et al. [WBKP08] use a low-quality kd-tree to accelerate the inner loop of the algorithm. Later work by Gue et al. [GHFB13] proposes Approximate Agglomerative Construction (AAC), where Morton code sorting is used to find an approximate spatial neighborhood for each leaf: the search for the closest primitive is limited to this neighborhood. A GPU builder by Meister and Bittner [MB17] works on a similar principle.

The Bonsai builder by Ganestam et al. [GBDAM15] is based on a fast implementation of SAH sweep which is optimized by means of multithreading, Single Instruction Multiple Data (SIMD) vectorization and algorithm-level improvements. The full algorithm uses a cheap top-down spatial median split to divide the scene into subsets, organizes each subset with SAH sweeps, and connects the resulting trees with a toplevel SAH sweep. Optionally, the subset trees are pruned to improve toplevel build quality. The resulting CPU build is only ca.  $2\times$  slower than the GPU TRBVH build [KA13], though with some generations newer hardware.

Meister and Bittner [MB16] have proposed a builder based on k-means clustering, which is more often seen in machine learning. The algorithm randomly selects bin prototypes from the primitive list, places each primitive in the bin of the closest prototype, and repeats with adjusted prototypes. A surface area based distance metric is used. The algorithm is based on recursive top-down partitioning like, e.g., binned SAH sweep, but generates multiple levels of hierarchy per pass, potentially allowing construction with fewer sweeps and less memory traffic.

#### 2.1.5 Refitting

Aside from rebuilding the acceleration data structure from scratch on each frame, another strategy to handle animations is to *refit* the data structure to the new geometry, using the structure from the previous frame as a base. BVHs are particularly easy to refit by keeping the original tree topology and recomputing all AABBs [LYMT06, WBS07]. This is equivalent to the AABB computation stage of LBVH, i.e., a small sub-component of a very fast tree builder.

However, refitting has two drawbacks to offset the high build performance. Firstly, the quality of a BVH tends to deteriorate with successive refits. Two main strategies to improve quality are to refresh the tree with an asynchronous high-quality build [IWP07, WIP08], and to recover quality with postprocessing, similarly to refinement based construction techniques. Proposed postprocessing techniques include tree rotations [KIS\*12], and restructuring based on culling detected empty spaces and overlaps [YL14]. Lauterbach et al. [LYMT06] give a heuristic criterion for initiating asynchronous rebuilds. Yoon et al. [YCM07] propose criteria to detect and rebuild low-quality subtrees.

The second drawback of refitting is that it is only applicable to mesh deformations. This is a fairly common class of animation, including, e.g., skeletal animations, but various procedural animation methods. E.g., physically simulated fluids are often rendered with marching cubes [LC87] or a similar isosurface method, where the amount and connectivity of triangles is dynamic. A more common difficult case in practical applications might be insertion and deletion of geometry.

#### 2.1.6 Summary

In summary, BVH construction and update has been a subject of intensive research. It is hard to compare the many proposed methods since their results have been obtained with varying hardware platforms, input datasets and degrees of optimization. However, LBVH [LGS\*09] with Karras' [Kar12] or Apetrei's [Ape14] algorithm is certainly the fastest published method to build a BVH from scratch. When aiming for a fairly high quality in addition to real-time build performance, the state of the art is likely one of the refinement based construction methods which build on LBVH. If animations are restricted to mesh deformations, refitting-based methods may give a better runtime-quality tradeoff.

#### 2.2 Hardware Accelerated Construction

A large body of scientific work investigates hardware architectures for ray tracing accelerators, often for mobile systems. In a mobile environment, real time tree construction on programmable hardware is unlikely to be feasible for nontrivial scenes. In order to enable dynamic scenes, tree construction hardware is of high interest. Likewise, in a desktop environment, tree construction for a large scene can take up most of a GPU's resources, and an accelerator unit could free up the GPU for rendering.

Furthermore, hardware tree builders may have applications beyond ray tracing – Heinzle et al. [HGBG08] have proposed a processing unit for point sets, and identified tree construction as future work. In a similar vein, Raabe et al. [RHAZ06] have proposed an accelerator architecture for triangle mesh collision detection, which makes use of BVHs, and leaves deformable objects as an open problem.

#### 2.2.1 Binned SAH Acceleration

The first hardware tree builder for ray tracing was proposed by Doyle et al. [DFM13], around the binned SAH sweep algorithm. This builder is denoted here as Binned SAH Accelerator (BSAHA).

Binned SAH is a recursive top-down build algorithm. At each recursion step, the builder considers a range of primitives, computes the SAH costs for S candidate splits along the three coordinate axes – typically S=8 or S=16 – and selects the split with the best cost. The algorithm then partitions the nodes on each side of the split to contiguous index ranges and proceeds recursively down to each child range. Recursion terminates when there is no split available that would improve the SAH cost compared to generating a leaf. Split SAHs are computed by first placing each primitive in one of S+1 bins which each have an AABB and a primitive count – the SAH for a split is then computed by joining the AABBs and primitive counts of the bins on each side of the split.

BSAHA includes separate pipelines for partitioning, binning and SAH computation. Two optimizations are used to reduce off-chip memory traffic:

- Sufficiently small primitive ranges are processed on-chip and

- the results of partitioning are immediately reused for the binning steps of each child node, halving the amount of DRAM reads in high-level sweeps compared to a naive implementation.

As a result, the architecture generates ca.  $2-3\times$  less traffic than a software build with the same algorithm. In followup work, the architecture was prototyped on Field Programmable Gate Array (FPGA) and applied on volumetric data in addition to triangle meshes [DTM17].

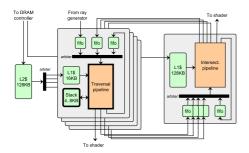

#### 2.2.2 Refit Acceleration

Another approach to hardware-assisted tree update is to accelerate BVH refitting, i.e., updating node AABBs to match new geometry while reusing the tree topology from a previous frame. The HART hardware architecture by Nah et al. [NKP\*15] incorporates a Geometry and Tree Update unit (GTU) for this task. In addition to updating node AABBs, the GTU contains hardware pipelines for generating the updated geometry by interpolation between keyframes, and packaging the updated geometry in TriAccel data structure [Wal04] for cheaper intersection tests. Refitting can be parallelized between multiple GTUs, in which case each unit is assigned a range in the primitive array, and a toplevel refit is done once all the parallel low-level refits finish.

In order to control the tree quality degradation due to refitting, the HART system incorporates asynchronous CPU rebuilds [IWP07, WIP08]. The system gives real time updates for large scenes, but it is noted that it depends on frame-to-frame coherence, and would have difficulty with, e.g., rapidly changing scenes and object insertion and deletion, and changes in mesh topology.

Earlier, the DRPU architecture by Woop et al. [WBS06] also included a programmable  $update\ processor$  for recomputing bounds in a Bounded k-dimensional tree (B-KD tree). A separate update processor program needs to be generated for each dynamic object. Programs can be designed to keep reused vertex coordinates in special  $bound\ registers$ , reducing memory traffic. There are no facilities to refresh degrading tree quality over the

course of animation, and it is emphasized that the system needs coherent motion to work well.

#### 2.2.3 k-Dimensional Tree Accelerators

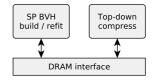

Apart from BVHs, accelerators have been proposed for constructing k-d trees, though these are computationally more complex to construct. The RayCore ray tracing architecture [NKK\*14] incorporates a Tree Build Unit (TBU) to support dynamic geometry, with several high-level optimizations to make the problem more tractable:

- Separate trees are used to index dynamic and static geometry, and the static tree is built using a high-quality offline algorithm. Each ray first traverses the dynamic tree, followed by the static tree.

- The dynamic tree uses a two-level approach similar to Wald et al. [WBS03]: on each frame, a separate tree is built for each dynamic object, followed by the construction of a top-level tree organizing the objects.

- Each dynamic object tree is built in two levels: the high-level hierarchy is generated with a binned SAH build, while subtrees small enough to fit in on-chip working memory are built with a full, sorting-based SAH sweep. The reasoning is that using SAH sweep for the high-level hierarchy would give an unfavorable random memory access pattern. Separate hardware pipelines are allocated for binned and sweep SAH.

The RayCore TBU enables real-time animations with up to ca. 50K triangles of dynamic geometry, but the results underline the difficulty of k-d tree update. Even with the above algorithm-level optimizations, the builder is an order of magnitude slower than BSAHA [DFM13] while using a similar amount of logic – ca. 100 floating-point multipliers for RayCore TBU and 200 for BSAHA.

The later FastTree builder [LDNL15] is based purely on Morton code sorting, and consequently achieves faster builds than the TBU. In this approach, triangle references are generated for each Morton code gridcell overlapped by a triangle's AABB. References are sorted with a radix sort based on hardware parallel prefix sums. When emitting the hierarchy, spatial split planes are generated based on Morton codes.

A weakness of FastTree is that tree quality is not evaluated – as described, it generates triangle references for each Morton code gridcell overlapped by the triangle AABB, potentially leading to a very large number of extra nodes. Intuitively, it appears the quality penalty of Morton code based building would, then, be larger than with SAH builds. In a surprising result, a later software implementation of the same algorithm is reported to give higher traversal performance than a SAH build [LDG17] – however, the result is obtained with a complex methodology which adjusts runtimes measured from different GPUs, rather than a direct comparison.

#### 2.2.4 Imagination Technologies Builder

Related to the recent Imagination Technologies ray tracing GPU project [Pow15], Mc-Combe et al. [MDPN16] patented a hardware builder which processes a single stream of input primitives into, e.g., a BVH or a k-d tree. This is accomplished by binning the input primitives into voxels picked from several volumetric grids of different granularities.

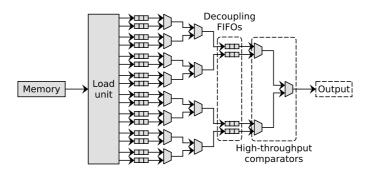

Figure 2.5: 16-way comparator tree used for multi-way merges in FPGA external sorting accelerators [KT11, CO14].

A *voxel cache* stores entries corresponding to voxels, which including primitive lists and compressed bounding volumes. When a voxel entry is evicted from the cache, it is processed into a part of an acceleration tree, and a reference to the resulting tree is added to a cached voxel of coarser granularity.

This streaming volumetric builder has several properties of interest: it is, e.g., able to take advantage of data compression during construction, and can break elongated triangles into multiple bounding volumes. Sadly, no public evaluation exists on the performance of this builder, or the quality of the resulting trees. Another interesting aspect is the proposed use in photon mapping.

#### 2.3 Sorting Hardware

Since sorting is a major component of Morton-code based tree builds, it is interesting to look at the literature on sorting accelerators. This literature can be divided into accelerators for internal and external sorting, which are used, respectively, on arrays small enough to fit on-chip, and on arrays so large that they need to be stored in slow off-chip memory. The best hardware design for internal sorting also depends on the input size, e.g., very small arrays can be handled with sorting networks [Knu99] at a rate of one array per cycle, but these quickly explode in complexity. Since only trivial 3D scenes fit on-chip, tree construction has more use for an external sort. The recent work on external sorting accelerators focuses on FPGA-based designs built around the multimergesort, or external mergesort algorithm [Knu99].

Multimergesort first sorts runs of data which are small enough to fit in local memory, and then repeatedly merges multiple runs together, until a single run remains. More formally, the goal is to sort N data elements, taking advantage of M elements of fast local memory while N >> M, and minimizing traffic to a slow external memory. Moreover, the external memory should be accessed in block transfers of size B. Each merge, then, reads M/B runs and writes out a single run. At the time of the algorithm's invention, the fast memory was Dynamic Random Access Memory (DRAM) and the slow memory was, e.g., a rotary magnetic drive, but contemporary work instead minimizes traffic to the DRAM in favor of on-chip Static Random Access Memorys (SRAMs) blocks.

The initial local sorts in hardware multimergesort could be implemented with any internal

sorting algorithm, for example, bitonic sorts are recently popular. Starting with the design of Koch and Torrensen [KT11], multi-way merges are largely performed by means of comparator trees, which consists of comparators that push the lower of the input values to the output. An exception is the work by Zhang et al. [ZCP16], where an FPGA accelerates block sorts, and the multi-way merges are done on CPU. A 16-way comparator tree is shown in Figure 2.5. A K-way tree requires  $\mathcal{O}(k \log k)$  comparators and First In First Outs (FIFOs), however, only  $\mathcal{O}(\log k)$  of them are active at a time. One difficulty with a large tree is to determine backpressure propagation, i.e., which comparators should consume their inputs and which should stall, in one cycle. This can be resolved by inserting decoupling FIFOs between some tree levels [KT11].

Later work focuses on improving the throughput of comparator trees, as they are in the basic design limited to serial operation by the final comparator in the tree. FPGASort by Casper et al. [CO14] places high-throughput comparators near the top of the tree, which consume and produce multiple data items per cycle for a throughput of 6. Mashimo et al. [MVCK17] give comparators with a throughput of 8. Srivastava et al. [SCPC15] propose to replace the top levels of the tree with bitonic networks.

Since memory traffic is determined by the number of merge passes, it is desirable to build very large trees with, e.g., hundreds or thousands of sources. Large comparator trees may consume the resources of an entire FPGA, limiting the possible merge width. Usui et al. [UVCK16] propose a multi-way merge design with only a single physical comparator per tree level, in which the logical FIFOs are stored in Block Random Access Memorys (BRAMs). This gives logarithmic resource utilization in terms of merge width, except for BRAMs, and allows large merges: merge widths up to 4096 are evaluated.

In order to reach high operating frequencies on FPGA, sorter designs are creatively pipelined. Koch and Torrensen [KT11] pipeline comparators by comparing the more significant half of the on the first clock cycle, and the less significant half on the second. Casper et al. [CO14] also propose a complex pipelining strategy for the high-throughput comparators near the top of the tree. These techniques are a special feature of FPGA circuit design: Application Specific Integrated Circuit (ASIC) designs typically do not need this degree of pipelining to reach the desired operating frequency.

#### 2.4 Thesis Contribution

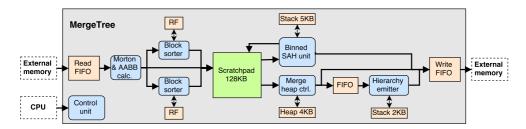

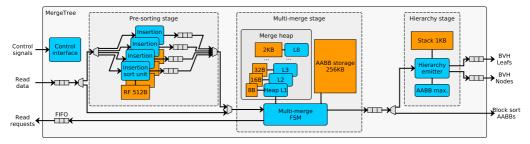

To summarize the state of the art review above, the hardware tree updaters proposed to date are the refit-based HART architecture by Nah et al. [KSS\*13], the tree builder by Doyle et al. [DFM13], which we refer to as BSAHA, and k-d tree builders [NKK\*14, LDNL15]. In [P1,P2], we propose a new builder architecture based on LBVH, MergeTree. MergeTree applies the general traffic reduction approaches of streaming computation and local memory usage — used to good effect in BSAHA and TBU — to the computationally cheaper LBVH algorithm. Since primitive sorting is a major component of memory traffic, it is performed with an external sorting algorithm. The main novel contributions in [P1,P2] are:

- a streaming algorithm for HLBVH hierarchy emission and AABB computation in LBVH and

- an external sorting implementation based on a hardware heap [IK07] rather than a comparator tree.

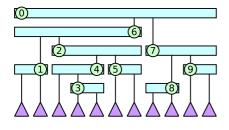

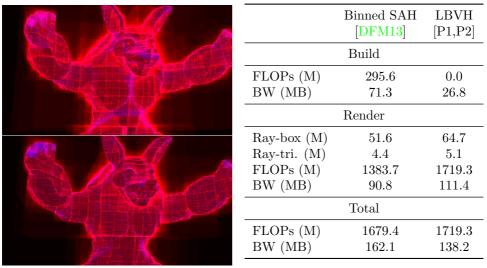

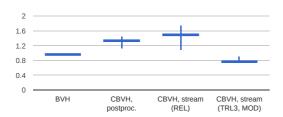

(a) Traversal cost with LBVH (top) and binned SAH (bottom) builds.

(b) Memory layout of Apetrei [Ape14]

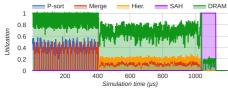

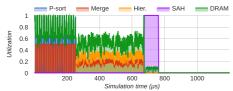

Figure 2.6: Detailed example comparison of MergeTree [P1,P2] to BSAHA [DFM13] in platform-independent metrics for one test scene. The Armadillo scene (213K triangles) is drawn with 1spp, one diffuse bounce, without next event estimation. BW: external memory bandwidth, FLOPs: floating-point operations. Addition, subtraction and multiplication are counted as a single FLOP, reciprocal as 3. Tree build BW is exact; rendering BW depends heavily on the cache hierarchy. Here, the simple cache model from [P3] is used. The Armadillo model is courtesy of the Stanford Computer Graphics Laboratory.

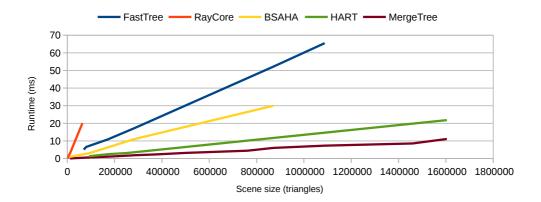

Figure 2.7: Reported runtimes of hardware tree builders.

The combination of external sorting and streaming allows MergeTree to use ca.  $3 \times$  less bandwidth than software LBVH, while the heap-based sorter gives a compact silicon area. A similarly economical sorter architecture was later proposed by Usui et al. [UVCK16].

The proposed architecture gives distinct advantages compared to the state of the art: Compared to BSAHA, MergeTree uses an inexpensive algorithm, allowing significant reductions in build time, energy, silicon area and memory traffic. BSAHA, e.g., comprises

hundreds of Floating Point Units (FPUs) while MergeTree performs no floating-point arithmetic. As a drawback, the quality of output trees is lower, increasing the cost of ray tracing. A part of the quality can be recovered via *toplevel builds*, which are inexpensive enough to run in real time on a mobile CPU.

The tradeoff between the builders depends heavily on scene complexity and rendering parameters, and is quantified in [P2] for a variety of scenes and parameters. A worked example using platform-independent metrics is shown for a single test scene in Figure 2.6. In this case, the low quality of LBVH significantly increases the arithmetic and bandwidth cost of traversal, but these costs are compensated by savings in the tree build. Larger scenes tilt the tradeoff in favor of LBVH, and more complex visual effects, in favor of BSAHA. It should be noted that both hardware units use ca.  $3 \times$  less bandwidth than a corresponding software builder.

Compared to the Morton code based k-d tree units, MergeTree contributes memory traffic optimizations for sorting. Combined with the simpler hierarchy emission of BVHs, this gives a much faster build speed than seen in the k-d tree units.

Refitting hardware such as HART is likely cheaper and faster than MergeTree to some degree, though not as much as software refitting is when compared to tree construction. A rough comparison is included in [P3]. However, refitting can only handle a limited class of animations, i.e., mesh deformations such as skeletal animation. Interesting classes of animation are out of reach, such as fracturing and fluid simulations rendered with marching cubes. Moreover, a refitting system requires full builds whenever new geometry is introduced, and at intervals to refresh the degrading tree quality.

A summary of reported build speeds of MergeTree and related work is shown in Figure 2.7. It is visible that MergeTree gives the fastest build performance out of hardware builders in the literature.