Jari Heikkinen

# **Program Compression in Long Instruction Word Application-Specific Instruction-Set Processors**

| Tampereen teknillinen yliopisto. Julkaisu 689 Tampere University of Technology. Publication 689                                                                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Jari Heikkinen                                                                                                                                                                                                                                |

| Program Compression in Long Instruction Word Application-Specific Instruction-Set Processors                                                                                                                                                  |

| Thesis for the degree of Doctor of Technology to be presented with due permission for public examination and criticism in Tietotalo Building, Auditorium TB109, at Tampere University of Technology, on the 7th of December 2007, at 12 noon. |

| Tampereen teknillinen yliopisto - Tampere University of Technology<br>Tampere 2007                                                                                                                                                            |

### **ABSTRACT**

Modern day embedded systems set high requirements for the processing hardware to minimize the area, and more importantly, the power consumption. Moreover, the ever increasing complexity of embedded applications requires more and more processing power. Application-specific architectures, where the hardware resources can be tailored for a given application, have been introduced to meet these requirements.

Parallel processor architectures have also become favorable as they provide more processing power by utilizing the instruction level parallelism. However, parallel processor architectures result in large program codes, which require large memories that increase not only the area, but also the power consumption of the system due to increased memory I/O bandwidth. Program compression methods have been proposed to tackle this problem and reduce the size of the program code and, therefore, also the area and power consumption.

The focus of this Thesis is on program compression in parallel processor architectures. State-of-the-art program compression methods are surveyed and compared against the derived comparison metrics. Based on the survey, three compression methods are chosen to be evaluated on transport triggered architecture, a parallel processor architecture template used to design application-specific instruction-set processors. The methods are adapted to exploit the characteristics of the architecture. In addition to code density evaluations in terms of compression ratio, an evaluation methodology based on hardware implementations is proposed. It allows to evaluate the effects of compression on the actual area and power consumption of the system.

Program compression may also result in poor instruction-set orthogonality, which makes the programming after compression more difficult and worsens the performance. The orthogonality may turn out to be so poor that the program code cannot be modified anymore. A novel methodology with a small overhead in area and power consumption is proposed to allow to modify the program code also after compression.

#### **PREFACE**

The work presented in this Thesis has been carried out in the Institute of Digital and Computer Systems at Tampere University of Technology during the years 2001-2007.

I would like to express my gratitude to my supervisor Prof. *Jarmo Takala* for his professional guidance and encouragement towards doctoral degree. I am also thankful to Prof. *Henk Corporaal* for his invaluable support to my research work. Acknowledgements go also to my Thesis reviewers Prof. *Johan Lilius* and *Jan Hoogerbrugge*, Ph.D., for their constructive and valuable comments on the manuscript.

Many thanks to all my colleagues in the FlexDSP research group for their cooperation. Especially, *Andrea Cilio*, Ph.D., *Tommi Rantanen*, M.Sc., *Jaakko Sertamo*, M.Sc., *Teemu Pitkänen*, M.Sc., and *Pekka Jääskeläinen*, M.Sc., deserve special thanks for helping me in several matters related to my research work. I would also like to thank *Mauri Kuorilehto*, M.Sc., *Panu Hämäläinen*, Dr.Tech., *Mikko Kohvakka*, M.Sc., *Tero Kangas*, Dr.Tech., and *Erno Salminen*, M.Sc., for sharing ideas, knowledge, and opinions, both on and off the topic.

This Thesis was financially supported by Graduate School in Telecommunication System-on-Chip Integration (TELESOC), National Technology Agency (TEKES), Nokia Foundation, Ulla Tuominen Foundation, Foundation of Advancement of Technology, Heikki and Hilma Honkanen Foundation, Jenny and Antti Wihuri Foundation, and HPY Research Foundation, which are gratefully acknowledged.

I wish to express my sincere gratitude to my parents, *Hannu* and *Irma Heikkinen*, and my brother *Jarkko* for their unconditional support and encouragement throughout my academic career and, for that matter, throughout my life. Finally, I thank you *Terhi* for your love, patience, and understanding.

Tampere, November 2007

Jari Heikkinen

# TABLE OF CONTENTS

| Ab  | stract  |             |                                                       | i    |

|-----|---------|-------------|-------------------------------------------------------|------|

| Pre | eface   |             |                                                       | iii  |

| Tai | ble of  | Conten      | ts                                                    | v    |

| Lis | st of F | Publication | ons                                                   | ix   |

| Lis | st of F | igures      |                                                       | xi   |

| Lis | st of T | ables       |                                                       | XV   |

| Lis | st of A | Abbrevia    | tions                                                 | τvii |

| Lis | st of S | Symbols     |                                                       | xxi  |

| 1.  | Intro   | duction     |                                                       | 1    |

|     | 1.1     | Objecti     | ive and Scope of Research                             | 3    |

|     | 1.2     | Main C      | Contributions                                         | 4    |

|     |         | 1.2.1       | Author's Contribution                                 | 4    |

|     | 1.3     | Thesis      | Outline                                               | 5    |

| 2.  | Prog    | ram Coi     | mpression                                             | 7    |

|     | 2.1     | Progra      | m Compression on Single-Issue Processor Architectures | 10   |

|     | 2.2     | Progra      | m Compression on Parallel Processor Architectures     | 12   |

|     |         | 2.2.1       | Comparison Metrics                                    | 13   |

|     |         | 2.2.2       | Comparison of Methods                                 | 18   |

|     |         | 2.2.3       | Comparison Summary                                    | 36   |

| 3. | Proc | essor Ha | ardware Customization                               | 39 |

|----|------|----------|-----------------------------------------------------|----|

|    | 3.1  | Custon   | nizable Processor Architectures                     | 41 |

|    |      | 3.1.1    | Instruction-Set Extensions                          | 42 |

|    |      | 3.1.2    | Fully Customizable Processor Architectures          | 45 |

|    | 3.2  | Transp   | ort Triggered Architecture                          | 48 |

|    |      | 3.2.1    | Principles                                          | 48 |

|    |      | 3.2.2    | Software Characteristics                            | 50 |

|    |      | 3.2.3    | Hardware Characteristics                            | 51 |

|    |      | 3.2.4    | Pipelining                                          | 53 |

|    |      | 3.2.5    | Instruction Format                                  | 53 |

|    | 3.3  | TTA-B    | Based ASIP Design Methodologies                     | 55 |

|    |      | 3.3.1    | Move Framework                                      | 56 |

|    |      | 3.3.2    | TTA Codesign Environment                            | 59 |

| 4. | Prog | ram Co   | mpression on TTA                                    | 63 |

|    | 4.1  | Utilize  | d Compression Methods                               | 64 |

|    |      | 4.1.1    | Huffman Coding                                      | 65 |

|    |      | 4.1.2    | Instruction Template-Based Compression              | 68 |

|    |      | 4.1.3    | Dictionary-Based Compression                        | 73 |

|    | 4.2  | Hardw    | are Implementations                                 | 75 |

|    |      | 4.2.1    | Implementation Principles                           | 76 |

|    |      | 4.2.2    | Implementing Dictionary-Based Compression           | 78 |

|    |      | 4.2.3    | Implementing Instruction Template-Based Compression | 80 |

|    | 4.3  | Summa    | ary of the Program Compression Evaluations          | 83 |

| 5. | Maiı | ntaining | Programmability after Compression                   | 85 |

|    | 5.1  | Progra   | mmability on TTA                                    | 89 |

|    |        | 5.1.1    | Requirements for Programmability       | 90   |

|----|--------|----------|----------------------------------------|------|

|    |        | 5.1.2    | Programmability Support Methodology    | 92   |

| 6. | Resi   | ılts     |                                        | 101  |

|    | 6.1    | Evalua   | tion Methodology                       | 101  |

|    |        | 6.1.1    | Benchmarks                             | 102  |

|    |        | 6.1.2    | Processor Design                       | 104  |

|    | 6.2    | Code D   | Density                                | 110  |

|    |        | 6.2.1    | Dictionary-Based Compression           | 110  |

|    |        | 6.2.2    | Huffman Coding                         | 113  |

|    |        | 6.2.3    | Instruction Template-Based Compression | 118  |

|    | 6.3    | Area aı  | nd Power Consumption                   | 121  |

|    |        | 6.3.1    | Dictionary-Based Compression           | 122  |

|    |        | 6.3.2    | Instruction Template-Based Compression | 131  |

|    | 6.4    | Prograi  | mmability Evaluation                   | 133  |

|    |        | 6.4.1    | Design of the Extended Dictionary      | 133  |

|    |        | 6.4.2    | Area and Power Consumption             | 136  |

|    |        | 6.4.3    | Performance                            | 138  |

|    | 6.5    | Summa    | ary of Results                         | 140  |

| 7. | Cond   | clusions |                                        | 143  |

| D; | bliogr | onhy     |                                        | 1/15 |

### LIST OF PUBLICATIONS

This Thesis is a monograph, which contains some unpublished material, but is mainly based on the following publications. In the text, these publications are referred to as [P1], [P2], ..., [P6].

- [P1] J. Heikkinen, J. Takala, and J. Sertamo, "Code Compression on Transport Triggered Architectures," in *System-on-Chip for Real-Time Applications*, W. Badawy and G.A. Jullien Eds., pp. 203–213. Kluwer Academic Publishers, Boston, MA, USA, 2003.

- [P2] J. Heikkinen, T. Rantanen, A. Cilio, J. Takala, and H. Corporaal, "Evaluating Template-Based Instruction Compression on Transport Triggered Architectures," in *Proceedings of the International Workshop on System-on-Chip for Real-Time Applications*, Calgary, Canada, June 30 – July 2 2003, pp. 129– 195.

- [P3] J. Heikkinen, A. Cilio, J. Takala, and H. Corporaal, "Dictionary-Based Program Compression on Transport Triggered Architectures," in *Proceedings of the IEEE International Symposium on Circuits and Systems*, Kobe, Japan, May. 23–26 2005, pp. 1122–1125.

- [P4] J. Heikkinen, J. Takala, and H. Corporaal, "Dictionary-Based Program Compression on TTAs: Effects on Area and Power Consumption," in *Proceedings of IEEE Workshop on Signal Processing Systems*, Athens, Greece, Nov. 2–4 2005, pp. 479–484.

- [P5] J. Heikkinen and J. Takala, "Programmability in Dictionary-Based Compression," in *Proceedings of International Symposium on System-on-Chip*, Tampere, Finland, Nov. 13–16 2006.

[P6] J. Heikkinen and J. Takala, "Effects of Program Compression," in *Journal of Systems Architecture*, vol. 53, no. 10, pp. 679–688, Oct. 2007.

# LIST OF FIGURES

| 1  | Principle of compressing and decompressing data                                                                                                                    | 8  |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2  | Alternative locations for the decompressor                                                                                                                         | 10 |

| 3  | An example of VLIW instruction word. FU-(x): functional unit field.  Opcode: Operation code field. RD: Destination register field. RS(y):  Source register field.  | 14 |

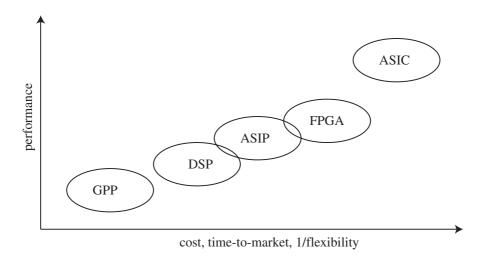

| 4  | Classification of processing architectures based on their characteristics.                                                                                         | 42 |

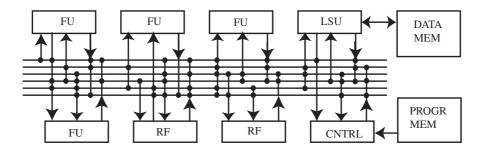

| 5  | TTA processor organization FU: functional unit. RF: register file. LSU: load-store unit. CNTRL: control unit. Dots represent connections between buses and sockets | 52 |

| 6  | Organization of the three-stage TTA transport pipeline                                                                                                             | 54 |

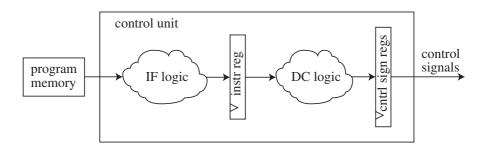

| 7  | Organization of the transport pipeline logic in the control unit of the processor. instr reg: instruction register. cntrl sign regs: control signal registers      | 55 |

| 8  | Structure of the TTA instruction word. G: Guard field. S: Source ID field. D: Destination ID field. LI: Long immediate field. (x): x-bit field.                    | 56 |

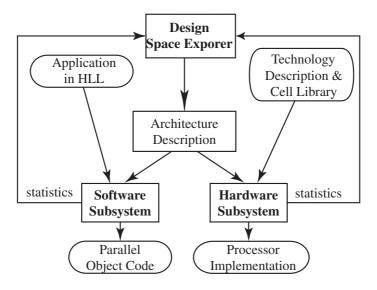

| 9  | Principal design flow in the MOVE framework                                                                                                                        | 57 |

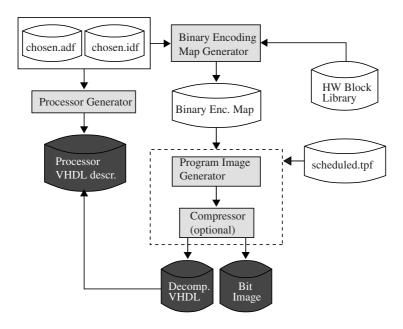

| 10 | Principal design flow of processor and program image generation phase in the TCE design flow.                                                                      | 62 |

| 11 | a) Original symbols with their probabilities and the assigned Huffman codewords. b) Huffman tree. c) Huffman decoding table                                        | 66 |

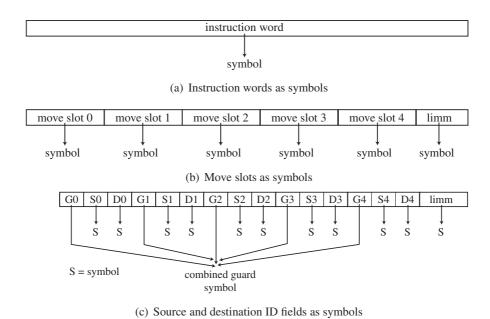

| 12 | Different granularity levels for selecting the symbols for Huffman coding.                                                                                         | 68 |

| 13 | Compression alternatives for the move slot and ID field granularity levels                                                                                                                                                                                                                                             | 69  |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 14 | a) Profile of the used move slot and long immediate field combinations with their usage frequencies. b) The chosen templates and their widths                                                                                                                                                                          | 72  |

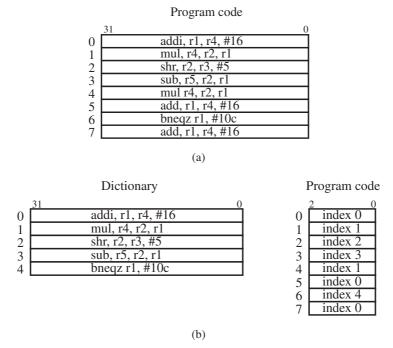

| 15 | a) The original uncompressed program code. b) The generated dictionary and the compressed program code                                                                                                                                                                                                                 | 74  |

| 16 | Transport pipeline organization for the alternative decompressor implementations                                                                                                                                                                                                                                       | 79  |

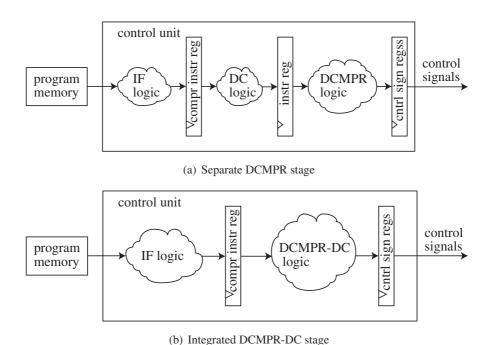

| 17 | a) An example of transport pipeline execution when an uncompressed instruction is xexecuted among compressed instructions. b) An example of transport pipeline execution in region compression                                                                                                                         | 89  |

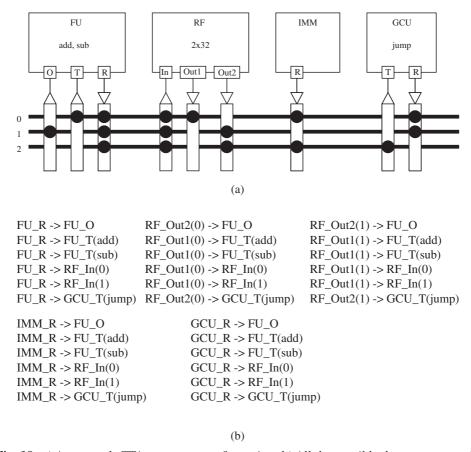

| 18 | a) An example TTA processor configuration. b) All the possible data transports that can be executed on the example TTA processor                                                                                                                                                                                       | 91  |

| 19 | An example of dictionary extension. a) an example set of data transports to be added. The extended dictionaries for compression at b) instruction, c) move slot, and d) ID field levels. The three dots () represent the entries that correspond to bit patterns already stored into the dictionary during compression | 95  |

| 20 | The optimized set of the required data transports with the utilization of the GCR in the example TTA processor configuration illustrated in Fig. 18(a).                                                                                                                                                                | 97  |

| 21 | Example of a compressed program code including immediate values.                                                                                                                                                                                                                                                       | 99  |

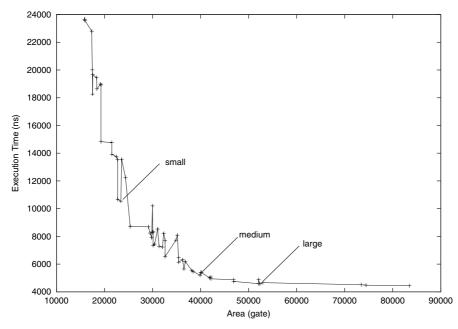

| 22 | The chosen processor configurations for the 32-point DCT application on the pareto curve                                                                                                                                                                                                                               | 105 |

| 23 | The results of applying dictionary-based compression at instruction level                                                                                                                                                                                                                                              | 111 |

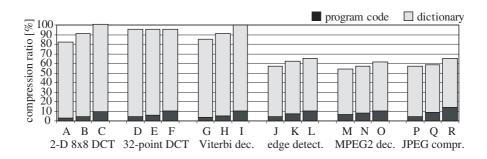

| 24 | The results of applying dictionary-based compression at move slot level                                                                                                                                                                                                                                                | 112 |

| 25 | The results of applying dictionary-based compression at ID field level.                                                                                                                                                                                                                                                | 114 |

| 26 | The results of applying Huffman coding at instruction level                                                                       | 115 |

|----|-----------------------------------------------------------------------------------------------------------------------------------|-----|

| 27 | The results of applying Huffman coding at move slot level                                                                         | 116 |

| 28 | The results of applying Huffman coding at ID field level                                                                          | 118 |

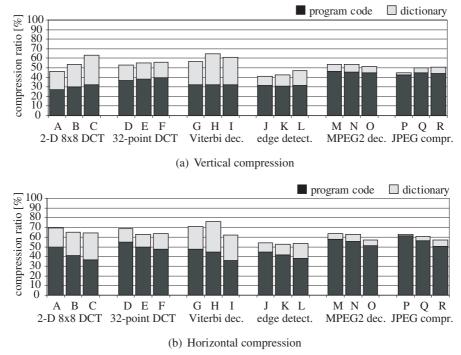

| 29 | The results of applying instruction template-based compression                                                                    | 120 |

| 30 | The relative code sizes of the benchmark applications when instruction template-based compression is utilized                     | 121 |

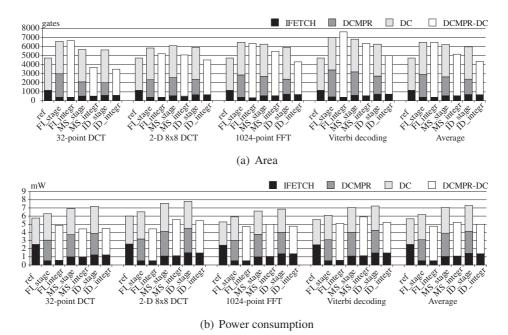

| 31 | Area and power consumption results on configuration A                                                                             | 123 |

| 32 | Area and power consumption results on configuration B                                                                             | 124 |

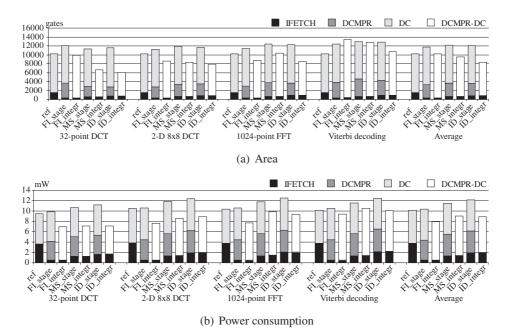

| 33 | Area and power consumption of the control logic on configuration A with different transport pipeline organizations                | 128 |

| 34 | Area and power consumption of the control logic on configuration B with different transport pipeline organizations                | 129 |

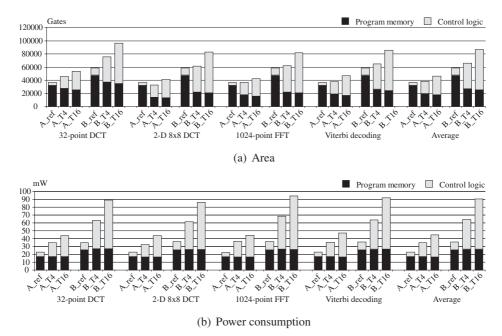

| 35 | Area and power consumption of the program memory and the control logic when the instruction template-based compression is applied | 132 |

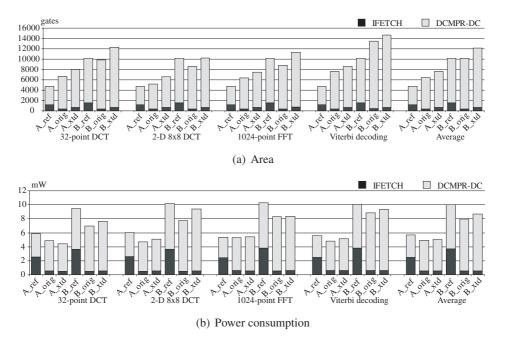

| 36 | The effects of the dictionary extension and immediate support on area and power consumption of the control logic                  | 137 |

| 37 | Summary of the code density evaluations in terms of average compresion ratio.                                                     | 141 |

| 38 | Summary of the area and power consumption evaluations based on the average area and power consumption reductions                  | 142 |

# LIST OF TABLES

| 1  | Comparison of the target architecture and instruction encoding of the program compression methods on parallel processor architectures.  NA: Not available                                                                    | 19  |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2  | Comparison of the compression granularity and decompressor implementation of the program compression methods on parallel processor architectures. PMEM: Program Memory. CPU: Central Processing Unit                         | 20  |

| 3  | Comparison of the random access support and effectiveness of the program compression methods on parallel processor architectures                                                                                             | 21  |

| 4  | Summary of the program compression methodology evaluations on TTA                                                                                                                                                            | 83  |

| 5  | Hardware resources of the chosen processor configurations. LSU: Load-stored unit. MUL: Multiplier. ARITH: Arithmetic unit. SHIFT: Shifter. LOGIC: Logic unit. CMP: Compare unit. Regs.: Registers. Iwidth: Instruction width | 106 |

| 6  | Performance and code size statistics of the benchmark applications, each compiled on the three different TTA processor configurations                                                                                        | 107 |

| 7  | Hardware resources of the two TTA processor configurations                                                                                                                                                                   | 108 |

| 8  | Benchmark statistics on the two TTA processor configurations and on the TMS320C62x.                                                                                                                                          | 109 |

| 9  | Area and power consumption of the reference designs. PMEM: Program memory. DMEM: Data memory                                                                                                                                 | 109 |

| 10 | Summary of the area and power consumption evaluations with a separate pipeline stage for the decompressor.                                                                                                                   | 126 |

xvi List of Tables

| 11 | Increase in cycle count due to increased branch latency                                                                                                     | 127 |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 12 | Summary of the area and power consumption evaluations with the integrated decompressor implementation                                                       | 130 |

| 13 | Statistics of the number of data transports required to maintain the programmability on the two TTA processor configurations. Src: source. Dst: destination | 134 |

| 14 | Statistics of the original and extended dictionaries for the four benchmarks                                                                                | 136 |

| 15 | The effects on the performance of programming basic blocks (BB) using the extended entries                                                                  | 139 |

# LIST OF ABBREVIATIONS

ADF Architecture Definition File

ALU Arithmetic-Logic Unit

ASIC Application-Specific Integrated Circuit

ASIP Application-Specific Instruction-Set Processor

BB Branch Block

CISC Complex Instruction-Set Computer

CMOS Complementary Metal Oxide Semiconductor

CPU Central Processing Unit

DC DeCode

DCMPR DeCoMPRess

DCT Discrete Cosine Transform

DMEM Data MEMory

DSP Digital Signal Processing or Digital Signal Processor

EPIC Explicitly Parallel Instruction Computer

EOP End of a Packet

EX EXecute

FFT Fast Fourier Transform

FIFO First In First Out

FIW Functional Instruction Word

FPGA Field Programmable Gate Array

FU Functional Unit

GCR Global Connection Register

GCU Global Control Unit

GPP General-Purpose Processor

HBL Hardware Block Library

HDB Hardware DataBase

HDL Hardware Description Language

HLL High-Level Language

ID IDentifier

IDF Implementation Definition File

IEEE the Institute of Electrical and Electronics Engineers

IF Instruction Fetch

II.P Instruction-Level Parallelism

IMM IMMediate unit

JPEG Joint Photographic Experts Group

LAT Line Address Table

LIM Local Instruction Memory

LISA Language for Instruction Set Architectures

LSU Load-Store Unit

LZW Lempel-Ziv-Welch

MAC Multiply-ACcumulate

MBL MetaCore Behavioral Language

MPEG Moving Picture Expert Group

MSL MetaCore Structural Language

MV MoVe

NOP No-Operation

NRE Non-Recurring Engineering

OSAL Operation-Set Abstraction Layer

OTA Operation Triggered Architecture

PC Program Counter

PDA Personal Digital Assistant

PICO Program In, Chip Out

PIG Program Image Generator

PMEM Program MEMory

RAM Random Access Memory

ROM Read-Only Memory

RISC Reduced Instruction-Set Computer

RF Register File

RTL Register Transfer Level

SFU Special Functional Unit

SIMD Single Instruction, Multiple Data

SoC System-on-Chip

SRAM Static Random Access Memory

TCE TTA Codesign Environment

TTA Transport Triggered Architecture

TPEF TTA Program Exhange Format

TVLIW Tagged Very Long Instruction Word

VHDL Very High Speed Integrated Circuit Hardware Description Lan-

guage

VLES Variable-Length Execution Set

VLIW Very Long Instruction Word

XML EXtensible Markup Language

# LIST OF SYMBOLS

CR compression ratio

$S_c$  compressed code size

$S_t$  decoding table size

$S_u$  uncompressed code size

*k* budget of templates

$\tau$  set of templates

W program code size

$T_l$  template l in  $\tau$

*n* number of minimal templates

$C_i$  unique move slot and long immediate field combination i

$f_i$  usage frequency of  $C_i$

$N(\tau, C_i)$  narrowest template  $T_l$  in  $\tau$  to encode  $C_i$

$w(T_l)$  width of template  $T_l$

$T_{C_i}$  candidate template j

$v(C_i)$  lower bound of the width of  $T_{C_i}$

$b_{C_j}$  benefit of  $T_{C_i}$

K number of bit patterns in program code

N number of unique bit patterns in program code

| C                 | connectivity of a register file                                 |

|-------------------|-----------------------------------------------------------------|

| W                 | width of bit pattern                                            |

| $I_{\mathcal{S}}$ | set of buses to which an input socket $i$ is connected to       |

| $O_s$             | set of buses to which an output socket <i>i</i> is connected to |

List of Symbols

xxii

## 1. INTRODUCTION

The recent advances in the semiconductor technologies, fabrication processes, and design methodologies have allowed to implement more and more functionality on a single chip, even entire systems that are composed of programmable processors cores, memories, customized hardware accelerators, and radio frequency and analogue parts. Such a system is often referred to as System-on-Chip (SoC). The higher integration rate has allowed to reduce the size and, therefore, the cost of digital systems and has enabled the introduction of many new digital products. The growth has been explosive especially in the embedded systems market. Embedded system usually refers to a computing system that has been specifically designed to control some device, i.e., the system is not used for general purpose computing. Embedded systems are also often embedded into the device they control. Nowadays, the market share of embedded systems far surpasses that of the general purpose computing systems, such as personal computers.

Embedded systems can nowadays be found in almost every aspect of our everyday life; automobiles, home automation, banking, multimedia, and telecommunications to name a few. The most recent advances have concentrated on the market of portable handheld embedded systems. These systems, like cellular phones, personal digital assistants (PDA), game consoles, and media players, are often limited by constraints on size, weight, battery life, and cost. Hence, the area and, nowadays more importantly, the power consumption have turned out to be the most important design constraints in the embedded system development.

Apart from the area and power consumption requirements, embedded systems require nowadays more and more processing power from the computing hardware due to the increased complexity of embedded applications. The requirements for small area and low power consumption but high performance have lead to the utilization of application-specific structures where the hardware resources can be tailored ac-

cording to the requirement of the application. This allows to meet the performance requirements. The area and power consumption are also reduced as the system contains only the hardware resources that are required to execute the given applications.

Recently, very long instruction word (VLIW) architectures have gained considerable popularity in embedded systems, especially in digital signal processing (DSP) tasks, due to their modularity and scalability [100]. VLIW architectures can provide more processing power through utilizing the instruction-level parallelism (ILP) available in the application by executing operations in parallel in concurrently operating functional units (FU). The FUs are controlled by a long instruction word that contains dedicated fields for each FU. This kind of an instruction encoding leads to poor code density, i.e., large size of the program code, as the full processing power of the architecture cannot always be fully utilized [29].

The size of the program code is increasing also due to increased complexity of the applications that are developed for the embedded systems. Furthermore, high-level languages (HLLs), like C and C++, are gradually replacing assembly language in writing embedded applications due to lower application development and maintenance costs. This incurs a penalty in the code size as the compiler cannot achieve the quality of the hand-written and hand-optimized assembly code when the HLL code is translated into machine code. Moreover, compilers traditionally favor performance at the cost of code size.

Large program codes require large memories, which may lead to systems where the memories consume more area than the actual processor core [14]. Large memories may also increase the power consumption of the system due to higher memory I/O bandwidth. This reduces the battery life. Therefore, methods to reduce the size of the program code need to be developed in order to preserve area, and more importantly, reduce the power consumption of the program memory and the entire system.

Program compression methods have been proposed to reduce the size of the program code to allow to use smaller memories and hence save the area and power consumption. The program is compressed during compile-time and stored in compressed form into the program memory. During execution, the compressed instructions are fetched from the program memory and decompressed back to their original form using a dedicated decompressor hardware before they are decoded into control signals that control the hardware resources of the processor.

# 1.1 Objective and Scope of Research

The objective of this Thesis is to develop an effective program compression methodology for a new type of customizable parallel processor architecture, the transport triggered architecture (TTA). Transport triggered architecture suffers from poor code density due to the programming model of the architecture and the minimal instruction encoding that has been utilized to simplify instruction decoding.

The first objective is to perform a survey over the proposed program compression approaches on parallel processor architectures. The survey is performed by defining the main metrics related to program compression, which are then used to perform a comparison over the methods included in the survey.

The second objective is to adapt and utilize the most effective methodologies found in the survey on TTA. In addition to code density evaluations, the processor systems executing both compressed and uncompressed instructions are implemented in hardware. This allows to evaluate the compression methods in terms of area, and more importantly, power consumption, which provide more accurate estimates on the effectiveness of the compression methods. Such measures have been rarely reported for program compression approaches.

The third objective is to design a methodology that allows to maintain the programmability, i.e., allow to make modifications to the program code also after the compression has been applied. In case the hardware decompressor is implemented using nonprogrammable structures, such as standard cell logic, the programmability may be lost as the decompression hardware is tailored for a particular application or a set of applications and cannot be modified after the processor has been implemented in hardware. The objective of the methodology is to provide full programmability with a small overhead in area, power consumption, and performance.

The fourth objective is to integrate the TTA program compression methodology to the TTA codesign environment toolset. This allows to include the program compression in the TTA processor design and code generation flow. The binary image generator of the TTA codesign environment is designed to provide a methodology that allows easy integration and modification of the compression methodology. The compressor module generates not only the compressed binary code, but also the hardware description of the decompressor hardware.

#### 1.2 Main Contributions

In this Thesis, a design methodology for compressing the program code to reduce the area and power consumption is developed for transport triggered architecture. To summarize, the main contributions are the following:

- Study and comparison of state-of-the-art program compression methods on parallel processor architectures by comparing the methods against the defined comparison metrics

- Utilization of dictionary-based, Huffman encoding, and instruction templatebased compression methods on transport triggered architecture by employing the characteristics of the architecture to achieve better compression

- Evaluation methodology based on hardware implementations of the processor designs to measure the effects of program compression on area and power consumption, which allows to include the decompression overhead in the results

- Novel methodology to maintain the programmability and increase the orthogonality of the instruction set that is affected when program compression methods are utilized

- Integration of the program compression methodology to the transport triggered architecture codesign environment, allowing to utilize plug-in compressor modules to compress the program code and generate the decompressor and integrate it to the hardware description of the processor

#### 1.2.1 Author's Contribution

The author was responsible for making the survey of state-of-the-art program compression methodologies and to define the comparison metrics that were used to compare the proposed compression methodologies.

The author was responsible for adapting Huffman coding, dictionary-based compression, and instruction template-based compression methods on transport triggered architecture. The profiling tools for the Huffman coding and dictionary-based compression were implemented by the author. The program code profiling and template

selection tool for the instruction template-based compression was implemented by M.Sc. Tommi Rantanen. The code density estimations of the utilized compression method on TTA were carried out by the author. The results of these studies have been presented in [P1, P2, P3].

The author also derived the hardware implementations for the dictionary-based and instruction template-based compression approaches and evaluated the hardware implementations in terms of area and power consumption. The results of these experiments have been reported in [P4, P6].

The author was also responsible for developing the dictionary extension methodology to maintain the programmability after the compression has been utilized. The author proposed and designed also the methodology to minimize the overhead of the dictionary extension on area and power consumption of the decompression logic. The author was responsible for performing the evaluations of the proposed methodology in terms of area, power consumption, and performance. The methodology and the results of the evaluations have been published in [P5].

The integration of the compression methodology in the TTA Codesign Environment has been designed together with Pekka Jääskeläinen, M.Sc., and Lasse Laasonen, M.Sc.. Lasse Laasonen was responsible for the implementation of the program image generator and the processor generator of the codesign environment with support for program compression.

The work reported in this Thesis has been published earlier in six publications [P1–P6]. Therefore, some Chapters contain verbatim extracts from these publications. These extracts are under copyright of respective copyright holders. None of the publications has been used in another person's academic Thesis.

## 1.3 Thesis Outline

Chapter 2 presents the related work on program compression. A detailed survey of the program compression methods proposed for parallel processor architectures is presented. The methods are compared in terms of the defined comparison metrics.

Processor hardware customization is discussed in Chapter 3. An overview of the related work on customizable processor architectures is given. The main objective of

the Chapter is to present the details of the TTA, which is the customizable parallel processor architecture utilized in this Thesis. The Chapter presents also the MOVE framework and TTA Codesign Environment (TCE), which are semi-automatic design methodologies for designing TTA processors. Tools of the MOVE framework were used in this Thesis for designing the TTA processors and compiling the benchmark applications that were used in the evaluation of the compression methodologies on TTA. The designed program compression methodology developed in this Thesis was integrated to the tools of the TCE.

Chapter 4 describes the principles of Huffman coding, dictionary-based compression, and instruction template-based compression and how the methods were utilized on TTA. In addition, the details of the hardware implementations of the dictionary-based and instruction template-based compression methods to evaluate the effects of the compression methods on area and power consumption are presented. Implementation details of the hardware decompressor are also explained.

In Chapter 5, a description of a dictionary extension method to maintain the programmability after compression is given. The results of utilizing the three compression methods to compress program code compiled on TTA processors are presented in Chapter 6. The effectiveness of all the three compression methods is measured in terms of compression ratio. In addition, the results of the hardware implementation of the dictionary-based and instruction template-based compression methods are given. The effects of the proposed dictionary extension method to maintain the programmability on the area, power consumption, and performance are also presented. Chapter 7 concludes the Thesis.

## 2. PROGRAM COMPRESSION

In computer science, compression traditionally refers to data compression, which can be understood as a process of encoding data to save data storage space or reduce transmission bandwidth. Although the data has already been encoded in digital form, i.e., represented in bits, it can often be encoded more effectively using less bits. Data contains usually redundancy that can be removed by using specific encoding algorithms. This reduces the number of bits required to represent the data and, therefore, allows to reduce the cost of the data storage space or communication network as less bits need to be stored or transmitted.

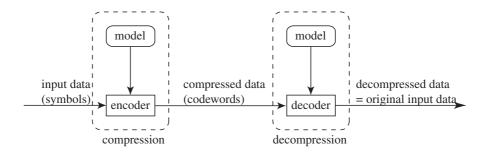

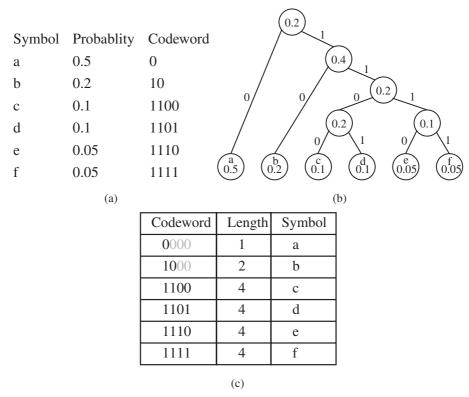

In principle, compression is performed by first forming a model of the data to be compressed and then using this model in the encoder to transform the input data into compressed form. Encoding is done by utilizing the model to transform data units, denoted as symbols, into codewords that represent the original symbols with fewer bits. Symbols can be arbitrary units of data, e.g., a byte, a word, or a cache line. The model typically characterizes statistical properties of the symbols in the input data. For example, a model may represent the probabilities of the symbols in the input data, i.e., how frequently each symbol exists. This information is then utilized to perform the compression, e.g., by assigning variable-width codewords to symbols based on their probabilities of occurrence.

Compressed data cannot be interpreted directly by the receiver of the data as the encoding has changed. Hence, prior to using the compressed data, either fetched from the code storage or transmitted over the communication channel, it has to be decoded back to the format in which the data was originally encoded in. This process is denoted as decompression. An identical model to the one used in the encoding process is required to decode the codewords back to the original symbols that represent the original input data. The compression and decompression phases and the data flow in between these two phases is exemplified in Fig. 1.

Fig. 1. Principle of compressing and decompressing data.

Compression algorithms may be either lossy or lossless. Lossy algorithms trade some loss of data for more effective compression while lossless compression algorithms do not allow any loss of data, i.e., the original data can be perfectly reconstructed when decompression is performed. Lossy algorithms have traditionally been applied for images, audio, and video, where some loss of quality can be tolerated without losing the essential data so that the data can still be perceived. Text compression, on the other hand, requires lossless compression so that the data corresponding to the characters of the text can be perfectly recovered during decompression.

The increased complexity of applications, especially in embedded systems, has lead to an increase in the size of the program code. This has set higher requirements for the code storage space. It has been estimated that the cost of the memory that stores the program code may nowadays be up to 50% of the total cost of the embedded system [39]. Hence, interest has been raised to compress also the program code. Program compression can be considered as a special case of data compression.

Program compression differs from the data compression in the sense that the data to be compressed is not general data. It has a hierarchical structure, which may allow to achieve better compression. Program code consists of instructions that all have a specific structure. Specific information inside the instruction word is in most cases in the same locations among all the instruction words, depending of course on the instruction format. This allows to inspect the data in smaller fragments and find more redundancy that can be removed by applying the compression methods. Furthermore, program code typically uses only a small part of the possible instructions in the instruction set. This property can also be utilized and the instructions can be encoded so that only the actual instructions used in the program code are covered in the compressed program code. This allows to encode the instructions with fewer bits.

Program compression requires also that the compression is lossless. The original representation of the program has to be perfectly reconstructable so that the program can be executed correctly. Another requirement is to guarantee random access decompression, i.e., to allow the decompression to start from any location in the program code or at some block boundaries [78]. As the execution flow may be discontinuous due to branch and jump operations, the decompression has to be capable of starting directly at the branch targets. This requirement is usually guaranteed by compressing the program in blocks inside which the execution flow is continuous, i.e., there are no branch or jump targets within the blocks. The blocks are chosen so that the branch and jump targets are directly at the beginnings of these blocks. Compression blocks need to be aligned to addressable memory locations so that the target instructions can be interpreted directly after the branch or jump has been taken.

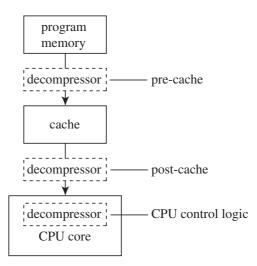

Program compression is typically performed during compile-time. Therefore, the compression speed is of little importance. Decompression, on the other hand, is performed during run-time, so it adds an overhead to the execution time. Decompression is typically performed by a dedicated decompression hardware that is added to the system. Hence, it affects also the hardware cost of the system. The overhead in the execution time due to decompression depends not only on the complexity of the compression algorithm and the implementation of the decompression hardware, but also on the location of the decompressor in the system. The decompressor can be placed in different locations in the system. Usually, the decompressor is placed in between the program memory and the processor core. If the system contains a cache in between the processor core and the program memory, the decompressor can be placed either pre- or post-cache. The decompressor can also be placed inside the processor core. In such a case, decompression is usually performed in between the instruction fetch and decode stages of the instruction pipeline. Figure 2 illustrates the different alternatives for placing the decompressor.

Initially, program compression methods were proposed for single issue processor architectures, such as *reduced instruction-set computers (RISC)*, *complex instruction-set computers (CISC)*, and single-issue *digital signal processors (DSP)*. Later, when parallel processor architectures, such as VLIW, started to gain popularity, program compression methods started to emerge for those architectures as well. Program compression approaches on single-issue and parallel processor architectures are introduced in this Chapter. As this Thesis concentrates on parallel processor architectures

Fig. 2. Alternative locations for the decompressor.

tectures, the compression methods on single-issue processor architectures have been discussed only briefly. The compression methods proposed for parallel processor architectures are discussed in more detail. A comparative analysis of the program compression methods on parallel processor architectures based on the defined compression metrics is also given.

# 2.1 Program Compression on Single-Issue Processor Architectures

The first compression methods on single-issue processor architectures were mostly adaptations of the traditional data compression methods. In one of the earliest approaches [123], Wolfe and Chanin used Huffman coding [50] to compress the instructions of a 32-bit RISC processor architecture. Huffman coding assigns variable-width codewords to the symbols being coded based on their usage frequencies. The most frequent symbols are assigned the shortest codewords and vice versa. The work was extended in [63] by experimenting the Huffman coding on five different 32-bit RISC architectures. Huffman coding on RISC architectures has further been experimented in [36,56,57,75,77,89,119]. Huffman coding has also been applied on DSP architectures in [95].

Another statistical compression method, arithmetic coding [103], has been studied extensively by Lekatsas et. al. on RISC architectures in [76–82]. Arithmetic coding

is similar to Huffman coding as it assigns codewords to symbols based on their usage frequencies. However, arithmetic coding is not limited to integral number of bits as Huffman encoding and can therefore perform better. The drawback of arithmetic coding is its more complex decompression procedure as it requires complex arithmetic operations. Lekatsas et. al. have applied reduced-precision arithmetic coding [49] in their work to replace the complex arithmetic operations with table look-ups to make decompression less compute-intensive and, therefore, better suitable for program compression.

Dictionary-based program compression is another extensively studied program compression method. Dictionary-based compression identifies the unique instructions in the program code and stores them into a dictionary and replaces the occurrences of these instructions in the program code with indices to the dictionary. Dictionary-based compression methodologies have been proposed for RISC architectures in [14, 17–20, 58, 72, 73, 75, 80, 132, 133]. Dictionary-based compression has also been applied on DSP architectures in [26, 84, 85, 112].

Dictionary-based compression can be applied at different symbols granularity levels. In addition to assigning codewords to single instructions, instruction sequences can be considered as symbols to be stored into a dictionary and be replaced with a single dictionary index, as proposed in [27, 53, 71]. Instructions can also be divided to smaller fields inside which unique bit patterns are searched for to be stored into the dictionary [28,74,89,93,98,131]. The division can be made according to the existing fields in the instruction word, i.e., the opcode, operand, and immediate fields, or by dividing instructions arbitrarily to smaller fields, e.g., by dividing a 32-bit instruction to two 16-bit halves.

An adaptive dictionary-based compression scheme, proposed by Ziv and Lempel in [135, 136], has also gained success in program compression. The dictionary is generated adaptively when symbols are encountered. The incoming symbols are replaced with pointers that point to locations where the symbols occurred previously. The methodology proposed by Lempel and Ziv has been adapted and applied on RISC architectures in [15,62,73,75].

The program code size can also be reduced by re-encoding the instructions in the instruction set to be represented with fewer bits. For example, ARM Thumb [16], SH3 [44], and MIPS16 [61] are architectures where the original 32-bit RISC instruc-

tions are re-encoded to 16-bit instructions. This is accomplished by, e.g., restricting the amount of registers the instructions can use as operands. A methodology is usually provided to execute also the original 32-bit wide instructions. Micro RISC [40], Heads and Tails [94], and EISC [70] are further examples of tightly encoded 16-bit RISC architectures. Simonen et. al. have experimented instruction set re-encoding on DSP architectures in mixed 32/16-bit execution mode in [110].

Aside from compressing the already compiled program code, attention can be given to reduce the code size already during the compilation phase. One example of such an alternative is to factor out frequently executed instruction patterns into subroutines and replacing these instructions with calls to the subroutine [32,60,107,113]. Similar methods have also been proposed for DSP architectures in [83,86].

## 2.2 Program Compression on Parallel Processor Architectures

Program compression methods have also been proposed for parallel processor architectures, where the poor code density is even a bigger problem than on single issue processor architectures. Parallel processor architectures typically require a long instruction word to control explicitly each of the concurrently operating hardware resources. This kind of an encoding usually leads to increased size of the program code and, therefore, to poor code density.

As the main topic of this Thesis is program compression on parallel processor architectures, a detailed survey of the proposed compression methods on parallel processor architecture is presented. The objective of the survey is to describe the methods proposed in the literature and provide a comparison between them. Direct comparison of the methods is fairly difficult as the methods have been proposed for different target architectures and the specific features of the architectures are often utilized in the compression methods. Furthermore, in many cases, the required details for direct comparison are not reported, or are reported using different metrics. For example, quantitative comparison between different methods is difficult as there are several ways in which the effectiveness of the method has been presented. Therefore, the comparison of the methods is more feasible when the different aspects are characterized and compared separately.

## 2.2.1 Comparison Metrics

In order to compare the compression methods, some metrics are defined. They try to capture the essential characteristics of the compression methods. The defined metrics to ease the comparison of the program compression methodologies on parallel processor architectures include target architecture, instruction encoding, compression granularity, decompression properties, branch handling, and effectiveness. These metrics are described in more detail in the following.

### Target Architecture

Target architecture defines the details of the processor architecture on which the compression method has been applied on. All of the processor architectures included in the survey belong to the class of very long instruction word architectures that provide more processing power by executing several operations in parallel in concurrently operating function units. Special classes of VLIW architectures included in the survey are the explicitly parallel instruction computing architecture (EPIC), and TTA. TTA is the processor architecture for which program compression methods are developed in this Thesis.

The target architectures can be compared in terms of the degree of available parallelism, i.e., how many operations they can issue in parallel. This has an effect on the size of the program code and also on the effectiveness of the compression method. Parallel processor architectures are typically programmed using a wide instruction word that has dedicated fields for each of the concurrently operating functional resources. Hence, the more parallel resources there are, the wider the instruction word. Figure 3 shows an example of a VLIW instruction word that has three dedicated fields to specify operations for three functional resources. Each field is comprised of the opcode and operand fields that are required to specify a single RISC-type operation.

Most programs contain parallelism that can be exploited by the parallel resources of the architecture. However, programs contain also parts where the data dependencies limit the available parallelism. This results in sequences of instructions where only few of the parallel resources can be utilized. Null values, i.e., no-operations (NOPs) need to be explicitly defined for the unutilized functional resources. The greater the degree of parallelism, the more NOPs need to be defined. This increases the size

| FU-1 field |            |    |     | FU-2 field |        |    |     | FU-3 field |        |    |     |     |

|------------|------------|----|-----|------------|--------|----|-----|------------|--------|----|-----|-----|

|            | opcode   I | RD | RS1 | RS2        | opcode | RD | RS1 | RS2        | opcode | RD | RS1 | RS2 |

Fig. 3. An example of VLIW instruction word. FU-(x): functional unit field. Opcode: Operation code field. RD: Destination register field. RS(y): Source register field.

of the program code. Consequently, this also makes the compression more effective as there are more NOPs that can be exploited in the compression to achieve more compact code.

The degree of parallelism on VLIW and EPIC architectures can be expressed in terms of operation issue-rate, i.e., the number of operations that can be issued in parallel. As TTA has a different programming paradigm, operation issue-rate cannot be used to measure the degree of parallelism. TTA processors are programmed by explicitly specifying the data transports that transport data between functional resources. The number of data transports required to complete a single operation depends on the operation type. A typical three-operand RISC-like operation requires three data transports. On the other hand, jump instruction requires only one data transports. TTA allows also operand bypassing, which means that two operations can share a data transports. Therefore, it is difficult to estimate the operation issue-rate on TTA. A better measure is to express the degree of parallelism in terms of data transport issue-rate, i.e., how many data transports can be issued in parallel.

### Instruction encoding

Instruction encoding in the context of this Thesis defines how the original instructions are encoded into compressed codewords. More accurately, it defines whether the original bit patterns in the program code, e.g., instructions or operations slots, are encoded to fixed- or variable-width codewords. Fixed-width codewords are simple from the instruction fetch and decompression point of view as all the codewords are of same width. Variable-width codewords complicate both the instruction fetch and decompression logic as the width of the codeword is not known during instruction fetch or at the beginning of decompression.

Fixed-width codewords are easy to fetch from the program memory. The codewords can be aligned evenly to the program memory. Usually the instruction fetch packet

can be adjusted to be as wide as a single codeword. This allows to fetch one codeword at a time from the program memory. Decompression is also fairly straightforward as there is no need to first detect the width of the codeword and extract it from the bit stream fetched from the program memory before it can be decompressed. Fixed-width codewords usually result from dictionary-based compression methods. Codewords represent indices that point to unique bit patterns stored into the dictionary. Decompression is simple as the index can be used directly to access the dictionary to obtain the corresponding bit pattern.

Variable-width instructions are more problematic from the instruction fetch and decompression point of view as the codewords are of different width and the width of the codeword is known only during the decompression phase. The instruction fetch packet is usually configured to be as wide as the widest possible compressed instruction word to guarantee that during each clock cycle enough bits are fetched from the program memory to cover an entire compressed instruction word. This guarantees that one instruction word per clock cycle can be decompressed and stalling of the instruction pipeline can thus be avoided. The decompressor becomes also more complicated as the width of the compressed instruction has to be determined before the decompression can be performed. Buffers and shift registers are also needed in order to handle the incoming bit stream and to avoid overflow in case the compressed instruction consumes less bits than have been fetched from the program memory. Variable-width codewords results from the compression methods that utilize the non-uniform probability distribution to encode symbols with variable-width codewords, such as Huffman coding and arithmetic coding.

## Compression granularity

Compression granularity defines the granularity of the bit patterns that are considered as symbols for compression. The granularity level affects directly the possibility to find redundancy, i.e., find repeated bit patterns from the program code. This affects the size of the generated coding tables. The more fine-grained the granularity level, i.e., the smaller the bit patterns that are considered as symbols for compression, the greater the probability to find redundancy from the program code. On the other hand, fine-grained granularity level means that the entire compressed instruction words will be represented with several codewords. This increases the width of the compressed

instruction word and, therefore, also the size of the compressed program code. Higher granularity level leads to less possibilities to find repeated bit patterns from the program code, but on the other hand, to smaller size of the compressed program code as it consists of only a single or a few codewords that correspond to the original bit patterns stored into a coding table.

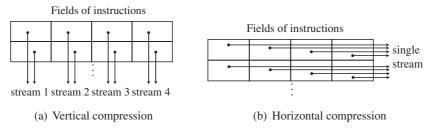

Compression methods included in this survey consider several different granularity levels. The highest granularity level corresponds to entire VLIW-type instruction words. The other more fine-grained levels utilized in the methods include the granularity levels of operation slots, operation slot sequences, opcode fields, and fields of arbitrary size, e.g., bytes that do not correspond to any structural fields of the instruction words.

### Decompressor Implementation

Decompressor implementation defines the location of the decompression hardware in the processor system. The decompressor is in most cases placed outside the processor core, in between the core and the program memory. With the existence of a cache, the decompressor can be placed either pre- or post-cache. The decompressor can also be placed inside the control path of the processor core. Figure 2 already presented the alternative locations of the decompressor. The location of the decompressor affects both the effectiveness of the compression and the performance.

In case the decompressor is placed pre-cache, only the program memory is in compressed form. Instructions are fetched from the program memory during cache miss and decompressed back to the original format before they are placed in the cache. This alternative hides the decompression latency behind the cache miss. Decompression latency is paid only when a cache miss occurs. In post-cache implementation, also the cache is in compressed form. This means that the total size of the code storage in the system is smaller as the size of the cache can be decreases. Decompression is performed when instructions are fetched from the cache and consumed in the processor core. Decompression latency is paid whenever instructions are fetched from the cache. This tends to increase the execution time. However, as the cache contains compressed instructions, more instructions fit in the cache if its size is maintained unchanged. This improves the cache hit ratio and reduces the number of cache misses, i.e., shortens the execution time. The net effect depends on the compression

parameters and the code to be compressed. Hence, there is a tradeoff in between minimizing the size of the code storage space and the performance.

When the decompressor is placed in the control path of the processor core, the complexity of the decompressor may require it to be implemented in a separate pipeline stage in between the instruction fetch and decode stages. The additional pipeline stage increases the depth of the instruction pipeline and, therefore, the branch delay. The increased branch delay is paid only when a branch is taken. In some of the compression approaches the decompression procedure is fairly simple, e.g., only a simple look-up table access in the dictionary-based compression. This allows to integrate the decompressor to the logic of the instruction fetch or decode stage without affecting the clock period too much. In such a case, the performance is maintained as the depth of the instruction pipeline is unchanged.

### Random Access Support

Random access support defines how the change of the execution flow due to branches and jumps can be supported after the program code has been compressed. Random access is maintained if the decompressor can start the decompression process directly from the target instruction after a branch or a jump is executed. Program compression complicates the random access support because the program representation in the program memory is typically changed due to encoding the original instructions with compressed instructions. Change in the program representation means that the addresses of the target instructions have changed. Moreover, the target instructions may end up to be placed in unaddressable locations in the program memory if no instruction alignment is made.

Random access can be typically guaranteed by compressing the program code in blocks inside which the program flow is continuous. The beginnings of the compressed blocks, representing branch and jump targets, have to be aligned to addressable locations in the program memory to guarantee that after a branch or a jump the execution continues immediately from the correct target instruction. This alignment may require some padding bits to be inserted in the program memory before the target instructions. In addition, as the addresses of the instructions in the program memory have changed, some sort of translation between the compressed and uncompressed address spaces is required. One alternative is to modify the branch and jump target

addresses in the instructions to correspond to the target addresses in the compressed address space [71]. Another alternative is to use a *Line Address Table (LAT)* that provides a mapping between the original and the compressed addresses spaces [122].

#### Effectiveness

Effectiveness defines how effectively the size of the program code can be reduced. Effectiveness of a compression method is typically measures in terms of compression ratio, which defines the ratio of the compressed and uncompressed code sizes. Compression ratio has to include also the overhead of the decoding tables that are used in the decompression phase. The decoding tables usually define the model that can be used to decompress the compressed instructions back to the original form. Hence, compression ratio *CR* can be defined as

$$CR = \frac{S_c + S_t}{S_u}$$

where,  $S_c$  is the size of the compressed code,  $S_t$  the size of the decoding tables, and  $S_u$  the size of the uncompressed code.

### 2.2.2 Comparison of Methods

Tables 1- 3 list the proposed compression approaches for parallel processor architectures and present their classification according to the comparison metrics. Table 1 shows the details of the compression method, the target architecture, and the type of instruction encoding used for the methods. Table 2 describes the compression granularity and the decompressor implementation, i.e., the location of the decompressor in the processor system. Table 3 considers the random access support mechanisms and presents statistics on the effectiveness of the compression methods in terms of compression ratio. The table illustrates also whether the presented compression ratio takes into account the decompression overhead, i.e., the size of the decoding table.

The columns in the tables correspond to the comparison metrics that were presented in the previous Section. Each row in the table corresponds to a compression method. Each method is named based on the first author of the publication in which the method is described. Reference to this publication is also given. On few occasions,

**Table 1.** Comparison of the target architecture and instruction encoding of the program compression methods on parallel processor architectures. NA: Not available.

| Method                  |            | Target Architecture        | Instr. enc.     |             |                |

|-------------------------|------------|----------------------------|-----------------|-------------|----------------|

|                         |            |                            |                 | Fixed-width | Variable-width |

| Author                  | Ref.       | Architecture               | Max. issue rate | 臣           | Va             |

| NOP removal             |            |                            |                 |             |                |

| Colwell                 | [29]       | Trace VLIW                 | 28 ops.         |             | X              |

| Conte                   | [30]       | Tinker VLIW                | NA              |             | X              |

| Weiss                   | [118]      | DSP16 VLIW                 | NA              |             | X              |

| Richter                 | [102]      | M3-DSP VLIW                | 16 ops.         |             | x              |

| Starcore                | [1]        | SC 140 VLIW                | 6 ops           |             | X              |

| Texas Instruments       | [3–5]      | TMS320C6x VLIW             | 8 ops.          |             | X              |

| Suzuki                  | [114]      | VLIW                       | 2 ops.          | X           |                |

| Aditya                  | [10]       | VLIW                       | 4-12 ops.       |             | X              |

| Haga                    | [42]       | IA-64 EPIC                 | 6 ops.          |             | x              |

| Heikkinen               | This work  | Move TTA                   | 3-13 trans.     |             | X              |

| Dictionary-based        |            |                            |                 |             |                |

| Nam                     | [92]       | Sparc-based VLIW           | 4-12 ops.       | X           |                |

| Hoogerbugge             | [48]       | TM 1000 VLIW               | 5 ops.          | X           |                |

| Ros                     | [104]      | TMS320C6x VLIW             | 8 ops.          | X           |                |

| Ros                     | [105]      | TMS320C6x VLIW             | 8 ops.          |             | X              |

| Lin                     | [88]       | TMS320C6x VLIW             | 8 ops.          | X           |                |

| Piccinelli              | [97]       | ST200 VLIW                 | 4 ops.          |             | x              |

| Ibrahim                 | [51]       | VLIW                       | NA              | X           |                |

| Heikkinen               | This work  | Move TTA                   | 3-13 trans.     | Х           |                |

| Entropy encoding        |            |                            |                 |             |                |

| Larin                   | [68]       | TEPIC VLIW                 | 6 ops.          |             | X              |

| Xie                     | [125, 126] | TMS320C6x VLIW             | 8 ops.          |             | X              |

| Xie                     | [127]      | TMS320C6x VLIW, IA-64 EPIC | 8 ops., 6 ops.  | X           |                |

| Heikkinen               | This work  | Move TTA                   | 3-13 trans.     |             | x              |

| Instruction set re-enc. |            |                            |                 |             |                |

| Larin                   | [68]       | TEPIC VLIW                 | 6 ops.          |             | X              |

| Biswas                  | [21]       | TMS320C6x VLIW             | 8 ops.          | X           |                |

| Liu                     | [90]       | VLIW                       | 4 ops.          |             | X              |

two or more methods have been combined into a single row due to their tight correspondence between each other. The compression methods in the table are organized into four compression categories based on the general compression principle. Compression approaches inside each category have been arranged based on the year they were published. The compression categories include *NOP removal*, *dictionary-based compression*, *Entropy encoding*, and *instruction set re-encoding*. The compression methods included in the survey are presented in the following Subsections based on the above mentioned compression category classifications.

**Table 2.** Comparison of the compression granularity and decompressor implementation of the program compression methods on parallel processor architectures. PMEM: Program Memory. CPU: Central Processing Unit.

| Method                  |            | Granularity      |                |                         |                    |                        | Decompressor impl. |            |                      |                  |

|-------------------------|------------|------------------|----------------|-------------------------|--------------------|------------------------|--------------------|------------|----------------------|------------------|

| Author                  | Ref.       | Instruction word | Operation slot | Operation slot sequence | Opcodeopcode field | Arbitrary bit sequence | Pre-cache          | Post-cache | Between PMEM and CPU | CPU control path |

| NOP removal             |            |                  |                |                         |                    |                        |                    |            |                      |                  |

| Colwell                 | [29]       |                  | X              |                         |                    |                        | X                  |            |                      |                  |

| Conte                   | [30]       |                  | X              |                         |                    |                        | X                  | X          |                      |                  |

| Weiss                   | [118]      |                  |                | X                       |                    |                        |                    |            |                      | X                |

| Richter                 | [102]      |                  |                | X                       |                    |                        |                    |            |                      | X                |

| Starcore                | [1]        |                  | X              |                         |                    |                        |                    |            |                      | X                |

| Texas Instruments       | [3–5]      |                  | X              |                         |                    |                        |                    |            |                      | X                |

| Suzuki                  | [114]      |                  | X              |                         |                    |                        |                    |            |                      | X                |

| Aditya                  | [10]       |                  | X              |                         |                    |                        |                    |            |                      | X                |

| Haga                    | [42]       |                  | X              |                         |                    |                        |                    |            |                      |                  |

| Heikkinen               | This       |                  | X              |                         |                    |                        |                    |            |                      | X                |

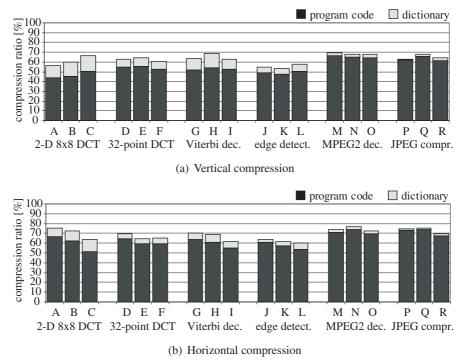

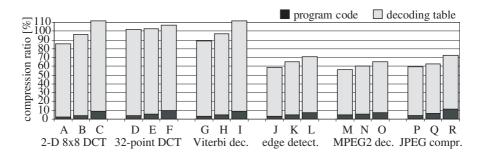

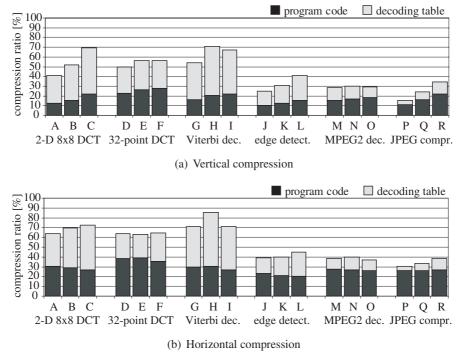

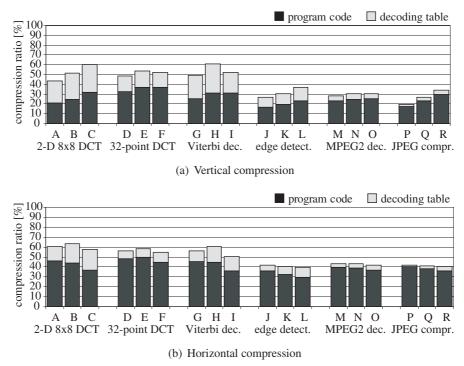

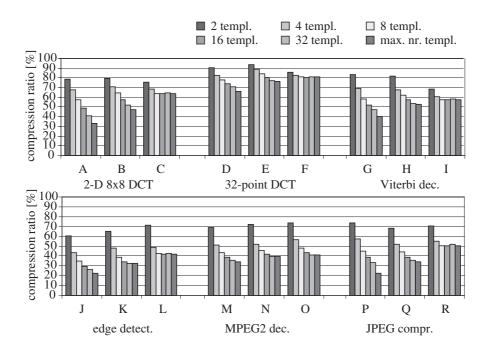

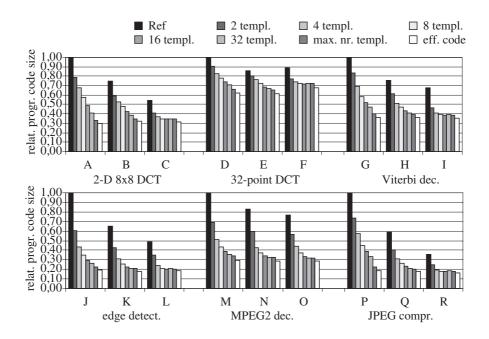

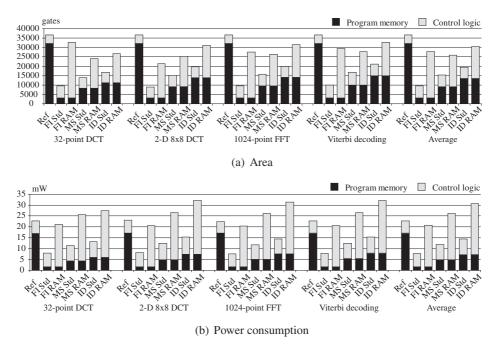

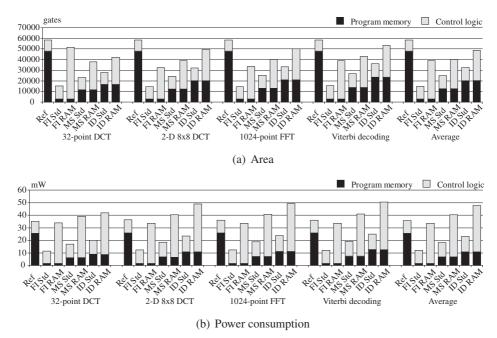

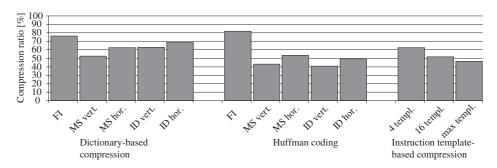

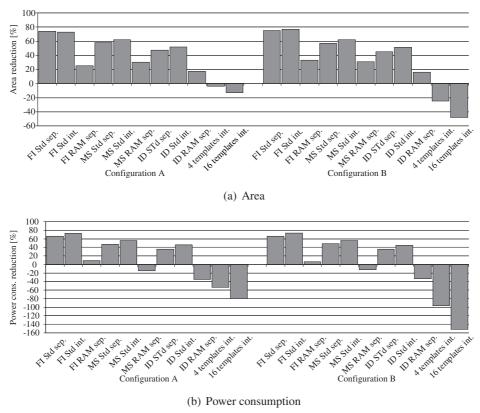

| Dictionary-based        |            |                  |                |                         |                    |                        |                    |            |                      |                  |