Perttu Salmela

Implementations of Baseband Functions for Digital Receivers

Tampereen teknillinen yliopisto. Julkaisu 821 Tampere University of Technology. Publication 821

Perttu Salmela

# Implementations of Baseband Functions for Digital Receivers

Thesis for the degree of Doctor of Technology to be presented with due permission for public examination and criticism in Tietotalo Building, Auditorium TB104, at Tampere University of Technology, on the 7th of August 2009, at 12 noon.

ISBN 978-952-15-2187-4 (printed) ISBN 978-952-15-2210-9 (PDF) ISSN 1459-2045

#### ABSTRACT

With ever higher data rates, the complexity of baseband processing increases basically for two reasons. Firstly, the required processing rate is proportional to the bit rate and, secondly, with higher data rates, more demanding and sophisticated algorithms must be applied. For example, new wireless telecommunications systems like 3G long term evolution (LTE) can have even a 100 Mbps data rate and multipleinput multiple-output (MIMO) transmission methods are applied. Thus, the problem domain of implementation of baseband functions includes both addressing the high computational complexity and describing the implementations in a flexible way so that even complex algorithms can be used without extensive efforts.

In this Thesis, implementations and implementation methods of baseband processing functions are proposed. Computational complexity and flexibility of implementation are approached with application-specific processors (ASP). The computing demands can be met with high parallelism when parallelization of the targeted algorithm is possible, and the software description of the computation possesses flexibility. Especially, the error correction decoding, matrix decomposition, and symbol detection tasks of the baseband processing chain are targeted in this Thesis. Both processor implementations and implementations of assisting hardware units are presented. With all the presented principles and implementations, programmable ASPs are targeted even though other platforms could also be used.

As a result, the essential computational challenges and the design space of wireless receivers is clarified. The work in this Thesis shows how the computation of the addressed baseband functions can be implemented efficiently, and the work shows how they can be implemented when a programmable platform is targeted. The results show that the benefits of the programmability do not sacrifice efficiency of the implementation.

#### PREFACE

The work presented in this Thesis has been carried out in the Department of Computer Systems at Tampere University of Technology during the years 2003–2009 and partially at University of Maryland, College Park in 2006.

I would like to express my gratitude to my supervisor Prof. *Jarmo Takala* for his support, motivation, and efforts to make this research work possible. I would like to thank my thesis Reviewers, Prof. *Holger Blume* and Prof. *Joseph R. Cavallaro*, who provided valuable and insightful comments. Thanks to their constructive comments, this Thesis has achieved its final form. Also, I would like to thank Prof. *Shuvra S. Bhattacharyya* for his efforts to make my exchange visit possible and for his help and guidance in the US. I would like to thank also Prof. *Olli Silvén* for his encouraging support.

My friends and colleagues deserve also special thanks. Especially, the closest colleagues during the research work of this Thesis, *Harri Sorokin*, M.Sc., *Lassi Nurmi*, M.Sc., *Juho Antikainen*, M.Sc., Dr.Tech. *Tuomas Järvinen*, Dr.Tech. *Jari Nikara*, and Dr.Tech. *Vesa Lahtinen* deserve many thanks for many fruitful discussions, observant comments, and motivations. A lot of thanks are given to my colleagues *Pekka Jääskeläinen*, M.Sc., *Teemu Pitkänen*, M.Sc., and *Riku Uusikartano*, M.Sc., for their helpful assistance, constructive comments, and influential enthusiasm. In addition, I wish to express special thanks to Dr.Tech. *Adrian Burian* for his support, ideas, and productive collaboration. The whole research group in University of Maryland, College Park and, especially, Ph.D. *Chung-Ching Shen* and *Ruirui Gu*, M.Sc., deserve many thanks for their assistance and creative atmosphere.

I also want to thank *Teemu Sipilä*, M.Sc., and *Aki Happonen*, M.Sc., for their comments and industrial point of view. Yet, there are still far too many people to name in the Department of Computer Systems, who deserve thanks and with whom this work has been carried out. All the mentioned and many unmentioned people have had a

great influence on this Thesis. Without that influence this work would not have been possible.

This Thesis was financially supported by the Nokia Foundation, the Ulla Tuominen Foundation, the Foundation of Advancement of Technology (TES), and the National Technology Agency of Finland (TEKES). The financial support is appreciated and acknowledged gratefully.

Finally, I express the deepest gratitude to the *Salmela* family and *Hanna* for the support and motivation and to all the friends for their influence on this Thesis.

Tampere, June 11, 2009 Perttu Salmela

### TABLE OF CONTENTS

| Ab  | stract  | •••      |                                                      | i    |

|-----|---------|----------|------------------------------------------------------|------|

| Pre | eface   |          |                                                      | iii  |

| Ta  | ble of  | Conten   | ts                                                   | v    |

| Lis | st of P | ublicati | ons                                                  | xi   |

| Lis | st of F | ligures  |                                                      | xiii |

| Lis | st of T | ables    |                                                      | xix  |

| Lis | st of A | bbrevia  | tions                                                | xxi  |

| Lis | st of S | ymbols   |                                                      | xxv  |

| 1.  | Intro   | duction  |                                                      | 1    |

|     | 1.1     | Scope    | and Objective of Research                            | 3    |

|     | 1.2     | Main C   | Contributions                                        | 4    |

|     | 1.3     | Author   | 's Contribution                                      | 5    |

|     | 1.4     | Thesis   | Outline                                              | 6    |

| 2.  | Rece    | eiver Mo | odel and Processor Template                          | 7    |

|     | 2.1     | System   | n Model                                              | 7    |

|     |         | 2.1.1    | Orthogonal Frequency Division Multiplexing           | 8    |

|     |         | 2.1.2    | Symbol Detection                                     | 9    |

|     |         | 2.1.3    | Forward Error Correction                             | 10   |

|     | 2.2     | Transp   | ort Triggered Architecture Processor Implementations | 13   |

|     |         | 2.2.1    | Programming TTA Processors                           | 16   |

|    |      | 2.2.2    | Developing TTA Processor Applications                                     | 17 |

|----|------|----------|---------------------------------------------------------------------------|----|

|    |      | 2.2.3    | Multiprocessor Systems with TTA Processors                                | 18 |

| 3. | Spec | ial Func | ction Units for Viterbi Decoding                                          | 21 |

|    | 3.1  | Viterbi  | Decoding Principles                                                       | 21 |

|    | 3.2  | Previou  | us Work                                                                   | 22 |

|    | 3.3  | Special  | l Function Units                                                          | 23 |

|    |      | 3.3.1    | Add Compare Select Unit                                                   | 23 |

|    |      | 3.3.2    | Branch Metric Generation Unit                                             | 24 |

|    |      | 3.3.3    | Path Metrics Packing Unit                                                 | 25 |

|    |      | 3.3.4    | Address Generation Unit                                                   | 26 |

|    | 3.4  | Viterbi  | Decoder Implementation                                                    | 27 |

|    |      | 3.4.1    | Decoder Program                                                           | 28 |

|    |      | 3.4.2    | Discussion                                                                | 29 |

| 4. | Mult | tiplexed | ACSUs for Max-Log-MAP Computation                                         | 33 |

|    | 4.1  | Paralle  | lism and Throughput                                                       | 33 |

|    | 4.2  | Max-L    | og-MAP Algorithm                                                          | 34 |

|    | 4.3  | Re-Org   | ganized Forms for Efficient Resource Mapping                              | 35 |

|    |      | 4.3.1    | Example with 3GPP Constituent Code                                        | 37 |

|    | 4.4  | Decodi   | ing with Modified ACSUs                                                   | 41 |

|    |      | 4.4.1    | Modified Add Compare Select Unit                                          | 41 |

|    |      | 4.4.2    | Decoding Example                                                          | 41 |

|    | 4.5  | -        | I Function Units for an ASP Implementation of Max-Log-MAP         Decoder | 44 |

|    |      | 4.5.1    | Multiplexed ACSUs and Forward Metric Stack SFU                            | 44 |

|    |      | 4.5.2    | Branch Metric Computation SFU                                             | 48 |

|    |      | 4.5.3    | Applying the SFUs in Turbo Decoder TTA Processor                          | 50 |

| 5. | Spec  | ial Func | tion Units for Stage-Parallel Turbo Decoding            | 55 |

|----|-------|----------|---------------------------------------------------------|----|

|    | 5.1   | Previou  | us Work                                                 | 55 |

|    | 5.2   | Special  | Function Units for Kernel Computations                  | 56 |

|    |       | 5.2.1    | Forward Computation SFU                                 | 57 |

|    |       | 5.2.2    | Backward Computation SFU                                | 58 |

|    |       | 5.2.3    | Branch Metric Computation SFU                           | 58 |

|    | 5.3   | Turbo I  | Decoder Processor                                       | 61 |

|    |       | 5.3.1    | Address Generation SFU                                  | 63 |

|    |       | 5.3.2    | Control SFU                                             | 63 |

|    |       | 5.3.3    | Turbo Decoder Program                                   | 65 |

|    |       | 5.3.4    | Performance and Complexity                              | 66 |

|    | 5.4   | Compa    | rison of Turbo Decoder Implementations                  | 67 |

|    |       | 5.4.1    | Scaling and Processing without SFUs                     | 70 |

| 6. | Paral | llel Men | nory Access in Turbo Decoders                           | 73 |

|    | 6.1   | Princip  | les of Extrinsic Information Memory Accesses            | 73 |

|    |       | 6.1.1    | 3GPP Turbo Coding Interleaver                           | 76 |

|    | 6.2   | Previou  | us Work                                                 | 77 |

|    | 6.3   | Paralle  | Memory Structure for 3GPP Turbo Decoding                | 78 |

|    |       | 6.3.1    | Proposed Structure                                      | 79 |

|    |       | 6.3.2    | Area of Memory Configurations                           | 80 |

|    | 6.4   | Branch   | Metric Buffering                                        | 81 |

|    | 6.5   |          | ic Information Memory Access with Buffered Write Opera- |    |

|    |       | tions .  |                                                         | 83 |

|    |       | 6.5.1    | Parallel Memory Access Method                           | 83 |

|    |       | 6.5.2    | Operation with 3GPP Interleaving Pattern                | 86 |

|    | 6.6  | Discus   | sion                                                | 86  |

|----|------|----------|-----------------------------------------------------|-----|

|    | 6.7  | 3G LT    | E Interleaving Sequence Generation                  | 87  |

|    |      | 6.7.1    | Previous Work                                       | 87  |

|    |      | 6.7.2    | Problem Definition                                  | 89  |

|    |      | 6.7.3    | Modulo in Limited Domain                            | 89  |

|    |      | 6.7.4    | Modulo of High-Degree Polynomials                   | 90  |

|    |      | 6.7.5    | Hardware Implementations                            | 93  |

|    |      | 6.7.6    | Case Study on 3G LTE Interleaver                    | 95  |

| 7. | Inve | rse Squa | are Root Approximation and QR Decomposition         | 99  |

|    | 7.1  | Low-C    | Complexity Inverse Square Root Approximation        | 99  |

|    |      | 7.1.1    | Previous Work                                       | 99  |

|    |      | 7.1.2    | Low-Complexity Approximation Method                 | 100 |

|    |      | 7.1.3    | Inverse Square Root Unit Implementations            | 104 |

|    |      | 7.1.4    | Comparison                                          | 106 |

|    | 7.2  | QR De    | ecomposition                                        | 109 |

|    |      | 7.2.1    | Previous Work                                       | 109 |

|    |      | 7.2.2    | Modified Gram-Schmidt QR Decomposition              | 110 |

|    |      | 7.2.3    | Application-Specific Processor for QR Decomposition | 111 |

|    |      | 7.2.4    | Throughput and Complexity                           | 112 |

| 8. | List | Process  | ing for Symbol Detection                            | 115 |

|    | 8.1  | List Pr  | rocessing in List Sphere Decoding                   | 115 |

|    | 8.2  | Memo     | ry-Based List Updating for List Sphere Decoders     | 116 |

|    |      | 8.2.1    | List Updating with Heap Data Structure              | 116 |

|    |      | 8.2.2    | List Updating Special Function Units                | 119 |

|    |      | 8.2.3    | Resource Requirements and Performance               | 123 |

|     | 8.3    | Registe   | er-Based List Updating for List Sphere Decoders        | 126 |

|-----|--------|-----------|--------------------------------------------------------|-----|

|     |        | 8.3.1     | Insertion Sort SFU                                     | 127 |

|     |        | 8.3.2     | Comparisons with Binary Tree                           | 128 |

|     |        | 8.3.3     | Comparisons with High Parallelism                      | 129 |

|     |        | 8.3.4     | Power and Complexity Estimates                         | 130 |

| 9.  | Com    | plexity a | and Power Estimations of Baseband Processing with ASPs | 133 |

|     | 9.1    | System    | Model                                                  | 134 |

|     | 9.2    | Process   | sing Requirements and Complexity                       | 135 |

|     |        | 9.2.1     | Time and Throughput Requirements                       | 135 |

|     |        | 9.2.2     | Required Number of Clock Cycles                        | 135 |

|     |        | 9.2.3     | Number of Processors                                   | 137 |

|     |        | 9.2.4     | Delay                                                  | 138 |

|     |        | 9.2.5     | ASP Configurations as Functions of Clock Frequency     | 139 |

|     |        | 9.2.6     | Analysis                                               | 140 |

|     |        | 9.2.7     | Memory Requirements                                    | 144 |

|     |        | 9.2.8     | Inter-Processor Communication Requirements             | 145 |

| 10. | Conc   | clusions  |                                                        | 147 |

|     | 10.1   | Possibl   | e Future Trends of Baseband Processing Implementations | 147 |

| Bil | bliogr | aphy      |                                                        | 149 |

Table of Contents

\_\_\_\_

#### LIST OF PUBLICATIONS

This Thesis is a monograph, which contains some unpublished material, but is mainly based on the following publications. In the text, these publications are referred to as [P1], [P2],..., and [P9].

- [P1] P. Salmela, J. Antikainen, T. Pitkänen, O. Silvén, and J. Takala, "3G long term evolution baseband processing with application-specific processors," *International Journal of Digital Multimedia Broadcasting*, Vol 2009, Article ID 503130, 13 p., 2009.

- [P2] P. Salmela, H. Sorokin, and J. Takala, "A programmable max-log-MAP turbo decoder implementation," *VLSI Design*, Vol. 2008, Article ID 319095, 17 p., 2008.

- [P3] P. Salmela, H. Sorokin, and J. Takala, "Low-complexity polynomials modulo integer with linearly incremented variable," in *Proceedings of the IEEE Workshop on Signal Processing Systems*, Washington D.C., USA, Oct. 8–10, 2008, pp. 251–256.

- [P4] P. Salmela, A. Burian, H. Sorokin, and J. Takala, "Complex-valued QR decomposition implementation for MIMO receivers," in *Proceedings of the IEEE International Conference on Acoustics, Speech, and Signal Processing*, Las Vegas, NV, USA, Mar. 30–Apr. 4, 2008, pp. 1433–1346.

- [P5] P. Salmela, J. Antikainen, O. Silvén, and J. Takala, "Memory-based list updating for list sphere decoders," in *Proceedings of the IEEE Workshop on Signal Processing Systems*, Shanghai, China, Oct. 17–19, 2007, pp. 633– 638.

- [P6] P. Salmela, R. Gu, S. S. Bhattacharyya, and J. Takala, "Efficient parallel memory organization for turbo decoders," in *Proceedings of the 15th Euro-*

*pean Signal Processing Conference*, Poznan, Poland, Sept. 3–7, 2007, pp. 831–835.

- [P7] P. Salmela, T. Järvinen, and J. Takala, "Simplified max-log-MAP decoder structure," in *Proceedings of SympoTIC'06 the Joint IST Workshop on Sensor Network & Symposium on Trends in Communications*, Bratislava, Slovakia, June 24–27, 2006, pp. 10–13.

- [P8] P. Salmela, T. Järvinen, T. Sipilä, and J. Takala, "256-state rate 1/2 Viterbi decoder on TTA processor," in *Proceedings of IEEE 16th International Conference on Application-specific Systems, Architectures and Processors*, Samos, Greece, July 23–25, 2005, pp. 370–375.

- [P9] P. Salmela, T. Järvinen, T. Sipilä, and J. Takala, "Parallel memory access in turbo decoders," in *Proceedings of the IEEE Symposium on Personal, Indoor, and Mobile Radio Communications*, Beijing, China, Sept. 7–10, 2003, pp. 2157–2161.

## LIST OF FIGURES

| 1 | A high-level block diagram showing the position of baseband func-<br>tions in wireless digital transmission system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4  |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

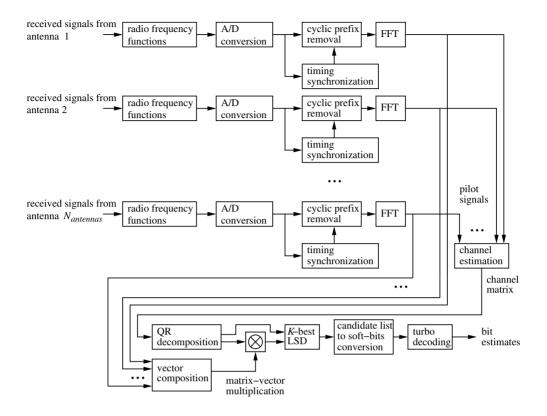

| 2 | A simplified block diagram of baseband processing of a MIMO-<br>OFDM receiver using $K$ -best LSD for symbol detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8  |

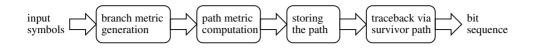

| 3 | The Viterbi decoding consists of four loosely distinct computation phases                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 11 |

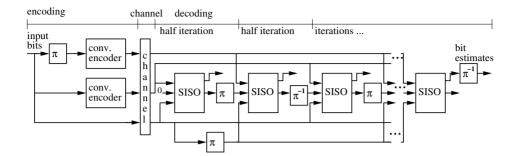

| 4 | Turbo encoding and decoding. The decoding is an iterative process, which runs SISO component decoder several times. Interleaving and de-interleaving are denoted with $\pi$ and $\pi^{-1}$ , respectively                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 12 |

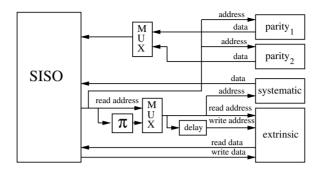

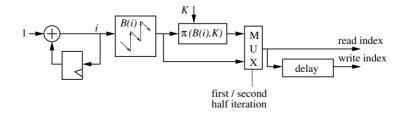

| 5 | Practical decoder requires SISO component decoder, interleaved ad-<br>dress generation, and memories. Extrinsic information memory is<br>both read and written.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 13 |

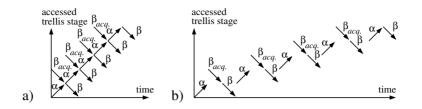

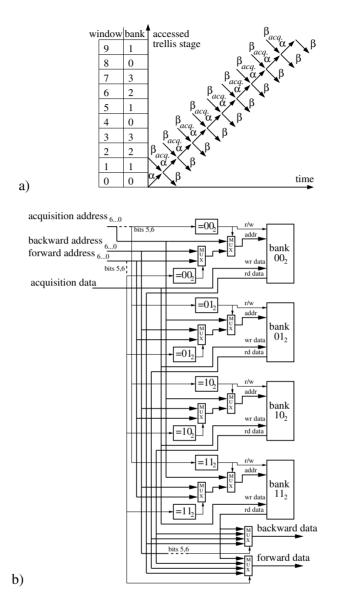

| 6 | Schedules for sliding window algorithm: a) stage-parallel schedule applies three parallel processes, b) one process runs at a time in partial-stage schedule. Initialization of backward metrics with acquisition process is denoted with $\beta_{acq.}$ , backward computation with $\beta$ , forward computation with $\alpha$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 14 |

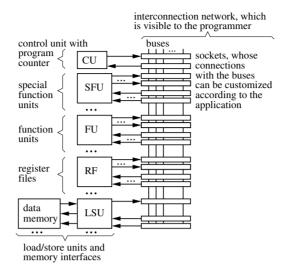

| 7 | TTA processors consist of control unit (CU), function units (FU), special FUs (SFU), load/store units (LSU), register files (RF), and an interconnection network between the resources.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15 |

| 8 | Principles of software pipelining: a) an example loop consisting of operations A, B, C, and D, b) pipelined iterations are mapped to function units $FU_{03}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 17 |

|   | $\mathbf{u}_{0} \mathbf{u}_{0} \mathbf$ | 1/ |

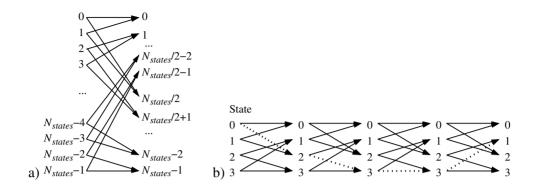

| 9  | Trellis diagrams: a) an example of $N_{states}$ -state trellis shows valid state transitions. b) An example path via states 0, 2, 3, 3, and 1 of a 4-state trellis is shown.                                                                                                                                                                                                                                                                                                                                                  | 22 |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

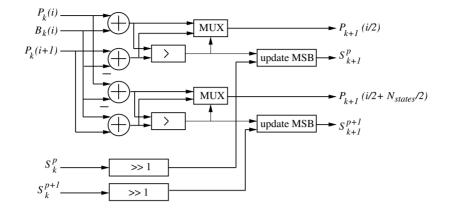

| 10 | Radix-2 ACSU with single branch metric, $B_k(i)$ , input and survivor<br>path information, $S_k^p$ , update circuit. The path metrics are denoted<br>with $P_k(i)$ and right shift with >> 1                                                                                                                                                                                                                                                                                                                                  | 24 |

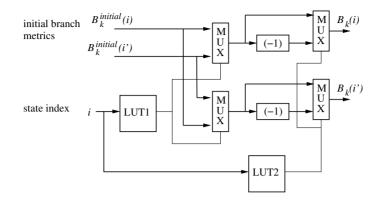

| 11 | Branch metrics are generated by selecting the metric corresponding to the transmitted symbol according to the index of the ACS operation. Negating the value is denoted with $(-1)$ .                                                                                                                                                                                                                                                                                                                                         | 25 |

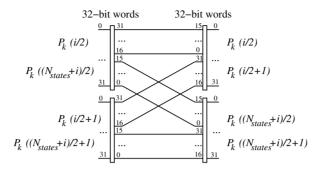

| 12 | Path metrics packing SFU alleviates efficient usage of 32-bit load and store operations.                                                                                                                                                                                                                                                                                                                                                                                                                                      | 26 |

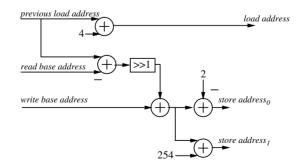

| 13 | Address generation unit generates one load address and two store addresses. Right shift is denoted with $>> 1$                                                                                                                                                                                                                                                                                                                                                                                                                | 26 |

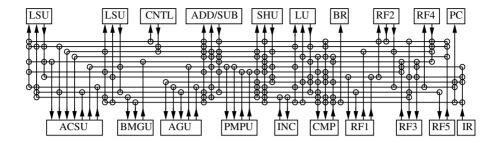

| 14 | Viterbi decoder TTA processor. Controllable connections between<br>resources and buses are denoted with circles. AGU: address genera-<br>tion unit, BMGU: branch metric generation unit, PMPU: path metric<br>packing unit, LSU: load store unit, CNTL: status word, ADD/SUB:<br>addition and subtraction, SHU: left and right shifting, LU: logical op-<br>erations, CMP: comparison, INC: increment by one, BR: boolean reg-<br>ister, PC: program counter, IR: long immediate register, RF1RF5:<br>integer register files. | 27 |

| 15 | Pseudo code of the core decoder program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 28 |

| 16 | Pseudo assembly code of the main loop kernel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 29 |

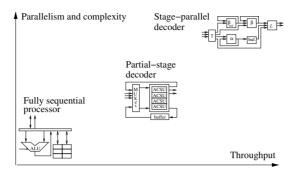

| 17 | The throughput increases as parallel computing resources are increased<br>until a component decoder processing one trellis stage in one clock<br>cycle is achieved.                                                                                                                                                                                                                                                                                                                                                           | 34 |

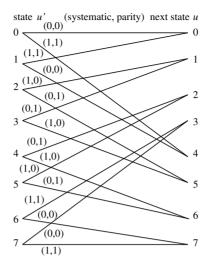

| 18 | Trellis of eight state 3GPP constituent code. Transmitted systematic<br>and parity bit pairs $(x^s, x^p)$ correspond with state transitions of the<br>component encoder.                                                                                                                                                                                                                                                                                                                                                      | 37 |

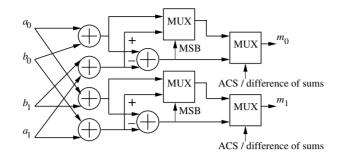

| 19 | Proposed ACSU can compute difference of sums                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 41 |

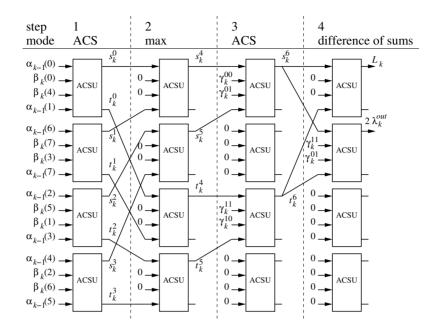

| 20 | Soft output, $L_k$ , and extrinsic information, $\lambda_k^{out}$ , can be computed within four steps with the proposed ACSUs.                                                                                                                                                                                                                                                                                                                                                                                            | 42 |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

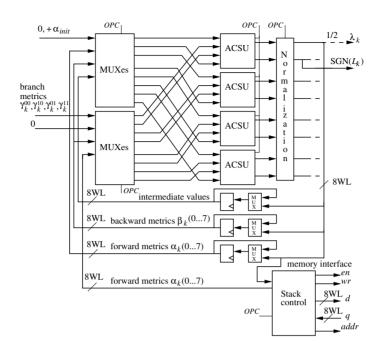

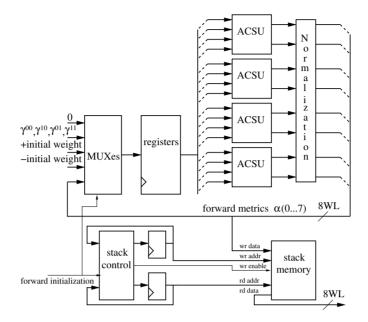

| 21 | Multiplexed ACSUs and interface to the forward metric stack. Division by two is denoted with 1/2 and word length with WL                                                                                                                                                                                                                                                                                                                                                                                                  | 44 |

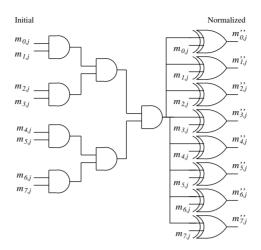

| 22 | Applied normalization method. The <i>j</i> th bit of the <i>i</i> th path metric is denoted with $m_{i,j}$ . The same structure is repeated for those <i>j</i> th path metrics bits, whose normalization is targeted.                                                                                                                                                                                                                                                                                                     | 47 |

| 23 | Branch metric computation and memory interfaces SFU. The inter-<br>leaver memory is denoted with $\pi$ .                                                                                                                                                                                                                                                                                                                                                                                                                  | 49 |

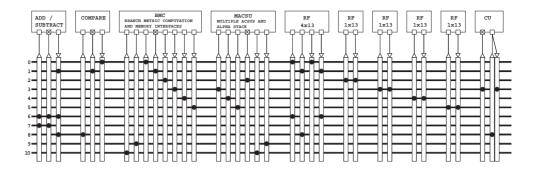

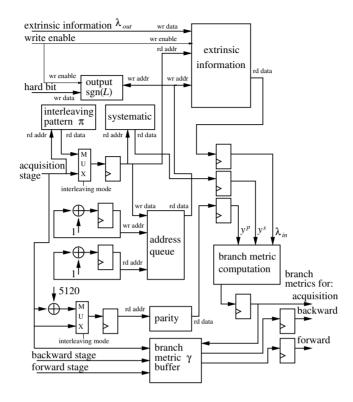

| 24 | TTA turbo decoder processor. Connections between FUs and buses<br>are denoted with filled circles. The external memory banks are inter-<br>faced with branch metric computation, BMC, and multiplexed ACSUs,<br>MACSU, SFUs. The control unit is denoted with CU                                                                                                                                                                                                                                                          | 51 |

| 25 | High-level turbo decoder program flow. Parallelism is denoted with $ $   and $\pi$ presents the flag indicating interleaved access                                                                                                                                                                                                                                                                                                                                                                                        | 52 |

| 26 | Forward path metric SFU with four ACSUs. The unit interfaces an external stack memory. Word length is denoted with WL                                                                                                                                                                                                                                                                                                                                                                                                     | 57 |

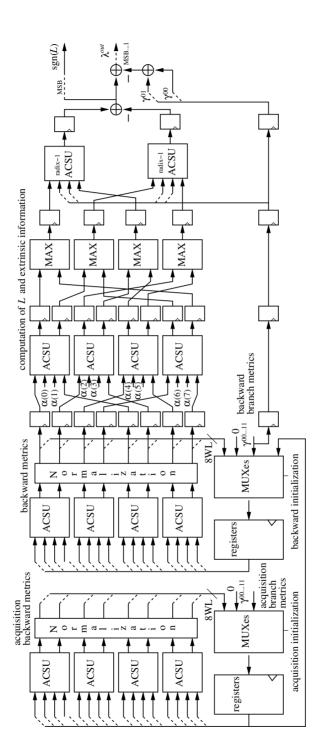

| 27 | Backward computation SFU contains several stages for acquisition<br>of path metrics, computation of valid backward path metrics, and<br>computation of extrinsic information, $\lambda_k^{out}$ , and hard output, $\operatorname{sgn}(L_k)$ .<br>Word length of path metrics is denoted with WL.                                                                                                                                                                                                                         | 59 |

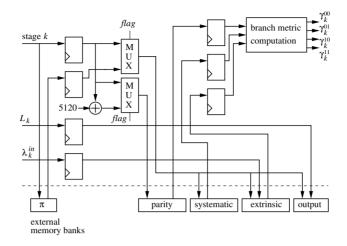

| 28 | Branch metric computation unit interfaces external output, extrinsic information, systematic bit, parity bit, interleaver, address queue, and branch metric buffer memories.                                                                                                                                                                                                                                                                                                                                              | 60 |

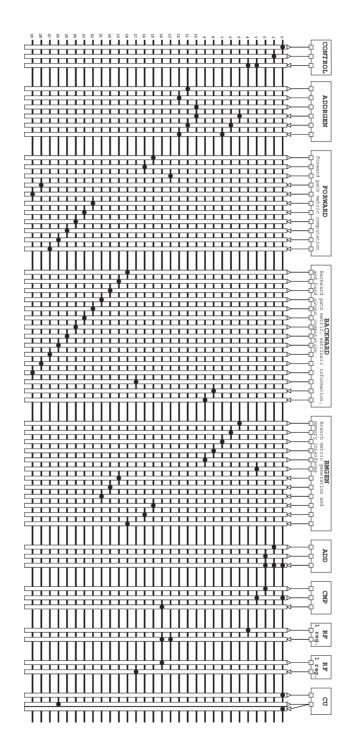

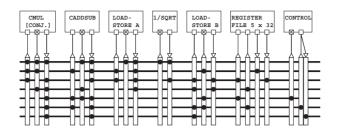

| 29 | TTA turbo decoder processor. Filled circles denote connections be-<br>tween resources and buses. CONTROL: generation of control word<br>for SFUs, ADDRGEN: address generation, FORWARD forward path<br>metric computation and stack memory interface, BACKWARD: acqui-<br>sition, backward path metric, extrinsic information, and hard output<br>computations, BMGEN: branch metric buffering and memory inter-<br>faces, ADD: addition unit, CMP: comparison unit, RF: register file,<br>CU: program flow control unit. | 62 |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 04 |

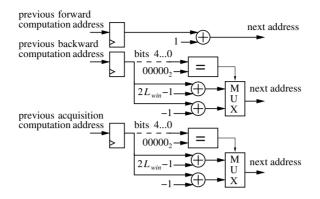

| 30 | Address generation SFU generates one sequential and two sawtooth pattern address sequences. Length of the sliding window is denoted with $L_{win}$ .                                                                                                                                                                                   | 64 |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

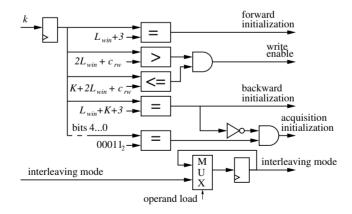

| 31 | Control SFU evaluates several conditions in parallel and generates<br>control word for the other SFUs. Length of sliding window is de-<br>noted with $L_{win}$ , distance between extrinsic information read and<br>write operations with $2L_{win} + c_{rw}$ , and code block length with K.<br>Input k is the current trellis stage. | 64 |

| 32 | High-level program flow of the turbo decoder. Parallelism is denoted with $   $ . Code block length and window length are denoted with $K$ and $L_{win}$ , respectively                                                                                                                                                                | 65 |

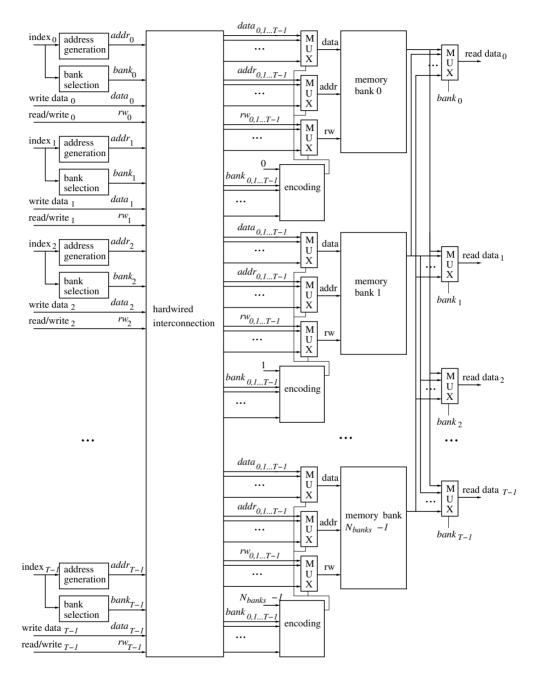

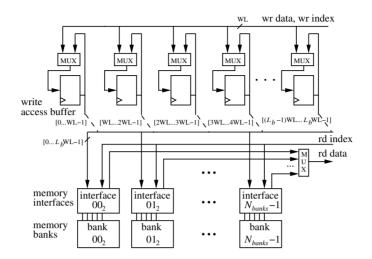

| 33 | General parallel memory bank structure with $T$ parallel access inter-<br>faces and $N_{banks}$ memory banks. The encoding unit selects <i>address</i> ,<br><i>data</i> , and <i>rw</i> signals of that interface which has selected the respec-<br>tive bank                                                                          | 74 |

| 34 | Access sequence of the extrinsic information is based on the sawtooth pattern.                                                                                                                                                                                                                                                         | 75 |

| 35 | Generation of read and write indexes of linear access sequence and interleaved access sequence.                                                                                                                                                                                                                                        | 75 |

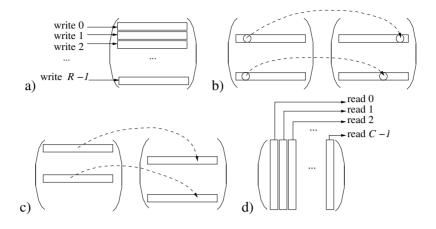

| 36 | 3GPP interleaving: a) the interleaving matrix is filled row-wise, b) intra-row permutations are applied, c) inter-row permutation is applied, and d) the matrix is read column-wise                                                                                                                                                    | 77 |

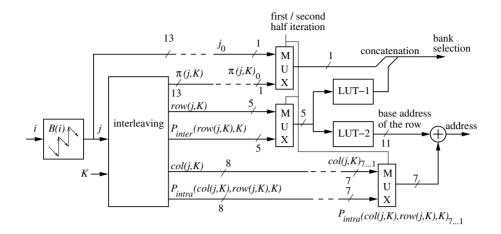

| 37 | Proposed structure for interleaved and linear access sequences. The word length of the output of the LUT-1 depends on the number of banks.                                                                                                                                                                                             | 80 |

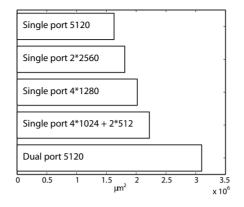

| 38 | Required area for different memory configurations.                                                                                                                                                                                                                                                                                     | 81 |

| 39 | Buffering of branch metrics: a) mapping the accessed windows to four memory banks, b) structure of memory interface with four banks.                                                                                                                                                                                                   | 82 |

| 40 | Proposed memory structure with buffered write operations. Word length of data and address pair is denoted with WL. Indices in brackets index the bus connected to the $L_b$ length buffer.                                                                                                                                             | 84 |

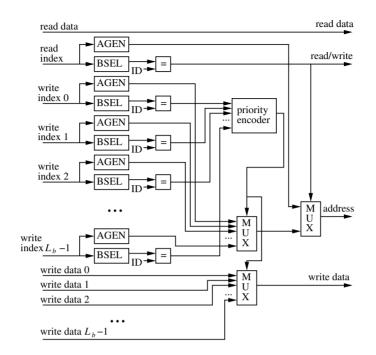

| 41 | Memory bank interface. Length of the buffer is denoted with $L_b$<br>and address generation and bank selection with AGEN and BSEL,<br>respectively. The ID refers to the number of the interfaced bank.<br>Write index and data signals are connected to the respective elements<br>of the buffer | 85        |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

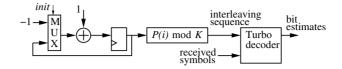

| 42 | Targeted number generator applied for interleaving sequence genera-                                                                                                                                                                                                                               | 89        |

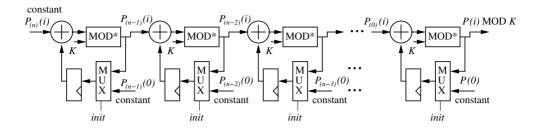

| 43 | A general structure for computing modulo of a polynomial with lin-<br>early incremented variable. The structure consists of systematically<br>repeated computing elements.                                                                                                                        | 94        |

| 44 | Structures of: a) elementary block for structures computing the mod-<br>ulo of polynomials, b) computing element for $x \mod^* K$ , and c)<br>elementary block capable of computing $x \mod K$ iteratively. The<br>dashed line denotes an optional output signal                                  | 94        |

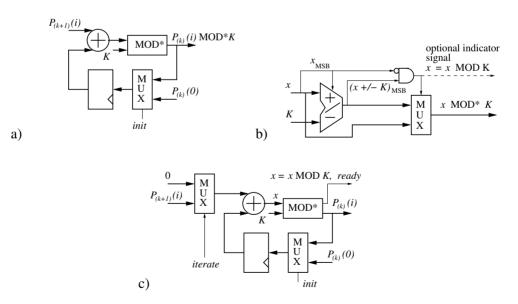

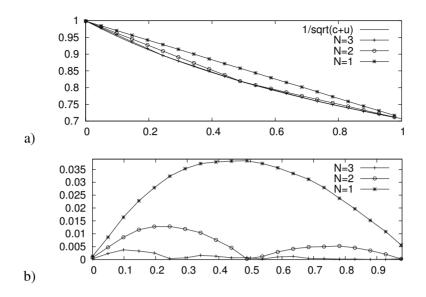

| 45 | Linear approximation of $1/\sqrt{c+u}$ : a) approximating lines, b) approximation error decreases as N is increased                                                                                                                                                                               | 103       |

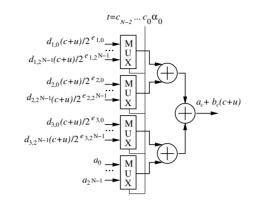

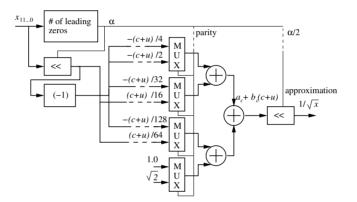

| 46 | Units for: a) linear approximation with $a_t - b_t(c+u)$ , b) approximation of $1/\sqrt{x}$ in subunitary domain, c) approximation in non-<br>subunitary domain. Left and right shifting are denoted with $<<$ and $>>$ , respectively. Negating is marked with $(-1)$ .                          | 105       |

| 47 | Modified Gram-Schmidt algorithm decomposes $H_{n \times n}$ to the orthog-<br>onal $Q_{n \times n}$ and upper triangular $R_{n \times n}$ . Conjugated transpose is de-<br>noted with $(\cdot)^{H}$                                                                                               | 111       |

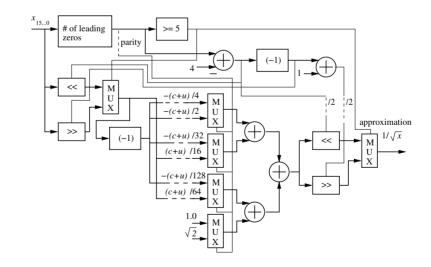

| 48 | Proposed TTA processor for QR decomposition has LSUs, RF, SFU for the approximation of $1/\sqrt{x}$ , and SFUs for complex-valued addition, subtraction, and optionally conjugated multiplication. Filled circles denote connections to buses.                                                    | 112       |

| 49 | An example of heap data structure. Addresses are marked in square boxes and data in rounded boxes                                                                                                                                                                                                 | 117       |

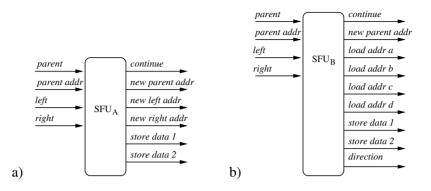

| 50 | List updating SFUs for: a) non-pipelined execution, b) software pipeline execution.                                                                                                                                                                                                               | ed<br>120 |

| 51 | Functional description of SFUs for: a) non-pipelined execution, b) software pipelined execution.                                                                                                                                                      | 121       |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 52 | In software pipelined version all the participating units, the SFU and LSUs with load (LD) and store (ST) operations run in parallel                                                                                                                  | 122       |

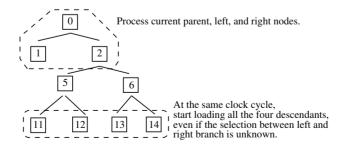

| 53 | Prefetching loads four descendants, from which only two will be selected. Selection decision will be available at the next clock cycle.                                                                                                               | 122       |

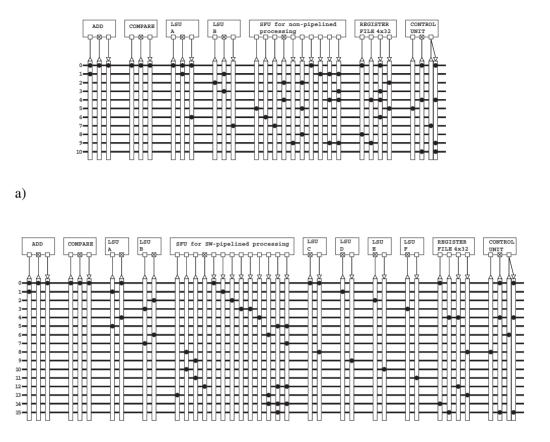

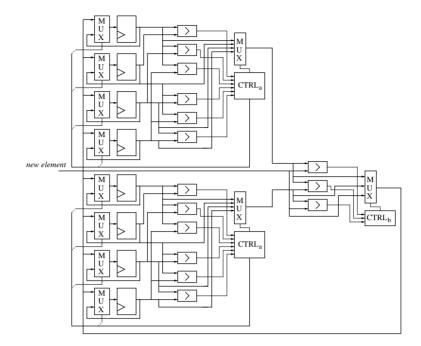

| 54 | TTA processors which are capable of exploiting the proposed SFUs:<br>a) processor for non-pipelined processing, b) processor for software<br>pipelined processing. The memory is accessed with LSUs. Filled<br>circles denote connections with buses. | 124       |

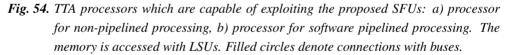

| 55 | Comparison of list processing methods: a) throughput, b) area-efficience as throughput / area of SFUs and accompanying LSUs.                                                                                                                          | су<br>125 |

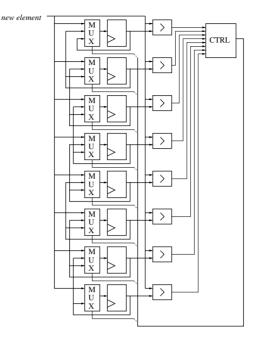

| 56 | Register based insertion sort SFU. The registers contain the sorted list after the insertion operation.                                                                                                                                               | 127       |

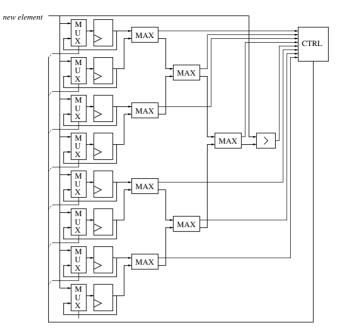

| 57 | List processing SFU applying a binary tree of comparisons to find the maximum value                                                                                                                                                                   | 128       |

| 58 | List processing SFU applying more parallelism in comparisons                                                                                                                                                                                          | 129       |

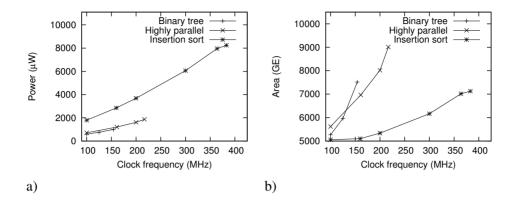

| 59 | Comparison of register based list units with 16-length list: a) power consumption, b) area in terms of logic GEs.                                                                                                                                     | 130       |

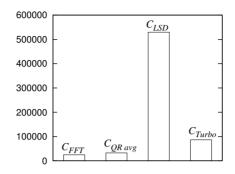

| 60 | Required number of clock cycles for processing the tasks in $T_{\text{FFT}} = 71 \ \mu \text{s}$ time frame.                                                                                                                                          | 137       |

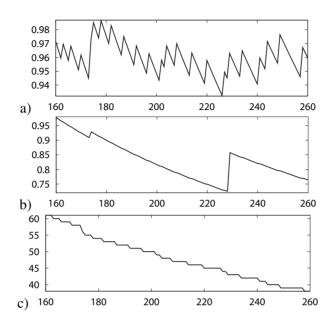

| 61 | Configurations as functions of $f_i$ with single clock domain: a) total utilization, b) total delay in ms, c) the number of processors. The x-axis denotes $f_i$ in MHz.                                                                              | 139       |

|    |                                                                                                                                                                                                                                                       |           |

## LIST OF TABLES

| 1  | Characteristics of the SFUs and Viterbi decoder TTA processor with 100 MHz clock frequency.                                                                                            | 28  |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2  | Radix-2 ACS computations with different processor architectures                                                                                                                        | 30  |

| 3  | Computation of accelerated functions with conventional operations.                                                                                                                     | 31  |

| 4  | Internal utilization of the computing resources of four ACSUs in max-log-MAP decoding example.                                                                                         | 43  |

| 5  | Operation codes of the multiplexed ACSUs SFU                                                                                                                                           | 46  |

| 6  | Sizes of external memory banks with 5120 length code block. The length of the sliding window is denoted with $L_{win}$ .                                                               | 50  |

| 7  | Area as GEs and throughput of the turbo decoder TTA processor.                                                                                                                         | 53  |

| 8  | External memory banks. Turbo code block length is 5120                                                                                                                                 | 61  |

| 9  | Complexity and throughput of the turbo decoder TTA processor                                                                                                                           | 66  |

| 10 | Comparison of turbo decoder implementations. The proposed ASPs are denoted with Chapter 4 and Chapter 5                                                                                | 68  |

| 11 | Modes of the addition/subtraction unit and the multiplexer of $x \mod^* K$ computing element.                                                                                          | 95  |

| 12 | Complexity in terms of logic kGEs of the proposed 3G LTE con-<br>forming interleaving function unit and complexity of elementary op-<br>erations for a straightforward implementation. | 97  |

| 13 | Estimated area of basic units and LUTs in compared implementations.                                                                                                                    | 106 |

| 14 | Suggestive comparison of inverse square root methods                                                                                                                                   | 107 |

| 15 | Area of the proposed processor and execution time of 2048 QR de-<br>compositions.                                                                                            | 113 |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 16 | The baseband processing chain with TTA processors, $2 \times 2$ antennas, 1201 subcarriers, 64-QAM, 6144-length turbo code block, list length $n = 16$ , data rate 100 Mbps. | 141 |

| 17 | An example baseband processing chain with $2 \times 2$ antennas, 1201 subcarriers, 16-QAM, 4804-length turbo code block, data rate 68 Mbps.                                  | 142 |

| 18 | An example baseband processing chain with $4 \times 4$ antennas, 601 subcarriers, 16-QAM, 4808-length turbo code block, list length $n = 10$ , data rate 68 Mbps.            | 142 |

| 19 | Requirements of 4G baseband processing chain for 100 Mbps data rate [133].                                                                                                   | 143 |

| 20 | Area of the core processor without memories and data memory re-<br>quirements of the processors                                                                              | 144 |

| 21 | Additional buffer memory requirements for seamless IPC                                                                                                                       | 145 |

## LIST OF ABBREVIATIONS

| ACS    | Add Compare Select                      |

|--------|-----------------------------------------|

| ACSU   | Add Compare Select Unit                 |

| ALU    | Arithmetic Logic Unit                   |

| ASIC   | Application-Specific Integrated Circuit |

| ASP    | Application-Specific Processor          |

| BCJR   | Bahl, Cocke, Jelinek, and Raviv         |

| BR     | Boolean Register                        |

| СМР    | CoMPare                                 |

| CORDIC | COordinate Rotation DIgital Computer    |

| CSSU   | Compare-Select-Store Unit               |

| CU     | Control Unit                            |

| DFT    | Discrete Fourier Transform              |

| DP     | Dual Precision                          |

| DSP    | Digital Signal Processor                |

| FEC    | Forward Error Correction                |

| FFT    | Fast Fourier Transform                  |