Stanislav Stanković

# XML-Based Framework for Representation of Decision Diagrams

| Tampereen teknillinen yliopisto. Julkaisu 842<br>Tampere University of Technology. Publication 842                                                                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                           |

| Stanislav Stanković                                                                                                                                                                                                                                       |

| XML-Based Framework for Representation of Decision Diagrams                                                                                                                                                                                               |

| Thesis for the degree of Doctor of Technology to be presented with due permission for public examination and criticism in Tietotalo Building, Auditorium TB109, at Tampere University of Technology, on the 3 <sup>rd</sup> of November 2009, at 12 noon. |

|                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                           |

| Tampereen teknillinen vlieniste. Tampere University of Technology                                                                                                                                                                                         |

| Tampereen teknillinen yliopisto - Tampere University of Technology<br>Tampere 2009                                                                                                                                                                        |

## Preface

Graph-like structures are often used as a means of organizing data with complex internal structure. In recent decades, decision diagrams, a special class of directed acyclic graphs, have found numerous applications in a wide range of fields, from circuit design and testing to information theory and image processing. A variety of types of decision diagrams have proven to be an efficient method of representation of discrete functions, both in terms of memory size and processing time requirements. Over time a variety of decision diagram types have been introduced to represent different classes of discrete functions and to address different application needs.

At the moment, a plethora of software packages employing decision diagrams in some way is present either in industrial environment, or in academic circles. However, most of these software packages make use of proprietary formats for the internal representation and storage of decision diagrams. This makes data exchange between different software packages difficult. As far as we are aware, no attempt has been made to establish a standard format for the representation of such structures.

Our primary aim is to attempt to amend this situation by proposing a uniform framework for the representation of various classes of decision diagrams. Such a platform needs to satisfy several important criteria. Above all it needs to achieve a high degree of generality, i.e. it should to be able to describe as many as possible of the decision diagram classes introduced so far. It should also be easily extensible in order to accommodate possible new types of decision diagrams that may be introduced in the future. This abstract platform

needs to be flexible enough to be transformed into various application specific formats. Finally, one cannot reasonably expect a wide adoption of a new standard which would require radical changes in the present software systems. Thus, this framework needs to be based on a technology that can be easily implemented on most operating systems, and programming environments.

In order to satisfy these criteria, we have chosen to build our framework using XML, an already established data description language created especially for the task of representing complex data structures. In our work we demonstrate that properties of XML make it well suited for the problem of representing decision diagrams. Furthermore, XML is in a wider sense a family of closely related languages dedicated to a particular data manipulation task.

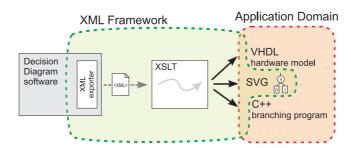

In order to demonstrate the applicability of the proposed framework we exploit the features of XML to convert the abstract representation of decision diagrams into formats suitable for a range of distinct applications, such as hardware register transfer level (RTL) models in VHDL, EDIF based netlists, SVG vector images containing graphical representation of diagrams or branching programs in C++.

The author hopes that the discussion and examples presented in this thesis prove the validity of the chosen approach.

## Acknowledgements

The material presented in this thesis represents the result of research conducted by the author between January 2005 and January 2009, at the Department of Signal processing of Tampere University of Technology (TUT), Finland.

This work was accomplished under the supervision of Professor Jaakko Astola. I wish to express my sincere gratitude for his scientific expertise as well as his support and guidance throughout this years. Without his help none of this work would have been possible.

I am also very grateful to Professor Jarmo Takala of Tampere University of Technology, the co-author of my publications for their contribution, advices and encouragement.

I wish to thank to Professor Michael Miller from University of Victoria and Professor Raimund Ubar of Tallinn Technical University, the reviewers of this thesis, for their valuable comments and recommendations.

I owe thanks to Professor Claudio Moraga for his valuable advices and support.

My thanks to Ms Pirkko Ruotsalainen, Ms Virve Larmila and Ms Ulla Siltaloppi for their assistance in practical arrangements.

I am tankful to my friends and colleagues from TUT, especially to Annamaria, Atanas, Vladislav, Michail, Kostadin, Aram, Robert, and may others for making working hours at university as pleasant as my free time. I also wish to thank my constant online companions Joannis, Valentin and Uroš for providing the much needed breaks from the daily routine.

My deepest gratitude and love goes to my family. Above all, to my father Radomir, for his love, support and help not only personal but professional, as well. Then, also, to my mother Milena from whom I acquired both my interest in computer science and first lessons in programming. Also, to my sister Smiljana.

Finally, my warmest thanks to my dear Jugoslava for her unconditional love, support and patience, and for giving me the happiest moments of my life.

Tampere, October 2009 Stanislav Stanković

## Contents

|   | Preface                                        | v           |

|---|------------------------------------------------|-------------|

|   | Acknowledgements                               | vii         |

| 1 | Introduction                                   | 1           |

| 2 | Mathematical Background of Decision Diagrams   | 5           |

|   | 2.1 Discrete Functions                         |             |

|   | 2.1.1 Switching Functions                      | 7           |

|   | 2.2 Representation of Discrete Functions       | 5<br>7<br>8 |

|   | 2.2.1 Tabular Forms                            | g           |

|   | $\it 2.2.2$ Algebraic Expressions              | 10          |

|   | 2.2.3 Spectral Techniques                      | 19          |

|   | 2.2.4 Decision Diagrams                        | 21          |

|   | 2.3 Topological properties of Decision Diagram | 27          |

|   | 2.4 Classification of Decision Diagrams        | 28          |

| 3 | XML Framework for Decision Diagrams            | 37          |

|   | 3.1 eXtensible Markup Language                 | 38          |

|   | 3.2 XML Documents                              | 39          |

|   | 3.3 XPath                                      | 41          |

|   | 3.4 Software for processing XML documents      | 43          |

|   |                                                |             |

#### x CONTENTS

|   | 3.5  | Data structures for Decision Diagrams                                      | 4  |

|---|------|----------------------------------------------------------------------------|----|

|   | 3.6  | XML Schema                                                                 | 4  |

|   | 3.7  | Decision Diagrams as XML Documents                                         | 5  |

|   | 3.8  | Examples of XML Representations of Various<br>Classes of Decision Diagrams | 5  |

|   | 3.9  | Memory Requirements                                                        | 6  |

|   | 3.10 |                                                                            | 6  |

|   | 3.11 | XSLT                                                                       | 6  |

| 4 | Appl | ications of Decision Diagrams                                              | 7  |

|   | 4.1  | Logic Circuit Minimization                                                 | 7  |

|   | 4.2  | Sensitivity Analysis and Test Pattern Generation                           | 7  |

|   | 4.3  | Probabilistic Analysis of Digital Circuits                                 | 7  |

|   | 4.4  | Cross-correlation of Functions                                             | 7  |

|   | 4.5  | Power Consumption Analysis Using Decision<br>Diagrams                      | 7  |

|   | 4.6  | Information Measures on BDD and Switching<br>Activity                      | 7  |

|   | 4.7  | Formal Verification                                                        | 7  |

|   | 4.8  | Verification of Sequential Circuits                                        | 8  |

|   | 4.9  | Application of Decision Diagrams in Digital<br>Image Processing            | 3  |

|   | 4.10 |                                                                            | ٤  |

| 5 | Appl | ications of the XML Framework in Logic Design                              | 8  |

|   | 5.1  | Related Work                                                               | 8  |

|   | 5.2  | Net lists                                                                  | 8  |

|   | 5.3  | EDIF Netlist Description Language                                          | g  |

|   | 5.4  | EDIF Historical Development                                                | g  |

|   | 5.5  | EDIF Netlists in Comparison to VHDL Models                                 | g  |

|   | 5.6  | Basics of EDIF Syntax                                                      | g  |

|   | 5.7  | VHDL                                                                       | g  |

|   | 5.8  | VHDL Historical Notes                                                      | g  |

|   | 5.9  | VHDL Basic Concepts                                                        | g  |

|   | 5.10 |                                                                            | 10 |

|   | 5.11 | Decision Diagrams and the XSLT Conversion<br>Mechanism                     | 10 |

|   | 5.12 | Application to FBDDs                                                       | 10 |

|   |      | 5.12.1 Efficiency of Implementation of FDDs                                | 10 |

|   | 5.13 | Comparison of Efficiency of QDDs and BDDs                                  | 11 |

|          |        | 5.13.1 XSLT Implementation of the Conversion<br>Algorithm             | 117 |

|----------|--------|-----------------------------------------------------------------------|-----|

|          |        | 5.13.2 A complexity Comparison of QDD and<br>BDD Based Implementation | 125 |

|          | 5.14   |                                                                       | 120 |

|          | 0124   | MTBDDs                                                                | 128 |

|          |        | 5.14.1 Hardware Implementation of Multi-output                        | 400 |

|          |        | Switching Functions Using MTBDD                                       | 130 |

|          |        | 5.14.2 Comparison with SBDDs                                          | 133 |

| 6        | Entr   | opy Estimation Using Decision Diagrams                                | 135 |

|          | 6.1    | Calculation of Entropy Estimates using BDDs                           | 136 |

|          | 6.2    | Experimental Results                                                  | 141 |

| $\gamma$ | Visu   | alization of Decision Diagrams using SVG                              | 143 |

| •        | 7.1    | SVG Graphics Description Language                                     | 143 |

|          | 7.2    | Vizualisation of Decision Diagrams                                    | 144 |

|          | 7.3    | Examples                                                              | 147 |

| 8        | Auto   | matic Code Generation Using the XML Framework                         | 149 |

|          | 8.1    | Branching Programs and Decision Diagrams                              | 149 |

|          | 8.2    | The XSLT Conversion Mechanism                                         | 150 |

|          | 8.3    | Example                                                               | 151 |

|          | 8.4    | Generalizations                                                       | 152 |

| 9        | Cone   | clusions                                                              | 153 |

| Re       | ferenc | ces                                                                   | 157 |

| Ap       | pendi  | x A                                                                   | 173 |

| Ap       | pendi  | x B                                                                   | 175 |

| An       | pendi  | $x \in C$                                                             | 179 |

| P        | r      | ** ·                                                                  |     |

# List of Figures

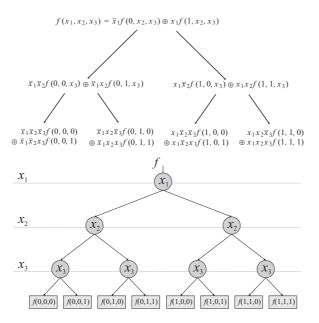

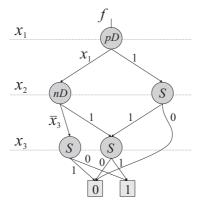

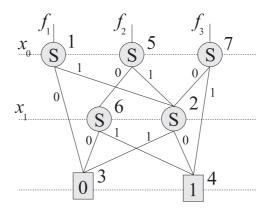

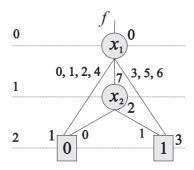

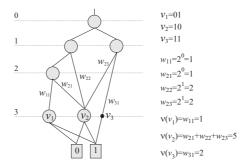

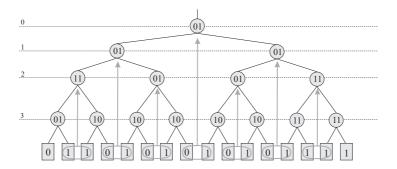

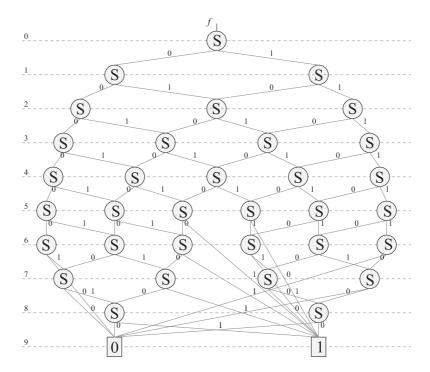

| 2.1 | A tree-like representation of the Shannon expansion for $n = 3$ .                                                                                        | 23  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

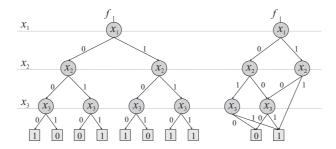

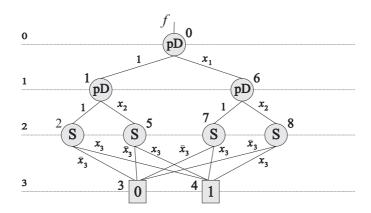

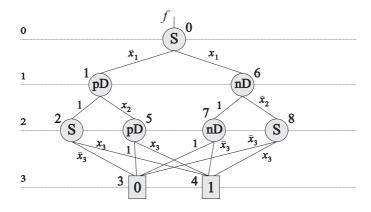

| 2.2 | The Binary Decision Tree and the Binary Decision Diagram for the function $f(x_1, x_2, x_3) = x_2x_3 \oplus \bar{x}_2\bar{x}_3 \oplus x_1x_2\bar{x}_3$ . | 25  |

| 2.3 | Binary decision diagram reduction rules.                                                                                                                 | 29  |

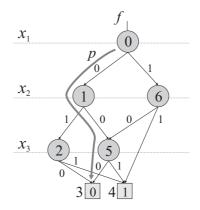

| 2.4 | The Binary Decision Diagram of the function $f(x_1, x_2, x_3) = x_2 x_3 \oplus \bar{x}_2 \bar{x}_3 \oplus x_1 x_2 \bar{x}_3$ .                           | 30  |

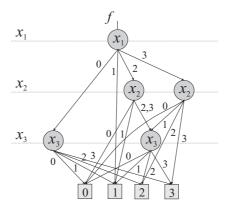

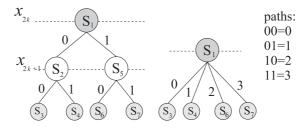

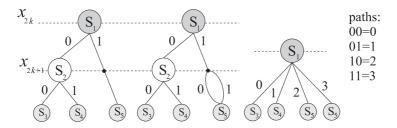

| 2.5 | A Quaternary Decision Diagram for a three-<br>variable discrete function.                                                                                | 31  |

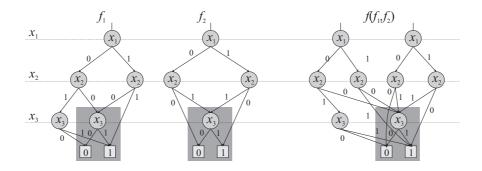

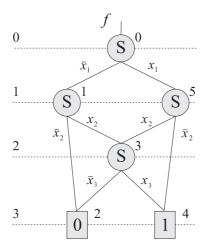

| 2.6 | A Shared Decision Diagram for a multi-output three-variable function $f(f_1, f_2)$ .                                                                     | 31  |

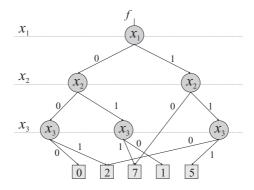

| 2.7 | A Multi-terminal Binary Decision Diagram.                                                                                                                | 32  |

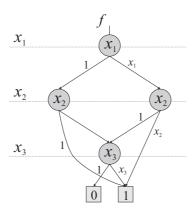

| 2.8 | A Functional Decision Diagram for a Positive<br>Polarity Reed-Muller expansion of the three-<br>variable switching function in Example 2.20.             | 33  |

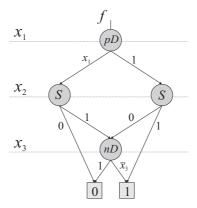

| 2.9 | A Kronecker Decision Diagram for a three-<br>variable switching function, derived using the<br>BDD reduction rules.                                      | 35  |

|     |                                                                                                                                                          | xii |

| 2.10 | A Pseudo Kronecker Decision Diagram for a<br>three-variable switching function, derived using<br>the BDD reduction rules. | 35  |

|------|---------------------------------------------------------------------------------------------------------------------------|-----|

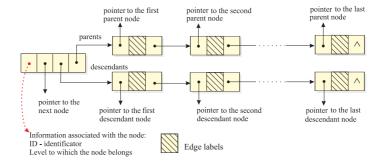

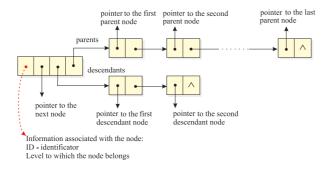

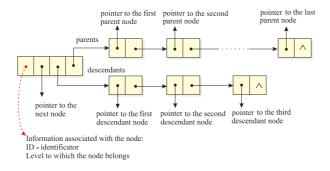

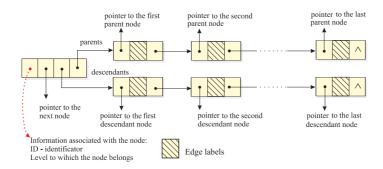

| 3.1  | Diagram of Node data structure.                                                                                           | 46  |

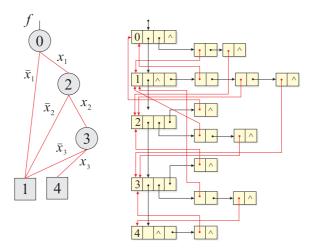

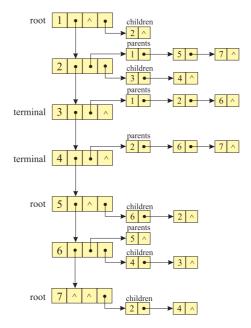

| 3.2  | BDD and the corresponding data structure.                                                                                 | 47  |

| 3.3  | An example of a weighted edge.                                                                                            | 53  |

| 3.4  | Binary decision diagram in Example 1.                                                                                     | 54  |

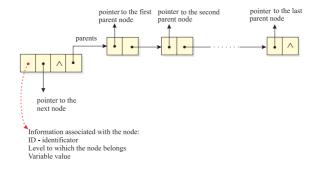

| 3.5  | Data structure for a non-terminal node.                                                                                   | 55  |

| 3.6  | Data structure for the terminal node.                                                                                     | 55  |

| 3.7  | Data structure for the root node.                                                                                         | 56  |

| 3.8  | An example of a shared binary decision diagram.                                                                           | 58  |

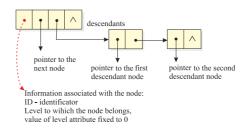

| 3.9  | Data structures representing a shared decision diagram.                                                                   | 58  |

| 3.10 | A Kronecker decision diagram.                                                                                             | 59  |

| 3.11 | A Pseudo-Kronecker decision diagram.                                                                                      | 59  |

| 3.12 | Example of a ternary decision diagram.                                                                                    | 61  |

| 3.13 | A Non-terminal node for a ternary decision diagram.                                                                       | 61  |

| 3.14 | A Heterogeneous decision diagram.                                                                                         | 63  |

| 3.15 | $A\ non-terminal\ node\ in\ a\ heterogeneous\ decision\ diagram.$                                                         | 63  |

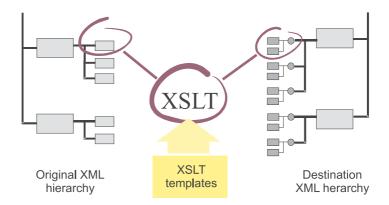

| 3.16 | The position of the XSLT mechanism in the process of conversion of data between two XML-based formats.                    | 66  |

| 3.17 | Hierarchy of XML elements.                                                                                                | 67  |

| 4.1  | Position of the XML-based framework in a larger context.                                                                  | 83  |

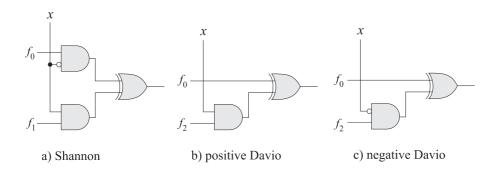

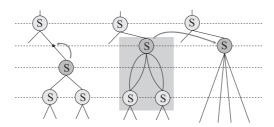

| 5.1  | Logic circuits corresponding to three types of expansions, $f_2 = f_0 \oplus f_1$ .                                       | 105 |

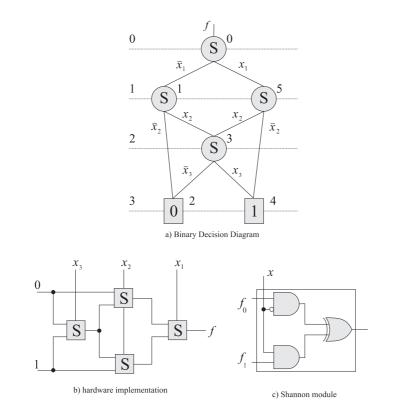

| 5.2  | BDD and a logic network corresponding to the function $f(x_1, x_2, x_3) = x_1 \bar{x_2} \vee x_2 x_3$ .                   | 105 |

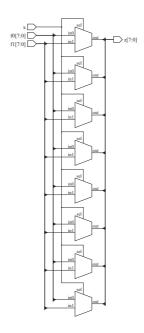

| 5.3  | Decision diagram created using a Shannon decomposition rule and RTL schematic for the fifth output of the misex1 benchmark function.        | 113 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.4  | Decision diagram created using a positive Davio decomposition rule and RTL schematic for the fifth output of the misex1 benchmark function. | 114 |

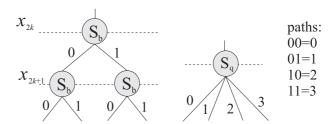

| 5.5  | Relationships among nodes of binary and quaternary decision diagrams.                                                                       | 116 |

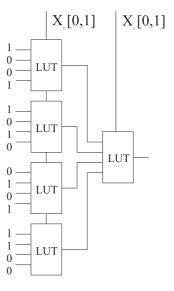

| 5.6  | Replacement of an odd level binary node with a quaternary node.                                                                             | 117 |

| 5.7  | Replacement of an odd level binary node with children on a level immediately below.                                                         | 118 |

| 5.8  | Replacement of an odd level binary node with children deeper in the hierarchy.                                                              | 119 |

| 5.9  | Hardware implementation of a given function using a quaternary decision tree.                                                               | 120 |

| 5.10 | A multi-output binary function represented by MTBDD.                                                                                        | 129 |

| 5.11 | A multi-output binary function represented by shared BDD.                                                                                   | 129 |

| 5.12 | Circuit implementation of the integer Shannon expansion rule.                                                                               | 131 |

| 6.1  | Example of a calculation of entropy estimate via binary decision diagrams.                                                                  | 138 |

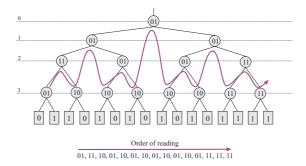

| 6.2  | Subvectors of order $k = 2$ over nodes of a decision tree.                                                                                  | 139 |

| 6.3  | Subvectors of the order $k = 2$ over nodes of a reduced ordered decision diagram.                                                           | 139 |

| 6.4  | The order of reading of the subvectors for $k = 2$ , presented on a decision tree.                                                          | 140 |

| 7.1  | Binary Decision Diagram.                                                                                                                    | 144 |

| 7.2  | A graphic representation of a binary decision diagram of a 9sym benchmark function.                                                         | 148 |

| 8.1  | BDD and a branching program corresponding to the function $f(x_1, x_2, x_3) = x_1 \bar{x}_2 \vee x_2 x_3$ .                                 | 151 |

## List of Tables

| 2.1 | Classes of discrete functions.                                                                                                                              | $\ell$ |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 2.2 | An example of a binary switching function.                                                                                                                  | g      |

| 2.3 | An example of a binary multi-output switching function.                                                                                                     | 10     |

| 2.4 | An example of a ternary function.                                                                                                                           | 10     |

| 2.5 | The truth-table of the function f in Example 2.5.                                                                                                           | 12     |

| 2.6 | Boolean and Arithmetic operations.                                                                                                                          | 18     |

| 5.1 | Selected benchmark functions implemented using<br>a Shannon binary decision diagram and Xilinx<br>Spartan 3 FPGA technology.                                | 110    |

| 5.2 | Selected benchmark functions implemented using<br>a binary decision diagram with a positive Davio<br>decomposition and Xilinx Spartan 3 FPGA<br>technology. | 110    |

| 5.3 | Selected benchmark functions implemented using<br>a Kronecker binary decision diagram and Xilinx<br>Spartan 3 FPGA technology.                              | 111    |

|     |                                                                                                                                                             | xvi    |

| 5.4  | Selected benchmark functions implemented using a Kronecker binary decision diagram with different choice of decomposition rules and Xilinx Spartan 3 FPGA technology.              | 111 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.5  | Selected benchmark functions implemented using<br>a Shannon binary decision diagram and Altera<br>Stratix III FPGA technology.                                                     | 111 |

| 5.6  | Selected benchmark functions implemented using<br>a positive Davio binary decision diagram and<br>Altera Stratix III FPGA technology.                                              | 111 |

| 5.7  | Selected benchmark functions implemented using<br>a Kronecker binary decision diagram and Altera<br>Stratix III FPGA technology.                                                   | 112 |

| 5.8  | Selected benchmark functions implemented using<br>a Kronecker binary decision diagram with a<br>different choice of decomposition rules and Altera<br>Stratix III FPGA technology. | 112 |

| 5.9  | An example of the encoding of a binary and into an equivalent quaternary function.                                                                                                 | 116 |

| 5.10 | Comparison of the size and complexity of binary and quaternary decision diagrams for the selected benchmark functions.                                                             | 125 |

| 5.11 | Standard synthesis method results.                                                                                                                                                 | 127 |

| 5.12 | Results for synthesis using Quaternary decision diagrams.                                                                                                                          | 128 |

| 5.13 | Size comparison of MTBDDs and Shared BDDs of some benchmark functions.                                                                                                             | 130 |

| 5.14 | The selected benchmark functions implemented using MTBDDs and Altera Cyclon II FPGA technology.                                                                                    | 133 |

| 5.15 | The selected benchmark functions implemented using SBDDs and Altera Cyclon II FPGA technology.                                                                                     | 134 |

| 5.16 | The selected benchmark functions implemented using MTBDDs and Xilinx Virtex II FPGA technology.                                                                                    | 134 |

| 5.17 | The selected benchmark functions implemented using SBDDs and Xilinx Spartan II FPGA technology.              | 134 |

|------|--------------------------------------------------------------------------------------------------------------|-----|

| 6.1  | $LUT\ of\ indices\ for\ k=2.$                                                                                | 138 |

| 6.2  | Number of steps needed to calculate the occurrence rate of subvectors using BDDs, and the standard approach. | 141 |

## List of Abbreviations

\*BMD Multiplicative Binary Momentum Diagram

Two Dimensional

API Application Programming Interface

ASIC Application Specific Integrated Circuit

BDD Binary Decision Diagram

BDT Binary Decision Tree

BMD Binary Momentum Diagram

CLB Configurable Logic Block

CPU Central Processing Unit

DD Decision Diagram

DOM Document Object Model

DSP Digital Signal Processor

DT Decision Tree

DTL Decision Type List

EDIF Electronic Design Interchange Format

ESOP Exclusive-OR Sum-Of-Products

EVBDD Edge Valued Binary Decision Diagram

FEVBDD Functional Decision Diagram

FEVBDD Factorized Edge Valued Binary Decision Diagram

FPRM Fixed Polarity Reed-Muller

FPGA Generalized Reed-Muller

HDD Hybrid Decision Diagram Hypertext Markup Language Kronecker Decision Diagram HTML

Look Up Table

KDD LUT MCNC MTBDD Microelectronics Center of North Carolina Multi Terminal Binary Decision Diagram

Negative Davio Ordered Binary Decision Diagram nD OBDD

Positive Davio

$_{\rm PKDD}^{\rm pD}$ Pseudo Kronecker Decision Diagram

POS Product of Sums

PPRM QDD Positive Polarity Reed-Muller Quaternary Decision Diagram

ŘOBDD

Reduced Ordered Binary Decision Diagram

Register Transfer Level

Shannon Decomposition

Simple API for XML

Shared Binary Decision Diagram

Standard Generalized Markup Language RTL

SAX SBDD SGML SOP SVG TDD

Standard Generalized Markup Language Sum of Products Scalable Vector Graphics Ternary Decision Diagrams VHSIC Hardware Description Language Very-High-Speed Integrated Circuits Very-large-scale Integration Walsh Decision Diagram Extensible Markup Language VHDL VHSIC

VLSI WDD Extensible Markup Language XML

Extensible Stylesheet Language Transformations XSLT

**ZBDD** Zero-Suppressed Binary Decision Diagram

# 1

## Introduction

The basic idea that motivated the research presented in this thesis is to establish a standardized method for the representation of various classes of decision diagrams. Our main aim is to provide a means for efficient data exchange between various existing and potential, future software systems that deal with decision diagrams in some way.

Although decision diagrams have already been employed as a valuable tool in several important applications for a significant period of time, to our best knowledge no attempts at standardization have been made so far.

Such a platform has to satisfy several important criteria. Above all it needs to achieve generality, in the sense that it needs to be able to record all the significant structural features of as many distinct classes of decision diagrams already present in practice and the literature as possible. The platform needs to be easily extensible, in order to accommodate possible new types of decision diagrams that might be introduced in the future. In order to do so, the format specification must be focused on the common structural features shared by most classes of decision diagrams.

Furthermore, the proposed solution needs to be flexible enough to be applicable in various application scenarios. An abstract decision diagram representation should be easily convertible to particular application specific formats.

Finally, the whole solution needs to be easy to implement on various operating systems and programming environments. It would be unrealistic to expect a wide acceptance of a standard which would require significant changes in existing and established software packages.

In order to fulfill these requirements we have selected the XML data modeling language as a basis for our solution. The Extensible Markup Language (XML) is a versatile data description language designed specially for the task of representing data with a complex and variable internal structure. The XML does not proscribe a strict data structure to which a certain class of documents needs to conform. Rather, it specifies a set of general rules that these documents need to adhere to. In a wider sense, XML is also a family of languages, XML proper and various derivatives, which offers a set of tools for efficient data manipulation, such as conversion of data between different formats. Recursive properties inherent in XML match the recursive properties exhibited by decision diagrams very well. XML parsers, software modules dedicated to processing XML documents, exist for all major software platforms as libraries for all common programming languages.

The work presented in this thesis is interdisciplinary. It is a software engineering task, related to the field of data structures, with applications in such areas as logic design and information theory and touching on topics such as group theory, graph theory and spectral techniques.

In order to make this thesis as simple to understand as possible, we decided to organize it in the following way.

The first part of this document is introductory in nature. We begin by examining the mathematical background of decision diagrams as a canonical representation of discrete functions. We start with the formal definition of discrete functions, discuss their classification and present several methods for their representation gradually introducing the more complex methods, culminating with decision diagrams. Next we turn our attention to spectral transforms which provide a uniform interpretation of various types of decision diagrams. Formal definitions of decision diagrams are given next. Further, decision diagrams are examined from the graph theory point of view, with special attention given to their topological properties, as these properties in large part determine the organization of the proposed XML based framework. The topological properties of decision diagrams, such as the size, i.e. number of nodes, maximal path length, etc., are of great importance to the applications of decision diagrams, especially the minimization of logic circuits.

In the second part of this thesis, we introduce the basic notions of the XML, its syntax and data description principles. Here we also present, the other members of the XML family which are of interest for our work. The XML Schema language is used to specify the file format of particular types of XML documents, and also to validate individual XML documents. Internal data addressing in XML based solutions is performed via the XPath language. Most importantly, a mechanism for the conversion of XML documents to other XML or non-XML based formats is provided by XSLT. We pay special attention to the XSLT language as it is employed by all of the application examples for the presented framework.

We focus next on the core of the proposed solution itself, the structure of XML documents for the representation of decision diagrams. We first discuss the data structures commonly employed for representation of acyclic directed graphs from the theoretical point of view. The details of XML Schema spec-

ification for decision diagrams are presented next. Since the primary task of the proposed framework is representation of various classes of decision diagrams, we give several examples of XML documents for a range of decision diagram types, starting with reduced ordered binary decision diagrams (ROB-DDs) and functional decision diagrams (FDDs), through multi-output binary decision diagrams (MTBDDs) and shared binary decision diagrams (SBDDs) to multivalued ternary (TDDs) and quaternary (QDDs) decision diagrams.

In order to prove the validity of the proposed framework, we also present several examples of its potential application. However, before we are able to do so, we first need to examine the possible applications of decision diagrams in general, especially in the field of logic design. This discussion is presented in Chapter 4.

The majority of these examples deal with the application of decision diagrams in logic design, especially the implementation of switching functions using FPGA devices. The application of high-level programing languages in hardware design is known as High Level Synthesis. A quick overview of the related software solutions is given. We also examine the standard way in which switching functions expressed in decision diagram form are implemented in hardware. Therefore, a brief introduction to the concept of netlists is given in Section 5.2. Several high-level hardware description languages are currently in wide use. In our examples, we make use of two of them, VHDL as a general purpose hardware modeling language and EDIF for the specific task of netlist specification. An introduction to the basic concepts of both of them is given in Section 5.9 and Section 5.6 respectively. Their mutual similarities and differences are discussed in Section 5.5.

The first example we present deals with the implementation of switching functions using various families of FPGA devices. We have developed a set of two XSLT stylesheets capable of converting an XML document containing a ROBDD of a given function into a RTL hardware model expressed in VHDL syntax. In the next example, we compare the efficiency of MTBDD implementations of multi-output switching functions versus the more common SBDD implementation. In recent years, six input LUT based FPGA devices have been introduced as an optimal solution to the problem of granularity of logic blocks. QDDs have been proposed as a tool for logic design for such devices. We introduce an algorithm for generating a QDD function representation from its ROBDD. The XSLT implementation of this algorithm is presented in Section 5.13.

Information theory is one of the possible fields for application of decision diagrams. In the example, given in Chapter 6, we introduce a ROBDD based method for the calculation of the entropy estimate of a given binary string.

We further demonstrate the flexibility of the proposed framework in Chapter 7. A set of XSLT stylesheets is employed to automatically generate graphic representations of decision diagrams. The final product of this process is a vector image in SVG format.

Finally, in the last example we discuss the behavioral and structural aspects of system modeling with regards to decision diagrams in Chapter 8.

Concluding remarks are given in Chapter 9.

This thesis consists, in the greatest part, of the material originally presented in the following publications by the author:

- **P 1** S. Stanković, J. Astola, "XML framework for various types of decision diagrams for discrete functions", IEICE Trans. Inf. and Syst., Vol. E90-D, No. 11, 2007, 1731-1740.

- P 2 S. Stanković., J. Takala, J. Astola, "Method for Automatic Generation of RTL in VHDL Using Decision Diagrams", Proc. The 2006 Int. TICSP Workshop on Spectral Methods and Multirate Signal processing, SMMSP, Florence, Italy, 2006.

- P 3 S. Stanković, J. Astola, "QDD Based Method of Automatic Circuit Design for Xilinx Virtex-5 FPGA Devices", Journal of Multiple-Valued Logic and Soft Computing, accepted for publicaiuton.

- P 4 S. Stanković, J. Astola, "Calculating Entropy Estimate Using Binary Decision Diagrams", Proc. XI International Symposium on Problems of Redundancy in Information and Control Systems, 02 06 July, 2007, Saint Petersburg, Russia, 32-36.

- P 5 S. Stanković, J. Astola, "XSLT Based Method for Automatic Generation of a Graphical Representation of a Decision Diagram Represented using XML", 7th International Workshop on Boolean Problems, Freiberg, Germany, 21-22 Sept. 2006.

- P 6 S. Stanković, J. Astola, "Method for automatic generation of branching programs using decision diagrams", Proc. The 2007 Int. TICSP Workshop on Spectral Methods and Multirate Signal processing, SMMSP 2007, Moscow, Russia, September 3-4, 2007, paper cr1023.

The general concept of XML-based framework for representation of Decision Diagrams was introduced in P 1. The applications of this framework in logic design have been discussed in P 2 and later in P 3. Other publications by the author discuss the application of the framework in other fields. Decision Diagram based method for entropy estimation was presented in P 4. An XML-based method for authomatic visualization of Decision Diagrams was proposed in P 5 and the method of authomatic generation of branching programs was presented in P 6.

The whole thesis and the publications cited above represent original work, of which the author was the main contributor. In particular, the XML-based methodology for representation of Decision Diagrams, the presented framework, conversion algorithms and related software implementations were proposed and developed by the author. Furthermore, all experimental results represent original work by the author.

# 2

# $\begin{array}{c} Mathematical \\ Background\ of\ Decision \\ Diagrams \end{array}$

In this chapter we present the mathematical background of decision diagrams. These underlying concepts to a great extent determine the conditions which the XML-based framework for the representation of decision diagrams needs to satisfy. We begin our discussion by restating the definition of discrete functions. Special interest is devoted to switching functions, a special class of discrete functions which forms the foundation of digital circuit technology based on two stable state circuits. We continue by examining several forms of the representation of discrete functions, from the most simple tabular forms to graphics representation, ending with a formal definition of decision trees and decision diagrams. Further, we list the topological properties of decision diagrams that are of interest from an application point of view. We end this chapter with an overview of several important classes of decision diagrams, especially those which will be used in examples of applications of the proposed framework.

### 2.1 DISCRETE FUNCTIONS

In this section, we discuss some basic properties of discrete functions, and give an overview of certain classes of discrete functions that are of special interest in this work. We devote special attention to switching functions, since these functions are most important in practice. In the reminder of this thesis, we make use of switching functions to introduce many important concepts and give generalizations to other classes of discrete functions as appropriate.

Table 2.1 Classes of discrete functions.

| Integer            | $f: \times_n^{i=1} \{0, 1,, m_i - 1\} \to \{0, 1,, \tau_i - 1\}$                                                               |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------|

| Multivalued        | $f: \times_{i=1}^{i=1} \{0, 1,, m_i - 1\} \to \{0, 1,, \tau_i - 1\}$<br>$f: \{0, 1,, \tau_i - 1\}^n \to \{0, 1,, \tau_i - 1\}$ |

| Switching, Boolean | $f: B^n \to B$                                                                                                                 |

| Pseudo-logic       | $f: \times_n^{i=1} \{0, 1,, m_i - 1\} \rightarrow \{0, 1\}$                                                                    |

| Pseudo-Boolean     | $f: \{0,1\}^n \to R, R$ - field of real numbers                                                                                |

| Galois             | $f: \{GF(p)\}^n \to \{GF(p)\}$                                                                                                 |

A general definition of discrete functions can be stated in the following form:

**Definition 2.1** Let A and B be sets. A relation is a subset r of  $A \times B$ . A relation f is a function if, and only if, for every  $a \in A$  there exists exactly one  $b \in B$  such that  $(a,b) \in f$ . A relation f is called an incompletely specified function if for each  $a \in A$  there is at most one  $b \in B$  such that  $(a,b) \in f$ , and there is at least one a for which there is no  $(a,b) \in f$ . The sets A and B are usually called the domain and the range of f, and written  $f : A \to B$ .

Depending on the choice of domain and range there are different classes of discrete functions. We list the most important classes in Table 2.1.

The number of discrete functions is exponential in the cardinality of the domain. Consider discrete functions  $f:X\to Y$ , where each function is specified by a vector of its values with length |X|, where |X| denotes the cardinality of the set X.  $Y^X$  is the set of all functions from X to Y. The total number of functions is  $|Y|^{|X|}$ .

The set of all subsets of a set A is called the power set of A and denoted by  $\mathcal{P}(A)$ . Often, the power set of A is denoted by  $2^A$  due to the following considerations. The set of all functions from a set A to the set  $2 = \{0, 1\}$  is  $2^A$ . Each function in  $2^A$  can be viewed as the characteristic function of a subset in A and can be identified with that subset. Therefore, there is a bijection between  $2^A$  and  $\mathcal{P}(A)$ , and the power set of A can be denoted by  $2^A$ .

From an application point of view, another very important concept is the concept of multi-output discrete functions.

**Definition 2.2** A multi-output discrete function is a function defined as:

$$f: \times_{i=1}^n D_i \to \times_{i=1}^m R_i \tag{2.1}$$

where  $D_i$ ,  $R_i$  are finite, non-empty sets.

The multi-output function f is clearly equivalent to a system  $(f_1, ..., f_m)$  of single output functions  $f_i: D_i \to R_i, i = 1, ..., n$ .

Multi-output discrete functions can be used to describe the behavior of a system with multiple inputs and outputs. Especially, multi-output switching functions are used to describe the behavior of logic circuits.

#### 2.1.1 Switching Functions

As shown in Table 2.1, switching functions represent a special class of discrete functions. We review some of their properties.

**Definition 2.3** A Boolean algebra  $\langle B; \vee, \wedge; \bar{}; 0, 1 \rangle$  is defined as a set B, two elements of B, 0 and 1, two binary operations  $\vee$ ,  $\wedge$ , and a unary operation  $\bar{}$ . These operations are known as logic OR, AND and NOT, respectively, and satisfy the following postulates:

- 1. Idempotencity  $x \lor x = x$ ,  $x \land x = x$ ,

- 2. Commutativity  $x \vee y = y \wedge x$ ,  $x \vee y = y \wedge x$ ,

- 3. Associativity  $x \lor (y \lor z) = (x \lor y) \lor z, \ x \land (y \land z) = (x \land y) \land z,$

- 4. Absorption  $x \lor (x \land y) = x$ ,  $x \land (x \lor y) = x$ ,

- 5. Distributivity  $x \land (y \lor z) = (x \land y) \lor (x \land z), \ x \lor (y \land z) = (x \lor y) \land (x \lor z),$

- 6. Complement  $x \vee \bar{x} = 1$ ,  $x \wedge \bar{x} = 0$ ,

for  $x, y, z \in B$ .

Boolean functions are defined in terms of expressions over a Boolean algebra.

In the case of a two-valued Boolean algebra  $B = \{0,1\}$  and the operations can be expressed as:

The logic OR operation

$$\begin{array}{c|cccc} & \vee & 0 & 1 \\ \hline 0 & 0 & 1 \\ 1 & 1 & 1 \end{array}$$

the logic AND operation

$$\begin{array}{c|cccc} & \wedge & 0 & 1 \\ \hline 0 & 0 & 0 \\ 1 & 0 & 1 \end{array}$$

and the unary logic NOT operation

$$\begin{array}{c|c} - & & \\ \hline 0 & 1 \\ 1 & 0 \end{array}$$

.

Logic AND, OR and NOT operations are extended to  $B^n$  component wise.

**Example 2.1** For all  $x = (a_1, ..., a_n), y = (b_1, ..., b_n), where <math>a_i, b_i \in B$ ,  $i = 1, ..., n, x \lor y = (a_1 \lor b_1, ..., a_n \lor b_n).$

**Definition 2.4** Let  $\langle B; \vee; \wedge; -; 0; 1 \rangle$  be a Boolean algebra. A variable that takes values in the set B is a Boolean variable. The expression that is obtained from the Boolean variables and constants by combining with the operations  $\vee$ ,  $\wedge$ , and - and parentheses is a Boolean expression. A Boolean mapping is a Boolean function if and only if every element in  $B^n$  has exactly one element in B associated with it. If a mapping  $f: B^n \to B$  is represented by a Boolean expression, then f is a Boolean function. However, not all the mappings  $f: B^n \to B$  are Boolean functions.

Switching functions possess certain properties which make them suitable for the theoretical foundation of circuit design.

- 1. There exist exactly four distinct functions of a single variable x:  $f_0(x) = 0$ ,  $f_1(x) = 1$ ,  $f_2(x) = x$  and  $f_3(x) = \bar{x}$ .

- 2. There are 16 two variable switching functions. They are used to describe the elementary logic gates (AND, OR, EXOR, etc.)

- 3. The number of n-variable switching functions with one output is equal to  $2^{2^n}$ .

- 4. The number of m-output, n-variable switching functions is equal to  $2^{m2^n}$ .

- 5. A logic circuit with n inputs and one output can be described by an n-variable switching function  $f = (x_1, x_2, ..., x_n)$ .

- 6. A logic circuit with n inputs and m outputs can be described in terms of m-tuple  $f = (f_1, f_2, ..., f_m)$ .

Switching functions, and discrete functions in general, can be represented in a variety of forms. The central subject of this work, decision diagrams, are one of the several forms of representation encountered in practice. In order to give a better view of the position of decision diagrams in relation to other forms of representation, we discus some of these forms in the following section. These forms will also be used for initial specification of functions in certain examples.

#### 2.2 REPRESENTATION OF DISCRETE FUNCTIONS

Depending on the intended application, a variety of methods have been proposed for the representation of discrete functions. These methods can be divided into three large groups:

Table 2.2 An example of a binary switching function.

- 1. Decision tables and tabular forms in general,

- 2. Algebraic expressions,

- 3. Graphic methods, graphs, hypercubes, etc.

We present an overview of these methods with a special focus on switching functions.

#### 2.2.1 Tabular Forms

Discrete functions can always be represented in tabular form, due to the fact that their domain is finite.

**Example 2.2** Table 2.2 presents a three-variable switching function f by listing function values for all possible inputs.

The left side of the table represents the elements of the domain. The right part displays the corresponding function values.

In the case of binary functions this form of representation is known as the truth-table. The vector of function values is known as the truth-vector. The same concept is readily extended to multi-output functions.

**Example 2.3** Consider a three-variable two-output binary function  $f = (f_1, f_2)$ . We present the tabular representation of this function in Table 2.3.

The tabular display is also convenient for other classes of discrete functions, as illustrated in Example 2.4 and Example 2.5 below.

**Example 2.4** Table 2.4 shows an example of a ternary three-valued discrete function in tabular form, with ternary variables on the left and the function values on the right.

In the tabular form all the values of the variables are shown explicitly. Any interdependence of the function values is ignored. However, this manner of displaying causes a serious problem. The size of the table is exponential in

Table 2.3 An example of a binary multi-output switching function.

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |                  |       | -     |       | _     |

|-------------------------------------------------------|------------------|-------|-------|-------|-------|

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ | $\overline{x_1}$ | $x_2$ | $x_3$ | $f_1$ | $f_2$ |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | 0                | 0     | 0     | 1     | 0     |

| $0 \ 1 \ 1 \ 1 \ 1$                                   | 0                | 0     | 1     | 0     | 0     |

|                                                       | 0                | 1     | 0     | 0     | 0     |

| 1 0 0 1 1                                             | 0                | 1     | 1     | 1     | 1     |

| 1 0 0 1 1 1                                           | 1                | 0     | 0     | 1     | 1     |

| 1  0  1  0  1                                         | 1                | 0     | 1     | 0     | 1     |

| 1  1  0     1  0                                      | 1                | 1     | 0     | 1     | 0     |

| 1 1 1 1 1                                             | 1                | 1     | 1     | 1     | 1     |

Table 2.4 An example of a ternary function.

|                              | •                                                                                                       |                                                            |

|------------------------------|---------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| $\frac{\overline{x_1}}{0}$   | $x_2$                                                                                                   | $\int f$                                                   |

| 0                            | 0                                                                                                       | $\overline{0}$                                             |

| 0                            | 1                                                                                                       | 1                                                          |

|                              | 2                                                                                                       | 0                                                          |

| 1                            | 0                                                                                                       | $\stackrel{\circ}{1}$                                      |

| 1                            | $     \begin{array}{c}       1 \\       2 \\       0 \\       1 \\       2 \\       0     \end{array} $ | 2                                                          |

| 1                            | 2                                                                                                       | 1                                                          |

| $\bar{2}$                    | Ō                                                                                                       | $\bar{2}$                                                  |

| $0 \\ 1 \\ 1 \\ 2 \\ 2 \\ 2$ |                                                                                                         | $\begin{bmatrix} 0 \\ 2 \\ 2 \\ 1 \\ 2 \\ 2 \end{bmatrix}$ |

| $\bar{2}$                    | $\frac{1}{2}$                                                                                           | Ιī                                                         |

|                              |                                                                                                         |                                                            |

the number of variables. Tabular representations quickly become unwieldy for even a relatively small number of discrete variables. Other methods of representation of discrete functions aim to achieve better economy by exploiting internal dependencies between function values.

#### 2.2.2 Algebraic Expressions

An algebraic expression is a formal description of a discrete function in terms of algebraic relations between variables.

**Definition 2.5** If a discrete k-valued variable  $x_i$  takes its values in a set  $Q_i = \{0, 1, ..., k-1\}$ , then  $x_i^S$ ,  $S \subseteq Q_i$ , is a literal of  $x_i$ , where

$$x_i^S = \left\{ \begin{array}{ll} 1, & \text{if } x_i \in S, \\ 0, & \text{if } x_i \notin S. \end{array} \right.$$

When S contains only one element,  $x_i^{\{j\}}$  is denoted by  $x_i^j$ .

$\begin{array}{l} \textbf{Definition 2.6} \ \ Let \ x_i \ \ take \ values \ in \ Q_i, i=1,...,n \ \ and \ x_{i_1}^{S_{i_1}},...,x_{i_j}^{S_{i_j}}, \ 1 \leq \\ i_1 \leq i_2 \leq ... \leq i_j \leq n \ \ be \ \ literals. \ \ The \ logic \ AND \ \ of \ literals \ x_{i_1}^{S_{i_1}} \wedge ... \wedge \\ x_{i_j}^{S_{i_j}} \left(=x_{i_1}^{S_{i_1}}...x_{i_j}^{S_{i_j}}\right) \ is \ called \ a \ product \ term. \end{array}$

A product term of the form  $x_1^{S_1}...x_n^{S_n}$  is called a minterm. We emphasize that all the variables appear in a minterm and there can be at most one literal for a variable.

**Definition 2.7** Let  $\rho \subseteq 2^{Q_1} \times 2^{Q_2} \times ... \times 2^{Q_n} = \times_{i=1}^n 2^{Q_i}$ . Then,

$$\bigvee_{(S_1, \dots, S_n) \in \rho} x_1^{S_1} \dots x_n^{S_n}, \tag{2.2}$$

is a Sum-of-Products expression (SOP), where  $\bigvee_{(S_1,S_2,...,S_n)\in\rho}$  denotes the logic OR (inclusive OR) of product terms. If OR is replaced by the exclusive OR (EXOR) then the resulting expression

$$\bigoplus_{(S_1,S_2,\ldots,S_n)\in\rho} x_1^{S_1}x_2^{S_2}\cdots x_n^{S_n}$$

is an Exclusive-Sum-Of-Froduct expression (ESOP).

**Example 2.5** [141] Table 2.5 is an example of a multiple-valued input two-valued output function  $f: Q_1 \times Q_2 \times Q_3 \rightarrow Q_1$ , where  $Q_1 = \{0,1\}$ ,  $Q_2 = \{0,1,2\}$ , and  $Q_3 = \{0,1,2,3\}$ . Thus, the variables  $x_1 \in Q_1$ ,  $x_2 \in Q_2$ ,  $x_3 \in Q_3$  take two, three, and four values, respectively.

The minterm expression for f is

$$\begin{array}{lcl} f & = & x_1^{\{0\}} x_2^{\{0\}} x_3^{\{0\}} \vee x_1^{\{0\}} x_2^{\{1\}} x_3^{\{1\}} \vee x_1^{\{0\}} x_2^{\{1\}} x_3^{\{3\}} \\ & & \vee x_1^{\{0\}} x_2^{\{2\}} x_3^{\{2\}} \vee x_1^{\{1\}} x_2^{\{0\}} x_3^{\{0\}} \vee x_1^{\{1\}} x_2^{\{0\}} x_3^{\{3\}} \\ & & \vee x_1^{\{1\}} x_2^{\{1\}} x_2^{\{1\}} \vee x_1^{\{1\}} x_2^{\{1\}} x_2^{\{3\}} \vee x_1^{\{1\}} x_2^{\{2\}} x_2^{\{2\}}. \end{array}$$

The SOP derived by extracting common terms in products, is

$$f = x_1^{\{0,1\}} x_2^{\{0\}} x_3^{\{0\}} \vee x_1^{\{0,1\}} x_2^{\{1\}} x_3^{\{1,3\}} \vee x_1^{\{0,1\}} x_2^{\{2\}} x_3^{\{2\}} \vee x_1^{\{1\}} x_2^{\{0,1\}} x_3^{\{3\}}.$$

After removing redundant literals, it is

$$f = x_2^{\{0\}} x_3^{\{0\}} \vee x_2^{\{1\}} x_3^{\{1,3\}} \vee x_2^{\{2\}} x_3^{\{2\}} \vee x_1^{\{1\}} x_2^{\{0,2\}} x_3^{\{3\}}.$$

The concept of SOP and ESOP expressions can be extended and generalized to derive other algebraic expressions. The product terms in these two expressions can be viewed as particular examples of basis function in the spaces of n-variable discrete functions with the domain and the range specified over some finite sets. It is assumed that the domain and the range are enriched with the necessary operations to express the algebraic structure of a finite group for the domain and a field for the range that can be a finite field or the field of complex numbers C.

Values for variables and function values can be interpreted as either logic (binary or multiple-valued) values or in general case as elements of the field

$\frac{x_1x_2x_3}{000}$  $\frac{x_1x_2x_3}{020}$ 001 0 021 0 0  $022 \\ 023$ 002  $0 \frac{1}{0}$ 0  $00\overline{3}$ 010 100 1200 0  $\frac{1}{0}$ 013

Table 2.5 The truth-table of the function f in Example 2.5.

assumed for the range of the functions considered. The minterms can be replaced with various other complete sets of linearly independent functions. Recall that here the term complete means that the number of basis functions is equal to the cardinality of the domain for the functions. Further, instead of OR and EXOR, other operations over the field assumed for the range can be used as the addition to define series-like expressions for discrete functions  $f: D \to R, \ D = \times_{i=1}^n D_i$  as

$$f(x_1, x_2, \dots, x_n) = \sum_{i=1}^{|D|} c_i \phi_i(x_1, x_2, \dots, x_n),$$

(2.3)

where the coefficients  $c_i$  and the basis functions  $\phi_i$  take values in the range R, and the addition is defined as the addition in the field imposed on R that is viewed as the support set of a field.

Expressions where the coefficients  $c_i$  and the basis functions  $\phi_i$  take values in a finite field are called *bit-level expressions*, where bits are understood as either binary or multiple-valued. If  $c_i$  and  $\phi_i(x_1, x_2, \ldots, x_n)$  take values in the field of complex numbers C, the expressions are called *word-level expressions*. The expressions with integer-valued coefficients and basis functions are viewed as particular cases of expressions over C. These expression are most often used in dealing with switching (binary-valued) and multiple-valued logic functions due to simple encoding of n-tuples of logic values by the corresponding integers.

The properties of particular kinds of algebraic expressions are discussed in detail in what follows.

In particular, SOP expressions are defined by using minterms as basis functions  $\phi_i$ ,  $i=0,1,\ldots 2^n-1$ , where n is the number of variables. SOPs are widely used to describe behavior of switching functions and, therefore, will be discussed in more details in what follows. Another reason is that various other expressions can be derived from SOP expressions by converting minterms into different sets of basis functions.

We can compare the basic notion of the Sum-Of-Product expression to the tabular representation examined in the previous section. The assignment of variable values is, in this setting, expressed in terms of minterms multiplied by the corresponding function values. Minterms that are multiplied by 0 have no effect on the function output and are discarded. The remaining minterms, those that are multiplied by 1, make up the final function representation.

**Example 2.6** The binary function presented in tabular form in Example 2.2 can be represented by the following SOP expression:  $f = x_2x_3 \vee \bar{x}_2\bar{x}_3 \vee x_1x_2\bar{x}_3$ .

Sum-of-Products can be seen as series-like expressions, where minterms play the role of basis functions, and again, the corresponding function values the role of coefficients.

In matrix notation minterms can be generated through the Kronecker product of the basic matrices  $X(1) = [\bar{x}_i, x_i]$ , for i = 1, ..., n. This Kronecker product produces an identity matrix. Therefore, the set of minterms (columns of the identity matrix) is known as the trivial basis.

**Definition 2.8** The Shannon (S) Expression [149] of a switching function f with respect to the variable  $x_i$  is:

$$f = \bar{x}_i f_0 \vee x_i f_1 \tag{2.4}$$

where

$$f_0 = f(x_1, ..., x_{i-1}, 0, x_{i+1}, ..., x_n)$$

and  $f_1 = f(x_1, ..., x_{i-1}, 1, x_{i+1}, ..., x_n)$

are the co-factors of f with respect to  $x_i$ .

**Remark 2.1** Since product terms in 2.4 has no comon minters, ∨ can be repalced by  $\oplus$ . In this case the Shannon expression has the form:

$$f = \bar{x}_i f_0 \oplus x_i f_1. \tag{2.5}$$

In matrix notation, the Shannon expansion can be expressed in terms of basic matrices  $\mathbf{X}(1)$  and  $\mathbf{B}(1)$ ,

$$f = \begin{bmatrix} \bar{x}_i & x_i \end{bmatrix} \begin{bmatrix} 1 & 0 \\ 0 & 1 \end{bmatrix} \begin{bmatrix} f_0 \\ f_1 \end{bmatrix}$$

(2.6)

$$f = \mathbf{X}(1)\mathbf{B}(1)\mathbf{F},\tag{2.7}$$

where

$$\mathbf{X}(1) = \begin{bmatrix} \bar{x}_i & x_i \end{bmatrix}$$

,  $\mathbf{B}(1) = \begin{bmatrix} 1 & 0 \\ 0 & 1 \end{bmatrix}$  and,  $\mathbf{F}(1) = \begin{bmatrix} f_0 \\ f_1 \end{bmatrix}$ .

where  $\mathbf{X}(1) = [\bar{x}_i \ x_i]$ ,  $\mathbf{B}(1) = \begin{bmatrix} 1 & 0 \\ 0 & 1 \end{bmatrix}$  and,  $\mathbf{F}(1) = \begin{bmatrix} f_0 \\ f_1 \end{bmatrix}$ .

The Shannon expansion rule can be applied recursively to a switching function. tion  $f(x_1,...,x_n)$ , with respect to the variable  $x_i$ , i=1,...,n, which leads to the complete SOP for the considered function.

Example 2.7 Recursive application of the Shannon expansion to a twovariable switching function  $f(x_1, x_2)$ :

$$f(x_1, x_2) = \bar{x}_1 f(0, x_2) \oplus x_1 f(1, x_2)$$

$$= \bar{x}_1 (\bar{x}_2 f(0, 0) \oplus x_2 f(0, 1))$$

$$\oplus x_1 (\bar{x}_2 f(1, 0) \oplus x_2 f(1, 1))$$

$$= \bar{x}_1 \bar{x}_2 f(0, 0) \oplus \bar{x}_1 x_2 f(0, 1)$$

$$\oplus x_1 \bar{x}_2 f(1, 0) \oplus x_1 x_2 f(1, 1)$$

In the general case for an n-variable switching function, this can be expressed in the following form:

$$f = \mathbf{X}(n)\mathbf{B}(n)\mathbf{F} = \left(\bigotimes_{i=1}^{n} \mathbf{X}(1)\right) \left(\bigotimes_{i=1}^{n} \mathbf{B}(1)\right)\mathbf{F}$$

(2.8)

which is the matrix notation for the complete Sum-of-Products.

In the complete disjunctive form there are no common terms, thus is it possible to formally replace EXOR by OR in the Shannon expansion rule and it will remain true. This is, however, not the case for the reduced Sum-of-Products derived from the complete Sum-of-Products by exploiting properties of the Boolean algebra.

The binary Shannon expansion can be generalized to the p-valued case. The following example illustrates the generalization of the Shannon decomposition for four-valued discrete functions.

**Example 2.8** The Shannon expansion of an arbitrary r-variable four-valued function  $f(x_1, x_2, ..., x_r)$ , with respect to  $x_1$  is:  $f(x_1, x_2, ..., x_r) = x_1^0 f(0, x_2, ..., x_r) \vee x_1^1 f(1, x_2, ..., x_r) \vee x_1^2 f(2, x_2, .... x_r) \vee x_1^3 f(3, x_2, ..., x_r)$ , or in short form  $f = \bigvee_{(a_1, a_2, ..., a_n)} f(a_1, a_2, ..., a_n) x_1^{a_1} x_2^{a_2} ... x_n^{a_n}$ , where where  $x_i^k$  are literals of four-valued variables as defined in Definition 2.5.

A different choice of matrix  $\mathbf{X}(1)$  and the corresponding  $\mathbf{B}(1)$  in (2.8) produces a different expansion. We present some examples of such expansions.

**Remark 2.2** Recalling one of the basic properties of Boolean logic,  $\bar{x}_i = 1 \oplus x_i$ , the Shannon expansion can be rewritten as:

$$f = \bar{x}_i f_0 \oplus x_i f_1 = (1 \oplus x_i) f_0 \oplus x_i f_1$$

=  $1 \cdot f_0 \oplus x_i f_0 \oplus x_i f_1 = 1 \cdot f_0 \oplus x_i (f_0 \oplus f_1)$  (2.9)

This expansion is called the positive Davio (pD) expansion. Every switching function f can be written, using this expansion, in the following form:

$$f = c_0 \oplus c_1 x_i \tag{2.10}$$

where  $c_0 = f_0$  and  $c_1 = f_0 \oplus f_1$ .

**Remark 2.3** The expansion that is obtained by iterative application of the positive Davio expansion is called the Positive Polarity Reed-Muller expansion (PPRM).

**Example 2.9** The positive Polarity Reed-Muller expansion of a two variable switching function  $f(x_1, x_2)$ :

$$f = 1 \cdot f(0, x_2) \oplus x_1(f(0, x_2) \oplus f(1, x_2))$$

$$= 1 \cdot (1 \cdot f(0, 0) \oplus x_2(f(0, 0) \oplus f(0, 1)))$$

$$\oplus x_1(1 \cdot f(0, 0) \oplus x_2(f(0, 0) \oplus f(0, 1))$$

$$\oplus 1 \cdot f(1, 0) \oplus x_2(f(1, 0) \oplus f(1, 1)))$$

$$= 1 \cdot f(0, 0) \oplus x_2(f(0, 0) \oplus f(0, 1)) \oplus x_1 \cdot (f(0, 0) \oplus f(1, 0))$$

$$\oplus x_2(f(0, 0) \oplus f(0, 1) \oplus f(1, 0) \oplus f(1, 1))$$

$$= c_0 \oplus c_1 x_2 \oplus c_2 x_1 \oplus c_3 x_1 x_2$$

where,

$$c_0 = f_0$$

$$c_1 = f(0,0) \oplus f(0,1)$$

$$c_2 = f(1,0) \oplus f(1,1)$$

$$c_3 = f(0,0) \oplus f(0,1) \oplus f(1,0) \oplus f(1,1)$$

These are the Reed-Muller coefficients.

The matrix notation of the Reed-Muller expansion has the following form:

$$f = \begin{bmatrix} 1 & x_i \end{bmatrix} \begin{bmatrix} 1 & 0 \\ 1 & 1 \end{bmatrix} \begin{bmatrix} f_0 \\ f_1 \end{bmatrix}, \tag{2.11}$$

$$f = \mathbf{X}_{rm}(1)\mathbf{R}(1)\mathbf{F}. (2.12)$$

The extension to functions of an arbitrary number of variables is done by the Kronecker product

$$f = \mathbf{X}(n)\mathbf{B}(n)\mathbf{F} = \left(\bigotimes_{i=1}^{n} \mathbf{X}_{rm(1)}\right) \left(\bigotimes_{i=1}^{n} \mathbf{R}(1)\right) \mathbf{F}.$$

(2.13)

**Remark 2.4** Similarly to the case of the positive Davio expansion, the negative Davio (nD) expansion is derived from the Shannon expansion by the relation  $x_i = 1 \oplus \bar{x}_i$ .

In matrix notation:

$$f = \begin{bmatrix} 1 & \bar{x}_i \end{bmatrix} \begin{bmatrix} 0 & 1 \\ 1 & 1 \end{bmatrix} \begin{bmatrix} f_0 \\ f_1 \end{bmatrix}. \tag{2.14}$$

The positive and negative Davio rules can be combined in an expansion of a single switching function.

Remark 2.5 Fixed Polarity Reed-Muller (FPRM) expansions are a generalization of the Positive Polarity Reed-Muller (PPRM) expansions, in which we can choose between either the positive or negative Davio expansion for each variable  $x_i$ .

A Reed-Muller expansion is usually specified by a binary polarity vector  $H=(h_0,...,h_n)$ , where  $h_i \in 0,1$  specifies the polarity for variable  $x_i$ . By convention  $h_i = 0$  implies a negative literal  $\bar{x}_i$ , and  $h_i = 1$  a positive literal  $x_i$ . Expansions for different polarities differ in the number of non-zero coefficients.

**Example 2.10** Consider a binary polarity vector H = (1,0,1). A Fixed Polarity Reed-Muller matrix defined by this vector has the form:

Remark 2.6 A Fixed Polarity Reed-Muller expansion with the minimal number of non-zero coefficients is known as a minimal expansion.

For an n-variable function there are  $2^n$  possible choices of polarities for variables and, therefore,  $2^n$  different Fixed-polarity Reed-Muller expressions. Finding the minimal expansion is an NP-complete problem. There can be more than one minimal Fixed Polarity Reed-Muller expansion for a given function, [9].

We can further extend the concept of a Fixed Polarity Reed-Muller expansion by including the possibility to also choose the Shannon expansion rule for an individual variable  $x_i$ . Since we now have three possible choices, Shannon, positive and negative Davio, the total number of expansions for an n-valued function is  $3^n$ .

Coefficients in these expansions can be calculated using the Kronecker transform matrix defined as:

$$\mathbf{K}(n) = \bigotimes_{i=1}^{n} \mathbf{K}_{i}(1) \tag{2.15}$$

where  $\mathbf{K}_{i}(1)$  can be any of the matrices for S, pD, and nD expansion rules.

The choice of the decomposition rule for the variables of a function is specified using a Decision Type List (DTL).

In a Fixed Polarity Reed-Muller expression, the polarity of a variable is fixed throughout each individual minterm. Each variable can appear as either a positive or negative literal, but never both in a single expression.

Remark 2.7 A Generalized Reed-Muller expression (GRM) is a Reed-Muller-like expression where the polarity of each individual variable can be different in different product terms.

**Example 2.11** Consider a three-variable switching function  $f(x_1, x_2, x_3)$ . The generalized Reed-Muller expression for this function will have the following form

$$f = c_0 \oplus c_1 \widetilde{x}_1 \oplus c_2 \widetilde{x}_2 \oplus c_3 \widetilde{x}_1 \widetilde{x}_2 \oplus c_4 \widetilde{x}_3 \oplus c_5 \widetilde{x}_1 \widetilde{x}_3 \oplus c_6 \widetilde{x}_3 \widetilde{x}_3 \oplus c_7 \widetilde{x}_1 \widetilde{x}_2 \widetilde{x}_3,$$

where  $c_i \in \{0,1\}$  and  $\widetilde{x}_i \in \{x_i, \overline{x}_i\}$ .

There are  $2^{n2^{n-1}}$  possible generalized Reed-Muller expressions for an n variable function, since each input can be  $0, 1, \bar{x}_i$  or  $x_i$ .

Generalized Reed-Muller expressions retain one important constraint. No two product terms may have an identical set of variables. These product terms are called primary products. However, this constraint is not present in EXOR Sum-of-Products expressions (ESOPs), an even more general class of algebraic expressions.

**Definition 2.9** An EXOR Sum-of-Products expression is a sum of arbitrary product terms of the form:

$$f = \bigoplus_{I} \widetilde{x}_1 \widetilde{x}_2 ... \widetilde{x}_n, \tag{2.16}$$

where I is a set of all the possible products, and  $\tilde{x}_i \in \{1, x_i, \bar{x}_i\}$ .

**Example 2.12** For a two-variable switching function f there exists total of 9 EXOR Sum-of-Products expressions:

$$\bar{x}_1\bar{x}_2, \quad \bar{x}_1x_2, \quad \bar{x}_1\cdot 1, \quad x_1\bar{x}_2, x_1\cdot 1, \quad 1\cdot \bar{x}_2, \quad 1\cdot x_2, 1.$$

(2.17)

We are not limited strictly to Boolean operations and Boolean values when dealing with discrete function expansions. For instance, the so-called arithmetic expressions are defined as expressions where the coefficients and the

Table 2.6 Boolean and Arithmetic operations.

| Boolean          | Arithmetic            |  |  |

|------------------|-----------------------|--|--|

| $x_1 \wedge x_2$ | $x_1x_2$              |  |  |

| $x_1 \vee x_2$   | $x_1 + x_2 - x_1 x_2$ |  |  |

| $x_1 \oplus x_2$ | $x_1 + x_2 - 2x_1x_2$ |  |  |

basis functions take values over the field of rational numbers. These expressions are effectively used in the representation of multi-output functions, since it permits their representations by a single expression with integer-valued coefficients polynomial, while bit-level expressions require a separate expression for each output. Further, arithmetic expressions are useful in compact representation of arithmetic circuits as adders, multipliers, and various control circuits.

**Remark 2.8** Arithmetic expansions can be derived if operations in GF(2) are replaced with operations in the field of rational numbers Q. Table 2.6 gives a list of Boolean and the corresponding arithmetic operations.

The values 0 and 1 are treated as rational numbers,  $0, 1 \in Q$ , where Q is the field of rational numbers. These expansions belong to the class of word-level expansions.

For an n-variable function f the arithmetic expansion is defined as:

$$f = \left(\bigotimes_{i=1}^{n} \mathbf{X}_{a}(1)\right) \left(\bigotimes_{i=1}^{n} \mathbf{A}^{-1}(1)\right) \mathbf{F}$$

(2.18)

where,

$$A^{-1}(1) = \begin{bmatrix} 1 & 0 \\ -1 & 1 \end{bmatrix}$$

.

Walsh expansions are another example of word-level expressions.

Walsh expansions for discrete functions are defined in terms of discrete version of Walsh functions, which were introduced in 1923 by J. L. Walsh, [175].

**Definition 2.10** Walsh functions of order n, denoted as wal(w, x),  $x, k \in 0, 1, ..., 2^n$ , are defined as columns of the Walsh matrix:

$$\mathbf{W}(n) = \bigotimes_{i=1}^{n} \mathbf{W}(1) \tag{2.19}$$

where

$$W(1) = \begin{bmatrix} 1 & 1 \\ 1 & -1 \end{bmatrix}$$

.

The expansion of a function f using the Walsh matrix can be expressed in the following form:

$$f = \frac{1}{2} \begin{bmatrix} 1 & 1 - 2\bar{x}_i \end{bmatrix} \begin{bmatrix} 1 & 1 \\ 1 & -1 \end{bmatrix} \begin{bmatrix} f_0 \\ f_1 \end{bmatrix}. \tag{2.20}$$

Increasing the freedom of choice of the form of product terms increases the expressive power of the arithmetic expressions. The number of possible expressions for each function grows, increasing the probability of finding an optimal expression. However, this is also reflected in the computational complexity of the problem. A heuristic approach is necessary as exact algorithms for finding all possible expressions of a given function of a certain class quickly become inefficient for even a relatively small number of variables.

#### 2.2.3 Spectral Techniques