Mona Aghababaeetafreshi

Software Defined Radio Solutions for Wireless

Communications Systems

Julkaisu 1595 • Publication 1595

| Tampereen teknillinen yliopisto. Julkaisu 1595<br>Tampere University of Technology. Publication 1595 |

|------------------------------------------------------------------------------------------------------|

|                                                                                                      |

|                                                                                                      |

|                                                                                                      |

| Mona Aghababaeetafreshi                                                                              |

# **Software Defined Radio Solutions for Wireless Communications Systems**

Thesis for the degree of Doctor of Science in Technology to be presented with due permission for public examination and criticism in Sähkötalo Building, Auditorium SA203, at Tampere University of Technology, on the 23<sup>rd</sup> of November 2018, at 12 noon.

Doctoral candidate: Mona Aghababaeetafreshi

Laboratory of Electronics and Communications Engineering

Faculty of Computing and Electrical Engineering

Tampere University of Technology

Tampere, Finland

Supervisor: Mikko Valkama, Professor

Laboratory of Electronics and Communications Engineering

Faculty of Computing and Electrical Engineering

Tampere University of Technology

Tampere, Finland

Instructor: Jarmo Takala, Professor

Laboratory of Pervasive Computing

Faculty of Computing and Electrical Engineering

Tampere University of Technology

Tampere, Finland

Pre-examiner: Fernando H. Gregorio, Professor

Electric and Computer Engineering The National University of South

Bahía Blanca, Argentina

Pre-examiner and

opponent:

Luigi Carro, Professor Institute of Informatics

Federal University of Rio Grande do Sul

Porto Alegre, Brazil

Opponent: Janne Janhunen, D.Sc.

Solmu Technologies

Oulu, Finland

## **ABSTRACT**

Wireless technologies have been advancing rapidly, especially in the recent years. Design, implementation, and manufacturing of devices supporting the continuously evolving technologies require great efforts. Thus, building platforms compatible with different generations of standards and technologies has gained a lot of interest. As a result, software defined radios (SDRs) are investigated to offer more flexibility and scalability, and reduce the design efforts, compared to the conventional fixed-function hardware-based solutions.

This thesis mainly addresses the challenges related to SDR-based implementation of today's wireless devices. One of the main targets of most of the wireless standards has been to improve the achievable data rates, which imposes strict requirements on the processing platforms. Realizing real-time processing of high throughput signal processing algorithms using SDR-based platforms while maintaining energy consumption close to conventional approaches is a challenging topic that is addressed in this thesis.

Firstly, this thesis concentrates on the challenges of a real-time software-based implementation for the very high throughput (VHT) Institute of Electrical and Electronics Engineers (IEEE) 802.11ac amendment from the wireless local area networks (WLAN) family, where an SDR-based solution is introduced for the frequency-domain baseband processing of a multiple-input multiple-output (MIMO) transmitter and receiver. The feasibility of the implementation is evaluated with respect to the number of clock cycles and the consumed power. Furthermore, a digital front-end (DFE) concept is developed for the IEEE 802.11ac receiver, where the 80 MHz waveform is divided to two 40 MHz signals. This is carried out through time-domain digital filtering and decimation, which is challenging due to the latency and cyclic prefix (CP) budget of the receiver. Different multi-rate channelization architectures are developed, and the software implementation is presented and evaluated in terms of execution time, number of clock cycles, power, and energy consumption on different multi-core platforms.

Secondly, this thesis addresses selected advanced techniques developed to realize inband full-duplex (IBFD) systems, which aim at improving spectral efficiency in today's congested radio spectrum. IBFD refers to concurrent transmission and reception on the same frequency band, where the main challenge to combat is the strong self-interference (SI). In this thesis, an SDR-based solution is introduced, which is capable of real-time mitigation of the SI signal. The implementation results show possibility of achieving real-time sufficient SI suppression under time-varying environments using low-power, mobile-scale multi-core processing platforms.

To investigate the challenges associated with SDR implementations for mobile-scale devices with limited processing and power resources, processing platforms suitable for hand-held devices are

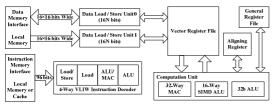

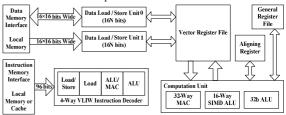

ii Abstract

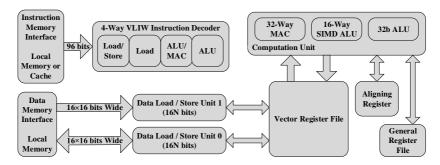

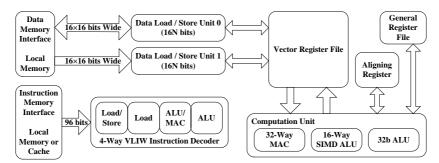

selected in this thesis work. On the baseband processing side, a very long instruction word (VLIW) processor, optimized for wireless communication applications, is utilized. Furthermore, in the solutions presented for the DFE processing and the digital SI canceller, commercial off-the-shelf (COTS) multi-core central processing units (CPUs) and graphics processing units (GPUs) are used with the aim of investigating the performance enhancement achieved by utilizing parallel processing.

Overall, this thesis provides solutions to the challenges of low-power, and real-time software-based implementation of computationally intensive signal processing algorithms for the current and future communications systems.

## **PREFACE**

This thesis is based on the research work carried out during the years 2014–2017 in the Laboratory of Electronics and Communications Engineering, Tampere University of Technology, Tampere, Finland. I would like to gratefully acknowledge the financial support I received from the Tampere University of Technology Graduate School (during the years 2014–2017), Nokia Foundation, and Tuula and Yrjö Neuvo Research Fund. The research work carried out for this thesis was also partially supported by the Finnish Funding Agency for Technology and Innovation (TEKES) under the Parallel Acceleration (ParallaX) project.

First and foremost, I would like to sincerely thank my supervisors Prof. Mikko Valkama and Prof. Jarmo Takala for their invaluable help, guidance, and support during these years. It has been a privilege to learn from their extensive knowledge and experience. I am also very grateful to Prof. Luigi Carro and Prof. Fernando Gregorio for acting as the pre-examiners of this thesis, and providing their valuable comments and insights. Furthermore, I wish to thank Prof. Luigi Carro and D.Sc. Janne Janhunen for agreeing to act as the opponents in the public examination of this thesis.

I am also very grateful to D.Sc. Toni Levanen, D.Sc. Pekka Jääskeläinen, and D.Sc. Dani Korpi for sharing their deep knowledge in this field with me along the way. In addition, I wish to thank my co-authors Lasse Lehtonen, Matias Koskela, D.Sc. Juha Yli-Kaakinen, and Maliheh Soleimani for our fruitful collaborations.

I would also like to thank all my friends, especially Parinaz, Kamiar, Nader, Afsaneh, Saeed, and Sajjad who have always lifted my spirits and made life much more fun from the very first days of my studies in Tampere.

Finally, my deepest and most sincere thanks go to my parents, who have never stopped supporting and encouraging me in life. None of this would have been possible without their endless love and support. And last but not least, I would like to express my warmest thanks to Orod. There are no words to describe how grateful I am to have him both in my personal and professional life.

Espoo, October 2018

Mona Aghababaeetafreshi

## **Contents**

| At | ostrac  | t        |             |                                        | ì   |

|----|---------|----------|-------------|----------------------------------------|-----|

| Pr | eface   |          |             |                                        | iii |

| Ac | crony   | ms       |             |                                        | vii |

| Li | st of 1 | Publicat | ions        |                                        | xi  |

| 1  | Intr    | oduction |             |                                        | 1   |

|    | 1.1     | Object   | ives and So | cope of the Work                       | . 3 |

|    | 1.2     |          |             | l Outline                              |     |

|    | 1.3     | Author   | 's Contrib  | utions                                 | . 4 |

| 2  | Wir     | eless Te | chnologies  | S                                      | 7   |

|    | 2.1     |          |             | 02.11ac                                | . 7 |

|    |         | 2.1.1    |             | of WiFi                                |     |

|    |         | 2.1.2    | •           | 2.11ac Features                        |     |

|    |         | 2.1.3    | IEEE 802    | 2.11ac PHY Packet Structure            | . 9 |

|    |         | 2.1.4    |             | 2.11ac Baseband Processing             |     |

|    |         |          | 2.1.4.1     | Transmitter Processing                 |     |

|    |         |          | 2.1.4.2     | Receiver Processing                    |     |

|    |         | 2.1.5    | IEEE 802    | 2.11ac Digital Front-End Processing    |     |

|    |         |          | 2.1.5.1     | Polyphase Halfband Filters             |     |

|    |         |          | 2.1.5.2     | Cyclic Polyphase Halfband Filters      |     |

|    | 2.2     | Future   | Wireless S  | Systems and Full-Duplex Communication  |     |

|    |         | 2.2.1    |             | lex Communication                      |     |

|    |         |          | 2.2.1.1     | Digital Self-Interference Cancellation |     |

|    |         |          | 2.2.1.2     | Self-Interference Modelling            |     |

|    |         |          | 2.2.1.3     | Orthogonalization                      |     |

|    |         |          | 2.2.1.4     | LMS Parameter Learning                 |     |

| 3  | SDR     | Solutio  | ns for Wi   | Fi                                     | 27  |

| •  | 3.1     |          |             |                                        |     |

|    | 3.2     |          |             | sing                                   |     |

|    |         | 3.2.1    |             | sion Scenarios                         |     |

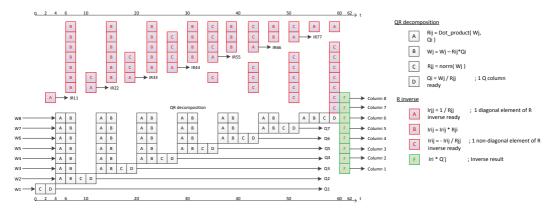

|    |         | 3.2.2    |             | tor for Matrix Inversion               |     |

|    |         | 3.2.3    |             |                                        |     |

|    | 3.3     | Digital  |             | d Processing                           |     |

|    |         | 3.3.1    |             | zation Filtering                       |     |

vi

|     |        |         | 3.3.1.1 Halfband Filters                        | 37 |

|-----|--------|---------|-------------------------------------------------|----|

|     |        |         | 3.3.1.2 Non-Halfband Filters                    | 38 |

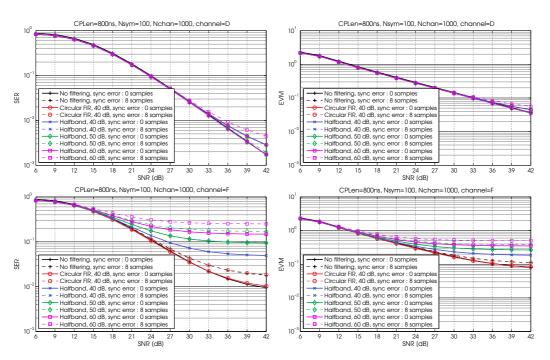

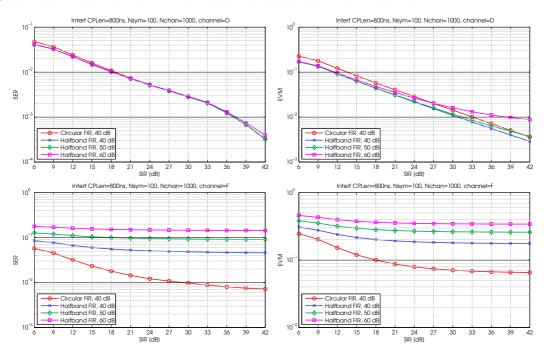

|     |        | 3.3.2   | Results                                         | 39 |

| 4   | SDR    | Solutio | ons for Full-Duplex Communications              | 43 |

|     | 4.1    | Related | d Work                                          | 44 |

|     | 4.2    | Digital | Self-Interference Cancellation                  | 45 |

|     | 4.3    | -       | ·                                               |    |

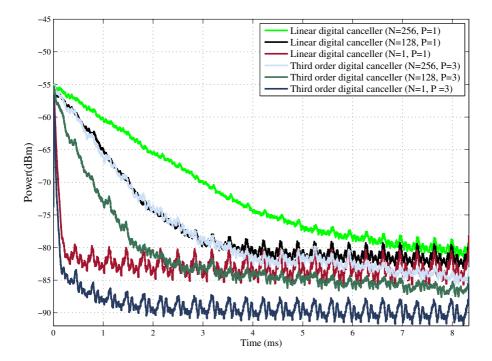

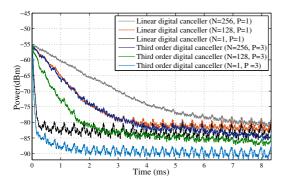

|     |        | 4.3.1   | Digital Self-Interference Canceller Performance |    |

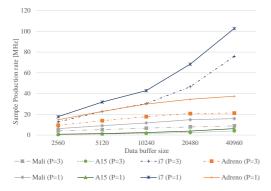

|     |        | 4.3.2   | Execution Time                                  |    |

|     |        | 4.3.3   | Delay                                           |    |

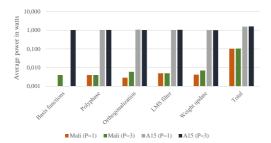

|     |        | 4.3.4   | Power Consumption                               |    |

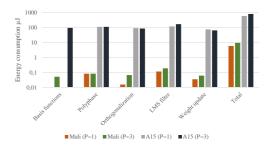

|     |        | 4.3.5   | Energy Consumption                              |    |

| 5   | Con    | clusion |                                                 | 55 |

|     | 5.1    | Summa   | ary and Main Results                            | 55 |

|     | 5.2    |         | Work                                            |    |

| Bil | bliogr | aphy    |                                                 | 57 |

| Pu  | blicat | tions   |                                                 | 65 |

## **ACRONYMS**

**5G** fifth generation

**6G** sixth generation

**ALU** arithmetic logic unit

**ANPI** average noise power indicator

AP access point

**ASIC** application specific integrated circuit

**ASIP** application specific instruction-set processor

**BCC** binary convolutional codes

**BW** bandwidth

**COTS** commercial off-the-shelf

**CP** cyclic prefix

**CPU** central processing unit

**CS** carrier sensing

**CSD** cyclic shift diversity

**DFE** digital front-end

**DRAM** dynamic random-access memory

**DSP** digital signal processing

**FDD** frequency-division duplexing

**FEC** forward error correction

**FFT** fast Fourier transform

**FIR** finite impulse response

viii Acronyms

**FPGA** field-programmable gate array

**GI** guard interval

**GPP** general-purpose processor

**GPU** graphics processing unit

**GSM** global system for mobile communications

**HARQ** hybrid automatic repeat request

**HSPA** high speed packet access

HT high throughput

I/Q in-phase/quadrature

**IBFD** inband full-duplex

**IEEE** Institute of Electrical and Electronics Engineers

**IFFT** inverse fast Fourier transform

**ISM** industrial, scientific, and medical

**L-LTF** non-HT long training field

L-SIG non-HT SIGNAL field

**L-STF** non-HT short training field

LAN local area networking

**LDPC** low-density parity check

LMMSE linear minimum mean square error

LMS least mean squares

LNA low-noise amplifier

**LS** least square

LTE long-term evolution

LUT lookup table

MAC medium access control

MIMO multiple-input multiple-output

MU multi-user

**NDP** null data packet

NR new radio

**OFDM** orthogonal frequency-division multiplexing

**OpenCL** open computing language

**PA** power amplifier

**PE** processing element

PHY physical

QAM quadrature amplitude modulation RCPI received channel power indicator

**RF** radio frequency

**RSNI** received signal to noise indicator

**SDR** software defined radio

**SI** self-interference

**SIMD** single instruction multiple data

**SoC** system on chip

**SPMD** single program, multiple data

**STBC** space-time block codes

**SVD** singular value decomposition

**TDD** time-division duplexing

**UE** user equipment

**UMTS** universal mobile telecommunications system

VHDL VHSIC hardware description language

VHT very high throughput

VHT-LTF VHT long training field

VHT-SIG-A VHT signal A field

VHT-SIG-B VHT signal B field

VHT-STF VHT short training field

**VLIW** very long instruction word

WCDMA wideband code division multiple access

**WLAN** wireless local area networks

## LIST OF PUBLICATIONS

- [P1] M. Aghababaeetafreshi, L. Lehtonen, M. Soleimani, M. Valkama and J. Takala, "IEEE 802.11AC MIMO transmitter baseband processing on customized VLIW processor," in *IEEE International Conference on Acoustics, Speech and Signal Processing*, Florence, Italy, May 4-9, 2014, pp. 7500-7504, doi: 10.1109/ICASSP.2014.6855058.

- [P2] M. Aghababaee Tafreshi, L. Lehtonen, T. Levanen, M. Valkama and J. Takala, "IEEE 802.11ac MIMO receiver baseband processing on customized VLIW processor," in *IEEE Workshop on Signal Processing Systems*, Belfast, UK, Oct. 22-24, 2014, pp. 1-6, doi: 10.1109/SiPS.2014.6986092.

- [P3] M. Aghababaeetafreshi, L. Lehtonen, T. Levanen, M. Valkama and J. Takala, "IEEE 802.11ac MIMO transceiver baseband processing on a VLIW Processor", *Journal of Signal Processing Systems*, Oct 2016, 85(1), pp. 167–182, doi: 10.1007/s11265-015-1032-2.

- [P4] M. Aghababaeetafreshi, J. Yli-Kaakinen, T. Levanen, V. Korhonen, P. Jääskeläinen, M. Renfors, M. Valkama and J. Takala, "Parallel processing intensive digital front-end for IEEE 802.11ac receiver," in 49th Asilomar Conference on Signals, Systems and Computers, Pacific Grove, CA, USA, 8-11 Nov, 2015, pp. 1619-1626, doi: 10.1109/ACSSC.2015.7421422.

- [P5] M. AghababaeeTafreshi, M. Koskela, D. Korpi, P. Jääskeläinen, M. Valkama and J. Takala, "Software defined radio implementation of adaptive nonlinear digital self-interference cancellation for mobile inband full-duplex radio," in *IEEE Global Conference on Signal and Information Processing*, Washington, DC, USA, 7-9 Dec, 2016, pp. 733-737, doi: 10.1109/GlobalSIP.2016.7905939.

- [P6] M. Aghababaeetafreshi, D. Korpi, M. Koskela, P. Jääskeläinen, M. Valkama and J. Takala, "Software defined radio implementation of a digital self-interference cancellation method for inband full-duplex radio using mobile processors," *Journal of Signal Processing Systems*, Oct 2018, 90(10), pp. 1297–1309, doi: 10.1007/s11265-017-1312-0.

## **CHAPTER 1**

## INTRODUCTION

With the rapid evolution of wireless network standards, emerges the need for more flexible radios, which can easily adapt to new technologies. For this reason, the concept of software defined radios (SDRs) was introduced in the early 1990s [1], and is still being developed to this day. The aim of SDRs is to liberate the radio implementation from the restrictions of a hard-wired system, which, as a result, introduces a high degree of flexibility and programmability that cannot be achieved with the traditional solutions using fixed-function hardware-based approaches.

In addition to offering higher flexibility, SDRs reduce the design efforts considerably, and thus time-to-market cycles are shortened compared to application-specific solutions. Furthermore, designing platforms that could support different existing, and even upcoming standards increases significantly the costs and complexity of the implementation process. Consequently, SDR-based approaches can, in general, minimize the efforts and costs of design, fabrication, testing, and maintenance [2, 3].

With SDRs, the characteristics of the radio system, such as bandwidth (BW), air interface protocol, and functionality would no longer be static. However, the behavior of the radio can be dynamically modified through software. In other words, a new software upgrade can update the operation of the radio, rather than having to replace the whole hardware. This facilitates the development of a multi-standard, multi-band, and multi-functional systems, which, for example, can operate with different carrier frequencies, BWs, modulation schemes, and coding rates [4]. As a result, a future can be realized, in which the radio system can be re-configured in the field to operate in a different frequency band or transmission scenario. Furthermore, SDRs promise to facilitate deployment of new features and functionalities with the rapid development of technologies.

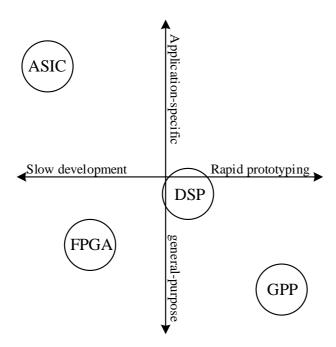

Some of the characteristics of an SDR architecture include re-programmability, scalability, and flexibility. Additionally, SDRs are usually associated with commercially available and affordable platforms, which support low cost and fast market delivery goals. SDR platforms range from general-purpose processors (GPPs) and graphics processing units (GPUs) to digital signal processing (DSP) cores, each offering different degrees of flexibility and development cycles. Fig. 1.1 provides a perspective into the trade-off between reconfigurability and development time for some known platforms [4, 5]. One important advantage of GPPs is the very low programming complexity, which allows for much faster prototyping compared to the other platforms. DSPs, on the other hand, offer great processing performance, however, they are considered less general

Figure 1.1: Trade-off between reconfigurability and development cycles in different platforms

purpose than field-programmable gate arrays (FPGAs) and GPPs, as they are optimized for digital signal processing algorithms.

In today's radio systems, programmable dedicated hardware is typically used for the main processing tasks, particularly at physical layer, while control tasks are carried out using GPPs. However, ideally, in an entirely software-defined system, all the radio functionality could be implemented on general-purpose processing platforms, and only antennas, basic amplification and coarse filtering stages, and digital-to-analogue and analogue-to-digital converters would be added. Realizing such systems comes with many challenges which need to be studied and overcome.

Application specific hardware platforms are believed to provide better performance compared to flexible software-based solutions as they are tailored to a dedicated functionality. Furthermore, being customized for specific operations means less area on the silicon, and consequently lower power consumption. Thus, the feasibility of the software-based solutions as a more flexible, yet efficient, alternative to the application specific integrated circuits (ASICs) is an interesting research area.

With the ever-growing amount of wireless data and its applications, wireless networks are constantly evolving to meet the demands for higher capacity and more efficiency. One of the most widely used wireless connectivity standards is the Institute of Electrical and Electronics Engineers (IEEE) 802.11 wireless local area networks (WLAN) family, which is continuously developing. Thus, utilization of software-based solutions in this area can considerably accelerate the progress, improve service life-cycle, and portability to other platforms.

The state of the art technology in the WLAN family is the IEEE 802.11ac. The 802.11ac amendment is designed to significantly improve the throughput to above gigabit ranges. This is achieved by using wider bandwidth, up to 160 MHz, in the 5 GHz industrial, scientific, and medical (ISM) band. Furthermore, higher order modulation, up to 256-quadrature amplitude modulation (QAM), and multi-user (MU) multiple-input multiple-output (MIMO) with up to eight

spatial streams are defined in the standard specification [6, 7]. A software-based implementation of the IEEE 802.11ac transceiver can offer high degree of flexibility in terms of adjusting the bandwidth, modulation order, coding rate, and MIMO configuration.

As available spectral resources for wireless communications are scarce, pursuing high spectral efficiency is a common target for most of the wireless standards. As a result, different technologies are being studied and developed which help to improve the efficiency of spectrum use, e.g., inband full-duplex (IBFD) communications. Full-duplex communication systems can utilize the spectral resources more efficiently by transmitting and receiving simultaneously on the same frequency within the same device, while in more ordinary duplexing methods, transmission and reception are based on sharing either the time-domain (time-division duplexing (TDD)) or frequency-domain (frequency-division duplexing (FDD)) resources. Thus, IBFD systems can potentially double spectral efficiency compared to traditional duplexing systems. However, deployment of these systems comes with challenge, particularly the inherent self-interference (SI) [8–11].

The cancellation of the SI signal is, in theory, rather simple as the transmitted signal is known by the transceiver. However, in practice, it is far more challenging since the overall effective coupling channel is not accurately known [12]. Furthermore, the system should dynamically adapt to the constantly changing environment, especially around a mobile device, which could benefit from the flexibilities offered by SDRs.

#### 1.1 Objectives and Scope of the Work

This thesis addresses current and future wireless technologies and the challenges related to their implementation. The demanding requirements of these technologies, such as very high throughput, has led to very strict timing constraints for the implementation platforms. These constraints are even more challenging in case of mobile terminals with less processing and power resources. In the work carried out in this thesis, we target processing platforms which are suitable for hand-held devices.

This research work evaluates the implementation of different computationally intensive digital signal processing algorithms from physical (PHY) layer baseband and digital front-end (DFE) processing of the IEEE 802.11ac standard to full-duplex communications systems on different mobile-scale platforms. The solutions are examined in terms of performance, power, and energy consumption to investigate, the extent to which these solutions can be utilized in today's communications systems.

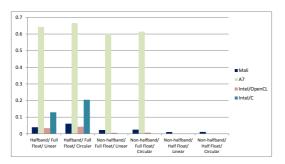

In this thesis work, a very long instruction word (VLIW) processor, specifically designed for wireless communication applications, is selected for the IEEE 802.11ac baseband processing. For the DFE channelization concept and the SI canceller implementation, multi-core general-purpose central processing units (CPUs) and GPUs are used to investigate the performance enhancement achieved by utilizing parallel processing. This topic has gained a lot of interest since clock rate scaling and aggressive uniprocessor performance scaling has reached its limits [13].

The main target of the research carried out during the work of this thesis is to develop and analyze software-based solutions for the implementation of the aforementioned computationally intensive algorithms on selected processors. Mainly, commercial off-the-shelf (COTS) platforms are adopted, which highlight the benefits of SDR based implementations. Then, the feasibility of the proposed solutions for achieving real-time operation is investigated. Furthermore, power and energy consumption are measured to evaluate the viability of the implementations.

The feasibility of the proposed solutions is studied by measuring the performance of the implementations. The objective is to deliver reprogrammable solutions that can provide real-time processing,

while consuming relatively low power/energy suitable for mobile devices. The SDR-based implementation is declared feasible when execution times and consumed power/energy are less or comparable with the traditional fixed-function implementations. In case of mobile-scale devices, where processing and energy resources are more limited, the requirements are even more strict. This thesis proposes software-based solutions that can meet the tight timing and power/energy consumption requirements of today's wireless standards while offering high flexibility.

#### 1.2 Main Results and Outline

The main contributions of the Thesis can be highlighted as follows:

- A software-based solution for the MIMO transmitter and receiver baseband processing conforming to the IEEE 802.11ac standard is proposed, and the feasibility of achieving a real-time operation using a customized VLIW processor is shown by manually optimizing the implementation and exploiting the processor intrinsic instructions [P1][P2][P3].

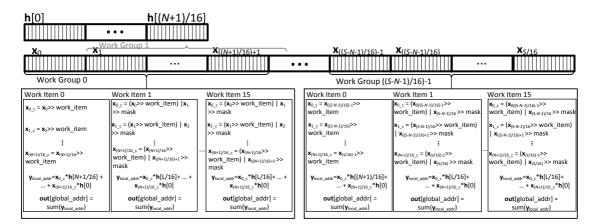

- A DFE concept to divide the 80 MHz bandwidth of the IEEE 802.11ac is introduced, which uses circular and linear filtering based multi-rate channelization architectures. Additionally, an SDR implementation on mobile-scale COTS CPUs and GPUs is presented and analyzed, which is optimized by exploiting the parallel resources of the processors [P4].

- A self-adaptive nonlinear digital self-interference cancellation method for full-duplex transceivers is presented. Furthermore, an SDR based implementation is proposed for the SI canceller, which optimally parallelizes the computing resources of multi-core CPUs and GPUs for better performance [P5][P6].

- In all of the above cases, implementations are evaluated and the performance results are reported.

This thesis is divided into five chapters. Chapter 2 provides an introduction to the wireless technologies investigated in the scope of this thesis and presents the implemented algorithms. Chapter 3 describes the proposed implementations for IEEE 802.11ac baseband and DFE processing, where the main existing challenges are explained and solutions are provided. Then the performance of the implementations is evaluated and the results are reported in terms of execution time, and power/energy consumption. Chapter 4 gives a detailed description of the implementation methods for an adaptive digital SI canceller method used in IBFD systems. The corresponding challenges are pointed out and addressed, and finally the implementation results are discussed and analyzed. Chapter 5 presents the conclusions and discusses open issues and future directions.

#### 1.3 Author's Contributions

The Author of the Thesis has been the main author in all the publications [P1]-[P6]. In [P1]-[P3], the Author of this thesis has done mathematical algorithm modifications to reduce the computational complexity of the algorithms for implementation purposes. The author has carried out the software implementation for the algorithms and further manual optimizations for better performance on the selected platforms using the processor's intrinsic instructions. Additionally, all the performance measurements have been done by the Author.

In [P4], the Author has designed and optimized the open computing language (OpenCL) kernels implementing the channelization filters. The Author has also carried out the measurements related to the implementation performance.

5

In [P4]-[P6], the Author has done the software implementations and manual optimizations for parallel processing on the selected multi-core platforms. The author has modified parts of the original methods with the aim of reducing the computational complexity of the algorithms to fit the available processing resources of the selected COTS platforms. Furthermore, the performance evaluations for the implementations were carried out by the Author.

## **CHAPTER 2**

## WIRELESS TECHNOLOGIES

Wireless communication systems continue to evolve to provide faster, more reliable and more energy efficient connectivity to Internet and other wireless applications. Based on the current predictions, the overall amount of wireless data will increase exponentially in the coming years. This, along with the numerous new wireless applications emerging everyday have resulted in the need for great advances and improvements in the future generations of wireless standards. In this chapter, first the IEEE 802.11ac, a leading WLAN technology is introduced. Then, addressing one of the most important issues in wireless networks, i.e. limited spectral resources, IBFD communication systems, and the corresponding challenges and solutions are described.

#### **2.1** WiFi and IEEE 802.11ac

WiFi is a local area networking (LAN) technology for wireless connectivity, which provides indoor broadband coverage for fixed, portable, and mobile stations. WiFi is developed by IEEE standards association and promoted by the WiFi Alliance<sup>®</sup>. First IEEE 802.11<sup>TM</sup> standard was published in 1999, and since then it has been growing through different amendments to meet the high demands for more traffic, increasing number of devices, and new applications [14].

#### 2.1.1 History of WiFi

Introduced in 1999, the IEEE 802.11b with maximum raw data rate of 11 Mbps using the 2.4 GHz band, established a basis for the WiFi industry. However, with the growing popularity, and thus the big market for WiFi, grew the expectations for higher data rates, better quality, and more security [15]. Thus, new amendments had to be developed to add support for higher data density and new applications.

The next amendment, the IEEE 802.11a, operated in the 5 GHz band and increased the throughput to 54 Mbps. However, due to lack of backward compatibility with the 2.4 GHz band used in 802.11b devices, it required two radios, and thus failed to gain a big market.

The amendment which followed 802.11a was the IEEE 802.11g. Similar to the 802.11b, this amendment used the 2.4 GHz band, and was able to achieve data rates up to 54 Mbps using

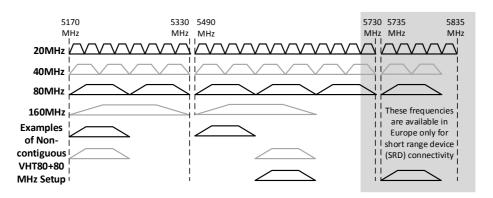

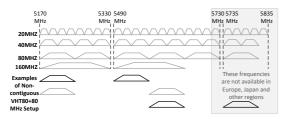

Figure 2.1: The different channelization configurations for the IEEE 802.11ac at the 5 GHz band

orthogonal frequency-division multiplexing (OFDM). Unlike the 802.11a, the 802.11g was backward compatible with 802.11b, and became a big success.

As WiFi Continued to develop, the IEEE 802.11n amendment was introduced with higher data rates, bigger range, improved security, and more reliability. The 802.11n standardized the use of MIMO and was able to yield a throughput of 150 Mbps. Both 2.4 and 5 GHz bands were supported by this amendment and it took advantage of a 40 MHz bandwidth. The 802.11n was also known as the high throughput (HT) amendment.

Next section describes the IEEE 802.11ac, also referred to as the very high throughput (VHT) amendment, and its main improvements compared to the 802.11n. The higher performance delivered by the 802.11ac opened the door to various new application areas. As an example, high definition video streaming is made possible, which was a challenge for the existing 802.11n devices.

#### **2.1.2 IEEE 802.11ac Features**

The IEEE 802.11ac amendment aims to provide extremely higher throughput and better user experience quality compared to its predecessor. For this reason, the 802.11ac has adopted several new techniques to improve its performance, some of which are briefly introduced in the following.

More Channel Bonding The IEEE 802.11ac supports channel bonding up to 160 MHz. Thus, two non-overlapping adjacent 40 MHz channels can be used to form an 80 MHz channel. Furthermore, two 80 MHz channels can be used to form either a contiguous or non-contiguous 160 MHz channel. The use of the 160 MHz channel is not mandatory in this amendment. The possibility of a non-contiguous channel setup provides more flexibility for channel assignment in 802.11ac [16]. Examples of different channelization configurations for the 802.11ac at 5 GHz band can be seen in Fig. 2.1.

**Mandatory 5 GHz Operation** The previous amendments mostly operated in the 2.4 GHz band, and the 802.11n supported the optional use of 5 GHz band. However, as a result of the legacy WiFi devices crowding the 2.4 GHz band, this band is susceptible to higher interference. Furthermore, more non-overlapping channels are available in the 5 GHz band, which provides more flexibility for channel assignment. Thus, the IEEE 802.11ac mandates operation in the 5 GHz band [17].

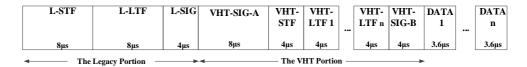

Figure 2.2: IEEE 802.11ac PHY layer packet structure assuming short GI for the data symbols.

**Higher Order Modulation** The IEEE 802.11ac allows use of denser modulation schemes compared to its predecessors. Increasing from the 64-QAM used in the 802.11n, this amendment supports constellation configurations up to 256-QAM, yielding up to 33% increase in data rates [7].

**Higher Order MIMO** While the HT amendment, the first to introduce MIMO in WiFi specifications, allowed four spatial streams, the VHT adds support for up to eight spatial streams. This improvement can double the total network throughput compared to the 802.11n [17].

**Multi-User MIMO** The IEEE 802.11ac is the first amendment to introduce MU-MIMO. This feature allows multiple users to be scheduled in the same time-slot, which means that the access point transmitter can simultaneously transmit multiple packets to multiple users by diving the available streams among the stations.

#### 2.1.3 IEEE 802.11ac PHY Packet Structure

The PHY layer packet defined in the IEEE 802.11ac consists of a header and a data part. The header itself comprises of non-HT (legacy) and VHT fields. The legacy field includes non-HT short training field (L-STF), non-HT long training field (L-LTF), and non-HT SIGNAL field (L-SIG). VHT signal A field (VHT-SIG-A), VHT short training field (VHT-STF), VHT long training field (VHT-LTF), and VHT signal B field (VHT-SIG-B) are the VHT specific portions. The PHY layer packet structure defined in this specification can be seen in Fig. 2.2, where the duration of each field, assuming a short guard interval (GI) for the data symbols, is shown.

#### 2.1.4 IEEE 802.11ac Baseband Processing

This section describes the transceiver functional blocks of the IEEE 802.11ac baseband processing which were included in the works carried out for this thesis.

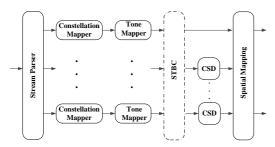

#### 2.1.4.1 Transmitter Processing

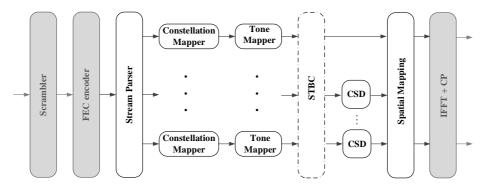

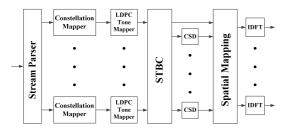

In this section, only the transmitter processing related to DATA symbols is covered, as the processing of preamble symbols is rather straight-forward, and thus less computationally intensive. Fig. 2.3 illustrates the building blocks related to the processing of a DATA symbol, where the grey colored blocks are not included in the work of this thesis.

It is assumed that, first, the bits are scrambled, and then encoded in the forward error correction (FEC) unit, using either binary convolutional codes (BCC) or low-density parity check (LDPC) codes. The high complexity encoding is to be carried out on a separate hardware accelerator. Then, the rest of the processing is performed using our proposed software-based solution. At the final stage, inverse fast Fourier transform (IFFT) is executed on a dedicated hardware, after which the time-domain processing starts.

**Figure 2.3:** Principal block diagram of the IEEE 802.11ac transmitter baseband processing. The blocks marked with grey color are not included in the software-based implementation.

The functionality of the transmitter blocks, implemented in the work of this thesis, are briefly explained in the following.

**Stream Parsing** To create the required number of spatial streams, the incoming bits from the encoder are divided into the number of spatial streams  $(N_{ss})$ . Each stream receives a group of s bits in a round robin fashion, as defined in (2.1).

$$s = max \left\{ 1, \frac{N_{BPSCS}}{2} \right\} \tag{2.1}$$

Here,  $N_{BPSCS}$  is the number of coded bits per single subcarrier for each spatial stream and is equivalent to the modulation order.

According to (2.1), having 256-QAM modulation, s would be equal to four. Thus, in case of  $N_{ss}=2$ , each of the two streams receives a block of four bits in each round, thus dividing the incoming bit stream  $[y_0, y_1, y_2, \ldots, y_i]$  into streams of  $[y_0, y_1, y_2, y_3, y_8, y_9, \ldots]$ , and  $[y_4, y_5, y_6, y_7, y_{12}, y_{13}, \ldots]$ .

**Modulation Mapping** Each group of  $N_{BPSCS}$  bits received from the stream parser are mapped to constellation points. BPSK, 16-QAM, 64-QAM, or 256-QAM with Gray-coded mapping can be used as the modulation scheme. The resulting complex numbers are normalized by a factor of  $K_{mod}$ . Thus, output values are calculated as:

$$d_{mod} = (I + Qj) \times K_{mod}. \tag{2.2}$$

With 256-QAM, the modulation scheme employed in this work, we have:  $K_{mod} = \frac{1}{\sqrt{170}}$  [7].

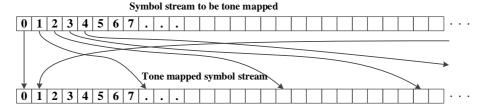

**LDPC Tone Mapping** Since LDPC coding is selected as the FEC method here, LDPC tone mapping should be carried out after the modulation. The purpose of tone mapping is to achieve full frequency diversity in 80 MHz and 160 MHz bands. The tone mapper places the received consecutive constellations at tones with distance  $D_{TM}$  from each other. The LDPC tone mapping distance parameter  $D_{TM}$  is constant for each bandwidth. Fig. 2.4 illustrates the tone mapping process assuming 80 MHz bandwidth ( $D_{TM} = 9$ ).

Figure 2.4: The tone mapping process for 80 MHz bandwidth

**STBC Coding** A generalized version of the well-known Alamouti codes [18], space-time block codes (STBC), is performed at this stage. Space-time coding exploits spatial and temporal diversity by transmitting multiple copies of a data stream over different antenna streams. This helps to compensate for multipath fading, and as a result, higher reliability and robustness of data transmission is achieved. STBC codes are orthogonal and can achieve full diversity.

Having a two-antenna configuration with one spatial stream, STBC coding is performed as follows. At time instance  $t_1$ , antenna 1 and antenna 2 transmit symbols  $x_1$  and  $x_2$ , respectively. Then, at time instance  $t_2 = t_1 + T$ , symbols  $-x_2^*$  and  $x_1^*$  are transmitted from antenna 1 and antenna 2, respectively. Here, T is the symbol duration, and  $x^*$  represents the complex conjugate of symbol x.

**CSD** Cyclic shifts, referred to as cyclic shift diversity (CSD), are performed on the signal in order to decorrelate space-time streams. As a result, there will be a large phase shift between the signals transmitted from different antennas, and unwanted beamforming is avoided. These phase shifts are translated to delays in time-domain. Different shift values are used for VHT and non-VHT fields.

**Spatial Mapping** This last step performs a mapping between the space-time streams and the antennas. Thus, the final signals to be transmitted are produced at this stage. In the scope of this work, space-time streams are mapped to the transmit antennas directly after getting scaled by a normalization factor. Scaling factor is defined as  $\sqrt{N_{STS}}$ , where  $N_{STS}$  is the number of space-time streams.

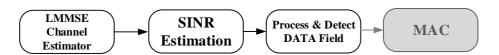

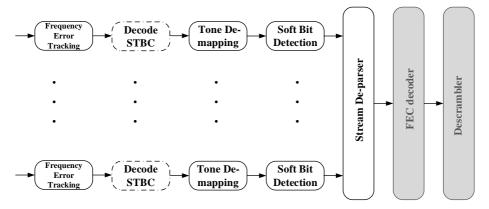

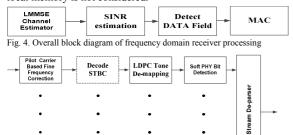

#### 2.1.4.2 Receiver Processing

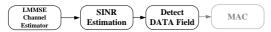

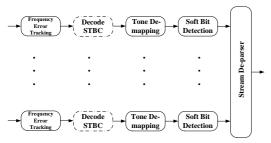

In the receiver side, it is assumed that, first, time-domain processing is carried out, and then fast Fourier transform (FFT) is performed in a dedicated hardware unit. The samples then go through the processing implemented in the work of this thesis, shown in Fig. 2.5 and Fig. 2.6. Finally, at the last stage, LDPC decoding and descrambling are carried out in a separate hardware.

As the received preamble symbols are used to measure received signal quality and estimate the channel, the processing carried out on these symbols in the receiver is much more complex than

Figure 2.5: Overall logical block diagram of the receiver side processing

**Figure 2.6:** Principal block diagram of the IEEE 802.11ac receiver baseband processing. The blocks marked with grey color are not included in the software-based implementation.

the transmitter side. Thus, the receiver processing related to the preamble symbols is described in this section in addition to the DATA processing.

The stream de-parser and LDPC tone de-mapper blocks in the receiver simply reverse the functionality of their counter blocks in the transmitter. Thus, they are left out from the discussions of this section.

The functionality of the receiver blocks, implemented in the work of this thesis, are briefly explained in the following.

**SINR Estimation** SINR measurement is carried out in the receiver to evaluate the quality of the received signal. This information then can be sent to the transmitter to adjust the transmit power, or the modulation and coding scheme. The calculated indicators are received channel power indicator (RCPI), average noise power indicator (ANPI), and the received signal to noise indicator (RSNI).

RCPI RCPI measures the received radio frequency (RF) power in the channel, which includes the signal, noise, and interference. It is measured over the DATA portion of the received frame. However, if a null data packet (NDP) is received, VHT-SIG-B or VHT-LTF symbols can be used. The power is measured over all active non-pilot subcarriers and is then averaged over all antennas. Thus, RCPI can be calculated as:

$$RCPI = \frac{1}{N_{R_x} N_{sc} N_d} \sum_{R_x} \sum_{d} \sum_{i \in I} |y_{R_x, d, i}|^2,$$

(2.3)

where  $R_x = 1, 2, \dots, N_{R_x}$  is the receiver antenna index,  $d = 1, 2, \dots, N_d$  is the DATA symbol index, and  $N_{sc} = |I_{active, non-pilot\ subcarriers}|$ , where |I| is the cardinality of the set I

In this implementation, calculation is carried out after reception of each DATA symbol, and the average is updated with every symbol until reception of the whole frame is completed.

**ANPI** ANPI is a medium access control (MAC) layer indicator, which calculates average noise plus interference power, and is used for symbol detection. ANPI can be measured when the channel is idle as defined by three simultaneous conditions: 1) the virtual carrier

sensing (CS) mechanism indicates idle channel, 2) the station (STA) is not transmitting a frame, and 3) the STA is not receiving a frame [14].

ANPI can be calculated over any received frame during any period. In this work, it is calculated over non-DC null subcarriers. L-STF and VHT-STF are selected for ANPI measurement, as these symbols include many zero-valued subcarriers, in addition to the non-active carriers. This means that any change in their values can be considered as noise. Thus, ANPI can be written as:

$$ANPI = \frac{1}{N_{R_x} N_z} \sum_{N_{R_x}} \sum_{N_{i \in I}} |y_{R_x, i}|^2, \qquad (2.4)$$

where  $N_z = |I_{active, zero-valued pilot subcarriers}|$ .

For the purpose of this measurement, we assume that the accuracy of time and frequency synchronization is enough, in a way that zero-valued subcarriers would be only carrying noise.

**RNSI** RSNI is the signal to noise plus interference ratio of a received frame as defined in [14]. Having calculated RCPI and ANPI, RNSI can be written as:

$$RSNI = 10\log_{10}\frac{RCPI - ANPI}{ANPI},$$

(2.5)

where ANPI and RCPI are in linear scale. Averaging RCPI, ANPI, and RSNI can help to improve stability. It should be noted that averaging must be done closely in time for high correlation.

**Channel Estimation** The preamble symbols used for channel estimation are L-LTF and VHT-LTF symbols. Two channel estimates are required in the receiver, one for the precoded and one for the non-precoded symbols. For this reason, VHT-LTF symbols are precoded as defined in [7], whereas L-LTF symbols are not.

Channel estimator for the legacy part Having transmitted the training symbols  $x_{L-LTF,k}$ , the received L-LTF symbols per symbol index t, t = [1,2], per subcarrier index  $k, k \in I_{active, non-pilot, L-LTF subcarriers}$ , can be written as:

$$\mathbf{y}_{k,t} = \mathbf{H}_{k} \mathbf{x}_{L-LTF,k} + \mathbf{n}_{k,t}$$

$$= x_{L-LTF,k} \begin{bmatrix} \frac{1}{N_{T_{x}}} \sum_{j=1}^{N_{T_{x}}} h_{1,j} \\ \vdots \\ \frac{1}{N_{T_{x}}} \sum_{j=1}^{N_{T_{x}}} h_{N_{R_{x}},j} \end{bmatrix} + \mathbf{n}_{k,t}$$

$$= x_{L-LTF,k} \mathbf{h}_{eff,k} + \mathbf{n}_{k,t},$$

(2.6)

where  $\mathbf{H}_k$  is a  $(N_{R_x} \times N_{T_x})$  complex channel matrix,  $\mathbf{x}_{L-LTF,k}$  is a  $(N_{T_x} \times 1)$  real vector containing  $x_{L-LTF,k}$  symbols,  $\mathbf{n}_{k,t}$  is a  $(N_{R_x} \times 1)$  complex Gaussian noise vector, and  $\mathbf{h}_{eff,k}$ , expanded in (2.6), is the legacy  $(N_{R_x} \times 1)$  effective channel vector.

Having transmitted only one and minus one symbols in the two L-LTF symbols t = [1, 2], the effective least square (LS) channel estimate per subcarrier k can be written as:

$$\hat{\mathbf{h}}_{LS,k} = \frac{x_{L-LTF,k}}{2} \sum_{t=1}^{2} \mathbf{y}_{k,t}.$$

(2.7)

The calculated LS channel estimate is used for linear minimum mean square error (LMMSE) channel estimation, FFT smoothing and wiener filtering.

Now, the LMMSE channel estimate per subcarrier k can be calculated using the LS channel estimate from (2.7) as:

$$\hat{\mathbf{h}}_{LMMSE,k} = \hat{\mathbf{h}}_{LS,k} \hat{\mathbf{h}}_{LS,k}^{H} \times (\hat{\mathbf{h}}_{LS,k} \hat{\mathbf{h}}_{LS,k}^{H} + \frac{\sigma_{n}^{2}}{2} I_{N_{R_{x}}})^{-1} \hat{\mathbf{h}}_{LS,k}.$$

(2.8)

Here  $\mathbf{h}^H$  is the Hermitian transpose of vector  $\mathbf{h}$ , and  $\sigma^2$  is the noise variance.

Channel estimator for the VHT part Using the above calculated legacy channel estimates, the L-SIG and VHT-SIG-A symbols can be detected. Thus, the number of transmitted VHT-LTF symbols  $(N_{VHT-LTF})$  will be known for the VHT channel estimation.

As defined by [7], these symbols are precoded with precoding matrix  $\mathbf{P}$ . Furthermore, precoder matrix  $\mathbf{Q}_j$   $j \in I_{active,\ VHT-LTF\ subcarriers}$  may also be applied to VHT-LTF symbols. Having transmitted the training symbols  $x_{VHT-LTF,k}$ , the received VHT-LTF symbols per symbol index  $t,\ t=[1,\ldots,N_{VHT-LTF}]$ , per subcarrier index  $k,\ k\in I_{active,\ non-pilot,\ VHT-LTF\ subcarriers}$ , can be written as:

$$\mathbf{y}_{k,t} = \mathbf{H}_k \mathbf{Q}_k \mathbf{P}(:,t) x_{VHT-LTF,k} + \mathbf{n}_{k,t}$$

=  $\mathbf{H}_{eff\,k} \mathbf{P}(:,t) x_{VHT-LTF\,k} + \mathbf{n}_{k\,t}.$  (2.9)

The VHT-LTF symbols are precoded by matrix  $\mathbf{P}$  and averaged over  $N_{VHT-LTF}$  symbols to achieve effective channel estimates per space time stream. For clearer presentation, received samples on subcarrier k from all  $R_x$  antennas, and VHT-LTF symbols are put into a column vector. Thus, the received VHT-LTF symbols can be shown as:

$$\mathbf{y}_{k} = \begin{bmatrix} \mathbf{y}_{k,1} \\ \vdots \\ \mathbf{y}_{k,N_{VHt-LTF}} \end{bmatrix}$$

$$= (\mathbf{P} \otimes \mathbf{I}_{N_{R_{x}}})^{T} \begin{bmatrix} \mathbf{h}_{eff,k,1} \\ \vdots \\ \mathbf{h}_{eff,k,N_{VHT-LTF}} \end{bmatrix}$$

$$\times x_{VHT-LTF,k} + \mathbf{n}_{k}.$$

(2.10)

Here  $P \otimes I_{N_{R_x}}$  represents Kronecker tensor product of Matrices P and  $I_{N_{R_x}}$ . Now the

received VHT-LTF training symbols after decoding diversity coding can be written as:

$$\tilde{\mathbf{y}}_{k} = \frac{1}{N_{VHT-LTF}} (\mathbf{P} \otimes \mathbf{I}_{N_{R_{x}}}) \begin{bmatrix} \mathbf{y}_{k,1} \\ \vdots \\ \mathbf{y}_{k,N_{VHT-LTF}} \end{bmatrix}$$

$$= x_{VHT-LTF,k} \begin{bmatrix} \mathbf{h}_{eff,k,1} \\ \vdots \\ \mathbf{h}_{eff,k,N_{VHT-LTF}} \end{bmatrix} + \mathbf{z}_{k},$$

$$\vdots$$

$$\vdots$$

$$\vdots$$

where  $\mathbf{z}_k \in \mathcal{CN}(0, \frac{\sigma_n^2}{N_{VHT-LTF}})$ . Thus, the effective LS channel estimate per subcarrier k can be given as:

$$\hat{\mathbf{H}}_{eff,LS,k} = x_{VHT-LTF,k} \hat{\tilde{\mathbf{Y}}}_k, \tag{2.12}$$

where  $\hat{\hat{\mathbf{Y}}}_k$  contains weighted received symbols  $\tilde{\mathbf{y}}_k$  from all  $N_{R_x}$  antennas.

Using the effective LS channel estimate from (2.12) and (2.8), the LMMSE channel estimate for the VHT part can be expressed as:

$$\hat{\mathbf{H}}_{eff,LMMSE,k} = \hat{\mathbf{H}}_{eff,LS,k} \hat{\mathbf{H}}_{eff,LS,k}^{H}

\times (\hat{\mathbf{H}}_{eff,LS,k} \hat{\mathbf{H}}_{eff,LS,k}^{H} + \sigma_n^2 I_{N_{R_x}})^{-1} \hat{\mathbf{H}}_{eff,LS,k}.$$

(2.13)

Equation (2.13) should be simplified to avoid the complicated computations involved in the matrix inversion required for LMMSE channel estimation. We stack the columns of the effective  $(N_{R_x} \times N_{T_x})$  LS channel estimate for  $N_{R_x} = N_{T_x} = 2$  on top of each other in a way that  $\hat{\mathbf{h}}_{LS} = [h_1, h_2, h_3, h_4]^T$ . Thus, LMMSE channel estimate can be re-written as:

$$\hat{\hat{\mathbf{h}}}_{LMMSE} = \begin{bmatrix} h_1 \\ h_2 \\ h_3 \\ h_4 \end{bmatrix} \begin{bmatrix} h_1^* h_2^* h_3^* h_4^* \end{bmatrix} \\

\times \begin{pmatrix} \begin{bmatrix} h_1 \\ h_2 \\ h_3 \\ h_4 \end{bmatrix} \begin{bmatrix} h_1^* & h_2^* & h_3^* & h_4^* \end{bmatrix} + \mathbf{N} \end{pmatrix}^{-1} \begin{bmatrix} h_1 \\ h_2 \\ h_3 \\ h_4 \end{bmatrix}, \tag{2.14}$$

where  $h^*$  is the complex conjugate of h, and  $\mathbf{N} = \sigma_n^2 \mathbf{I}_{N_{R_x}}$ . Using the Shannon-Morrison law [19], (2.14) can be simplified to:

$$\hat{\hat{\mathbf{h}}}_{LMMSE} = \frac{h_1 h_1^* + h_2 h_2^* + h_3 h_3^* + h_4 h_4^*}{\sigma_n^2 + h_1 h_1^* + h_2 h_2^* + h_3 h_3^* + h_4 h_4^*} \begin{bmatrix} h_1 \\ h_2 \\ h_3 \\ h_4 \end{bmatrix}

= \frac{\hat{\mathbf{h}}_{LS} \hat{\mathbf{h}}_{LS}^T \times conj(\hat{\mathbf{h}}_{LS})}{\sigma_n^2 + \hat{\mathbf{h}}_{LS}^T \times conj(\hat{\mathbf{h}}_{LS})}.$$

(2.15)

Same solution can be applied to reduce the computational complexity associated with matrix inversion of a  $N_{R_x} = N_{T_x} = 4$  MIMO antenna configuration.

**Frequency Domain Pilot Based Residual Frequency Error Tracking** This procedure is carried out to estimate and correct the frequency error of the received symbols. The frequency error on the received pilot subcarriers is estimated by calculating the mean of phase angle differences between the current pilots and the ones from the preceding symbol.

As the received pilots can have low power due to the frequency selective channel fading, we define a weighting vector for the pilots to reduce the degradation of phase rotation estimates. Denoting the power of each received subcarrier as  $\sigma_{I_P(N_p)}^2$ , the weighting vector w can be written as:

$$\mathbf{w} = \frac{1}{\sum_{i=1}^{N_p} \sigma_{I_P(i)}^2} \left[ \sigma_{I_P(1)}^2 \sigma_{I_P(2)}^2 \cdots \sigma_{I_P(N_p)}^2 \right]^T, \tag{2.16}$$

where  $N_p$  is the number of pilot subcarriers in  $I_P$  set (  $N_p = |I_P|$ ).

The phase rotation estimate between pilot subcarriers of two consecutive symbols at time instances t and t-1, produced as a result of frequency error  $\mathbf{F}_{error}$ , can be written as:

$$\hat{\Theta}_{t} = \mathbf{w}^{T} \left( arg \left( \mathbf{P}_{t-1} \right) - arg \left( \mathbf{P}_{t} \right) \right), \tag{2.17}$$

where arg(x) returns the argument of the complex number x, and t,  $t = [1, ... N_t]$  is the data symbol index. Here, data symbol zero (t = 0) is the VHT-SIG-B symbol.

Now frequency error at symbol index t can be written as:

$$\hat{\mathbf{F}}_{error,t} = \frac{1}{2\pi t (N_s + N_{GI})} \sum_{i=1}^{t} \hat{\Theta}_i,$$

(2.18)

where  $N_s$  denotes the number of subcarriers, and  $N_{GI}$  is the number of GI samples. The phase rotation estimates are averaged over the symbols, and the accuracy of the estimate is improved by the end of the DATA field.

Thus, the frequency error of received symbols per subcarrier k can be corrected by:

$$\hat{\mathbf{y}}_k = exp\left(j\sum_{i=1}^t \hat{\Theta}_i\right)\mathbf{y}_k. \tag{2.19}$$

**Symbol Detection** Symbol detection is carried out using the LMMSE channel estimates obtained by (2.13). First the symbol detection matrix per subcarrier k is calculated as:

$$\mathbf{D}_{coeff,k} = (\hat{\mathbf{H}}_k^H \hat{\mathbf{H}}_k + \sigma_n^2 \mathbf{I}_{N_{STS}})^{-1} \hat{\mathbf{H}}_k^H, \tag{2.20}$$

where  $\hat{\mathbf{H}}_k$  is the LMMSE channel estimate and  $N_{STS}$  is the number of space time streams.

Now the received symbols per subcarrier k can be detected as:

$$\hat{\mathbf{x}} = \mathbf{D}_{coeff} \, _k \mathbf{y}_k. \tag{2.21}$$

In case of STBC coding, channel estimates and received symbols should be defined accordingly. For instance, in case of  $N_{T_x} = N_{R_x} = 2$ , and STBC coding,  $\hat{\mathbf{H}}_k$  is written as:

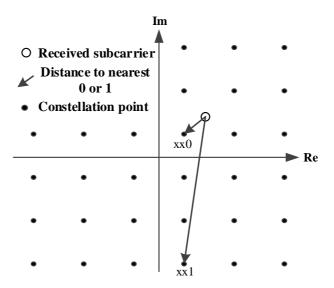

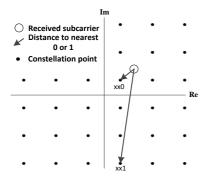

Figure 2.7: Soft bit detection

$$\hat{\mathbf{H}}_{k} = \begin{bmatrix} h_{11} & h_{12} \\ h_{21} & h_{22} \\ h_{12}^{*} & -h_{11}^{*} \\ h_{22}^{*} & -h_{21}^{*} \end{bmatrix}, \tag{2.22}$$

where matrix elements  $h_{ij}$  denote the channel from  $i_{th}$  receiver antenna to  $j_{th}$  transmitter antenna.

Furthermore, the received symbols vector  $\mathbf{y}_k$ , having  $N_{T_x} = N_{R_x} = 2$  antenna setting and STBC coding, is written as:

$$\mathbf{y}_{k} = \begin{bmatrix} y_{11} \\ y_{12} \\ y_{21}^{*} \\ y_{22}^{*} \end{bmatrix}, \tag{2.23}$$

where  $y_{ij}$  is the received symbol at time slot i on receiver antenna j.

Channel estimate matrix and received symbols vector from (2.22) and (2.23) can be similarly extended for a  $N_{T_x} = N_{R_x} = 4$  antenna configuration with STBC coding.

Similar to LMMSE channel estimation, calculation of  $D_{coeff,k}$  involves a matrix inversion, which cannot be simplified in a similar manner. More details on reducing the complexity of symbol detection can be found in Chapter 3.

**Soft Bit Detection** The detected symbols go through tone de-mapping and arrive at soft bit detection block. In this step demodulation is carried out, and symbols are converted to bits. First, the corresponding constellation point is found for each symbol. Then, for each bit position, the difference between the distances to the nearest zero and one bit for the constellation point is calculated. This process is illustrated in Fig. 2.7. This method helps to reduce the complexity of soft bit detection by only calculating the distance to the nearest one and zero bits.

**LDPC Decoding** Similar to LDPC coding in the transmitter side, LDPC decoding is assumed to be carried out in a coarse-grain accelerator in the design. This accelerator can function in

**Figure 2.8:** The overall receiver principle with digital channelization filtering yielding two 40 MHz subsignals.

parallel with the rest of the frequency domain processing. The existing literature provides many implementations of LDPC architecture [20–22].

#### 2.1.5 IEEE 802.11ac Digital Front-End Processing

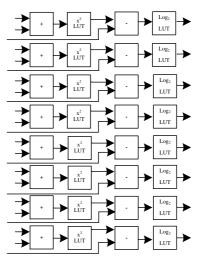

This section describes a digital front-end concept developed for the IEEE 802.11ac receiver. The IEEE 802.11ac allows usage of both 80 MHz or 160 MHz bandwidths. The 80 MHz waveform is primarily comprised of two 40 MHz sub-signals, with three null subcarriers in between. Thus, with precise time-domain filtering, the 80 MHz band can be divided into two 40 MHz signals.

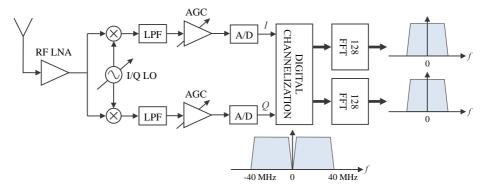

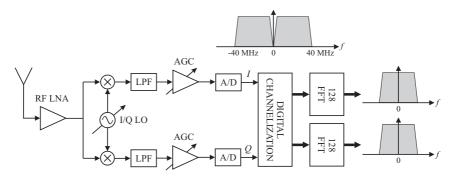

Then, having divided the waveform, the rest of the processing can be done with less complexity and in parallel for the two sub-bands. Furthermore, existing hardware for the IEEE 802.11n, which primarily used a 40 MHz band, can be employed. Including the chain from RF to baseband, the receiver principle incorporating this channelization concept is depicted in Fig 2.8. This concept can also be extended to the 160 MHz channel setup, introduced in the IEEE 802.11ac.

In this work, we focus on the 80 MHz bandwidth with 256 subcarriers, of which 234 are data and eight are pilot subcarriers. Thus, the positive and negative frequency components will each have 121 active subcarriers, resulting in  $k = \pm [2, 3, \dots, 122]$ , and the three subcarriers around DC, k = [-1, 0, 1] are zero.

The symbol duration in IEEE 802.11ac is defined as 4  $\mu$ s, from which 800 ns is reserved for the GI. Having FFT size of 256, this translates to a cyclic prefix (CP) of 64 samples. Linear filtering is used to divide the signal into two 40 MHz waveforms, so that they can be further processed in parallel using two 128 point FFTs.

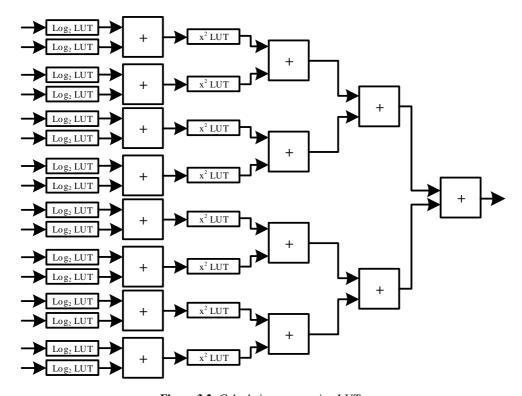

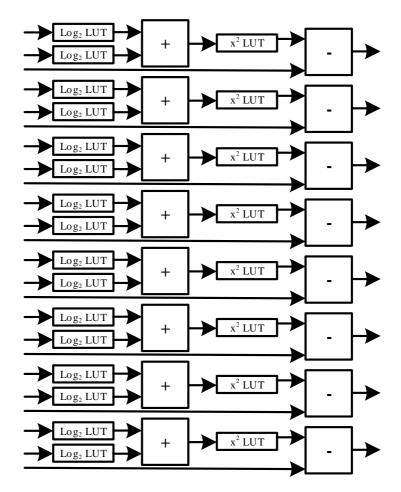

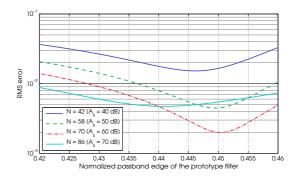

This channelization concept can be realized using a finite impulse response (FIR) filter. Furthermore, to reduce the computational complexity of the design, and minimize the required number of multiplications, halfband filters are selected.

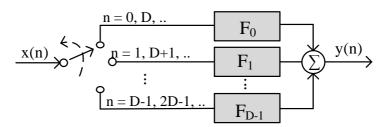

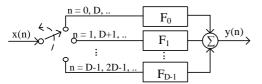

#### 2.1.5.1 Polyphase Halfband Filters

Halfband filters are commonly used in many digital communication systems, due to their efficiency in multi-rate applications. The transfer function for a halfband FIR filter is of the form [23]:

$$H(z) = \sum_{n=0}^{2M} h[n]z^{-n},$$

$$h[2M-n] = h[n].$$

(2.24)

In these filters,

$$h[M] = 1/2,$$

$h[M+2r] = 0, for \ r = \pm 1, \pm 2, \dots, \pm (M-1)/2,$  (2.25)

where M is an odd integer.

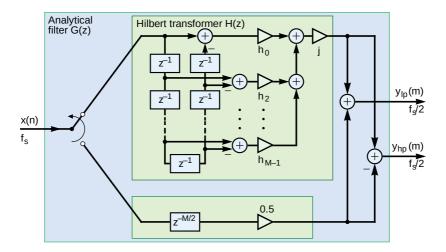

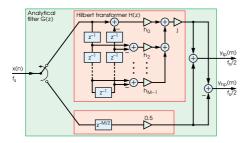

A highpass/lowpass filter pair satisfying these conditions can be realized using a type II (M is odd) FIR transfer function  $G(z^2)$  with a delay of M as [23]:

$$H(z) = G(z^2) \pm \frac{1}{2}z^{-M},$$

(2.26)

where the order of the overall transfer function is 2M and the lowpass/highpass filter is realized by the plus/minus sign.

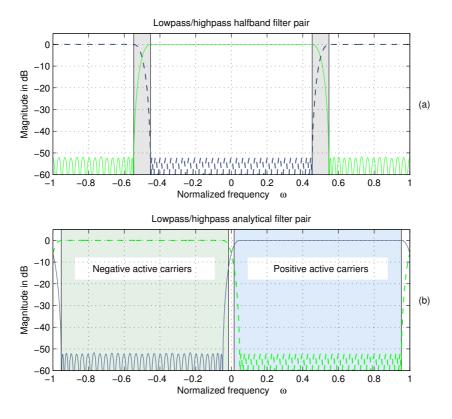

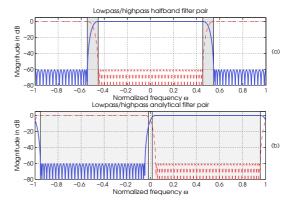

The magnitude response of the halfband and analytical filters are shown in Fig 2.9a and Fig 2.9b, respectively.

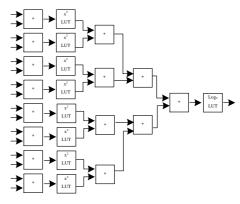

To decimate the signal by two, half of input samples go through G(z) and half through  $\frac{1}{2}z^{-M}$  filter. Thus, each filter branch works at the same rate as the output, which is half of the input sample rate. This structure is illustrated in Fig 2.10.

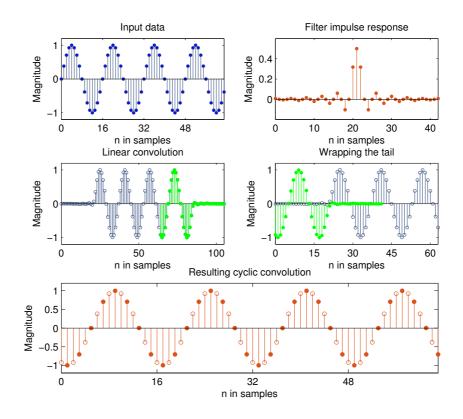

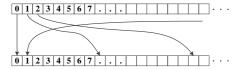

#### 2.1.5.2 Cyclic Polyphase Halfband Filters

The linear halfband filter designed for channelization, described in the previous section, increases the time dispersion of the received signal, which invades the CP. To avoid the increase in length of the impulse response, cyclic convolution can be adopted instead of linear convolution. This is an effective solution, since cyclic convolution is carried out after CP removal, and thus CP would not be compromised. Cyclic filtering is performed block-wise in a way that the last 2M produced samples are added to the beginning of the block. An illustration of cyclic convolution using linear halfband filtering can be found in Fig. 2.11 [24].

#### 2.2 Future Wireless Systems and Full-Duplex Communication

One common target being pursued in the new generations of wireless networks is providing very high capacity to meet the expected dramatic growth in mobile traffic. One example is the upcoming generation of the 3GPP cellular networks, i.e. fifth generation (5G), which is currently being standardized and developed, and aims for a 1000-fold increase in capacity compared to its preceding generations [25, 26].

Such big growth in capacity can be achieved by combining different mechanisms, namely increasing spectral efficiency, base-station densification, and using more spectrum (available in higher bands). In this section, IBFD communications is introduced, which enables more efficient use of the available spectrum. Full-duplex communications exploit the less efficient use of spectral and temporal resources in current available communication systems. For clarity, we state that 5G new radio (NR) still builds on FDD and TDD duplexing principles, while the IBFD technology may be adopted in future releases or in sixth generation (6G) era.

**Figure 2.9:** Magnitude response of (a) halfband and (b) analytical filters, grey areas in (a) indicate the transition bands, and in (b) the active subcarriers.

Figure 2.10: Structure of decimating analytical filter producing both the lowpass and highpass outputs  $y_{lp}(m)$  and  $y_{hp}(m)$ , respectively

Figure 2.11: Cyclic convolution using linear halfband filtering

In the existing wireless networks, including 5G NR Release 15, the spectral and temporal resources are typically divided between downlink and uplink in two ways: FDD, and TDD. In FDD, which is used in most commercial cellular systems, transmission and reception are separated in frequency. TDD, on the other hand, divides downlink and uplink transmission in time [27].

In this section, we briefly introduce full-duplex radios and the challenges affiliated with realizing such systems. Then, a solution is described which can help to combat these challenges.

#### 2.2.1 Full-Duplex Communication

All two-way wireless devices and systems existing today, such as global system for mobile communications (GSM), universal mobile telecommunications system (UMTS)/high speed packet access (HSPA), and WLAN/WiFi, are based on separating the transmission and reception either in time or frequency, i.e., systems operate in either TDD or FDD mode. This has the inevitable downside, however, that the spectral efficiency of using the radio frequencies is only half of its potential in theory. In contrast, full-duplex transmission is based on the challenging idea of simultaneously transmitting and receiving on a single frequency, and hence, in theory, doubling the efficiency of radio spectrum use compared to any existing system. However, as the strong transmit signal now directly couples to the sensitive receiver circuitry, substantial SI is generated, which needs to be tackled in the transceiver [28].

Figure 2.12: Principal illustration of full-duplex radio transceiver.

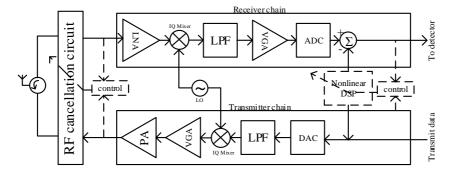

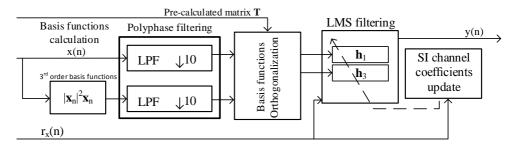

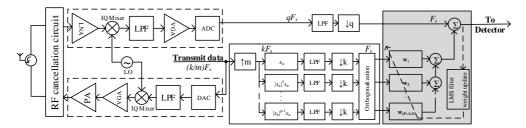

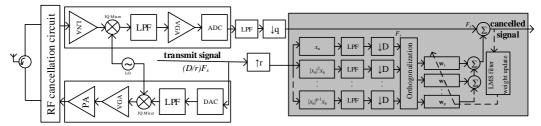

## 2.2.1.1 Digital Self-Interference Cancellation

Both RF and digital domain cancellations are required to reduce the SI signal to a level not interfering with the detection of the desired signal. SI cancellation in RF domain prevents the saturation of analogue-to-digital converter and receiver low-noise amplifier (LNA). However, the SI signal needs to be further suppressed in the digital domain to improve system performance.

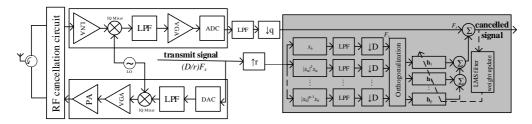

The overall structure of a full-duplex transceiver, illustrating both the RF and digital cancellers is shown in Fig. 2.12. In this section, we discuss digital SI cancellation by first introducing a model for the SI signal.

## 2.2.1.2 Self-Interference Modelling

Numerous non-ideal components exist in the transmitter and receiver paths which cause both linear and non-linear distortion in the transmitted signal coupling at the receiver. These distortions originate from different sources such as, power amplifier non-linearities, local oscillator phase noise, transmitter and receiver in-phase/quadrature (I/Q) imbalance, and analogue-to-digital converter quantization noise.

In this work, the parallel Hammerstein model, commonly used for highly nonlinear power amplifiers (PAs), is adopted for modelling the signal. This is due to the fact that the PA is known as the most significant contributor to the non-linear distortion of the signal.

Denoting the PA input by  $x_{PA,in}$ , and using the aforementioned parallel Hammerstein model, the signal at the PA output can be written as [29]:

$$x_{PA,out} = \sum_{\substack{p=1\\p \ odd}}^{P} \sum_{k=0}^{K-1} h_p^{PA}(k) u_p(x_{PA,in}(n-k)), \tag{2.27}$$

where P is the highest non-linearity order of the PA model, K is the memory length of the PA,  $h_p^{PA}$  represents the pth-order model for the PA memory, and  $u_p(x_{PA,in}(n))$  produces the pth-order basis function, and is computed using  $|x_{PA,in}(n)|^{p-1}x_{PA,in}(n)$ .

With the assumption of the PA as the most prominent source of non-linearity, the effective SI channel can be modelled using (2.27). Hence, denoting the original transmitted signal with x(n), the received signal at the digital canceller input can be expressed as:

$$r_x(n) = \sum_{\substack{p=1\\ p \text{ odd}}}^P \sum_{l=0}^{L-1} h_p(l) u_p(x(n-l)) + z(n), \tag{2.28}$$

where L denotes length of the modelled SI channel memory,  $h_p(l)$  contains the pth-order SI channel coefficients, and z(n) represents noise and potential modelling mismatch. Having an estimation of the unknown SI channel coefficients, the signal after the digital canceller can be written as:

$$e(n) = r_x(n) - \sum_{\substack{p=1\\p \ odd}}^{P} \sum_{l=0}^{L-1} \hat{h}_p(l) u_p(x(n-l)), \tag{2.29}$$

where the estimated SI channel coefficients are denoted by  $\hat{h}_p(l)$ . According to (2.28) and (2.29), a precise estimation of the SI channel coefficients will result in only noise remaining after cancellation, which consequently means that  $e(n) \approx z(n)$ .

It is important to update the SI channel estimates frequently, as the environment surrounding a moving device varies in time. However, the estimation method should be also of low computational complexity to be compatible with the limited processing power available in mobile devices. Thus, a least mean squares (LMS) based solution, proposed in [29], is selected to meet the aforementioned requirements.

Furthermore, a novel basis function orthogonalization method, also proposed in [29], is adopted to help further improve the SI suppression. The following sections describe the two methods in more details.

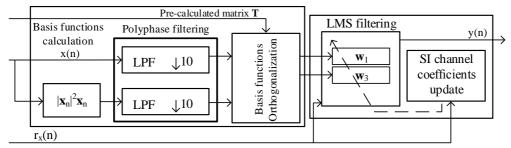

# 2.2.1.3 Orthogonalization

Being produced from the same transmitted signal, the generated basis functions are expected to be correlated. As a result, the SI channel coefficient estimation process, using the LMS algorithm, would suffer from slow convergence and excess mean squared error. Thus, it is beneficial to orthogonalize the basis functions for more efficient LMS parameter learning. This is carried out using a method proposed in [29], which will be described briefly in the following.

This method uses a whitening transformation matrix for basis functions orthogonalization. The transformation matrix can be obtained from the eigen-decomposition of covariance matrix  $\Sigma$ . Let us define the instantaneous basis function vector as:

$$\mathbf{u}(n) = \begin{bmatrix} u_1(x(n)) & u_3(x(n)) & \dots & u_p(x(n)) \end{bmatrix}^T, \tag{2.30}$$

where  $u_p(x(n)) = |x(n)|^{p-1}x(n)$  is the pth-order non-linear basis function.

Now, the covariance matrix of the basis functions across different non-linearity orders can be defined as:

$$\Sigma = \mathbb{E}[\mathbf{u}(n)\mathbf{u}(n)^H]. \tag{2.31}$$

The eigen-decomposition of covariance matrix  $\Sigma$  can be written as:

$$\Sigma = \mathbf{V}\mathbf{D}\mathbf{V}^H,\tag{2.32}$$

where eigenvalues of  $\Sigma$  comprise the diagonal matrix  $\mathbf{D}$ , and the corresponding eigenvectors build matrix  $\mathbf{V}$ . Having (2.32), the whitening transformation matrix  $\mathbf{T}$  is defined as:

$$\mathbf{T} = \mathbf{D}^{-\frac{1}{2}} \mathbf{V}^H. \tag{2.33}$$

Here,  $D^{-\frac{1}{2}}$  denotes element-wise square root and inversion of the diagonal elements of matrix **D**. Now, the basis functions can be orthogonalized using transformation matrix **T** by:

$$\tilde{\mathbf{u}}(n) = \mathbf{T}\mathbf{u}(n). \tag{2.34}$$

Having the orthogonalized basis functions from (2.34), (2.29) can be re-written as:

$$e(n) = r_x(n) - \sum_{\substack{p=1\\p \ odd}}^{P} \sum_{l=0}^{L-1} \hat{h}_{p,ort}(l) \tilde{u}_p(x(n-l)), \tag{2.35}$$

where the orthogonalized pth-order basis functions are represented by  $\tilde{u}_p(x(n))$ , and the SI channel estimates are denoted by  $\hat{h}_{p,ort}(l)$ . Now, (2.35) can be expressed using vector notations as:

$$e(n) = r_x(n) - \mathbf{h}^H \mathbf{u}_{ort}(n), \tag{2.36}$$

where

$$\mathbf{h} = \left[ \hat{h}_{1,ort}(0), \hat{h}_{3,ort}(0), \dots, \hat{h}_{P,ort}(0), \dots \right]^{T},$$

$$\hat{h}_{1,ort}(L-1), \hat{h}_{3,ort}(L-1), \dots, \hat{h}_{P,ort}(L-1) \right]^{T},$$

(2.37)

and

$$\mathbf{u}_{ort}(n) = \left[\tilde{\mathbf{u}}(n)^T, \tilde{\mathbf{u}}(n-1)^T, \dots, \tilde{\mathbf{u}}(n-L+1)^T\right]^T.$$

(2.38)

It should be noted that the covariance matrix  $\Sigma$  is only dependent on the statistical properties of the transmitted signal, and as a result, is time-invariant. Hence, we can assume that matrix T is pre-computed when used in the processing.

# 2.2.1.4 LMS Parameter Learning

This section describes the LMS-based method used to adaptively estimate the effective SI channel coefficients in a time-varying channel. The orthogonalized basis functions calculated in (2.34) are used to prevent high excess mean-squared error and slow convergence of the algorithm. Furthermore, different step sizes are used for different non-linear terms. The memory model of the channel includes both pre-cursor and post-cursor taps for more precision.

In this work, the proposed algorithm in [29] is adopted and modified to be more computationally friendly for our implementation purposes. Thus, as described in Algorithm 1, the SI channel estimates are not updated with every sample but only when a pre-defined number of samples are processed. The impact of this adjustment on the system performance is investigated and the results are presented in the following Chapters.

# Algorithm 1 LMS-based adaptive nonlinear digital cancellation.

```

1: Initialize:

2:

\mathbf{h} \leftarrow [0 \dots 0]

n \leftarrow L_{post}

4: while transmitting do

\mathbf{u_{ort}}(n) = \left[\tilde{\mathbf{u}}(n + L_{pre})^T \dots \tilde{\mathbf{u}}(n - L_{post})^T\right]^T

e(n) = r_x(n) - \mathbf{h}(n)^H \mathbf{u}_{ort}(n)

5:

6:

if (n \mod N == 0) then

7:

\mathbf{h}(n+1) \leftarrow \mathbf{h}(n) + \boldsymbol{\mu}e^*(n)\mathbf{u}_{ort}(n)

8:

9:

end if

n \leftarrow n + 1

10:

11: end while

```

Algorithm 1 presents the adopted LMS-based approach, where  $\tilde{\mathbf{u}}$  is a vector of the orthogonalized basis functions,  $\mathbf{h}$  contains the SI channel coefficient estimates,  $r_x(n)$  denotes the received signal, e(n) is the cancelled signal, and  $L_{pre}$  and  $L_{post}$  are the number of pre-cursor and post-cursor taps, respectively. Furthermore,  $\boldsymbol{\mu}$  contains the step sizes for different non-linearity orders, and N defines how often the estimated  $\mathbf{h}$  is updated.

# **CHAPTER 3**

# SDR SOLUTIONS FOR WIFI

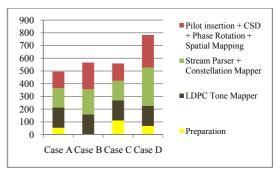

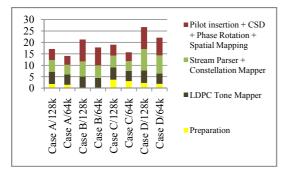

In this chapter, the proposed SDR solutions for both the baseband and DFE processing of the IEEE 802.11ac are described. For each solution, first the employed processing platform is introduced. Then, the implementation is presented and evaluated in terms of execution time, number of clock cycles, power, and energy consumption. The achieved results are then analyzed to investigate the feasibility of a real-time software-based solution for the processing. The contents of this chapter are based on publications [P1]–[P4].

## 3.1 Related Work

Many works related to the implementation of the WLAN standard family have been reported in the literature. However, only a limited number of implementations with a software-based approach exists, particularly when it comes to the physical layer. As an example, [30] reports an ASIC implementation of an IEEE 802.11a transceiver PHY, with OFDM and up to 64-QAM. Similarly, in [31], an ASIC implementation of the HT IEEE 802.11n transceiver using a 40 MHz bandwidth, with two transmit and three receive antennas is described. An IEEE 802.11ac implementation can be found in [32], where the transceiver is tailored to operate with 80 MHz bandwidth and  $4\times 4$  MIMO.

The above-mentioned studies target to a fixed scenario, and thus lack the flexibility to operate in different modes. However, programmable approaches are gaining more interest due to the advances in processor technologies. The work carried out in [33] only focuses on the FFT/IFFT processing for the VHT amendment, where larger FFT sizes are required due to the wider bandwidths supported. The authors of [33] propose a software defined FFT/IFFT architecture that meets the point size, throughput and multiple data streams requirements of the IEEE 802.11ac. The implementation uses a customized soft stream processor on FPGA, and is then compared to a dedicated Xilinx FFT core. The comparison shows better resource efficiency using the flexible software defined architecture. This work, however, does not provide a solution for the rest of the transceiver processing.

Some research works found in the literature use application specific instruction-set processors (ASIPs) as a solution for a flexible, yet high performance transceiver design. With an ASIP core, the instruction-set can be optimized for specific tasks, which results in better performance for some

applications, but less flexibility in other areas. As an example, [34] presents an 802.11ac/ax design using an ASIP processor. The design includes channel singular value decomposition (SVD), channel compression/decompression, and beamforming weight computations to support the MU-MIMO features of the IEEE 802.11ac. The article reports the synthesis results, which show that while the ASIP core requires less lookup tables (LUTs) and DSP resources, it uses more registers and memories compared to the implementation with a dual ARM processor system and programmable logic. Furthermore, the measured latency was shown to fit the timing requirements of the standard. Another baseband ASIP design for SDR is presented in [35], where algorithms from 3G, 4G, and WiFi are analyzed and selected for implementation. The article reports execution costs for different algorithms and introduces heterogeneous ASIPs for different processing tasks.

Both [36] and [37] address SDR based baseband processing of the IEEE 802.11ac. The work presented in [36] covers most of the baseband functionality assuming  $4 \times 4$  MIMO, 64-QAM, and 80MHz bandwidth. The radio processor used in this work, named RP-32 [38], has 256-bit data buses, 32-way single instruction multiple data (SIMD) operations, and 512-bit vector processing. The assumed clock frequency for this DSP core is 1 GHz. Similarly, [37] focuses on the inner part of the receiver (for synchronization and data detection) for IEEE 802.11ac with up to 80 MHz bandwidth,  $4 \times 4$  MIMO, and 64-QAM, as well as long-term evolution (LTE) Cat-4/5/7 user equipment (UE). This work is based on an instance of the custom baseband processor template ADRES [39]. This instance, called BOARDES, has four vector processing units supporting 256-bit SIMD. The assumed clock frequency for achieving real-time processing is 800 MHz in this work.

On the DFE processing side, [40] reports a FPGA implementation of a DFE block for multi-carrier multi-antenna systems. The design includes decimation/interpolation filters implemented as polyphase filters, as well as a frame synchronization block and an automatic gain controller. The article reports the area of the implemented design, but lacks information about the timing and power consumption.

Another FPGA-based implementation for polyphase FIR filters can be found in [41], where emphasis has been put on an efficient pipelined implementation in VHSIC hardware description language (VHDL). The results in terms of area on FPGA are reported, and the design is shown suitable for synthesis on low-cost SDR hardware.

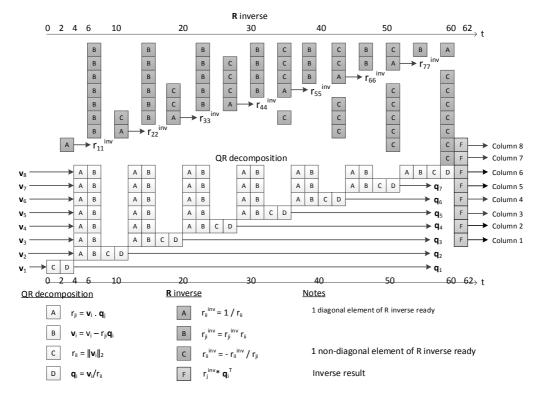

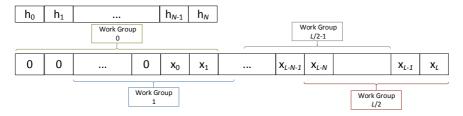

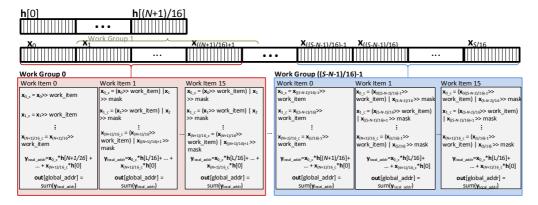

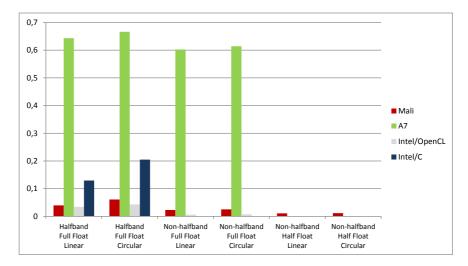

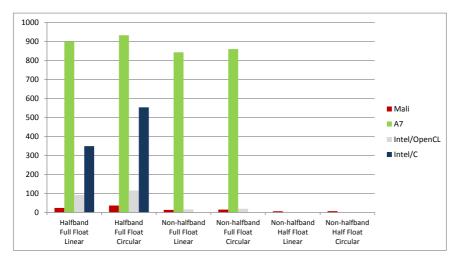

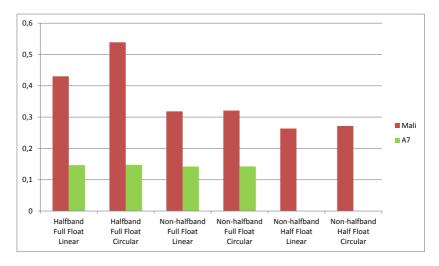

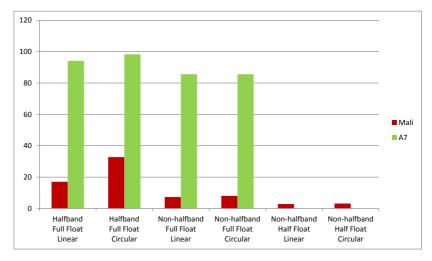

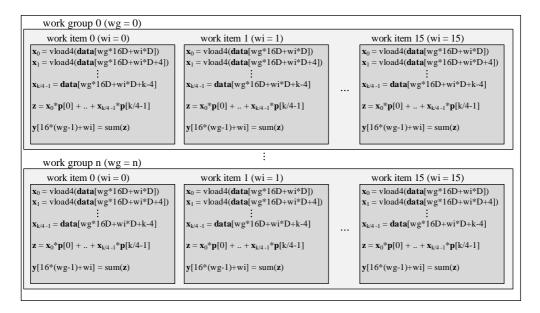

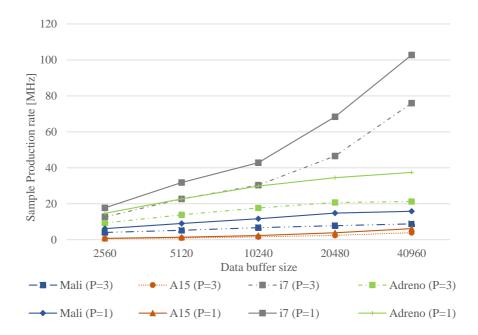

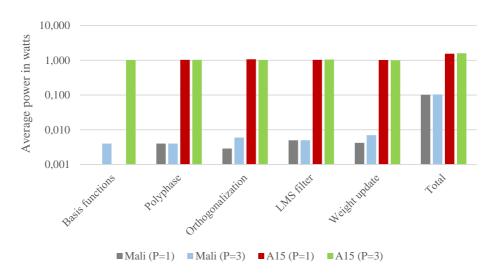

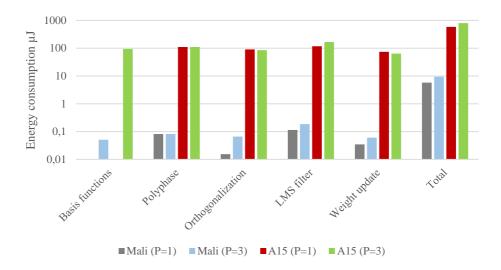

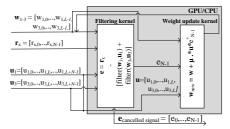

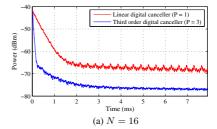

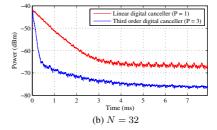

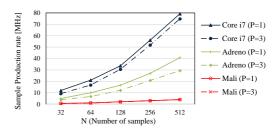

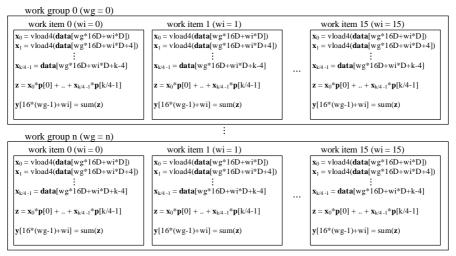

The work presented in [42] describes a similar concept to the one reported in this thesis, implementing polyphase filters using general-purpose GPUs. In this work, two GPU-based systems are employed, and CUDA is used as the software programming language [43]. The implemented polyphase filter bank channelizers on the two GPUs are compared to a CPU-based implementation, and results show that the parallelization on the GPUs can provide a speedup up to 9-16 times.