Xin Wang

# **Designing Globally-Asynchronous Locally-Synchronous On-Chip Communication Networks**

Tampereen teknillinen yliopisto. Julkaisu 742 Tampere University of Technology. Publication 742

# Xin Wang

# Designing Globally-Asynchronous Locally-Synchronous On-Chip Communication Networks

Thesis for the degree of Doctor of Technology to be presented with due permission for public examination and criticism in Tietotalo Building, Auditorium TB104 at Tampere University of Technology, on the 3rd of June 2008, at 12 noon.

Tampereen teknillinen yliopisto - Tampere University of Technology

Tampere 2008

## **ABSTRACT**

This thesis addresses two aspects of designing on-chip communication networks. One is about applying Globally-Asynchronous Locally-Synchronous (GALS) communication scheme into Network-on-Chip (NoC). Another is of designing and realizing different types of on-chip communication structures in the frame of GALS scheme.

The work of applying GALS scheme into on-chip networks presented in this thesis includes the strategy of realizing GALS scheme in a NoC, synchronization method in a GALS NoC, and asynchronous circuit design. GALS scheme is applied in the NoC designs presented in this thesis by applying synchronous style in the communications between network nodes and their attached function hosts while applying asynchronous style in the communications among network nodes. The asynchronous circuits developed for realizing the GALS on-chip networks include an asynchronous First-In First-Out (FIFO) design, control pipeline structures, C-element structure, and an arbiter design.

Three different types of on-chip networks are designed and presented in this thesis, which include a direct network, a Code-Division Multiple-Access (CDMA) network, and a crossbar network. The direct on-chip network presented in this thesis is a bidirectional ring network which gives an example of realizing GALS scheme in Proteo NoC architecture. The ring network realization consists of six nodes and requires an area of 177K equivalent gates when it is realized with a 0.18µm standard-cell library of Application Specific Integrated Circuits (ASIC). Although the ring network has a scalable network structure, its data transfer latency can vary largely depending on the data destination and routing process. This drawback increases the difficulty for the ring network to provide constant quality of communication service.

Therefore, a network structure which applies CDMA technique is developed and presented in this thesis in order to provide non-blocking data transfers among network nodes so that data transfer latencies have small variances. The CDMA NoC achieves this feature by applying orthogonal codes to build non-blocking data transfer channels among network nodes. The six-node realization of CDMA NoC presented in this thesis has an area of 272K equivalent gates when it is realized with a  $0.18\mu m$  standard-cell library and the data path width is 32 bits. The compensation of the larger area cost is that the asynchronous data transfer latency in the six-node CDMA NoC is equivalent to the best-case latency in the ring network. When the

ii Abstract

data path width is 32 bits, the realized CDMA network can transfer a 96-bit payload packet between network nodes within 49ns through a four-phase handshake protocol if there is no congestion of destination, which is equivalent to 11.76Gbits/s throughput of the network.

Crossbar is a well-known structure which can also supply the feature of non-blocking data transfers. Therefore, a six-node crossbar network is developed in this work as a reference to evaluate the CDMA network. In comparison with the six-node crossbar network, the CDMA network realization has 39.4% larger logic gate area cost when the data path width is 8 bits, whereas, the number of data wires in the CDMA network is 80.1% less than the number in the crossbar network if there are 31 network nodes.

Besides ASIC realizations, a four-node GALS bidirectional ring network is realized on an Field-Programmable Gate Array (FPGA) device as an example of prototyping a synchronous-asynchronous mixed NoC design on a Look-Up-Table (LUT) based FPGA device. The realization consumes 41.7K LUTs on an Altera StratixII FPGA device.

## **PREFACE**

The work presented in this thesis has been carried out in the Department of Computer Systems at Tampere University of Technology (TUT) during the years 2003-2007.

I would like to deeply thank my supervisor Professor Jari Nurmi for his kind encouragement, patient guidance, and financial support throughout this research work. I would also like to express my deep gratitude to Dr. Tapani Ahonen and Dr. David Sigüenza-Tortosa for their numerously inspiring suggestions and warmly help during the past four years. I also want to express many thanks to my other colleagues, Mikko Alho, Sanna Määttä, Bin Hong, Yang Qu, Claudio Brunelli, Fabio Garzia, Markus Moisio, Srinivasan Sudharsan, Pauli Perälä, Raimo Mäkelä, Ethiopia Nigussie, for their kindness, friendliness, encouragement, and help during these years. I would also like to thank Professor Hannu Heusala from University of Oulu in Finland and Professor Axel Jantsch from Royal Institute of Technology in Sweden for reviewing this thesis and giving valuable comments to improve it.

I would also like to thank Juha Pirttimäki, Ari Nuuttila, and Timo Rintakoski for their patient and warm help to handle all kinds of computer and software problems or requests from me during these years. My sincere gratitude is also expressed to the institute secretaries and coordinators, Irmeli Lehto, Johanna Reponen, Ulla Siltaloppi, and Elina Orava, for their warm help about many administrative and document affairs during my stay in TUT. Of course, there are many other friends whose names are not listed at here are also very important to make my living in Tampere smoothly and happily, I would also like to express my thankfulness to them.

This research work was financially supported by the Department of Computer Systems of Tampere University of Technology, which is gratefully acknowledged.

Finally, I would like to express my sincere love and deep thankfulness to my wife – Xi Guo, my parents – YanMing Zhang and FuLu Wang, my brother – Qun Wang, and other relatives who constantly supported and encouraged me during my living in Finland. Without their love and support, I can not imagine how I could carry out this research work.

Tampere, April 2008

iv Preface

# TABLE OF CONTENTS

| Ab  | stract            | f                                                       | i    |  |  |

|-----|-------------------|---------------------------------------------------------|------|--|--|

| Pre | Preface iii       |                                                         |      |  |  |

| Tai | Table of Contents |                                                         |      |  |  |

| Lis | st of P           | Publications                                            | ix   |  |  |

| Lis | List of Figures   |                                                         |      |  |  |

| Lis | st of T           | Tables                                                  | xiii |  |  |

| Lis | st of A           | Abbreviations                                           | xv   |  |  |

| Б   | . T. A            |                                                         |      |  |  |

| Pai | rt I: A           | argumentation                                           | 1    |  |  |

| 1.  | Intro             | oduction                                                | 3    |  |  |

|     | 1.1               | Research Background                                     | 3    |  |  |

|     | 1.2               | Objective and Scope of Research                         | 4    |  |  |

|     | 1.3               | Thesis Outline                                          | 5    |  |  |

| 2.  | Netv              | Network-on-Chip Overview                                |      |  |  |

|     | 2.1               | NoC Design Issues                                       | 8    |  |  |

|     | 2.2               | Examples of Existing NoC Designs                        | 13   |  |  |

| 3.  | App               | Applying GALS Scheme into On-Chip Networks              |      |  |  |

|     | 3.1               | Multi-Clock Challenge and GALS Scheme                   | 17   |  |  |

|     | 3.2               | The Synchronization in GALS NoC                         | 18   |  |  |

|     | 3.3               | The Asynchronous Design for GALS NoC                    | 20   |  |  |

|     |                   | 3.3.1 Introduction of Asynchronous Design               | 21   |  |  |

|     |                   | 3.3.2 The Asynchronous Designs Applied in the GALS NoCs | 22   |  |  |

| 4. | AD                         | irect On-Chip Network                         | 25 |  |  |

|----|----------------------------|-----------------------------------------------|----|--|--|

|    | 4.1                        | Network Topology                              | 25 |  |  |

|    | 4.2                        | Network Structure                             |    |  |  |

|    | 4.3                        | Network Node Design                           | 26 |  |  |

|    | 4.4                        | Front-End Synthesis and Simulation Results    | 28 |  |  |

| 5. | A CDMA On-Chip Network     |                                               |    |  |  |

|    | 5.1                        | Introduction of CDMA Technique                | 31 |  |  |

|    | 5.2                        | Motivation of Applying CDMA Technique in NoC  |    |  |  |

|    | 5.3                        | Applying CDMA Technique into On-Chip Networks | 34 |  |  |

|    | 5.4                        | CDMA NoC Structure                            | 36 |  |  |

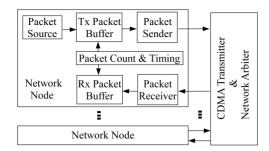

|    |                            | 5.4.1 Network Node                            | 37 |  |  |

|    |                            | 5.4.2 Network Arbiter                         | 38 |  |  |

|    |                            | 5.4.3 CDMA Transmitter                        | 39 |  |  |

|    | 5.5                        | Front-End Synthesis and Simulation Results    | 40 |  |  |

|    | 5.6                        | SystemC Modeling and Performance Estimation   | 42 |  |  |

|    |                            | 5.6.1 Modeling the CDMA NoC with SystemC      | 43 |  |  |

|    |                            | 5.6.2 Performance Estimations                 | 43 |  |  |

| 6. | A Crossbar On-Chip Network |                                               |    |  |  |

|    | 6.1                        | Introduction of Crossbar Structure            | 49 |  |  |

|    | 6.2                        | Network Structure and Network Node Design     | 50 |  |  |

|    | 6.3                        | Front-End Synthesis and Simulation Results    | 51 |  |  |

| 7. | Comparisons                |                                               |    |  |  |

|    | 7.1                        | Data Transfer Principles                      | 55 |  |  |

|    | 7.2                        | Network and Node Structures                   | 56 |  |  |

|    | 7.3                        | Performance                                   | 57 |  |  |

|    |                            | 7.3.1 Area Cost of Logic Gates                | 57 |  |  |

|    |                            | 7.3.2 Number of Data Connection Wires         | 58 |  |  |

|    |                            | 7.3.3 Area Cost of Interconnect Wires         | 60 |  |  |

|              |                          | 7.3.4 Data Transfer Latency                                             | 62 |  |  |  |

|--------------|--------------------------|-------------------------------------------------------------------------|----|--|--|--|

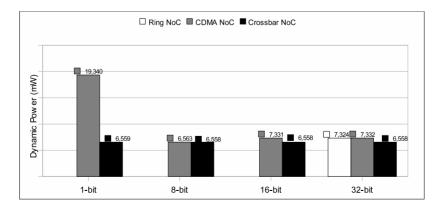

|              |                          | 7.3.5 Dynamic Power Consumption                                         | 64 |  |  |  |

|              | 7.4                      | Performance Comparisons with Other NoC Designs                          | 65 |  |  |  |

| 8.           | Real                     | Realizing a GALS NoC on an FPGA Device                                  |    |  |  |  |

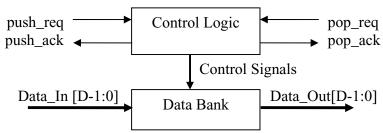

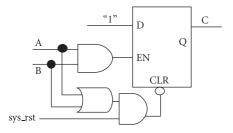

|              | 8.1                      | Two Key Components for Realizing Asynchronous Designs on an FPGA Device |    |  |  |  |

|              |                          | 8.1.1 C-element Structure                                               | 70 |  |  |  |

|              |                          | 8.1.2 Arbiter Structure                                                 | 70 |  |  |  |

|              | 8.2                      | Realizing a Four-Node GALS Ring NoC                                     | 72 |  |  |  |

| 9.           | Cond                     | usions                                                                  | 75 |  |  |  |

|              | 9.1                      | Summary of Publications                                                 | 75 |  |  |  |

|              | 9.2                      | The Main Results                                                        | 77 |  |  |  |

|              | 9.3                      | Future Research Directions                                              | 80 |  |  |  |

| Bibliography |                          |                                                                         |    |  |  |  |

|              |                          |                                                                         |    |  |  |  |

| Pa           | Part II: Publications 9: |                                                                         |    |  |  |  |

### LIST OF PUBLICATIONS

This is a compilation style thesis which bases on the following nine publications. The publications are enclosed in Part II of this thesis and are referred as [P1], [P2] ..., [P9].

- [P1] X. Wang, T.Ahonen, and J. Nurmi, "A Synthesizable RTL Design of Asynchronous FIFO", in *Proceedings of the 2004 International Symposium on System-on-Chip*, (SOC 2004), pages 123-128, Tampere, Finland, November 2004.

- [P2] X. Wang, D. Sigüenza-Tortosa, T. Ahonen, and J. Nurmi, "Asynchronous Network Node Design for Network-on-Chip", in *Proceedings of the 2005 International Sym*posium on Signal, Circuits, and System, (ISSCS 2005), Volume 1, pages 55-58, Iasi, Romania, July 2005.

- [P3] X. Wang, and J. Nurmi, "An On-Chip CDMA Communication Network", in *Proceedings of the 2005 International Symposium on System-on-Chip*, (SOC 2005), pages 155-160, Tampere, Finland, November 2005.

- [P4] X. Wang, T. Ahonen, and J. Nurmi, "Prototyping A Globally Asynchronous Locally Synchronous Network-on-Chip On A Conventional FPGA Device Using Synchronous Design Tools", in *Proceedings of the 2006 International Conference on Field Programmable Logic and Applications*, (FPL 2006), pages 657-662, Madrid, Spain, August 2006.

- [P5] X. Wang, and J. Nurmi, "A RTL Asynchronous FIFO Design Using Modified Micropipeline", in *Proceedings of the 10<sup>th</sup> Biennial Baltic Electronics Conference*, (BEC 2006), pages 95-98, Tallinn, Estonia, October 2006.

- [P6] X. Wang, and J. Nurmi, "Comparison of a Ring On-Chip Network and a Code-Division Multiple-Access On-Chip Network", in VLSI Design, Special Issue on Networks-on-Chip, Volume 2007, Article ID 18372, 14 pages, Hindawi Publishing Corporation, April 2007.

- [P7] X. Wang, and J. Nurmi, "Comparing Two Non-Blocking Concurrent Data Switching Schemes for Network-on-Chip", in *Proceedings of the 2007 International Conference on Computer as a tool*, (EUROCON 2007), pages 2587-2592, Warsaw, Poland, September 2007.

- [P8] X. Wang, T. Ahonen, and J. Nurmi, "Applying CDMA Technique to Network-on-Chip", in *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, Volume 15, Number 10, pages 1091-1100, October 2007.

- [P9] X. Wang, and J. Nurmi, "Modeling A Code-Division Multiple-Access Network-on-Chip Using SystemC", in *Proceedings of the 25<sup>th</sup> Norchip Conference*, (NORCHIP 2007), Aalborg, Denmark, November 2007.

# LIST OF FIGURES

| 1  | ISO Open Systems Interconnection Reference Model         | 8  |

|----|----------------------------------------------------------|----|

| 2  | Network Topology Examples.                               | 10 |

| 3  | Packet-Buffer Flow Control Methods.                      | 11 |

| 4  | Flit-Buffer Flow Control Methods                         | 13 |

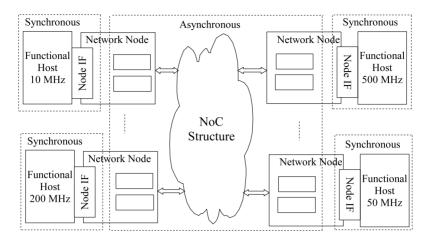

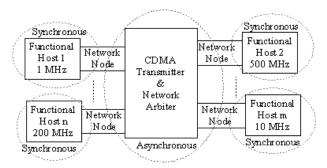

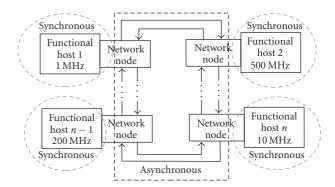

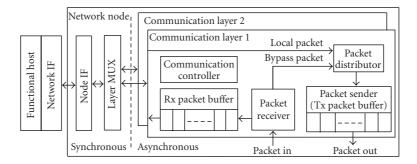

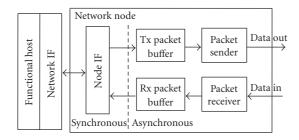

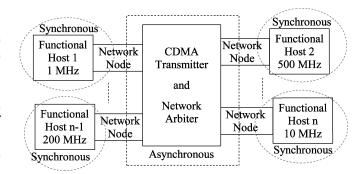

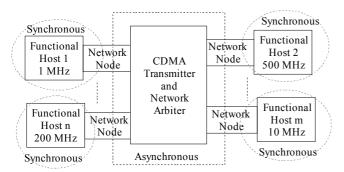

| 5  | A Method of Applying GALS Scheme in a NoC Design         | 18 |

| 6  | Double-Latching Synchronization Scheme.                  | 19 |

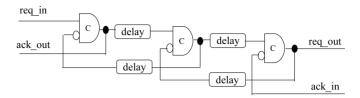

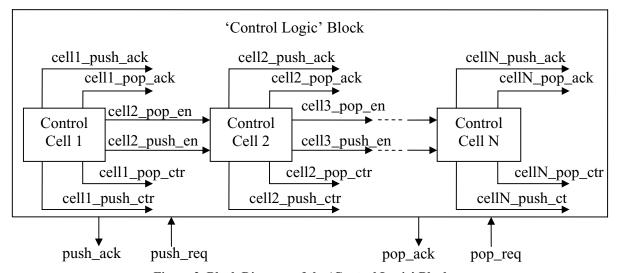

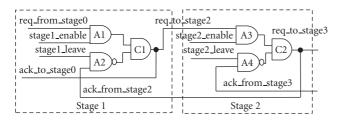

| 7  | The Control Logic of Micropipeline                       | 22 |

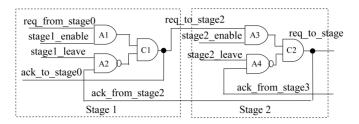

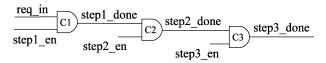

| 8  | Control Pipeline of Control-Centric Blocks               | 24 |

| 9  | Block Control Pipeline                                   | 24 |

| 10 | Ringlet Topology Example                                 | 25 |

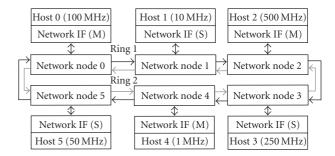

| 11 | Six-Node Bidirectional Ring Network                      | 26 |

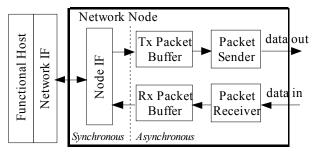

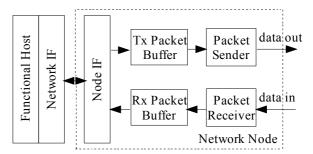

| 12 | Network Node Structure of the Bidirectional Ring Network | 27 |

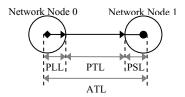

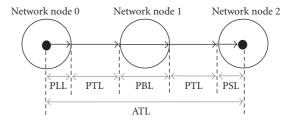

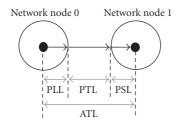

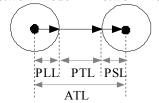

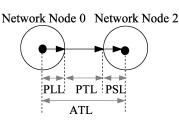

| 13 | ATL Portions of the Bidirectional Ring Network           | 30 |

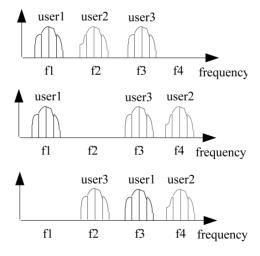

| 14 | The Principle of FHSS Technique                          | 32 |

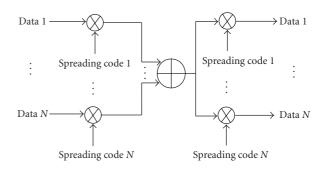

| 15 | The Principle of DSSS Technique                          | 33 |

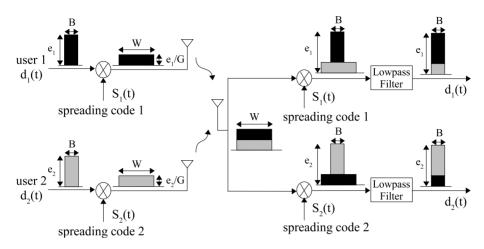

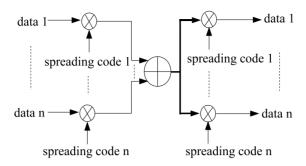

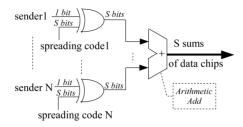

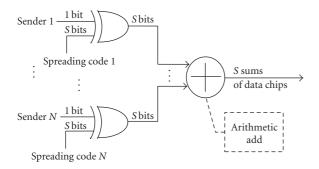

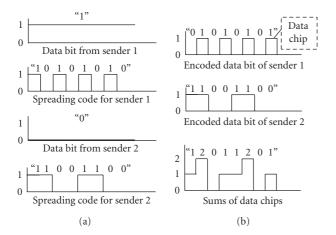

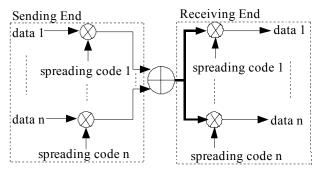

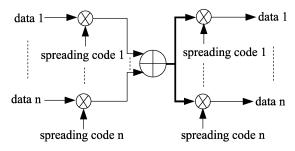

| 16 | The Principle of Digital CDMA NoC.                       | 34 |

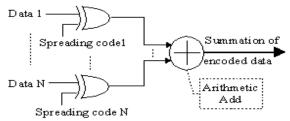

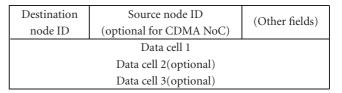

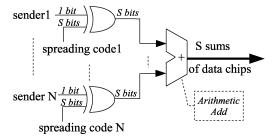

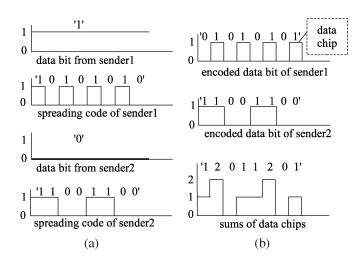

| 17 | Digital CDMA Data Encoding Scheme.                       | 35 |

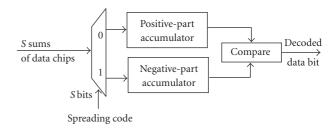

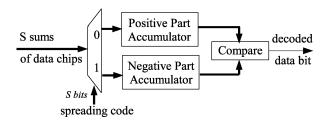

| 18 | Digital CDMA Data Decoding Scheme.                       | 35 |

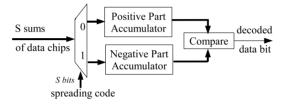

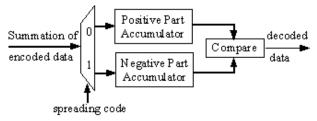

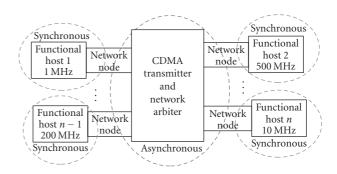

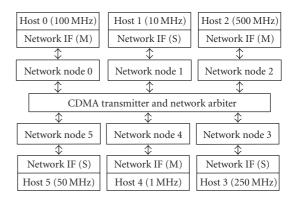

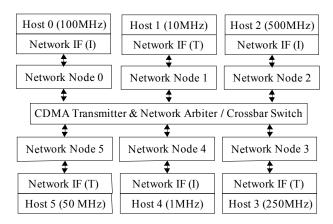

| 19 | Six-Node CDMA On-Chip Network Structure.                 | 37 |

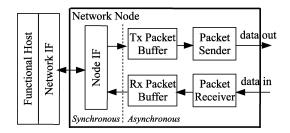

| 20 | The Block Diagram of the Network Node for CDMA NoC       | 37 |

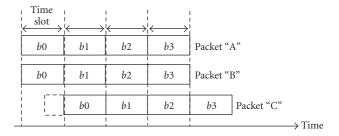

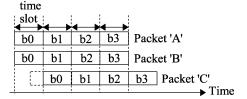

| 21 | Bit-Synchronous Transfer Scheme                          | 39 |

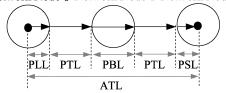

| 22 | ATL Portions of the CDMA NoC                             | 42 |

| 23 | Channels and Interfaces in the CDMA Network Node        | 44 |

|----|---------------------------------------------------------|----|

| 24 | Channels and Interfaces in the CDMA NoC                 | 44 |

| 25 | Open-Loop Simulation Environment                        | 45 |

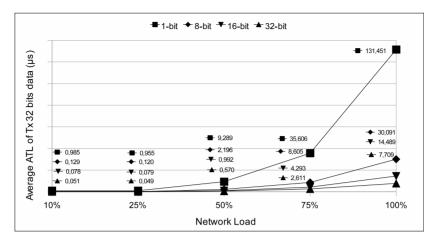

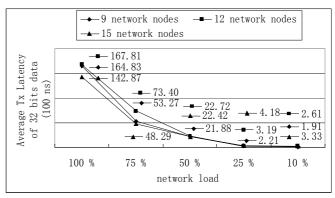

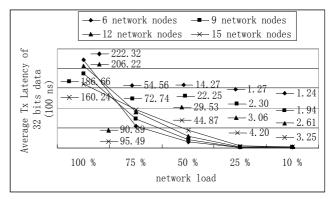

| 26 | ATL Estimations with Different Channel Widths.          | 46 |

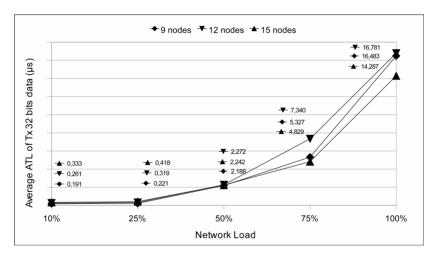

| 27 | ATL Estimations with Different Number of Network Nodes. | 46 |

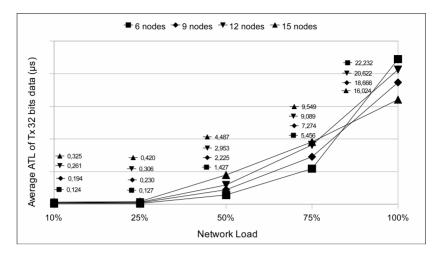

| 28 | ATL Estimations with Hot-Spot Traffic Pattern.          | 47 |

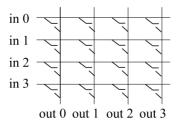

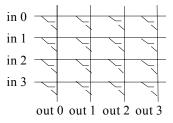

| 29 | An Example of Crossbar Structure                        | 49 |

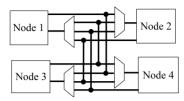

| 30 | A Four-Node Crossbar Switch Structure                   | 50 |

| 31 | Crossbar Network Structure                              | 51 |

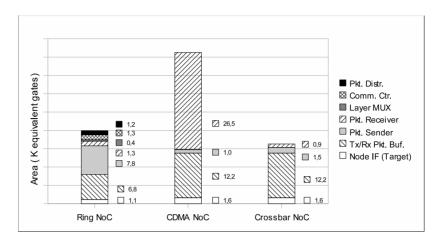

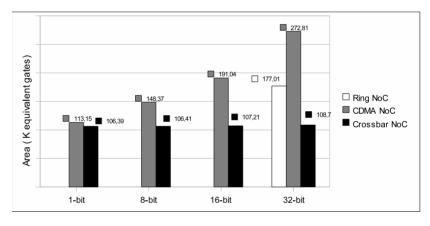

| 32 | Logic Gate Area Costs of Network Nodes                  | 58 |

| 33 | Total Logic Gate Area Costs of the Three Networks       | 58 |

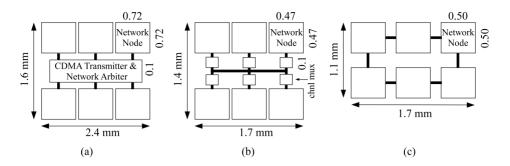

| 34 | Placement of the NoC Designs                            | 61 |

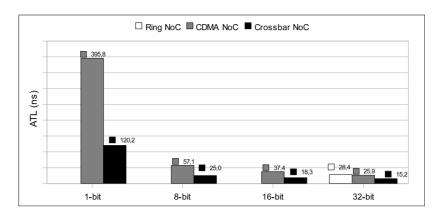

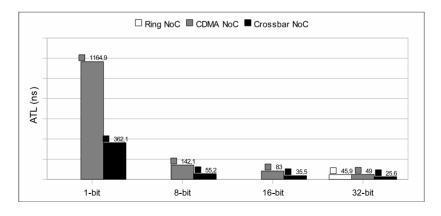

| 35 | ATL Values of Tx 1-data-cell Packet                     | 63 |

| 36 | ATL Values of Tx 2-data-cell Packet                     | 63 |

| 37 | ATL Values of Tx 3-data-cell Packet                     | 63 |

| 38 | Dynamic Power Consumption Comparison                    | 64 |

| 39 | C-element Structures                                    | 70 |

| 40 | The Arbiter Structure for EPGA Realization              | 71 |

# LIST OF TABLES

| 1  | Truth Table of C-Element.                               | 23 |

|----|---------------------------------------------------------|----|

| 2  | Area Cost of the Bidirectional Ring Network             | 28 |

| 3  | STL Values of the Bidirectional Ring Network.           | 29 |

| 4  | ATL Values of the Bidirectional Ring Network            | 29 |

| 5  | Area Cost of the Six-Node CDMA Network                  | 41 |

| 6  | ATL Values of the CDMA NoC                              | 42 |

| 7  | Area Cost of the Six-Node Crossbar Network              | 52 |

| 8  | ATL Values of the Crossbar Network.                     | 52 |

| 9  | Number of Data Connection Wires.                        | 60 |

| 10 | Equivalent Number of Intermediate Nodes in the Ring NoC | 64 |

| 11 | Theoretical Throughput of the Six-Node CDMA Network     | 65 |

| 12 | ALUTs Utilization of 'Network Node' Blocks.             | 73 |

## LIST OF ABBREVIATIONS

2-D 2-Dimensional

AHB Advanced High-performance Bus

ALUT Adaptive LUT

AMBA Advanced Microcontroller Bus Architecture

APB Advanced Peripheral Bus

ASB Advanced System Bus

ASIC Application Specific Integrated Circuits

ATL Asynchronous Transfer Latency

A-T Protocol Arbiter-based T Protocol

BE Best-Effort

BVCI Basic VCI

CDMA Code-Division Multiple-Access

CRC Cyclic Redundant Code

DCR Device Control Register

D-FF D-Flip-Flop

DI Delay-Insensitive

DS-CDMA Direct-Sequence CDMA

DSM Deep Sub-Micron

DSSS Direct-Sequence Spread-Spectrum

EMI Electromagnetic Interference

FF Flip-Flop

FHSS Frequency-Hopping Spread-Spectrum

FIFO First-In First-Out

FPGA Field-Programmable Gate Array

GALS Globally-Asynchronous Locally-Synchronous

GS Guaranteed Services

HDL Hardware Description Language

IC Integrated Circuit

ITRS International Technology Roadmap for Semiconductors

LAB Logic Array Block

LUT Look-Up-Table

MTBF Mean Time Between Failure

NoC Network-on-Chip

NRE Non-Recurring Engineering

OCP Open Core Protocol

OPB On-chip Peripheral Bus

OSI Open Systems Interconnection

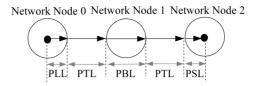

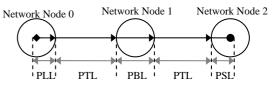

PBL Packet Bypass Latency

PCB Printed Circuit Board

PCC Packet Connected Circuit

PCI Peripheral Component Interconnect

PLB Processor Local Bus

PLL Packet Loading Latency

PSL Packet Storing Latency

PTL Packet Transfer Latency

QDI Quasi-Delay-Independent

QoS Quality of Service

RTL Register-Transfer Level

SI Speed-Independent

SoC System-on-Chip

SS Spread Spectrum

STL Synchronous Transfer Latency

TLM Transaction-Level Modeling

T Protocol Transmitter-based Protocol

T-R Protocol Transmitter-Receiver-based Protocol

TUT Tampere University of Technology

VCI Virtual Component Interface

VHDL VHSIC Hardware Description Language

VHSIC Very High Speed Integrated Circuit

VME VersaModule Eurocard

XOR eXclusive-OR

#### 1. INTRODUCTION

Communications play a fundamental and crucial role for the development of human society in every aspect because better communications facilitate better understanding and cooperation between individuals, which in turn facilitate the achievements and development in society. As the society is continuously growing and developing, the need for cooperation and development expands to global level. Therefore, communication plays more and more important role of this globalization process, and the need for effective communications in all kinds of ways becomes higher and higher.

As a researcher in electronics field, the author believes that the same truth also applies to onchip systems, which means that the quality of communication in an on-chip system prominently affects system performance. As the complexity of an on-chip system keeps growing, the communication among functional hosts in the system becomes a non-trivial issue to deal with. Therefore, with the interest in on-chip communication, the author started his research work on this topic in Tampere University of Technology (TUT) in October of 2003.

## 1.1 Research Background

Currently, silicon chips which contain thousands of million of transistors with 45nm feature size are already available on market, e.g. Intel Penryn processor. According to the report [42] from International Technology Roadmap for Semiconductors (ITRS) in 2007, a single semiconductor chip will contain multi-billion transistors with feature sizes around 22nm and clock frequencies around 35GHz by the year of 2016. This growing manufacture capacity and the highly demanding applications continuously drive the complexity of a System-on-Chip (SoC) to a higher degree in terms of number of system components and functionalities. For example, Cell Broadband Engine Architecture (CBEA) [33] jointly developed by IBM, Sony, and Toshiba, also referred as Cell processor, contains altogether 9 processing units in one chip. Furthermore, Tilera, a MIT spin-off company, released a 64-core processor called TILE64 [89] in 2007. As the number of system components becomes larger, current widely applied bus structures for data transfers in an on-chip system, e.g. CoreConnect [39], expose several disadvantages as addressed in [34]. Two main disadvantages are bus arbitration bottleneck and bandwidth limitation. The arbitration bottleneck means that the arbitration delay

will grow if the number of bus hosts increases. The bandwidth limitation refers to the fact that the data transfer bandwidth of a bus structure is shared by all hosts attached to it in a time division manner. Hence, more hosts incur a lower share of bandwidth for each one.

Another challenge that an on-chip system faces is the heterogeneous characteristics of system components. The components in a SoC may include processors for computation tasks, functional blocks for accelerating certain tasks, and the modules for communicating with the peripherals of system. The different functions among different system components naturally cause them to work in different clock rates for optimal performance. Hence, coordination and communications among those components become challenging tasks. At the same time, the issues of wire delay, on-chip noise, process variance, and power consumption in the realm of Deep Sub-Micron (DSM) technologies also become challenging for chip design. Altogether, these challenges have brought more and more concerns on the on-chip communication issue of a SoC design.

In order to overcome the disadvantages of bus structures, the concept of Network-on-Chip (NoC) has been proposed as a solution at the beginning of 2000s, e.g. [6, 19, 34]. The idea of NoC is to separate the concerns of communication from computation by building on-chip communication structure with concepts adopted from computer networks. Each component of a SoC is viewed as a node of the on-chip communication network. System components communicate with each other through the on-chip network. For the challenges of multiple clock domains and DSM technology effect, Globally-Asynchronous Locally-Synchronous (GALS) scheme has been proposed as a solution. In 1984, the concept of GALS scheme was firstly introduced in [15] to handle metastability problem. In 1999, several chip designs [62,69] which apply GALS scheme were published. The idea of a GALS system is to partition a system into separate clock domains which run at different clock rates, and the separated domains communicate with each other in an asynchronous manner.

When the author joined the research group at TUT in 2003, a NoC architecture named Proteo [85] was under development in the group. At that time, a few NoC designs have been published, including Æthereal NoC [23], NOSTRUM NoC [54], and SPIN NoC [34]. There was no published paper dedicated to GALS NoC. Therefore, the author started this research work with realizing GALS scheme in a Proteo NoC instance.

# 1.2 Objective and Scope of Research

The goal of this work is to design a GALS on-chip network in the frame of Proteo NoC architecture while experimenting with different NoC structures. The work focuses on the following topics.

(1) Developing a network node structure and building a bidirectional-ring network to find a

way of realizing GALS scheme in Proteo NoC.

- (2) Designing asynchronous circuits which include asynchronous FIFO design and asynchronous control logic for realizing the GALS NoC designs.

- (3) Developing a GALS on-chip network which applies CDMA technique.

- (4) Developing a modeling and performance estimation method for a GALS NoC design using SystemC.

- (5) Developing a crossbar on-chip data switch structure for comparison purpose.

- (6) Examining the characteristics of the developed CDMA NoC by comparing it with other NoC structures.

- (7) Realizing a synchronous-asynchronous mixed GALS NoC design on a LUT-based FPGA device.

#### 1.3 Thesis Outline

This thesis consists of two parts: Argumentation (Part I) and Publications (Part II). Part II includes reprints of nine international conference and journal publications on which this thesis bases. Part I starts with this chapter, Chapter 1, to introduce background and objective of this work. Chapter 2 gives an overview of on-chip networks including the background of NoC, the related design issues, and some examples of existing NoC designs. The topics addressed in Chapter 3 include the method of applying GALS scheme in on-chip networks and the related issues including synchronization and asynchronous designs for realizing a GALS NoC. Chapter 4 presents the work of designing and realizing a GALS ring NoC as a direct network instance of Proteo NoC architecture. Chapter 5 presents the work of designing and realizing an on-chip network which applies CDMA technique. Chapter 6 presents a crossbar network developed for comparison purpose. The comparisons between the CDMA network and other types of NoC designs including the ring and crossbar networks developed in this work are presented in Chapter 7. Chapter 8 presents the work of realizing a GALS NoC design on an FPGA device. Finally, the conclusions of this thesis including summary of the publications in Part II and the main results of the research work are presented in Chapter 9.

## 2. NETWORK-ON-CHIP OVERVIEW

The appearance of Integrated Circuit (IC) in 1959 was a milestone of the development of electronics industry. It created a productive way to manufacture large scale electronic circuits on a semiconductor device. As stated by Gordon Moore in 1965, "the complexity for minimum component costs has increased at a rate of roughly a factor of two per year" [64]. This statement is known as the original formulation of Moore's law and often quoted as "the number of transistors that can be placed on an IC is increasing exponentially, doubling approximately every two years." The Moore's Law is still valid nowadays and believed to be valid until reaching the size of atoms.

Therefore, driven by the growing manufacture capacity and the growing requirement of applications, the complexity of an on-chip system is continuously growing in terms of number of transistors and functionalities. For example, Intel's 'Core 2 Duo' processor fabricated with 65nm technology process contains 291 million transistors [40]. When the on-chip system becomes complicated, the system design methodology called orthogonalization of concerns [49] can be applied to deal with the complexity. As addressed in Chapter 1, the communication issue is very crucial for an on-chip system to perform its tasks efficiently. Therefore, in the context of SoC design, one way of applying the methodology of concerns orthogonalization is to separate the concerns of communication from computation to enable more efficient exploration of optimal solutions on each subject.

On-chip bus structure was firstly applied to handle on-chip communications for a SoC design in 1990s. The idea of on-chip bus is derived from the bus schemes, such as VersaModule Eurocard (VME) bus [78] and Peripheral Component Interconnect (PCI) bus [77], which are designed for connecting discrete devices on a Printed Circuit Board (PCB). The examples of on-chip bus structures include CoreConnect [39] and Advanced Microcontroller Bus Architecture (AMBA) [3]. CoreConnect is a complete and versatile bus specification which defines three types of buses: Processor Local Bus (PLB), On-chip Peripheral Bus (OPB) and Device Control Register Bus (DCR). AMBA, which is similar to CoreConnect, also specifies three kinds of buses: Advanced High-performance Bus (AHB), Advanced System Bus (ASB) and Advanced Peripheral Bus (APB). These bus structures supply many advanced features, such as split transactions and line transfers, for on-chip systems which contain a few processors.

However, as addressed in [34], bus structures have several disadvantages by the compari-

son of on-chip networks. The main disadvantages, bus arbitration bottleneck and bandwidth limitation as mentioned in section 1.1 of Chapter 1, are caused by the centralized and time-division manner of sharing a communication channel among all the hosts of a bus. The trend of future on-chip systems is that a large number of processing units will be integrated into one system, as the example shown by TILE64 [89]. Therefore, if a bus structure is applied in the future on-chip systems which contain a large number of components, it will suffer from the problems of arbitration delay, bandwidth limitation, and poor scalability. Hence, developing a dedicated on-chip network is the most promising solution for future on-chip communication. The issues of designing an on-chip network and the existing NoC designs will be introduced in the following two sections of this chapter.

## 2.1 NoC Design Issues

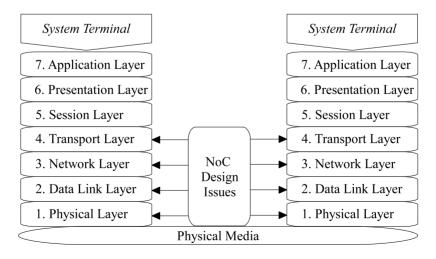

The concept of on-chip networks is derived from the well-established inter-computer networks. Therefore, taking a look at the design issues of designing computer networks is helpful for tackling design problems of NoC because they have a lot of similarities despite of different characteristics and application environments. The Open Systems Interconnection (OSI) reference model [41] is a layered description which has been used for building computer networks. Thus, the NoC design issues can be addressed according to the OSI reference model illustrated in Fig.1.

Seven layers are defined in the OSI model and illustrated in Fig.1. The seven layers include application layer, presentation layer, session layer, transport layer, network layer, data link layer, and physical layer. Each layer provides certain services to facilitate the communication

Fig. 1. ISO Open Systems Interconnection Reference Model.

processes in the network. The issues and challenges of designing on-chip networks will be addressed together with describing the functions of each layer in the following paragraphs of this section.

- (1) Physical Layer. This layer defines all the electrical and physical specifications to activate, maintain, and de-activate physical connections for data transfers. Normally, a NoC design is implemented on a silicon chip in which the characteristics of the physical connection medium are determined by the manufacturing technology. As the manufacture technology scales down to DSM domain, the on-chip physical links face the challenges of large wire delay, large power consumption, crosstalk noise, etc. Therefore, the NoC design efforts in this layer mainly concentrate on conquering the above mentioned challenges in physical level. For example, the work presented in [27] gives a wire segmentation repeater structure to reduce wire delays. The work in [71] presents a booster structure to drive long wires instead of repeaters to achieve better performance in terms of area, power, and placement sensitivity. The work presented in [98] applies low-swing signaling techniques to reduce the power consumption of link wires. A physical link design for a NoC application is presented in [59]. The design applies mesochronous approach to realize a clock skew insensitive physical link.

- (2) Data Link Layer. This layer is responsible for setting up reliable data transfers over physical links. The NoC design issues in this layer can include error detection and correction, access arbitration of physical media, and the methods of utilizing physical links. For instance, the Cyclic Redundant Code (CRC) scheme is applied in Xpipe NoC [7] to detect the possible transition errors. Another design issue related with this layer is the multi-clock-domain communication issue. In a large on-chip system, different functional hosts may work in different clock domains in order to achieve optimal performance; hence data transfer crossing clock domains is a design challenge. A data link design is presented in [58] to deal with this issue using mesochronous links. Another approach is to apply GALS scheme [15, 69] into on-chip networks. It means that the global links and the local links in a large on-chip system apply different communication methods to solve the multiple clock domain problem and increase data transfer reliability. This topic will be discussed further in Chapter 3.

- (3) **Network Layer.** The network layer provides the means of data transfers through a network connection between a source and a destination. It should make the transport layer independent on the data routing and relay considerations. For a NoC design, the main issues to be handled in this layer include network topology and data routing.

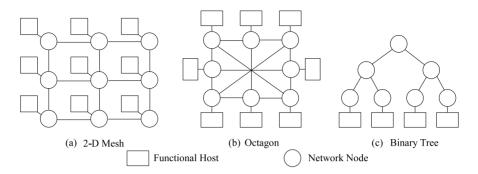

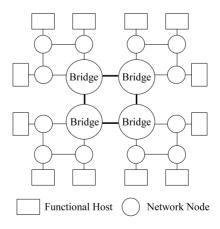

Network topology concerns the layout and connectivity of the nodes and channels in a network. According to the functions of network nodes in a network topology, networks can be classified into direct and indirect networks. In a direct network, each node is both a terminal and a switch node. An example topology of direct networks is the 2-Dimensional (2-D) mesh topology illustrated in Fig.2(a). In a mesh topology, each node is used as a terminal node connecting with a functional host and as a router node switching data to their destinations.

Fig. 2. Network Topology Examples.

Many NoC designs apply mesh topology since its simple structure and the ease of placement. Another topology of direct networks which has been applied in NoC designs is the octagon topology illustrated in Fig.2(b). It is an eight-node ring network with extra links between each pair of opposite nodes in the ring structure. In an indirect network, each node works either as a terminal or a switch. It cannot carry out both functions. An example of this category is the tree-based topology illustrated in Fig.2(c) with a case of binary tree. As illustrated in the figure, the nodes at the bottom level work as terminals to connect with functional hosts, while the nodes in higher levels function only as data switching nodes. Although other topologies exist for interconnection networks, only a few examples which have been applied in NoC designs were presented in this paragraph to give a glimpse on NoC topology choices. The NoC examples which apply these topologies will be presented in section 2.2.

Besides network topology, the routing method is another issue that needs to be considered in the network layer of a NoC design. After a network topology is set, a routing method is used to decide the path that data will be transferred from the source node to the destination node. According to different aspects, routing methods summarized in [72] can be classified in three ways as presented in the following three paragraphs.

Depending on where the routing decision is made, we can have source routing and distributed routing. By source routing method, the entire path of data transfers is determined by the source node before data transfers. By distributed routing, each router node decides the next node where the received data will be sent.

Depending on the information on which the routing decision bases, routing methods can be classified into deterministic routing and adaptive routing. Deterministic routing means that the data transfer path is determined only according to the source and destination addresses. Whereas, with adaptive routing method, the path is decided not only by the source and destination information, but also by the dynamic network conditions, such as traffic congestion information in the network.

Depending on the length of the decided path, minimal routing and non-minimal routing meth-

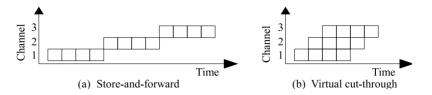

Fig. 3. Packet-Buffer Flow Control Methods.

ods can be differentiated. If a selected path is one of the shortest paths between the source and the destination, this method is called minimal routing. Otherwise, it is called non-minimal routing method.

A routing method applied in NoC designs can be a mixture of different routing categories. For example, the X-Y routing method is both deterministic and minimal. In X-Y routing, the data are transferred along the rows first, then are moved along the columns toward the destination in a 2-D mesh network. Because adaptive routing involves dynamic arbitration mechanisms which incur complex node implementation, deterministic routing is normally applied in NoC designs.

(4) **Transport Layer.** Transport layer protocols establish and maintain end-to-end connections between transport level entities. The concerned design issues in this layer include flow control and Quality of Service (QoS) management.

Flow control is the mechanism that determines the allocation of resources for data as they progress along their routes. According to the way of utilizing the channels between network nodes, two different approaches, circuit-switching and packet-switching [20], can be applied. In a circuit-switched network, a dedicated path from source to destination is set up before data transport and reserved until the transport is complete. In a packet-switched network, the data are transferred in form of packets. There are no channels set up for a data packet. All packets travel to their destinations by sharing the existing channels among nodes and following their paths determined by a routing method. The main disadvantage of circuit-switched networks is the lower efficiency of channel usage than the packet-switched network, which is caused by setting up dedicated paths for data transport. Therefore, packet-switching method is popular in NoC designs.

Normally, an on-chip network needs to include buffers to facilitate data transfers. According to the granularity at which buffers and channels are allocated and the way of forwarding data along their routes, flow control methods can be classified into packet-buffer flow control and flit-buffer flow control [20]. A flit is the minimum unit in a packet that can be recognized by a flow control method.

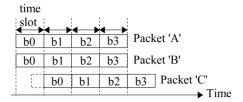

Two basic packet-buffer flow control methods are store-and-forward and virtual cut-through [20]. The principle of store-and-forward method is illustrated in Fig.3(a) with an example

of transferring a four-flit packet. With store-and-forward method, a packet will not be forwarded to the next node along its path until all flits of the packet are received by the current intermediate node. Therefore, the disadvantage of this method is the high packet transfer latency caused by inefficient usage of channels. Hence, virtual cut-through method is proposed to solve this problem by immediately forwarding the received packet flit to the next node if the buffer and channel resources are available for the whole packet, without waiting for the entire packet to be received. Its principle is illustrated in Fig.3(b) without contentions. By transferring packets as soon as possible, virtual cut-through method reduces the serialization latency of store-and-forward method. However, there are two main shortcomings of virtual cut-through, or of any other packet-based flow control methods. One of them is the inefficient usage of buffers caused by allocating buffers in units of packets. This is very important when there are multiple buffer sets to reduce blocking or providing deadlock avoidance in a NoC. Another shortcoming is that the contention latency is increased by allocating channels in units of packets. The blocked packet needs to wait for the whole packet in transmission passing through the channel before it can acquire that channel. These shortcomings can be overcome by allocating resources in units of flits rather than packets.

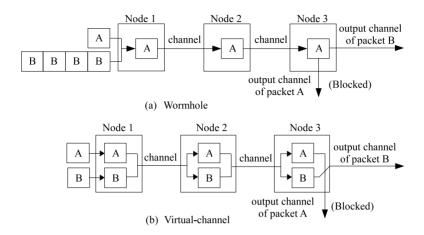

A popular flit-buffer flow control method is wormhole method [20] which operates like virtual cut-through, but with resources allocated to flits rather than packets. It means that a flit only needs to acquire one flit buffer and one flit channel bandwidth before it can travel to the next node, which relieves the requirement of resources in comparison with virtual cut-through method. Whereas, with wormhole method, a packet in transfer occupies multiple channels when its flits are traversing along the channels one by one. This will cause a problem if the current packet is blocked during transfer. As illustrated in Fig.4(a), if the flit of packet A is blocked at the intermediate node 3 because of congestions, all the channels occupied by this packet will exclude packet B from using them. In this situation, virtual-channel method [20] is proposed to solve this blocking problem by associating multiple buffers to one physical channel. By using the buffers, multiple virtual channels can be set up on a single physical channel. As illustrated in Fig.4(b), with the virtual channels, the flits of packet B can be transferred to node 3 even when the flits of packet A are blocked at node 3.

Generally, the flit-buffer flow control methods are preferred in NoC designs because of its efficient usage of buffers and channel bandwidth. The application examples in NoC designs will be presented later in section 2.2.

Another issue concerned in the transport layer of a NoC design is QoS. It refers to the service qualification that is provided by the network to its users. In [43], the QoS in the context of NoC designs is classified into two basic classes, Best-Effort (BE) services and Guaranteed Services (GS). In BE services, the network makes no strong guarantee about the delay or loss, while the GS scheme can guarantee a certain level of performance as long as the injected traffic complies with a set of restrictions. Both types of QoS have been applied in NoC

Fig. 4. Flit-Buffer Flow Control Methods.

designs. Because GS service demands more resource reservation and complex control logic than the BE service does, it is more expensive to support GS service in a NoC design.

(5) Session/Presentation/Application Layer. These three layers handle the communication processes of an interconnection network in high levels. Session layer mainly focuses on the connections between hosts. Presentation layer concerns the data representation and security issues. Application layer supplies services to user-defined application processes using interconnection networks. Generally, the services and functions of these three layers will be implemented by processors or software. Therefore, a NoC design normally does not need to directly handle the issues related to these layers.

The OSI model is only a reference for designing an interconnect network. Therefore, it only gives a guideline for designing an on-chip network rather than a regulation. From the above discussions about the OSI model and NoC design issues, we can see that the NoC design issues are generally within the three or four lowest layers in the OSI model and the boundaries between the design issues according to the layer definitions are not very strict. The presented design issues in this subsection do not mean a complete list of all possible design issues of on-chip networks, or rather, they are some typical NoC design issues addressed according to the OSI model.

# 2.2 Examples of Existing NoC Designs

A lot of research work about NoC structures has been carried out with different application requirements and backgrounds. There is no standard way to classify or summarize them. In this section, some examples are introduced to present the diversity of the existing NoC designs.

#### 1. Different Topologies

As presented in section 2.1, 2-D mesh is the most widely applied topology since its simple structure and tidiness for placement. The SoCBUS presented in [93], HERMES NoC presented in [66], and the NoC design presented in [19] are the examples of 2-D mesh network. Based on 2-D mesh, another topology called 2-D torus can be formed by connecting each row and column of nodes in a 2-D mesh network into a ring. An interconnection network presented in [60] is the example of 2-D torus network. The torus network consists of four nodes and it is implemented on an FPGA device. Another type of topology quite different from the mesh and torus is an octagon topology illustrated in Fig.2(b), the NoC presented in [45] applies this topology. In the octagon NoC, the channels between every node are bidirectional links.

Besides the topologies of direct networks, indirect network topology is also applied in NoC designs. For example, SPIN [34] is a NoC design which applies a fat-tree topology consisted of two levels of routers, four routers in each level. Each router in the first level connects with four functional hosts. Each channel is comprised of two one-way 32-bit data paths. The fat-tree topology network is further explored by a NoC design called XGFT [46]. The XGFT NoC applies an extended generalized fat-tree topology to achieve better scalability and performance in comparison with a fat-tree network.

## 2. Different Data Switching Methods

The PROPHID architecture [55] is an early developed NoC which applies circuit-switching scheme. PROPHID uses a three-stage switch structure which consists of time-division switch and space-division switch to carry out data transfers in a multiprocessor system. Because the circuit-switching scheme has the disadvantage of non-scalability and insufficient parallelism for future on-chip systems, packet-switching scheme is most widely applied in current NoC designs, such as the mentioned HERMES network, SPIN network, and XGFT network.

However, there exists switching methods which combine the characteristics of both circuit switching and packet switching in NoC designs. For example, the SoCBUS applies a Packet Connected Circuit (PCC) [93] method which hybrids circuit switching with packet switching to transfer data in the network. It uses packet switching to set up the connection between network nodes and lock the setup as a circuit for data transmission. The Æthereal NoC [23] developed by Philips research laboratories applies a pipelined time-division multiplexed circuit switching scheme in a packet-switched network in order to acquire contention-free routing.

#### 3. Different Routing Methods

For the sake of simplicity, deterministic routing methods are applied in the most of NoC designs. For example, the X-Y routing method introduced in section 2.1 has been applied in the 2-D mesh HERMES NoC, SoCIN NoC [97], and the network presented in [60]. In

SoCBUS, each node makes the routing decision based on the destination address and the static knowledge of the general direction to each destination. In Octagon NoC, a deterministic minimal routing method is realized by choosing the output direction at each node according to predefined rules.

In [22], three partially adaptive routing methods, west-first, north-last, and negative-first, are proposed for 2-D mesh networks. The common idea of those methods is that a deterministic route is followed when certain limits are obeyed, otherwise, the routing decision made by a node can be adaptive according to traffic conditions. For example, with the west-first routing, a node always tries to transfer packets firstly to the west direction of the source node whenever it is possible, otherwise, routing direction is adaptive to the traffic condition. The comparison between the three partially adaptive methods and X-Y method is also presented in [22]. The conclusion is that X-Y routing appears as the better choice in most situations in HERMES NoC.

#### 4. Different Flow Control Methods

Wormhole and virtual-channel methods are two most frequently used flow control methods in NoC designs. Because the wormhole method requires less buffers and simpler control, it is easier to be applied in NoC designs. The widely accepted Æthereal NoC applies wormhole method in its best-effort router. HERMES, SoCIN, and SPIN also apply wormhole method. For virtual-channel method, the NoC design presented in [19] is an example. It applies 10K bits storage for virtual channels at each input controller. Virtual channels are also applied in a router design presented in [28] to support different QoS.

#### 5. Different QoS Strategies

As addressed in section 2.1, GS and BE are two types of QoS applied in NoC designs. GS provides predictability of data transfers, while BE service has higher resource utilization. NOSTRUM [54] is an example of NoC design which provides GS. It uses looped containers implemented by virtual circuits to support GS in a mesh network. While in Æthereal NoC, both GS and BE services are provided by using a combined GS-BE router structure. The router includes two parts; one part applies pipelined circuit switching to implement its guaranteed service, while the other part applies input-queued wormhole flow control to provide best-effort service. Another type of combination of GS and BE services is presented in [28]. The design provides differentiated QoS between GS and BE by allowing higher priority data streams to overtake those of lower priority in virtual channels.

#### 6. Different Implementation Strategies

As the design requirements for a NoC may vary largely depending on the applications, there is no a universal design which suits for all applications. Therefore, some NoC designs, e.g. SoCIN and Xpipes, realize the network components in a soft format which can be customized for a specific application. With the support of specialized design tools, e.g. XpipesCompiler,

many design parameters, such as topology, network interfaces, and switch structures, can be customized to meet the requirements of a specific application during the design stage. Of course, the changeable design parameters in this type of NoC design can not be arbitrary. For instance, the topologies supported by SoCIN NoC only include mesh and torus. However, these choice limitations are reasonable since it is impossible to predict and meet all possible application requirements in one design.

#### 7. Different Communication Synchronization Strategies

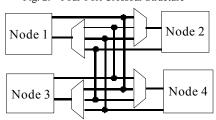

As addressed in section 2.1, GALS communication scheme is introduced in NoC to deal with the issue of multiple clock domain data transfer. Thus, asynchronous circuit design is applied in some NoC designs to implement GALS scheme. A NoC design called CHAIN [4] is such an example of an asynchronous NoC. It applies self-timed logic to build pipelines, multiplexing structures, and steering latches to transfer data with handshake protocols. Another GALS NoC example is MANGO presented in [8] which applies OCP compliant network adapter block to connect the functional blocks with its asynchronous communication network. It also provides both guaranteed and best-effort services by utilizing virtual channels [11]. Nexus NoC presented in [57] is an example of GALS NoC different from router-based NoC. It applies a 16-port asynchronous crossbar structure to build an on-chip data switch.

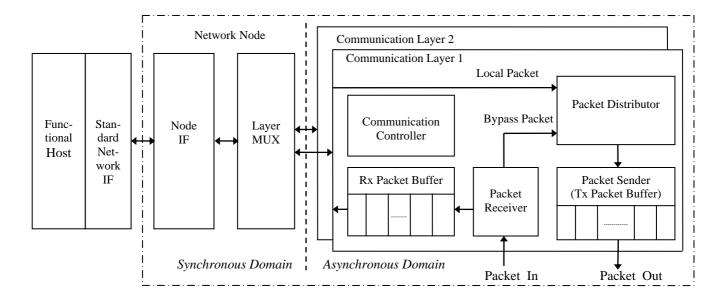

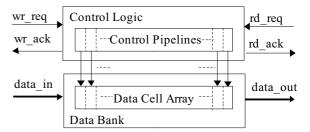

#### 8. The Proteo NoC Architecture

Finally, the Proteo NoC architecture [85] developed in our department is introduced. Its name, Proteo, is taken from ancient Greek mythology to express the idea of flexibility of the proposed NoC architecture. Conceptually, as stated in [85], the Proteo NoC architecture consists of a library of hardware components, a set of CAD tools and a methodology of usage. The idea of Proteo NoC is to make a NoC instance be easily and quickly built for a specific application by applying specialized design tools and optimization methodology on a heterogeneous hardware IP library. A Proteo NoC instance is a packet-switched network in which topologies can be customized according to applications. Currently, deterministic routing and virtual cut-through flow control method are applied in a Proteo NoC instance. Proteo NoC supports Virtual Component Interface (VCI) [91] and Open Core Protocol (OCP) [75] interface standards for connecting each functional host to its corresponding network node.

### 3. APPLYING GALS SCHEME INTO ON-CHIP NETWORKS

As mentioned in Chapter 2, the number of processing or functional components in an onchip system becomes larger and larger. Currently, a 64-core on-chip system, TILE64 [89], has already been produced. It is believed that a future on-chip system will consist of sea-ofprocessors in one chip [80]. Besides the growing number of system components, the functionalities of system components also become largely different from each other. It means that an on-chip system may include different processors for different computation tasks, varied hardware accelerators for varied functions, and various interface controllers for various peripheral devices. Therefore, these heterogeneous system components have different optimal working clock frequencies according to the tasks that they are handling. When integrating all the heterogeneous components into an on-chip system, coordinating different clock domains is a challenge.

# 3.1 Multi-Clock Challenge and GALS Scheme

From the viewpoint of a chip design, as addressed in [74], for large high-speed globally synchronous ASICs, designing the clock distribution net becomes a troublesome task because of the problems caused by clock skew, by the growing die sizes and shrinking clock periods. At the same time, the power consumption is increasing tremendously because the working clock frequency driven by demanding applications is getting higher in the scale of giga-hertz.

Therefore, one solution of the challenges mentioned above is to enable different processing or functional system components to work at their own clock rates. Thus, the following challenge that a SoC designer needs to handle is how to integrate the clock independent components into one system. In this situation, GALS scheme is proposed to solve the system integration challenge. The GALS scheme is firstly introduced in [15] to prevent metastability by stretching local clocks. The basic idea of applying GALS scheme into on-chip systems is to partition the system into several independently clocked domains that communicate with each other in an asynchronous fashion. The GALS scheme is the basis of the NoC structures designed and realized in this work. The method and challenges of designing a GALS on-chip network will be presented in the following two sections.

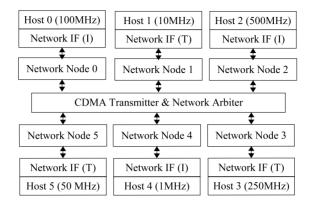

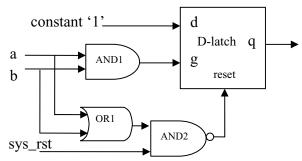

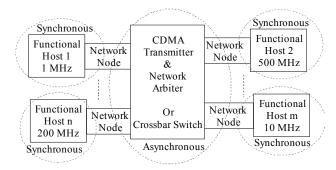

Fig. 5. A Method of Applying GALS Scheme in a NoC Design.

# 3.2 The Synchronization in GALS NoC

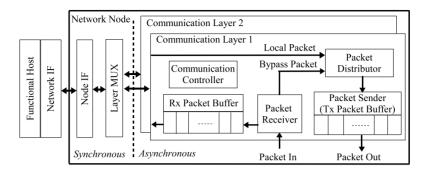

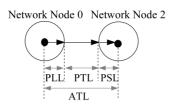

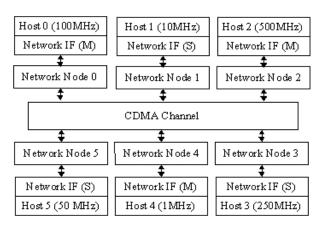

In an on-chip system, communication tasks among system components are performed by the on-chip network. Thus, the issue of realizing GALS scheme in an on-chip system equals to realize GALS scheme in the on-chip network. The method of applying GALS scheme in the NoC structures developed in this work are illustrated in Fig.5. From the figure, we can see that each network node contains an interface block which works at the same clock rate as the system functional block attached to it, while the blocks for global communication among network nodes apply asynchronous scheme.

Therefore, the data synchronization between synchronous and asynchronous domains is the main challenge of designing a GALS NoC. The term, synchronous domain, used in this thesis refers to the group of design blocks which work under the dictation of clock signals in a SoC, while, the term of asynchronous domain refers to the group of blocks which work in a self-timed manner without any clock signals.

Many synchronization schemes or structures for data transfers among independent clock domains in a GALS system have been presented. One category of solutions is to avoid synchronization failure by adjusting the clock signal of the local synchronous module or by generating a controllable clock signal in the synchronization interface. For example, the work presented in [35] develops a stoppable clock structure to build a deterministic wrapper. The work in [69, 99] presents stretchable clock schemes to avoid synchronization failure in the interface between synchronous and asynchronous domains. A pausible clock scheme is firstly presented in [96] to manage the data transfers between independent clock domains without synchronization failure. The work presented in [63, 68] further develops the pausible clock scheme. The work in [12] presents an asynchronous wrapper which combines the

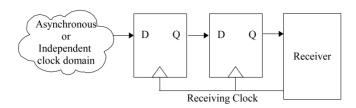

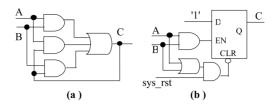

Fig. 6. Double-Latching Synchronization Scheme.

stretchable and pausible schemes together. This wrapper can avoid synchronization failures caused by metastability in circuits. One common feature of those presented synchronization schemes is that they all involve specialized clock generation or control circuits which need to be implemented in circuit level. Thus, if a GALS NoC design applies one of those synchronization schemes, the whole design can not be realized in Register-Transfer Level (RTL) by using Hardware Description Language (HDL), which in turn makes the NoC design less implementation flexible and portable. Therefore, this type of synchronization scheme is not applied in the NoC designs presented in this thesis.

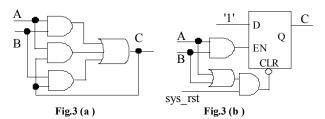

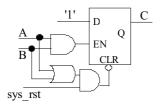

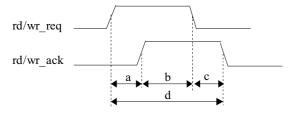

Another type of solutions of data synchronization in a GALS system is to synchronize the signals from asynchronous domain with the local clock in an arbitrary timing relationship and limit synchronization failures within an acceptable level. The most widely applied scheme in this category is the double-latching scheme as illustrated in Fig.6. It consists of two serially connected D-Flip-Flop (D-FF) components to latch the input signals with the reference clock of the receiver. It is possible that the first D-FF enters into metastable state if input signal transitions violate the setup or hold timing requirement. In this situation, the second D-FF gives a whole clock cycle for the first D-FF to resolve the metastability before latching its output. However, in the double-latching scheme, there still exists the failure possibility if the first latch can not get rid of metastability state before the second flip-flop samples its output. Therefore, Mean Time Between Failure (MTBF) is introduced to measure the safety of a synchronizer. MTBF gives indication about how often a synchronization failure occurs. The performance analysis of double-latching synchronizers and the equation of calculating MTBF of a synchronizer are presented in [24,53]. As addressed in [24] and presented in (1), the MTBF equation consists of the time (t) allowed for synchronization, the settling time (7) of Flip-Flop (FF), the sampling clock frequency  $(f_s)$ , the frequency  $(f_d)$  of data edges which generates a metastability, and a parameter  $(T_w)$  related to the metastability window of the FF.

$$MTBF = \frac{e^{t/\tau}}{T_w \cdot f_s \cdot f_d} \tag{1}$$

Besides the double-latching scheme, many other synchronization schemes or structures have also been proposed. For instance, a pipeline synchronization structure is proposed in [82] to achieve high communication bandwidth while keeping the failure possibility arbitrarily low.

Publication [26] presents a speculative synchronizer structure in transistor level to reduce synchronization latency. Another transistor level synchronizer design is presented in [44] to achieve high performance in a low voltage application. In [52], a parallel synchronizer scheme which bases on the double-latching scheme is introduced to reduce synchronization latency. All those presented synchronizer structures require the design to be implemented in gate or transistor level. In order to make the entire design of a GALS NoC suit the commonly used synchronous design flow, both the synchronous and asynchronous designs need to be modeled by using the commonly used HDL. Therefore, the double-latching scheme is selected to be used in the GALS NoC designs in this thesis.

In the GALS NoC designs presented in this thesis, double-latching scheme is used for synchronizing the handshake control signals for data transfers rather than the data signals themselves. For example, when transferring data from asynchronous domain to synchronous domain, the asynchronous logic will assert a request signal after the data to be transferred are ready. Then the asserted request signal will be synchronized with the receiving clock domain through a double-latching structure as illustrated in Fig.6. Whereas, the acknowledge signal that the synchronous domain sends back to the asynchronous domain can be received directly. When data are transferred from synchronous domain to asynchronous domain, the double-latching scheme is only needed for the synchronous logic to receive an acknowledge signal from the asynchronous domain during a four-phase handshake process. The safety of applying double-latching scheme has been analyzed in [31], where it is stated that the MTBF of most SoC designs is safe far more than enough by simply setting the resolving time window to one clock cycle. Among the published NoC designs, MANGO NoC is an example which applies the double-latching scheme to synchronize the synchronous and asynchronous domains. In [9], the designer of MANGO NoC claims that the estimated MTBF of the implemented double-latching synchronizer is longer than 8000 years. Therefore, the simple and safe enough double-latching scheme is a reasonable choice for a GALS NoC design.

# 3.3 The Asynchronous Design for GALS NoC

In order to realize a GALS NoC design, both synchronous and asynchronous designs are needed. Synchronous design methodology and techniques have been well established and applied. Many standard design tools and design flows are developed for synchronous designs. Whereas, asynchronous design has not been widely applied after it was born in 1950s. The asynchronous designs of the GALS NoCs developed in this work will be presented in this section.

### 3.3.1 Introduction of Asynchronous Design

As stated in [70], asynchronous design methods can date back to 1950s and to two people in particular: D.A. Huffman and D.E. Muller. Huffman developed an asynchronous design methodology known as fundamental-mode circuits [38] in which the delay in all circuit elements and wires is assumed to be known, or at least bounded. The methodology developed by Muller is Speed-Independent (SI) circuits [67] in which gate delays are assumed to be unbounded while the wire delays are negligible.

Almost all the other types of asynchronous design methods can find their roots in those two fundamental methodologies. For example, Delay-Insensitive (DI) circuit model extends the assumption of SI circuits by assuming that both gate and wire delays in circuits are unbounded. The burst-mode design methodology [73] assumes that only the specified input bursts which can make circuits leave the current state can occur in a given circuit state, and the fundamental-mode assumption is applied between transitions among different input bursts. Ivan Sutherland developed a micropipeline structure [87] as an asynchronous alternative of synchronous elastic pipelines. A micropipeline structure consists of a bounded-delay data path controlled by delay-insensitive control logic.

After the birth of asynchronous design in 1950s, it has not been as widely adopted as synchronous designs except several academic projects during the first several decades, such as the ILLIAC II computer [13] developed at University of Illinois in 1960s, the first operational data-flow computer [21] developed at the University of Utah in 1970s, and the first fully asynchronous microprocessor [61] developed at California Institute of Technology in 1980s. As the development of IC design in recent decades, synchronous designs face the hard challenges of clock distribution, power consumption, and design complexity. Therefore, as an alternative to synchronous design, asynchronous design gains more applications than before. For instance, Philips developed asynchronous pager chips [79] in 1998 and a contactless smart-card chip [48] in 2000. A series of asynchronous microprocessors called Amulet [29, 30, 94] have been developed in University of Manchester from 1994 to 2000. In 2005, products based on an asynchronous NoC design were released by a company called Silistix [37]. One common motivation of those asynchronous design applications is to utilize the advantages of asynchronous design. Several main advantages of asynchronous design are briefly introduced in the following five paragraphs as the end of this short introduction of asynchronous design.

- (1) Low power consumption. Because asynchronous circuits do not need any clock signals, the power spent on clock switching in a synchronous chip is avoided. Additionally, the signal transitions in asynchronous circuits will automatically stop when there is no driven event. Therefore, asynchronous designs can achieve lower power consumption.

- (2) No clock distribution and clock skew. This advantage is obvious since the lack of clock

Fig. 7. The Control Logic of Micropipeline.

signal in asynchronous circuits. Thus, the difficulties of clock distribution and clock skew faced by synchronous designs are removed from asynchronous designs.

- (3) Average-case performance. In a synchronous design, the operating speed is limited by the worst-case, called critical path, in the circuits. However, in asynchronous circuits, the operating speed is determined by actual local latencies in the circuits rather than the global worst-case latency. In most of cases, the average-case of latencies are smaller than the worst-case latency, hence, asynchronous designs can achieve better operating speed performance.

- (4) Less Electromagnetic Interference (EMI) radiation. In a synchronous design, flip-flop transitions follow a certain clock frequency so that the energy spent on signal transitions concentrates within the very narrow bands around the clock frequency. Thus, the synchronized signal switching activities will produce substantial electrical noise. Whereas, the switching activities in an asynchronous circuit are correlated loosely because there is no universal timing pace, hence, they produce a more distributed noise spectrum and a lower peak noise value.

- (5) **Robust and adaptive.** A synchronous circuit is sensitive to the delay variations caused by the variations of clock signal, supply voltage, and operating temperature related with the manufacture process and application surrounding. Whereas, because the loose timing requirement, asynchronous circuits can operate correctly under large variations caused by different manufacture processes and application environment.

### 3.3.2 The Asynchronous Designs Applied in the GALS NoCs

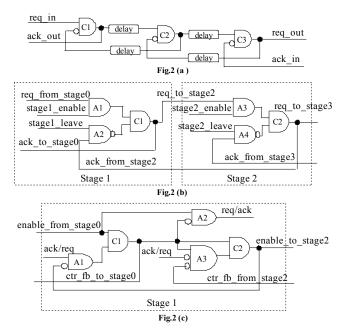

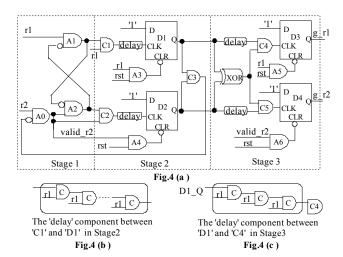

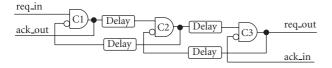

Although some asynchronous design tools and methods have been proposed, such as Balsa [81] and Tangram [90], there is no widely adopted or standard one. The asynchronous designs applied in the GALS NoC structures in this thesis base on the delay-insensitive control logic of micropipeline. The structure of micropipeline control logic is illustrated in Fig.7.

The logic components marked with 'C' in the figure represent the basic component of asynchronous circuits called C-element. The truth table of a C-element is listed in Table 1. From Fig.7, we can see that the principle of micropipeline control logic is to use the output from the next stage to enable or disable the output of the current stage. The components marked

| Input1 | Input2 | Output    |

|--------|--------|-----------|

| 0      | 0      | 0         |

| 0      | 1      | No Change |

| 1      | 0      | No Change |

| 1      | 1      | 1         |

Table 1. Truth Table of C-Element.

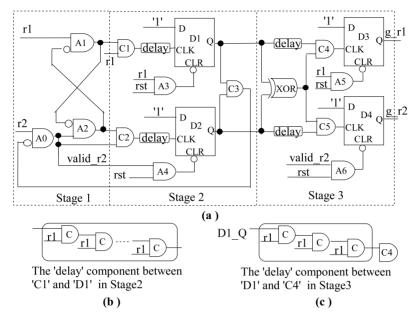

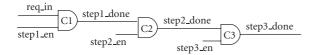

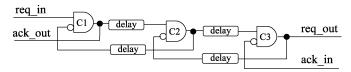

with 'delay' in Fig.7 illustrate the logic and wire delays along the paths. The asynchronous design applied in this work bases on the micropipeline control logic and will be presented in the following paragraphs.

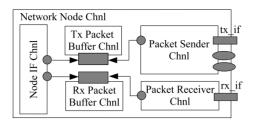

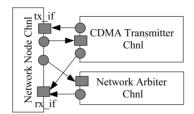

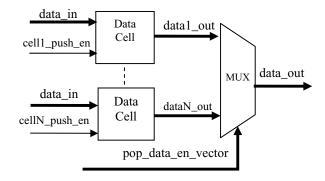

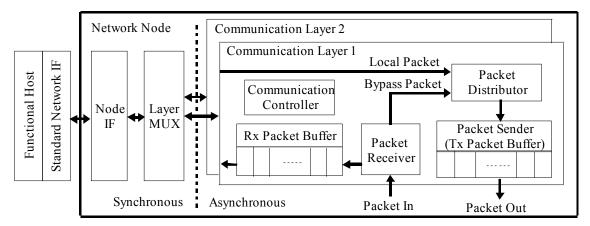

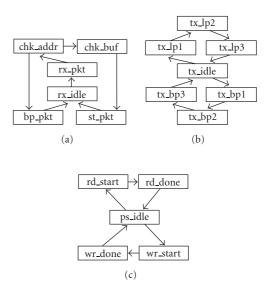

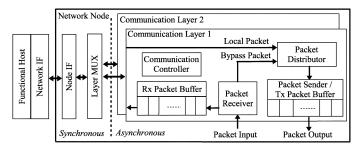

As illustrated in Fig.5, the GALS NoC designs in this thesis apply asynchronous design in a part of the network node and the interconnection structures between network nodes. The asynchronous design in the GALS NoCs can be divided into two parts which include data path and control logic. The data path is composed of the data registers which store or deliver the data items through a four-phase dual-rail handshake protocol under the control of the micropipeline-based control logic. Hence, the main design task is to design the control logic.

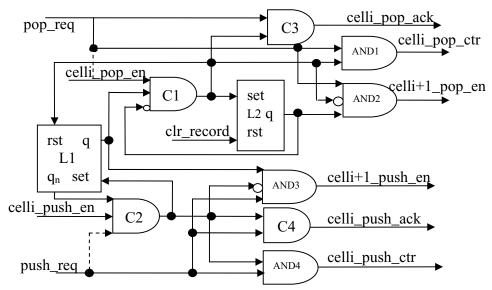

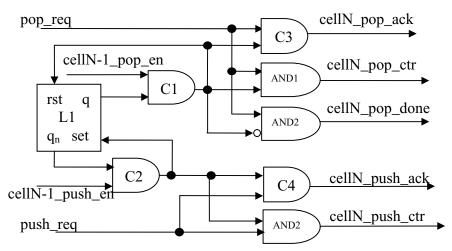

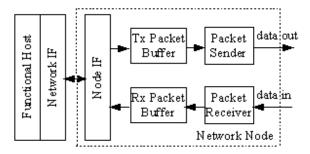

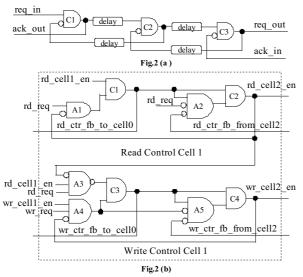

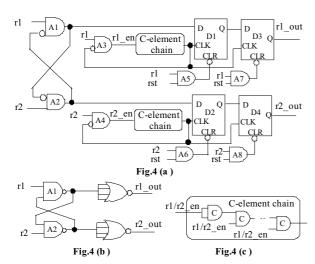

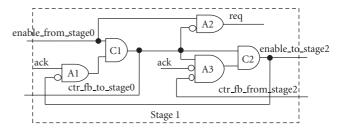

Two pipeline structures were developed as the control logic of the asynchronous design. One type of control pipeline is used for control-centric blocks, such as the control block in a network node which coordinates packet receiving and sending tasks. Another type of control pipeline, called block control pipeline, is used in data-path centric blocks, such as packet receiver and packet sender blocks in a network node. A hybrid control pipeline structure which combines the two pipelines mentioned above is applied as the control logic of the asynchronous FIFOs used in the packet buffer blocks of the GALS NoCs. Therefore, the following two paragraphs will present the two main control pipeline structures by analyzing their basic portions.

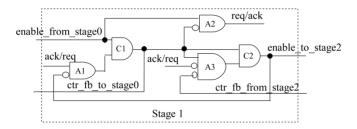

Two stages of the control pipeline used in control-centric blocks are illustrated in Fig.8. In the figure, we can see that the control pipeline uses micropipeline control logic as the backbone and applies a few AND gates as the delay components, hence, it is still delay-insensitive. The state information of the pipeline is passed through each stage in the pipeline by a four-phase handshake protocol. If we take the 'Stage 1' illustrated in Fig.8 as an example, when both the 'req\_from\_stage0' and 'stag1\_enable' signals are '1', the output of 'C1' will be set to logic '1' which indicates that the current active state of the pipeline is in the 'Stage 1'. Then the output of 'C1' can be used as a request signal to trigger the control logic in the corresponding function blocks for a certain communication process.

The structure of block control pipeline is illustrated in Fig.9. The main task of this type of control logic is to generate four-phase request or acknowledge signals for data transfers. Each stage of the control pipeline is composed of two C-elements as illustrated in Fig.9. The 'C1' is used to record the rising edge of a request or acknowledge signal, while the 'C2' is used

Fig. 8. Control Pipeline of Control-Centric Blocks.

Fig. 9. Block Control Pipeline.

to record the falling edge of a request or acknowledge signal. Therefore, each stage of the block control pipeline will pass the enable signal to the next stage only after the four-phase handshake process on the current stage has been completed. Although the presented block control pipeline structure can only meet Quasi-Delay-Independent (QDI) model because the input 'ack/req' signal is branched to 'A1' and 'A3', the timing requirement for distributing the 'ack/req' input signal along the isochronic wire forks is quite loose since the logic delays in 'A1' and 'C1' are usually much larger than the logic delay of the inverter at the input of 'A3'.

By using the presented control pipelines, the asynchronous design for the GALS NoCs proposed in this thesis are realized in RTL by using VHSIC Hardware Description Language (VHDL) together with the synchronous design. Thus, the GALS NoC designs are compatible with the commonly used design tools and flow for synchronous circuits. This feature facilitates the portability and flexibility of the NoC designs.

### 4. A DIRECT ON-CHIP NETWORK

As mentioned in section 1.1, the work presented in this thesis started from implementing GALS scheme in Proteo NoC architecture. This chapter presents the work of designing a GALS direct on-chip network as an instance of Proteo NoC architecture.

# 4.1 Network Topology

As stated in [85], Proteo NoC architecture consists of an interconnection IP library and software tools which automate the process of designing and configuring a network instance. Therefore, the topology of Proteo NoC architecture is open for exploration during the design stage. An optimal topology can be generated and utilized in a network instance of Proteo NoC for a specific application.

The author of Proteo NoC suggests applying ring-like topologies in an instance of Proteo NoC. As addressed in [85], this kind of topologies can simplify the analysis and make routing algorithms straightforward, while attaining a reasonable flexibility. After the further development of the automation tools and interconnect IP library of Proteo NoC architecture, the topologies presented in Chapter 2, such as 2-D mesh, torus, and octagon, can also be included.

Fig. 10. Ringlet Topology Example.

Fig. 11. Six-Node Bidirectional Ring Network.

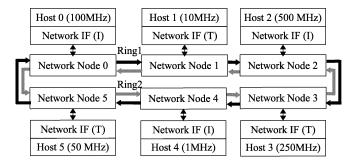

Currently, studying on ring-like topologies can already give a clue of the characteristics of Proteo NoC when a direct network structure is applied. Therefore, the GALS NoC design presented in this chapter applies a bidirectional ring topology. More complex topologies can be built by using the ring structure and bridge blocks as described in [85] and illustrated in Fig.10.

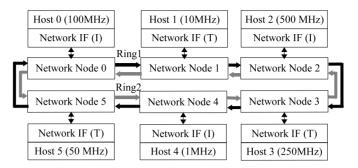

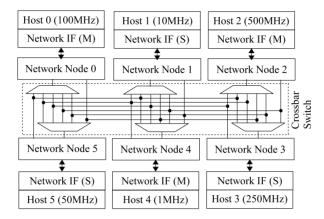

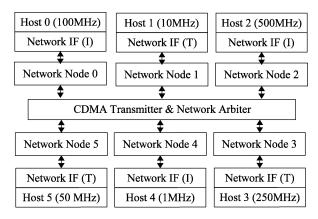

#### 4.2 Network Structure

The bidirectional ring NoC developed in this work is illustrated in Fig.11. It is a six-node network in which each functional host block is connected into the network through individual network node block. The interface between a functional host and a network node can apply one of the two widely accepted interface standards, VCI [91] or OCP [75], to adopt heterogeneous functional IP blocks in the design library. In this work, Basic VCI (BVCI) is applied because it is a good compromise between advanced features and the simplicity of realization. In the bidirectional ring network, each network node has two output and two input connections with its two neighbour nodes. From Fig.11, we can see that each functional host works at its own clock rate which may be very different from the clock rates of the other functional hosts. This setup highlights the necessity of applying GALS scheme in an on-chip network since all functional hosts work at different clock rates. In the context of the illustrated network, applying GALS scheme means that each local functional host can work with its own frequency while the communications between network nodes are performed in an asynchronous manner.

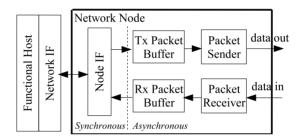

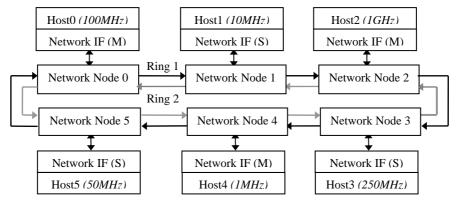

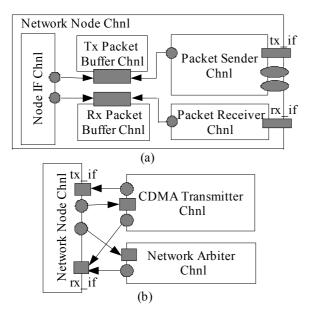

# 4.3 Network Node Design

A ring network belongs to direct network category in which each network node is both an interface block of a functional host in the system and a router node of switching data in the

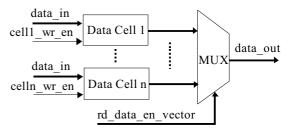

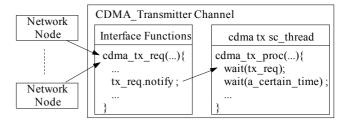

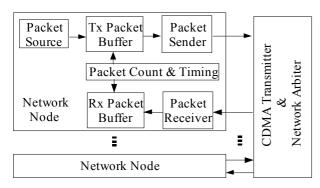

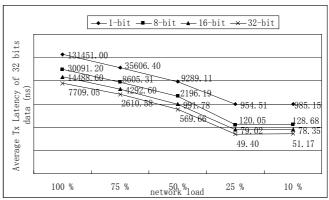

Fig. 12. Network Node Structure of the Bidirectional Ring Network.