### TAMPEREEN TEKNILLINEN YLIOPISTO TAMPERE UNIVERSITY OF TECHNOLOGY

Sanna Määttä

Modelling Embedded Applications for On-Chip Multiprocessing Platforms

Julkaisu 968 • Publication 968

Tampere 2011

Tampereen teknillinen yliopisto. Julkaisu 968 Tampere University of Technology. Publication 968

Sanna Määttä

### Modelling Embedded Applications for On-Chip Multiprocessing Platforms

Thesis for the degree of Doctor of Science in Technology to be presented with due permission for public examination and criticism in Tietotalo Building, Auditorium TB109, at Tampere University of Technology, on the 3<sup>rd</sup> of June 2011, at 12 noon.

Tampereen teknillinen yliopisto - Tampere University of Technology Tampere 2011

ISBN 978-952-15-2579-7 (printed) ISBN 978-952-15-2617-6 (PDF) ISSN 1459-2045

### ABSTRACT

The complexity of state-of-the-art embedded systems requires designers to focus on abstraction levels much higher than Register Transfer Level (RTL). As the designers are familiar with using RTL, system design often starts at levels of abstraction that are too close to implementation. Higher levels of abstraction substantially reduce the amount of details designers need to consider enabling complex system design in shorter time.

Modelling and simulation are essential methods in state-of-the-art embedded system design. In model-based design, a system model is the key element of the design process from the specification to the implementation. Modelling helps designers to manage complex systems, better understand the system under development, visualise a system, specify the structure and behaviour of the system, validate the system behaviour, and document the design decisions. Moreover, modelling reduces development time and costs.

This thesis describes a model-based approach for embedded application modelling and validation together with an on-chip multiprocessing platform. The aim of the work was to facilitate the programming of multiprocessing systems as well as to enable early system validation, design space exploration, and performance evaluation.

## PREFACE

The work presented in this thesis has been carried out in the Department of Computer Systems at Tampere University of Technology, Finland during the years 2005-2010 and in the Institute of Microelectronic Systems at Technical University Darmstadt, Germany during the academic year 2007-2008.

I would like to thank my supervisor Prof. Jari Nurmi for his guidance and encouragement through all these years as well as for providing such a positive atmosphere in the Team Nurmi. Moreover, I would like to express my gratitude to my "surrogate" advisor Dr. Leandro Soares Indrusiak, who took me under his wings during my stay in Germany and from that time on. Also, many thanks to Prof. Manfred Glesner who enabled my stay at MES. I am also grateful to the reviewers of this thesis Prof. Johan Lilius and Prof. Lisane Brisolara for providing constructive comments on this thesis.

I would like to thank my parents and brother as well as all my friends for their tolerance and support. I would also like to thank all the members of Team Nurmi for all kinds of co-operation and all entertaining (especially coffee table) conversations. Also, many thanks to Dr. Luciano Ost and M.Sc. Leandro Möller for their wonderful company in Germany and for never letting me swim alone...

This thesis was financially supported by the Tampere Graduate School in Information Science and Engineering (TISE), the SYSMODEL project, and Tampereen kaupungin tiederahasto, which are gratefully acknowledged.

> Tampere, May 2011 Sanna Määttä

# TABLE OF CONTENTS

| At                                                                   | stract  | i                                                             |

|----------------------------------------------------------------------|---------|---------------------------------------------------------------|

| Pre                                                                  | eface   |                                                               |

| Ta                                                                   | ble of  | Contents                                                      |

| Lis                                                                  | st of F | <i>ïgures</i>                                                 |

| Lis                                                                  | st of T | ables                                                         |

| Lis                                                                  | st of A | bbreviations                                                  |

| 1.                                                                   | Intro   | <i>duction</i>                                                |

|                                                                      | 1.1     | Objective and Scope of Research                               |

|                                                                      | 1.2     | Thesis Outline                                                |

| 2. Rising Above RTL: System Description at Higher Levels of Abstrac- |         | ng Above RTL: System Description at Higher Levels of Abstrac- |

|                                                                      | tion    |                                                               |

|                                                                      | 2.1     | Levels of Abstraction                                         |

|                                                                      | 2.2     | System Design and Modelling 6                                 |

|                                                                      | 2.3     | Design Space Exploration                                      |

|                                                                      | 2.4     | Model Accuracy versus Simulation Speed 9                      |

|                                                                      | 2.5     | Heterogeneity and Models-of-Computation 11                    |

|                                                                      | 2.6     | System (Level) Design Languages                               |

|                                                                      | 2.7     | UML                                                           |

|    |       | 2.7.1 UML Profiles                                                                       | 14 |

|----|-------|------------------------------------------------------------------------------------------|----|

|    |       | 2.7.2 Repetitive Structure Modelling using MARTE                                         | 16 |

|    |       | 2.7.3 UML Diagrams                                                                       | 16 |

| 3. | Ptole | emy II: A Software Framework for Actor Oriented Experimenting                            | 21 |

|    | 3.1   | The Ptolemy Project                                                                      | 22 |

|    | 3.2   | Actor Orientation and Hierarchical Heterogeneity                                         | 23 |

|    | 3.3   | Advantages of the Ptolemy II Framework                                                   | 25 |

| 4. | More  | e and Less Abstract Models of Network-on-Chip Interconnects                              | 27 |

|    | 4.1   | HERMES: The RTL Reference Model                                                          | 28 |

|    | 4.2   | RENATO: Modelling the HERMES Switch Using UML In-<br>teractions                          | 29 |

|    | 4.3   | JOSELITO: Number of Model Details Versus Simulation Speed                                | 32 |

|    | 4.4   | BOÇA: Analytical Calculation of Communication Latency                                    | 33 |

| 5. | UML   | Extension to the Ptolemy II Framework                                                    | 35 |

|    | 5.1   | Encapsulating UML Sequence Diagrams Inside Composite<br>Actors                           | 35 |

|    | 5.2   | Simulating UML Sequence Diagrams within Executable System Models                         | 37 |

| 6. |       | lating Embedded Applications Together with on-Chip Multipro-<br>ng Platforms             | 41 |

|    | 6.1   | An Approach for Embedded Application Modelling for on-<br>Chip Multiprocessing Platforms | 42 |

|    | 6.2   | Application Modelling                                                                    | 43 |

|    | 6.3   | Platform Modelling                                                                       | 47 |

|    | 6.4   | Mapping Application Models on Platform Models                                            | 48 |

|     | 6.5     | Enabli           | ng Joint Validation of Application and Platform Models       | 49 |

|-----|---------|------------------|--------------------------------------------------------------|----|

|     |         | 6.5.1            | Basic Principles                                             | 49 |

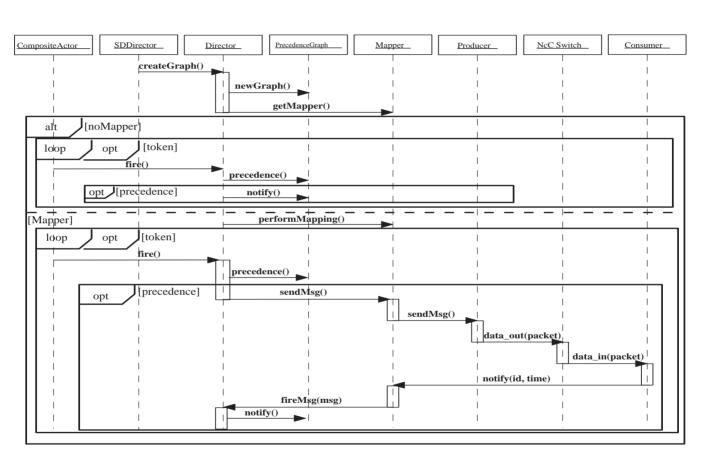

|     |         | 6.5.2            | Interaction Between the Different Elements of the System     | 50 |

|     | 6.6     | Creatin          | g Hierarchically Heterogeneous Application Models            | 56 |

|     | 6.7     | UML F            | Profiling                                                    | 60 |

| 7.  | Case    | Studies          |                                                              | 65 |

|     | 7.1     | Case S<br>Models | tudy of Joint Simulation of Application and Platform         | 67 |

|     | 7.2     |                  | tudy of Application Validation on Multi-Abstraction m Models | 70 |

|     | 7.3     |                  | tudy of Evaluating Communication and Computation             | 75 |

|     | 7.4     | Case S           | tudy of Modelling with Priorities and Timing Constraints     | 79 |

|     | 7.5     | Case S           | tudy of Simulating Heterogeneous System Models               | 82 |

|     | 7.6     | Discus           | sion                                                         | 86 |

| 8.  | Conc    | clusions         |                                                              | 91 |

|     | 8.1     | Future           | Development                                                  | 91 |

| Bil | bliogra | aphy .           |                                                              | 93 |

## LIST OF FIGURES

| Y-chart [63] ©IEEE, 1999                                                                                                     | 9                                                                                                                                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| The abstraction pyramid depicts the trade-off between the modelling effort and level of detail [57] ©A.C.J. Kienhuis, 1999 . | 10                                                                                                                                                                                                            |

| UML extension mechanisms: stereotypes, constraints, and tagged values                                                        | 14                                                                                                                                                                                                            |

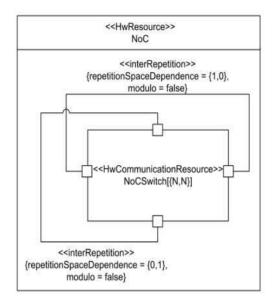

| A 3x3 torus topology described using the RSM notation                                                                        | 17                                                                                                                                                                                                            |

| UML sequence diagram and the corresponding communica-<br>tion diagram                                                        | 18                                                                                                                                                                                                            |

| Vergil workspace showing composite and atomic actors and executive and local directors                                       | 24                                                                                                                                                                                                            |

| RENATO's UML interactions [46] ©IEEE, 2008                                                                                   | 31                                                                                                                                                                                                            |

| Encapsulating a UML sequence diagram inside a composite actor [44] ©IEEE, 2006                                               | 36                                                                                                                                                                                                            |

| Actors connected to the input and output ports of a composite actor [44] ©IEEE, 2006                                         | 37                                                                                                                                                                                                            |

| UML editor extension to the Ptolemy II framework                                                                             | 38                                                                                                                                                                                                            |

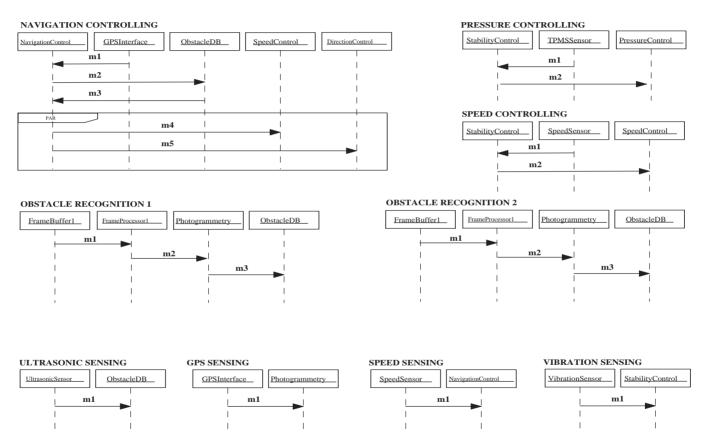

| Sequence diagrams describing an autonomous vehicle appli-<br>cation                                                          | 45                                                                                                                                                                                                            |

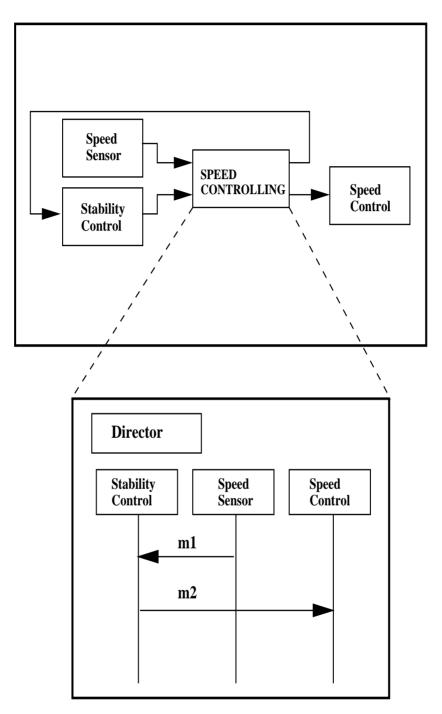

| Speed controlling sequence diagram connected to application actors                                                           | 46                                                                                                                                                                                                            |

| Platform description using the RSM notation                                                                                  | 48                                                                                                                                                                                                            |

|                                                                                                                              | The abstraction pyramid depicts the trade-off between the mod-<br>elling effort and level of detail [57] ⓒA.C.J. Kienhuis, 1999 .<br>UML extension mechanisms: stereotypes, constraints, and<br>tagged values |

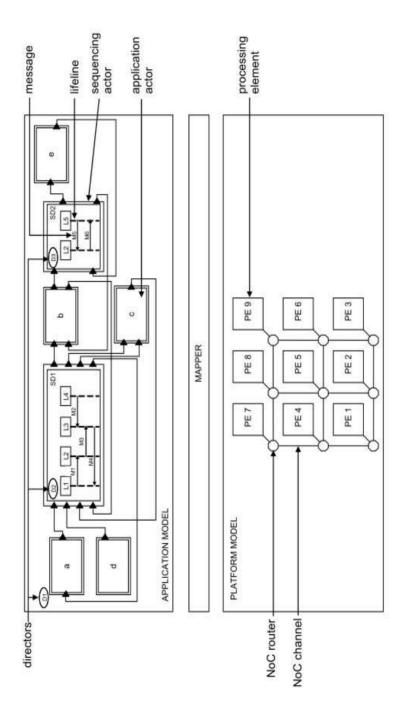

| 14 | Application and platform models [67] ©IGI Global, 2010                                                                                                  | 51 |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 15 | Sequence diagram of the application elements' interaction dur-<br>ing simulation                                                                        | 52 |

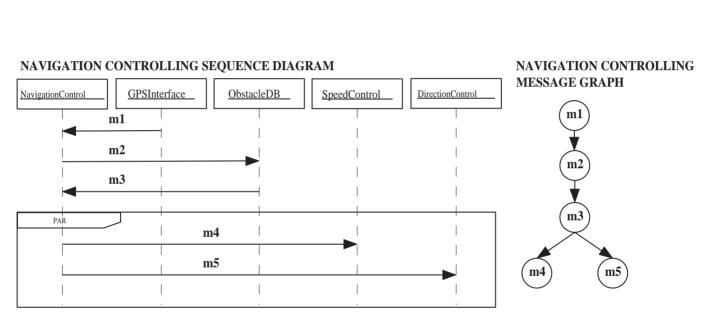

| 16 | A sequence diagram with its corresponding message graph                                                                                                 | 53 |

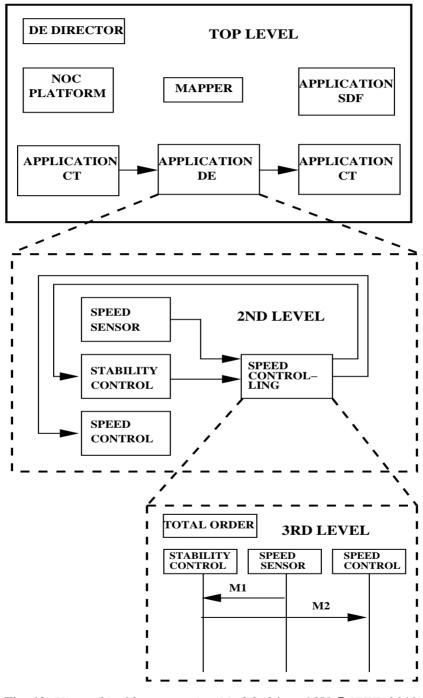

| 17 | Hierarchical description style of the Ptolemy II framework                                                                                              | 57 |

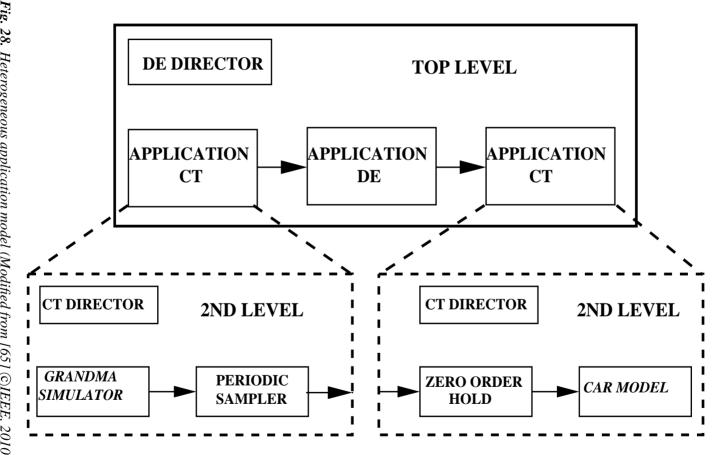

| 18 | Hierarchical heterogeneity (Modified from [65] ©IEEE, 2010)                                                                                             | 59 |

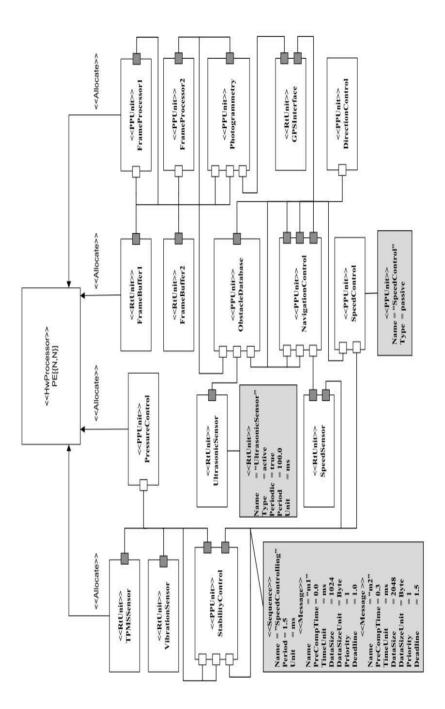

| 19 | Composite structure diagram of the application model (Ex-<br>tended from [64] ©IEEE, 2009)                                                              | 62 |

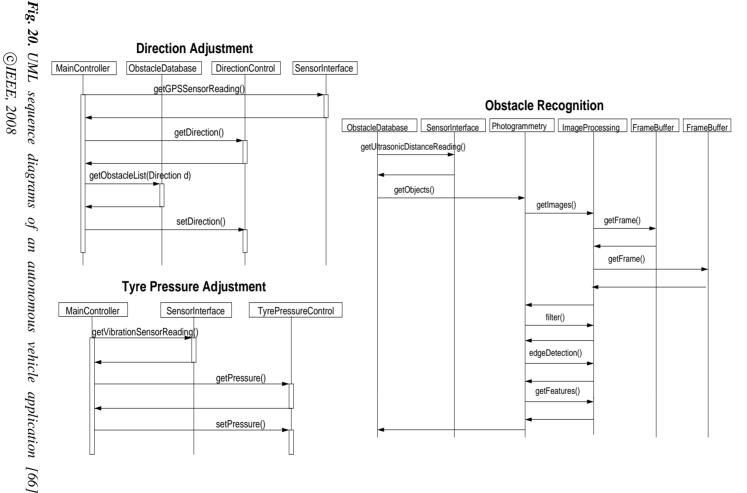

| 20 | UML sequence diagrams of an autonomous vehicle applica-<br>tion [66] ©IEEE, 2008                                                                        | 68 |

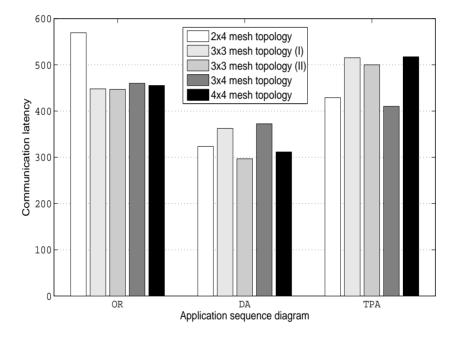

| 21 | Communication latency of the sequence diagrams using dif-<br>ferent network configurations                                                              | 69 |

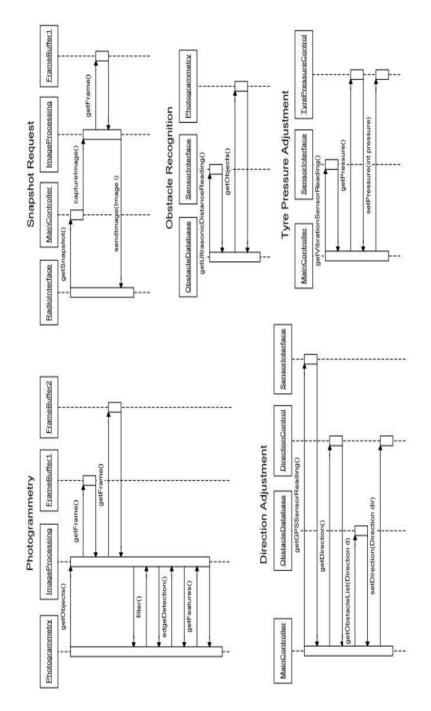

| 22 | UML sequence diagrams of an autonomous vehicle applica-<br>tion [67] ©IGI Global 2010                                                                   | 72 |

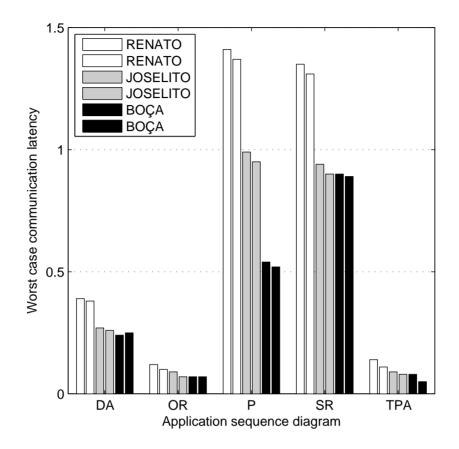

| 23 | Worst case communication latency for each sequence diagram using 2 different random mappings for each NoC model                                         | 75 |

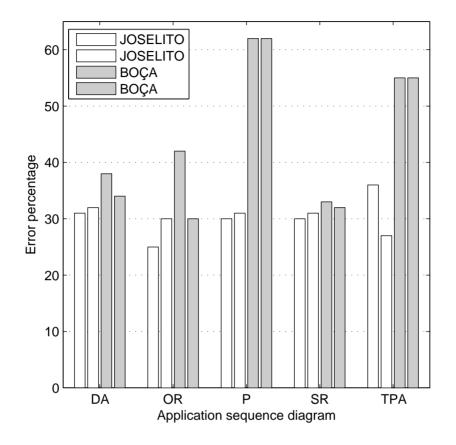

| 24 | Latency error of JOSELITO and BOÇA in comparison with RENATO using two different mappings                                                               | 76 |

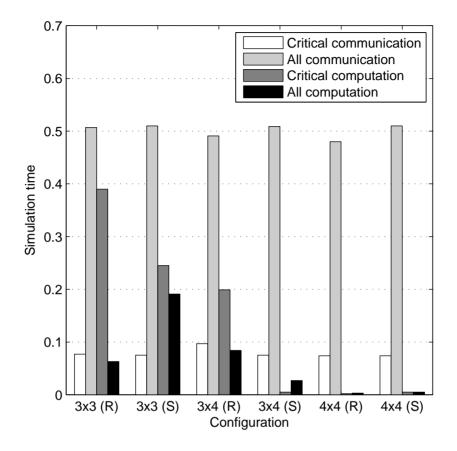

| 25 | Average latency of critical and all communication and com-<br>putation using different platform configurations and random<br>(R) and static (S) mapping | 79 |

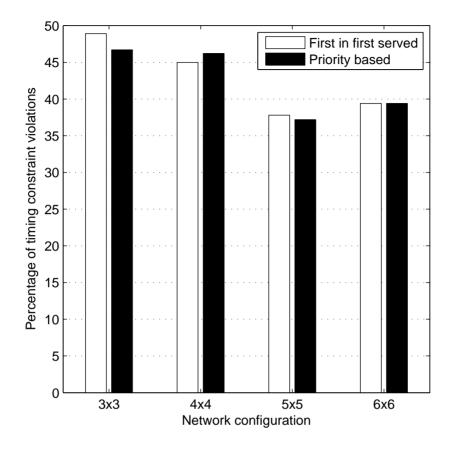

| 26 | Percentage of critical messages violating timing constraints                                                                                            | 83 |

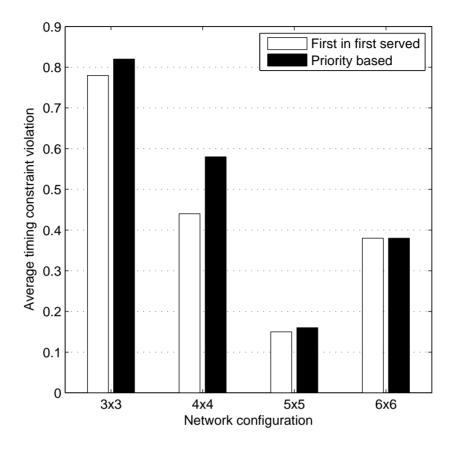

| 27 | Average timing constraint violation in milliseconds                                                                                                     | 84 |

| 28 | Heterogeneous application model (Modified from [65] ©IEEE, 2010)                                                                                        | 85 |

# LIST OF TABLES

| 1 | Stereotypes describing the application and platform elements (Extended and modified from [64] ©IEEE, 2009)                | 61 |

|---|---------------------------------------------------------------------------------------------------------------------------|----|

| 2 | Parameters for the UML sequence diagrams (Extended from [65] ©IEEE, 2010)                                                 | 63 |

| 3 | Communication latency for each sequence diagram of the application model [66] ©IEEE, 2008                                 | 69 |

| 4 | Worst case latencies of each sequence diagram in millisec-<br>onds for mapping 1 (Modified from [67] ©IGI Global, 2010) . | 73 |

| 5 | Worst case latencies of each sequence diagram in millisec-<br>onds for mapping 2 (Modified from [67] ©IGI Global, 2010) . | 73 |

| 6 | Average latency of critical and all communication and com-<br>putation in milliseconds [64] ©IEEE, 2009                   | 78 |

| 7 | Worst case latency for each message for all configurations in milliseconds [64] ©IEEE, 2009                               | 80 |

| 8 | Percentage of messages of each platform configuration vio-<br>lating timing constraints                                   | 81 |

| 9 | Average timing constraint violation of each platform configu-<br>ration in milliseconds                                   | 82 |

## LIST OF ABBREVIATIONS

| AMS     | Analogue and Mixed Signal             |

|---------|---------------------------------------|

| ANSI    | American National Standards Institute |

| CF      | Combined Fragment                     |

| CSP     | Concurrent Sequential Processes       |

| СТ      | Continuous Time                       |

| DE      | Discrete Event                        |

| DSP     | Digital Signal Processor              |

| EDA     | Electronic Design Automation          |

| ESL     | Electronic System Level               |

| FIFO    | First In First Out                    |

| flit    | Flow Control Digit                    |

| ForSyDe | Formal System Design                  |

| FSMD    | Finite State Machine with Datapath    |

| GPS     | Global Positioning System             |

| HDL     | Hardware Description Language         |

| HDTV    | High-Definition Television            |

| HetSC  | Heterogeneous Specifications using SystemC                       |

|--------|------------------------------------------------------------------|

| HW     | Hardware                                                         |

| IP     | Intellectual Property                                            |

| ITRS   | International Technology Roadmap for Semiconductors              |

| JVM    | Java Virtual Machine                                             |

| LUT    | Look-Up Table                                                    |

| MARTE  | Modelling and Analysis of Real-Time and Embedded Systems         |

| MESCAL | Modern Embedded Systems, Compilers, Architectures, and Languages |

| MoC    | Model of Computation                                             |

| MPEG   | Moving Picture Experts Group                                     |

| MPSoC  | Multiprocessor System-on-Chip                                    |

| MSC    | Message Sequence Chart                                           |

| NoC    | Network-on-Chip                                                  |

| PAT    | Payload Abstraction Technique                                    |

| PBD    | Platform Based Design                                            |

| PE     | Processing Element                                               |

| PTRT   | Packet Trailer Release Time                                      |

| RT     | Register Transfer                                                |

| RTE    | Real-Time and Embedded                                           |

| RTL    | Register Transfer Level                                          |

| RSM   | Repetitive Structure Modelling                                   |

|-------|------------------------------------------------------------------|

| SDF   | Synchronous Data Flow                                            |

| SoC   | System-on-Chip                                                   |

| SPT   | Schedulability, Performance and Time                             |

| SW    | Software                                                         |

| SysML | Systems Modelling Language                                       |

| TLM   | Transaction Level Modelling                                      |

| UML   | Unified Modelling Language                                       |

| VHDL  | Very High Speed Integrated Circuit Hardware Description Language |

| VOPD  | Video Object Plain Decoder                                       |

| XML   | Extensible Markup Language                                       |

## 1. INTRODUCTION

Embedded systems, such as consumer electronics, kitchen appliances, mobile phones, medical systems, and traffic control systems, can be found everywhere. Embedded systems are dedicated to perform a certain function. They are often portable devices and targeted to mass production. Most of them also interact continuously with their embedding environment. Thus, they need to be energy efficient, small, low cost, and operate in real-time [25] [69].

The diversity and complexity of applications, increased number of nonfunctional requirements, increased need for integration and networking, increased heterogeneity of products, increased flexibility, and shortened time to market characterise the state-of-the-art embedded systems and set requirements for their design [25].

State-of-the-art embedded systems are complex and heterogeneous, containing for example analogue and digital parts, as well as hardware (HW) and software (SW) [26]. The hardware-driven design flow poorly addresses the dominance of SW in embedded systems [32]. The integration of the HW and SW late in the design flow might lead to a system that does not work at all, does not work as it should, or does not meet its performance requirements. Therefore, it is important to model the whole system already early at the design process in order to validate its correct functionality and explore the design space in order to make necessary trade-offs for instance in terms of area, speed, and power consumption.

System complexity can be addressed by raising the level of abstraction above the Register Transfer Level (RTL) [50]. Higher levels of abstraction are usually closer to human way of reasoning. For instance, it is very difficult to catch the system functionality when it is described as a schematic or by a Hardware Description Language (HDL). Furthermore, system level methodologies narrow the gap between application and hardware designers, since the application designer can validate the whole embedded system without detailed knowledge about system manufacturing [29].

The increasing complexity of embedded systems cannot lead to increasing design costs. The design cannot be based on for instance repetitive proto-typing, since it is expensive and time consuming. More systematic and well-defined approaches are necessary in order to make systems meet their requirements [25].

### 1.1 Objective and Scope of Research

This thesis presents an approach for modelling and validating embedded applications together with on-chip multiprocessing platforms. This approach relies on executable specifications; however, without excluding (semi) formal description of the application. Even if the main focus is on embedded systems, the application modelling approach does not exclude general purpose applications.

The novelty of this approach is it being fully model-based using actor orientation and executable Unified Modelling Language (UML) sequence diagrams. Moreover, neither code generation nor HW emulation is required when simulating applications on a multiprocessing Network-on-Chip (NoC) platform.

The scope of the thesis is modelling at high levels of abstraction (that is, system level). Thus, this thesis considers neither the HW/SW division nor the process of system refinement into lower levels of abstraction. SW means exclusively application SW, operating systems or middleware are not addressed.

To summarize, the main contributions of this thesis are the following:

• An approach for joint modelling and validation of application and platform models using UML sequence diagrams, actor orientation, Java, and the Ptolemy II framework

- Implementation of a mapping between the application and platform models

- Implementation of Processing Elements (PEs) to be connected to the NoC switches

- Design space exploration of application models mapped on different platform models and configurations

- Describing the application model using the UML profile for Modelling and Analysis of Real-Time and Embedded Systems (MARTE) and defining a few necessary extension to the MARTE profile

- Describing the platform model using the MARTE profile and its Repetitive Structure Modelling (RSM) notation

## 1.2 Thesis Outline

This thesis is a monograph, which contains some unpublished material, but is mainly based on the author's publications [64], [65], [66], and [67]. Publications [47], [83], and [84] are directly complementary, whereas publication [85] is used as a reference only.

This thesis can be divided in three parts: background theory (Chapters 2-3), closely related previous work not carried out by the author (Chapters 4 and 5), and the actual contribution of this thesis (Chapters 6-7).

Chapter 2 gives an overview of the concepts and terminology the author considered relevant for the rest of this thesis. Chapter 2 first presents different abstraction levels. Then, it introduces the terminology and concepts of system design and modelling, design space exploration, heterogeneity, and Models-of-Computation (MoCs). Moreover, Chapter 2 discusses the effect of the accuracy of a simulatable model on the simulation speed. Finally, Chapter 2 presents a few system level design and modelling languages, from which UML is discussed in more detail, since it is relevant for the rest of this thesis.

Chapter 3 gives first an overview of a few system level modelling frameworks and approaches. The emphasis of Chapter 3 is on academic approaches that are freely available. Chapter 3 then presents the Ptolemy II framework, within which the application modelling approach presented in this thesis is implemented.

One of the contributions of this thesis is the joint validation of application and platform models. Therefore, Chapter 4 presents the models of NoC interconnects used as a part of the platform models (the PEs are presented in Chapter 6). Chapter 4 presents first the reference interconnect, HERMES, since the more abstract models are based on it. Then, Chapter 4 presents three models of NoC interconnects, RENATO, JOSELITO, and BOÇA that are all implemented on system level yet still presenting different level of accuracy. The work presented in this Chapter is not carried out by the author.

Chapter 5 describes the previous work on creating executable application models using UML sequence diagrams within the Ptolemy II framework. The work presented in this Chapter is not carried out by the author.

Chapter 6 describes the contribution of this thesis and explains the application modelling approach for on-chip multiprocessing platforms.

Chapter 7 presents a few case studies in which the application modelling approach is demonstrated. Finally, Chapter 8 draws conclusions and presents some future work.

## 2. RISING ABOVE RTL: SYSTEM DESCRIPTION AT HIGHER LEVELS OF ABSTRACTION

According to the International Technology Roadmap for Semiconductors (IT-RS) the cost effective and reliable design of such a complex system on a single chip that is possible with the current technology would need a fifty-fold increase in design productivity. Hence, the specification, design, verification, and design space exploration of complex systems require a level of abstraction that is above the RTL [50].

Despite the clear need for system level design, neither industry nor academia has been able to sufficiently formalise a system level design technology or methodology [29]. In fact, the term system level does not even have a clear or unified definition [91] [96]. Usually system level is described to be a level above RTL including both HW and SW [50] [96].

### 2.1 Levels of Abstraction

As the definition of the term system level is not unified, neither is the terminology describing the rest of the abstraction levels: Rabaey et al. divide the abstraction levels in digital circuit design from the lowest level to the highest in device, circuit, gate, functional module, and system levels [93], whereas Gajski et al. call them circuit, logic, processor, and system levels [29]. At the device level, the basic component of the models is a transistor, whereas circuit level components are standard cells consisting of them. Further, at the gate level (or logic level according to Gajski et al. [29]), components are logic gates and flip-flops building register transfer components. At the functional module level (or processor level) systems are described using components such as adders that compose bigger systems (such as processors) that are used at the system level [29] [93].

RTL is a low level of abstraction and is usually associated with HDLs, such as Very High Speed Integrated Circuit Hardware Description Language (VHDL) or Verilog [34]. At the Register Transfer (RT) level, a design has clocked behaviour described in terms of data transfers between storage elements (such as registers) [40].

Transaction Level and Electronic System Level (ESL) are not exactly levels of abstraction, even though both of them are placed in a level above RTL [34] [59] [99]. Transaction Level Modelling (TLM) is a high level modelling style that enables the separation between the implementation of the communication functionality and the functional units that use the communication functions. Especially SystemC [41] advocates the use of TLM, in which the communication functionality is modelled as channels and the SystemC modules can request a transaction by calling the interface functions of other modules [34].

ESL is an intermediate design phase above RTL (or rather a new "buzzword" in the Electronic Design Automation (EDA) industry). The raise of the abstraction level has been a trend during the past few years; therefore, the EDA industry has had room for a new definition [59] [99]. ITRS defines ESL to be a level above RTL that consists of behavioural and architectural levels. At the behavioural level the system functions have not yet been partitioned into SW and HW, whereas at the architectural level this partitioning has been already done [49].

## 2.2 System Design and Modelling

Benini and de Micheli define a system to be a collection of components providing a useful service when operating together [9]. System design is the process of refining a functional specification of a system into the final system implementation [91]. However, the gap between the system specification and implementation is too large to be closed in a single step. Thus, closing the gap requires a successive stepwise refinement of system models [29].

A model is a simplification of reality. Building models helps us to better visualise and understand the system we are designing. Especially complex systems cannot easily be comprehended without an abstract model of them [10]. An abstract model is a source of nondeterministic behaviour and the implementation process makes it a deterministic system [56]. Hence, according to Selic, the main purpose of models is to understand the aspects of a complex system before constructing it [98]. Systems models can be created many ways, most of the ways being ad hoc. However, without modelling it is likely to either build a malfunctioning system or fail building it at all [10].

Modelling is an accepted engineering technique [10]. It is the process of creating or generating models. According to ITRS, modelling aims at supporting technology development and optimisation as well as reducing development time and costs [51]. Modelling also enables the analysis of existing systems, for instance when it is too impractical to experiment with the actual system [98].

Models have a central role in model-based design, model-integrated engineering [100], and model-driven architecture [75]. All of them depict the same idea using models; how it is called depends on the user. For instance, the Mathworks has adopted the concept of model-based design, in which a system model is used as an executable specification throughout the development process [70]. Furthermore, according to Sztipanovits and Karsai, model-integrated engineering uses models as a backbone for the development of computer-based systems. Though, they claim that model-integrated computing uses models in a more general sense than model-based design. In model-integrated computing models do not only capture for instance the SW architecture but also its environment [100]. The Object Management Group's (OMG) model-driven architecture is targeted mostly to SW domain, since it considers a platform-independent model to be a base of the application development [75]. Regardless of how the use of models is called, usually a single model is not sufficient for the whole system design process. Hence, we need different models at different levels of abstraction [29] [91]. A model serves as a specification of the desired functionality to be implemented in the next lower level of abstraction and as a description for the validation of the design decisions through simulation or analysis [29].

## 2.3 Design Space Exploration

The early stages of any system design process can be characterised by incompleteness and exploration. Therefore, system level design deals with incomplete and inconsistent information and the evaluation of different design decisions based on it [91].

Plantin and Stoy emphasise the importance of models to capture the existing knowledge of the system, even if the knowledge is incomplete. The incomplete system level models are the base of making trade-offs between available system solutions [91]. The process of finding out the trade-offs by testing different solutions and optimising the design under a set of constraints is called design space exploration [29]. Hence, the purpose of system design is to realise a desired functionality while satisfying design constraints that delimit the design space and making trade-offs between system performance versus costs [9].

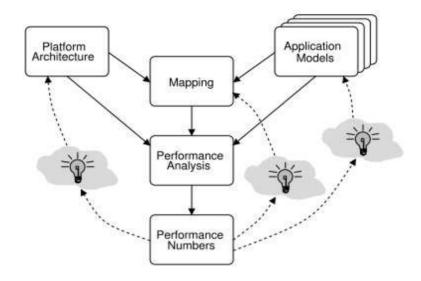

The Y-chart method, depicted in Figure 1 emphasises the separation of architecture and application models, which facilitates the design space exploration. Different methods can be used for designing and refining the application models and platform architecture separately until the mapping of the application models onto different architectures for performance evaluation [58] [63].

Design space exploration is easier and faster at the system level than at the lower levels of abstraction. Too detailed simulation, such as cycle accurate simulation, is not very suitable for design space exploration of for instance state-of-the-art embedded systems. As their design space is large, simulators

Fig. 1. Y-chart [63] ©IEEE, 1999

get too complicated and are too slow [90]. Even though at the system level designers need to trade-off between the simulation speed and accuracy, it is not always necessary to sacrifice accuracy for speed, as shown for instance in [43].

### 2.4 Model Accuracy versus Simulation Speed

Modelling systems at the higher levels of abstraction reduces the number of objects designers need to consider by an order of magnitude [29]. Moreover, at the system level, designers can exploit all the freedom without making any design decisions, such as the HW/SW partitioning [56]. However, when using higher level models, designers need to trade-off between the simulation speed and accuracy.

Ideally, the designers should start the system design process by using fast but not very accurate system models, and stepwise refine the models towards more accurate ones at the expense of the simulation speed. However, very often the RTL model exists before the more abstract models. Nevertheless, this enables the back-annotation of for instance timing information to the more

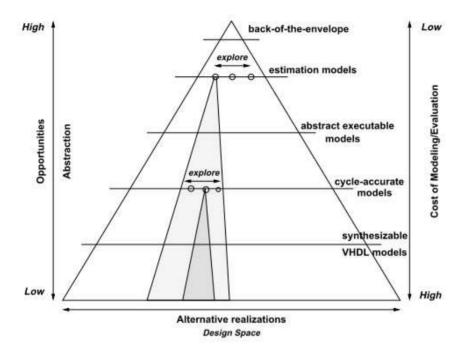

Fig. 2. The abstraction pyramid depicts the trade-off between the modelling effort and level of detail [57] ©A.C.J. Kienhuis, 1999

abstract models making them also more accurate.

Figure 2 depicts the abstraction pyramid. The bottom of the pyramid presents the whole design space, whereas the top of the pyramid is the designer's original idea about the system. The abstraction pyramid addresses various modelling issues: cost of modelling and evaluation, opportunity to change, level of detail, and accuracy. On top of the pyramid, system models are very abstract, meaning that their level of detail is low. However, the possibility to explore various design choices is high, because the more detailed the system description is, the more difficult and costly it is to change it [57].

When refining the system model towards the bottom of the abstraction pyramid, the modelling and evaluation costs increase: the number of different design choices increases making the system simulation and design space exploration more time consuming [57].

### 2.5 Heterogeneity and Models-of-Computation

State-of-the-art embedded systems are often heterogeneous containing for instance analogue, digital, and mixed-signal parts as well as hardware and software [20] [33]. The various domains of heterogeneous systems require modelling and design using different MoCs.

According to Keutzer et al. a MoC refers to a mathematical model that describes the system behaviour in terms of specifying the semantics of computation and concurrency [56]. The definition of a MoC has been often refined to apply for instance to the context it is used in: For example, Eker et al. define a MoC to be a framework that specifies the interaction of components in a subsystem covering both the flow of data and the flow of control between them [26], whereas Jantsch and Sander describe a MoC to represent time and the semantics of communication and synchronisation between processes in a process network [54].

Even though MoCs have been described in detail [53], compared [62], and categorized [24], it is difficult to model or implement a system using various MoCs. However, it is beneficial to choose the right MoC and to understand the impact of different MoCs on the design and implementation choices [53]. MoCs provide the designers with useful properties, such as determinism and deadlock protection [54]. Therefore, choosing a MoC has a significant impact on the quality of the system design [13]. Moreover, an appropriate MoC speeds up the simulation of the system since only the issues relevant to that particular MoC need to be simulated [54].

MoCs can be either timed or untimed. Timed MoCs (such as Discrete Event (DE) or Continuous Time (CT)) have temporally ordered events, whereas untimed MoCs (such as Synchronous Data Flow (SDF)) have only partially ordered events [15] [24] [59].

The DE MoC is often used in HDL simulators, synchronous languages, and in general in all time oriented models of systems (such as communication networks or digital hardware). The CT MoC is suitable for systems requiring continuous time, such as analogue circuits, mechanical systems, or embedded systems interacting with continuous environments. The CT MoC supports continuous time mixed-signal modelling because a model in the CT domain can include both continuous signals and discrete events. The SDF MoC suits for modelling simple dataflow systems without complicated flow of control, such as signal processing systems. The execution order of actors in the SDF domain (and the number of produced and consumed data samples of each actor) is statically determined prior to execution. This results in minimal execution overhead, bounded memory use, and the occurrence of no deadlocks [15].

The modelling languages and frameworks need to support system modelling and design using multiple MoCs. Whereas SpecC supports various MoCs (such as Concurrent Sequential Processes (CSP), Finite State Machine with Datapath (FSMD), and DE) [30], the SystemC standard simulation kernel supports only the simulation of DE models [41]. This poorly addresses the heterogeneity of the state-of-the art embedded systems.

Heterogeneous specifications in SystemC (HetSC) [36], Analogue and Mixed-Signal extensions to SystemC (SystemC-AMS) [102], SysteMoC [27], and SystemC kernel extensions [86] [87] enable the simulation of hybrid and mixed-signal SystemC models. The latter approach modifies the SystemC kernel directly, whereas HetSC, SystemC-AMS, and SysteMoC are built on top of SystemC. Also Verilog-AMS [2] and VHDL-AMS [39] enable the analogue and mixed-signal description and simulation.

Besides languages, also some frameworks, such as the Formal System Design (ForSyDe) [94] or Ptolemy II [26] (described in more detail in Chapter 3) enable heterogeneous system modelling using multiple MoCs.

## 2.6 System (Level) Design Languages

System design languages need to capture not only the behaviour of the HW but also to enable the description of the system SW [34] [96]. Sangiovanni-Vincentelli points out that the current industrial approaches of system level de-

sign address either HW or SW but not both. HW approaches, such as VHDL or Verilog, have poor or no support for SW, whereas SW languages, such as C or C++ are not able to describe concurrency and time [96].

C and C++ are popular among SW engineers for creating executable specifications. However, although they execute fast, they lack the notion of concurrency and time, which are supported by for instance the American National Standards Institute (ANSI) C based SpecC [30] or C++ based SystemC [41]. One of the main goals of the development of SystemC was to enable system level modelling of systems that include both HW and SW [34]. SpecC is a system level design language that facilitates the specification and design of digital embedded systems containing both HW and SW [22] [30].

HDL based system level languages, such as System Verilog [42], preserve all the features of the underlying language [42], but might be hard to use by SW engineers [96]. For instance, System Verilog is built on top of the Verilog 2001 standard [42]. While preserving all the Verilog features it also supports system level and object oriented modelling as well as the specification, design, and verification of HW [1] [42]. However, it does not enable the modelling of system SW.

The proportion and complexity of SW in embedded systems have increased in recent years [16]. This increasing dominance of SW in embedded systems needs to be addressed with other methods than using traditional HDLs. One potential approach is UML [68].

### 2.7 UML

UML is a standardised modelling language for visualising, specifying, constructing, and documenting especially software intensive systems. Hence, one of the ideas behind the development of UML was to bring some stability to the object oriented marketplace in forms of a unified and mature modelling language and tools [10].

Fig. 3. UML extension mechanisms: stereotypes, constraints, and tagged values

UML can be applied to various types of systems, domains, methods, or processes [4]. The growing interest of the embedded systems and real-time communities in UML, UML's extension mechanisms, and support for object orientation among others are considered the strengths of the language. The shortcomings, such as the lack of platform models or mapping methodology [68], are later addressed for instance by the MARTE profile [78].

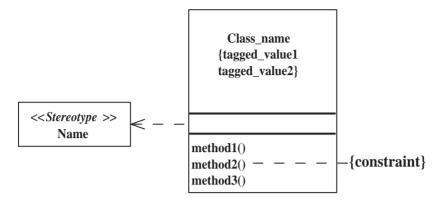

#### 2.7.1 UML Profiles

A metamodel defines UML syntax and semantics. UML can be extended by defining new metaclasses, extending the existing metaclasses, or defining new constraints or more precise semantics. UML extension mechanisms (that do not alter the UML metamodel) are stereotypes, constraints, and tagged values [10] [80], whose syntax is shown in Figure 3.

Stereotypes extend the vocabulary of UML and allow the creation of new building blocks. Furthermore, constraints extend the semantics of UML building blocks and enable the definition of new rules, whereas tagged values extend the properties of UML building blocks. The extensions can be arranged as profiles. A profile is a set of stereotypes, constraints, and tagged values that customise UML to a specific domain [10] [80].

Sangiovanni-Vincentelli points out that UML profiling can be considered ei-

ther a strength or a weakness of the language. The over 300 existing UML profiles will for sure customise UML for various needs while they most likely also overlap [96]. Well known UML profiles include the Systems Modelling Language (SysML) [76], a profile for Schedulability, Performance and Time (SPT) [79], and the MARTE profile [78].

The UML profile for MARTE customises UML for model-driven development of real-time and embedded systems [78]. Already MARTE's predecessor, the SPT profile extended UML with periodic tasks, schedulable objects, timing, and concurrency aspects [79].

The MARTE profile supports the specification, design, and validation stages of embedded system design. MARTE extends UML to provide constructs for modelling Real-Time and Embedded (RTE) SW applications, high-level RTE HW, and their non-functional properties. Moreover, MARTE provides designers with necessary extension units in order to address performance and schedulability analysis of RTE systems [78].

The MARTE profile is organised into a set of packages, such as foundations, design model, and analysis model. The foundation package contains basic elements for modelling non-functional properties, timing, and general resources. Moreover, an allocation concept associates application functions with the execution platform resources. The design model package includes elements for modelling generic components, software and hardware components, and the application. Finally, the analysis package contains modelling capabilities for scheduling and performance analysis and enables designers to perform for instance timing analysis directly from the UML description instead of building a separate model for analysis [78].

Several approaches use the UML extensibility through profiles in order to customise UML for embedded system design. For example, Kukkala et al. introduce a UML 2.0 profile for embedded system design [60], whereas Arpinen et al. explore the embedded SW platform modelling using that profile [5]. Moreover, Brisolara et al. show the benefit of using the MARTE profile when defining the same system with and without the profile [12]. Boulet et al. and Cuccuru et al. demonstrate the expressiveness of the MARTE profile's notation for describing repetitive structures [11] [17].

#### 2.7.2 Repetitive Structure Modelling using MARTE

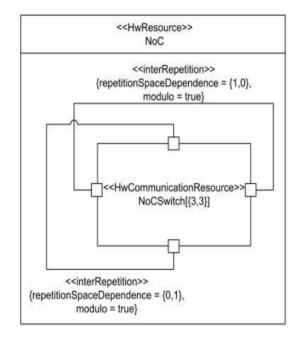

The MARTE profile has also high level modelling constructs to describe (parallel) data computations using several computation units. The RSM notation provides a compact way to depict the regularity of such repetitions of structural elements connected via a regular connection pattern [17] [78].

The RSM notation extends the UML multiplicity concept in order to enable to specify a shape of the repetitive structure elements. The RSM modelling aspects can be used to model HW platforms, applications, and the allocation of the application onto the HW platform [17] [78].

Figure 4 illustrates a 3x3 torus network using the RSM notation. The  $\langle Hw$ -*CommunicationResource* $\rangle$  stereotype (which inherits from the  $\langle HwRe$ *source* $\rangle$  stereotype) describes NoC switches. The repetitionSpaceDependence attribute defines the relative position of an adjacent instance for each element (a vector {1,0} means that the adjacent instance is one hop along the x-axis and zero hops along the y-axis, while {0,1} is zero hops along the xaxis and one hop along the y-axis). The modulo attribute describes whether the topology is cyclic (modulo is true) or not (modulo is false). In the case depicted in Figure 4, a true modulo value means a torus topology, whereas a false modulo value would mean a mesh topology.

RSM is necessary for describing massive regular parallelism: it makes the model more compact, readable, and maintainable. However, it only handles regular topologies [17].

#### 2.7.3 UML Diagrams

The earlier version of UML, UML 1.1, included nine different diagrams: class, object, component, and deployment diagrams depict the system struc-

Fig. 4. A 3x3 torus topology described using the RSM notation

ture while use case, activity, statechart, sequence, and collaboration diagrams depict the system behaviour [10]. Later, in UML 2.0 the number of diagrams has increased to thirteen: composite structure and package diagrams are the additional structural diagrams, whereas timing and interaction overview diagrams are behavioural. Also the collaboration diagram is nowadays called communication diagram and the statechart diagram state machine diagram. Moreover, some of the behavioural diagrams (sequence, communication, timing, and interaction overview diagrams) are subcategorised into interaction diagrams [77]. The sequence diagram is described next in more detail, since it is used to create the executable application models as explained in Chapters 5 and 6.

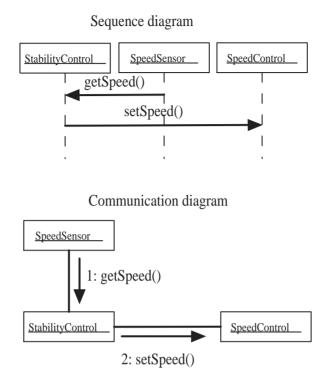

UML sequence diagram is an interaction diagram and depicts the time ordering of messages. Booch defines an interaction to be a behaviour that consists of a set of messages exchanged among a set of objects. Moreover, a message specifies a communication between the objects [10]. Figure 5 illustrates a

Fig. 5. UML sequence diagram and the corresponding communication diagram

sequence diagram that has three lifelines and two messages. In the sequence diagram, each object has a lifeline that describes its existence over a period of time. The messages represent the communication between the objects.

Some of the UML diagrams are almost overlapping, as can be seen from Figure 5. The lower part of Figure 5 depicts the corresponding communication diagram. While the sequence diagram emphasises the temporal ordering of messages, the communication diagram emphasises the structural organisation of objects. These two diagrams are semantically equivalent [10]: as can be seen from Figure 5 both diagrams contain the same objects and messages, and no information is lost when converting one to the other.

A sequence diagram is one variant of Message Sequence Charts (MSCs). MSCs are a visual formalism used to capture system requirements during the early design stages. MSCs specify scenarios that describe interaction patterns between processes or objects [35]. However, as much as the visual notation of UML is expressive and the diagrams have underlying formalism, the UML diagrams can be misinterpreted. For instance Graaf et al. have noticed that in many companies UML is used for drawing instead of modelling and the interpretation of the drawings (not always being syntactically correct or consistent) might get obscured [32]. Therefore, executable models are necessary.

## 3. PTOLEMY II: A SOFTWARE FRAMEWORK FOR ACTOR ORIENTED EXPERIMENTING

System design at various levels of abstraction requires support from design automation tools, but they are hardly mature enough for system level design [50]. Moreover, system level design tools lack universal applicability [53] and instead of creating a unified flow from the system level specification to the implementation, they are merely a bunch of unlinked tools requiring informal techniques and human intervention during the design flow [8].

Several methods and frameworks exist for embedded system design. Platform Based Design (PBD) aims at reducing system design costs by reusing applications and architectures [28] [56]. The ForSyDe framework aims at heterogeneous system modelling using multiple MoCs and the development of transformational design refinement methodology for embedded systems and Systems-on-Chip (SoCs) [94] [95].

Polis is an approach for the design and verification of control dominated reactive systems. Polis is a full design methodology and a design framework for HW/SW co-design of embedded system [7]. Metropolis continues the work done within Polis. Metropolis is a design environment for heterogeneous systems designed to support PBD [8] [96] [101]. The goal of the development of Metropolis has been to obtain a unified environment for unambiguous system presentation at various levels of abstraction [101].

MILAN is a model-based simulation framework facilitating the design and optimisation of embedded systems [6]. The Modern Embedded Systems, Compilers, Architectures, and Languages (MESCAL) project aims at creating a disciplined approach to produce reusable architectural platforms [72].

Artemis and SESAME are frameworks aiming at efficient design space exploration of heterogeneous embedded systems architectures at multiple abstraction levels [89] [90]. The Ptolemy II framework [21] [26] is presented next in further detail.

### 3.1 The Ptolemy Project

The Ptolemy project of the University of California at Berkeley aims at modelling, simulating, and designing of concurrent, real-time embedded systems [21]. The first outcome of the project was the Gabriel software for signal processing at 1986. Gabriel included a code generator to produce efficient assembly code for Digital Signal Processors (DSPs) as well as a HW/SW co-simulator. Early 1990s, the project announced Ptolemy Classic, which is a modelling environment supporting multiple MoCs. At 1996 the project started working on the Ptolemy II software framework [13].

Although the Ptolemy II framework used some of Ptolemy Classic's capabilities, it also introduced several new features: data and domain polymorphism, new MoCs, a new visual editor (called Vergil), actor oriented classes and subclasses, and the use of the Extensible Markup Language (XML) for representing models [13].

Whereas Gabriel was implemented in Lisp and Ptolemy Classic in C++, the Ptolemy II's implementation language was changed to Java due to its capability to for instance built-in threading and building user interfaces. Even though Java has several advantages, which is why it was chosen to implement the Ptolemy II framework in the first place [13], the fact that it runs over the Java Virtual Machine (JVM) is also one of its biggest shortcomings. The simulation of Ptolemy II models may be slow in some cases and also dependent on the size of the Java heap space.

One of the aim of the Ptolemy project is to create an environment for actor oriented experimenting [21].

#### 3.2 Actor Orientation and Hierarchical Heterogeneity

An actor is a component that communicates with its environment by sending and receiving data tokens (that encapsulate messages) via ports using channels [13] [61]. The actor model derives from the mathematical model of concurrent computation [37] and later from the formal models of concurrency [3].

The development of actors is influenced by the concept of objects in the Simula language [3]. Agha defines that each actor has an independent thread of control and the actors communicate via asynchronous message passing [3].

Actor orientation is the theoretical foundation behind the Ptolemy II framework. Thus, Lee at al. have further refined the concept of actor orientation: Even though the actors are still parallel, they can share the thread of control and the message passing does not necessarily need to be asynchronous. Moreover, each actor can run in its own thread or the whole system can run sequentially in a single thread [61].

Ptolemy II actors belong to a domain, which defines both a receiver and a director. The receiver implements the communication of data tokens and can be either a QueueReceiver (containing a First In First Out (FIFO) queue) or a Mailbox (a FIFO with a capacity of one). The director is an object that defines the interaction semantics of components. Thus, a director controls the communication and execution of actors in the domain defining when the actors communicate and update their internal state (thus following the rules defined by a MoC) [13] [14] [26].

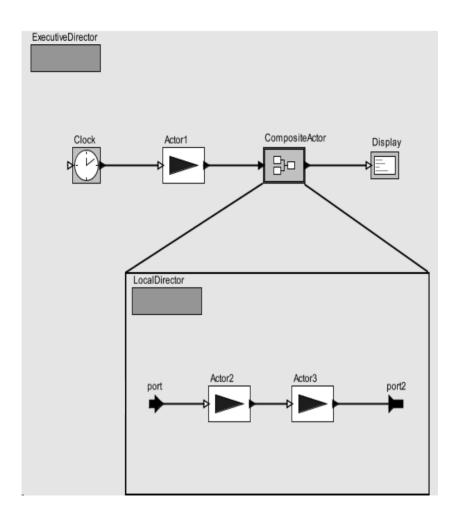

Ptolemy II actors can be either atomic or a composition of other actors (called composite actors). Atomic actors are primitive and cannot contain other actors. Composite actors contain other composite actors, atomic actors, or both. Opaque composite actors have a local director, whereas transparent composite actors do not and their execution follows the rules of the executive director [13] [26]. Figure 6 depicts executive and local directors as well as a composite actor and atomic actors (Actor1, Actor2, and Actor3).

Lee et al. consider the most important advantage of actor orientation to be

Fig. 6. Vergil workspace showing composite and atomic actors and executive and local directors

the use of MoCs in the actor interaction [61]. A MoC defines the details of scheduling and communication and how the actors are related if they are related. The actors themselves do not do that, unlike objects in object oriented design. This increases reusability and the model can be easier analysed and understood [26]. The use of MoCs in actor interaction is necessary in order to comprehend the heterogeneity of the state-of-the-art embedded systems.

The Ptolemy II framework, as targeted at the design of heterogeneous embedded systems, enables the integration of various MoCs by using hierarchical heterogeneity. That is, the composite actors can encapsulate subsystems, whose components' interaction a MoC controls, as seen in Figure 6. Furthermore, the MoC also turns the subsystem into a component that can be used in other systems. This hierarchical heterogeneity enables the analysis and modification of subsystems without affecting the overall systems [26].

### 3.3 Advantages of the Ptolemy II Framework

Various Ptolemy II frameworks characteristics have been useful for the application modelling approach presented in this thesis:

- The Ptolemy II framework is open source and can be modified and extended. For instance, as described in further detail in Chapter 5, the visual editor has been extended with a UML editor, in which UML sequence diagrams can be drawn.

- The Ptolemy II framework defines a large, domain polymorphic component library from which components can be selected to the workspace of the visual editor.

- The Ptolemy II framework enables the definition of more components. For instance, the Ptolemy II composite actor has been modified in order to enable it to encapsulate a UML sequence diagram.

- One of the objectives of the Ptolemy II is to enable modelling using different MoCs. Various directors supporting different MoCs can be selected from the component library and the implementation of new ones is ongoing work.

- The Ptolemy II framework enables the creation of new directors. For instance, the implementation of two additional directors was necessary in order to define total and partial order execution semantics for the UML sequence diagrams.

- One of the Ptolemy II framework's advantage over other system level design methods and tools is the visual editor, called Vergil. Vergil and the component library make the building of models fast and quite effortless.

- Using the Ptolemy II framework, both application and platform models can be described and simulated in the same model using the visual editor.

- Ptolemy II can also be set up with Eclipse software development environment [23] making the programming of user defined components convenient.

## 4. MORE AND LESS ABSTRACT MODELS OF NETWORK-ON-CHIP INTERCONNECTS

A platform has various definitions depending on the domain of application [96]. In the context of PBD, a platform is an abstraction that covers several possible lower level refinements [97] or a library of both computational and communication components that can be composed to a design at a certain level of abstraction. The selected parameterised components form a platform instance [96]. Jantsch and Tenhunen define a NoC platform to include not only the communication infrastructure, but also middleware and operating system communication services, and a design methodology and tools to map applications onto a NoC platform [55].

Traditional von Neumann uniprocessor architectures will not meet the power, performance, and cost requirements of the state-of-the art and future systems [56] [81]. Thus, multiprocessor systems are needed in order to increase the performance without increasing the power consumption of a processor [81]. When programming multiprocessing system, we try to exploit parallelism in order to achieve increased performance. The increase in parallelism causes also increasing communication overhead [88]. Therefore, the interconnection network has a central role in state-of-the-art multiprocessing systems.

The design and verification of the inter-task communication of applications is hard if the interconnect is a bus based system due to the unpredictability of the communication performance [55]. Even though on-chip buses are cost efficient and have high performance, they do not scale when the number of communicating components increases. This makes their behaviour unpredictable. The concept of a NoC replaces ad hoc wiring with a more structured approach and increases predictability [18] [55].

In this thesis, a platform denotes a NoC based multiprocessing platform that consists of one of the models of a NoC interconnect described in the next subsections and Processing Elements (PEs) connected to local ports of the NoC switches.

The rest of this Chapter describes first a RT level reference model of a NoC infrastructure called HERMES and then three different system level models based on it. The modelling and implementation of the NoC interconnects are not carried out by the author and are therefore not a contribution of the thesis. The models of the NoC interconnects are presented here, because the system level models RENATO, JOSELITO, and BOÇA are used as the platform interconnects in the case studies described in more detail in sections 7.1 - 7.5.

### 4.1 HERMES: The RTL Reference Model

HERMES is an infrastructure for low area overhead packet-switching NoC. A switch is the basic element of the network and can be connected to four other switches and to a local Intellectual Property (IP) core implementing especially 2D mesh topologies [74].

Each HERMES switch contains routing control logic and five bi-directional input ports that establish the connection to four adjacent switches and to the local core. Each port uses input buffering for incoming packets. The arbitration logic gives a priority to the port, which has been granted routing longest time ago. The routing control logic implements the routing strategy, arbitration logic, and a packet switching algorithm with wormhole switching mode [74].

The routing strategy chosen for HERMES is XY routing [74]. In the XY routing flow control digits (flits) are first routed in the X direction until the right X-coordinate is found and then in the Y direction until the right Y-coordinate is found. HERMES switches use wormhole switching because it allows efficient use of buffers, resulting in less buffer space needed than for instance in cut-through switching. Moreover, wormhole switching is able to multiplex a physical channel into more than one logical channel [19]. However, in HERMES switches, only one logical channel is used of one physical channel in order to reduce the switch complexity and cost [74]. In wormhole switching, packets are divided into entities called flits [19].

The flit size in HERMES can be parameterised, but the number of flits in a packet is fixed to be  $2^{flit \ size \ in \ bits}$ . The first and second flits of the packet form the header and contain the address of the target switch of the packet and the size of the payload in flits respectively. The payload is carried by the rest of the flits, which do not contain any routing information. Therefore, the payload flits must follow the same path as the header flits. Each switch has a unique address expressed as X and Y coordinates corresponding the horizontal and vertical position of the switch in the network. This representation facilitates the XY routing of the packet [74].

HERMES aims at small design size and a NoC switch with low latency. The HERMES switch is described in VHDL and prototyped on FPGA Virtex II. A NoC configuration having a fixed flit size of 10 bits (2 bits for control and 8 bits data), buffer size 8, and 5x5 mesh topology has 500 Mbits per second peak performance at 25 MHz operation frequency. With this configuration, the switch area is 555 Look-Up Tables (LUTs) [74].

## 4.2 RENATO: Modelling the HERMES Switch Using UML Interactions

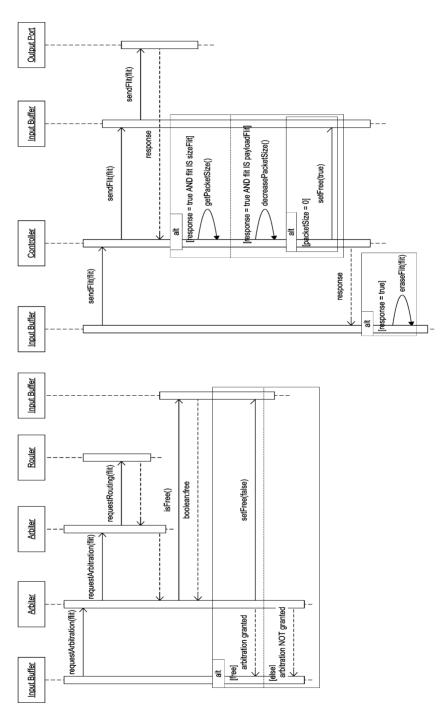

RENATO is an actor oriented system-level NoC model written in Java within the Ptolemy II framework. RENATO is based on the UML interactions that describe the functionality of the HERMES switch [46]. The interactions are illustrated as UML sequence diagrams in Figure 7. These interactions only visualise the RENATO model's behaviour and are not associated with the executable UML sequence diagrams for the application modelling explained in Chapters 5 and 6.

The leftmost sequence diagram in Figure 7 describes an arbitration request of an input buffer in a switch. An input buffer requests arbitration if it has received a packet. The buffer sends the packet's header flit to the router controller and waits for a response (denoted by a synchronous message in the sequence diagram). The controller requests arbitration from the arbiter for the packet the header flit belongs to [46].

The arbiter handles all incoming requests and grants arbitration to one of the buffers requesting it according to an arbitration scheme, such as round robin. If the arbitration is granted, the arbiter sends the flit to the router that determines which of the 5 output ports the flit should be sent to. After the routing is done, the router controller verifies that the chosen output port is free. If it is free, the input buffer can establish the connection to the output port and send the flit, otherwise the connection is refused and the input buffer has to request for arbitration again [46].

The rightmost sequence diagram in Figure 7 describes the transmission of a flit between two adjacent routers. The controller receives the flit from the local input buffer and determines to which output port it belongs to. After sending the flit to the correct output port, the controller waits for an acknowledgement. After a positive acknowledgement, the controller removes the flit from the source router's input buffer, whereas a negative acknowledgement causes resending of the flit [46]. Since there is only one condition in the last two interactions of the rightmost sequence diagram, the alt combined fragments could also be replaced with opt combined fragments.

Originally, RENATO was untimed. In order to increase its accuracy, timing information extracted from the cycle accurate HERMES model was annotated to RENATO's interactions. The simulation results of RENATO have been compared to the results of HERMES using various traffic scenarios and NoC configurations. For a long lasting traffic, the error is up to 10 per cent. This can be considered as a good result since the actor oriented model is based on

Fig. 7. RENATO's UML interactions [46] ©IEEE, 2008

only the interactions and works without a synchronising clock signal [46].

## 4.3 JOSELITO: Number of Model Details Versus Simulation Speed

JOSELITO is a simplified NoC model that uses Payload Abstraction Technique (PAT) and allows the performance evaluation of a NoC using both simulation and analytical methods. Even if JOSELITO uses the same UML interactions as RENATO, it is more abstract. The PAT decreases the simulation time of JOSELITO in comparison with RENATO, because it reduces the number of communication events by abstracting the payload and therefore omitting the flit by flit payload forwarding. Whereas RENATO forwards all packets flit by flit, JOSELITO defines the packet as a header and a trailer and uses an analytical method for denoting the transmission time of the payload, which is actually the packet trailer release time (PTRT) [85].

Using JOSELITO, three different transmission scenarios are possible: blocking free, header blocking, or header and trailer blocking. In the blocking free scenario no resource conflicts occur. Therefore, the latency and throughput can be measured with no loss of accuracy. The packet header can be blocked if the input buffer of the next router on the header's way is full or the output port of the current router is used by another packet. If the header cannot proceed further within the time the trailer is released and reaches the header, also the trailer is blocked. Both blocking situations increase the possibility of the loss of accuracy in the latency evaluation, because either the header or trailer may block other packets [85].

JOSELITO performs in average 2.3 times faster than RENATO in 88 per cent of the test cases. Moreover, when compared to the results of HER-MES, JOSELITO has 5.26 per cent error in latency and 0.1 per cent error in throughput [85]. Moreover, the difference in the average energy consumption between HERMES and JOSELITO is close to zero per cent (0.001247 mJ) [82].

## 4.4 BOÇA: Analytical Calculation of Communication Latency

BOÇA is a fully analytical model and the most abstract of the NoC models used in the simulation cases used in Chapter 7. A BOÇA model is parameterised with the network topology and it uses that information to analytically calculate the latency of each communication that happens. BOÇA disregards any interference between different traffic. Although being a very simplified model, BOÇA enables fast simulation and early analysis of the effect of the network topology or different application mappings [67].

When simulating an application model on the abstract platform models, hundreds of actors are simulated. As the simulation case in section 7.2 indicates, there is a clear need for more abstract models, such as BOÇA, at least as long as the system is modelled and simulated within the Ptolemy II framework.

## 5. UML EXTENSION TO THE PTOLEMY II FRAMEWORK

This Chapter covers first how UML sequence diagrams can be encapsulated inside the Ptolemy II's composite actors and then how the execution semantics are assigned to the sequence diagrams in order to create executable UML models. The work and ideas presented in this Chapter are not carried out by the author; the starting point of the contribution of this thesis was the already existing idea and work of simulating UML sequence diagrams within the Ptolemy II framework.

Most attempts of using UML as a system level language use either static analysis, code generation, or manual transformation into an executable form. Static analysis provides designers with information they can use when building models for instance with SystemC or implementing systems, whereas code generation requires model transformation. A manual transformation is however a slow and error-prone task. Even though UML lacks execution semantics, actor-orientation has the coexistence of multiple execution semantics as its major feature. Therefore, it is reasonable to have a joint approach of UML and actor orientation where the shortcomings of one of them are compensated by the strengths of the other [45].

# 5.1 Encapsulating UML Sequence Diagrams Inside Composite Actors

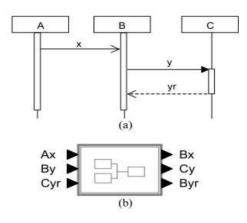

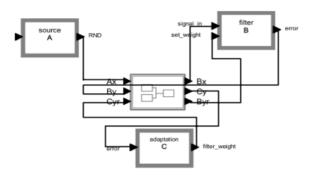

Figure 8 depicts a UML sequence diagram with one asynchronous and one synchronous message (messages x and y respectively). When the sequence

Fig. 8. Encapsulating a UML sequence diagram inside a composite actor [44] ©IEEE, 2006

diagram is encapsulated inside a composite actor, input and output ports are created for each message so that one input and output port is created for the asynchronous message (ports Ax and Bx in Figure 8), whereas two input and output ports are created for each synchronous message (ports By, Cy, Cyr, and Byr in Figure 8).

The input ports are connected to the source of the message while output ports are connected to the receiver of the message, as depicted in Figure 9 [44]. This can be used for the creation of generic communication patterns that are reusable in various application domains in a similar way that Gamma defines in [31].

Each lifeline of the UML sequence diagram represents an application actor: As seen in Figures 8 and 9, lifeline A represents the actor "source A", lifeline B the actor "filter B", and lifeline C the actor "adaptation C". Moreover, the messages between the lifelines in the sequence diagram contain the data tokens that the actors send to each other. The sequence diagram defines the sequence of the messages between actors and the director associated with the sequence diagram enforces their ordering [44].

Fig. 9. Actors connected to the input and output ports of a composite actor [44] ©IEEE, 2006

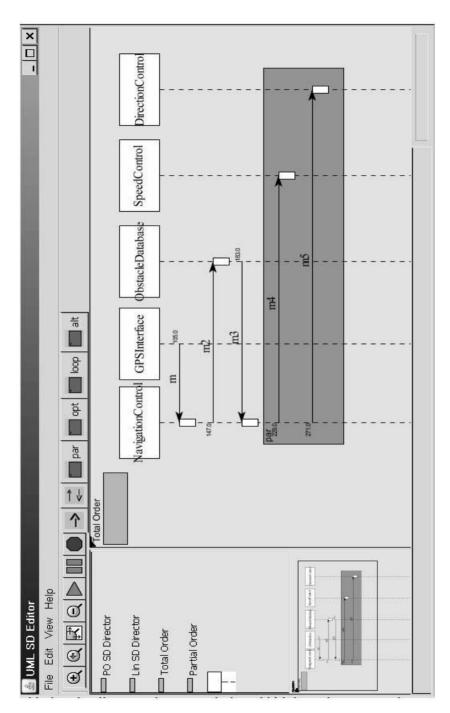

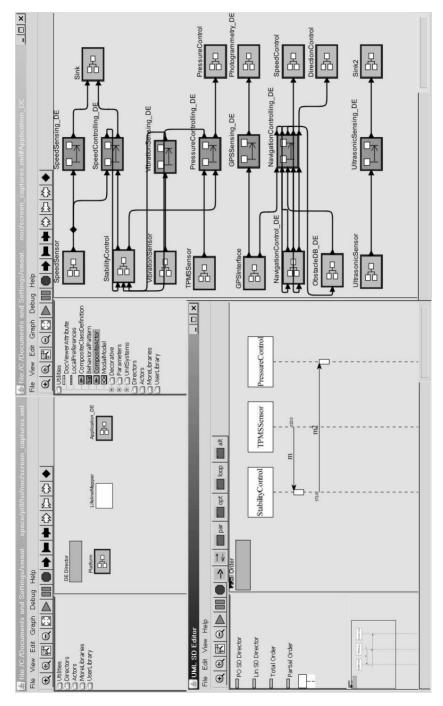

The Ptolemy II framework's visual editor, Vergil, was extended to support the description of UML sequence diagrams as seen in Figure 10 [44]. In the Figure, all directors on the left, the lifelines, messages (both synchronous and asynchronous), and the Combined Fragments (CFs) belong to the extension: the directors PO SD Director and Lin SD Director, lifelines, messages, and the parallel CF (par) were added within the work described in [44]. The directors Total Order, Partial Order, optional, loop, and alternative CFs (as well as the functionality of all the CFs) were added later, within the work described from Chapter 6 onwards.

## 5.2 Simulating UML Sequence Diagrams within Executable System Models

Indrusiak et al. describe how to directly validate UML models by combining them with executable system models in [44], [45], and [48]. The Ptolemy II framework's hierarchically heterogeneous modelling style that allows the

Fig. 10. UML editor extension to the Ptolemy II framework

inclusion of different execution semantics for each hierarchical level enables the execution of UML sequence diagrams.

When UML sequence diagrams are encapsulated inside composite actors, in addition to the creation of the input and output ports, the sequence diagrams need to implement a firing scheme so that it can be simulated with other actors and commanded by a director. The firing scheme depends on the precedence of messages (the precedence of the message occurrence specification within a lifeline). The formalism behind sequence diagrams does not formally determine the precedence between messages that are not sent and received by the same lifeline. However, in that case, a total ordering of messages can be achieved by taking into account the messages' position on the y-axis of the lifeline, since a lifeline has a temporal dimension. That is, time passes when going downwards along the lifeline [45].

The firing scheme determines in which order the tokens arriving at the input ports of the composite actor containing the sequence diagram are forwarded to the respective output ports of the actor. On each firing, the sequence diagram triggers all messages that have tokens in their respective input port and whose all preceding messages have been triggered. The firing scheme of each opaque composite actor is modelled by a director. It is possible to create directors implementing different firing schemes, such as total order (director Lin SD Director in Figure 10) or partial order (director PO SD Director) [45].